#### (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-71204 (P2008-71204A)

(43) 公開日 平成20年3月27日(2008.3.27)

(51) Int.Cl. F I テーマコード (参考) GO6F 17/50 (2006.01) GO6F 17/50 666V 5BO46

GO6F 17/50 662G GO6F 17/50 658V

審査請求 有 請求項の数 43 OL (全 29 頁)

(21) 出願番号 特願2006-250076 (P2006-250076) (22) 出願日 平成18年9月14日 (2006. 9.14) (71) 出願人 500174247

エルピーダメモリ株式会社

東京都中央区八重洲2-2-1

(71) 出願人 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74)代理人 100117341

弁理士 山崎 拓哉

(72) 発明者 片桐 光昭

東京都中央区八重洲2-2-1 エルピー

ダメモリ株式会社内

(72) 発明者 中村 聡

神奈川県横浜市戸塚区吉田町292番地 株式会社日立製作所生産技術研究所内

最終頁に続く

(54) 【発明の名称】半導体チップを含む装置の設計方法、設計支援システム及びプログラム

### (57)【要約】

【課題】入力回路が出力回路に対する負荷として機能する場合において、入力回路を適切にモデル化することにより、必要とする設計変更の判断等を精度良く行うことのできる設計方法を提案すること。

【解決手段】入力回路として動作する第1半導体チップ10と、出力回路として動作する第2半導体チップ20と、調整対象となる調整対象系とを備えた装置の設計方法において、入力パッド11と電源パッド12との間に接続された容量14及び入力パッド11とグランドパッド13との間に接続された容量15のみならず、電源パッド12とグランドパッド13との間に接続された容量17をも考慮して第1半導体チップ10を周波数領域で表現するようにして作成された入力回路チップモデルを用いてシミュレーションを行い、問題点の特定等を行う

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

入力パッド、第1電源パッド及び第1グランドパッドを有し且つ入力回路として動作する第1半導体チップと、前記入力パッドに電気的に接続された出力パッド、第2電源パッド及び第2グランドパッドを有し且つ出力回路として動作する第2半導体チップと、前記第1半導体チップ及び前記第2半導体チップに接続され且つ調整対象となる調整対象系とを備えた装置の設計方法であって、

前記入力パッドと前記第1電源パッドとの間に接続された第1容量及び前記入力パッドと前記第1グランドパッドとの間に接続された第2容量のみならず前記第1電源パッドと前記第1グランドパッドとの間に接続されたチップ内部容量をも考慮して前記第1半導体チップを周波数領域で表現するようにして作成された入力回路チップモデルと、前記第2半導体チップを周波数領域で表現するようにして作成された出力回路チップモデルと、前記調整対象系を周波数領域で表現するようにして作成された調整対象系インピーダンスモデルとに基づいて、調整対象値を導出する調整対象値導出ステップと、

周波数領域において予め定められた制約値と導出された前記調整対象値とを比較して、 当該比較結果に基づき前記調整対象系に対する設計指針を決定する設計指針決定ステップ と

を備える設計方法。

## 【請求項2】

前記調整対象値導出ステップは、

前記第1容量と前記第2容量と前記チップ内部容量を備えた第1入力回路チップモデルと、前記入力パッドと前記第1グランドパッドとの間に接続され且つ前記第1容量の容量値と前記第2容量の容量値とを加算してなる容量値を有する第3容量を備えた第2入力回路チップモデルのいずれか一方を、前記調整対象系の設計上の情報である調整対象情報に基づいて、前記入力回路チップモデルとして選択する入力回路チップモデル選択ステップを備えている、請求項1記載の設計方法。

## 【請求項3】

前記調整対象系が、前記第1半導体チップ及び前記第2半導体チップを備えた半導体パッケージにおける前記第1半導体チップ及び前記第2半導体チップを除いた部分と、前記半導体パッケージを搭載するプリント配線基板である場合であって、前記半導体パッケージにおける前記第1電源パッドと前記第2電源パッドの間を実質的にオープンとみなすことができ、且つ、前記プリント配線基板における前記第1電源パッドと前記第2電源パッドの間を実質的にオープンとみなすことができる場合、前記入力回路チップモデル選択ステップは、前記入力回路チップモデルとして前記第2入力回路チップモデルを選択する、請求項2記載の設計方法。

#### 【請求項4】

前記調整対象値導出ステップは、前記入力回路チップモデルとして、前記入力パッドと前記第 1 グランドパッドとの間に接続され且つ前記第 1 容量の容量値と前記第 2 容量の容量値とを加算してなる容量値を有する第 3 容量を備えたモデルを用いる、請求項 1 記載の設計方法。

## 【請求項5】

前記第3容量の容量値は、前記入力パッドと前記第1グランドパッドにプローブを当てて実測した場合に得られる容量値に実質的に等しい、請求項2乃至請求項4のいずれかに記載の設計方法。

#### 【請求項6】

前記第2半導体チップが、前記第2電源パッドと前記出力パッドとの間に接続されたpMOS回路及び前記第2グランドパッドと前記出力パッドとの間に接続されたnMOS回路からなる出力部、並びに前記第2電源パッドと前記第2グランドパッドとの間に前記出力部と並列に接続された内部インピーダンスを備えている場合において、

前記調整対象値導出ステップは、

10

20

30

前記第2半導体チップの出力値がローレベルからハイレベルに遷移する第1遷移ケースに対応させて前記第2半導体チップを周波数領域にて表現するようにして作成された第1出力回路チップモデルと前記調整対象系インピーダンスモデル及び前記入力回路チップモデルに基づいて第1調整対象値を算出する一方、前記第2半導体チップの出力値がハイレベルからローレベルに遷移する第2遷移ケースに対応させて前記第2半導体チップを周波数領域にて表現するようにして作成された第2出力回路チップモデルと前記調整対象系インピーダンスモデル及び前記入力回路チップモデルに基づいて第2調整対象値を算出する調整対象値算出ステップと、

前記第1調整対象値と前記第2調整対象値を比較し、調整必要性のより高い一方を前記調整対象値として選択する調整対象値選択ステップと

を備えている、請求項1乃至請求項5のいずれかに記載の設計方法。

#### 【請求項7】

前記第1遷移ケースを想定して設定された制約値である第1制約値と前記第2遷移ケースを想定して設定された制約値である第2制約値のうち、前記調整対象値に対応する遷移ケースに関する制約値を、前記設計指針決定ステップにおける前記予め定められた制約値として選択する制約値選択ステップを更に備える、

請求項6記載の設計方法。

#### 【請求項8】

前記調整対象値算出ステップは、前記第1調整対象値及び前記第2調整対象値として、それぞれ、前記第1遷移ケースにおける電源/GND電圧変動スペクトラム及び前記第2遷移ケースにおける電源/GND電圧変動スペクトラムを算出するものである、請求項6又は請求項7記載の設計方法。

#### 【請求項9】

前記第2半導体チップに関するチップ情報に基づいて、前記第1出力回路チップモデル及び前記第2出力回路チップモデルを作成するチップモデル作成ステップと、前記調整対象系に関する調整対象系情報に基づいて、前記調整対象系インピーダンスモデルを作成するインピーダンスモデル作成ステップとを更に備えており、

前記調整対象値算出ステップは、前記第1出力回路チップモデルを前記調整対象系インピーダンスモデルに接続して前記第1調整対象値を算出すると共に前記第2出力回路チップモデルを前記調整対象系インピーダンスモデルに接続して前記第2調整対象値を算出する、請求項6乃至請求項8のいずれかに記載の設計方法。

### 【請求項10】

前記チップモデル作成ステップは、

前記第2電源パッドと前記第2グランドパッドとの間に前記内部インピーダンスを接続し、オン状態の前記pMOS回路をインピーダンス表現してなる第1pMOS回路インピーダンスと前記第1遷移ケースにおける変動電流値を考慮した電流源である第1電流源とを前記第2電源パッドと前記出力パッドとの間に並列接続し、前記nMOS回路をインピーダンス表現してなる第1nMOS回路インピーダンスを前記出力パッドと前記第2グランドパッドとの間に接続することにより、前記第1出力回路チップモデルを作成する第1出力回路チップモデル作成ステップと、

前記第2電源パッドと前記第2グランドパッドとの間に前記内部インピーダンスを接続し、オン状態の前記 n M O S 回路をインピーダンス表現してなる第2n M O S 回路インピーダンスと前記第2遷移ケースにおける変動電流値を考慮した電流源である第2電流源とを前記出力パッドと第2電源パッドとの間に並列接続し、前記 p M O S 回路をインピーダンス表現してなる p M O S 回路インピーダンスを前記第2電源パッドと前記出力パッドとの間に接続することにより、前記第2出力回路チップモデルを作成する第2出力回路チップモデル作成ステップと

を備えている、請求項9記載の設計方法。

#### 【請求項11】

前記第1出力回路チップモデル作成ステップは、

10

20

30

電源電圧変動用の前記第1出力回路チップモデルを作成する場合において、オフ状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第1n M O S 回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第1n M O S 回路インピーダンスよりも遥かに小さいと仮定して、前記第1遷移ケースにおいて前記第2電源パッドを流れる電流のほとんどが、前記第1pMOS回路インピーダンスと前記所定の外部負荷モデルに流れるものとして算出した電流源を前記第1電流源として用い、

GND電圧変動用の前記第1出力回路チップモデルを作成する場合においては、オン状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第1 n M O S 回路インピーダンスとして用いると共に、前記出力パッドと前記グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第1 n M O S 回路インピーダンスよりも遥かに大きいと仮定して、前記第1遷移ケースにおいて前記第2グランドパッドを流れる電流のほとんどが、前記第1 p M O S 回路インピーダンスと前記第1 n M O S 回路インピーダンスに流れるものとして算出した電流源を前記第1電流源として用いるものであり、

前記第2出力回路チップモデル作成ステップは、

前記電源電圧用の前記第2出力回路チップモデルを作成する場合において、オン状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第2 n M O S 回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第2 n M O S 回路インピーダンスよりも遥かに大きいと仮定して、前記第2遷移ケースにおいて前記第2電源パッドを流れる電流のほとんどが、前記第2 p M O S 回路インピーダンスと前記第2 n M O S 回路インピーダンスに流れるものとして算出した電流源を第2電流源として用い、

GND電圧変動用の前記第2出力回路チップモデルを作成する場合において、オフ状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第2n M O S 回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第2p M O S 回路インピーダンスよりも遥かに小さいと仮定して、前記第2遷移ケースにおいて前記第2グランドパッドを流れる電流のほとんどが、前記第2n M O S 回路インピーダンスと前記所定の外部負荷モデルを流れるものとして算出した電流源を前記第2電流源として用いるものである、

請求項10記載の設計方法。

### 【請求項12】

前記所定の外部負荷モデルは、前記出力パッドと前記入力パッドの間のインダクタンスと、前記第1容量の容量値と前記第2容量の容量値とを加算してなる容量値を有する第3容量とを直接に接続してなるものである、

請求項11記載の設計方法。

#### 【請求項13】

前記調整対象値算出ステップは、前記調整対象系インピーダンスモデルと前記入力回路チップモデル及び前記第1出力回路チップモデルを接続して、閉路回路方程式を解くことにより、前記第1調整対象値を算出する一方、前記調整対象系インピーダンスモデルと前記入力回路チップモデル及び前記第2出力回路チップモデルを接続して、閉路回路方程式を解くことにより、前記第2調整対象値を算出する、

請求項6乃至請求項12のいずれかに記載の設計方法。

#### 【請求項14】

前記設計指針決定ステップは、前記調整対象値が前記制約値を超えてしまうような周波数部分に対応する前記調整対象系の部位を調整対象箇所として前記設計指針を決定する、 請求項1乃至請求項13のいずれかに記載の設計方法。 10

20

30

40

#### 【請求項15】

入力パッド、電源パッド及びグランドパッドを有し且つ入力回路として動作する第1半 導体チップと、前記入力パッドに電気的に接続された出力パッドを有し且つ出力回路とし て動作する第2半導体チップとを備えた装置の設計方法であって、

前記入力パッドと前記電源パッドの間に接続された第 1 容量及び前記入力パッドと前記グランドパッドの間に接続された第 2 容量の 2 つの容量のみならず前記電源パッドと前記グランドパッドの間に接続されたチップ内部容量の存在をも考慮してなる入力回路チップモデルを用いたシミュレーションを行って設計指針を決定し、当該設計指針に基づいた設計を行う、設計方法。

#### 【請求項16】

入力パッド、第1電源パッド及び第1グランドパッドを有し且つ入力回路として動作する第1半導体チップと、前記入力パッドに電気的に接続された出力パッド、第2電源パッド及び第2グランドパッドを有し且つ出力回路として動作する第2半導体チップと、前記第1半導体チップ及び前記第2半導体チップに接続され且つ調整対象となる調整対象系とを備えた装置の設計支援システムであって、

前記入力パッドと前記第1電源パッドとの間に接続された第1容量及び前記入力パッドと前記第1グランドパッドとの間に接続された第2容量のみならず前記第1電源パッドと前記第1グランドパッドとの間に接続されたチップ内部容量をも考慮して前記第1半導体チップを周波数領域で表現するようにして作成された入力回路チップモデルと、前記第2半導体チップを周波数領域で表現するようにして作成された出力回路チップモデルと、前記調整対象系を周波数領域で表現するようにして作成された調整対象系インピーダンスモデルとに基づいて、調整対象値を導出する調整対象値導出部と、

周波数領域において予め定められた制約値を提供する制約値提供部と、

該制約値と導出された前記調整対象値とを比較して、当該比較結果に基づき前記調整対象系に対する設計支援情報を決定する設計支援情報決定部と、

前記設計支援情報を表示する表示部と

を備える設計支援システム。

#### 【請求項17】

前記調整対象値導出部は、

前記第1容量と前記第2容量と前記チップ内部容量を備えた第1入力回路チップモデルを提供すると共に、前記入力パッドと前記第1グランドパッドとの間に接続され且つ前記第1容量の容量値と前記第2容量の容量値とを加算してなる容量値を有する第3容量を備えた第2入力回路チップモデルを提供する入力回路チップモデル提供部と、

前記第1入力回路チップモデル及び前記第2入力回路チップモデルのいずれか一方を、前記調整対象系の設計上の情報である調整対象情報に基づいて、前記入力回路チップモデルとして選択する入力回路チップモデル選択部と

を 備 え て い る 、 請 求 項 1 6 記 載 の 設 計 支 援 シ ス テ ム 。

#### 【請求項18】

前記調整対象系が、前記第1半導体チップ及び前記第2半導体チップを備えた半導体パッケージにおける前記第1半導体チップ及び前記第2半導体チップを除いた部分と、前記半導体パッケージを搭載するプリント配線基板である場合であって、前記半導体パッケージにおける前記第1電源パッドと前記第2電源パッドの間を実質的にオープンとみなすことができ、且つ、前記プリント配線基板における前記第1電源パッドと前記第2電源パッドの間を実質的にオープンとみなすことができる場合、前記入力回路チップモデル選択部は、前記入力回路チップモデルとして前記第2入力回路チップモデルを選択する、請求項17記載の設計支援システム。

#### 【請求項19】

前記調整対象値導出部は、前記入力回路チップモデルとして、前記入力パッドと前記第 1 グランドパッドとの間に接続され且つ前記第 1 容量の容量値と前記第 2 容量の容量値と を加算してなる容量値を有する第 3 容量を備えたモデルを用いる、請求項 1 6 記載の設計 10

20

30

40

支援システム。

#### 【請求項20】

前記第3容量の容量値は、前記入力パッドと前記第1グランドパッドにプローブを当てて実測した場合に得られる容量値に実質的に等しい、請求項17乃至請求項19のいずれかに記載の設計支援システム。

#### 【請求項21】

前記第2半導体チップが、前記第2電源パッドと前記出力パッドとの間に接続された p M O S 回路及び前記第2グランドパッドと前記出力パッドとの間に接続された n M O S 回路からなる出力部、並びに前記第2電源パッドと前記第2グランドパッドとの間に前記出力部と並列に接続された内部インピーダンスを備えている場合において、

前記調整対象値導出部は、

前記第2半導体チップの出力値がローレベルからハイレベルに遷移する第1遷移ケースに対応させて前記第2半導体チップを周波数領域にて表現するようにして作成された第1出力回路チップモデルを提供すると共に、前記第2半導体チップの出力値がハイレベルからローレベルに遷移する第2遷移ケースに対応させて前記第2半導体チップを周波数領域にて表現するようにして作成された第2出力回路チップモデルを提供する出力回路チップモデル提供部と、

前記第1出力回路チップモデルと前記調整対象系インピーダンスモデル及び前記入力回路チップモデルに基づいて第1調整対象値を算出する一方、前記第2出力回路チップモデルと前記調整対象系インピーダンスモデル及び前記入力回路チップモデルに基づいて第2調整対象値を算出する調整対象値算出部と、

前記第1調整対象値と前記第2調整対象値を比較し、調整必要性のより高い一方を前記調整対象値として選択する調整対象値選択部と

を 備 え て い る 、 請 求 項 1 6 乃 至 請 求 項 2 0 の い ず れ か に 記 載 の 設 計 支 援 シ ス テ ム 。

#### 【請求項22】

前記調整対象値選択部は、前記第1調整対象値と前記第2調整対象値のいずれを選択しかたを示す情報を前記制約値提供部に対して調整対象値選択情報として出力するものであり。

前記制約値提供部は、

前記第1遷移ケースを想定して設定された制約値である第1制約値と前記第2遷移ケースを想定して設定された制約値である第2制約値を少なくとも保持する制約値保持部と、前記調整対象値選択情報に従って、前記選択された調整対象値に対応する遷移ケースに関する前記第1制約値又は前記第2制約値のいずれか一方を、前記予め定められた制約値として選択する制約値選択部と

を備える、請求項21記載の設計支援システム。

#### 【請求項23】

前記調整対象値算出部は、前記第1調整対象値及び前記第2調整対象値として、それぞれ、前記第1遷移ケースにおける電源/GND電圧変動スペクトラム及び前記第2遷移ケースにおける電源/GND電圧変動スペクトラムを算出するものである、

請求項21又は請求項22記載の設計支援システム。

## 【請求項24】

前記出力回路チップモデル提供部は、

前記第2電源パッドと前記第2グランドパッドとの間に前記内部インピーダンスを接続し、オン状態の前記pMOS回路をインピーダンス表現してなる第1pMOS回路インピーダンスと前記第1遷移ケースにおける変動電流値を考慮した電流源である第1電流源とを前記第2電源パッドと前記出力パッドとの間に並列接続し、前記nMOS回路をインピーダンス表現してなる第1nMOS回路インピーダンスを前記出力パッドと前記第2グランドパッドとの間に接続することにより、前記第1出力回路チップモデルを作成する第1出力回路チップモデル作成部と、

前記第2電源パッドと前記第2グランドパッドとの間に前記内部インピーダンスを接

10

20

30

40

続し、オン状態の前記 n M O S 回路をインピーダンス表現してなる第 2 n M O S 回路インピーダンスと前記第 2 遷移ケースにおける変動電流値を考慮した電流源である第 2 電流源とを前記出力パッドと第 2 電源パッドとの間に並列接続し、前記 p M O S 回路をインピーダンス表現してなる p M O S 回路インピーダンスを前記第 2 電源パッドと前記出力パッドとの間に接続することにより、前記第 2 出力回路チップモデルを作成する第 2 出力回路チップモデル作成部と

を 備 え て い る 、 請 求 項 2 1 乃 至 請 求 項 2 3 の い ず れ か に 記 載 の 設 計 支 援 シ ス テ ム 。

#### 【請求項25】

前記第1出力回路チップモデル作成部は、

電源電圧変動用の前記第1出力回路チップモデルを作成する場合において、オフ状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第1n M O S 回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第1n M O S 回路インピーダンスよりも遥かに小さいと仮定して、前記第1遷移ケースにおいて前記第2電源パッドを流れる電流のほとんどが、前記第1pMOS回路インピーダンスと前記所定の外部負荷モデルに流れるものとして算出した電流源を前記第1電流源として用い、

GND電圧変動用の前記第1出力回路チップモデルを作成する場合においては、オン状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第1 n M O S 回路インピーダンスとして用いると共に、前記出力パッドと前記グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第1 n M O S 回路インピーダンスよりも遥かに大きいと仮定して、前記第1遷移ケースにおいて前記第2グランドパッドを流れる電流のほとんどが、前記第1 p M O S 回路インピーダンスと前記第1 n M O S 回路インピーダンスに流れるものとして算出した電流源を前記第1電流源として用いるものであり、

前記第2出力回路チップモデル作成部は、

前記電源電圧用の前記第2出力回路チップモデルを作成する場合において、オン状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第2n M O S 回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第2n M O S 回路インピーダンスよりも遥かに大きいと仮定して、前記第2遷移ケースにおいて前記第2電源パッドを流れる電流のほとんどが、前記第2pMOS回路インピーダンスと前記第2n M O S 回路インピーダンスに流れるものとして算出した電流源を第2電流源として用い、

GND電圧変動用の前記第2出力回路チップモデルを作成する場合において、オフ状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第2 n M O S 回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第2 p M O S 回路インピーダンスよりも遥かに小さいと仮定して、前記第2遷移ケースにおいて前記第2グランドパッドを流れる電流のほとんどが、前記第2 n M O S 回路インピーダンスと前記所定の外部負荷モデルを流れるものとして算出した電流源を前記第2電流源として用いるものである、

請求項24記載の設計支援システム。

## 【請求項26】

前記所定の外部負荷モデルは、前記出力パッドと前記入力パッドの間のインダクタンスと、前記第1容量の容量値と前記第2容量の容量値とを加算してなる容量値を有する第3容量とを直接に接続してなるものである、

請求項25記載の設計支援システム。

#### 【請求項27】

前記調整対象値算出部は、前記調整対象系インピーダンスモデルと前記入力回路チップ

10

20

30

40

モデル及び前記第1出力回路チップモデルを接続して、閉路回路方程式を解くことにより、前記第1調整対象値を算出する一方、前記調整対象系インピーダンスモデルと前記入力回路チップモデル及び前記第2出力回路チップモデルを接続して、閉路回路方程式を解くことにより、前記第2調整対象値を算出する、

請求項21乃至請求項26のいずれかに記載の設計支援システム。

#### 【請求項28】

前記設計支援情報決定部は、前記調整対象値が前記制約値を超えてしまうような周波数部分に対応する前記調整対象系の部位を調整対象箇所として前記設計支援情報を決定する

請求項16乃至請求項27のいずれかに記載の設計支援システム。

#### 【請求項29】

演算部、記憶部及び表示部を備えたコンピュータシステムにおいて前記演算部に対して所定の処理を実行させ前記コンピュータシステムを所定の装置の設計支援システムとして機能させるためのプログラムであって、前記所定の装置は、入力パッド、第1電源パッド及び第1グランドパッドを有し且つ入力回路として動作する第1半導体チップと、前記入力パッドに電気的に接続された出力パッド、第2電源パッド及び第2グランドパッドを有し且つ出力回路として動作する第2半導体チップと、前記第1半導体チップ及び前記第2半導体チップに接続され且つ調整対象となる調整対象系とを備えている、プログラムにおいて、

前記所定の処理は、

前記入力パッドと前記第1電源パッドとの間に接続された第1容量及び前記入力パッドと前記第1グランドパッドとの間に接続された第2容量のみならず前記第1電源パッドと前記第1グランドパッドとの間に接続されたチップ内部容量をも考慮して前記第1半導体チップを周波数領域で表現するようにして作成された入力回路チップモデルと、前記第2半導体チップを周波数領域で表現するようにして作成された出力回路チップモデルと、前記調整対象系を周波数領域で表現するようにして作成された調整対象系インピーダンスモデルとに基づいて、調整対象値を導出する調整対象値導出ステップと、

周波数領域において予め定められた制約値と導出された前記調整対象値とを比較して、 当該比較結果に基づき前記調整対象系に対する設計支援情報を決定する設計支援情報決定 ステップと、

前記設計支援情報を前記表示部に表示する表示ステップとを備える、プログラム。

#### 【請求項30】

前記調整対象値導出ステップは、

前記第1容量と前記第2容量と前記チップ内部容量を備えた第1入力回路チップモデルと、前記入力パッドと前記第1グランドパッドとの間に接続され且つ前記第1容量の容量値と前記第2容量の容量値とを加算してなる容量値を有する第3容量を備えた第2入力回路チップモデルのいずれか一方を、前記調整対象系の設計上の情報である調整対象情報に基づいて、前記入力回路チップモデルとして選択する入力回路チップモデル選択ステップを備えている、請求項29記載のプログラム。

## 【請求項31】

前記調整対象系が、前記第1半導体チップ及び前記第2半導体チップを備えた半導体パッケージにおける前記第1半導体チップ及び前記第2半導体チップを除いた部分と、前記半導体パッケージを搭載するプリント配線基板である場合であって、前記半導体パッケージにおける前記第1電源パッドと前記第2電源パッドの間を実質的にオープンとみなすことができ、且つ、前記プリント配線基板における前記第1電源パッドと前記第2電源パッドの間を実質的にオープンとみなすことができる場合、前記入力回路チップモデル選択ステップは、前記入力回路チップモデルとして前記第2入力回路チップモデルを選択する、請求項30記載のプログラム。

### 【請求項32】

10

20

30

前記調整対象値導出ステップは、前記入力回路チップモデルとして、前記入力パッドと前記第1グランドパッドとの間に接続され且つ前記第1容量の容量値と前記第2容量の容量値とを加算してなる容量値を有する第3容量を備えたモデルを用いる、請求項29記載のプログラム。

#### 【請求項33】

前記第3容量の容量値は、前記入力パッドと前記第1グランドパッドにプローブを当てて実測した場合に得られる容量値に実質的に等しい、請求項30乃至請求項32のいずれかに記載のプログラム。

#### 【請求項34】

前記第2半導体チップが、前記第2電源パッドと前記出力パッドとの間に接続されたpMOS回路及び前記第2グランドパッドと前記出力パッドとの間に接続されたnMOS回路からなる出力部、並びに前記第2電源パッドと前記第2グランドパッドとの間に前記出力部と並列に接続された内部インピーダンスを備えている場合において、

前記調整対象値導出ステップは、

前記第2半導体チップの出力値がローレベルからハイレベルに遷移する第1遷移ケースに対応させて前記第2半導体チップを周波数領域にて表現するようにして作成された第1出力回路チップモデルと前記調整対象系インピーダンスモデル及び前記入力回路チップモデルに基づいて第1調整対象値を算出する一方、前記第2半導体チップの出力値がハイレベルからローレベルに遷移する第2遷移ケースに対応させて前記第2半導体チップを周波数領域にて表現するようにして作成された第2出力回路チップモデルと前記調整対象系インピーダンスモデル及び前記入力回路チップモデルに基づいて第2調整対象値を算出する調整対象値算出ステップと、

前記第1調整対象値と前記第2調整対象値を比較し、調整必要性のより高い一方を前記調整対象値として選択する調整対象値選択ステップと

を備えている、請求項29乃至請求項33のいずれかに記載のプログラム。

#### 【請求項35】

前記記憶部には、前記第1遷移ケースを想定して設定された制約値である第1制約値と前記第2遷移ケースを想定して設定された制約値である第2制約値が少なくとも保持されており、

前記所定の処理は、前記調整対象値選択ステップにより選択された調整対象値に対応する遷移ケースに関する前記第1制約値又は前記第2制約値のいずれか一方を、前記設計指針決定ステップにおいて前記比較に用いる前記予め定められた制約値として選択する制約値選択ステップを更に備える、

請求項34記載のプログラム。

### 【請求項36】

前記調整対象値算出ステップは、前記第1調整対象値及び前記第2調整対象値として、それぞれ、前記第1遷移ケースにおける電源/GND電圧変動スペクトラム及び前記第2遷移ケースにおける電源/GND電圧変動スペクトラムを算出するものである、

請求項34又は請求項35記載のプログラム。

#### 【請求項37】

前記所定の処理は、前記第2半導体チップに関するチップ情報に基づいて、前記第1出力回路チップモデル及び前記第2出力回路チップモデルを作成するチップモデル作成ステップと、前記調整対象系に関する調整対象系情報に基づいて、前記調整対象系インピーダンスモデルを作成するインピーダンスモデル作成ステップとを更に備えており、

前記調整対象値算出ステップは、前記第1出力回路チップモデルを前記調整対象系インピーダンスモデルに接続して前記第1調整対象値を算出すると共に前記第2出力回路チップモデルを前記調整対象系インピーダンスモデルに接続して前記第2調整対象値を算出する

請求項34乃至36のいずれかに記載のプログラム。

#### 【請求項38】

10

20

30

00

20

30

40

50

前記チップモデル作成ステップは、

前記第2電源パッドと前記第2グランドパッドとの間に前記内部インピーダンスを接続し、オン状態の前記 p M O S 回路をインピーダンス表現してなる第1 p M O S 回路インピーダンスと前記第1遷移ケースにおける変動電流値を考慮した電流源である第1電流源とを前記第2電源パッドと前記出力パッドとの間に並列接続し、前記 n M O S 回路をインピーダンス表現してなる第1 n M O S 回路インピーダンスを前記出力パッドと前記第2グランドパッドとの間に接続することにより、前記第1出力回路チップモデルを作成する第1出力回路チップモデル作成ステップと、

前記第2電源パッドと前記第2グランドパッドとの間に前記内部インピーダンスを接続し、オン状態の前記 n M O S 回路をインピーダンス表現してなる第2 n M O S 回路インピーダンスと前記第2遷移ケースにおける変動電流値を考慮した電流源である第2電流源とを前記出力パッドと第2電源パッドとの間に並列接続し、前記 p M O S 回路をインピーダンス表現してなる p M O S 回路インピーダンスを前記第2電源パッドと前記出力パッドとの間に接続することにより、前記第2出力回路チップモデルを作成する第2出力回路チップモデル作成ステップと

を備えている、請求項37記載のプログラム。

#### 【請求項39】

前記第1出力回路チップモデル作成ステップは、

電源電圧変動用の前記第1出力回路チップモデルを作成する場合において、オフ状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第1n M O S 回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第1n M O S 回路インピーダンスよりも遥かに小さいと仮定して、前記第1遷移ケースにおいて前記第2電源パッドを流れる電流のほとんどが、前記第1pMOS回路インピーダンスと前記所定の外部負荷モデルに流れるものとして算出した電流源を前記第1電流源として用い、

GND電圧変動用の前記第1出力回路チップモデルを作成する場合においては、オン状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第1 n M O S 回路インピーダンスとして用いると共に、前記出力パッドと前記グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第1 n M O S 回路インピーダンスよりも遥かに大きいと仮定して、前記第1遷移ケースにおいて前記第2グランドパッドを流れる電流のほとんどが、前記第1 p M O S 回路インピーダンスと前記第1 n M O S 回路インピーダンスに流れるものとして算出した電流源を前記第1電流源として用いるものであり、

前記第2出力回路チップモデル作成ステップは、

前記電源電圧用の前記第2出力回路チップモデルを作成する場合において、オン状態の前記 n M O S 回路に対応する前記 n M O S 回路インピーダンスを前記第2n M O S 回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第2n M O S 回路インピーダンスよりも遥かに大きいと仮定して、前記第2遷移ケースにおいて前記第2電源パッドを流れる電流のほとんどが、前記第2pMOS回路インピーダンスと前記第2n M O S 回路インピーダンスに流れるものとして算出した電流源を第2電流源として用い、

GND電圧変動用の前記第2出力回路チップモデルを作成する場合において、オフ状態の前記nMOS回路に対応する前記nMOS回路インピーダンスを前記第2nMOS回路インピーダンスとして用いると共に、前記第2出力パッドと前記第2グランドパッドとの間に前記所定の外部負荷モデルを接続した上で、該所定の外部負荷モデルのインピーダンスが当該第2pMOS回路インピーダンスよりも遥かに小さいと仮定して、前記第2遷移ケースにおいて前記第2グランドパッドを流れる電流のほとんどが、前記第2nMOS回路インピーダンスと前記所定の外部負荷モデルを流れるものとして算出した電流源を前

記第2電流源として用いるものである、

請求項38記載のプログラム。

#### 【請求項40】

前記所定の外部負荷モデルは、前記出力パッドと前記入力パッドの間のインダクタンスと、前記第1容量の容量値と前記第2容量の容量値とを加算してなる容量値を有する第3容量とを直接に接続してなるものである、

請求項39記載のプログラム。

#### 【請求項41】

前記第1出力回路チップモデル作成ステップは、

電源電圧変動用のモデルを作成する場合において、前記第2半導体チップに関するSPICEモデルを前記第1遷移ケースに関してトランジェント解析することにより得られる電流波形をフーリエ変換して、前記第1遷移ケースにおいて前記電源パッドを流れる電流のスペクトラムを算出し、

GND電圧変動用のモデルを作成する場合において、前記第2半導体チップに関するSPICEモデルを前記第1遷移ケースに関してトランジェント解析することにより得られる電流波形をフーリエ変換して、前記第1遷移ケースにおいて前記グランドパッドを流れる電流のスペクトラムを算出するものであり、

前記第2出力回路チップモデル作成ステップは、

電源電圧変動用のモデルを作成する場合において、前記第2半導体チップに関するSPICEモデルを前記第2遷移ケースに関してトランジェント解析することにより得られる電流波形をフーリエ変換して、前記第2遷移ケースにおいて前記電源パッドを流れる電流のスペクトラムを算出し、

GND電圧変動用のモデルを作成する場合において、前記第2半導体チップに関するSPICEモデルを前記第2遷移ケースに関してトランジェント解析することにより得られる電流波形をフーリエ変換して、前記第2遷移ケースにおいて前記グランドパッドを流れる電流のスペクトラムを算出する

請求項39又は請求項40記載のプログラム。

#### 【請求項42】

前記調整対象値算出ステップは、前記調整対象系インピーダンスモデルと前記第1チップモデルを接続して、閉路回路方程式を解くことにより、前記第1調整対象値を算出する一方、前記調整対象系インピーダンスモデルと前記第2チップモデルを接続して、閉路回路方程式を解くことにより、前記第2調整対象値を算出する、 請求項41記載のプログラム。

#### 【請求項43】

前記設計支援情報決定ステップは、前記調整対象値が前記制約値を超えてしまうような周波数部分に対応する前記調整対象系の部位を調整対象箇所として前記設計支援情報を決定する、

請求項29乃至請求項42のいずれかに記載のプログラム。

【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、半導体チップのパワーインテグリティを目的とした当該半導体チップを含む 装置の設計方法、当該設計方法に従った設計を支援する設計支援システム及びプログラム に関する。

#### 【背景技術】

#### [0002]

半導体チップを含む装置、例えば、半導体パッケージや半導体パッケージをプリント配

10

20

30

00

線基板上に搭載してなる装置の設計を行う場合、半導体チップの電源パッド及び/又はグランドパッドにおける電圧変動を許容値以下としなければならず、その適否を判断するため電圧変動の解析が行われている。

[0003]

従来、かかる電圧変動の解析として、一般的には、SPICEモデルを用いた過渡解析が行われていた。かかる過渡解析の場合、電圧変動が許容値を超えていたときには、例えばレイアウト修正などを行い、再度過渡解析を実行して電圧変動が許容値以下になったか否かを判断するといったことが繰り返し行われる(例えば、特許文献1)。しかしながら、時間領域における解析では、レイアウト修正のたびに過渡解析を行うため、計算量が多く、設計期間の長期化を避けることができない。

[0004]

これに対して、最近では、時間領域ではなく周波数領域における解析を導入しようという試みも提案されている(例えば、特許文献 2)。

[0005]

【特許文献1】特開2004-054522号公報

【特許文献2】特開2005-196406号公報

【発明の開示】

【発明が解決しようとする課題】

[0006]

特許文献 2 に提案された技術は、半導体チップ上のレイアウトを主たる対象としている ものであり、既に設計されてしまった半導体チップを含んでなる装置の設計に適用するの は困難である。

[0007]

既に設計されてしまった半導体チップを含む装置、例えば、半導体パッケージや半導体パッケージをプリント配線基板上に搭載してなる装置の設計において、電圧変動解析の結果を反映させるように設計変更できるのは半導体チップ以外の部分、具体的にはパッケージ配線等であり、パッケージ配線等が設計変更を要するものであるのか否かを精度良く判断するためには、半導体チップを適切にモデル化する必要がある。

[0008]

例えば、一方が入力回路として動作し且つ他方が出力回路として動作する2つの半導体チップにおいて、出力回路の電源/GND電圧変動が生じる原因の一つには、出力回路の出力には、出力回路の過渡電流がある。この過渡電流には、入力回路が出力回路の負荷として機能した結果としての負荷の充放電電流も含まれるので、入力回路についても適切なモデル化をしなければならない。想定したモデルが適切であり負荷の値が現実的なものであれば、シミュレーションの精度も担保されるが、モデルが不適切なためにシミュレーションに用いられた負荷の値が高すぎると例えば過渡解析における出力信号波形は実際のものよりもなまってしまうし、逆に、負荷の値が低すぎると現実には問題ないにもかかわらずシミュレーション上ではオーバーシュートしてしまうといった食い違いを生じさせることとなる。

[0009]

そこで、本発明は、入力回路が出力回路に対する負荷として機能する場合において、入力回路を適切にモデル化することにより、必要とする設計変更の判断等を精度良く行うことのできる設計方法を提案すると共に、当該設計方法に従った設計を支援する設計支援システム及びプログラムを提供することを目的とする。

【課題を解決するための手段】

[0010]

入力パッドとGNDパッドとの間に接続されているものと設計データから理解されうる容量としては、例えば、ESD保護素子の容量がある。しかし、このESD保護素子の容量値は、入力パッドとGNDパッドとにプローブを当てて計測した場合の実測値とは異なっている。この点に気づかずに実測値に基づく容量が入力パッドとGNDパッドとの間に

10

20

30

40

接続されているとして入力回路のモデル化をしてしまうと、上述したような波形なまりが 生じてしまう。

#### [0011]

データから想定しうる容量の値と実測値とに大きな開きがあるのは、電源パッドとGNDパッドとの間に存在している潜在的な電流パスを見落としているからである。電源パッドとGNDパッドとの間には、いわばチップ内部容量とでも言うべき容量が付いており、この容量値は、例えばある種の半導体チップの場合、ESD保護素子の容量値と2,3桁以上も異なっている。チップ内部容量がESD保護素子の容量と2桁も異なる場合、チップ内部容量は事実上短絡されているに等しい。即ち、入力回路の入力パッドに流れ込んできた電流のパスとしては、入力パッド・GNDパッド間に設けられているESD保護素子を通るものと、入力パッド・電源パッド間に設けられているESD保護素子及び内部での短絡)を通るものとの2つの並列パスがあることになる。換言すると、入力パッド・GNDパッド間の電流パスを考えた場合、入力回路の入力パッド・GNDパッド間には、GNDパッド間の電流パスを考えた場合、入力回路の入力パッド・GNDパッド間になり、これが入力パッドとGNDパッド間の実測値となるのである。

#### [0012]

本発明は、上述したような知見に基づいてなされたものであり、具体的には以下に示される設計方法並びに当該設計方法に従った設計を支援する設計支援システム及びプログラムを提供する。

### [0013]

即ち、本発明は、入力パッド、第1電源パッド及び第1グランドパッドを有し且つ入力回路として動作する第1半導体チップと、前記入力パッドに電気的に接続された出力パッド、第2電源パッド及び第2グランドパッドを有し且つ出力回路として動作する第2半導体チップと、前記第1半導体チップ及び前記第2半導体チップに接続され且つ調整対象となる調整対象系とを備えた装置の設計方法であって、

前記入力パッドと前記第1電源パッドとの間に接続された第1容量及び前記入力パッドと前記第1グランドパッドとの間に接続された第2容量のみならず前記第1電源パッドと前記第1グランドパッドとの間に接続されたチップ内部容量をも考慮して前記第1半導体チップを周波数領域で表現するようにして作成された入力回路チップモデルと、前記第2半導体チップを周波数領域で表現するようにして作成された出力回路チップモデルと、前記調整対象系を周波数領域で表現するようにして作成された調整対象系インピーダンスモデルとに基づいて、調整対象値を導出する調整対象値導出ステップと、

周波数領域において予め定められた制約値と導出された前記調整対象値とを比較して、 当該比較結果に基づき前記調整対象系に対する設計指針を決定する設計指針決定ステップ と

を備える設計方法を提供する。

## [0014]

また、本発明は、入力パッド、第1電源パッド及び第1グランドパッドを有し且つ入力回路として動作する第1半導体チップと、前記入力パッドに電気的に接続された出力パッド、第2電源パッド及び第2グランドパッドを有し且つ出力回路として動作する第2半導体チップと、前記第1半導体チップ及び前記第2半導体チップに接続され且つ調整対象となる調整対象系とを備えた装置の設計支援システムであって、

前記入力パッドと前記第1電源パッドとの間に接続された第1容量及び前記入力パッドと前記第1グランドパッドとの間に接続された第2容量のみならず前記第1電源パッドと前記第1グランドパッドとの間に接続されたチップ内部容量をも考慮して前記第1半導体チップを周波数領域で表現するようにして作成された入力回路チップモデルと、前記第2半導体チップを周波数領域で表現するようにして作成された出力回路チップモデルと、前記調整対象系を周波数領域で表現するようにして作成された調整対象系インピーダンスモデルとに基づいて、調整対象値を導出する調整対象値導出部と、

周波数領域において予め定められた制約値を提供する制約値提供部と、

10

20

30

40

該制約値と導出された前記調整対象値とを比較して、当該比較結果に基づき前記調整対象系に対する設計支援情報を決定する設計支援情報決定部と、

前記設計支援情報を表示する表示部と

を備える設計支援システムを提供する。

#### [0015]

更に、本発明は、演算部、記憶部及び表示部を備えたコンピュータシステムにおいて前記演算部に対して所定の処理を実行させ前記コンピュータシステムを所定の装置の設計支援システムとして機能させるためのプログラムであって、前記所定の装置は、入力パッド、第1電源パッド及び第1グランドパッドを有し且つ入力回路として動作する第1半導体チップと、前記入力パッドに電気的に接続された出力パッド、第2電源パッド及び第2グランドパッドを有し且つ出力回路として動作する第2半導体チップと、前記第1半導体チップ及び前記第2半導体チップに接続され且つ調整対象となる調整対象系とを備えている、プログラムにおいて、

前記所定の処理は、

前記入力パッドと前記第1電源パッドとの間に接続された第1容量及び前記入力パッドと前記第1グランドパッドとの間に接続された第2容量のみならず前記第1電源パッドと前記第1グランドパッドとの間に接続されたチップ内部容量をも考慮して前記第1半導体チップを周波数領域で表現するようにして作成された入力回路チップモデルと、前記第2半導体チップを周波数領域で表現するようにして作成された出力回路チップモデルと、前記調整対象系を周波数領域で表現するようにして作成された調整対象系インピーダンスモデルとに基づいて、調整対象値を導出する調整対象値導出ステップと、

周波数領域において予め定められた制約値と導出された前記調整対象値とを比較して、 当該比較結果に基づき前記調整対象系に対する設計支援情報を決定する設計支援情報決定 ステップと、

前記設計支援情報を前記表示部に表示する表示ステップとを備える、プログラムを提供する。

#### 【発明の効果】

## [0016]

本発明によれば、従来見落とされていたチップ内部容量をも考慮して入力回路の半導体 チップのモデル化を適切に行えることから、計算量を増やすことなく、精度良いシミュレーションを行うことができる。

【発明を実施するための最良の形態】

#### [0017]

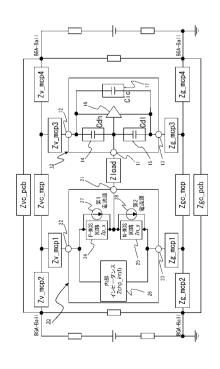

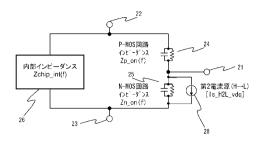

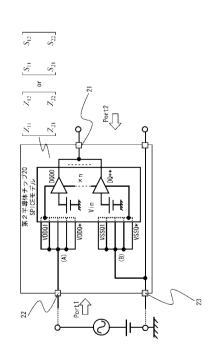

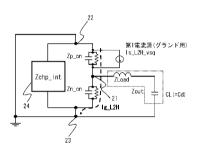

本発明の実施の形態による設計方法は、入力回路及び出力回路として動作する2つの半導体チップを含む装置の設計に関するものであり、この装置について、図1に示されるようなモデルを想定して設計指針の決定を行うものである。

## [0018]

図1を参照すると、入力回路として動作する第1半導体チップ10、出力回路として動作する第2半導体チップ20を備えるマルチチップパッケージ(MCP)をプリント配線基板上に搭載してなる装置をモデル化したものが示されている。第1半導体チップ10は、入力パッド11、電源パッド12及びグランドパッド13を有しており、第2半導体チップ20は、出力パッド21、電源パッド22及びグランドパッド23を有している。第2半導体チップ20の出力パッド21は、第1半導体チップ10の入力パッド11に電気的に接続されている。例えば、第1半導体チップ10は、プロセッサなどを搭載したコントローラチップであり、第2半導体チップ20は、リード時のDRAMチップである。逆に、第1半導体チップ10をライト時のDRAMチップとし、第2半導体チップをコントローラチップとして捉えても良い。

#### [0019]

図 1 において、 Z  $_{v~\_m~c~p~1}$  及び Z  $_{v~\_m~c~p~3}$  は、それぞれ、ワイヤボンディングパッドと電源パッド 1 2 及び 2 2 を接続するワイヤのインピーダンスを示し、 Z  $_{v~\_m~c}$

10

20

30

40

20

30

40

50

p2及び Z<sub>v\_mcp4</sub>は、それぞれ、ワイヤボンディングパッドとパッケージ端子(BGAパッケージの半田ボール)を接続する配線のインピーダンスを示す。 Z<sub>vc\_mcp</sub>は、電源パッド12用のワイヤボンディングパッドと電源パッド22用のワイヤボンディングパッドとの間に見えるインピーダンスを総合的に示したものである。 Z<sub>vc\_pc</sub>は、プリント配線基板のインピーダンス、特に、第1半導体チップ10用の電源側パッケージ端子(半田ボール)と第2半導体チップ20用の電源側パッケージ端子(半田ボール)との間に見えるインピーダンスを総合的に示したものである。

#### [0020]

同様に、 Z g \_ m c p 1 及び Z g \_ m c p 3 は、それぞれ、ワイヤボンディングパッドとグランドパッド 1 3 及び 2 3 を接続するワイヤのインピーダンスを示し、 Z g \_ m c p 2 及び Z g \_ m c p 4 は、それぞれ、ワイヤボンディングパッドとパッケージ端子(BGAパッケージの半田ボール)を接続する配線のインピーダンスを示す。 Z g c \_ m c p は、グランドパッド 1 3 用のワイヤボンディングパッドとグランドパッド 2 3 用のワイヤボンディングパッドとの間に見えるインピーダンスを総合的に示したものである。 Z g c \_ p c b は、プリント配線基板のインピーダンス、特に、第 1 半導体チップ 1 0 用のグランド側パッケージ端子(半田ボール)と第 2 半導体チップ 2 0 用のグランド側パッケージ端子(半田ボール)との間に見えるインピーダンスを総合的に示したものである。

#### [0021]

第1半導体チップ10の入力パッド11と電源パッド12との間には容量14が接続されており、入力パッド11とグランドパッド13との間には容量14が接続されている。 本実施の形態の場合、これら容量14及び15は、それぞれ、電源側ESD保護素子をモデル化したものである。例えば、入力パッド11と高いパッド12との間の寄生容量が電源側ESD保護素子の容量に対して無視できないくらいものである場合、それと電源側ESD保護素子の容量を合成したものを容量14とドリンドのである場合、入力パッド11とグランドパッド13との間の寄生容量がグランドのである場合、それとでランドパッド13との間の高とそれとで表別ESD保護素子の容量に対して無視できないくらいものである場合、それとグランド側ESD保護素子の容量を合成したものを容量15としても良い。参照符号17で示されるものは、入力回路の電源パッド12とグランドパッド13の間に意図的に接続された容量及び寄生容量などの総和を示す。容量17の容量値Cicは容量14及び15の容量位Cdh及びCd1に比べて、通常、2,3桁程度大きい。

## [0022]

この容量17の存在を考慮して適切なモデル化を行うことで、シミュレーションを行う 場合には、より精度の高い結果を得ることができる。

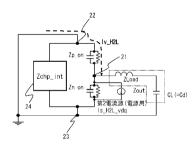

### [0023]

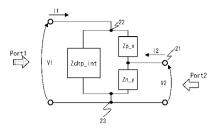

実際の製品においては、インピーダンスススッと、「mcpやインピーダンススッと、pcleのインピーダンスに比べて非常に大きく、従って、MCP上においては電源パッド12と電源パッド22の間を実質的にオープンとみなすことができ、同様に、プリント配線基板における電源パッド12と電源パッド22の間も実質的にオープンとみなすことができる。その場合、上述したような容量の大きい容量17の存在を考慮すると、図2に示されるように、入力パッド21とグランドパッド23との間に見える負荷容量を、容量14と容量15とを並列接続した場合の容量値Cd=Cdh+Cd1を有する容量18で示すことができる。図2に示されるモデルによれば、簡略化されていることから計算量を激減させることができる一方、容量17の存在を考慮して得られた適切なモデルでもあるので高い精度を維持することが出来る。

## [0024]

以上述べたことを鑑みると、例えば、パッケージの設計データやプリント配線基板の設計データにより Z<sub>vc\_mcp</sub>や Z<sub>vc\_pcb</sub>が非常に高いインピーダンスを持っている(オープンとみなせる)か否かにより、入力回路のモデルとして図 1 に示されるモデルを用いるか図 2 に示されるモデルを用いるかを選択することとしても良い。また、計算量

20

30

40

50

と計算結果の精度との兼ね合いで、もっぱら計算量を減らしたい場合には、常に図2に示されるモデルを用いることとしても良い。特に、チップの設計データ等を入手できない場合などにおいては、Cic Cdh,Cdlであることを前提として図2のモデルを用いることとしても良く、その場合、Cdの値として、第1半導体チップ10の入力パッド11とグランドパッド13とにプローブを当てて計測した容量の実測値を用いることができる。なお、これらのことから理解されるように、容量17の存在を考慮できるようになると、入力パッド11とグランドパッド13とにプローブを当てて計測できる容量の実測値がCdlではなくCd(=Cdh+Cdl)であることも分かるので、電源側ESD保護素子に相当する容量14の値をもCdとしてしまう誤解は生じない。

#### [0025]

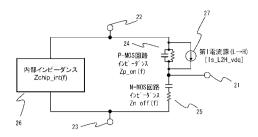

第2半導体チップ20は、出力ドライバとそれ以外の部分(主として半導体チップ20の機能を司る部分)とに分けてモデル化されている。出力ドライバは、出力パッド21と電源パッド22の間に接続されたpMOS回路24と、出力パッド21とグランドパッド23の間に接続されたnMOS回路25を備えている。出力ドライバ以外の部分は、内部インピーダンス26として示されている。この内部インピーダンス26は、第2半導体チップ20の出力ドライバを除いた部分を出力側から見た場合に、電源パッド22とグランドパッド23との間に見えるインピーダンスであり、その大きさは、Zchp\_int(f)で示される。この第2半導体チップ20の出力ドライバには、出力の変化に応じて、第1電流源27か第2電流源28が接続される。第2半導体チップのモデル化については、後で詳細に述べる。

#### [0026]

本実施の形態においては、上述したようにして適切にモデル化された第1半導体チップ10のチップモデルとパッケージ配線やプリント配線基板上の配線などのインピーダンスモデルとを、以下に詳述する第2半導体チップ20のチップモデルと接続し、電源パッド22及びグランドパッド23における電圧変動を算出して、周波数領域において予め定められた制約値との対比を行うことにより、電源/GND電圧の変動が許容値内におさまっているか否かを判断する。なお、以下においては、パッケージ配線やプリント配線基板上の配線など、調整対象となる回路網を調整対象系といい、そのインピーダンスモデルを調整対象系インピーダンスモデルという。

#### [ 0 0 2 7 ]

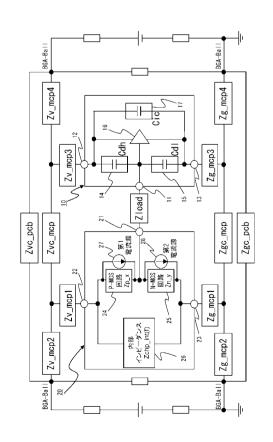

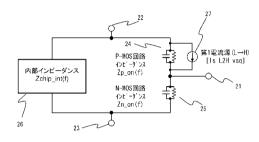

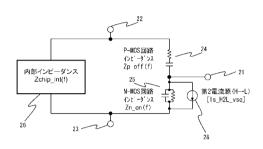

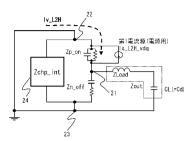

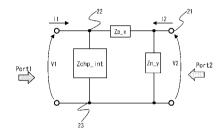

詳しくは、第2半導体チップ20の出力回路チップモデルとして、図3乃至図6の4通りの場合を考慮した出力回路チップモデルを用意して、それぞれを第1半導体チップ10の入力回路チップモデル及び調整対象系インピーダンスモデルと接続することとする。

#### [0028]

このうち、図3及び図4に示される出力回路チップモデルは、第2半導体チップ20の出力値がローレベルからハイレベルに遷移する第1遷移ケースを想定して第2半導体チップ20をモデル化してなる第1出力回路チップモデルである。第1出力回路チップモデルは、pMOS回路24及びnMOS回路25をそれぞれインピーダンス表現してなるpMOS回路インピーダンスZp\_on(f)及びnMOS回路インピーダンスZn\_\*(f)を直列に接続したものを電源パッド22及びグランドパッド23間に接続すると共に、それと並列に内部インピーダンス26(Zchip\_int(f))を接続し、更に、第1遷移ケースにおける変動電流値を考慮した電流源である第1電流源27をpMOS回路インピーダンスZp\_on(f)に並列に接続するようにして作成される。

## [0029]

20

30

40

50

れている。

#### [0030]

また、図4に示される第1出力回路チップモデルはグランドパッド23における電圧変動値算出用の出力回路チップモデルであり、pMOS回路インピーダンス及びnMOS回路インピーダンスのいずれに関しても対応するpMOS回路24及びnMOS回路のオン状態におけるインピーダンスZp\_。n(f)及びZn\_。n(f)を用いた上で、グランド電圧変動値算出用の第1電流源27(電流値はIs\_L2H\_vsa)をpMOS回路インピーダンスZ。。n(f)に並列接続するようにして作成されている。

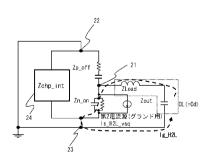

#### [0031]

一方、図 5 及び図 6 に示されるチップモデルは、第 2 半導体チップ 2 0 の出力値がハイレベルからローレベルに遷移する第 2 遷移ケースを想定して第 2 半導体チップ 2 0 をモデル化してなる第 2 出力回路チップモデルである。第 2 出力回路チップモデルは、 p M O S 回路インピーダンス Z p \_ \* (f) 及び n M O S 回路インピーダンス Z n \_ o n (f) を直列に接続したものを電源パッド 2 2 及びグランドパッド 2 3 間に接続すると共に、それと並列に内部インピーダンス 2 6 を接続し、更に、第 2 遷移ケースにおける変動電流値を考慮した電流源である第 2 電流源 2 7 を n M O S 回路インピーダンス Z n \_ o n (f) に並列に接続するようにして作成される。

#### [0032]

詳しくは、図 5 に示される第 2 出力回路チップモデルは電源パッド 2 2 における電圧変動値算出用の出力回路チップモデルであり、 p M O S 回路インピーダンス及び n M O S 回路インピーダンスのいずれに関しても対応する p M O S 回路 2 4 及び n M O S 回路のオン状態におけるインピーダンス Z p \_ o n ( f ) 及び Z n \_ o n ( f ) を用いた上で、電源電圧変動値算出用の第 2 電流源 2 7 (電流値は l s \_ H 2 L \_ v d q )を n M O S 回路インピーダンス Z n o n ( f ) に並列接続するようにして作成されている。

#### [0033]

また、図6に示される第2出力回路チップモデルはグランドパッド23における電圧変動値算出用の出力回路チップモデルであり、pMOS回路インピーダンスとしてはpMOS回路24のオフ状態におけるインピーダンスZp\_off(f)を用い、nMOS回路25のオン状態におけるインピーダンスZn\_on(f)を用いた上で、グランド電圧変動値算出用の第2電流源27(電流値は1g\_H2L\_vsa)をnMOS回路インピーダンスZn\_on(f)に並列接続するようにして作成されている。なお、図6におけるpMOS回路24は、出力パッド21に対してキャパシタ、抵抗の順に直列に接続してなる等価回路で示されているが、キャパシタの順に直列接続順は逆でも構わない。即ち、出力パッド21に対して抵抗、キャパシタの順に直列接続してなる回路をpMOS回路24の等価回路としても良い。

#### [0034]

以下、図 7 乃至図 1 6 をも参照して、上述した 4 種類の出力回路チップモデルの作成方法も含め、本実施の形態による設計方法について具体的に説明する。

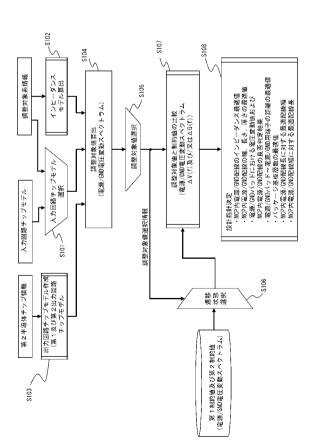

#### [0035]

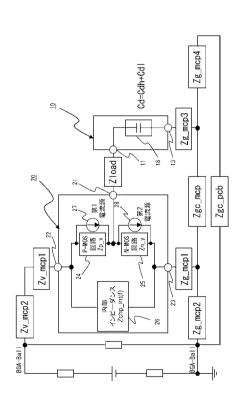

まず、調整対象系(パッケージ配線やプリント配線基板上の配線など)についての設計上の情報(設計データなど:以下、「調整対象系情報」という。)に基づいて、図1に示されるような第1入力回路チップモデルか図2に示されるような第2入力回路チップモデルのいずれか一方を入力回路チップモデルとして選択する(図7:ステップS101)。また、パッケージ配線長などの調整対象系の情報に基づいて、図1又は図2に示されるような調整対象系インピーダンスモデルを作成する(図7:ステップS102)。

### [0036]

更に、第2半導体チップ20についての設計データなどの情報から、図3及び図4に示されるような第1出力回路チップモデル(電源電圧変動用/GND電圧変動用)並びに図5及び図6に示されるような第2出力回路チップモデル(電源電圧変動用/GND電圧変動用)を作成する(図7:ステップS103)。

20

40

[0037]

具体的には、図8に示されるように第2半導体チップ20についてSPICEモデルをAC解析してZパラメータを算出する。本実施の形態においては、Zパラメータを直接算出することとするが、これに代えて、まずはSパラメータを算出し、その後、そのSパラメータをZパラメータに変換することとしても良い。

[0038]

一方、本実施の形態におけるチップモデルのうちインピーダンスに関する部分のみを抽出すると図9に示されるようなものとなる。ここで、 $Z_{p_-}$  及び $Z_{n_-}$  以は出力ドライバの状態にかかわらず、p M O S 回路 2 4 及び n M O S 回路 2 5 を表現するために導入した表記である。従って、第 2 半導体チップ 2 0 の出力値がハイレベルの場合、 $Z_{p_-}$  なオン状態にある p M O S 回路 2 4 のインピーダンス  $Z_{p_-}$  。 $p_-$  を示し、 $p_-$  はオフ状態にある p M O S 回路 2 5 のインピーダンス  $p_-$  。 $p_-$  を示す。また、第 2 半導体チップ 2 0 の出力値がローレベルの場合、 $p_-$  なオフ状態にある p M O S 回路 2 4 のインピーダンス  $p_-$  。 $p_-$  を示し、 $p_-$  なオン状態にある p M O S 回路 2 5 のインピーダンス  $p_-$  。 $p_-$  を示す。

[0039]

上記の図9に示されるインピーダンスモデルを2ポート回路網としてより分かりやすい形に変形したものが図10に示される回路である。この図10に示される回路網における Zパラメータは、下記式(1)に示される。

[ 0 0 4 0 ]

【数1】

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} Z_{11} & Z_{12} \\ Z_{21} & Z_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

$$= \begin{bmatrix} \frac{Z_{chp\_int} \times (Z_{p\_x} + Z_{n\_y})}{Z_{chp\_int} + (Z_{p\_x} + Z_{n\_y})} & \frac{Z_{chp\_int} \times Z_{n\_y}}{(Z_{chp\_int} + Z_{p\_x}) + Z_{n\_y}} \\ \frac{Z_{chp\_int} \times Z_{n\_y}}{Z_{chp\_int} + (Z_{p\_x} + Z_{n\_y})} & \frac{(Z_{chp\_int} + Z_{p\_x}) + Z_{n\_y}}{(Z_{chp\_int} + Z_{p\_x}) + Z_{n\_y}} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix} & \cdots (1)$$

30

[0041]

この式(1)に含まれる行列の各要素の関係を整理して、 $Z_{p_x}$ 、 $Z_{n_y}$ 及び $Z_{chp_i}$  のそれぞれについて解くと、以下に掲げる式(2)~(4)が得られる。 【0042】

【数2】

$$Z_{p_{-}x} = \frac{Z_{11} \cdot Z_{22}}{Z_{12}} - Z_{12} \quad \dots \quad (2)$$

[ 0 0 4 3 ]

【数3】

$$Z_{n_{-}y} = \frac{Z_{11} \cdot Z_{22} - Z_{12}^{2}}{Z_{11} - Z_{12}} \quad \dots \quad (3)$$

[0044]

【数4】

$$Z_{chp\_int} = \frac{Z_{11} \cdot Z_{22} - Z_{12}^2}{Z_{22} - Z_{12}} \cdot \cdot \cdot (4)$$

[ 0 0 4 5 ]

式(2)及び式(3)から理解されるように、出力ドライバの出力値がハイレベルの場合における  $Z_{1,1}$  、  $Z_{1,2}$  及び  $Z_{2,2}$  を用いれば  $Z_{p_0}$  。  $n_0$  及び  $Z_{n_0}$  。  $n_0$  方  $n_0$  できる。 なお、本実施の形態 ことができ、出力ドライバの出力値がローレベルの場合における  $Z_{1,1}$  、  $Z_{1,2}$  及び  $Z_{2,2}$  を 用いれば  $Z_{p_0}$  。  $p_0$  を 算出することができる。 なお、本実施の形態においては、  $S_{p_1}$  で  $E_{p_0}$  解析により 算出した  $Z_{1,1}$  、  $Z_{1,2}$  、  $Z_{2,1}$  及び  $Z_{2,2}$  に基づいて各部のインピーダンスを求めているが、  $Z_{1,1}$  、  $Z_{1,2}$  、  $Z_{2,1}$  及び  $Z_{2,2}$  を 実測し、その結果を利用することとしても良い。即ち、出力ドライバの出力値がハイレベルの場合及びローレベルの場合のそれぞれについて  $Z_{1,1}$  、  $Z_{1,2}$  、  $Z_{2,1}$  及び  $Z_{2,2}$  を 実測し(又は、図  $Z_{2,1}$  及び  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,1}$  及び  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,2}$  の  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,2}$  の  $Z_{2,2}$  を  $Z_{2,2}$  の  $Z_{2,2}$  を  $Z_{2,2}$  を  $Z_{2,2}$  の  $Z_{2,2}$

[0046]

上記のようにして各インピーダンスの値を求めた後、図11乃至図14に示されるようにして、第1電流源27(電源用/GND用)及び第2電流源28(電源用/GND用)を導出する。ここで、図11は、電源電圧変動値算出用の第1電流源27の導出に関する図であり、図12は、グランド電圧変動値算出用の第1電流源27の導出に関する図である。また、図13は、電源電圧変動値算出用の第2電流源28の導出に関する図であり、図14は、グランド電圧変動値算出用の第2電流源28の導出に関する図である。

[0047]

【0048】

10

20

30

20

30

50

[0049]

同様に、グランド電圧変動値算出用の第1電流源I<sub>s\_L2H\_vsa</sub>を導出する際に は、まず、図12に示されるように、出力パッド21とグランドパッド23の間に所定の 外部負荷モデルZ。」」を接続する。ここで、オン状態のnMOS回路インピーダンスZ n onが所定の外部負荷モデルのインピーダンス Zloadよりも遥かに小さいと仮定 すると、第1遷移ケース(L H)においてグランドパッド23を流れる電流 I g L2 н のほとんどが、オン状態の р М О S 回路インピーダンス Z <sub>р \_ 。 п</sub> 及びオン状態の n M OS回路インピーダンス Znonに流れることとなる。その場合、第1遷移ケース(L H )においてグランドパッド 2 3 を流れる電流  $I_{g_L 2 H}$  が分かれば、下記式( 6 ) により、第1電流源の電流値  $I_s$   $L_2$  H  $v_s$  g を導出することができる。

[0050]

【数6】

$$I_{s_{\_L2H\_vsq}} = \frac{Z_{p\_on} + Z_{n\_on} / / Z_{laad}}{Z_{p\_on}} \cdot \frac{Z_{n\_on}}{Z_{n\_on} / / Z_{laad}} \times I_{g\_L2H} \quad . \quad . \quad (6)$$

[0051]

電源電圧変動値算出用の第2電流源I<sub>s \_ H 2 L \_ vdgを導出する際には、まず、図</sub> 13に示されるように、出力パッド21とグランドパッド23の間に所定の外部負荷モデ ルZ。」,を接続する。ここで、所定の外部負荷モデルのインピーダンスZ╷。。。はがオ ン状態のnMOS回路インピーダンスZn\_。nよりも遥かに大きいと仮定すると、第2 遷移ケース(H L)において電源パッド22を流れる電流 I <sub>V\_H2 L</sub>のほとんどが、 オン状態の p M O S 回路インピーダンス Z  $_{\rm p}$  \_  $_{\rm o}$  n とオン状態の n M O S 回路インピーダ ンス Z n o n に流れることとなる。この場合、第 2 遷移ケース(H L)において電源 パッド 2 2 を流れる電流  $I_{v_{-H_2}}$  が分かれば、下記式( 7 )により、第 2 電流源の電 流値 I <sub>s \_ H 2 L \_ v d q</sub> を導出することができる。

[0052] 【数7】

$$I_{s\_H2L\_vdq} = \frac{Z_{n\_on} + Z_{p\_on} / / Z_{laad}}{Z_{n\_on}} \cdot \frac{Z_{p\_on}}{Z_{p\_on} / / Z_{laad}} \times I_{v\_H2L} \quad . \quad . \quad . \quad (7)$$

[0053]

同様に、グランド電圧変動値算出用の第2電流源I<sub>s н2L vsa</sub>を導出する際に は、まず、図14に示されるように、出力パッド21とグランドパッド23の間に所定の 外部負荷モデルZ。utを接続する。ここで、所定の外部負荷モデルのインピーダンスZ 。u t がオフ状態の p M O S 回路インピーダンス Z p o n がよりも遥かに小さいと仮定 すると、第2遷移ケース(H L)においてグランドパッド23を流れる電流 I g H 2 」のほとんどが、オン状態のnMOS回路インピーダンスZ n on及び所定の外部負荷 モデルのインピーダンス Z <sub>1 o a d</sub> に流れることとなる。その場合、第 2 遷移ケース( H

20

30

40

50

L)においてグランドパッド 2 3 を流れる電流  $I_{g_{H_2}}$  が分かれば、下記式(8)により、第 2 電流源の電流値  $I_{g_{H_2}}$  、 $g_{g_g}$  を導出することができる。

[0054]

【数8】

$$I_{s\_H2L\_vsq} = \frac{Z_{n\_on} + Z_{p\_off} // Z_{laad}}{Z_{n\_on}} \times I_{g\_H2L} \quad . \quad . \quad . \quad . \quad (8)$$

[0055]

[0056]

このようにして、本実施の形態においては、第2半導体チップ20の設計データなどの情報である第2半導体チップ情報に基づいて、第1遷移ケース用及び第2遷移ケース用の第1出力回路チップモデル及び第2出力回路チップモデルを、それぞれ電源電圧変動値算出用とGND電圧変動値算出用の2種類(従って、出力回路チップモデルは計4種類)作成する(図7:ステップS103)。上述したように、これらの出力回路チップモデルを作成するにあたってはSPICEモデルをトランジェント解析する場面も考えられるが、一旦、出力回路チップモデルを作成してしまった後は、第2半導体チップ20の構成が変わらぬ限り、作成された出力回路チップモデルを用いることができる。

[0057]

このようにして作成された電源変動値算出用/GND変動値算出用の第1出力回路チップモデル及び第2出力回路チップモデルは、それぞれ、ステップS101で選択された入力回路チップモデル及びステップS102で作成した調整対象系インピーダンスモデルと接続される。イメージ的には、図11~図14において求められた第2半導体チップ20の出力回路チップモデルを図1又は図2に組み込む感じである。その上で、図1又は図2に示される回路に含まれる各閉路について閉路回路方程式を解くことにより、トランジェント解析をすることなく、電源/GND電圧変動スペクトラムを算出する。ここで、各インピーダンスの大小関係、特に、短絡とみなせる箇所があるかオープンとみなせる箇所があるかなどの情報をも考慮することにより、解くべき閉路方程式を簡略化することもできる。

[0058]

このようにして、第1遷移ケース及び第2遷移ケースの双方について調整対象値の算出(図7:ステップS104)を行った後、第1遷移ケースにおける電源/GND電圧変動スペクトラムとを比較して、調整必要性のより高い一方を選択する(ステップS105)。

[0059]

ここで、本実施の形態においては、制約値に関しても、第1遷移ケースを想定して設定された制約値である第1制約値と第2遷移ケースを想定して設定された制約値である第2制約値の2種類用意してあり、ステップS105においていずれの遷移ケースに関する電源/GND電圧変動スペクトラムが選択されたのかを示す調整対象値選択情報に従って、第1制約値と第2制約値のいずれか一方を選択する(ステップS106)。

[0060]

次いで、ステップS105で選択された第1遷移ケース又は第2遷移ケースにおける電

源 / GND電圧変動スペクトラムと、ステップS106において選択された第1制約値又は第2制約値とを比較し(ステップS107)、その比較結果に基づいて、設計指針を決定する(ステップS108)。

#### [0061]

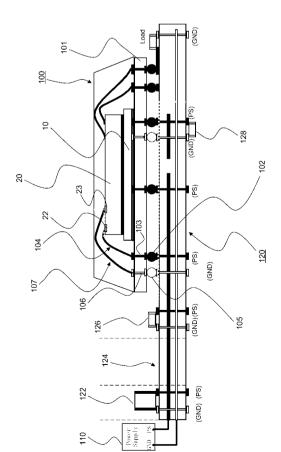

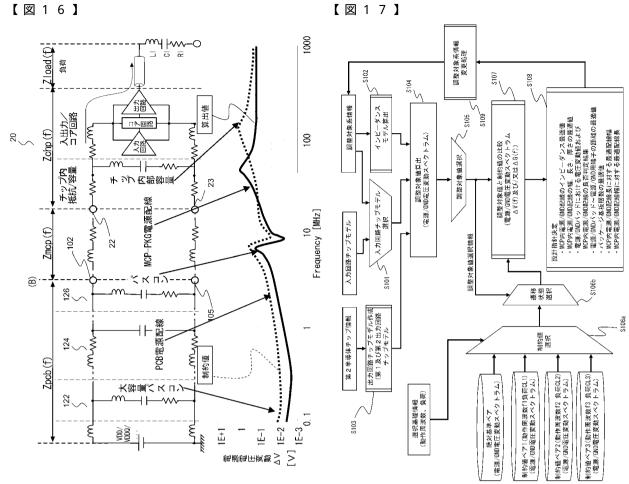

ここで、ステップS107に示されるように調整対象値と制約値とを周波数領域において比較する利点について、図15及び図16をも参照して説明する。

#### [0062]

図15を参照すると、図1又は図2に示された装置のうち、マルチチップパッケージの一部及びプリント配線基板について詳細に示した図が示されている。図15に示される装置は、電源(PS)部及びグランド(GND)部を有する電源装置110、プリント配線基板(PCB)120及びマルチチップパッケージ(MCP)100を備えている。プリント配線基板120上には、電気的構成要素として、大容量コンデンサ122、PCB上で記録はPCB上電源プレーン)124、PCB上バイパスコンデンサ128などが設けられている。マルチチップパッケージ100は、電源パッド22及びグランドパッド23を有する第2半導体チップ10をパッケージ基板101上に積層してなるものである。第2半導体チップ20の電源パッド22には、電源用端子(ボール)102、スルーホール103及びMCP内電源配線104等を介して、電源が供給される。一方、第2半導体チップ20のグランドパッド23は、グランド用端子(ボール)105、スルーホール1

#### [0063]

かかるシステムの電気的構成要素は、図16上段に示されるように、すべてRLCからなる受動回路ブロックとして表現することができる。この受動回路ブロックからなる調整対象系インピーダンスモデルと入力回路チップモデルを図3~図6に示される各出力回路チップモデルと接続し、回路方程式を解くことにより、トランジェント解析よりは少ない計算量で、変圧変動値を算出することができる。

## [0064]

そして、例えば、図7のステップS107に示されるようにして、調整対象値と制約値の比較をすることにより、調整対象値が制約値を超えてしまうような周波数部分に対応する調整対象系の部位を特定し、その部位を調整対象箇所として設計指針を決定することとしても良い(図16下段の例においては、MCP-PKG電源配線部分)。

### [0065]

ステップS108において決定される設計指針の例としては、上記の調整対象箇所の特定に加え、例えば、1)電源 / グランドパッド22,23における電圧変動値及びMCP内電源 / グランド配線の良否判定結果、2)MCP電源 / グランド配線のインピーンスの最適値、3)MCP内電源 / グランド配線の幅、長さ、厚さの最適値、4)電源 / グランドパッド22,23から電源 / グランド用端子までの距離の最適値、5)パッケージ基板層数の最適値、6)MCP内電源 / グランド配線の配線長に対する最適配線幅、並びに、7)MCP内電源 / グランド配線の配線幅に対する最適配線長などが挙げられる。

#### [0066]

以上説明したように、本実施の形態によれば、一旦、出力回路チップモデルを作成して ししまった後は、調整対象系に関する調整対象値は関連する閉路について回路方程式を解 くだけで算出することができることから、例えば、パッケージ配線長を調整する等して設 計変更した場合など、再チェックを簡易且つ短時間で行うことができる。

#### [0067]

なお、上述した実施の形態におけるステップS106(図7)では、一対の第1制約値及び第2制約値のうちから、いずれか一方を選択することとしていたが、例えば、図17に示されるように、既に動作確認された半導体パッケージに基づいて絶対基準ペア(使用条件にかかわらず選択されうるペア)や複数の制約値ペア1~3といった複数の制約値ペアを用意しておき、パッケージの使用条件(動作周波数や負荷など)を示す選択基礎情報

10

20

30

40

20

30

40

50

に基づいて制約値ペアを選択し(図17:ステップS106a)、その後、ステップS105における選択結果に関連した調整対象値選択情報に従って、ステップS106aにて選択された制約値ペアを構成する第1制約値と第2制約値のいずれか一方を選択する(ステップS106b)こととしても良い。

#### [0068]

また、図17に示されるように、設計指針を決定した後(ステップS108)、設計指針に従って調整対象系情報に変更を加え(ステップS109)、その後、再度、調整対象系インピーダンスモデルを算出して(ステップS102)、当該調整対象系インピーダンスモデルと先の処理において作成された第1出力回路チップモデル及び第2出力回路チップモデルとの組み合わせに基づいて、ステップS104以降の処理を自動的に再度行うこととしても良い。なお、当初の調整対象系が極端な修正を要するものでない限り、通常は調整対象系情報に変更があったとしても入力回路チップモデル選択の前提条件が大きく変わるわけではないので、2回目以降のループにおいてはステップS101の入力回路チップモデルの選択は省略することとしても良い。

#### [0069]

以上、マルチチップパッケージをプリント配線基板に搭載してなる装置を設計対象とした例について説明してきたが、本発明の概念は、例えば、パッケージ設計自体にも適用することができる。その場合、調整対象系は、パッケージのうち、第1及び第2半導体チップを除いた部分(パッケージ配線等)となる。また、本発明の概念は、マルチチップパッケージのみならずSiP(System In Package)、PoP(Package On Package)、PiP(Package In Package)などの入力側及び出力側の2つのチップを少なくとも備えたパッケージ又はそれを含む装置に適用可能である。

### [0070]

更に、上述した実施の形態においては、入力回路が一つの場合について説明してきたが、本発明の概念は、出力回路に対して複数の入力回路が負荷として接続されている場合に も適用可能である。

#### [0071]

なお、以上説明してきた設計方法は、その少なくとも一部をプログラム化することにより、設計支援用プログラム及び設計支援システムとして具現化することができる。

## [0072]

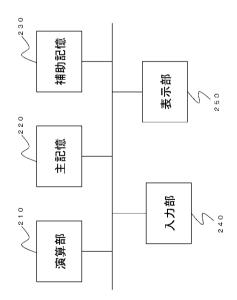

以下、設計支援システムの実現例について説明する。実現例による設計支援システムは、図18に示されるように、演算部210、主記憶220、補助記憶230、入力部24 0及び表示部250を備えている。

## [0073]

主記憶220は、例えば、DRAM装置で構成され、補助記憶230は、例えば、HDDやCD-ROMなどで構成される。また、入力部240は、例えば、キーボード及びマウスなどで構成され、表示部250は、例えば、CRTや、液晶ディスプレイなどで構成される。

#### [0074]

より具体的には、上述した各実施の形態における設計方法の少なくとも一部を実装してなるプログラムは補助記憶230に格納されている。このプログラムは、主記憶220上に展開され、演算部210によって実行される。演算部210が当該プログラムを実行することにより、図22に示されるシステムは、前述した設計方法の少なくとも一部を具現化し、設計支援システムとして機能する。また、主記憶220上には、演算部210が当該プログラムに従って動作している間に生成したデータ及び演算部210により利用されるデータが一時的に記憶される。なお、一般にはコンピュータシステム上で本発明を実現する場合、上記したように主記憶220と補助記憶230とを分ける構成が主として採用されるが、概念的には両者をまとめて記憶部として捉えることも可能である。

## [0075]

上述した各実施の形態による設計方法をプログラム上に実装して設計支援システムを構

20

30

40

50

築する場合、調整対象値と制約値との周波数領域における比較結果に基づいて決定された 設計指針を表示部 2 5 0 に表示させるステップを更に備えることとしても良い。

【図面の簡単な説明】

- [0076]

- 【図1】本発明の実施の形態において設計対象とした装置をモデル化した図である。

- 【図2】所定の条件を加味して図1のモデルを変形して得られるモデルを示した図である

- 【図3】電源電圧変動スペクトラム算出用の第1出力回路チップモデル(L H)を示す図である。

- 【図4】GND電圧変動スペクトラム算出用の第1出力回路チップモデル(L H)を示す図である。

- 【図5】電源電圧変動スペクトラム算出用の第2出力回路チップモデル(H L)を示す図である。

- 【図 6 】 G N D 電圧変動スペクトラム算出用の第 2 出力回路チップモデル(H L )を示す図である。

- 【図7】本発明の実施の形態による設計方法を示すフローチャートである。

- 【図8】第1出力回路チップモデル及び第2出力回路チップモデルのインピーダンス値を 決定する手順を説明するための図である。

- 【図9】第1出力回路チップモデル及び第2出力回路チップモデルのインピーダンス値を 決定する手順を説明するための他の図である。

- 【図10】第1出力回路チップモデル及び第2出力回路チップモデルのインピーダンス値を決定する手順を説明するための更に他の図である。

- 【図11】電源電圧変動スペクトラム算出用の第1電流源の電流値の算出手順を説明する ための図である。

- 【図12】GND電圧変動スペクトラム算出用の第1電流源の電流値の算出手順を説明するための図である。

- 【図13】電源電圧変動スペクトラム算出用の第2電流源の電流値の算出手順を説明するための図である。

- 【図14】GND電圧変動スペクトラム算出用の第2電流源の電流値の算出手順を説明するための図である。

- 【図15】本発明を適用可能な装置の概略構成を示す図である。

グランドパッド

pMOS回路

- 【図16】本発明を図15に示される装置に適用した例を示す図である。

- 【図17】図7に示される設計方法の変形例を示すフローチャートである。

- 【図18】本発明による設計方法に基づいた設計支援システムの構成を示すブロック図である。

【符号の説明】

[0077]

2 3

| 0 | 077] |                 |

|---|------|-----------------|

| 1 | 0    | 第 1 半 導 体 チ ッ プ |

| 1 | 1    | 入力パッド           |

| 1 | 2    | 電 源 パ ッ ド       |

| 1 | 3    | グランドパッド         |

| 1 | 4    | 容量              |

| 1 | 5    | 容量              |

| 1 | 7    | 容量              |

| 1 | 8    | 容量              |

| 2 | 0    | 第2半導体チップ        |

| 2 | 1    | 出力パッド           |

| 2 | 2    | 電源パッド           |

|   |      |                 |

| 2 5<br>2 6<br>2 7<br>2 8<br>1 0 0<br>1 0 1 | n M O S 回路<br>内部インピーダンス<br>第 1 電流源<br>第 2 電流源<br>マルチチップパッケージ<br>パッケージ基板 |    |

|--------------------------------------------|-------------------------------------------------------------------------|----|

| 1 0 2<br>1 0 3<br>1 0 4                    | 電源用端子(ボール)<br>スルーホール<br>M C P 内電源配線                                     |    |

| 1 0 5<br>1 0 6<br>1 0 7<br>1 1 0           | グランド用端子(ボール)<br>スルーホール<br>M C P 内グランド配線<br>電源                           | 10 |

| 1 2 0<br>1 2 2<br>1 2 4                    | プリント配線基板( P C B )<br>大容量コンデンサ<br>P C B 電源配線 / プレーン                      |    |

| 1 2 6<br>1 2 8<br>2 1 0                    | バイパスコンデンサ<br>バイパスコンデンサ<br>演算部                                           | 20 |

| 2 2 0<br>2 3 0<br>2 4 0<br>2 5 0           | 主 記 憶<br>補 助 記 憶<br>入 力 部<br>表 示 部                                      | 20 |

# 【図1】

## 【図3】

## 【図5】

## 【図4】

【図6】

## 【図7】

## 【図8】

## 【図9】

# 【図11】

# 【図10】

## 【図12】

## 【図13】

【図15】

# 【図14】

【図18】

### フロントページの続き

(72)発明者 須賀 卓

神奈川県横浜市戸塚区吉田町292番地 株式会社日立製作所生産技術研究所内

(72)発明者 清水 浩也

茨城県ひたちなか市堀口832番地2 株式会社日立製作所機械研究所内

(72)発明者 伊佐 聡

東京都中央区八重洲2-2-1 エルピーダメモリ株式会社内

(72)発明者 板谷 哲

東京都中央区八重洲2-2-1 エルピーダメモリ株式会社内

(72)発明者 廣瀬 行敏

東京都中央区八重洲2-2-1 エルピーダメモリ株式会社内

F ターム(参考) 5B046 AA08 BA03 JA04