(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第6761361号 (P6761361)

(45) 発行日 令和2年9月23日 (2020.9.23)

(24) 登録日 令和2年9月8日 (2020.9.8)

(51) Int.Cl. F 1

**GO5F** 1/56 (2006.01) GO5F 1/56 31OF HO3F 3/45 (2006.01) HO3F 3/45 22O

請求項の数 9 (全 18 頁)

(21) 出願番号

特願2017-21597 (P2017-21597)

(22) 出願日 (65) 公開番号 平成29年2月8日 (2017.2.8) 特開2018-128868 (P2018-128868A)

(43) 公開日

審查請求日

平成30年8月16日 (2018.8.16) 平成30年11月26日 (2018.11.26) ||(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(73)特許権者 317011920

東芝デバイス&ストレージ株式会社 東京都港区芝浦一丁目1番1号

|(74)代理人 100091982

弁理士 永井 浩之

|(74)代理人 100091487

弁理士 中村 行孝

|(74)代理人 100082991

弁理士 佐藤 泰和

(74)代理人 100105153

弁理士 朝倉 悟

最終頁に続く

(54) 【発明の名称】電源装置

## (57)【特許請求の範囲】

## 【請求項1】

入力電圧に応じた出力電圧を出力する第1トランジスタと、

第1電圧が印加されるゲートを有する第1および第2素子を含み、前記出力電圧から得られた電圧を増幅して第2電圧を出力し、前記第2電圧に基づいて前記第1トランジスタを制御する第1増幅器と、

前記第1電圧が印加されるゲートを有する第2トランジスタと、

前記第2電圧が印加されるゲートを有する第3トランジスタと、

前記第1増幅器に電流を供給する第1電流源と、

前記第2トランジスタを流れる電流と前記第3トランジスタを流れる電流とに基づいて 、前記第1増幅器に電流を供給する第2電流源と、

を備える電源装置。

#### 【請求項2】

入力電圧に応じた出力電圧を出力する第1トランジスタと、

第1電圧が印加されるゲートを有する第1および第2素子を含み、前記出力電圧から得られた電圧を増幅して第2電圧を出力し、前記第2電圧に基づいて前記第1トランジスタを制御する第1増幅器と、

前記第1電圧が印加されるゲートを有する第2トランジスタと、

前記第1増幅器に電流を供給する第1電流源と、

前記第2トランジスタを流れる電流に基づいて、前記第1増幅器に電流を供給する第2

#### 電流源と、

前記第2トランジスタを流れる電流としきい値とを比較する電流比較器と、

前記電流比較器の出力信号に基づいて動作し、前記第2トランジスタを流れる電流と<u>前</u>記しきい値との比較結果に基づいて、前記第2電流源から前記第1増幅器に電流を供給するか否かを切り替える第1切替器と、

を備える電源装置。

#### 【請求項3】

入力電圧に応じた出力電圧を出力する第1トランジスタと、

第1電圧が印加されるゲートを有する第1および第2素子を含み、前記出力電圧から得られた電圧を増幅して第2電圧を出力し、前記第2電圧に基づいて前記第1トランジスタを制御する第1増幅器と、

前記第1電圧が印加されるゲートを有する第2トランジスタと、

前記第2電圧が印加されるゲートを有する第3トランジスタと、

前記第1増幅器に電流を供給する第1電流源と、

前記第2トランジスタを流れる電流<u>と前記第3トランジスタを流れる電流と</u>に基づいて、前記第1増幅器に電流を供給する第2電流源と、

前記第 2 トランジスタを流れる電流としきい値との比較結果に基づいて、前記第 2 電流源から前記第 1 増幅器に電流を供給するか否かを切り替える第 1 切替器と、

を備える電源装置。

## 【請求項4】

前記第2電圧が印加されるゲートを有する第3トランジスタをさらに備え、

前記第2電流源は、前記第2トランジスタを流れる電流と前記第3トランジスタを流れる電流とに基づいて、前記第1増幅器に電流を供給する、請求項2に記載の電源装置。

#### 【請求項5】

前記第2トランジスタは、前記第1素子を流れる電流および前記第2素子を流れる電流 をモニタする、請求項1から4のいずれか1項に記載の電源装置。

#### 【請求項6】

入力電圧に応じた出力電圧を出力する第1トランジスタと、

第1電圧が印加されるゲートを有する第1および第2素子を含み、前記出力電圧から得られた電圧を増幅して第2電圧を出力する第1増幅器と、

前記第2電圧が印加されるゲートを有する第3素子を含み、前記第2電圧を増幅して第3電圧を出力し、前記第3電圧に基づいて前記第1トランジスタを制御する第2増幅器と

前記第1電圧が印加されるゲートを有する第2トランジスタと、

前記第2電圧が印加されるゲートを有する第3トランジスタと、

前記第1増幅器に電流を供給する第1電流源と、

前記第2トランジスタを流れる電流と前記第3トランジスタを流れる電流とに基づいて、前記第1増幅器に電流を供給する第2電流源と、

を備える電源装置。

## 【請求項7】

入力電圧に応じた出力電圧を出力する第1トランジスタと、

第1電圧が印加されるゲートを有する第1および第2素子を含み、前記出力電圧から得られた電圧を増幅して第2電圧を出力する第1増幅器と、

前記第2電圧が印加されるゲートを有する第3素子を含み、前記第2電圧を増幅して第3電圧を出力し、前記第3電圧に基づいて前記第1トランジスタを制御する第2増幅器と

前記第1電圧が印加されるゲートを有する第2トランジスタと、

前記第1増幅器に電流を供給する第1電流源と、

前記第2トランジスタを流れる電流に基づいて、前記第1増幅器に電流を供給する第2 電流源と、 10

20

30

40

前記第2トランジスタを流れる電流としきい値とを比較する電流比較器と、

前記電流比較器の出力信号に基づいて動作し、前記第2トランジスタを流れる電流と<u>前</u>記しきい値との比較結果に基づいて、前記第2電流源から前記第1増幅器に電流を供給するか否かを切り替える第1切替器と、

を備える電源装置。

## 【請求項8】

入力電圧に応じた出力電圧を出力する第1トランジスタと、

第1電圧が印加されるゲートを有する第1および第2素子を含み、前記出力電圧から得られた電圧を増幅して第2電圧を出力する第1増幅器と、

前記第2電圧が印加されるゲートを有する第3素子を含み、前記第2電圧を増幅して第3電圧を出力し、前記第3電圧に基づいて前記第1トランジスタを制御する第2増幅器と

10

前記第1電圧が印加されるゲートを有する第2トランジスタと、

前記第2電圧が印加されるゲートを有する第3トランジスタと、

前記第1増幅器に電流を供給する第1電流源と、

前記第2トランジスタを流れる電流<u>と前記第3トランジスタを流れる電流と</u>に基づいて、前記第1増幅器に電流を供給する第2電流源と、

前記第2トランジスタを流れる電流としきい値との比較結果に基づいて、前記第2電流源から前記第1増幅器に電流を供給するか否かを切り替える第1切替器と、

を備える電源装置。

20

#### 【請求項9】

前記第2電圧が印加されるゲートを有する第3トランジスタをさらに備え、

前記第2電流源は、前記第2トランジスタを流れる電流と前記第3トランジスタを流れる電流とに基づいて、前記第1増幅器に電流を供給する、請求項7に記載の電源装置。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明の実施形態は、電源装置に関する。

#### 【背景技術】

[0002]

30

電子機器は、集積回路、センサ、ドライバなどのデバイスに適切な電圧を供給するための電源装置を備えることが一般的である。このような電源装置の例として、スイッチングレギュレータやリニアレギュレータが挙げられる。近年、バッテリで駆動される携帯機器に電源装置を適用するケースが増えており、電源装置は低消費電流と高速応答との両立を求められることが多くなっている。

#### [0003]

例えば、電源装置の出力電圧を一定に維持するために、出力電圧が低下した場合には、電源装置内の増幅器を流れる電流を増加させる方式が知られている。しかし、この場合には、異常電圧の判定用のしきい値と正常電圧との差電圧を小さく設定すると、誤って増幅器に電流が流れ続ける場合があり、低消費電流の妨げとなる。一方、差電圧を大きく設定すると、出力電圧が正常電圧から大きく外れないと増幅器の電流が増加せず、高速応答の妨げとなる。さらには、出力電圧の低下に応じて、増幅器の電流をどのように増加させるかも問題となる。このように、低消費電流の達成と高速応答の達成は相反する関係にあることから、これらを両立させることが可能な手法が求められている。

【先行技術文献】

#### 【特許文献】

[0004]

【特許文献 1 】特開 2 0 1 2 - 1 5 5 3 9 5 号公報

## 【発明の概要】

【発明が解決しようとする課題】

50

#### [0005]

低消費電流と高速応答とを両立させることが可能な電源装置を提供する。

#### 【課題を解決するための手段】

#### [0006]

一の実施形態によれば、電源装置は、入力電圧に応じた出力電圧を出力する第1トランジスタを備える。前記装置はさらに、第1電圧が印加されるゲートを有する第1および第2素子を含み、前記出力電圧から得られた電圧を増幅して第2電圧を出力し、前記第2電圧に基づいて前記第1トランジスタを制御する第1増幅器と、前記第1電圧が印加されるゲートを有する第2トランジスタとを備える。前記装置はさらに、前記第1増幅器に電流を供給する第1電流源と、前記第2トランジスタを流れる電流に基づいて、前記第1増幅器に電流を供給する第2電流源とを備える。

10

#### 【図面の簡単な説明】

#### [0007]

- 【図1】第1実施形態の電源装置の構成を示す回路図である。

- 【図2】第1実施形態の比較例の電源装置の構成を示す回路図である。

- 【図3】第1実施形態の電源装置の動作を説明するための波形図である。

- 【図4】第1実施形態の電源装置の動作を説明するためのさらなる波形図である。

- 【図5】第1実施形態の第1変形例の電源装置の構成を示す回路図である。

- 【図6】第1実施形態の第1変形例の電源装置の動作を説明するための図である。

- 【図7】第1実施形態の第2変形例の電源装置の構成を示す回路図である。

- 【図8】第2実施形態の電源装置の構成を示す回路図である。

- 【図9】第3実施形態の電源装置の構成を示す回路図である。

- 【図10】第3実施形態の変形例の電源装置の構成を示す回路図である。

- 【発明を実施するための形態】

#### [00008]

以下、本発明の実施形態を、図面を参照して説明する。

## [0009]

#### (第1実施形態)

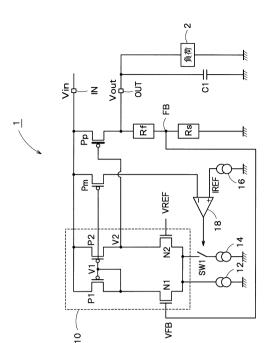

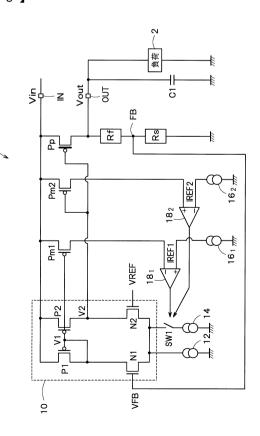

図1は、第1実施形態の電源装置1の構成を示す回路図である。図1は、電源装置1の 例としてリニアレギュレータを示している。

30

20

#### [0010]

図1の電源装置1は、第1増幅器10と、第1電流源12と、第2電流源14と、参照電流源16と、電流比較器18と、第1トランジスタPpと、第2トランジスタPmと、第1切替器SW1と、抵抗Rf、Rsとを備えている。第1トランジスタPpと第2トランジスタPmは、ここではpMOSトランジスタである。

## [0011]

図1はさらに、電源装置1の入力端子INおよび出力端子OUTと、出力端子OUTに接続された負荷2およびコンデンサC1とを示している。この電源装置1では、入力端子INと出力端子OUTとの間の回路構成が1つの半導体チップで実現されている。

#### [0012]

40

第1トランジスタPpは、入力電圧Vinに応じた出力電圧Voutを出力する出力トランジスタである。第1トランジスタPpのソースは、入力端子INに接続され、第1トランジスタPpのドレインは、出力端子OUTに接続されている。入力電圧Vinは、入力端子INから第1トランジスタPpに入力される。出力電圧Voutは、第1トランジスタPpから出力端子OUTに出力される。第1トランジスタPpは、出力端子OUTに接続された負荷2に応じて電流を調整し出力する。

#### [0013]

抵抗Rf、Rsは、第1トランジスタPpのドレインと接地ノードとの間に直列に接続されている。抵抗Rf、Rsは、出力電圧Voutを分圧してフィードバック電圧(帰還電圧)VFBを生成する。フィードバック電圧VFBは、抵抗Rf、Rs間のノードFB

から第1増幅器10に印加される。

## [0014]

第1増幅器10は、入力された2つの電圧の差電圧を増幅する差動増幅回路であり、ここではトランジスタN1、N2、P1、P2を備えている。トランジスタN1、N2は、nMOSトランジスタであり、差動入力素子として設けられている。トランジスタP1、P2は、pMOSトランジスタであり、能動負荷素子として設けられている。トランジスタP1は第1素子の例であり、トランジスタP2は第2素子の例である。

## [0015]

トランジスタP1、P2のソースは、いずれも入力端子INに接続されている。トランジスタP1、P2のドレインは、それぞれトランジスタN1、N2のドレインに接続されている。トランジスタP1、P2のゲートは、互いに接続され、かつトランジスタP1のドレインに接続されている。図1は、トランジスタP1、P2のゲートに印加される第1電圧V1と、トランジスタP2のドレインに発生する第2電圧V2とを示している。

## [0016]

トランジスタN1、N2のソースは、第1電流源12に接続されており、かつ第1切替器SW1を介して第2電流源14に接続可能である。トランジスタN1のゲートには、出力電圧Voutに応じたフィードバック電圧VFBが印加される。トランジスタN2のゲートには、定電圧である参照電圧VREFが印加される。

#### [0017]

第1増幅器10の入力ノードは、トランジスタN1、N2のゲートであり、第1増幅器10の出力ノードは、トランジスタN2のドレインとトランジスタP2のドレインとの間に位置する。よって、第1増幅器10の入力ノードには、フィードバック電圧VFBと参照電圧VREFが入力され、これらの差電圧が第2電圧V2へと増幅され、第2電圧V2が第1増幅器10の出力ノードから出力される。第2電圧V2は第1トランジスタPpのゲートに印加され、第1トランジスタPpの動作が第2電圧V2により制御される。第1増幅器10は、フィードバック電圧VFBと参照電圧VREFが等しくなるように第2電圧V2を制御する。

#### [0018]

第1電流源12は、第1増幅器10に流れる電流を供給する定電流源である。第2電流源14は、第1切替器SW1がオンのときに、第1増幅器10に流れる電流を供給する定電流源である。

## [0019]

第2トランジスタPmは、トランジスタP1、P2の出力電流をモニタするモニタトランジスタであり、トランジスタP1、P2の出力電流に応じた電流を出力する。第2トランジスタPmのソースは、入力端子INに接続されている。第2トランジスタPmのドレインは、電流比較器18の反転入力端子(・入力端子)に接続されている。第2トランジスタPmのゲートは、トランジスタP1、P2のゲートに接続されており、第1電圧V1が印加される。第2トランジスタPmは、トランジスタP1、P2とカレントミラー回路を構成しており、トランジスタP1の出力電流やトランジスタP2の出力電流に比例した電流を出力する。

## [0020]

参照電流源16は、しきい値となる定電流である参照電流IREFを、電流比較器18の非反転入力端子(+入力端子)に供給する定電流源である。電流比較器18は、第2トランジスタPmの出力電流と参照電流IREFとを比較し、これらの比較結果を示す出力信号を第1切替器SW1に出力する。

## [0021]

第1切替器SW1は、この出力信号に基づいて動作し、具体的には、第2トランジスタPmの出力電流と参照電流IREFとの比較結果に基づいて、第2電流源14から第1増幅器10に電流を供給するか否かを切り替える。例えば、上記出力電流が参照電流IREFよりも大きい場合には、第1切替器SW1がオフになり、第2電流源14から第1増幅

10

20

30

40

器10に電流は供給されない。一方、上記出力電流が参照電流IREFよりも小さい場合には、第1切替器SW1がオンになり、第2電流源14から第1増幅器10に電流が供給される。

## [0022]

本実施形態の電源装置1では、出力電圧Voutが参照電圧VREFを抵抗Rfと抵抗Rsで逓倍した電圧になるよう帰還経路が働く。よって、電源装置1は、負荷2を流れる電流が変化しても出力電圧Voutを一定に維持する定電圧回路となる。

## [0023]

本実施形態の電源装置1は、出力電圧Voutを電圧比較器により異常電圧の判定用のしきい値(参照電圧)と比較するのではなく、第2トランジスタPmの出力電流を電流比較器18によりしきい値(参照電流IREF)と比較している。

#### [0024]

前者の電圧比較の場合には、出力電圧Voutの変化が小さいため、参照電圧の設定が難しいことが問題となる。例えば、出力電圧Voutと参照電圧との差電圧を小さく設定すると、誤って第2電流源14から第1増幅器10に電流が流れ続ける場合があり、低消費電流の妨げとなる。一方、差電圧を大きく設定すると、出力電圧Voutが参照電圧から大きく外れないと第2電流源14から第1増幅器10に電流が流れず、高速応答の妨げとなる。

## [0025]

このような問題は、後者の電流比較を採用することで解消可能である。理由は、出力電圧Voutはできるだけ一定に維持する必要があるのに対し、第2トランジスタPmの出力電流は一定に維持する必要がないからである。よって、本実施形態では、第2トランジスタPmの出力電流と参照電流IREFとを比較する方式を採用することで、参照電流IREFを高い精度で設定することが不要となり、参照電流IREFの設定が容易になっている。よって、本実施形態によれば、電源装置1の低消費電流と高速応答とを両立させることが可能となる。

#### [0026]

本実施形態において、第1トランジスタPpは出力トランジスタであるため、サイズが大きいのに対し、トランジスタP1、P2はサイズを大きくする必要はない。よって、本実施形態のトランジスタP1のサイズやトランジスタP2のサイズは、第1トランジスタPpのサイズよりも小さく設計されており、第1トランジスタPpよりも高速で動作することができる。よって、第2トランジスタPmは、第1トランジスタPpの出力電流ではなくトランジスタP1、P2の出力電流をモニタすることで、出力電圧Voutの変化に素早く対処することが可能となる。

## [0027]

一方、第2トランジスタPmのサイズは、トランジスタP1、P2のサイズよりも大きくてもよいし、トランジスタP1、P2のサイズよりも小さくてもよい。本実施形態の第2トランジスタPmのサイズは、トランジスタP1、P2のサイズの1/2~1/5程度に設計されている。本実施形態の第2トランジスタPmは、第1トランジスタPpの出力電流ではなくトランジスタP1、P2の出力電流をモニタするため、このように小型化することができる。

#### [0028]

次に、第1実施形態の電源装置1の動作の詳細について説明する。

## [0029]

電源装置1の消費電流を低減するため、第1電流源12からの電流は微小電流となっている。電源装置1の通常の動作時には、トランジスタP1とトランジスタP2(またはトランジスタN1とトランジスタN2)には同じ値の電流が流れる。具体的には、第1電流源12からの微小電流の半分の値の電流が、トランジスタP1とトランジスタP2の各々に流れる。

## [0030]

20

10

30

しかし、負荷2が増加した直後は、トランジスタN2を流れる電流が増加し、トランジスタP2を流れる電流が減少する。そのため、これらの差電流は、第1トランジスタPpのゲート寄生容量の電荷を放電して、第1トランジスタPpのゲート電圧(すなわち第2電圧V2)を低下させる働きをする。このゲート電圧が低下すると、第1トランジスタPpは、出力電流を増加させるために出力電圧Voutを上昇させる。このように、トランジスタP1、P2を流れる電流が少ない場合には、第1トランジスタPpの出力電流が増加するように帰還回路が働く。

## [0031]

第2トランジスタPmは、トランジスタP1、P2を流れる電流をモニタし、電流比較器18は、第2トランジスタPmからの出力電流(以下「駆動電流」と呼ぶ)と参照電流IREFとを比較する。

## [0032]

駆動電流が参照電流IREFを上回る場合には、負荷2が小さいと判断され、第1切替器SW1がオフのままの低消費電流モードが維持される。この場合、第1電流源12から第1増幅器10には微小電流が供給されるものの、第2電流源14から第1増幅器10には電流(以下「加算電流」と呼ぶ)が供給されない。そのため、低消費電流モードでは、電源装置1の消費電流を低く抑えることができる。

## [0033]

一方、駆動電流が参照電流IREFを下回る場合には、負荷2が大きいと判断され、第1切替器SW1がオンになる高速応答モードに移行する。この場合、第1電流源12から第1増幅器10に微小電流が供給されると共に、第2電流源14から第1増幅器10に加算電流が供給される。そのため、高速応答モードでは、低消費電流モードに比べて第1トランジスタPpを高速で制御することができる。

#### [0034]

第1トランジスタPpのサイズはリニアレギュレータの電流能力を決定するため、数百ミリアンペアの大電流を供給可能なサイズ、場合によっては数アンペアの大電流を供給可能なサイズが求められる。よって、第1トランジスタPpがMOSトランジスタの場合、第1トランジスタPpのゲートには数十ピコファラドの寄生容量が存在する。そのため、仮に第1トランジスタPpのゲート電圧を微小電流だけで生成しようとすると、数十から数百マイクロ秒の時間がかかる。この場合、この遅延時間の間に出力電圧Voutが負荷電流に応じて大きく変動してしまう。

## [0035]

よって、本実施形態では、第1トランジスタPpの出力電流が変化するよりも早い段階で状態が変化するトランジスタP1、P2に注目し、負荷電流の変化に高速で応答可能なリニアレギュレータを実現している。本実施形態のトランジスタP1、P2のサイズは小さく、かつトランジスタP1、P2の付近には第1トランジスタPpのような大きな素子も存在しないため、寄生容量によるトランジスタP1、P2の動作遅延は小さい(例えば数マイクロ秒未満)。よって、トランジスタP1、P2の状態をモニタして加算電流を供給することで、負荷電流の変化を素早く検出し、第1トランジスタPpのゲート電圧を素早く変化させることが可能となる。すなわち、低消費電流モードから高速応答モードに素早く移行し、出力電圧Voutの変動を素早く収めることが可能となる。

## [0036]

例えば、負荷2が急激に増加した場合、トランジスタP1、P2を流れる電流は、加算電流の供給前にほぼゼロになる。理由は、負荷2が急激に増加しても負荷電流はすぐには変化しないため、出力電圧Voutやフィードバック電圧VFBが低下し、トランジスタN1に電流があまり流れなくなり、その結果、トランジスタP1、P2にも電流があまり流れなくなくなるからである。そして、トランジスタP1、P2の電流の減少は、第2トランジスタPmが素早く検出できるため、低消費電流モードから高速応答モードに素早く移行することができる。また、本実施形態の加算電流は、負荷電流に比例する値ではなく負荷電流に依存しない一定値であるため、負荷電流が小さくても十分な加算電流を得るこ

10

20

30

40

とができ、負荷電流が大きくても加算電流が過剰になることを避けることができる。

## [0037]

なお、本実施形態の電源装置1は、第1トランジスタPpの出力電流をモニタする回路を備えない簡易型の構成となっている。よって、出力電圧Voutの変動が収まると、負荷電流の大きさに関わらず低消費電流モードへ戻る。

#### [0038]

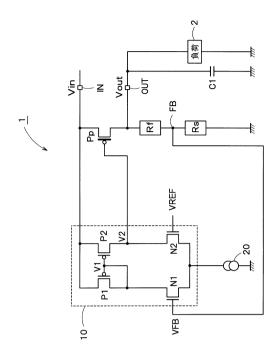

図2は、第1実施形態の比較例の電源装置1の構成を示す回路図である。

## [0039]

図2の電源装置1は、第1電流源12、第2電流源14、参照電流源16、電流比較器 18、第2トランジスタPm、および第1切替器SW1を備えておらず、代わりに電流源 20を備えている。

[0040]

以下、第1実施形態の電源装置1(図1)の動作を、その比較例の電源装置1(図2)の動作と比較しつつ説明する。

[0041]

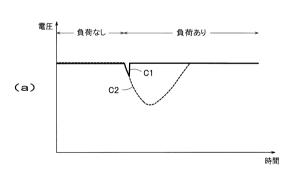

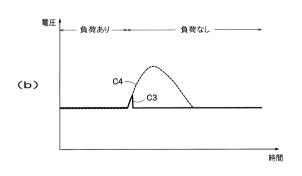

図3は、第1実施形態の電源装置1の動作を説明するための波形図である。

[0042]

図3(a)において、曲線C1は、本実施形態の電源装置1の出力電圧Voutの時間変化を示し、曲線C2は、本比較例の電源装置1の出力電圧Voutの時間変化を示す。曲線C1、C2は、負荷2がない状態からある状態に変化した場合の出力電圧Voutの変化を示している。

[0043]

本比較例において負荷2が新たに接続されると、負荷電流の増加に伴い一時的に出力電圧Voutが低下するが、電源装置1の作用により出力電圧Voutが再び元の値に復帰する(曲線C2)。

[0044]

これは、本実施形態でも同様である(曲線 C 1)。しかし、本実施形態の出力電圧 V o u t の最大変化量は、比較例のそれに比べて 1 / 4 程度に改善される。このように、本実施形態によれば、電源装置 1 の高速応答の特性を向上させることで、出力電圧 V o u t の変化を抑制することができる。

[0045]

図3(b)において、曲線C3は、本実施形態の電源装置1の出力電圧Voutの時間変化を示し、曲線C4は、本比較例の電源装置1の出力電圧Voutの時間変化を示す。曲線C3、C4は、負荷2がある状態からない状態に変化した場合の出力電圧Voutの時間を示している。曲線C3、C4においても、曲線C1、C2と同様の現象が見られる。

[0046]

なお、曲線 C 3 の波形は、正確には図 1 の電源装置 1 ではなく後述する図 5 の電源装置 1 により実現される。曲線 C 1 と曲線 C 3 との違いについては、後述する。

[0047]

図4は、第1実施形態の電源装置1の動作を説明するためのさらなる波形図である。

[0048]

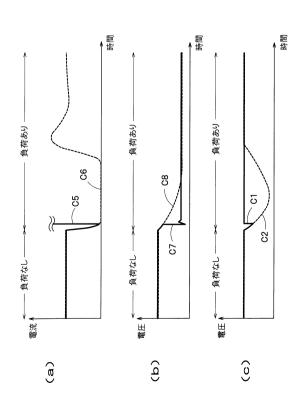

図 4 (a) と図 4 (b) において、曲線 C 5、 C 7 はそれぞれ、本実施形態のトランジスタ P 1 の出力電流と第 1 トランジスタ P p のゲート電圧の時間変化を示し、曲線 C 6、 C 8 はそれぞれ、本比較例のトランジスタ P 1 の出力電流と第 1 トランジスタ P p のゲート電圧の時間変化を示す。曲線 C 5 ~ C 8 は、負荷 2 がない状態からある状態に変化した場合におけるトランジスタ P 1 と第 1 トランジスタ P p の出力電流とゲート電圧の変化を示している。図 4 (c)の曲線 C 1、 C 2 は、図 3 (c)の曲線 C 1、 C 2 と同じものである。

[0049]

本比較例において負荷2が新たに接続されると、出力電圧Voutが下がり始める(曲線C2)。この場合、電源装置1の帰還回路はこれを検知し、第1トランジスタPpのゲ

10

20

30

40

ート電圧を低下させるよう、トランジスタP1の出力電流をゼロに減少させる(曲線C6、C8)。出力電流がゼロになった結果、ゲート電圧は低下し始めるが、電流源20からの微小電流により第1トランジスタPpのゲートの寄生容量が放電し続けるため、出力電流とゲート電圧が安定化するまでに長い時間がかかっている(曲線C6、C8)。

## [0050]

同様に、本実施形態において負荷2が新たに接続されると、出力電圧Voutが下がり始める(曲線C1)。この場合、電源装置1の帰還回路はこれを検知し、第1トランジスタPpのゲート電圧を低下させるよう、トランジスタP1の出力電流をゼロに減少させる(曲線C5、C7)。この場合、第1切替器SW1がオンになり、第2電流源14からの加算電流により第1トランジスタPpのゲートの寄生容量が迅速に放電するため、ゲート電圧が短い時間で安定化している(曲線C7)。

[0051]

次に、第1実施形態の第1および第2変形例について説明する。

[0052]

図5は、第1実施形態の第1変形例の電源装置1の構成を示す回路図である。

[0053]

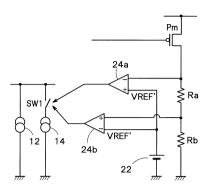

本変形例の電源装置1は、参照電流源16および電流比較器18の代わりに、参照電圧源22と、第1電圧比較器24aと、第2電圧比較器24bと、抵抗Ra、Rbとを備えている。

[0054]

抵抗 R a 、 R b は、第 2 トランジスタ P m のドレインと接地ノードとの間に直列に接続されている。参照電圧源 2 2 は、しきい値となる定電圧である参照電圧 V R E F 'を、第 1 電圧比較器 2 4 a の非反転入力端子と第 2 電圧比較器 2 4 b の反転入力端子とに供給する定電流源である。

[0055]

第1電圧比較器24aの反転入力端子には、第2トランジスタPmのドレインと抵抗Raとの間のノードから電圧が供給される。第1電圧比較器24aは、この電圧と参照電圧VREF'とを比較し、これらの比較結果を示す第1出力信号を第1切替器SW1に出力する。

[0056]

第2電圧比較器24bの非反転入力端子には、抵抗Raと抵抗Rbとの間のノードから電圧が供給される。第2電圧比較器24bは、この電圧と参照電流VREF′とを比較し、これらの比較結果を示す第2出力信号を第1切替器SW1に出力する。

[0057]

第1切替器SW1は、第1および第2出力信号に基づいて動作し、具体的には、第1電圧比較器24aの比較結果と第2電圧比較器24bの比較結果とに基づいて、第2電流源14から第1増幅器10に電流を供給するか否かを切り替える。例えば、第1電圧比較器24aの電圧が参照電圧VREF'よりも高く、かつ第2電圧比較器24bの電圧が参照電圧VREF'よりも低い場合には、第1切替器SW1がオフになり、第2電流源14から第1増幅器10に電流は供給されない。一方、第1電圧比較器24aの電圧が参照電圧VREF'よりも高い場合には、第1切替器SW1がオンになり、第2電流源14から第1増幅器10に電流が供給される。

[0058]

本変形例によれば、負荷2が急激に増加したときだけでなく、負荷2が急激に減少したときにも、第2電流源14から第1増幅器10に加算電流を供給することができ、出力電圧Voutの変動をより効果的に抑制することができる。なお、第1電圧比較器24aの比較結果に基づいて第1切替器SW1がオンしている間は、第2電圧比較器24bの比較動作を停止することにより、第2電圧比較器24bの誤動作を防ぐことが望ましい。

[0059]

10

20

30

40

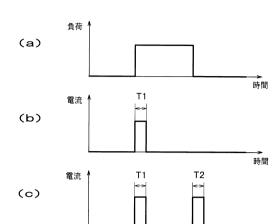

図6は、第1実施形態の第1変形例の電源装置1の動作を説明するための図である。

## [0060]

図 6 (a)は、図 1 または図 5 の電源装置 1 における負荷 2 の時間変化の例を示す。図 6 (b)および図 6 (c)は、図 6 (a)の場合における加算電流の時間変化の例を示す。

## [0061]

図 6 (b)では、負荷 2 が急激に増加したときに加算電流が供給されており、これは図 1 の電源装置 1 により実現される。このときの出力電圧 V o u t は、図 3 (a)の曲線 C 1 のように変化する。

## [0062]

一方、図 6 (c)では、負荷 2 が急激に増加または減少したときに加算電流が供給されており、これは図 5 の電源装置 1 により実現される。このときの出力電圧 V o u t は、図 3 (a)の曲線 C 1 や図 3 (b)の曲線 C 3 のように変化する。

#### [0063]

符号T1は、負荷2が急激に増加したときの加算電流の持続期間を示す。符号T2は、負荷2が急激に減少したときの加算電流の持続期間を示す。本変形例では、これらの持続期間T1、T2を延長するための延長回路を、図1または図5の電源装置1に設けてもよい。これにより、第1切替器SW1のオン/オフ動作が煩雑になることを回避することができるため、帰還回路の安定性を高めることができる。

#### [0064]

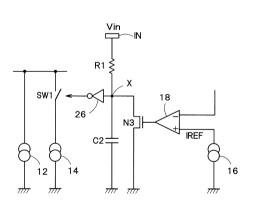

図7は、第1実施形態の第2変形例の電源装置1の構成を示す回路図である。

#### [0065]

図7の電源装置1は、図1の電源装置1に上述の延長回路を設けて構成されている。図7の電源装置1は、延長回路の構成要素として、電流比較器18と第1切替器SW1との間に直列に設けられたトランジスタN3およびインバータ26と、接地ノードとノードXとの間に設けられたキャパシタC2と、入力端子INとノードXとの間に設けられたプルアップ抵抗R1とを備えている。ノードXは、トランジスタN3とインバータ26との間に位置している。トランジスタN3は、ここではnMOSトランジスタであり、電流比較器18に接続されたゲートを有している。トランジスタN3のソースおよびドレインは、インバータ26と接地ノードとの間に位置している。この延長回路は、加算電流の立ち上がり時間を維持しつつ、加算電流の立ち下がり時間を遅延させることができ、これにより加算電流の持続期間T1を延長することができる。

## [0066]

なお、この延長回路は、図5の電源装置1に設けられていてもよい。この場合、加算電流の持続期間T1、T2を延長することができる。

## [0067]

以上のように、本実施形態の電源装置1は、第2トランジスタPmの出力電流と参照電流IREFとを比較し、これらの比較結果に基づいて第2電流源14から第1増幅器10に加算電流を供給する。よって、本実施形態によれば、電源装置1の低消費電流と高速応答とを両立させることが可能となる。

## [0068]

また、本実施形態の電源装置1は、第1トランジスタPpの出力電流の代わりに、第1トランジスタPpよりサイズの小さいトランジスタP1、P2の出力電流をモニタして、電流比較器18や第1切替器SW1の動作を制御する。よって、本実施形態によれば、出力電圧Voutの変化に素早く対処可能な電源装置1を実現することが可能となる。

#### [0069]

なお、本実施形態の第1増幅器10では、トランジスタN1、N2をpMOSトランジスタに置き換え、かつトランジスタP1、P2をnMOSトランジスタに置き換えてもよい。この場合、これらのトランジスタのソースおよびドレインの位置関係は、適宜入れ替えが可能である。これは、後述する第2および第3実施形態にも適用可能である。また、上述の第1および第2変形例についても、後述する第2および第3実施形態に適用可能で

10

20

30

40

ある。

## [0070]

(第2実施形態)

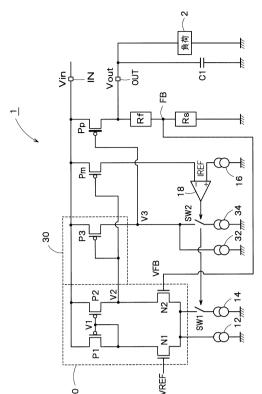

図8は、第2実施形態の電源装置1の構成を示す回路図である。

## [0071]

図 8 の電源装置 1 は、図 1 の参照電流源 1 6、電流比較器 1 8、および第 2 トランジスタ P m の代わりに、第 1 参照電流源 1 6  $_1$  と、第 2 参照電流源 1 6  $_2$  と、第 1 電流比較器 1 8  $_1$  と、第 2 電流比較器 1 8  $_2$  と、第 2 トランジスタ P m 1 と、第 3 トランジスタ P m 2 は、ここでは p M O S トランジスタである。

[0072]

第2トランジスタPm1は、第1実施形態の第2トランジスタPmと同様に、トランジスタP1、P2の出力電流をモニタするモニタトランジスタであり、トランジスタP1、P2の出力電流に応じた電流を出力する。第2トランジスタPm1のソースは、入力端子INに接続されている。第2トランジスタPm1のドレインは、第1電流比較器18<sub>1</sub>の反転入力端子に接続されている。第2トランジスタPm1のゲートは、トランジスタP1、P2のゲートに接続されており、第1電圧V1が印加される。第2トランジスタPm1は、トランジスタP1、P2とカレントミラー回路を構成しており、トランジスタP1の出力電流やトランジスタP2の出力電流に比例した電流を出力する。

[0073]

第1参照電流源16<sub>1</sub>は、第1しきい値となる定電流である参照電流IREF1を、第1電流比較器18<sub>1</sub>の非反転入力端子に供給する定電流源である。第1電流比較器18<sub>1</sub>は、第2トランジスタPm1の出力電流と参照電流IREF1とを比較し、これらの比較結果を示す第1出力信号を第1切替器SW1に出力する。

[0074]

第3トランジスタPm2は、第1トランジスタPpの出力電流をモニタするモニタトランジスタであり、第1トランジスタPpの出力電流に応じた電流を出力する。第3トランジスタPm2のソースは、入力端子INに接続されている。第3トランジスタPm2のドレインは、第2電流比較器18 $_2$ の反転入力端子に接続されている。第3トランジスタPm2のゲートは、トランジスタP2のドレインに接続されており、第2電圧V2が印加される。第3トランジスタPm2は、第1トランジスタPpとカレントミラー回路を構成しており、第1トランジスタPpの出力電流に比例した電流を出力する。

[0075]

第2参照電流源16<sub>2</sub>は、第2しきい値となる定電流である参照電流IREF2を、第2電流比較器18<sub>2</sub>の反転入力端子に供給する定電流源である。第2電流比較器18<sub>2</sub>は、第3トランジスタPm2の出力電流と参照電流IREF2とを比較し、これらの比較結果を示す第2出力信号を第1切替器SW1に出力する。

[0076]

第 1 切替器 S W 1 は、第 1 および第 2 出力信号に基づいて動作し、具体的には、第 1 電流比較器 1  $8_1$  の比較結果と第 2 電流比較器 1  $8_2$  の比較結果とに基づいて、第 2 電流源 1 4 から第 1 増幅器 1 0 に電流を供給するか否かを切り替える。例えば、第 1 電流比較器 1  $8_1$  の電流が参照電流 I R E F 1 よりも大きく、かつ第 2 電流比較器 1  $8_2$  の電流が参照電流 I R E F 2 よりも小さい場合には、第 1 切替器 S W 1 がオフになり、第 2 電流源 1 4 から第 1 増幅器 1 0 に電流は供給されない。一方、第 1 電流比較器 1  $8_1$  の電流が参照電流 I R E F 1 よりも小さく、または第 2 電流比較器 1  $8_2$  の電流が参照電流 I R E F 2 よりも大きい場合には、第 1 切替器 I W 1 がオンになり、第 2 電流源 1 4 から第 1 増幅器 1 0 に電流が供給される。

[0077]

次に、第2実施形態の電源装置1の動作の詳細について説明する。

[0078]

10

20

30

40

第1実施形態では、高速応答モードで出力電圧 Voutの変動が収まると、負荷電流の大きさに関わらず低消費電流モードへ戻る。一方、本実施形態の電源装置 1 は第 3 トランジスタ Pm 2 を備えているため、高速応答モードで負荷電流が大きいときには、出力電圧 Voutの変動の大きさに関わらず高速応答モードが維持される。

## [0079]

具体的には、本実施形態の第1切替器 SW 1 は、上述のように、第1電流比較器 1 8  $_1$  からの第1出力信号と、第2電流比較器 1 8  $_2$  からの第2出力信号とのOR演算結果に基づいて動作する。よって、第2および第3トランジスタPm1、Pm2のいずれかが加算電流が必要と判断すれば、低消費電流モードから高速応答モードに移行するか、高速応答モードがそのまま維持される。

[0800]

本実施形態では、第2および第3トランジスタPm1、Pm2の両方が加算電流は不要と判断すれば、第1増幅器10が第1電流源12からの微小電流のみにより動作する。この微小電流の電流値は小さいため、第1増幅器10が微小電流のみにより動作することで低消費電流を実現できる。

[0081]

一方、第 2 および第 3 トランジスタ P m 1、 P m 2 のいずれかが加算電流が必要と判断すれば、第 1 増幅器 1 0 は第 1 および第 2 電流源 1 2、 1 4 からの微小電流と加算電流により動作する。すなわち、出力電圧 V o u t の変動が大きい場合か、負荷電流が大きい場合かのいずれかであれば、第 1 増幅器 1 0 が微小電流と加算電流により動作することで高速応答を実現できる。

[0082]

よって、第2実施形態によれば、第1実施形態よりもさらに効果的に加算電流を活用して、高速応答を促進することが可能となる。一方、第1実施形態によれば、第2実施形態よりもさらに消費電流の低減を促進することが可能となる。

[0083]

なお、これらの実施形態の高速応答モードでは、電源装置1の帰還動作の遅延時間は短い。理由は、第1トランジスタPpのゲート寄生容量が大きい場合でも加算電流が大きいため、ゲート寄生容量の充放電にかかる時間が短くて済むためである。

[0084]

また、第2トランジスタPm1のサイズについては、第1実施形態の第2トランジスタPmのサイズと同様に設計可能である。そのため、第2トランジスタPm1のサイズは、トランジスタP1、P2のサイズよりも大きくてもよいし、トランジスタP1、P2のサイズよりも小さくてもよい。本実施形態の第2トランジスタPm1のサイズは、トランジスタP1、P2のサイズの1/2~1/5程度に設計されている。本実施形態の第2トランジスタPm1は、第1トランジスタPpの出力電流ではなくトランジスタP1、P2の出力電流をモニタするため、このように小型化することができる。

[0085]

(第3実施形態)

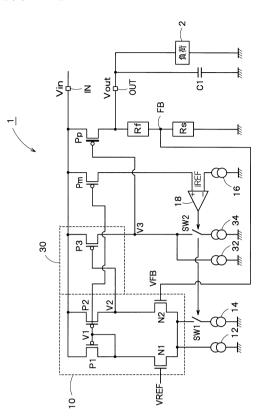

図9は、第3実施形態の電源装置1の構成を示す回路図である。

[0086]

図9の電源装置1は、図1に示す構成要素に加え、第2増幅器30と、第3電流源32と、第4電流源34と、第2切替器SW2とを備えている。第2増幅器30は、第3素子の例であるトランジスタP3を備えている。トランジスタP3は、ここではPMOSトランジスタであるが、nMOSトランジスタに置き換えてもよい。

[0087]

第2増幅器30は、第1増幅器10から出力された第2電圧V2を増幅して、第3電圧 V3を出力する回路である。第3電圧V3は第1トランジスタPpのゲートに印加され、 第1トランジスタPpの動作が第3電圧V3により制御される。このように、本実施形態 の第1トランジスタPpの動作は、第2電圧V2そのものではなく、第2電圧V2に依存 10

20

30

40

する第3電圧V3により制御される。

## [0088]

トランジスタP3のソースは、入力端子INに接続されている。トランジスタP3のドレインは、第3電流源32に接続されており、かつ第2切替器SW2を介して第4電流源34に接続可能である。トランジスタP3のゲートは、トランジスタP2のドレインに接続されており、第2電圧V2が印加される。

#### [0089]

第3電流源32は、第2増幅器30に流れる電流を供給する定電流源である。第4電流源34は、第2切替器SW2がオンのときに、第2増幅器30に流れる電流を供給する定電流源である。

## [0090]

本実施形態の第2トランジスタPmは、トランジスタP3の出力電流をモニタするモニタトランジスタであり、トランジスタP3の出力電流に応じた電流を出力する。第2トランジスタPmのゲートは、トランジスタP2のドレインとトランジスタP3のゲートとに接続されており、第2電圧V2が印加される。第2トランジスタPmは、トランジスタP3とカレントミラー回路を構成しており、トランジスタP3の出力電流に比例した電流を出力する。

#### [0091]

参照電流源16は、しきい値となる定電流である参照電流IREFを、電流比較器18の非反転入力端子に供給する定電流源である。電流比較器18は、第2トランジスタPmの出力電流と参照電流IREFとを比較し、これらの比較結果を示す出力信号を第1および第2切替器SW1、SW2に出力する。

#### [0092]

第2切替器SW2は、この出力信号に基づいて動作し、具体的には、第2トランジスタPmの出力電流と参照電流IREFとの比較結果に基づいて、第4電流源34から第2増幅器30に電流を供給するか否かを切り替える。例えば、上記出力電流が参照電流IREFよりも大きい場合には、第2切替器SW2がオフになり、第4電流源34から第2増幅器30に電流は供給されない。一方、上記出力電流が参照電流IREFよりも小さい場合には、第2切替器SW2がオンになり、第4電流源34から第2増幅器30に電流が供給される。なお、第1切替器SW1の動作については、第1実施形態と同様である。

#### [0093]

次に、第3実施形態の電源装置1の動作の詳細について説明する。

## [0094]

第2増幅器30は、第1増幅器10の後段に設けられており、第1および第2増幅器10、30はそれぞれ、第1および第2利得段として機能する。第2増幅器30は、第1増幅器10の出力電圧(第2電圧V2)をトランジスタP3のゲートで受信し、第2増幅器30の出力電圧(第3電圧V3)をトランジスタP3のドレインから出力する。第1トランジスタPpのゲートは、第3電圧V3により充電され、その結果、このゲートの電圧がト昇する。

## [0095]

第1トランジスタPpのゲートを放電させる、すなわち、このゲートの電圧を低下させる役割を担うのは、第3電流源32からの微小電流と、第4電流源34からの加算電流である。第2増幅器30は、電源装置1の帰還経路の中に位置し、帰還回路の開放利得を増加させる機能を有する。本実施形態によれば、第2増幅器30により帰還回路の開放利得を増加させることで、出力電圧Vout中のノイズを低減したり、入力信号Vin中のノイズから出力信号Voutへの影響を低減することが可能となる。

#### [0096]

なお、トランジスタP3のサイズについては、第1実施形態のトランジスタP1、P2のサイズと同様に設計可能である。よって、本実施形態のトランジスタP3のサイズは、第1トランジスタPpのサイズよりも小さく設計されており、第1トランジスタPpより

10

20

30

40

も高速で動作することができる。よって、本実施形態の第2トランジスタPmは、トランジスタP3の出力電流をモニタすることで、出力電圧Voutの変化に素早く対処することが可能となる。

#### [0097]

図10は、第3実施形態の変形例の電源装置1の構成を示す回路図である。

#### [0098]

図10の電源装置1は、図9の電源装置1と同じ構成要素を備えているが、第2トランジスタPmのゲートが、トランジスタP3のゲートではなく、トランジスタP1、P2のゲートに接続されている。よって、本変形例の第2トランジスタPmは、第1実施形態と同様に、トランジスタP1、P2の出力電流をモニタするモニタトランジスタであり、トランジスタP1、P2の出力電流に応じた電流を出力する。本変形例の第2トランジスタPmのゲートには、第1電圧V1が印加される。また、本変形例の電流比較器18では、非反転入力端子が参照電流源16に接続され、反転入力端子が第2トランジスタPmに接続されている。

## [0099]

以上のように、本実施形態の電源装置1は、第1増幅器10の後段に第2増幅器30を備えている。よって、本実施形態によれば、入力信号Vinおよび出力信号Voutに関するオフセットやノイズの問題を抑制することが可能となる。

## [0100]

なお、図9の構成や図10の構成は、第1実施形態だけでなく、第2実施形態にも適用 可能である。

#### [0101]

以上、いくつかの実施形態を説明したが、これらの実施形態は、例としてのみ提示したものであり、発明の範囲を限定することを意図したものではない。本明細書で説明した新規な装置は、その他の様々な形態で実施することができる。また、本明細書で説明した装置の形態に対し、発明の要旨を逸脱しない範囲内で、種々の省略、置換、変更を行うことができる。添付の特許請求の範囲およびこれに均等な範囲は、発明の範囲や要旨に含まれるこのような形態や変形例を含むように意図されている。

## 【符号の説明】

[0102]

1:電源装置、2:負荷、

10:第1增幅器、12:第1電流源、14:第2電流源、

16:参照電流源、161:第1参照電流源、162:第2参照電流源、

18:電流比較器、181:第1電流比較器、182:第2電流比較器、

20:電流源、22:第1参照電圧源、

2 4 a : 第1電圧比較器、2 4 b : 第2電圧比較器、2 6 : インバータ、

30:第2增幅器、32:第3電流源、34:第4電流源、

N 1 、N 2 、N 3 、 P 1 、 P 2 、 P 3 : トランジスタ、 P p : 第 1 トランジスタ、

Pm、Pm1:第2トランジスタ、Pm2:第3トランジスタ、

SW1:第1切替器、SW2:第2切替器、R1:プルアップ抵抗、

Rf、Rs、Ra、Rb:抵抗、C1、C2:コンデンサ

10

20

30

【図1】

【図2】

【図3】

【図4】

<del>--></del> 時間

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

## フロントページの続き

(74)代理人 100107582

弁理士 関根 毅

(74)代理人 100118843

弁理士 赤岡 明

(74)代理人 100124372

弁理士 山ノ井 傑

(72)発明者 小倉 暁生

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 柳下 勝幸

(56)参考文献 特開2010-256990(JP,A)

特開2009-069964(JP,A)

特開2006-099378(JP,A)

(58)調査した分野(Int.CI., DB名)

G05F 1/56

H03F 3/45