### (19) **日本国特許庁(JP)**

## (12) 特 許 公 報(B2)

(11)特許番号

特許第5792485号 (P5792485)

(45) 発行日 平成27年10月14日(2015.10.14)

(24) 登録日 平成27年8月14日 (2015.8.14)

| (51) Int.Cl. |        |           | FΙ   |       |          |          |        |

|--------------|--------|-----------|------|-------|----------|----------|--------|

| G09F         | 9/30   | (2006.01) | GO9F | 9/30  | 338      |          |        |

| HO1L         | 29/786 | (2006.01) | HO1L | 29/78 | 618B     |          |        |

| HO1L         | 21/336 | (2006.01) | HO1L | 29/78 | 612C     |          |        |

|              |        |           | HO1L | 29/78 | 618F     |          |        |

|              |        |           | HO1L | 29/78 | 616V     |          |        |

|              |        |           |      |       | 請求項の数 12 | (全 14 頁) | 最終頁に続く |

(21) 出願番号 特願2011-56669 (P2011-56669) (22) 出願日 平成23年3月15日 (2011.3.15) (65) 公開番号 特開2011-191764 (P2011-191764A) (43) 公開日 平成23年9月29日 (2011.9.29) 審查請求日 平成26年2月27日 (2014.2.27) (31) 優先権主張番号 10-2010-0023367 (32) 優先日 平成22年3月16日 (2010.3.16)

韓国(KR)

||(73)特許権者 512187343

三星ディスプレイ株式會社

Samsung Display Co.

, Ltd.

大韓民国京畿道龍仁市器興区三星二路95 95, Samsung 2 Ro, Gih eung-Gu, Yongin-City , Gyeonggi-Do, Korea

|(74)代理人 100121382

弁理士 山下 託嗣

(72) 発明者 尹 弼 相

大韓民国ソウル特別市江南區狎鴎亭洞現代 アパート208棟1102號

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ、その製造方法および薄膜トランジスタを利用した表示基板

### (57)【特許請求の範囲】

### 【請求項1】

(33) 優先権主張国

基板と、

前記基板上に配置されるゲートラインと、

前記基板上に前記ゲートラインから絶縁され、前記ゲートラインを交差するデータラインと、

前記ゲートラインと前記データラインに電気的に接続され、酸化物層を含む酸化物薄膜トランジスタ、および

前記酸化物薄膜トランジスタに電気的に接続される画素電極を含み、

前記酸化物薄膜トランジスタの酸化物層は、

チャネルを含み半導体特性を有する第1部分と、

前記第1部分を囲み、導電性を有する第2部分を含み、

前記第1部分は前記画素電極と電気的に接続して前記第2部分は前記データラインと電気的に接続される酸化物薄膜トランジスタ基板。

### 【請求項2】

前記酸化物層上に配置され前記第1部分を露出させる第1ホールを有する第1保護膜、および

前記第1保護膜の上に配置され前記第1ホールを露出させる第2ホールを有する第2保 護膜をさらに含み、

前記画素電極は前記第2保護膜の上に形成され、前記第1ホールおよび第2ホールを通

じて前記第1部分とコンタクトする請求項1に記載の酸化物薄膜トランジスタ基板。

### 【請求項3】

前記第1保護膜と前記第2保護膜は互いに異なる物質で形成される請求項2に記載の酸 化物薄膜トランジスタ基板。

### 【請求項4】

前記第1保護膜はSiOxを含み、前記第2保護膜はSiNxを含む請求項2又は3に 記載の酸化物薄膜トランジスタ基板。

### 【請求項5】

前記第1保護膜と前記第2保護膜は互いに同じ物質で形成される請求項2に記載の酸化 物薄膜トランジスタ基板。

10

### 【請求項6】

前記第1保護膜および前記第2保護膜はSiOxを含む請求項2又は5に記載の酸化物 薄膜トランジスタ基板

### 【請求項7】

前記第1ホールおよび前記第2ホールは複数個形成される請求項2に記載の酸化物薄膜 トランジスタ基板

### 【請求項8】

前記酸化物層は、インジウム(In)、亜鉛(Zn)、ガリウム(Ga)またはハフニ ウム(Hf)のうち少なくとも一つを含む非晶質酸化物で形成される請求項2に記載の酸 化物薄膜トランジスタ基板。

20

30

40

50

### 【請求項9】

前記非晶質酸化物は、インジウム(In)、亜鉛(Zn)およびガリウム(Ga)を含 む非晶質酸化物からなる請求項8に記載の酸化物薄膜トランジスタ基板。

#### 【請求項10】

前記非晶質酸化物は、インジウム(In)、亜鉛(Zn)およびハフニウム(Hf)を 含む非晶質酸化物からなる請求項8に記載の酸化物薄膜トランジスタ基板。

前記第1部分は前記画素電極と直接接続することを特徴とする請求項1に記載の酸化物 薄膜トランジスタ基板。

### 【請求項12】

前記第2部分は前記第1部分を完全に囲むことを特徴とする請求項1に記載の酸化物薄 膜トランジスタ基板。

### 【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、薄膜トランジスタ基板およびその製造方法に関するものである。より詳細に 酸化物半導体を利用した薄膜トランジスタおよびその製造方法に関するものである。

### 【背景技術】

### [0002]

薄膜トランジスタ(Thin film transistor、以下TFTという) は、液晶表示装置または有機発光表示装置などのような平板表示装置でスイッチング素子 として使用される。現在商用化されている液晶表示装置において、TFTのチャネル層は 大部分非晶質シリコーン層であり、この場合、TFTの移動度は約0.5cm<sup>2</sup> /Vsで ある。しかし、ディスプレイの大型化につれ高解像度および高周波数の駆動特性が要求さ れ、より高い移動度を有する高性能TFT技術が必要である。したがって、前記非晶質シ リコーン層より移動度が高い酸化物半導体層に対する研究が進んでいる。例えば、Ga‐ In - Zn - O層の移動度は非晶質シリコーン層の移動度の数十倍以上に優れた半導体特 性を見せている。

### [0003]

周知の通り、TFTのON電流はチャネル層の移動度およびチャネルのW/Lなどに比

10

20

30

40

50

例するため、移動度が高い酸化物半導体をTFTに使用する場合、ON電流を増加させることができる。前記Wはチャネルの幅を示し、Lはチャネルの長さを意味する。

【先行技術文献】

【特許文献】

[0004]

【特許文献 1 】大韓民国特開2008-0048936 公開(図 1 b)

【発明の概要】

【発明が解決しようとする課題】

[0005]

本発明は、酸化物半導体をチャネル層に適用して前述したような利益を追求すると共に、TFTの設計改善を通してON電流がさらに増加したTFT基板を提供することを目的とする。

[0006]

本発明のまた他の目的は、各画素に存在する寄生容量を減らし、表示装置の表示品質を向上させることである。

[0007]

本発明のまた他の目的は、TFTを成す各層間の整列に要る努力を減らし、工程を容易にすることである。

【課題を解決するための手段】

[0008]

前記のような目的を解決するため、基板、基板上に配置されるゲートライン、基板上にゲートラインから絶縁され、ゲートラインを交差するデータライン、ゲートラインとデータラインに電気的に接続され、酸化物層を含む酸化物薄膜トランジスタ、および酸化物薄膜トランジスタに電気的に接続される画素電極を含み、酸化物薄膜トランジスタの酸化物層は、チャネルを含み半導体特性を有する第1部分と、第1部分を囲み、導電性を有する第2部分を含み、第1部分は前記画素電極と電気的に接続され、前記第2部分は前記データラインと電気的に接続される酸化物薄膜トランジスタ基板が提供される。

[0009]

前記酸化物層上に配置され前記第1部分を露出させる第1ホールを有する第1保護膜、および前記第1保護膜の上に配置され前記第1ホールを露出させる第2ホールを有する第2保護膜をさらに含み、前記画素電極は前記第2保護膜の上に形成され、前記第1ホールおよび第2ホールを通じて前記第1部分とコンタクトすることができる。

[0010]

このように、導電性を有する酸化物層の第1領域が半導体特性を有する酸化物層の第2領域を囲むと共に前記第2領域に画素電極を直接コンタクトさせる構造によって、前記第1領域はソース電極であって、前記第2領域のうち前記画素電極にコンタクトされた部分はドレーン電極として機能することができる。したがって、本発明によるTFT構造に発れば、ドレーン電極が別途配置される必要はなく、ゲートパターンとドレーン電極間に発生する寄生容量を減らすことができる。周知の通り、前記寄生容量は、フリッカー現象など画質不良を起こす原因の一つであるため、その寄生容量を減らすことにより表示装置の表示品質を向上させることができる。また、前記酸化物層と前記第1ホールおよび第2ホールの間の整列のみを考慮すればよく、ソース電極とドレーン電極との間の整列が必要ないため、整列に要る努力を減らすことができ、全体的な工程が容易になる。さらに、本発明によるTFT構造によればチャネルの長さを減少させると共にチャネル幅を増加させることができるためTFT ON電流を増加させることができる。

[0011]

前記第1領域は、前記酸化物層上に配置された前記第1保護膜の境界と隣接した領域に 形成される。これについては詳細に後述する。

[0012]

前記第1保護膜と前記第2保護膜は互いに異なる物質で形成されるが、例えば前記第1

10

20

30

40

50

保護膜はシリコーン酸化物(SiOx)を含み、前記第2保護膜はシリコーン窒化物(SiNx)を含んでもよい。前記第2保護膜をSiNxで形成することによって前記酸化物層の第1領域に導電性を付与することができる。周知の通りSiNxを蒸着する工程には水素を含むガスが反応ガスとして添加されるが、この過程で前記酸化物層のうち前記SiNx層に近い部分の特性が変わり、導電性を有するようになる。前記酸化物層のうち前記第2保護膜に近い部分が酸化物層の縁である場合、前記酸化物層の縁に前記第1領域が形成され、前記第1領域は前記第2領域を囲む構造となる。

### [0013]

一方、前記第1保護膜と前記第2保護膜は互いに同じ物質で形成されてもよく、例えば、前記第1保護膜および前記第2保護膜は共にSiOxを含んでもよい。このように第2保護膜をSiOxで構成する場合、第2保護膜の蒸着により前記酸化物層に導電性を付与することができない。したがって、この場合には別途の工程により酸化物層に導電性を付与することができる。前記別途の工程は、例えば水素プラズマ処理であってもよい。

### [0014]

前記第 1 ホールおよび前記第 2 ホールは一個または複数個であってもよい。複数個を形成する場合、酸化物層と画素電極のコンタクト領域を広げることができる。

### [0015]

前記酸化物層は、インジウム(In)、亜鉛(Zn)、ガリウム(Ga)またはハフニウム(Hf)のうち少なくとも一つを含む非晶質酸化物でなされてもよい。具体的には、インジウム(In)、亜鉛(Zn)およびガリウム(Ga)を含む非晶質酸化物またはインジウム(In)、亜鉛(Zn)およびハフニウム(Hf)を含む非晶質酸化物でなされてもよい。

### [0016]

前述した酸化物TFT基板以外にも、前記した目的を達成するため、基板上に酸化物層形成する段階と、前記酸化物層の一部領域に導電性を付与する段階、および前記酸化物層の他の領域にコンタクトされた画素電極を形成する段階を含み、前記他の領域は前記一部領域によって囲まれる酸化物TFT基板製造方法が提供される。

### [0017]

より具体的に、前記導電性を付与する段階は、前記酸化物層を形成する段階の後に、前記酸化物層と一部重複する第1保護層を形成する段階、および前記第1保護層をマスクとして、前記酸化物層を水素プラズマ処理する段階を含んでもよい。前記第1保護層をマスクとして水素プラズマ処理をするため、前記第1保護層で覆われる領域の酸化物層は半導体特性が残ることに対し、前記第1保護層で覆われない他の領域は導電性を有するようになる。すなわち、前記第1保護層の境界付近を中心に半導体特性を有する酸化物層と導電性を有する酸化物層が区分される。

### [0018]

この場合、前記導電性を付与する段階の後に、前記導電性が付与された一部領域とコンタクトするデータパターンを形成する段階をさらに含んでもよい。

### [0019]

また、前記画素電極を形成する段階の前に、前記第1保護層上に第2保護層を形成する 段階、および前記第1保護層および前記第2保護層の一部をエッチングして前記酸化物層 の他の領域を露出させる段階をさらに含んでもよい。この場合、前記画素電極は前記露出 された酸化物層の他の領域とコンタクトする。

### [0020]

前記酸化物層に導電性を付与するまた他の方法は、前記酸化物層を形成する段階の後に、前記酸化物層と一部重複する第1保護層を形成する段階、および前記第1保護層を形成する段階の後に、前記酸化物層および前記第1保護層を覆う第2保護層を形成する段階を含んでもよく、前記第2保護層を形成する段階で水素を含む反応ガスが使用されてもよい。したがって、前記第2保護層に近い酸化物層の特性が変わり、導電性を有するようになる。前記第1保護層で覆われる領域の酸化物層は半導体特性が残ることに対し、前記第1

保護層で覆われない他の領域は導電性を有するようになる。すなわち、前記第 1 保護層の 境界付近を中心に半導体特性を有する酸化物層と導電性を有する酸化物層が区分される。

### [0021]

この場合、前記導電性を付与する段階の前に、前記酸化物層とコンタクトするデータパターンを形成する段階をさらに含んでもよい。

### [0022]

また、前記画素電極を形成する段階の前に、前記第1保護層および前記第2保護層の一部をエッチングし、前記酸化物層の他の領域を露出させる段階をさらに含んでもよい。この場合、前記画素電極は前記露出された酸化物層の他の領域とコンタクトする。

#### [0023]

その他実施形態の具体的な内容は詳細な説明および図面に含まれている。

【図面の簡単な説明】

#### [0024]

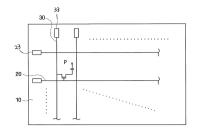

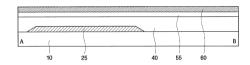

- 【図1】薄膜トランジスタ(TFT)基板を概ね示す図である。

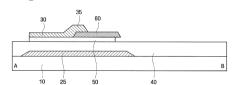

- 【図2】本発明の一実施形態によるTFT基板の一画素を概ね示す図である。

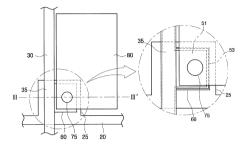

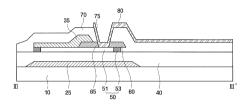

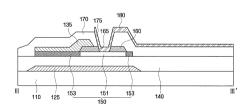

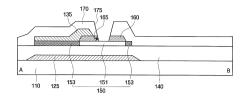

- 【図3】図2に示すIII-III′に沿って切断した断面図である。

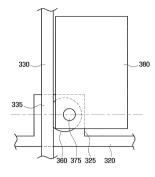

- 【図4】本発明の一実施形態によるTFT基板でTFT形状を変えた変形例を概ね示す図である。

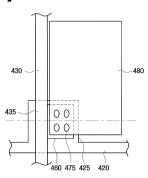

- 【図5】本発明の一実施形態によるTFT基板でTFT形状を変えた変形例を概ね示す図である。

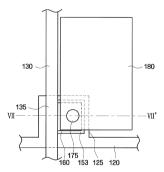

- 【図6】本発明の他の実施形態によるTFT基板の一画素を概ね示す図である。

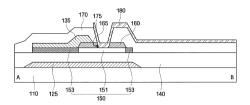

- 【図7】図6に示すVII・VII′に沿って切断した断面図である。

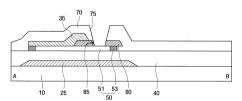

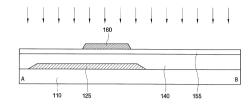

- 【図8A】本発明の一実施形態によるTFT基板の製造方法を順に追って示す図である。

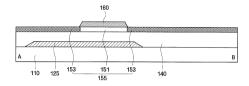

- 【図8B】本発明の一実施形態によるTFT基板の製造方法を順に追って示す図である。

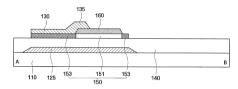

- 【図8C】本発明の一実施形態によるTFT基板の製造方法を順に追って示す図である。

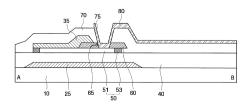

- 【図8D】本発明の一実施形態によるTFT基板の製造方法を順に追って示す図である。

- 【図8E】本発明の一実施形態によるTFT基板の製造方法を順に追って示す図である。

- 【図9A】本発明の他の実施形態によるTFT基板の製造方法を順に追って示す図である

【図9B】本発明の他の実施形態によるTFT基板の製造方法を順に追って示す図である

【図9C】本発明の他の実施形態によるTFT基板の製造方法を順に追って示す図である

【図9D】本発明の他の実施形態によるTFT基板の製造方法を順に追って示す図である

【図9E】本発明の他の実施形態によるTFT基板の製造方法を順に追って示す図である

【図9F】本発明の他の実施形態によるTFT基板の製造方法を順に追って示す図である

### 【発明を実施するための形態】

### [0025]

以下、添付した図面を参照して本発明の好ましい実施形態をより詳細に説明する。しかし、本発明は下記の実施形態に限定されず、他の形態で具現されることもできる。ここで紹介する実施形態は開示された内容がより完全になるようにするため、また当業者に本発明の技術的思想と特徴が充分に伝えられるようにするために提供される。図面において、各装置または膜(層)および領域の厚さは本発明の明確にするために誇張して示すものであり、また各装置は本明細書で説明されていない多様な付加の装置を備えてもよく、膜(層)が他の膜(層)または基板上に直接形成されるかそれらの間に追加的な膜(層)が介在されてもよい。

### [0026]

10

20

30

以下図1~図3を参照して本発明の一実施形態による薄膜トランジスタ(TFT)基板について説明する。

### [0027]

図1は、薄膜トランジスタ(TFT)基板を概ね示す図である。図2は、本発明の一実施形態によるTFT基板の一画素を概ね示す図である。図3は、図2に示すIII・II I'に沿って切断した断面図である。

#### [0028]

図示するようにTFT基板は絶縁基板10上に配置されたゲートライン20および前記ゲートラインと絶縁されて交差するデータライン30を含む。前記ゲートライン20と前記データライン30が交差する領域には画素(P)が形成され、TFT基板は複数の画素を含む。前記ゲートライン20の一端にはゲートパッド23が接続され、前記データライン30の一端にはデータパッド33が接続される。前記各画素(P)には前記ゲートライン20と前記データライン30に各々接続されたTFTおよび前記TFTに接続された画素電極80が配置される。

### [0029]

図2および図3を参照すると、前記TFTは前記ゲートライン20に接続され、前記ゲートライン20と共にゲートパターンを成すゲート電極25、前記ゲートパターンを覆うゲート絶縁膜40、前記ゲート絶縁膜40の上に配置され、前記ゲート電極25と重畳される酸化物層50、前記酸化物層50の上に配置された第1保護膜60、前記酸化物層50および前記第1保護膜60の一部と重複し、前記データライン30に接続されたソース電極35を含む。ソース電極35は別途のパターンで形成されることもできるが、後述するように前記データライン30の一部がソース電極として機能することもできる。

#### [0030]

前記TFTの上には第2保護膜70が配置される。前記第2保護膜70の上には前記第 1保護膜60に形成された第1ホール65および前記第2保護膜70に形成された第2ホール75を通じて前記酸化物層50とコンタクトする画素電極80が配置される。

### [0031]

前記ゲート絶縁膜40は、例えばシリコーン酸化物(SiOx)の単一膜またはシリコーン窒化物(SiNx)/シリコーン酸化物(SiOx)の二重膜で形成されてもよい。前記ゲート絶縁膜40が二重膜で形成される場合、シリコーン酸化物(SiOx)層が前記酸化物層50に近い位置に配置されることが好ましい。

### [0032]

前記第1保護膜60は、エッチストッパ(etch stopper)層として機能し、前記ソース電極35パターン時に前記酸化物層50のチャネル領域を保護する。前記第1保護膜60は、例えばシリコーン酸化物(SiOx)層で形成されてもよい。

### [0033]

本実施形態で、前記第2保護膜70は、例えばシリコーン窒化物(SiNx)を含む絶縁膜で形成されてもよい。

### [0034]

以下では、本実施形態による酸化物層50について詳細に説明する。

### [ 0 0 3 5 ]

前記酸化物層 50 はインジウム(In)、亜鉛(Zn)、ガリウム(Ga)またはハフニウム(Hf)のうち少なくとも一つを含む非晶質酸化物でなされてもよい。前記酸化物層 50 は、例えば Zn 酸化物または In-Zn 複合酸化物にガリウム(Ga)またはハフニウム(Hf)が添加されたものであってもよい。より詳細には、前記非晶質酸化物層は  $In_2O_3-Ga_2O_3-ZnO$ の形態で存在する Ga-In-Zn-O層、または HfO $_2-In_2O_3-ZnO$ の形態で存在する Hf-In-Zn-O 層であってもよい。

### [0036]

前記酸化物層50は、半導体特性を有する第1領域51および前記第1領域を囲み、導電性を有する第2領域53を含む。前記第2領域は前記ソース電極35に接続する。本実

10

20

30

40

施形態において、前記第2領域は53前記酸化物層50のうち前記第2保護膜70に隣接した領域に形成される。また他の観点からは、前記第2領域53は、前記酸化物層50のうち前記第1保護膜60の境界と近い領域に形成される。

### [0037]

前記第2保護膜70は、例えば化学気相蒸着法(CVD: Chemical Vapor Deposition)によって前記基板10上に蒸着することができる。一般的に、CVD法によってシリコーン窒化物(SiNx)を蒸着する工程には水素を含むガスが反応ガスとして添加されるが、水素の影響によって前記酸化物層50のうちシリコーン窒化物(SiNx)に隣接した領域の特性が変わり、導電性を有するようになる。これに対し、前記酸化物層50のうち前記第2保護膜70と隣接しない領域は、半導体の特性を維持することができる。

#### [0038]

本実施形態のように、前記酸化物層50のうち前記第2保護膜70に隣接する部分が前記酸化物層50の縁である場合、前記酸化物層50の縁に前記第2領域53が形成され、前記第2領域53は前記第1領域51を囲む構造となる。すなわち、前記酸化物層50は、半導体特性を有する第1領域51と前記第1領域を囲み、導電性を有する第2領域53に分けられる。

### [0039]

前述したように、前記第2領域53は、前記ソース電極35と接続するため前記データライン30に沿って流入された信号は前記ソース電極35を経て前記第2領域53にまで及ぼすことができる。すなわち、前記第2領域53は前記ソース電極35と共にまた他のソース電極として機能することができる。または、別途のソース電極を形成しない場合、前記第2領域53は前記データライン30のうち前記酸化物層50にコンタクトされた部分と共にソース電極として機能することができる。

### [0040]

一方、図2および図3に図示するように、前記第1ホール65および第2ホール75は前記第1領域51の一部に対応する位置に形成される。すなわち、前記第1ホールおよび第2ホール(65,75)によって前記第1領域51の一部が露出される。

### [0041]

前述したように、前記画素電極 8 0 は前記第 1 ホールおよび第 2 ホール(65,75)を通じて前記第 1 領域 5 1 とコンタクトするため、本発明によれば、ドレーン電極のための別途のパターンを形成する必要がなくなる。

### [0042]

結果的に、前記第2領域53はソース電極であって、前記第1領域51のうち前記画素電極80とコンタクトされた部分はドレーン電極であって、前記第1領域51のうち前記画素電極80とコンタクトされない部分はチャネルとして機能する。

### [0043]

したがって、本発明によるTFT構造によれば、ゲートパターンとドレーン電極との間に発生する寄生容量を減らすことができる。周知の通り、前記寄生容量はフリッカー現象など画質不良を起こす原因のうち一つであるため、その寄生容量を減らすことにより表示装置の表示品質を向上させることができる。

## [0044]

また、本発明によるTFT構造によればチャネルの長さを減少させると共にチャネル幅を増加させることができるためTFT ON電流を増加させることができる。

### [0045]

本発明の一実施形態によるTFTの形状は、前述したような特徴を有する限り、図2および図3に示すものに制限されない。例えば、図4には酸化物層(図示せず)および第1保護膜360が円形である場合が図示されている。また、図5には第1ホール(図示せず)および第2ホール475が酸化物層の第1領域内に複数個形成された場合が図示されている。

### [0046]

10

20

30

40

以下では本発明によるTFT基板の他の実施形態について図6および図7を参照して詳細に説明する。前述した一実施形態と同一の構成および機能に対する詳細な説明は省略する。

#### [0047]

図 6 は、本発明の他の実施形態によるTFT基板の一画素を概ね示す図である。図 7 は、図 6 に示すVII・VII ′ に沿って切断した断面図である。

#### [0048]

図示するようにTFT基板は絶縁基板110上に配置されたゲートライン120、前記ゲートラインと絶縁されて交差するデータライン130、ゲートライン120と前記データライン130に各々接続されたTFTおよび前記TFTに接続された画素電極180を含む。

### [0049]

前記TFTは前記ゲートライン120に接続され前記ゲートライン120と共にゲートパターンを成すゲート電極125、前記ゲートパターンを覆うゲート絶縁膜140、前記ゲート絶縁膜140の上に配置され、前記ゲート電極125と重畳される酸化物層150、前記酸化物層150の上に配置された第1保護膜160、前記酸化物層150および前記第1保護膜160の一部と重複し、前記データライン130に接続されたソース電極135を含む。ソース電極35は別途のパターンで形成されることもできるが、前述した一実施形態のように前記データライン30の一部がソース電極として機能することもできる。前記TFTの上には第2保護膜170が配置される。前記第2保護膜170の上には前記第1保護膜160に形成された第1ホール165および前記第2保護膜170に形成された第2ホール175を通じて前記酸化物層50とコンタクトする画素電極180が配置される。

#### [0050]

前記第1保護膜160は、エッチストッパ(etch stopper)層として機能し、前記ソース電極135パターン時に前記酸化物層150のチャネル領域を保護する。前記第1保護膜60は、例えばシリコーン酸化物(SiOx)で形成されてもよい。

### [0051]

本実施形態で、前記第2保護膜70は前記第1保護膜160のような物質で形成されて もよく、例えばシリコーン酸化物(SiOx)で形成されてもよい。

### [0052]

以下では前記酸化物層150についてより詳細に説明する。

### [0053]

前記酸化物層150は前述した一実施形態と同一の物質で形成され、半導体特性を有する第1領域151および前記第1領域を囲み、導電性を有する第2領域153を含む。前記第2領域153は前記ソース電極35または前記データライン30の一部に接続する。

### [0054]

前記のように第2保護膜170がシリコーン酸化物で形成される場合、前述した一実施 形態と異なり前記酸化物層150の特性は前記第2保護膜170の蒸着することによって 大きな影響は受けない。すなわち、第2保護膜170を蒸着するだけで前記酸化物層15 0の一部に導電性を付与することができず、別途の手段により前記第2領域153を形成 する。

### [0055]

前記別途の手段は、例えば、前記第1保護膜160をマスクとして前記酸化物層150を水素プラズマ処理することであってもよい。この場合、前記酸化物層150のうち、前記第1保護膜160と重畳された領域は実質的に水素プラズマ処理されないため、半導体特性を維持することに対し、前記第1保護膜160と重畳しない部分は水素プラズマ処理によって導電性を有する。

### [0056]

したがって、本実施形態による酸化物層150の第2領域153は、図6に示すように

20

10

30

40

10

20

30

40

50

前記第1保護膜160の境界付近、特に第1保護膜160の外部に形成される。すなわち、前記第2領域153は前記第1保護膜160の外部に突出した部分に形成される。

### [0057]

前記画素電極180が前記第1ホールおよび第2ホール(165,175)を通じて前記第1領域151とコンタクトすることは前述した一実施形態と同一であるため、詳細な説明は省略する。

#### [0058]

また、本実施形態で前記TFTの形状および前記第1ホール、第2ホール(165、1 75)の個数などを多様に変更できることは前述した一実施形態と同様である。

### [0059]

以下では、本発明の一実施形態によるTFT基板の製造方法について説明する。

#### [0060]

図8A~8Eは、本発明の一実施形態によるTFT基板の製造方法を順に追って示す図である。

### [0061]

図8Aを参照すると、基板10の上にゲート電極25を含むゲートパターンを形成した後に前記基板10の上に前記パターンを覆うゲート絶縁膜40を形成する。前記ゲート絶縁膜は、例えば前記基板10上にシリコーン酸化物(SiOx)からなる単一層を形成するか、またはシリコーン室化物(SiNx)およびシリコーン酸化物(SiOx)を連続して蒸着し、形成することができる。

### [0062]

図8Bを参照すると、前記ゲート絶縁膜40の上に酸化物55をPVD(Physical Vapor Deposition)、CVD、ALD(Atomic Layer Deposition)またはソリューションプロセスなどの工程により蒸着する。前記酸化物55はインジウム(In)、亜鉛(Zn)、ガリウム(Ga)またはハフニウム(Hf)のうち少なくとも一つを含む非晶質酸化物でなされてもよい。例えばスパッタリング(sputtering)工程によりGa-In-Zn-O酸化物層を形成する場合、In<sub>2</sub>O<sub>3</sub>、Ga<sub>2</sub>O<sub>3</sub>およびZnOで形成された各々のターゲットを利用するか、またはGa-In-Zn酸化物の単一ターゲットを利用することができる。また、スパッタリング(sputtering)工程によりhf-In-Zn-O酸化物層を形成する場合、HfO<sub>2</sub>、In<sub>2</sub>O<sub>3</sub>およびZnOで形成された各々のターゲットを利用するか、またはHf-In-Zn酸化物の単一ターゲットを利用することができる。

### [0063]

次に、前記酸化物 5 5 の上に、シリコーン酸化物(SiOx)層を連続して蒸着した後パターニングし、図 8 B に示すように第 1 保護層 6 0 形成する。前記パターニングは、例えば乾式エッチング(dry etch)工程により行われることができる。

### [0064]

図8Cを参照すると、前記基板10上に金属層(図示せず)を蒸着した後、前記金属層と前記酸化物を共にパターニングしてデータライン30、ソース電極35および酸化物層50を形成する。前記パターニングは例えば湿式エッチング(wet etch)により行われることができる。この場合、前記酸化物層50は前記データライン30、ソース電極35および前記第1保護膜60の下部に形成される。すなわち、前記ソース電極35は前記酸化物層50および前記第1保護膜60の一部と重複する。前記金属層は、例えば、A1、Mo、TiおよびCuのうち少なくとも一つを含む単一層または多重層で形成されてもよい。

### [0065]

本実施形態では前記酸化物と前記金属層を一つのマスクを使用してパターニングする場合について説明したが、前記酸化物と金属層は別個のマスクによりパターニングされてもよい。この場合、酸化物層は、データラインの下部において、酸化物層の端部が第2保護膜に対して一部が露出されるように形成されれば良く、データラインの下部の全てにおい

て酸化物層が配置されていなくてもよい。

### [0066]

図8 Dを参照すると、前記基板 1 0 全面にシリコーン窒化物(SiNx)層を例えばCVD法によって蒸着して第 2 保護膜 7 0 を形成する。CVDによるシリコーン窒化物層蒸着時 SiH4,NH3,H2 などが反応ガスとして添加される。このようにシリコーン窒化物の蒸着過程に水素を含む反応ガスが添加されるため、前記酸化物層 5 0 のうち前記第 2 保護膜 7 0 に隣接した領域は水素の影響によってその特性が変わり導電性を有するようになる。反面、前記第 2 保護膜 7 0 に隣接しない酸化物層 5 0 領域は半導体特性を維持する。

### [0067]

10 め前

20

30

図 8 D に示す場合は前記酸化物層 5 0 の縁領域が前記第 2 保護膜 7 0 に隣接するため前記酸化物層 5 0 の縁領域が導電性を有する。

### [0068]

また他の観点からは、前記酸化物層50のうち前記第1保護膜60の境界と近い領域が 導電性を有する。その結果、前記酸化物層50のうち導電性を有する第2領域53は、半 導体特性を有する第1領域51を囲む構造となる。

#### [0069]

前記第2保護膜70および前記第1保護膜60をパターニングして第2ホール75および第1ホール65を形成する。前記第1ホールおよび第2ホール(65,75)は同一の位置に形成され、前記酸化物層50の第1領域51一部を露出させる。前記第1ホールおよび第2ホール(65,75)は一度のエッチング過程により形成されることができる。

### [0070]

図8 E を参照すると、前記第 2 保護膜 7 0 の上に透明導電層を形成した後パターニングして画素電極 8 0 を形成する。前記画素電極 8 0 は前記第 1 ホールおよび第 2 ホール(6 5 , 7 5 )を通じて前記酸化物層の第 1 領域 5 1 とコンタクトする。すなわち、前記酸化物層 5 0 の第 1 領域 5 1 のうち前記画素電極 8 0 とコンタクトされた部分がドレーン電極として機能する。

### [0071]

したがって、本発明によれば、ドレーン電極のための別途のパターンを形成する必要がない。その結果、前記酸化物層 5 0 と前記第 1 ホールおよび第 2 ホール(6 5 , 7 5 ) の間の整列のみを考慮すればよく、ソース電極とドレーン電極との間の整列は必要ないため、整列に要る努力を減らすことができ、全体の工程が容易になる。

### [0072]

以下では本発明の第2実施形態によるTFTの製造方法を説明する。前述した第1実施 形態によるTFTの製造方法と同一の構成に対する詳細な説明は省略する。

### [0073]

図 9 A ~ 9 F は、本発明の他の実施形態によるTFT基板の製造方法を順に追って示す 図である。

### [0074]

図9Aおよび9Bを参照すると、酸化物の上に第1保護膜160を形成するまでの工程 40は前述した第1実施形態と同一である。

### [0075]

図9 B および9 C を参照すると、前記第 1 保護膜 1 6 0 をマスクとして前記酸化物 1 5 5 を水素プラズマ処理する。前記水素プラズマ処理によって前記酸化物 1 5 5 のうち前記第 1 保護膜 1 6 0 によって覆われた領域を除いた部分が導電性を有するようになる。前記第 1 保護膜 1 6 0 によって覆われた領域は半導体特性を維持する。

### [0076]

このように、本実施形態では別途の工程により酸化物層に導電性を付与するため、前述 した実施形態の場合より導電性がさらに強化されることができる。

### [0077]

図9 Dを参照すると、前記基板 1 1 0 上に金属層(図示せず)を蒸着した後、前記金属層と前記酸化物 1 5 5 を一個のマスクを使用して共にパターニングすることによってデータライン 1 3 0、ソース電極 1 3 5 および酸化物層 1 5 0 を形成する。前記酸化物層 1 5 0 は前記データライン 1 3 0、ソース電極 1 3 5 および前記第 1 保護膜 1 6 0 の下部に形成される。すなわち、前記ソース電極 1 3 5 は前記酸化物層 1 5 0 および前記第 1 保護膜 1 6 0 の一部と重複する。

### [0078]

前記酸化物層150は、半導体特性を有し、前記第1保護膜160の下部に配置された第1領域151と、導電性を有し、前記第1領域151を囲む第2領域153と、に区分される。図9Dに示すように、本実施形態により形成された第2領域153は、前記ソース電極135または前記データライン130と、より広い領域においてコンタクトすることができる。また、本実施形態により形成された第2領域153は、前述した実施形態により形成された第2領域253は、前述した実施形態により形成された第2領域とは異なり、前記第1保護膜160の外部に突出する構造を有する。例えば図9D等に示すように、右側の第2領域153は第1保護膜160よりも突出して形成されている。

### [0079]

一方、前述した実施形態と同様に、本実施形態においても前記酸化物と金属層は別個のマスクを通じてパターニングされてもよい。

#### [0080]

続いて、図9 E および図9 F を参照すると、前述した実施形態と同一の工程によって第2 保護膜170、第1ホールおよび第2ホール(165,175)、前記第1ホールおよび第2ホール(165,175)を通じて前記第1領域151とコンタクトされる画素電極180が各々形成される。

#### [0081]

前述した本発明によれば、酸化物半導体をチャネル層に適用することによって移動度を向上させることができるだけではなく、TFTのチャネル長さを減らし、チャネル幅を伸ばすことによってON電流がより一層増加したTFT基板を提供することができる。

### [0082]

また、別途のドレーン電極を除去することによって表示品質を低下させる寄生容量を減らし、表示装置の表示品質を向上させることができる。

### [0083]

さらに、TFTを成す各層間の整列に要る努力を減らし、工程を容易にすることができる。

10

30

【図1】

【図2】

【図3】

【図6】

【図7】

【図8A】

【図4】

【図5】

【図8B】

【図8C】

【図8D】

【図8E】

## 【図9A】

# 【図9B】

## 【図 9 C 】

## 【図 9 D】

## 【図9E】

## 【図9F】

### フロントページの続き

(51) Int.CI. F I

H 0 1 L 29/78 6 1 6 T H 0 1 L 29/78 6 1 6 T H 0 1 L 29/78 6 1 9 A

(72)発明者 李 永 旭

大韓民国京畿道水原市霊通區梅灘洞514-14未來ヴィレッジ イー棟108號

(72)発明者 李 禹 根

大韓民国京畿道龍仁市器興區甫羅洞現代モーニングサイドアパート2次107棟204號

審査官 田井 伸幸

(56)参考文献 特開2010-166030(JP,A)

特開2010-041058(JP,A)

特開2009-010362(JP,A)

特開2008-040343(JP,A)

特開2009-260378(JP,A)

特開平11-112002(JP,A)

(58)調査した分野(Int.CI., DB名)

G02F 1/1343 - 1/1345,

1/135- 1/1368

G09F 9/00- 9/46

H01L 21/33、

27/32、

29/786