# (10) **DE 10 2012 109 922 B4** 2020.04.16

(12)

# **Patentschrift**

(21) Aktenzeichen: 10 2012 109 922.7

(22) Anmeldetag: 18.10.2012(43) Offenlegungstag: 17.10.2013

(45) Veröffentlichungstag

der Patenterteilung: 16.04.2020

(51) Int Cl.: **H01L 21/60** (2006.01)

**H01L 23/50** (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

61/624,928 16.04.2012 US 13/526,073 18.06.2012 US

(62) Teilung in:

10 2012 025 865.8

(73) Patentinhaber:

Taiwan Semiconductor Manufacturing Co., Ltd., Hsin-Chu, TW

(74) Vertreter:

BOEHMERT & BOEHMERT Anwaltspartnerschaft mbB - Patentanwälte Rechtsanwälte, 28209 Bremen, DE (72) Erfinder:

Yu, Chen-Hua, Hsinchu, TW; Lii, Mirng-Ji, Sinpu, Hsinchu, TW; Liu, Chung-Shi, Hsinchu, TW; Chen, Meng-Tse, Changzhi Township, Pingtung, TW; Lin, Wei-Hung, Xinfeng Township, Hsinchu, TW; Cheng, Ming-Da, Shihsing Village, Jhubei, TW

(56) Ermittelter Stand der Technik:

| US | 2006 / 0 035 453 | <b>A</b> 1 |

|----|------------------|------------|

| US | 2009 / 0 146 314 | <b>A</b> 1 |

| US | 2009 / 0 256 256 | <b>A</b> 1 |

| US | 2010 / 0 084 765 | <b>A</b> 1 |

| WO | 2007/ 069 606    | <b>A</b> 1 |

### (54) Bezeichnung: Package-on-Package-Struktur und Verfahren zur Herstellung derselben

(57) Hauptanspruch: Verfahren für die Ausbildung eines Halbleiterbauteil-Package, das aufweist:

Bereitstellen eines Substrats (200) mit einem Kontaktblock (210);

Verbinden einer Metallkugel (240) mit dem Kontaktblock (210), um eine erste Verbindungsstruktur (255) auszubilden:

Verbinden eines Halbleiterchips (105) mit dem Substrat (200), wobei der Halbleiterchip (105) neben der Verbindungsstruktur (255) angeordnet ist;

Verbinden eines Chip-Package (110) mit einer Oberfläche des Substrats (200), die mit dem Halbleiterchip (105) verbunden ist, wobei das Verbinden eines Chip-Package (110) eine zweite Verbindungsstruktur (101) zwischen einem Anschluss auf dem Chip-Package (110) und der Metallkugel (240), die mit dem Substrat (200) verbunden ist, ausbildet; Ausbilden einer gegossenen Unterfüllung (260) auf dem Substrat (200); und

Vereinzeln des Halbleiterbauteils, einschließlich des Chip-Package (110) und des Halbleiterchips (105), das mit dem Substrat (200) über einen verbleibenden Abschnitt des Substrats (200) verbunden ist, wobei

die Metallkugel (240) einen nicht lothaltigen Metallkern (240 $_{\rm l}$ ) aufweist, der mit einer leitfähigen Zwischenschicht (240 $_{\rm c2}$ ) und einer Lotschicht (240 $_{\rm c1}$ ) beschichtet ist, wobei die leitfähige Zwischenschicht (240 $_{\rm c2}$ ) zwischen dem Me-

tallkern (240<sub>I</sub>) und der Lotschicht (240<sub>c1</sub>) angeordnet ist, wobei eine Breite  $W_3$  des Metallkerns (2401) zwischen 100 µm und 250 µm beträgt und die Dicke der leitfähigen Zwischenschicht (240<sub>c2</sub>) und der Lotschicht (240<sub>c1</sub>) jeweils ...

### **Beschreibung**

## HINTERGRUND

[0001] Halbleiterbauteile werden in einem breiten Gebiet elektronischer Anwendungen verwendet, wie beispielsweise in Personal-Computern, Mobiltelefonen, Digitalkameras und anderen elektronischen Geräten. Halbleiterbauteile werden typischerweise durch aufeinanderfolgendes Abscheiden nicht leitender oder dielektrischer Schichten, leitfähiger Schichten und Halbleiterschichten von Materialien über einem Halbleitersubstrat und durch Strukturieren der verschiedenen Materialschichten unter Verwendung von Lithographie hergestellt, um Schaltkreiskomponenten und -elemente auf diesen auszubilden.

[0002] Die Halbleiterindustrie setzt damit fort, die Integrationsdichte verschiedener elektronischer Komponenten (z.B. Transistoren, Dioden, Widerstände, Kondensatoren, usw.) durch kontinuierliche Verringerung der minimalen Bauteilgröße zu verbessern, was es erlaubt, dass mehr Komponenten in einen gegebenen Bereich integriert werden können. Diese kleineren elektronischen Komponenten erfordern ebenfalls kleinere Gehäuse, die bei manchen Anwendungen eine geringere Fläche und/oder geringere Höhe als aus der Vergangenheit bekannte Gehäuse einnehmen.

**[0003]** Somit wurden neuartige Packtechnologien wie Package-on-Package (PoP) entwickelt, bei welchen ein oberes Package mit einem Bauteilchip mit einem unteren Package mit einem weiteren Bauteilchip verbunden wird. Durch die Einführung der neuen Packtechnologien konnte der Integrationsgrad der Packages gesteigert werden. Diese vergleichsweise neuartigen Packtechnologien für Halbleiter begegnen nun Hürden bei der Herstellung.

**[0004]** Die WO 2007/ 069 606 A1 beschreibt ein Verfahren für die Ausbildung eines Halbleiterbauteil-Packages, bei dem ein unteres Substrat mit einem Halbleiter-Chip und einem oberen Substrat verbunden wird. Für die Verbindung zwischen dem unteren und dem oberen Substrat können Lötkugeln verwendet werden, in denen ein Abstandshalter angeordnet ist, wobei der Abstandshalter aus Kupfer oder einem Polymer-Material bestehen kann.

[0005] Ein weiteres Verfahren zum Ausbilden eines Halbleiterbauteil-Packages ist aus der US 2009 / 0 146 314 A1 bekannt. Dabei werden ein oberes und ein unteres Substrat durch einen dazwischen angeordneten Halbleiterchip hindurch miteinander elektrisch verbunden.

[0006] Die US 2009 / 0 256 256 A1 offenbart eine mehrschichtige Lotkugel mit einem formstabilen Kern, der mit einer oder mehreren Schichten be-

schichtet ist. Der Kern kann beispielsweise aus einem Polymer-Material bestehen, welches mit einer leitfähigen Schicht versehen ist, um eine leitende Verbindung herzustellen. Alternativ kann auch der Kern selbst auch aus einem leitfähigen Material wie Kupfer bestehen. Über der leitfähigen Schicht kann eine nickelhaltigen Schutzschicht und eine Lotschicht aufgebracht sein.

**[0007]** Die US 2010 / 0 084 765 A1 beschreibt eine mehrschichte Lotkugel mit einem Kupferkern, der mit einer Kupferlegierung und einer Lotschicht versehen ist.

**[0008]** Aus der US 2006 / 0 035 453 A1 ist ein Verfahren zur Strukturierung eines Kontaktpads für eine Lötverbindung bekannt.

#### ZUSAMMENFASSUNG

[0009] Die Erfindung stellt ein Verfahren zur Ausbildung eines Halbleiterbauteil-Package mit den Merkmalen des Anspruchs 1 und ein Halbleiter-Package mit den Merkmalen des Anspruchs 6 bereit. Beispielhafte Ausführungsformen sind in den abhängigen Ansprüchen angegeben. Das erfindungsgemäße Verfahren weist auf:

Bereitstellen eines Substrats mit einem Kontaktblock; Anbinden einer Metallkugel an den Kontaktblock, um eine erste Verbindungsstruktur auszubilden; Anbinden eines Halbleiterchips an das Substrat, wobei der Halbleiterchip neben der Verbindungsstruktur angeordnet ist; Anbinden eines Chip-Package an eine Oberfläche des Substrats, die mit dem Halbleiterchip verbunden ist, wobei das Anbinden eines Chip-Package eine zweite Verbindungsstruktur zwischen einem Anschluss auf dem Chip-Package und der Metallkugel, die auf dem Substrat angebunden ist, ausbildet; Ausbilden einer gegossenen Unterfüllung (molded underfill (MUF)) auf dem Substrat; und Vereinzeln des Halbleiterbauteils einschließlich des Chip-Package und des Halbleiterchips, der mit dem Substrat verbunden sind, in einem verbleibenden Abschnitt des Substrats. Die Metallkugel weist einen nicht lothaltigen Metallkern auf, der mit einer leitfähigen Zwischenschicht und einer Lotschicht beschichtet ist. Die leitfähige Zwischenschicht ist zwischen dem Metallkern und der Lotschicht angeordnet ist. Eine Breite des Metallkerns beträgt zwischen 100 µm und 250 µm. Die Dicke der leitfähigen Zwischenschicht und der Lotschicht beträgt jeweils zwischen 0,5 µm und 10 µm. Das Verfahren umfasst weiterhin ein Abflachen eines oberen Abschnitts der Metallkugel durch Gewichtbeaufschlagung der Metallkugel vor dem Verbinden des Chip-Packages. Ein Verhältnis zwischen einer Breite des abgeflachten oberen Abschnitts der Metallkugel und einer maximalen Breite der Metallkugel liegt

## DE 10 2012 109 922 B4 2020.04.16

in einem Bereich zwischen 20 % und 80 %. Die Breite des abgeflachten oberen Abschnitts der Metallkugel wird so gewählt, dass ein oberer Abschnitt des Metallkerns abgeflacht wird.

**[0010]** Die Metallkugel umfasst einen nicht lötfähigen Metallkern, wie beispielsweise eine nicht lötfähige Metallkugel umfassend Kupfer, Aluminium, Silber, Gold, Nickel, Wolfram, Legierungen dieser, oder Kombinationen dieser.

[0011] Bei einer Ausführungsform weist das Halbleiterbauteil-Package eine weitere Metallkugel neben der Metallkugel auf, und ein Abstand zwischen der Metallkugel und der weiteren Metallkugel liegt in einem Bereich zwischen 150 µm und ungefähr 300 µm.

**[0012]** Bei einer Ausführungsform umfasst die Zwischenschicht Ti oder Ni.

[0013] Der Kontaktblock kann eine temporäre Schutzschicht aufweisen, wobei die temporäre Schutzschicht vor oder während der Ausbildung der ersten Verbindungsstruktur entfernt wird, wobei die temporäre Schutzschicht einen organischen Lötverhinderer (organic soldering preservative (OSP)) aufweisen kann.

**[0014]** Bei einer Ausführungsform ist die MUF zwischen dem Chip-Package und dem Substrat angeordnet, wobei die MUF ebenfalls zwischen dem Halbleiterchip und dem Substrat angeordnet ist.

**[0015]** Bei einer Ausführungsform bedeckt die ausgebildete MUF nicht eine Oberfläche des Halbleiterchips und eine obere Position der Metallkugel.

**[0016]** Bei einer Ausführungsform umfasst der Kontaktblock einen leitfähigen Block auf dem Substrat und eine Verbindungsschicht, wobei der leitfähige Block mit einem Verbinder in dem Substrat verbunden ist.

**[0017]** Die Erfindung stellt weiterhin ein nicht beanspruchtes Verfahren zur Ausbildung eines Halbleiterbauteil-Package bereit, das aufweist:

Anbinden eines Halbleiterchips an ein Substrat, wobei das Anbinden des Halbleiterchips an das Substrat eine erste Verbindungsstruktur einschließlich einer nicht lötfähigen Metallkugel ausbildet; Anbinden eines Chip-Package an eine Oberfläche des Substrats, die mit dem Halbleiterchip verbunden ist, wobei das Anbinden eines Chip-Package eine zweite Verbindungsstruktur zwischen einem Verbinder auf dem Chip-Package und der Metallkugel, die mit dem Substrat verbunden ist, ausbildet; Ausbilden einer gegossenen Unterfüllung (MUF) auf dem Substrat; und Vereinzeln des Halbleiterbau-

teils einschließlich des Chip-Package und des Halbleiterchips, die mit dem Substrat in einem verbleibenden Abschnitt des Substrats verbunden sind.

[0018] Das erfindungsgemäße Halbleiter-Package weist auf: ein Substrat; einen ersten Halbleiterchip, der mit dem Substrat verbunden ist; ein Chip-Package, das mit dem Substrat verbunden ist, wobei der erste Halbleiterchip zwischen dem Chip-Package und dem Substrat angeordnet ist, und wobei das Chip-Package mit dem Substrat mittels einer Verbindungsstruktur umfassend eine Metallkugel verbunden ist, und wobei das Chip-Package zumindest einen zweiten Halbleiterchip aufweist; und eine gegossene Unterfüllung auf dem Substrat. Die Metallkugel weist einen nicht lothaltigen Metallkern auf, der mit einer leitfähigen Zwischenschicht und einer Lotschicht beschichtet ist. Die leitfähige Zwischenschicht ist zwischen dem Metallkern und der Lotschicht angeordnet. Eine Breite des Metallkerns beträgt zwischen 100 µm und 250 µm. Die Dicke der leitfähigen Zwischenschicht und der Lotschicht beträgt jeweils zwischen 0, 5 µm und 10 µm. Eine Oberfläche der Metallkugel ist abgeflacht, wobei ein Verhältnis zwischen einer Breite des abgeflachten oberen Abschnitts der Metallkugel und einer maximalen Breite der Metallkugel in einem Bereich zwischen 20 % und 80 % liegt. Die Breite des abgeflachten oberen Abschnitts der Metallkugel ist so gewählt, dass ein oberer Abschnitt des Metallkerns abgeflacht ist.

**[0019]** Der nicht lötfähige Metallkern kann Kupfer, Aluminium, Silber, Gold, Nickel, Wolfram, Legierungen dieser oder Kombinationen dieser aufweisen.

#### Figurenliste

**[0020]** Für ein umfassenderes Verständnis der vorliegenden Offenbarung und deren Vorteile wird nun auf die nachstehende Beschreibung in Verbindung mit den begleitenden Figuren Bezug genommen, wobei:

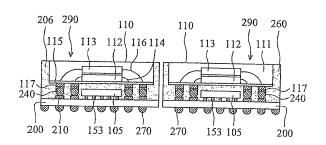

**Fig. 1A** zeigt eine perspektivische Ansicht eines Package gemäß manchen Beispielen.

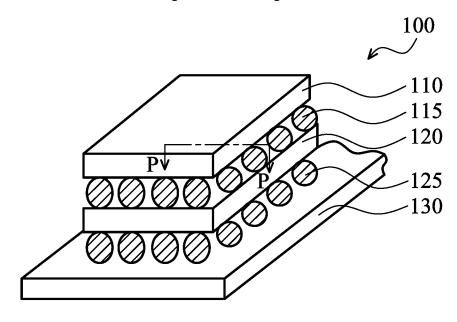

**Fig. 1B** zeigt eine Querschnittsansicht eines Abschnitts des Package gemäß **Fig. 1A** entlang der Linie **P-P** gemäß manchen Beispielen.

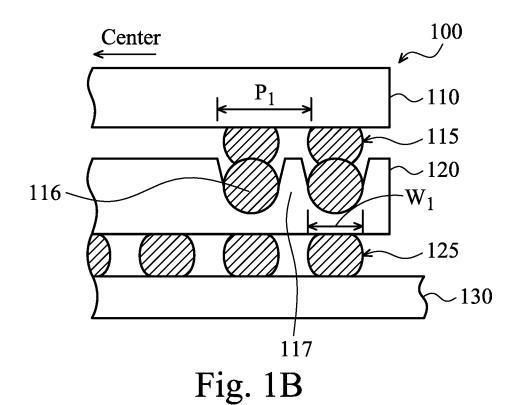

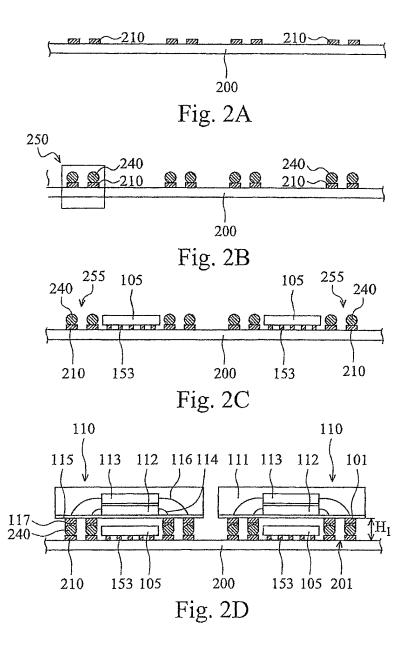

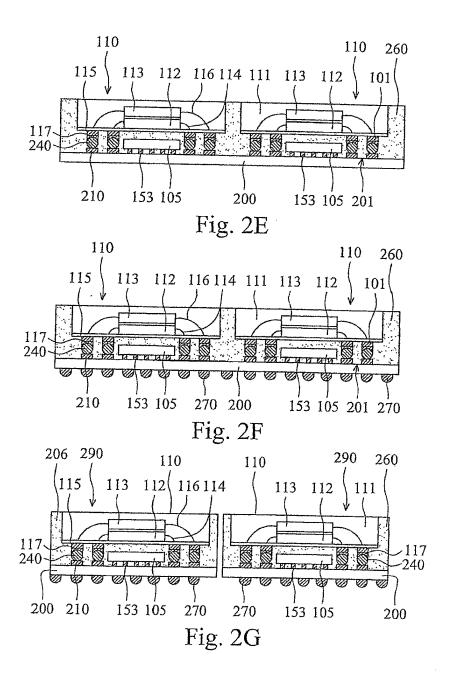

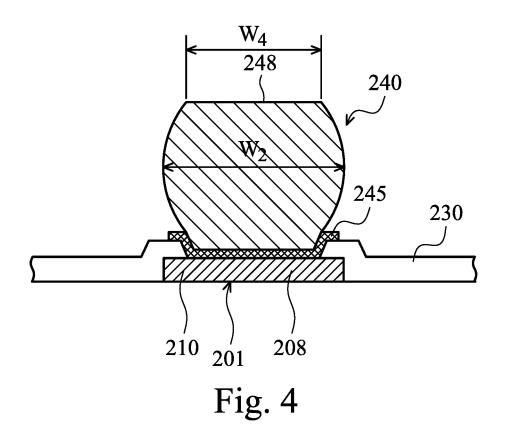

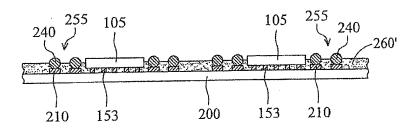

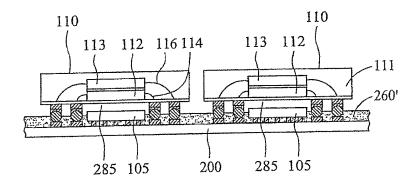

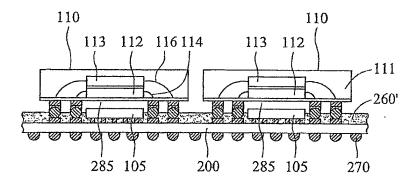

**Fig. 2A - Fig. 2G** sind Querschnittsansichten einer Package-on-Package-Struktur bei unterschiedlichen Herstellungsstadien gemäß manchen Beispielen.

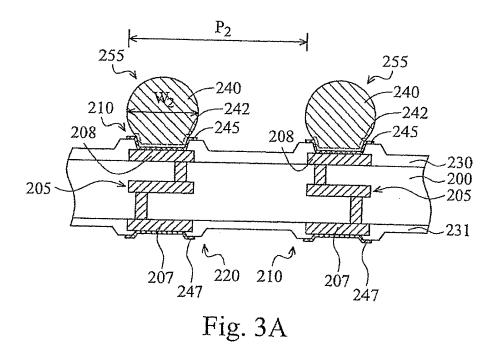

**Fig. 3A - Fig. 3C** sind Querschnittsansichten von verbundenen Metallkugelstrukturen gemäß manchen Beispielen.

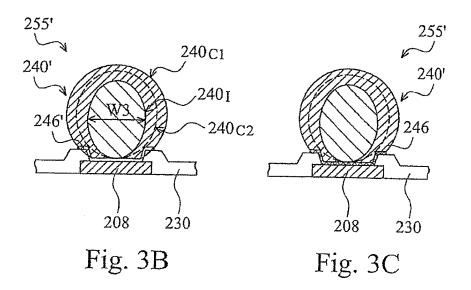

Fig. 4 ist eine Querschnittsansicht einer verbundenen Metallkugelstruktur gemäß manchen Bei-

spielen, nachdem die Oberfläche der Metallkugel abgeflacht wurde.

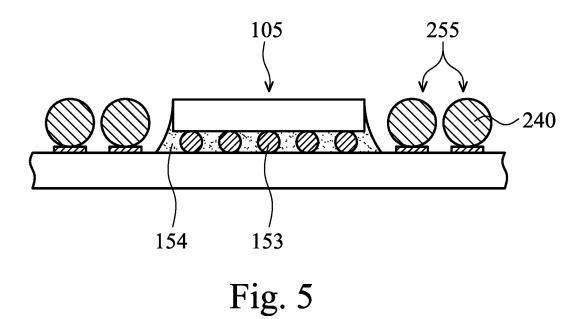

**Fig. 5** ist eine Querschnittsansicht eines Halbleiterchips, der mit einem Substrat verbunden ist, das mit einer Unterfüllung in dem Freiraum zwischen dem Halbleiterchip und dem Substrat ausgefüllt wurde, gemäß manchen Beispielen.

**Fig. 6A - Fig. 6D** sind Querschnittsansichten einer Package-on-Package-Struktur bei unterschiedlichen Herstellungsstadien, gemäß manchen Beispielen.

**[0021]** Korrespondierende Bezugszeichen und Symbole in den unterschiedlichen Figuren beziehen sich, soweit dies nicht anderweitig angegeben ist, grundsätzlich auf entsprechende Bauteile.

**[0022]** Die Figuren sind derart gezeichnet, um verständlich die relevanten Aspekte der Beispielen zu veranschaulichen, und sie sind nicht notwendigerweise maßstabsgetreu gezeichnet.

Genaue Beschreibung der veranschaulichenden Beispielen

**[0023]** Die Herstellung und die Verwendung der Beispiele der vorliegenden Offenbarung werden nachstehend im Detail diskutiert. Es sollte jedoch verstanden werden, dass die vorliegende Offenbarung viele anwendbare erfindungsgemäße Konzepte bereitstellt, die in einer breiten Vielfalt spezifischer Gebiete Anwendung finden können. Die diskutierten besonderen Beispiele dienen lediglich zur Veranschaulichung bestimmter Art und Weise, um von der Offenbarung Nutzen zu machen, und sollen nicht den Umfang der Offenbarung beschränken.

[0024] Die Fig. 1A zeigt eine perspektivische Ansicht einer Package-Anordnung 100, die ein Package 110 aufweist, das mit einem weiteren Package 120 verbunden ist, und welches weiterhin mit einem Substrat 130 gemäß manchen Beispielen der Erfindung verbunden ist. Jedes Package, wie das Package 110 oder das Package 120, umfasst zumindest einen Halbleiterchip (nicht dargestellt). Der Halbleiterchip umfasst ein Substrat, wie es bei der Herstellung von integrierten Halbleiterschaltkreisen verwendet wird, wobei integrierte Schaltkreise in diesem oder auf diesem ausgebildet sein können. Das Halbleitersubstrat ist definiert als irgendeine Konstruktion, die ein Halbleitermaterial aufweist, einschließlich, jedoch nicht ausschließlich, massives Silizium, ein Halbleiter-Wafer, ein Silizium-auf-Nichtleiter(SOI)-Substrat, oder ein Silizium-Germanium-Substrat. Es können ebenso andere Halbleitermaterialien verwendet werden, einschließlich Gruppe-III-, Gruppe-IV- und Gruppe-V-Elemente. Das Substrat 130 kann weiterhin eine Vielzahl Isolationsteile (nicht dargestellt) aufweisen, wie Shallow-Trench-Isolation(STI)-Teile oder Local-

Oxidation-of-Silicon(LOCOS)-Teile. Die Isolationsteile können die unterschiedlichen mikroelektronischen Bauteile definieren und isolieren. Beispiele der unterschiedlichen mikroelektronischen Bauteile, die in dem Substrat 130 ausgebildet sein können, umfassen Transistoren (z.B. Metalloxidhalbleiter-Feldeffekttransistoren (MOSFET), komplementäre Metalloxidhalbleiter(CMOS)-Transistoren, Bipolartransistoren (BJT), Hochspannungstransistoren, Hochfrequenztransistoren, p-Kanal- und/oder n-Kanal-Feldeffekttransistoren (PFETs/NFETs), usw.); Widerstände; Dioden; Kondensatoren; Spulen; Sicherungen; und andere geeignete Elemente. Verschiedene Prozesse werden durchgeführt, um die verschiedenen mikroelektronischen Bauteile auszubilden, einschließlich Abscheidung, Ätzen, Implantation, Photolithographie, Tempern, und andere geeignete Prozesse. Die mikroelektronischen Bauteile werden miteinander verbunden, um das integrierte Schaltkreisbauteil auszubilden, wie ein Logikbauteil, ein Speicherbauteil (z.B. SRAM), ein RF-Bauteil, ein Input/ Output(I/O)-Bauteil, ein System-on-Chip(SoC)-Bauteil, Kombinationen dieser, und andere geeignete Arten von Bauteilen.

[0025] Das Substrat 130 kann aus einem Halbleiter-Wafer hergestellt sein, oder aus einem Abschnitt eines Wafers. Bei manchen Beispielen umfasst das Substrat 130 Silizium, Galliumarsenid, Silizium-auf-Nichtleiter ("SOI"), oder andere ähnliche Materialien. Bei manchen Beispielen umfasst das Substrat 130 ebenfalls passive Bauteile, wie Widerstände, Kondensatoren, Spulen und dergleichen, oder aktive Bauteile, wie Transistoren. Bei manchen Beispielen umfasst das Substrat 130 zusätzliche integrierte Schaltkreise. Das Substrat 130 kann weiterhin sich durch das Substrat erstreckende Durchkontaktierungen (through substrate vias (TSVs)) aufweisen, und es kann ein Interposer sein. Darüber hinaus kann das Substrat 130 aus anderen Materialien hergestellt sein. Beispielsweise ist das Substrat 130 bei manchen Beispielen eine vielschichtige Leiterplatte. Bei manchen Beispielen umfasst das Substrat 130 ebenfalls Bismaleimid-Triazin (BT)-Harz, FR-4 (ein Verbundmaterial, bestehend aus verwobenen Glasfasern mit einem Epoxidharzbindemittel, welches flammresistent ist), Keramik, Glas, Kunststoff, Isolierband, ein Film oder andere Auflagematerialien, welche die leitfähigen Blöcke oder Lötaugen, welche dazu benötigt werden, leitfähige Kontakte aufzunehmen, zu tragen.

[0026] Das Package 110 ist mit dem Package 120 über Anschlüsse 115 verbunden, und das Package 120 ist mit dem Substrat 130 über Anschlüsse 125 verbunden. Die Fig. 1B ist eine Querschnittsansicht eines Abschnitts des PoP-Package gemäß Fig. 1, entlang der Linie P-P gemäß einigen Beispielen. Die Fig. 1B zeigt Anschlüsse 115 und 125, welche nahe der Kante der Chip-Package-Anordnung 100 an-

geordnet sind. Nahe der Mitte des Package 120 sind bei manchen Beispielen Anschlüsse 125 angeordnet. Ein Anteil der Anschlüsse 115 ist in Öffnungen 116 des Package 120 ausgebildet. Die Öffnungen 116 werden durch Ätzen des gegossenen Materials des Package 120 ausgebildet. Daraus resultiert, dass die Anschlüsse 115 auch als Durchkontaktierungen durch gegossenes Material (TMVs) bezeichnet werden können. Bei manchen Beispielen sind die Öffnungen 116 mittels Laserbohrungen ausgebildet, wobei die Breite W₁ der Öffnungen 116 vergleichsweise groß ist. Beispielsweise liegt die Breite  $\mathbf{W}_1$  gemäß manchen Beispielen in einem Bereich zwischen ungefähr 300 µm bis ungefähr 600 µm. Bei manchen Beispielen beträgt der Abstand P<sub>1</sub> zwischen zwei aneinandergrenzenden Anschlüssen 115 zwischen ungefähr 400 µm und ungefähr 800 µm. Der vergleichsweise große Abstand begrenzt die Flexibilität und Komplexität der Konstruktion, welche für hochentwickelte Vorrichtungen benötigt werden. Darüber hinaus hinterlässt das Laserbohren der Öffnungen 116 in den oberen Abschnitten 117' vergleichsweise dünne Isolationsbereiche 117 zwischen den Anschlüssen 115, wodurch die Kurzschlussgefahr zwischen den Anschlüssen 115 erhöht wird. Es besteht daher ein Bedarf dafür, alternative Mechanismen für die Ausbildung der Anschlüsse 115 zwischen dem Package 110 und dem Package 120 zu finden.

[0027] Die Fig. 2A - Fig. 2G sind Querschnittsansichten einer Package-on-Package-Struktur bei verschiedenen Herstellungsstadien gemäß manchen Beispielen. Die Fig. 2A zeigt ein Substrat 200 mit Anschlussblöcken 210 für die Herstellung externer Verbindungen, gemäß manchen Beispielen. Das Substrat 200 kann aus einem Halbleiter-Wafer hergestellt sein, oder aus einem Teil eines Wafers. Bei manchen Beispielen umfasst das Substrat 200 Silizium, Galliumarsenid, Silizium-auf-Nichtleiter ("SOI") oder andere ähnliche Materialien. Bei manchen Beispielen umfasst das Substrat 200 ebenfalls passive Bauteile, wie Widerstände, Kondensatoren, Spulen und dergleichen, oder aktive Bauteile, wie Transistoren. Bei manchen Beispielen umfasst das Substrat 200 zusätzlich integrierte Schaltkreise. Die Substrate 200 können darüber hinaus Durchkontaktierungen durch das Substrat (TSVs) aufweisen und sie können ein Interposer sein. Darüber hinaus kann das Substrat 200 aus anderen Materialien hergestellt sein. Beispielsweise ist das Substrat 200 in manchen Beispielen eine vielschichtige Leiterplatte. Bei manchen Beispielen umfasst das Substrat 200 Bismaleimid-Triazin(BT)-Harz, FR-4, FR-5, welches dem FR-4 ähnelt, Keramik, Glas, Kunststoff, Bandmaterial, Filmmaterial oder andere Trägermaterialien, welche die leitfähigen Blöcke oder Lötaugen, die dazu benötigt werden, die leitfähigen Anschlusselemente zu empfangen, zu tragen. Die Kontaktblöcke 210 sind aus leitfähigem Material hergestellt und mit einem Verbinder (nicht dargestellt) in dem Substrat 200 verbunden.

[0028] Dann werden Metallkugeln 240 auf den Kontaktblöcken 210 befestigt und mit den Kontaktblöcken 210 verbunden, um eine befestigte Metallkugelstruktur 255 auszubilden, wie sie in Fig. 2B gemäß manchen Beispielen gezeigt ist. Der Befestigungsprozess kann das Anordnen der Metallkugeln 240 auf den Kontaktblöcken 210 und das Durchführen eines Reflow-Prozesses umfassen, um die Kontaktmetallkugeln 240 mit den Kontaktblöcken 210 zu verbinden. Die Fig. 3A ist eine Querschnittsansicht eines vergrößerten Bereichs 250 von Fig. 2B gemäß manchen Beispielen. Die Fig. 3A zeigt, dass der Bereich 250 das Substrat 210 und befestigte Metallkugelstrukturen 250 gemäß manchen Beispielen umfasst. Das Substrat 200 umfasst Verbinderstrukturen 205, welche die leitfähigen Blöcke 208 und die leitfähigen Blöcke 207 auf gegenüberliegenden Seiten mit dem Substrat 200 verbinden, wie es in Fig. 3A gemäß manchen Beispielen gezeigt ist.

[0029] Bei manchen Beispielen umfassen die Verbinderstrukturen 205, dass die Metallleitungen und Durchkontaktierungen aus Kupfer oder Kupferlegierungen ausgebildet sind. Bei manchen Beispielen sind die Verbinderstrukturen 205 mittels Zwischenschicht-Dielektrika (ILDs) und/oder Zwischenmetall-Dielektrika (IMDs) umgeben und isoliert, welche aus einem undotierten Siliziumglas, einem dotierten Film, einem Dielektrikum mit niedriger dielektrischer Konstante (niedriger k-Wert), oder Kombinationen dieser hergestellt sein können. Die leitfähigen Blöcke 208 sind Bestandteil der befestigten Kugelstrukturen 210 gemäß manchen Beispielen. Bei manchen Beispielen weisen die leitfähigen Blöcke 208 und 207 Aluminium, Kupfer, Silber, Gold, Nickel, Wolfram, Legierungen dieser und/oder mehrere Schichten dieser auf.

[0030] Ein Anteil jedes leitfähigen Blocks 208 ist mittels einer Passivierungsschicht 230 geschützt, wobei der verbleibende Abschnitt jedes leitfähigen Blocks 208 freigelegt ist. Ebenso sind die leitfähigen Blöcke 207 ebenfalls teilweise mittels einer Passivierungsschicht 231 geschützt. Die Passivierungsschichten 230 und 231 sind gemäß manchen Beispielen aus weichem (oder verformbarem) dielektrischen Material, wie Polymeren, hergestellt, um Verbindungsspannungen zu lindern. Bei manchen Beispielen sind eine oder mehrere Passivierungsschichten über den Verbinderstrukturen 205 und auf derselben Ebene wie die leitfähigen Blöcke 208, oder darüber, ausgebildet. Bei manchen Beispielen umfassen die zusätzlichen Passivierungsschichten Siliziumoxid, Siliziumnitrid, undotiertes Silikatglas (USG), Polyamid oder Kombinationen dieser.

[0031] Eine optionale Verbindungsschicht 245 ist gemäß manchen Beispielen über den leitfähigen Blöcken 208 ausgebildet. Die optionale Verbindungsschicht 245 könnte dabei helfen, die Metallkugeln 240

mit den leitfähigen Blöcken **208** zu verbinden. Die Metallkugeln **240** sind gemäß manchen Beispielen aus nicht lötfähigen Materialien hergestellt, wie Kupfer, Aluminium, Silber, Gold, Nickel, Wolfram, Legierungen dieser, und/oder mehreren Schichten dieser. Die Metallkugeln **240** sind aus einem oder mehreren nicht lötfähigen Materialien hergestellt, so dass sich diese nicht deformieren und mit benachbarten Metallkugeln **240** bei einem thermischen Prozess kurzschließen. Bei manchen Beispielen beträgt die (maximale) Breite **W2** der Metallkugeln **240** zwischen ungefähr 100 µm und ungefähr 200 µm. Bei manchen Beispielen beträgt der Abstand **P2** der Metallkugeln **240** zwischen ungefähr 300 µm.

[0032] Wie bereits erwähnt, könnte die Verbindungsschicht 245 dazu verwendet werden, die Verbindung zwischen den leitfähigen Blöcken 208 und den Metallkugeln 240 zu verbessern. Beispielsweise kann die Verbindungsschicht 245 aus Lot bestehen, welches dazu verwendet werden kann, Kupfer mit Kupfer zu verbinden, falls sowohl die leitfähigen Blöcke 208 als auch die Metallkugeln 240 aus Kupfer bestehen. Bei manchen Beispielen besteht die Verbindungsschicht 245 aus Lot oder einer Lotlegierung, wie Sn-Ag, Sn-Ag-Cu, Sn-Bi, Sn-Cu, usw. Bei manchen Beispielen besteht die Verbindungsschicht 245 aus einer Lotlegierung, umfassend Sn, Pb, Ag, Cu, Ni, Bismuth (Bi), oder Kombinationen dieser.

[0033] Bei manchen Beispielen umfasst die (optionale) Verbindungsschicht 245 zwei Teilschichten. Beispielsweise können die zwei Teilschichten eine Lot enthaltende Schicht über einer Schutzschicht, wie eine Schicht aus Ti und/oder Ni, aufweisen. Die Schutzschicht ist zwischen der Lot enthaltenden Schicht und den leitfähigen Blöcken 208 angeordnet. Die Schutzschicht kann die Oxidation der Kupfer enthaltenden Metallkugeln 240 verhindern und sie verbessert die Benetzung der Metallkugeln 240. Bei manchen Beispielen beträgt die Dicke der Verbindungsschicht 245 zwischen ungefähr 0,5 µm und ungefähr 10 µm.

[0034] Nachdem die Metallkugeln 240 auf der Verbindungsschicht 245 angeordnet wurden, wird ein Reflow-Prozess durchgeführt, um die Metallkugeln 240 mit den leitfähigen Blöcken 208 unter Zuhilfenahme der Verbindungsschicht 245 zu verbinden. Beispielsweise würde eine Verbindungsschicht 245, die aus Lot hergestellt ist, dabei helfen, die Kupfer enthaltenden Metallkugeln 240 und die leitfähigen Blöcke 208 miteinander zu verbinden, wenn die Metallkugeln 240 und die leitfähigen Blöcke 208 aus Kupfer oder Kupferlegierung bestehen. Bei manchen Beispielen beträgt die Reflow-Temperatur zwischen ungefähr 180 °C und ungefähr 240 °C. Nach dem Reflow-Prozess werden die Metallkugeln 240 mit den leitfähigen Blöcken 208 verbunden (oder auf diesen

befestigt), um eine befestigte Metallkugelstruktur 255 auszubilden. Bei zumindest einer Ausführungsform bilden die leitfähigen Blöcke 208, die Verbindungsschicht 245 und die Metallkugeln 204 die befestigte Metallkugelstruktur 255 gemäß manchen Beispielen. Falls die Metallkugeln 240 Kupfer und die Verbindungsschicht 245 Lot aufweist, kann eine Inter-Metall-Verbund(IMC)-Schicht 242 zwischen den Metallkugeln 240 und der Verbindungsschicht 245 ausgebildet sein. Wie bereits erwähnt, könnte die Lot enthaltende Verbindungsschicht 245 einen beständigen Film über dem Lot aufweisen, um die Ausbildung der IMC-Schicht 242 zu verhindern.

[0035] Die leitfähigen Blöcke 207 können gemäß manchen Beispielen mit einer Verbindungsschicht 247 bedeckt sein. Jede der leitfähigen Blöcke 207 und der begleitenden Verbindungsschicht 247 bilden eine Verbindungsstruktur 220, welche gemäß manchen Beispielen dazu verwendet wird, um mit einem externen Anschluss (nicht dargestellt) zu verbinden. Bei manchen Beispielen wird die Verbindungsschicht 247 nicht benötigt. Beispielsweise wird die Verbindungsschicht 247 für das Verbinden nicht benötigt, wenn die externen Anschlüsse (nicht dargestellt) aus Lot und die leitfähigen Blöcke 207 aus Kupfer bestehen. Bei manchen Beispielen besteht die Verbindungsschicht 247 aus demselben Material wie die Verbindungsschicht 245. Bei manchen Beispielen besteht die Verbindungsschicht 247 aus einem Material, das sich von dem der Verbindungsschicht 245 unterscheidet. Das Vorliegen und die Auswahl der Materialien für die Verbindungsschicht 247 hängen von dem Material der leitfähigen Blöcke 207 und der externen Anschlüsse (nicht dargestellt), welche mit den leitfähigen Blöcken 207 verbunden werden sollen, ab.

[0036] Die Fig. 3B zeigt die befestigte Metallkugelstruktur 255' gemäß manch anderer Ausführungsform. Die Metallkugeln 240' sind mit einem leitfähigen Block 208 verbunden und umfassen eine innere Metallkugel 240, und eine oder mehrere Beschichtungen, wie die Beschichtung  $\mathbf{240}_{\mathbf{C1}}$  und eine optionale Zwischenschicht 240<sub>C2</sub>, gemäß manchen Beispielen. Die inneren Metallkugeln 240, ähneln den Metallkugeln 240 und können aus verschiedenen der oben beschriebenen Materialien hergestellt sein. Bei manchen Beispielen beträgt die Breite  $\mathbf{W_3}$  der inneren Metallkugeln 240, zwischen ungefähr 100 µm und ungefähr 250 µm. Die Beschichtung(en) wird/werden dazu verwendet, um die Verbindung zwischen den Metallkugeln 240' und den leitfähigen Blöcken 208 zu verbessern. Bei manchen Beispielen ersetzt/ersetzen die Beschichtung(en) die Verbindungsschicht 245, welche in Fig. 3A gezeigt ist, gemäß manchen Beispielen. Beispielsweise bestehen die inneren Metallkugeln **240**<sub>1</sub> aus Kupfer oder einer Kupferverbindung, und die leitfähigen Blöcke 208 aus Kupfer, wobei eine Lot enthaltende Beschichtung 240<sub>C1</sub> dabei helfen

würde, die inneren Metallkugeln 240, mit den leitfähigen Blöcken 208 zu verbinden. Bei manchen Beispielen wäre die Herstellung der Beschichtung der inneren Metallkugeln 240, einfacher als die Ausbildung einer Verbindungsschicht 245, was das Abscheiden der Verbindungsschicht 245 und das Entfernen des Uberschusses der Verbindungsschicht 245 von den leitfähigen Blöcken 208 umfasst. Das Entfernen der überschüssigen Verbindungsschicht 245 könnte das Strukturieren der Verbindungsschicht und einen Ätzprozess, um überschüssige Verbindungsschicht 245 zu entfernen, umfassen. Bei manchen Beispielen besteht die Beschichtung 240<sub>C1</sub> aus Materialien, die den Materialien der Verbindungsschicht 245 ähneln. Bei manchen Beispielen beträgt die Dicke der Beschichtung 240<sub>C1</sub> zwischen ungefähr 0,5 µm und ungefähr 10 µm. Sogar mit der Beschichtung würden sich die Metallkugeln 240' während des Reflow-Prozesses wesentlich weniger als Lotkugeln deformieren. Daraus resultiert, dass Metallkugeln 240' weniger dazu tendieren, sich nach dem Reflow-Prozess kurzzuschließen. Die Breiten- und Abstandsbereiche der Metallkugeln 240' ähneln denen der Metallkugeln 240.

[0037] Bei manchen Beispielen wird eine Zwischenschicht 240<sub>C2</sub> zwischen den inneren Metallkugeln 240<sub>I</sub> und der Beschichtung 240<sub>C1</sub> ausgebildet. Gemäß manchen Beispielen ist die Zwischenschicht 240<sub>C2</sub> leitfähig und verhindert die Ausbildung eines Inter-Metall-Verbundes (IMC) zwischen den inneren Metallkugeln 240, und der Beschichtung 240c1 während und nach dem Reflow-Prozess für die Verbindung der Metallkugeln 240' mit den leitfähigen Blöcken 208. Beispielsweise würde eine Zwischenschicht 240<sub>C2</sub>, die aus einem Metall oder einer Legierung, die reaktionsträge in Bezug auf Kupfer und Lot bei Reflow-Bedingungen ist, die Ausbildung eines IMC zwischen den inneren Metallkugeln 240, und der Beschichtung 240c1 verhindern, falls die inneren Metallkugeln 240, Kupfer und die Beschichtung 240<sub>C1</sub> Lot umfasst. Bei manchen Beispielen umfasst die Zwischenschicht  $\mathbf{240}_{\mathbf{C2}}$  Ti und/oder Ni. Bei manchen Beispielen beträgt die Dicke der Zwischenschicht 240<sub>C2</sub> zwischen ungefähr 0,5 µm und ungefähr 10 µm.

[0038] Bei manchen Beispielen wird eine temporäre Schutzschicht 246' über den leitfähigen Blöcken 208 ausgebildet, wie es in Fig. 3B gezeigt ist. Die temporäre Schutzschicht 246' kann die Oxidation der leitfähigen Blöcke 208 während des Transportes verhindern. Beispielsweise ist die temporäre Schutzschicht 246' aus einem organischen Material hergestellt, welches bei Reflow-Temperaturen verdampft, um zu ermöglichen, dass die Metallkugeln 240' mit den leitfähigen Blöcken 208 in Kontakt treten. Bei manchen Beispielen besteht die Schutzschicht 246 aus einem Organic Solderability Preservative (OSP), welches

ein Polymer ist. Beispielsweise kann das OSP auf einem organischen Azol basieren.

[0039] Bei manchen Beispielen wird eine Schutzschicht 246 über den leitfähigen Blöcken 208 ausgebildet, wie es in Fig. 3C gezeigt ist. Die Schutzschicht 246 kann die Oxidation der leitfähigen Blöcke 208 während des Transportes verhindern. Beispielsweise kann die Schutzschicht 246 aus einem beständigen Metall, wie Ti, Ni, Au, Ag, einer Kombination dieser, oder einer Legierung dieser bestehen, wenn die leitfähigen Blöcke 208 Kupfer aufweisen. Bei manchen Beispielen beträgt die Dicke der temporären Schutzschicht 246' oder der Schutzschicht 246 zwischen ungefähr 0,5 μm und ungefähr 10 μm.

[0040] Bei manchen Beispielen ist die Oberfläche der Metallkugeln 240 oder 240' abgeflacht, um den Kontakt zwischen den Anschlüssen (nicht dargestellt), welche mit den Metallkugeln 240 oder 240' verbunden werden sollen, zu verbessern. Fig. 4 zeigt eine verbundene Metallkugelstruktur, nachdem eine Oberfläche der Metallkugel 240 abgeflacht wurde, gemäß manchen Beispielen. Die abgeflachte Oberfläche 248 verläuft gemäß manchen Beispielen, im Wesentlichen parallel zu der Oberfläche 201 des Substrats 200. Für die Abflachung der Oberfläche kann Gewicht über eine Platte, die über den Metallkugeln 240 angeordnet ist, beaufschlagt werden. Bei manchen Beispielen beträgt die Breite W4 des abgeflachten Bereichs zwischen ungefähr 20 µm und ungefähr 100 µm. Bei manchen Beispielen beträgt das Verhältnis der Breite W<sub>4</sub> und der Breite W<sub>2</sub> der Metallkugeln 240 zwischen ungefähr 20 % und ungefähr 80 %. Der Abflachprozess ist jedoch optional. Es könnte sein, dass dieser bei manchen Beispielen nicht benötigt wird.

[0041] Nachdem die Metallkugeln 240 oder 240' auf den leitfähigen Blöcken 208 verbunden (oder befestigt) und optional abgeflacht wurden, werden die Halbleiterchips 105 auf dem Substrat 210 angeordnet, wie es in Fig. 2C gemäß manchen Beispielen gezeigt ist. Jeder Halbleiterchip 105 wird zwischen Metallkugeln 240 angeordnet. Um die Beschreibung zu vereinfachen, wird ab jetzt lediglich von Metallkugeln 240 gesprochen. Nichtsdestotrotz ist die nachstehende Beschreibung auch auf Metallkugeln 240' anwendbar, wie sie oben ebenfalls beschrieben worden sind. Bei manchen Beispielen wird ein Reflow-Prozess angewendet, um die Anschlüsse (nicht dargestellt) auf den Halbleiterchips 105 mit den Kontaktblöcken (nicht dargestellt) auf dem Substrat 200 zu verbinden, um Verbindungsstrukturen 153 auszubilden.

[0042] Jeder Halbleiterchip 105 umfasst ein Substrat, wie es in der Herstellung von integrierten Halbleiterschaltkreisen verwendet wird, und integrierte Schaltkreise können darin und/oder darauf ausgebil-

det sein. Das Halbleitersubstrat ist derart definiert, dass es jede Konstruktion, welche Halbleitermaterialien aufweist, umfassen soll, einschließlich, jedoch nicht ausschließlich, massives Silizium, ein Halbleiter-Wafer, ein Silizium-auf-Nichtleiter(SOI)-Substrat, oder ein Silizium-Germanium-Substrat. Andere Halbleitermaterialien, einschließlich Gruppe-III-, Gruppe-IV-, und Gruppe-V-Elemente, können ebenfalls verwendet werden.

[0043] Beispiele für die verschiedenen mikroelektronischen Elemente, die in dem Halbleiterchip 105 ausgebildet sein können, umfassen Transistoren (z.B. Metalloxidhalbleiter-Feldeffekttransistoren (MOSFET), komplementäre Metalloxidhalbleiter(CMOS)-Transistoren, Bipolartransistoren (BJT), Hochspannungstransistoren, Hochfrequenztransistoren, p-Kanal- und/oder n-Kanal-Feldeffekttransistoren (PFETs/NFETs), usw.); Widerstände, Dioden; Kondensatoren; Spulen; Sicherungen; und andere geeignete Bauteile. Unterschiedliche Prozesse werden durchgeführt, um die verschiedenen mikroelektronischen Bauteile auszubilden, einschließlich Abscheidung, Ätzen, Implantation, Photolithographie, Tempern, und andere geeignete Prozesse. Die mikroelektronischen Bauteile sind miteinander verbunden, um den integrierten Schaltkreis auszubilden, wie ein logisches Bauteil, ein Speicherbauteil (z.B. SRAM), ein RF-Bauteil, ein Eingabe/Ausgabe(I/O) -Bauteil, ein System-auf-Chip(SoC)-Bauteil, Kombinationen dieser, und andere geeignete Arten von Bauteilen.

[0044] Bei manchen Beispielen füllt die Unterfüllung 154 den Freiraum zwischen den Halbleiterchips 105 und dem Substrat 200, wie es in Fig. 5 gezeigt ist. Die Unterfüllung 154 stellt eine Auflage für die Halbleiterchips 105 bereit und verhindert ein Brechen der Lötverbindungen (nicht dargestellt) auf den Verbindungsstrukturen 153, welche die Halbleiterchips 105 und die leitfähigen Elemente (Anschlüsse) in dem Substrat 200 elektrisch miteinander verbinden. Das Ausbilden der Unterfüllung 154, nachdem die Halbleiterchips 105 mit dem Substrat 200 verbunden worden sind, ist optional. Bei manchen Beispielen ist die Unterfüllung 154 nicht ausgebildet. Die Unterfüllung 154 kann beispielsweise aus Epoxidharz (aminartiges, phenolartiges, anhydratartiges, usw.), aus Siliziumfüllern, Vernetzungsmitteln, Zusätzen und/oder Härtern bestehen (oder diese aufweisen).

[0045] Danach werden die Packages 110 oberhalb von dem Substrat 200 angeordnet und auf Metall-kugeln 240 befestigt, wie es in Fig. 2D gemäß einigen Beispielen gezeigt ist. Jedes Package 110 umfasst zwei Halbleiterchips 112 und 113, wobei der Chip 113 gemäß einigen Beispielen, über dem Chip 112 angeordnet ist. Das Package 110 könnte jedoch einen Halbleiterchip oder mehr als zwei Halbleiterchips aufweisen. Bei manchen Beispielen befindet

sich eine Klebeschicht (nicht dargestellt) zwischen den Chips 112 und 113. Die Halbleiterchips 112 und 113 können verschiedene mikroelektrische Bauteile aufweisen, wie sie zuvor für Halbleiterchips 105 beschrieben worden sind. Beispiele für diese verschiedenen mikroelektronischen Elemente wurden zuvor beschrieben. Der Halbleiterchip 112 ist mit dem Substrat 115 verbunden. Das Substrat 115 kann verschiedene der zuvor für das Substrat des Halbleiterchips 105 beschriebene Materialien und/oder Komponenten aufweisen. Der Halbleiterchip 112 ist mit leitfähigen Bauteilen (nicht dargestellt) in dem Substrat 115 über Verbindungsdrähte 114 gemäß einigen Beispielen elektrisch verbunden. Auf ähnliche Weise ist der Halbleiterchip 113 mit den leitfähigen Bauteilen in dem Substrat 115 über Verbindungsdrähte 116 elektrisch verbunden. Das Package 110 umfasst ein Gussmaterial 111, welches die Halbleiterchips 112 und 113 und ebenso die Verbindungsdrähte 114 und 116 überdeckt.

[0046] Jedes Package 110 umfasst eine Anzahl Anschlüsse 117, welche den Halbleiterchip 105 umgeben, gemäß einigen Beispielen. Die Anschlüsse 117 bestehen aus einem leitfähigen Material, wie Lot, einer Lotverbindung, usw. Die Anschlüsse 117 sind auf leitfähigen Strukturen (nicht dargestellt) auf der Oberfläche des Substrats 115 ausgebildet, um sich mit den Bauteilen in dem Substrat 115 elektrisch zu verbinden. Nachdem das Package 110 über dem Substrat 200 angeordnet ist, wobei Anschlüsse 117 des Package 110 mit Metallkugeln 240 in Kontakt stehen, wird gemäß einigen Beispielen, ein Reflow-Prozess ausgeführt, um die Anschlüsse 117 mit den Metallkugeln 240 zu verbinden. Nachdem die Anschlüsse 117 mit den Metallkugeln 240 verbunden worden sind, um Verbindungsstrukturen 118 auszubilden, werden die Packages 110 als auf dem Substrat 200 "befestigt" betrachtet. Aufgrund der nicht lötfähigen Metallkugeln 240 kann die Höhe der Verbindungsstrukturen 118 gleichmäßiger gesteuert werden. Bei manchen Beispielen beträgt die Höhe  $\mathbf{H_1}$  zwischen einer Oberseite 201 des Substrats 200 und der Unterseite 101 des Packages 110 (oder des Substrats 115) zwischen 100 µm und ungefähr 250 µm.

[0047] Nachdem die Packages 110 auf dem Substrat 200 befestigt worden sind, wird eine gegossene Unterfüllung (MUF) 260 auf das Substrat 200 gegeben, um den Freiraum zwischen den Packages 110 und zwischen den Packages 110 und dem Substrat, wie es in Fig. 2E gemäß einigen Beispielen gezeigt ist, auszufüllen. Bei manchen Beispielen weist der MUF 260 Füller auf. Der MUF 260 stützt die Packages 110 ab und verhindert ein Aufbrechen der Lötverbindungen auf den Verbindungsstrukturen 118 und zwischen den Metallkugeln 240 und den leitfähigen Blöcken 208. Weiterhin könnte die MUF 260 ebenfalls ein Verbiegen (eine Deformation) der Package-on-Package-Strukturen auf dem Substrat 200

aufgrund von Unterschieden in den thermischen Expansionskoeffizienten (CTE) der Materialien auf dem Substrat 200 nach der Temperaturwechselbeanspruchung verhindern. Bei manchen Beispielen besteht die MUF 260 aus Epoxidharz (aminartiges, phenolartiges, anhydratartiges, usw.), aus Siliziumfüllern, Vernetzungsmitteln, Zusätzen und/oder Härtermaterialien. Falls unterhalb der Halbleiterchips 105 keine Unterfüllung 154 angeordnet ist, füllt die MUF 260 ebenfalls den Freiraum zwischen den Halbleiterchips 105 und dem Substrat 200, um die Verbindungsstrukturen 153 zu schützen. Die Verarbeitungskosten könnten dadurch reduziert werden, dass die MUF 260 verwendet wird, um den Freiraum zwischen den Packages 110 und dem Substrat 200 und zugleich den Freiraum zwischen den Halbleiterchips 105 und dem Substrat 200 aufzufüllen.

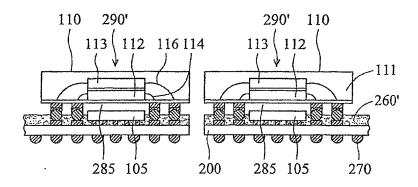

[0048] Nach dem MUF-Ausbildungsprozess werden die Anschlüsse 270 mit den leitfähigen Blöcken 207 (nicht dargestellt) auf der anderen Seite (gegenüberliegend von den Packages 110) des Substrats 200 verbunden, wie es in Fig. 2F gemäß manchen Beispielen gezeigt ist. Die Anschlüsse 270 bestehen aus leitfähigen Materialien. Diese könnten Lot, Lotlegierung, Kupfer, Kupferlegierung, Gold, oder Goldlegierung, usw. sein. Wie bereits erwähnt, könnte eine Verbindungsschicht 247 dazu vorgesehen sein, die leitfähigen Blöcke 207 zu bedecken. Die Anschlüsse 270 sind mit den leitfähigen Blöcken 207 mittels eines Reflow-Prozesses verbunden. Nachdem die Anschlüsse 270 an der den Packages 110 gegenüberliegenden Seite des Substrats verbunden worden sind. wird das Substrat 200 mit der angebundenen Vielzahl Packages 110 und Halbleiterchips 105 in einzelne Packages vereinzelt (oder zersägt), von denen jedes jeweils ein Package 110 und einen Halbleiterchip 105 aufweist. Die Fig. 2G zeigt das Substrat 200, nachdem es in einzelne Packages 290 vereinzelt worden ist, gemäß manchen Beispielen. Jedes einzelne Package 290 ist eine Package-on-Package-Struktur und weist ein Package 110 und einen Halbleiterchip 105 auf, gemäß manchen Beispielen.

[0049] Die zuvor in den Fig. 2A - Fig. 2G und Fig. 3-5 beschriebenen Beispiele für die Ausbildung des Package 290 der Package-on-Package(PoP)-Struktur umfasst MUF 260. Bei manchen alternativen Beispielen wird eine freiliegende Chipgussunterfüllung (eMUF) 260' auf dem Substrat bei freiliegenden oberen Abschnitten des Halbleiterchips 105 und der Metallkugeln 240 ausgebildet, wie es in Fig. 6A gemäß manchen Beispielen gezeigt ist. Nachdem die Halbleiterchips 105 auf dem Substrat 200 angeordnet und mit diesem verbunden worden sind, wie es in Fig. 2C gezeigt ist, wird die eMUF 260' über dem Substrat 200 ausgebildet. Indem die freiliegende eMUF 260' ausgebildet wird, entsteht ein Luftspalt 285 zwischen jedem Package 110 und dem Halbleiterchip 105. Der Luftspalt 285 ermöglicht, dass Chips,

wie die Chips 112 und 113, auf dem Package 110 im Wesentlichen thermisch isoliert von dem Halbleiterchip 105 sind. Daraus resultiert, dass von den Chips 112 und 113, welche sich in der Nähe des Halbleiterchips 105 befinden, erzeugte Wärme mit geringerer Wahrscheinlichkeit an den Halbleiterchip 105, und umgekehrt, geleitet wird. Die eMUF 260' kann immer noch die Lötverbindungen zwischen den Metallkugeln 240 und den leitfähigen Blöcken 208 schützen. Die eMUF 260' kann ebenso dabei helfen, die Verwindung des Substrats 200 vor der Vereinzelung und der ausgebildeten Packages nach der Vereinzelung aufgrund von Unterschieden der CTEs zu verringern.

[0050] Nachdem die eMUF 260`, wie zuvor beschrieben, auf dem Substrat 200 ausgebildet worden ist, werden die Packages 110 mit dem Substrat 200, wie es in Fig. 6B gemäß einigen Beispielen gezeigt ist, verbunden. Das Verbinden der Packages 110 mit dem Substrat 200 wurde zuvor beschrieben. Anschlüsse 270 werden dann mit dem Substrat auf ähnliche Weise, wie mit Bezug auf Fig. 2F beschrieben, verbunden, gemäß manchen Beispielen. Die Fig. 6C zeigt Anschlüsse 270, die mit dem Substrat 200 gemäß manchen Beispielen verbunden sind. Das Substrat 200 mit den Packages 110 und den Halbleiterchips 105 wird dann in einzelne Packages 290', wie es in Fig. 6D gemäß manchen Beispielen gezeigt ist, vereinzelt. Die Fig. 2A - Fig. 2C und Fig. 6A -Fig. 6D zeigen Querschnittsansichten von Package-Strukturen bei sequentiellem Prozessablauf der Ausbildung einer Package-on-Package-Struktur, gemäß manchen Beispielen.

[0051] Die beschriebenen Beispiele für Ausbildungsmechanismen für eine Package-on-Package (PoP)-Struktur umfassen das Verbinden mit Anschlüssen von nicht lötfähigen Metallkugeln an eine Package-Struktur. Die nicht lötfähigen Metallkugeln können eine Lotbeschichtung aufweisen. Die Anschlüsse mit den nicht lötfähigen Metallkugeln können im Wesentlichen die Form der Anschlüsse beibehalten und die Höhe der Verbindungsstrukturen zwischen oberen und unteren Packages steuern. Die Anschlüsse mit den nicht lötfähigen Metallkugeln tendieren ebenso weniger wahrscheinlich zur Ausbildung von Überbrückungen zwischen den Anschlüssen und Unterbrechungen (oder Kaltlötungen) der verbundenen Anschlüsse. Daraus resultiert, dass der Abstand der Anschlüsse mit nicht lötfähigen Metallkugeln gering gehalten werden kann.

[0052] Bei manchen Beispielen wird ein Verfahren zur Ausbildung eines Halbleiterbauteil-Packages bereitgestellt. Das Verfahren umfasst das Bereitstellen eines Substrats mit einem Kontaktblock, und das Verbinden einer Metallkugel mit dem Kontaktblock, um eine erste Verbindungsstruktur auszubilden. Das Verfahren umfasst ebenso das Verbinden

eines Halbleiterchips mit dem Substrat, und der Halbleiterchip ist neben der Verbindungsstruktur angeordnet. Das Verfahren umfasst weiterhin das Verbinden eines Chip-Package mit einer Oberfläche des Substrats, welche mit dem Halbleiterchip verbunden ist, und das Verbinden eines Chip-Packages bildet eine zweite Verbindungsstruktur zwischen einem Anschluss auf dem Chip-Package und der Metallkugel, die mit dem Substrat verbunden ist. Darüber hinaus umfasst das Verfahren das Ausbilden einer gegossenen Unterfüllung (MUF) auf dem Substrat, und das Vereinzeln des Halbleiterbauteils, welches das Chip-Package und den Halbleiterchip aufweist, welcher mit dem Substrat verbunden ist, in einem verbleibenden Abschnitt des Substrats.

[0053] Bei manchen anderen Beispielen wird ein Verfahren für das Ausbilden eines Halbleiterbauteil-Packages bereitgestellt. Das Verfahren umfasst das Verbinden eines Halbleiterchips mit einem Substrat, und das Verbinden des Halbleiterchips mit dem Substrat bildet eine erste Verbindungsstruktur, die eine nicht lötfähige Metallkugel umfasst. Das Verfahren umfasst ebenso das Verbinden eines Chip-Package mit einer Oberfläche des Substrats, die mit dem Halbleiterchip verbunden ist, und das Verbinden eines Chip-Package bildet eine zweite Verbindungsstruktur zwischen einem Anschluss auf dem Chip-Package und der Metallkugel, die mit dem Substrat verbunden ist. Das Verfahren umfasst weiterhin das Ausbilden einer gegossenen Unterfüllung (MUF) auf dem Substrat, und das Vereinzeln des Halbleiterbauteils, einschließlich des Chip-Package und des Halbleiterchips, der mit dem Substrat verbunden ist, über einem verbleibenden Abschnitt des Substrats.

[0054] Bei noch anderen Beispielen wird ein Halbleiter-Package bereitgestellt. Das Halbleiter-Package umfasst ein Substrat und einen ersten Halbleiterchip, der mit dem Substrat verbunden ist. Das Halbleiter-Package umfasst ein Chip-Package, das mit dem Substrat verbunden ist, und der erste Halbleiterchip ist zwischen dem Chip-Package und dem Substrat angeordnet. Das Chip-Package ist mit dem Substrat über eine Verbindungsstruktur, die eine nicht lötfähige Metallkugel aufweist, verbunden, und das Chip-Package umfasst zumindest einen zweiten Halbleiterchip. Das Halbleiter-Package umfasst weiterhin eine gegossene Unterfüllung auf dem Substrat.

#### Patentansprüche

1. Verfahren für die Ausbildung eines Halbleiterbauteil-Package, das aufweist:

Bereitstellen eines Substrats (200) mit einem Kontaktblock (210);

Verbinden einer Metallkugel (240) mit dem Kontaktblock (210), um eine erste Verbindungsstruktur (255) auszubilden: Verbinden eines Halbleiterchips (105) mit dem Substrat (200), wobei der Halbleiterchip (105) neben der Verbindungsstruktur (255) angeordnet ist;

Verbinden eines Chip-Package (110) mit einer Oberfläche des Substrats (200), die mit dem Halbleiterchip (105) verbunden ist, wobei das Verbinden eines Chip-Package (110) eine zweite Verbindungsstruktur (101) zwischen einem Anschluss auf dem Chip-Package (110) und der Metallkugel (240), die mit dem Substrat (200) verbunden ist, ausbildet;

Ausbilden einer gegossenen Unterfüllung (260) auf dem Substrat (200); und

Vereinzeln des Halbleiterbauteils, einschließlich des Chip-Package (110) und des Halbleiterchips (105), das mit dem Substrat (200) über einen verbleibenden Abschnitt des Substrats (200) verbunden ist, wobei die Metallkugel (240) einen nicht lothaltigen Metallkern (240 $_{\rm l}$ ) aufweist, der mit einer leitfähigen Zwischenschicht (240 $_{\rm c2}$ ) und einer Lotschicht (240 $_{\rm c1}$ ) beschichtet ist, wobei die leitfähige Zwischenschicht (240 $_{\rm c2}$ ) zwischen dem Metallkern (240 $_{\rm l}$ ) und der Lotschicht (240 $_{\rm c1}$ ) angeordnet ist, wobei eine Breite W $_{\rm 3}$  des Metallkerns (2401) zwischen 100 µm und 250 µm beträgt und die Dicke der leitfähigen Zwischenschicht (240 $_{\rm c2}$ ) und der Lotschicht (240 $_{\rm c1}$ ) jeweils zwischen 0, 5 µm und 10 µm beträgt, und

das Verfahren weiterhin aufweist:

vor dem Verbinden des Chip-Packages (110), Abflachen eines oberen Abschnitts der Metallkugel (240) durch Gewichtbeaufschlagung der Metallkugel (240), wobei ein Verhältnis zwischen einer Breite des abgeflachten oberen Abschnitts der Metallkugel (240) und einer maximalen Breite der Metallkugel (240) in einem Bereich zwischen 20 % und 80 % liegt,

wobei die Breite des abgeflachten oberen Abschnitts der Metallkugel (240) so gewählt wird, dass ein oberer Abschnitt des Metallkerns (240<sub>1</sub>) abgeflacht wird.

- 2. Verfahren nach Anspruch 1, bei dem der Kontaktblock (210) eine temporäre Schutzschicht (246') aufweist, wobei die temporäre Schutzschicht (246') vor oder während der Ausbildung der ersten Verbindungsstruktur (255) entfernt wird.

- 3. Verfahren nach Anspruch 2, wobei die temporäre Schutzschicht (246') ein organisches Lötschutzmittel aufweist.

- 4. Verfahren nach einem der vorangegangenen Ansprüche, bei dem die gegossene Unterfüllung (260) zwischen dem Halbleiterchip (105) und dem Substrat (200) ausgebildet wird, wobei die ausgebildete gegossene Unterfüllung (260) eine Oberseite des Halbleiterchips (105) und eine obere Position der Metallkugel (240) nicht bedeckt.

- 5. Verfahren nach einem der vorangegangenen Ansprüche, bei dem der Kontaktblock (210) einen leitfähigen Block (208) auf dem Substrat (200) und eine Verbindungsschicht (245) aufweist, wobei der leitfä-

hige Block (208) mit einem Verbinder in dem Substrat (200) verbunden ist.

6. Halbleiter-Package, das aufweist: ein Substrat (200);

einen ersten Halbleiterchip (105), der mit dem Substrat (200) verbunden ist;

ein Chip-Package (110), das mit dem Substrat (200) verbunden ist, wobei der erste Halbleiterchip (105) zwischen dem Chip-Package (110) und dem Substrat (200) angeordnet ist, und wobei das Chip-Package (110) über eine Verbindungsstruktur (255), die eine Metallkugel (240) aufweist, verbunden ist, und wobei das Chip-Package (110) zumindest einen zweiten Halbleiterchip (111) aufweist; und

Halbleiterchip (111) aufweist; und eine gegossene Unterfüllung (260) auf dem Substrat (200), wobei die Metallkugel (240) einen nicht lothaltigen Metallkern (240<sub>I</sub>) aufweist, der mit einer leitfähigen Zwischenschicht (240c2) und einer Lotschicht (240<sub>c1</sub>) beschichtet ist, wobei die leitfähige Zwischenschicht (240<sub>c2</sub>) zwischen dem Metallkern (240<sub>i</sub>) und der Lotschicht (240c1) angeordnet ist, wobei eine Breite W<sub>3</sub> des Metallkerns (240<sub>I</sub>) zwischen 100 µm und 250 µm beträgt und die Dicke der leitfähigen Zwischenschicht (240c2) und der Lotschicht (240c1) jeweils zwischen 0,5 µm und 10 µm beträgt, und eine Oberfläche (248) der Metallkugel (240) abgeflacht ist, wobei ein Verhältnis zwischen einer Breite des abgeflachten oberen Abschnitts der Metallkugel (240) und einer maximalen Breite der Metallkugel (240) in einem Bereich zwischen 20 % und 80 % liegt, wobei die Breite des abgeflachten oberen Abschnitts der Metallkugel (240) so gewählt ist, dass ein oberer Abschnitt des Metallkerns (240<sub>1</sub>) abgeflacht ist.

- 7. Halbleiter-Package nach Anspruch 6, bei dem der Metallkern (240<sub>I</sub>) Kupfer, Aluminium, Silber, Gold, Nickel, Wolfram, Legierungen dieser oder Kombinationen dieser aufweist.

- 8. Halbleiter-Package nach einem der Ansprüche 6 oder 7, bei dem das Halbleiterbauteil-Package eine weitere Metallkugel aufweist, die neben der Metallkugel (240) angeordnet ist, wobei ein Abstand der Metallkugel (240) zu der weiteren Metallkugel zwischen 150 μm und 300 μm liegt.

Es folgen 7 Seiten Zeichnungen

# Anhängende Zeichnungen

Fig. 1A

Fig. 6A

Fig. 6B

Fig. 6C

Fig. 6D