# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(11) 공개번호 10-2022-0017499(43) 공개일자 2022년02월11일

(51) 국제특허분류(Int. Cl.)

G11C 7/06 (2021.01) G11C 11/16 (2006.01) G11C 7/02 (2006.01) G11C 7/04 (2006.01) G11C 7/08 (2006.01) G11C 7/14 (2006.01)

(52) CPC특허분류

*G11C* 7/065 (2013.01) *G11C* 11/1655 (2013.01)

(21) 출원번호 10-2022-7000714

(22) 출원일자(국제) **2020년05월01일** 심사청구일자 **2022년01월07일**

(85) 번역문제출일자 **2022년01월07일**

(86) 국제출원번호 PCT/US2020/030937

(87) 국제공개번호 **WO 2020/251699** 국제공개일자 **2020년12월17일**

(30) 우선권주장

16/438,090 2019년06월11일 미국(US)

(71) 출원인

어플라이드 머티어리얼스, 인코포레이티드

미국 95054 캘리포니아 산타 클라라 바우어스 애 브뉴 3050

(72) 발명자

구오, 프랭크 쩬-웬

미국 95054 캘리포니아 산타 클라라 바우어스 애 브뉴 3050

아야가리-상가말리, 부바네슈와리

미국 95054 캘리포니아 산타 클라라 바우어스 애 브뉴 3050

(뒷면에 계속)

(74) 대리인

특허법인 남앤남

전체 청구항 수 : 총 15 항

#### (54) 발명의 명칭 잡음 및 변동에 대한 내성을 갖는 협-범위 감지 증폭기

# (57) 요 약

메모리 회로는, 판독 동작에 의해 선택될 때, 기준 신호를 제공하는 하나 이상의 기준 열들 및 데이터 신호를 제공하는 데이터 열을 갖는 메모리 어레이를 포함한다. 메모리 회로는 또한, 기준 신호를 논리 1 신호 레벨과 논리 0 신호 레벨 사이에 있도록 조정하는 제2 회로와 함께, 기준 신호 및 데이터 신호로부터 공통 신호 성분을 제거하는 제1 회로를 포함한다. 메모리 회로는 또한, 공통 신호 성분이 제거된 후의 데이터 신호와 함께, 공통 신호 성분이 제거된 후 그리고 조정된 후의 기준 신호를 사용하여, 데이터 신호가 논리 1을 나타내는지 또는 논리 0을 나타내는지를 결정하는 감지 증폭기를 포함한다.

#### 대 표 도 - 도2

## (52) CPC특허분류

*G11C 11/1673* (2013.01)

*G11C 7/02* (2013.01)

*G11C 7/04* (2013.01)

*G11C 7/08* (2013.01)

*G11C 7/14* (2013.01)

(72) 발명자

## 사치드, 앙가다 비.

미국 95054 캘리포니아 산타 클라라 바우어스 애브 뉴 3050

# 알렉산더, 블레시

미국 95054 캘리포니아 산타 클라라 바우어스 애브 뉴 3050

## 명 세 서

### 청구범위

#### 청구항 1

메모리 회로로서,

메모리 어레이 - 상기 메모리 어레이는,

기준 신호(reference signal)를 제공하는 하나 이상의 기준 열(reference column)들;

복수의 데이터 열들을 포함하고,

상기 복수의 데이터 열들은 판독 동작에 의해 선택될 때 데이터 신호를 제공하는 데이터 열을 포함함 -;

상기 기준 신호 및 상기 데이터 신호로부터 공통 신호 성분을 제거하는 제1 회로;

논리 1 신호 레벨과 논리 0 신호 레벨 사이에 있도록 상기 기준 신호를 조정하는 제2 회로; 및

감지 증폭기를 포함하며,

상기 감지 증폭기는,

상기 공통 신호 성분이 상기 제1 회로에 의해 제거된 후 그리고 상기 제2 회로에 의해 조정된 후의 상기 기준 신호; 및

상기 공통 신호 성분이 상기 제1 회로에 의해 제거된 후의 상기 데이터 신호를 사용하여,

상기 데이터 신호가 논리 1을 나타내는지 또는 논리 0을 나타내는지를 결정하는,

메모리 회로.

#### 청구항 2

제1 항에 있어서,

상기 감지 증폭기는 래치 증폭기를 포함하는,

메모리 회로.

## 청구항 3

제1 항에 있어서,

상기 메모리 어레이는 MRAM(Magnetic RAM) 어레이를 포함하는,

메모리 회로.

#### 청구항 4

제1 항에 있어서,

상기 하나 이상의 기준 열들은 상기 메모리 어레이의 대략적인 중심에 위치된 기준 열을 포함하는,

메모리 회로.

## 청구항 5

제1 항에 있어서,

상기 하나 이상의 기준 열들은 상기 기준 신호를 제공하는 제1 기준 열, 및 상기 제1 기준 열에 대한 백업으로 서 작용하는 제2 기준 열을 포함하는,

메모리 회로.

### 청구항 6

제1 항에 있어서,

상기 메모리 어레이의 복수의 데이터 열들은 저장된 논리 레벨들을 출력하도록 구성된 복수의 비트 셀들을 포함하고, 그리고 상기 하나 이상의 기준 열들은 상기 논리 0 신호 레벨을 출력하도록 구성된 복수의 비트 셀들을 포함하는,

메모리 회로.

#### 청구항 7

제1 항에 있어서,

상기 기준 신호는 상기 기준 신호를 상기 논리 1 신호 레벨과 상기 논리 0 신호 레벨 사이의 대략적인 중심 신호 레벨로 감소시킴으로써 조정되는.

메모리 회로.

#### 청구항 8

제1 항에 있어서,

상기 공통 신호 성분은, 상기 기준 신호 및 상기 데이터 신호에 신호를 주입함으로써 상기 기준 신호 및 상기 데이터 신호로부터 제거되며, 상기 기준 신호 및 상기 데이터 신호에 주입되는 상기 신호의 양은 캐스코딩 트랜지스터 쌍(cascoding transistor pair)들에 의해 제어되는,

메모리 회로.

#### 청구항 9

메모리 회로로부터 데이터를 판독하는 방법으로서,

메모리 어레이에 위치된 하나 이상의 기준 열들로부터 기준 신호를 수신하는 단계;

상기 메모리 어레이의 복수의 데이터 열들 내의 데이터 열로부터 데이터 신호를 수신하는 단계 — 상기 데이터 신호는 판독 동작에 의해 선택될 때, 상기 데이터 열에 의해 제공됨 —;

상기 기준 신호 및 상기 데이터 신호로부터 공통 신호 성분을 제거하는 단계;

논리 1 신호 레벨과 논리 0 신호 레벨 사이에 있도록 상기 기준 신호를 조정하는 단계;

상기 공통 신호 성분이 제거된 후 그리고 상기 논리 1 신호 레벨과 상기 논리 0 신호 레벨 사이에 있도록 조정된 후에, 상기 기준 신호를 감지 증폭기에 제공하는 단계; 및

상기 공통 신호 성분이 제거된 후에, 상기 데이터 신호를 상기 감지 증폭기에 제공하는 단계를 포함하는,

메모리 회로로부터 데이터를 판독하는 방법.

#### 청구항 10

제9 항에 있어서,

상기 하나 이상의 기준 열들은 복수의 기준 열들을 포함하고, 그리고 상기 기준 신호는 상기 복수의 기준 열들 의 서브세트로부터의 전류들을 평균화함으로써 생성되는,

메모리 회로로부터 데이터를 판독하는 방법.

#### 청구항 11

제9 항에 있어서.

상기 하나 이상의 기준 열들은 상기 기준 신호를 제공하는 제1 기준 열, 및 상기 제1 기준 열에 대한 백업으로 서 작용하는 제2 기준 열을 포함하는. 메모리 회로로부터 데이터를 판독하는 방법.

#### 청구항 12

제9 항에 있어서,

상기 메모리 어레이의 복수의 데이터 열들은 저장된 논리 레벨들을 출력하도록 구성된 복수의 비트 셀들을 포함하고, 그리고 상기 하나 이상의 기준 열들은 논리 0을 출력하도록 구성된 복수의 비트 셀들을 포함하는,

메모리 회로로부터 데이터를 판독하는 방법.

#### 청구항 13

제9 항에 있어서,

상기 기준 신호는 상기 기준 신호를 상기 논리 1 신호 레벨과 상기 논리 0 신호 레벨 사이의 대략적인 중심 신호 레벨로 감소시킴으로써 조정되는,

메모리 회로로부터 데이터를 판독하는 방법.

#### 청구항 14

제13 항에 있어서,

상기 기준 신호는 신호를 상기 기준 신호에 주입함으로써 감소되며, 상기 기준 신호에 주입되는 상기 신호의 양은 캐스코딩 트랜지스터 쌍에 의해 제어되는,

메모리 회로로부터 데이터를 판독하는 방법.

#### 청구항 15

제9 항에 있어서,

상기 공통 신호 성분은 상기 기준 신호 및 상기 데이터 신호에 신호를 주입함으로써 상기 기준 신호 및 상기 데이터 신호로부터 제거되며, 상기 기준 신호 및 상기 데이터 신호에 주입되는 상기 신호의 양은 캐스코딩 트랜지스터 쌍들에 의해 제어되는,

메모리 회로로부터 데이터를 판독하는 방법.

## 발명의 설명

## 기술분야

[0001] 본 출원은, 2019년 6월 11일자로 출원된 미국 특허 출원 제16/438,090호를 우선권으로 주장하며, 이로써 이 미국 특허 출원의 내용들은 모든 목적들을 위해 그 전체가 인용에 의해 포함된다.

## 배경기술

[0002] 현대의 컴퓨터 메모리들은 메모리로부터 데이터를 판독하는 데 사용되는 회로부의 일부로서 감지 증폭기들을 사용한다. 감지 증폭기의 역할은 메모리 셀에 저장된 단일 비트의 데이터(1 또는 0)를 나타내는 비트 라인으로부터의 저전력 신호들을 감지하는 것이다. 그런 다음, 감지 증폭기는, 작은 전압 스윙들을, 메모리와 인터페이싱하는 디지털 논리에 의해 적절하게 인식 및 해석될 수 있는 논리 레벨들로 증폭시킨다. 일반적으로, 메모리 어레이의 열 멀티플렉서(column multiplexor)를 통해 메모리 셀들의 열들에 대해 감지 증폭기가 포함된다. 고성능 메모리들은 전압-차이 증폭의 레벨을 최대화하면서 낮은 전력 소비로 감지 지연을 최소화하는 감지 증폭기들을 필요로 한다.

#### 발명의 내용

[0003] 일부 실시예들에서, 메모리 회로는 기준 신호를 제공하는 하나 이상의 기준 열들 및 복수의 데이터 열들을 갖는 메모리 어레이를 포함할 수 있다. 복수의 데이터 열들은 판독 동작에 의해 선택될 때 데이터 신호를 제공하는 데이터 열을 포함할 수 있다. 메모리 회로는 또한, 기준 신호 및 데이터 신호로부터 공통 신호 성분을 제거하

는 제1 회로; 논리 1 신호 레벨과 논리 0 신호 레벨 사이에 있도록 기준 신호를 조정하는 제2 회로; 및 데이터 신호가 논리 1을 나타내는지 또는 논리 0을 나타내는지를 결정하는 감지 증폭기를 포함할 수 있다. 감지 증폭기는 공통 신호 성분이 제1 회로에 의해 제거된 후 그리고 제2 회로에 의해 조정된 후의 기준 신호를 사용할 수 있다. 감지 증폭기는 또한, 공통 신호 성분이 제1 회로에 의해 제거된 후의 데이터 신호를 사용할 수 있다.

- [0004] 일부 실시예들에서, 메모리 회로로부터 데이터를 판독하는 방법은 메모리 어레이에 위치된 하나 이상의 기준 열들로부터 기준 신호를 수신하는 단계, 및 메모리 어레이의 복수의 데이터 열들 내의 데이터 열로부터 데이터 신호를 수신하는 단계를 포함할 수 있다. 데이터 신호는 판독 동작에 의해 선택될 때 데이터 열에 의해 제공될수 있다. 방법은 또한, 기준 신호 및 데이터 신호로부터 공통 신호 성분을 제거하는 단계를 포함할 수 있다. 방법은 추가적으로, 논리 1 신호 레벨과 논리 0 신호 레벨 사이에 있도록 기준 신호를 조정하는 단계를 포함할수 있다. 방법은, 공통 신호 성분이 제거된 후 그리고 논리 1 신호 레벨과 논리 0 신호 레벨 사이에 있도록 조정된 후에, 기준 신호를 감지 증폭기에 제공하는 단계를 더 포함할수 있다. 방법은 또한, 공통 신호 성분이 제거된 후에, 데이터 신호를 감지 증폭기에 제공하는 단계를 포함할수 있다.

- [0005] 임의의 실시예들에서, 다음의 특징들 중 임의의 특징은 임의의 조합으로 그리고 제한 없이 포함되거나 구현될수 있다. 감지 증폭기는 래치 증폭기일 수 있다. 메모리 어레이는 MRAM(Magnetic RAM) 어레이를 포함할 수 있다. 하나 이상의 기준 열들은 메모리 어레이의 대략적인 중심에 위치된 기준 열을 포함할 수 있다. 하나 이상의 기준 열들은 복수의 기준 열들을 포함할 수 있고, 기준 신호는 복수의 기준 열들의 서브세트로부터의 전류들을 평균화함으로써 생성될 수 있다. 하나 이상의 기준 열들은 기준 신호를 제공하는 제1 기준 열, 및 제1 기준열에 대한 백업으로서 작용하는 제2 기준 열을 포함할 수 있다. 메모리 어레이의 복수의 데이터 열들은 저장된는리 레벨들을 출력하도록 구성된 복수의 비트 셀들을 포함할 수 있고, 하나 이상의 기준 열들은 논리 0 신호레벨을 출력하도록 구성된 복수의 비트 셀들을 포함할 수 있다. 기준 신호는 기준 신호를 논리 1 신호 레벨과는리 0 신호 레벨 사이의 대략적인 중심 신호 레벨로 감소시킴으로써 조정될 수 있다. 기준 신호는 신호를 기준 신호에 주입함으로써 감소될 수 있으며, 여기서, 기준 신호에 주입되는 신호의 양은 캐스코딩 트랜지스터 쌍(cascoding transistor pair)에 의해 제어될 수 있다. 공통 신호 성분은 기준 신호 및 데이터 신호에 주입되는 신호의 양은 캐스코딩 트랜지스터 쌍들에 의해 제어될 수 있다.

## 도면의 간단한 설명

[0006]

다양한 실시예들의 성질 및 장점들의 추가의 이해는 도면들 및 본 명세서의 나머지 부분들을 참조하여 실현될수 있으며, 여러 도면들에 걸쳐 유사한 컴포넌트들을 지칭하기 위해 유사한 참조 번호들이 사용된다. 일부 경우들에서, 서브-라벨은 다수의 유사한 컴포넌트들 중 하나를 나타내기 위한 참조 번호와 연관된다. 기존의 서브-라벨에 대한 명시 없이 참조 번호가 참조될 때, 이는 모든 그러한 다수의 유사한 컴포넌트들을 지칭하는 것으로 의도된다.

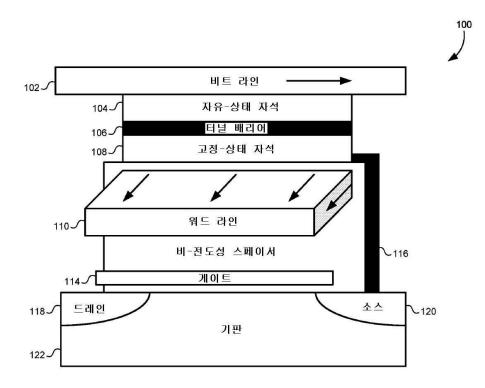

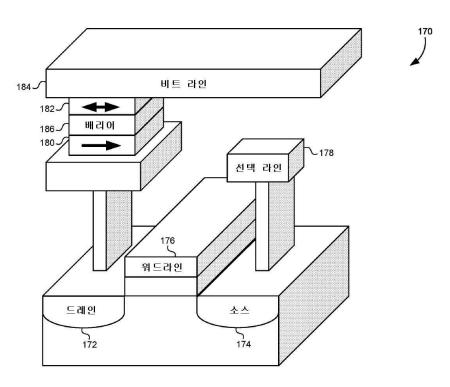

- 도 1a는 일부 실시예들에 따른 고전적인 MRAM 셀의 도면을 예시한다.

- 도 1b는 일부 실시예들에 따른, MRAM 셀에 대한 현대적인 설계를 예시한다.

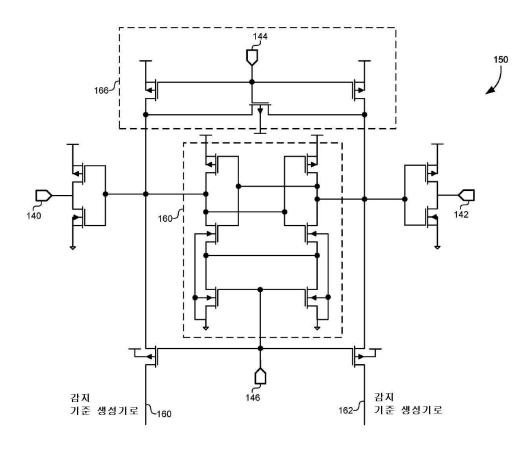

- 도 1c는 일부 실시예들에 따른 감지 증폭기의 개략도를 예시한다.

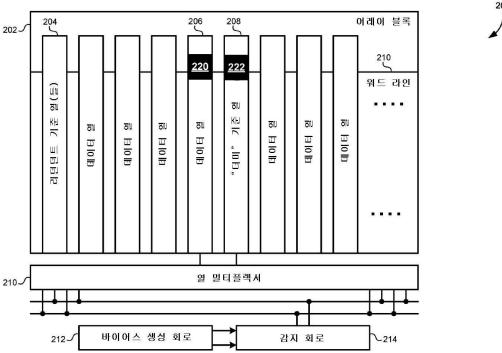

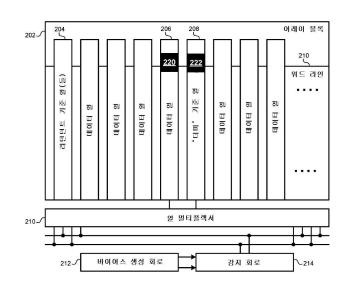

- 도 2는 일부 실시예들에 따른 메모리 아키텍처의 도면을 예시한다.

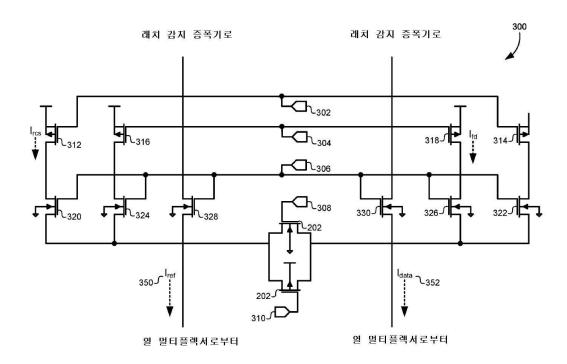

- 도 3은 일부 실시예들에 따른, 감지 증폭기에 제공되는 기준 전류 및 데이터 전류를 조정하는 감지 회로의 부분을 예시한다.

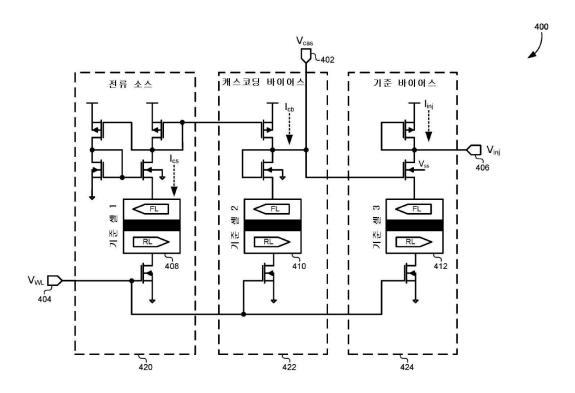

- 도 4는 일부 실시예들에 따른 바이어스-생성 회로를 예시한다.

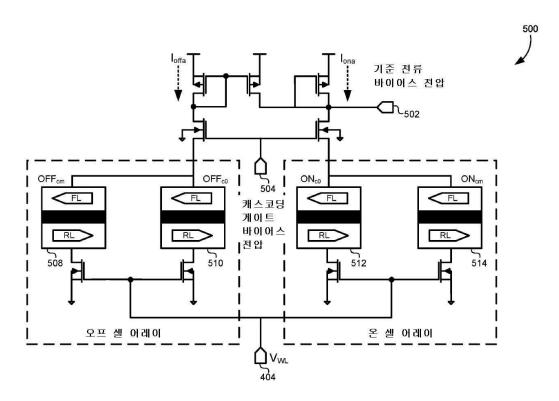

- 도 5는 일부 실시예들에 따른, 센터링 전류를 위해 사용되는 추가적인 기준 바이어스들을 생성하기 위한 회로들을 예시한다.

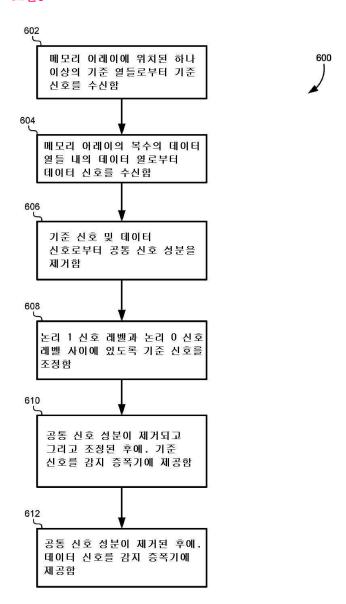

- 도 6은 일부 실시예들에 따른, 메모리 회로로부터 데이터를 판독하기 위한 방법의 플로차트를 예시한다.

### 발명을 실시하기 위한 구체적인 내용

[0007] 잡음 및 프로세스 변동들에 대한 내성을 갖는 협-범위 감지 증폭기에 대한 실시예들이 본원에서 설명된다. 저항성 메모리 셀들은 감지 증폭기에 의해 측정되는 온-저항과 오프-저항 사이의 비(ratio)들이 매우 작다. 게다

가, 프로세스 변동들은 감지 증폭기에 의해 사용되는 기준 전류들이 메모리 어레이로부터 수신된 데이터 신호들과 독립적으로 드리프트하도록 야기할 수 있다. 본원에서 설명되는 실시예들에서, 데이터 신호들에서 또한 발생하는 프로세스, 전압 및/또는, 온도 변동들을 추적하는 기준 신호들을 제공하기 위해 "더미" 기준 열들이 메모리 어레이에 배치될 수 있다. 기준 신호 및 데이터 신호 둘 모두는, 기준 신호 및 데이터 신호로부터 공통신호 성분을 제거하고 온-상태 저항과 오프-상태 저항 사이의 비를 증가시키기 위해, 감지 증폭기에 전달되기전에 사전프로세싱될 수 있다. 기준 신호는 또한, 온 상태 및 오프 상태에 대한 신호 레벨들 사이에 센터링될수 있다.

- [0008] 플래시 메모리, DRAM(dynamic RAM), SRAM(static RAM) 등과 같은 전통적인 RAM(random-access memory) 설계는 지난 20년 동안 컴퓨터 메모리 시장을 지배해 왔다. 그러나, 저항성 메모리 기술들은 특정 애플리케이션들에서 양호하게 수행될 수 있는 새로운 실행가능한 대안을 나타낸다. 저항성 랜덤-액세스 메모리(ReRAM 또는 RRAM)는 유전체 솔리드-스테이트 재료와 같은 재료에 걸친 저항을 변화시킴으로써 동작하는 일 유형의 비-휘발성 컴퓨터 메모리를 나타낸다. MRAM(magnetoresistive random-access memory)으로 알려진 특정 유형의 저항성 메모리 기술은 회로 저항에 영향을 미치는 자기 도메인들에 데이터를 저장한다. MRAM이 결국 컴퓨터 메모리에서 경쟁 기술들을 능가할 수 있다는 것이 오랫동안 생각되어 왔다. SRAM 및 DRAM과 같이, MRAM은 고속으로 판독할 수 있을 뿐만 아니라 고속으로 기록할 수 있는 대칭적 메모리이다. MRAM은 또한 비-휘발성이어서, 메모리 셀로부터 전력이 제거될 때 콘텐츠가 손실되지 않는다. 그러나, 플래시 RAM, SRAM, DRAM, 및 다른 비-자기 메모리들은 여전히, MRAM이 컴퓨터 메모리에서 널리 사용되는 것을 방해하는 실질적인 장점들을 갖는다. 본원에서 설명되는 실시예들은 현재의 MRAM 설계들에 존재하는 기술적 난제들 중 일부를 극복한다.

- [0009] 도 1a는 일부 실시예들에 따른 고전적인 MRAM 셀(100)의 도면을 예시한다. MRAM 기술은 단일 비트의 정보를 저장하기 위해 자석들의 쌍의 상대적인 극성을 활용한다. 2개의 자석들이 이들의 극성들이 정렬된 상태로 직렬로 배치될 때, 이러한 2개의 자석들을 통해 흐르는 전류의 저항은 비교적 낮을 것이다. 예컨대, 하나의 자석의 S 극이 다른 자석의 N극에 직렬-연결되도록 2개의 자석들을 직렬로 배치하는 것은 비교적 낮은 제1 저항을 생성할수 있다. 반대로, 하나의 자석의 S극이 다른 자석의 S극에 직렬-연결되도록 2개의 자석들을 직렬로 배치하는 것은 제1 저항에 비해 비교적 높은 제2 저항을 생성할수 있다. 자석들의 쌍에서 하나의 자석의 극성을 변화시 킴으로써 회로에서 저항을 변화시키는 능력은 MRAM 셀 기술에 대한 기초를 제공한다. 요컨대, 저-저항 자기 회로는 논리 0을 나타낼수 있고, 고-저항 자기 회로는 논리 1을 나타낼수 있다.

- [0010] MRAM 셀(100)은, MRAM 셀(100)의 저항을 제어하고 그에 따라 상이한 논리 상태들을 나타내기 위해 고정-상태 자석(108) 및 자유-상태 자석(104)을 포함할 수 있다. 고정-상태 자석(108)은 MRAM 셀(100)의 동작 동안 변하지 않는 자기 극성을 가질 수 있다. 따라서, 고정-상태 자석(108)의 전자들은 변하지 않는 단일 방향(예컨대, 북쪽에서 남쪽으로 볼 때 시계 방향)으로 스핀(spin)할 수 있다. 다른 한편으로, 자유-상태 자석(104)의 전자들은 상이한 논리 레벨들을 나타내도록 변할 수 있다.

- [0011] MRAM 셀(100)의 일부 실시예들은 자유-상태 자석(104)에서 전자들의 스핀 방향을 플립(flip)하기 위해 전류들을 사용할 수 있다. 이러한 전류들은 비트 라인(102) 및 워드 라인(110)을 통해 제공될 수 있다. 자유-상태 자석(104) 및 고정-상태 자석(108)은 터널 배리어(106)에 의해 분리될 수 있고, 자석들 둘 모두는 비트 라인(102)과 워드 라인(110) 사이에 배치될 수 있다. 도 1에 묘사된 바와 같이, 전류가 비트 라인(102)에서는 좌측으로부터 우측으로 그리고 워드 라인(110) 상에서는 지면 밖으로 흐르게 함으로써, 자유-상태 자석(104)의 전자들의 스핀이 시계 방향으로 회전하도록 야기될 수 있다. 이 분극은 논리 1 값을 나타낼 수 있다. 반대로, 전류가 비트라인(102)에서는 우측으로부터 좌측으로 그리고 워드 라인(110) 상에서는 지면 내로 흐르도록 야기되면, 자유-상태 자석(114)의 전자들의 스핀은 반시계 방향으로 회전하도록 야기될 수 있다. 이 분극은 논리 0 값을 나타낼 수 있다. 비트라인(102) 및/또는 워드 라인(110)에서 전류가 턴 오프될 때, 자유 상태 자석(104)의 전자들의 스핀은 유지되며, 이는 자유-상태 자석(104)의 극성을 변화시키기 위해 후속 전류들이 비트라인(102) 및 위드라인(110)에 인가될 때까지 MRAM 셀(100)의 "메모리" 기능을 제공한다.

- [0012] MRAM 셀(100)에 의해 저장된 논리 값을 판독하는 것은, 고정-상태 자석(108), 터널 배리어(106), 및 자유-상태 자석(104)을 통해 전류를 흐르게 함으로써 수행될 수 있다. 이 판독 전류는 MRAM 셀(100)의 최하부에 있는 기 판(122)의 드레인(118) 및 소스(120)에 의해 형성된 트랜지스터를 턴 온시킴으로써 인가될 수 있다. 트랜지스터를 위한 게이트(114)는 판독 워드 라인에 의해 형성될 수 있다. 혼동을 피하기 위해, 일부 구현들은 워드 라인(110)을 "기록 워드 라인"으로 그리고 게이트(114)를 "판독 워드 라인"으로 지칭할 수 있다. 전압(예컨대, 1.8V)이 게이트(114)에 인가될 때, 전류는 드레인(118)으로부터 기판(122)을 통해 트랜지스터의 소스(120)로 흐른다. 소스(120)를 빠져 나간 후에, 전류는 전도체(116)를 통해 고정-상태 자석(108) 내로, 터널 배리어(106)

를 통해, 자유-상태 자석(104)을 통해, 그리고 마지막으로 비트 라인(102)을 통해 계속 흐를 수 있다. 자석들 (104, 108)을 통한 전류 및/또는 전압 강하가 측정되어, 자유-상태 자석(104) 및 고정-상태 자석(108)을 통해 흐를 때 상대 저항이 결정될 수 있다. 전류가 제1 (예컨대, 비교적 더 낮은) 전류 레벨로 측정될 때, MRAM 셀(100)의 상태는 논리 0 값을 저장하는 것으로 해석될 수 있다. 전류가 제2 (예컨대, 비교적 더 높은) 전류 레벨로 측정될 때, MRAM 셀(100)의 상태는 논리 1 값을 저장하는 것으로 해석될 수 있다.

- [0013] MRAM 기술은 특정 애플리케이션들에서의 MRAM의 사용을 방해할 수 있는 다수의 고유한 난제들을 보인다. 예컨 대, 하나의 셀에서의 자석 분극들이 이웃하는 셀들에서의 자석 분극들에 영향을 미치지 않도록, 개별적인 MRAM 셀들 사이에서 어느 정도의 분리 또는 격리가 유지될 필요가 있을 수 있다. 추가적으로, 큰 외부 자기 소스들이 또한, 내부 MRAM 셀 상태들에 간섭할 수 있다. 그러나, 새로운 저항성 메모리 기술들에서의 주요 난제들 중하나는, 전형적으로 메모리 셀들의 열들을 동반하는 감지 증폭기 회로부를 수반한다.

- [0014] MRAM 셀(100)의 상태를 판독하기 위해 게이트(114)에 전압이 인가될 때, 결과적인 전류는 비트 라인(102)으로부터 감지 증폭기 내로 흐른다. 그런 다음, 감지 증폭기는 결과적인 전류와 기준 전류 사이의 차이를 측정하여, MRAM 셀(100)이 고-저항 상태에 있는지 또는 저-저항 상태에 있는지를 결정한다. 그러나, 저항성 메모리 셀들의 논리 0 상태와 논리 1 상태 사이의 저항의 차이는 매우 작을 수 있으며, 이는 메모리 셀의 온-상태와 오프-상태 사이의 매우 작은 저항 비로 이어진다. 전기 신호들이 이동하는 CMOS 회로부에서의 프로세스 변동들은 상태들 사이의 저항 윈도우에 매우 가까울 수 있고, 따라서 프로세스 변동들은 논리 0 상태와 논리 1 상태 사이의 저항 차이를 검출하기 위한 매우 작은 마진들을 침식(erode)시킬 수 있다. 그러한 작은 저항 비들의 경우, 고속으로 논리 상태들 사이를 구별할 수 있는 감지 증폭기의 감지 회로들은 본원에서 설명되는 실시예들에 의해 해결되는 기술적 난제를 나타낸다. 구체적으로, 이러한 실시예들은 CMOS 회로부의 프로세스 변동들 및 잡음 둘모두에 대한 높은 내성을 갖는 매우 작은 전류 비들을 감지하기 위해 감지 증폭기를 동반할 수 있는 회로부를 제시한다.

- [0015] 도 1b는 일부 실시예들에 따른, MRAM 셀(170)에 대한 현대적인 설계를 예시한다. 이 설계는 자기 충들 중 하나에서 전자들의 스핀을 플립하기 위해 MTJ(magnetic tunnel junction) 및 스핀-분극 전류(spin-polarized current)를 사용한다. 워드 라인(176)은 드레인(172) 및 소스(175)를 갖는 트랜지스터의 게이트 위로이어진다. 워드 라인(176)은 이 트랜지스터를 활성화시켜 MRAM 셀(170)의 콘텐츠에 액세스할 수 있다. 위에서 설명된 바와 같이, MRAM 셀(170)은 고정-상태 자석(180) 및 자유-상태 자석(182)을 포함할 수 있다.

- [0016] MRAM 셀(170)의 메모리 상태를 변경하기 위해, 자유-상태 자석(182)의 전자들의 스핀을 플립하기 위하여 분극된 전류가 인가될 수 있다. 전자들은 전자에 고유한 소량의 각운동량(angular momentum)을 설명하는 스핀 특성을 갖는다. 분극된 전류는, 전자들이 일 방향 또는 다른 방향으로 우세한 스핀 배향을 갖는 경우의 전류이다. 이 분극된 전류는 자유-상태 자석(182)의 전자들이 유사한 스핀 배향을 채택하도록 야기할 수 있다. 결과적으로, 이는 자유-상태 자석의 배향이 플립되도록 야기할 수 있다.

- [0017] 도 1a의 MRAM 셀(100)과 같이, 도 1b의 MRAM 셀(170)은 고정-상태 자석(180)과 자유-상태 자석(182) 사이에 배리어 산화물 층(186)을 포함한다. 터널 자기저항은 MTJ에서 발생하는 자기저항 효과이다. 배리어 산화물(186)은, 전자들이 고정-상태 자석(180)과 자유-상태 자석(182) 사이를 터널링할 수 있을 정도로 충분히 얇을 수있다. 따라서, 스핀-분극된 전류가 생성되어 고정-상태 자석(108)을 통과할 수 있다. MTJ는 전자 스핀의 각운 동량이 MTJ를 통해 자유-상태 자석(182) 내로 전달될 수 있게 하고, 이로써 그의 전자 스핀들을 변화시킨다. 이 프로세스는 저-저항 상태와 고-저항 상태 사이의 전기 저항을 변화시킨다.

- [0018] 도 1c는 일부 실시예들에 따른 감지 중폭기(150)의 개략도를 예시한다. 이 감지 중폭기(150)는 기준 전류 입력 (160) 및 데이터 전류 입력(162) 둘 모두를 포함한다. 일부 실시예들은 커넥터(146)에서 감지 증폭기에 대한 인에이블 입력을 포함할 수 있다. 인에이블 입력은 감지 증폭기에 전력을 공급하고 그리고/또는 감지 증폭기를 기준 전류 입력(160) 및 데이터 전류 입력(162)으로부터 분리하여, 빠른 감지-증폭기 응답을 제공할 수 있다. 감지 증폭기(150)는 기준 전류 입력(160)과 데이터 전류 입력(162) 사이의 작은 차이들을 검출하는 차동 증폭기 (164)로서 작용하는 6개의 트랜지스터들을 포함한다. 입력(144)은, 감지 회로의 양측들을 연결된 전력 공급부에 의해 제공되는 동일한 전위로 당기는 경향이 있는 3개의 PMOS 트랜지스터들로 구성된 감지 등화 회로(166)를 제어하는 데 사용될 수 있다. 이는 감지 증폭기(150)가 래치 감지 증폭기로서 작용할 수 있게 하였다. 2개의 출력들(140, 142)은 개개의 부스트 인버터들을 통과한 후의 감지 증폭기(150)의 반전 및 비-반전 출력들을 나타 낸다.

- [0019] 도 2는 일부 실시예들에 따른 메모리 아키텍처(200)의 도면을 예시한다. 메모리 아키텍처(200)는 하나 이상의

메모리 어레이들(202)을 포함할 수 있다. 각각의 메모리 어레이(202)는 복수의 데이터 열들(206)을 포함할 수 있고, 복수의 데이터 열들(206) 각각은 복수의 데이터 비트들을 포함할 수 있다. 복수의 데이터 열들(206) 내의 데이터 비트들은 워드 라인(210) 및 비트 라인(미도시)에 의해 개별적으로 어드레싱될 수 있다. 대부분의 종래의 메모리 어레이들에서와 같이, 메모리 어레이(202)로부터의 출력은 감지 증폭기로 전달되기 전에 열 멀티 플렉서(210)를 통과할 수 있다.

- [0020] 이 메모리 아키텍처(200)는 감지 증폭기의 감지 능력을 개선하는 다수의 상이한 방식들에 있어서 종래의 메모리 아키텍처들과 상이하다. 첫 번째로, 논리 레벨 1(예컨대, 고-저항 상태)과 논리 레벨 0(예컨대, 저-저항 상태) 사이의 전류 비는 데이터 전류 라인 및 기준 전류 라인에서 공통 전류 성분들을 필터링함으로써 부스팅될 수 있다. 두 번째로, 바이어스 생성 회로(212) 및 감지 회로(214)는 감지 증폭기에 프로세싱 변동들 및 메모리-판독 교란(disturbance)들에 대한 내성을 제공할 수 있다. 세 번째로, 메모리 어레이 블록(202)은 감지 증폭기에 대한 기준 전류를 생성하는 데 사용될 수 있는 하나 이상의 "더미" 기준 열들을 포함할 수 있다. 이는 기준 전류가, 복수의 데이터 열들(206)에서 발견될 수 있는 변동들에 매우 근접하게 될 프로세스, 전압, 및/또는 온도 (PVT) 변동들을 추적할 수 있게 한다. 메모리 아키텍처(200)의 이러한 특징들 각각은 아래에서 더 상세히 설명될 것이다.

- [0021] "더미" 또는 "기준" 어레이 열들은, 정규(regular) 테이터 열들(206)과 동일한 프로세스 및 타이밍 변동들을 겪는 기준 전류를 제공하기 위해 메모리 어레이(202)에 배치될 수 있다. 예컨대, 기준 열들(204)이 테이터 열들 (206)과 동일한 실리콘 기판 상에 그리고 동일한 제작 프로세스를 사용하여 제조될 수 있기 때문에, 제조 프로세스에 의해 야기되는 PVT 변동들은 테이터 열들(206) 및 기준 열들(208) 둘 모두에서 실질적으로 동일할 수 있다. 예컨대, PVT 변동들로 인해 데이터 열들(206)로부터의 전류가 목표 값보다 약간 더 높아지게 되면, 기준 열들(208)로부터 비롯되는 대응하는 기준 전류는 유사하게 목표 값보다 약간 더 높을 것이다. 메모리 어레이 블록(202)의 온도가 증가/감소하고 이로써 데이터 열들(206)의 내부 저항들 및/또는 전류들에 영향을 미치는 경우, 기준 열들(208)로부터의 기준 전류는 동일한 방식으로 영향을 받을 것인데, 왜냐하면, 그 회로부가 동일한 온도 변동을 겪기 때문이다. 기준 열들(208)를 메모리 어레이 블록(202)에 배치함으로써, 기준 열들(208)로부터의 기준 신호의 변동들은 데이터 열들(206)로부터의 데이터 신호에서 발생하는 임의의 변동들을 추적할 수 있다

- [0022] 일부 실시예들에서, 적어도 하나의 기준 열(208)이 사용될 수 있다. 기준 열(208)은 메모리 어레이 블록(202)의 대략적인 중심에 배치될 수 있다. 메모리 어레이 블록의 크기가 증가함에 따라, 추가적인 기준 열들(208)이 메모리 어레이 블록(202)에 추가될 수 있다. 열 멀티플렉서(210)는, 판독되고 있는 데이터 열(206)에 물리적으로 가장 가까운, 기준 열들(208)중 하나로부터 기준 전류를 선택할 수 있다. 이는 기준 신호 및 데이터 신호에 의해 횡단되는 트레이스 길이들의 차이를 최소화하기 위해 행해질 수 있다. 일부 실시예들은 메모리 어레이 블록(202)을 상이한 섹터들로 분할할 수 있고, 각각의 섹터는 그 섹터의 데이터 열들(206)의 중간에 그 자신의 대응하는 기준 열(208)을 가질 수 있다.

- [0023] 일부 실시예들은 리던던트 기준 열들(204)을 포함할 수 있다. 리던던트 기준 열들(204)은 (1차) 기준 열(208) 이 실패하는 경우에 백업들로서 사용될 수 있다. 대안적으로 또는 추가적으로, 리던던트 기준 열들(204)은 기준 전류를 결정하기 위한 추가적인 데이터 포인트들을 제공할 수 있다. 예컨대, 복수의 기준 열들(예컨대, 기준 열들(208) 및 리던던트 기준 열들(204))로부터의 기준 전류들은 판독 동작을 위한 기준 전류를 생성하기 위해 함께 평균화되거나 또는 다른 방식으로 조합될 수 있다.

- [0024] 기준 열들(208) 각각은 데이터 열들(206)에서 발견되는 비트 셀들(222)과 유사한 복수의 비트 셀들(220)을 포함할 수 있다. 일부 실시예들은 기준 열들(208) 내의 비트 셀들(220)이 데이터 열들(206) 내의 비트 셀들(222)과 완전히 똑같이 논리 0 값 또는 논리 1 값으로 프로그래밍될 수 있게 할 수 있다. 일부 실시예들은 논리 0 상태로 설정되도록 기준 열들(208)의 비트 셀들(220)을 프로그래밍할 수 있다. 전류 레벨들 및 프로세스 특징들로인해, 논리 0 상태는 논리 1 상태보다 더 안정적일 수 있다. MRAM 셀 내의 자석들의 극성으로인해, 논리 1 상태는 판독 동작 동안 더 쉽게 교란된다. 비교적으로, 논리 0 상태는 더 높은 전류 및 더 낮은 저항을 가지며, 따라서 판독 동작 동안 교란들에 덜 민감하다.

- [0025] 일부 환경들에서, 정규 데이터 열들(206)로서 기능하지 않는 특정 "더미" 기준 열들(208)이 어레이 블록(202)에 구축될 수 있다. 따라서, 기준 열들(208)은 메모리 아키텍처(200)의 외부 인터페이스에서 표준 판독/기록 동작들을 사용하여 어드레싱되거나 판독될 수 없다. 대신에, 이러한 기준 열들(208)은 기준 전류를 감지 회로(214)에 제공하기 위해 내부 동작들에 의해서만 판독될 수 있다. 대안적으로 또는 추가적으로, 일부 실시예들은,

외부적으로 어드레싱될 수 있고 그리고/또는 그로부터 판독되거나 그에 기록될 수 있는 기준 열들(208)을 사용할 수 있다. 이는 기준 열들(208)의 값들이 디폴트 논리 0 신호 레벨 이외의 값들로 동적으로 설정될 수 있게한다. 일부 실시예들은 또한, 정규 데이터 열들(206)을 기준 열들로서 사용할 수 있다. 예컨대, 데이터 신호는 특정 데이터 열(208)로부터 판독될 수 있고, 기준 신호는 기준 열로서 사용될 수 있는 인근의 데이터 열로부터 판독될 수 있다. 이러한 실시예들은 "더미" 기준 열들이 정상(normal) 데이터 열들 이상으로 어레이 블록(202)에 추가될 것을 요구하지 않는다.

- [0026] 도 3은 일부 실시예들에 따른, 감지 증폭기(150)에 제공되는 기준 신호(350) 및 데이터 신호(352)를 조정하는 감지 회로(214)의 부분을 예시한다. 감지 회로(214)의 이 부분은 기준-생성 회로(300)로 지칭될 수 있다. 기준-생성 회로(300)는 3개의 캐스코딩 트랜지스터 회로 구조들에 기반할 수 있다. 제1 캐스코딩 세트의 트랜지스터 스터들(328, 330)은 최종 데이터 신호(352) 및 기준 신호(350)를 감지 증폭기(150)에 공급하기 위한 트랜지스터 쌍으로서 작용할 수 있다.

- [0027] 제2 세트의 캐스코딩 트랜지스터들(324, 326)은 데이터 열 및 기준 열로부터 비롯되는 기준 신호(350) 및 데이터 신호(352) 둘 모두로부터 공통 신호 성분을 필터링 또는 제거하는 데 사용될 수 있다. 필터링 신호는 2개의 PMOS 트랜지스터들(316, 318)에 의해 제공되는 조절된 전류 소스들로부터 생성될 수 있다. 예컨대, 트랜지스터 (316)를 통해 생성되고 트랜지스터(324)에 의해 수정된 전류는 감지 증폭기(150)에 전송된 기준 신호(350)와 함께 주입되는 필터링 전류를 생성할 수 있다. 유사하게, 트랜지스터(318)를 통해 생성되고 트랜지스터(326)에 의해 수정된 전류는 감지 증폭기(150)에 전송된 데이터 신호(352)와 함께 주입되는 필터링 전류를 생성할 수 있다. 이러한 트랜지스터들은, 주입 전류가 데이터 전류(352) 및 기준 전류(350) 둘 모두에 대해 동일하도록 매칭될 수 있다. 트랜지스터들(328, 330)은 데이터 신호(352) 및 기준 신호(350) 라인들로의 이 필터링 전류 주입을 감지 증폭기(150)에 인터페이싱하기 위해 사용될 수 있다. 트랜지스터들(316, 318)이 조절된 전류 소스를 제공하기 때문에, 기준 신호(350) 및 데이터 신호(352) 둘 모두로부터 동일한 전류가 주입(즉, "감산")될 수 있다

- [0028] 아래에서 설명되는 이러한 트랜지스터들(316, 324, 318, 326) 및 연관된 바이어싱 회로들은 총괄적으로, 기준 신호 및 데이터 신호로부터 공통 신호 성분을 제거하는 "제1 회로"로 지칭될 수 있다. 이 예가 기준 전류 및 데이터 전류를 사용하지만, 다른 실시예들은 그렇게 제한되지 않는다. 일부 실시예들은 대신에, 전압, 저항, 전력, 인덕턴스, 및/또는 논리 레벨을 나타내는 데 사용될 수 있는 임의의 다른 전기적 특징을 측정할 수 있다. 따라서, 신호들은 일반적으로 "기준 신호" 및 "데이터 신호"로 지칭될 수 있고, "신호"는 회로에서 측정될 수 있는 전류들 및 임의의 다른 전기적 특징을 포함할 수 있다.

- [0029] 제3 세트의 캐스코딩 트랜지스터들은 트랜지스터들(320, 322)을 포함할 수 있다. 이러한 트랜지스터들(320, 322)은, 최종 기준 신호(350)를 생성하기 위해 기준 센터링 신호를 주입함으로써 기준 열로부터의 신호를 조정하기 위해 사용될 수 있다. 위에서 설명된 바와 같이, 기준 열(들)은 논리 0의 데이터 비트로부터 출력된 기준 신호를 제공할 수 있다. 데이터 신호(352)에서 논리 1 및 논리 0 레벨들 둘 모두를 검출할 수 있는 기준 전류 (350)를 생성하기 위해, 감지 증폭기(150)에 제공되는 기준 신호(350)가 조정될 수 있다. 예컨대, 트랜지스터 (320) 및 트랜지스터(312)는 기준 신호에 대한 기준-센터링 신호를 생성하는 데 사용될 수 있다. 기준 신호(350)는, 논리 0 레벨들을 검출하기에 충분히 크지만 논리 1 레벨들을 검출하기에 또한 충분히 작을 필요가 있을 수 있다. 이상적으로, 기준 신호(350)는 논리 0 셀의 신호와 논리 1 셀의 신호 사이의 대략 중간에 있도록 설정될 수 있고, 따라서 기준 신호(350)는 이들 2개의 가능한 데이터 신호 값들의 중심에 배치된다.

- [0030] 트랜지스터들(324, 326)에 의해 전류가 주입된 방식과 유사한 방식으로, 센터링 신호는 트랜지스터들(320, 322)을 사용하여 주입 및 조절될 수 있다. 주입된 센터링 신호, 이를테면, 센터링 전류는 전류 소스로서 작용하는 트랜지스터들(312, 314)에 의해 생성될 수 있다. 일부 실시예들에서, 이 캐스코딩 회로의 데이터 측에는 전력이 공급될 필요가 없으며, 따라서 이 기준 신호를 센터링하기 위해 데이터 신호(352)에 전류가 주입될 필요가 없을 수 있다. 기준 신호(350)만이 논리 0 전류 레벨과 논리 1 전류 레벨 사이에 센터링될 필요가 있을 수 있으며; 데이터 전류(352)는 유사하게 센터링될 필요가 없을 수 있다. 대신에, 트랜지스터들(314, 322)은 전체 회로에서 로딩 밸런스를 유지하기 위한 더미 트랜지스터들로서 구성될 수 있다. 트랜지스터들(320, 312)을 사용하여 센터링 신호를 주입함으로써, 기준 신호(350)는 각각의 어레이 열에 대해 자동-트리밍될 수 있다. 위에서 설명된 바와 같이, 이러한 실시예들에 의해 해결되는 핵심 기술 난제들 중 하나는 감지 증폭기들에 의해 사용되는 기준 신호들과 데이터 열들로부터의 신호들 사이의 변동들을 추적하는 타이트한 감지 윈도우를 생성하는 것이다. 센터링 전류에 의해 수행되는 이 자동-트리밍은 논리 0과 논리 1 사이의 윈도우가 데이터 신호(352)의 PVT 변동들을 추적하는 것을 보장한다. 이러한 트랜지스터들(312, 320)(및 선택적으로 314, 322)은 논리 1 신

호 레벨과 논리 0 신호 레벨 사이에 있도록 기준 신호를 조정하는 "제2 회로"로 지칭될 수 있다.

[0031] MRAM 메모리 셀의 경우, TMR(tunnel magnetoresistance)은 다음의 수식을 사용하여 설명될 수 있다.

$$TMR = \frac{R_{ap} - R_p}{R_p}$$

[0032] [0033]

이 수식에서,  $R_{ap}$ 는 메모리 셀의 역-병렬(anti-parallel) 상태에 대한 논리 1의 고저항을 나타내고,  $R_{p}$ 는 메모리 셀의 병렬 상태에 대한 논리 0의 더 낮은 저항을 나타낸다. 예컨대, TMR이 1.5이면, 1/0 상태들 사이의 저항

$R_{ap}$

$R_p$  비(  $R_p$  )는 대략 2.5일 것이다. 비트 라인, 워드 라인, 및 열 멀티플렉서 상의 추가적인 CMOS 회로 변동들과함께 이러한 저항 값들에 영향을 미치는 프로세스 변동들을 고려하면, 최악의 경우(worst-case)의 저항 비는 결국 2.5보다 훨씬 더 낮게 될 수 있다. 추가적으로, 기준 전류(350)는 또한, 그 자체의 PVT 변동들로 인해 시프트될 수 있으며, 이는 MRAM 감지 증폭기들에 대한 난제들을 추가한다.

[0034] 판독 동작 동안, 감지 증폭기는, 전류가 비트 라인, 열 멀티플렉서, 및 감지 회로들을 통해 흐른 후에 위에서 설명된 바와 같이 MRAM 비트 셀들을 통해 흐르는 전류를 수신할 수 있다. 위에서 제공된 기준 신호(350)를 사용하여 감지 증폭기에 의해 검출된 전류는 다음의 수식에 의해 특징지어질 수 있다.

$$\frac{I_p}{I_{ap}} = \frac{I_p - I_{ref}}{I_{ap} - I_{ref}}$$

[0035]

[0036] 이 수식에서,  $I_p$  및  $I_{ap}$ 는  $R_p$  및  $R_{ap}$  저항들에 대응하는 전류들이며,  $I_{ref}$ 는 위에서 설명된 기준 신호(350)의 전류이다. 이 수식은  $I_{ref}$ 가  $I_{ap}$ 에 더 가까울수록 전류 비가 더 크다는 것을 보여준다.

[0037] 도 3에 예시된 기준-생성 회로(300)의 효과는, PVT 변동들로 인해 데이터 전류(352)가 드리프트할 때 기준 전류 (350)가 데이터 전류(352)를 추적하도록 메모리 어레이의 데이터 열들에 의해 출력된 논리 레벨들 사이에 기준 전류를 센터링하는 것이다. 이러한 실시예들이 MRAM 어레이를 예로서 사용하여 설명되지만, 다른 저항성 메모리 기술들은 또한, 기준-생성 회로(300) 및 본원에서 설명된 다른 회로들을 사용하는 것으로부터 이익을 얻을수 있다. 예컨대, 도 2에 묘사된 메모리 어레이(202)는 MRAM 어레이, ReRAM(resistive RAM) 어레이, PCRAM(phase-change RAM) 어레이, 및/또는 임의의 다른 저항성 메모리 구조를 포함할 수 있다. 따라서, 아래에서 설명되는 기준-생성 회로(300), 기준 열들(208), 및 바이어스 생성 회로들은 임의의 유형의 저항성 메모리와함께 사용될 수 있으며, 본원에서 단지 예로서 사용되는 MRAM 메모리로 제한되지 않는다.

[0038] 도 4는 일부 실시예들에 따른 바이어스-생성 회로(400)를 예시한다. 바이어스 생성 회로(400)는 3개의 별개의 서브 회로들: 전류 소스(420), 캐스코딩 바이어스(422), 및 기준 바이어스(424)를 포함할 수 있다. 전류 소스(420)는 MRAM 비트 셀(408)의 저항에 기반하여 전류를 생성할 수 있다. 전류 소스(420)는, 캐스코딩 회로들 ( $V_{cas}(402)$ )을 바이어싱하기 위한 그리고 필터링 전류( $V_{inj}(406)$ )의 주입 전류들을 조절하기 위한 전압 레벨들을 생성하기 위해 캐스코딩 바이어스 회로(422) 및 기준 바이어스(424)에 의해 레퍼런싱(reference)될 수 있다. 이러한 기준 레벨들은 위에서 설명된 바와 같이 하나 이상의 기준 열들의 더미 비트 셀들(408, 410, 412)에 기반하여 생성될 수 있다. 이는 이러한 기준 전압들이 데이터 비트 셀들에서의 PVT 변동들 및 감지 증폭기에 대한 이들의 연관된 경로들을 자동으로 추적할 수 있게 한다. 바이어스-생성 회로(400)로부터의 출력들은, 공통신호 성분의 제거 및 기준 전류의 조정을 제어하기 위해 도 3의 회로에 직접 공급될 수 있다. 구체적으로,  $V_{cas}$  출력(402)은 도 3의 입력(306)에 연결될 수 있고,  $V_{inj}$  출력(406)은 도 3의 입력(304)에 연결될 수 있다.

[0039] 도 5는 일부 실시예들에 따른, 센터링 전류를 위해 사용되는 추가적인 기준 바이어스들을 생성하기 위한 회로들 (500)을 예시한다. V<sub>Ⅲ</sub> 신호는 도 4의 대응하는 V<sub>Ⅲ</sub> 입력(404)에 연결된다. V<sub>Ⅲ</sub> 신호는 전력을 절약하기 위해 도 4 및 도 5의 기준-바이어싱 회로들을 턴 온 및 턴 오프시키는 데 사용될 수 있다. 이러한 인에이블 신호는 위에서 설명된 메모리 회로의 워드 라인 신호로부터 생성될 수 있다. 이러한 회로들은, 비트 셀들(508, 510)로 부터의 논리 1 어레이 전류와 비트 셀들(512, 514)로부터의 논리 0 어레이 전류 사이의 차이를 사용하여 기준 전류 바이어스(502)를 생성한다. 도 5의 회로들(500)의 단자들은 이전 도면들의 대응하는 단자들에 연결될 수

있다. 예컨대, 기준 전류 바이어스 전압에 대한 출력(502)은 도 3의 단자(302)에 연결될 수 있다. 캐스코딩 게이트 바이어스 전압에 대한 단자(504)는 도 4의 대응하는 출력(404)에 연결될 수 있다.

- [0040] 도 6은 일부 실시예들에 따른, 메모리 회로로부터 데이터를 판독하기 위한 방법의 플로차트를 예시한다. 방법은 메모리 어레이에 위치된 하나 이상의 기준 열들로부터 기준 신호를 수신하는 단계(602)를 포함할 수 있다. 메모리 어레이는 MRAM 셀들 또는 임의의 다른 유형의 저항성 메모리 셀들을 포함할 수 있다. 하나 이상의 기준 열들은, 메모리 어레이의 대략적인 중심을 포함하여 메모리 어레이 전체에 걸쳐 위치될 수 있거나 또는 규칙적인 간격들로 메모리 어레이 내에 산재될 수 있다. 하나 이상의 기준 열들의 서브세트는 대응하는 데이터 열에 대한 근접도에 기반하여 판독 동작을 위해 선택될 수 있다. 예컨대, 각각의 데이터 열은 메모리 어레이의 동일한 섹터에 있는 특정 기준 열에 할당될 수 있다. 일부 실시예들은 또한, 정규 데이터 열들이 능동적으로 판독되고 있지 않을 때, 기준 열들로서 사용될 수 있는 그러한 데이터 열들을 선택할 수 있다.

- [0041] 일부 실시예들에서, 하나 이상의 기준 열들 중 복수의 기준 열들이 기준 신호를 생성하는 데 사용될 수 있다. 예컨대, 복수의 기준 열들로부터의 출력 전류들은 최종 기준 신호를 생성하기 위해 평균화되거나 또는 그렇지 않으면 함께 조합될 수 있다. 메모리 어레이는 또한, 1차 기준 열들이 실패하는 경우에 1차 기준 열들에 대한 백업으로서 사용될 수 있는 리던던트 기준 열들을 포함할 수 있다. 리던던트 기준 열 출력들은 또한, 기준 신호를 생성하기 위해 1차 기준 열 출력과 평균화될 수 있다. 하나 이상의 기준 열들에 저장된 값은 기준 열에 하드-코딩되거나 프로그래밍가능할 수 있다. 일부 실시예들은 기준 열의 비트 셀들 각각에서 논리 레벨 0을 사용할 수 있다.

- [0042] 방법은 또한, 메모리 어레이의 복수의 데이터 열들 내의 데이터 열로부터 데이터 신호를 수신하는 단계(604)를 포함할 수 있다. 데이터 열들 각각은 다수의 비트 셀들을 포함할 수 있으며, 이들 각각은 논리 0 또는 논리 1 의 표현을 저장한다. 예컨대, 각각의 비트 셀은 논리 값의 표현을 저장하기 위해 자유-상태 자석의 극성을 설정할 수 있다. 특정 데이터 열은 메모리 어레이의 비트 라인을 사용하는 판독 동작에 의해 선택될 수 있다. 판독 동작을 위해 선택될 때, 데이터 열은 데이터 신호를 제공할 수 있다. 일부 실시예들에서, 데이터 신호 및 기준 신호 둘 모두는 전류 및/또는 전압 값을 포함할 수 있다. 예컨대, 기준 전류와의 비교를 위해 데이터 열로부터 감지 증폭기로 전류가 제공될 수 있다. 단계(602) 및 단계(604)가 플로차트(600)에서 순차적으로 도시되지만, 이러한 단계들은 일반적으로 병렬로 실행될 것임을 주목한다. 구체적으로, 기준 신호 및 데이터 신호는 동시에 메모리 어레이로부터 전송되고 감지 증폭기에 의해 수신될 수 있으며, 이로써 상이한 신호들과 연관된 임의의 타이밍 차이들을 제거할 수 있다.

- [0043] 방법은 추가적으로, 기준 신호 및 데이터 신호로부터 공통 신호 성분을 제거하는 단계(606)를 포함할 수 있다. 공통 신호 성분은 기준 전류 및 데이터 전류로부터 제거될 수 있는 공통 전류 성분일 수 있다. 공통 신호 성분은, 기준 전류를 위한 캐스코딩 트랜지스터들의 쌍 및 데이터 전류를 위한 캐스코딩 트랜지스터들의 쌍을 포함하는 제1 회로를 사용하여 제거될 수 있다. 캐스코딩 트랜지스터들의 쌍들은 이들이 기준 신호 및 데이터 신호 둘 모두로부터 동일한 공통 신호를 제거하도록 매칭될 수 있다. 캐스코딩 트랜지스터들의 각각의 쌍은 직렬-연결된 NMOS 및 PMOS 트랜지스터들을 포함할 수 있다. 공통 신호 성분을 제거하기 위한 제1 회로의 예가 위의 도 3에서 예시되었다.

- [0044] 방법은, 논리 1 신호 레벨과 논리 0 신호 레벨 사이에 있도록 기준 신호를 조정하는 단계(608)를 더 포함할 수 있다. 예컨대, 기준 신호는 기준 열로부터 출력된 논리 0으로부터 수신된 하이 신호 레벨로부터 감소될 수 있다. 기준 신호는 논리 1 신호 레벨과 논리 0 신호 레벨 사이에 센터링되거나 대략적인 중간점으로 감소될 수 있다. 공통 신호 성분을 제거하기 위한 제1 회로에서와 같이, 제2 회로는 기준 신호에 대한 직렬-연결된 NMOS 및 PMOS 트랜지스터들의 캐스코딩 쌍을 포함할 수 있다. 대응하는 트랜지스터들이 또한 데이터 신호를 위해 포함될 수 있지만, 이러한 트랜지스터들은 전력 공급받을 필요가 있는 것이 아니라, 대신에, 데이터 신호 및 기준 신호에 대한 회로들이 모두 매칭하도록 포함될 수 있다. 기준 신호를 조정하기 위한 제2 회로의 예가 위의 도 3에서 예시되었다. 단계(606) 및 단계(608)가 플로차트(600)에서 순차적으로 도시되지만, 이러한 단계들은 또한, 병렬로 실행될 수 있음을 주목한다. 구체적으로, 도 3에 예시된 바와 같이, 공통 신호 성분이 제거될 수 있고 기준 신호는 동시에 캐스코딩 트랜지스터 브랜치들을 사용하여 병렬로 조정될 수 있다.

- [0045] 방법은 또한, 기준 신호를 감지 증폭기에 제공하는 단계(610)를 포함할 수 있다. 공통 신호 성분이 제거된 후 그리고 논리 1 신호 레벨과 논리 0 신호 레벨 사이에 있도록 조정된 후에, 기준 신호가 감지 증폭기에 제공될 수 있다. 예컨대, 기준 신호가 기준 전류를 포함할 때, 기준 신호 레벨을 감소시키기 위해 기준 전류에 반대 전류를 주입함으로써 기준 전류가 감소될 수 있다. 기준 열이 논리 0 신호 레벨을 출력할 때, 하이 논리 0 레

벨로부터 논리 0 레벨과 논리 1 레벨 사이가 되도록 감소된다.

- [0046] 방법은 추가적으로, 데이터 신호를 감지 증폭기에 제공하는 단계(612)를 포함할 수 있다. 데이터 신호는 위에서 설명된 바와 같이 공통 신호 성분을 제거한 후에 감지 증폭기에 제공될 수 있다. 감지 증폭기는 데이터 신호를 통해 메모리 어레이로부터 수신된 논리 1 신호와 및 논리 0 신호 사이의 차이들을 검출하도록 구성될 수 있다. 이러한 차이들은 기준 신호를 데이터 신호와 비교함으로써 검출될 수 있다. 감지 증폭기는 도 1c에 예시된 래칭 감지 증폭기를 포함하는, 임의의 구성의 감지 증폭기를 포함할 수 있다. 단계(610) 및 단계(612)가 플로차트(600)에서 순차적으로 도시되지만, 이러한 단계들은 일반적으로 병렬로 실행될 것임을 주목한다. 구체적으로, 기준 신호 및 데이터 신호는 감지 증폭기에 의해 동시에 수신될 수 있다. 신호들 둘 모두가 동일한 기록 라인에 의해 활성화되기 때문에, 이들은 전형적으로 도 3의 회로를 통해 전파되고 동시에 감지 증폭기에 도달할 것이다.

- [0047] 도 6에 예시된 특정 단계들은 다양한 실시예들에 따라 메모리 회로로부터 데이터를 판독하는 특정 방법들을 제공한다는 것이 인지되어야 한다. 대안적인 실시예들에 따라 다른 시퀀스들의 단계들이 또한 수행될 수 있다. 예컨대, 대안적인 실시예들은 위에서 약술된 단계들을 상이한 순서로 수행할 수 있다. 더욱이, 도 6에 예시된 개별적인 단계들은 개별적인 단계에 적절한 다양한 시퀀스들로 수행될 수 있는 다수의 서브-단계들을 포함할 수 있다. 게다가, 특정 애플리케이션들에 따라 추가적인 단계들이 추가되거나 제거될 수 있다. 당업자는 많은 변형들, 수정들, 및 대안들을 인식할 것이다.

- [0048] 전술한 설명에서, 설명의 목적들을 위해, 다양한 실시예들의 철저한 이해를 제공하기 위해 다수의 특정 세부사항들이 제시되었다. 그러나, 이러한 특정 세부사항들 중 일부 없이 실시예들이 실시될 수 있다는 것이 당업자에게 명백할 것이다. 다른 경우들에서, 잘 알려진 구조들 및 디바이스들은 블록도 형태로 도시된다.

- [0049] 전술한 설명은 단지 예시적인 실시예들을 제공하며, 본 개시내용의 범위, 적용가능성, 또는 구성을 제한하도록 의도되지 않는다. 오히려, 예시적인 실시예들의 전술한 설명은 예시적인 실시예를 구현하기 위한 가능한 설명을 당업자들에게 제공할 것이다. 첨부된 청구항들에 제시된 바와 같은 다양한 실시예들의 사상 및 범위를 벗어 나지 않으면서, 엘리먼트들의 기능 및 어레인지먼트에서 다양한 변경들이 이루어질 수 있다는 것이 이해되어야 한다.

- [0050] 실시예들의 철저한 이해를 제공하기 위해 전술한 설명에서 특정 세부사항들이 제공된다. 그러나, 실시예들이 이러한 특정 세부사항들 없이 실시될 수 있다는 것이 당업자에 의해 이해될 것이다. 예컨대, 회로들, 시스템들, 네트워크들, 프로세스들, 및 다른 컴포넌트들은 불필요한 세부사항으로 실시예들을 모호하게 하지 않기 위해 블록도 형태의 컴포넌트들로서 도시되었을 수 있다. 다른 경우들에서, 실시예들을 모호하게 하는 것을 피하기 위해, 잘 알려진 회로들, 프로세스들, 알고리즘들, 구조들, 및 기법들이 불필요한 세부 사항 없이 도시되었을 수 있다.

- [0051] 또한, 개별적인 실시예들은 플로차트, 흐름도, 데이터 흐름도, 구조도, 또는 블록도로서 묘사된 프로세스로서 설명되었을 수 있다는 것이 주목된다. 플로차트가 순차적인 프로세스로서 동작들을 설명했을 수 있지만, 동작들 중 다수는 병렬로 또는 동시에 수행될 수 있다. 게다가, 동작들의 순서는 재배열될 수 있다. 프로세스는 프로세스의 동작들이 완료될 때 종료되지만, 도면에 포함되지 않은 추가적인 단계들을 가질 수 있다. 프로세스는 방법, 기능, 절차, 서브루틴, 서브프로그램 등에 대응할 수 있다. 프로세스가 함수에 대응할 때, 프로세스의 종결은 호출 함수 또는 주 함수로의 함수의 리턴에 대응할 수 있다.

- [0052] 전술한 명세서에서, 다양한 실시예들의 양상들은 특정 실시예들을 참조하여 설명되지만, 당업자들은 본 발명이 이에 제한되지 않음을 인식할 것이다. 위에서 설명된 실시예들의 다양한 특징들 및 양상들은 개별적으로 또는 공동으로 사용될 수 있다. 또한, 실시예들은 본 명세서의 더 넓은 사상 및 범위를 벗어나지 않으면서, 본원에서 설명된 것들 이외의 임의의 수의 환경들 및 애플리케이션들에서 활용될 수 있다. 따라서, 명세서 및 도면들은 제한적이기 보다는 예시적인 것으로 간주되어야 한다.

# 도면1a

# *도면1b*

# 도면1c