(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5396878号 (P5396878)

(45) 発行日 平成26年1月22日(2014.1.22)

(24) 登録日 平成25年11月1日(2013.11.1)

| (51) Int.Cl. |      |           | FΙ   |      |   |

|--------------|------|-----------|------|------|---|

| нозк         | 3/03 | (2006.01) | нозк | 3/03 |   |

| нозк         | 4/50 | (2006.01) | нозк | 4/50 | C |

| нозк         | 5/00 | (2006.01) | нозк | 5/00 | V |

請求項の数 3 (全8頁)

| (21) 出願番号 | 特願2009-11741 (P2009-11741)    | ا(73) • |

|-----------|-------------------------------|---------|

| (22) 出願日  | 平成21年1月22日 (2009.1.22)        |         |

| (65) 公開番号 | 特開2010-171685 (P2010-171685A) |         |

| (43) 公開日  |                               | (74) 1  |

| 審査請求日     | 平成23年9月13日 (2011.9.13)        |         |

|           |                               | (72)    |

(73) 特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74)代理人 100074099

弁理士 大菅 義之

(72) 発明者 菅原 聡

東京都品川区大崎一丁目11番2号 富士

電機デバイステクノロジー株式会社内

||(72)発明者 山田 耕平

東京都品川区大崎一丁目11番2号 富士

電機デバイステクノロジー株式会社内

審査官 石田 勝

最終頁に続く

(54) 【発明の名称】 クロック同期回路

## (57)【特許請求の範囲】

## 【請求項1】

ヒステリシスインバータ,抵抗および接続端子を有し、前記ヒステリシスインバータの入力端子と前記抵抗の一方の端子を接続し、前記ヒステリシスインバータの入力端子と出力端子の間に、前記抵抗とスイッチの直列回路を接続し、前記ヒステリシスインバータの入力端子と前記接続端子を接続するとともに、

前記接続端子と接地の間にコンデンサを接続して前記ヒステリシスインバータの出力信号を内部クロック信号とする第1の動作モード、または前記接続端子に外部クロック信号を入力して前記ヒステリシスインバータの出力信号を外部クロック同期用信号として使用する第2の動作モードを選択可能とし、

前記ヒステリシスインバータの入力端子を入力とし、高電位の閾値と低電位の閾値を有するコンパレータを設け、前記高電位の閾値を外部クロックのハイレベルよりも低く、前記ヒステリシスインバータの高電位の閾値よりも高く設定し、さらに、前記低電位の閾値を外部クロックのローレベルよりも高く、前記ヒステリシスインバータの低電位の閾値よりも低く設定し、前記コンパレータの出力に基づいて前記スイッチの開閉を制御する、

ことを特徴とするクロック同期回路。

## 【請求項2】

前記コンパレータは、前記入力端子に印加される信号が、前記高電位の閾値よりも高い 場合および前記低電位の閾値よりも低い場合には、前記スイッチをオフする信号を出力し て、前記第1のモードで動作させるとともに、前記入力端子に印加される信号が、前記低

<u>電位の閾値よりも高く且つ前記高電位の閾値よりも低い場合には、前記スイッチをオンする信号を出力して、前記第2のモードで動作させる、</u>

ことを特徴とする請求項1記載のクロック同期回路。

## 【請求項3】

前記請求項1または2に記載されたクロック同期回路を、入力電源に接続されたスイッチング素子をオン/オフすることにより所定の直流電圧出力を得るスイッチング電源を制御するスイッチング電源の制御回路内に備えていることを特徴とするスイッチング電源の制御回路。

## 【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は、入力電源に接続されたスイッチング素子をオン / オフすることにより磁気素子にエネルギを蓄積させて所定の直流電圧出力を得るスイッチング電源を制御する制御回路において、内部クロックまたは外部クロックに同期して動作させる場合に、クロック入力機能を簡単に構成し得るスイッチング電源制御回路方式に関する。

### 【背景技術】

## [0002]

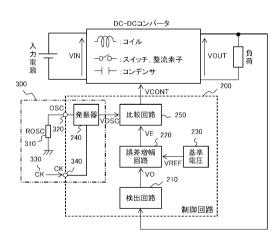

図6は、従来から知られているスイッチング電源の一般的な構成を示すブロック図である。スイッチング電源には、インバータやコンバータなど、さまざまなものがあるが、ここではスイッチング電源の一例であるDC-DCコンバータをその典型例として示している。図6に示されるDC-DCコンバータは、その出力VOUTが制御回路200にフィードバックされ、制御回路200では出力VOUTと目標値を比較しその結果に基づいてパルス信号(VCONT)を生成し出力する。

### [0003]

ここで制御回路200の動作について、簡単に説明する。一般に制御回路200は、DC-DCコンバータの出力VOUTを検出回路210で検出し、次段の誤差増幅回路220に入力可能な信号VOに変換して出力する。誤差増幅回路220は信号VOと基準電圧VREF(230)の差を増幅して誤差信号VEを出力する。比較回路250は誤差信号VEと発振器240の出力VOSCを比較し、PWMパルス(VCONT)を出力する。ここで、発振器240の出力波形VOSCには三角波、鋸波、正弦波、矩形波等がある。さらにパルス信号(VCONT)は、MOSFET(metal-oxide-semiconductor field effect transistor)やバイポーラトランジスタに代表される半導体スイッチ素子またはリレー回路で代表される機械スイッチ素子をオン/オフすることにより、出力VOUTを制御している。

## [0004]

上記のようなスイッチング電源において、複数台同時に駆動するものや、スイッチング電源の周りの電子部品へのノイズの影響を抑制することを想定しているものでは、スイッチング電源のスイッチング周波数を所定周波数に固定することが求められる場合がある。

### [0005]

周波数を固定するためには、外部クロックに同期してスイッチングを行う機能を搭載する方法がある。図6のスイッチング電源の制御回路におけるクロック同期回路300は、周波数を任意の値に調整する場合には、内部クロックを用い、スイッチング電源を用いるシステムが要求する周波数でスイッチングさせる場合には、外部クロックCK(330)に同期して動作するものの例である。

## [0006]

しかし、図6の回路方式では、一般に内部に発振器240を搭載し、内部の発振器240の周波数を任意に調整するための抵抗あるいはコンデンサ等の外付け部品(図6では抵抗ROSC)310を接続するための端子(図中OSC端子)320と外部クロックCK(330)を入力するための端子(図6中CK端子)340を必要とする。また、図6中の発振器240は、外部からクロックを選択する機能を搭載する必要がある。このためスイッチング電源制御回路の端子の増加および発振回路の複雑化を招く。

10

20

30

40

### [0007]

下記に示す特許文献 1 では、複数台のスイッチング電源を外部クロックで同期させた状態が示されているが、内部クロックと外部クロックの切替機能の搭載による回路構成の複雑化および端子の増加を抑制することには触れられていない。

【先行技術文献】

【特許文献】

[ 0 0 0 8 ]

【特許文献1】特開2004-357465号公報

【発明の概要】

【発明が解決しようとする課題】

[0009]

上記のような課題を解決するため本発明は、スイッチング電源において、回路の複雑化および端子の増加を抑制して、内部クロックまたは外部クロックに同期させることができるクロック同期回路を提供することを目的とするものである。

【課題を解決するための手段】

[0010]

本発明のクロック同期回路は、ヒステリシスインバータ,抵抗および接続端子を有し、前記ヒステリシスインバータの入力端子と前記抵抗の一方の端子を接続し、前記ヒステリシスインバータの入力端子と<u>出力</u>端子<u>の間に、前記抵抗とスイッチの直列回路</u>を接続し、前記ヒステリシスインバータの入力端子と前記接続端子を接続するとともに、前記接続端子と接地の間にコンデンサを接続して前記ヒステリシスインバータの出力信号を内部クロック信号とする第1の動作モード、または前記接続端子に外部クロック信号を入力して前記ヒステリシスインバータの出力信号を外部クロック同期用信号として使用する第2の動作モードを選択可能とし、前記ヒステリシスインバータの入力端子を入力とし、高電位の閾値と低電位の閾値を有するコンパレータを設け、前記高電位の閾値を外部クロックのハイレベルよりも低く、前記ヒステリシスインバータの高電位の閾値よりも高く設定し、さらに、前記低電位の閾値を外部クロックのローレベルよりも高く、前記ヒステリシスインバータの低電位の閾値を外部クロックのローレベルよりも高く、前記ヒステリシスインバータの低電位の閾値よりも低く設定し、前記コンパレータの出力に基づいて前記スイッチの開閉を制御するようにしたものである。

【発明の効果】

[0011]

本発明によれば、スイッチング電源において、回路の複雑化および端子の増加を抑制して内部クロックまたは外部クロックの同期機能を実現することができる。

【図面の簡単な説明】

[0012]

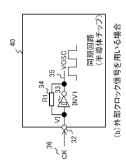

【図1】本発明の第1の実施形態に係るスイッチング電源の制御回路におけるクロック同期回路の構成例を示す図である。

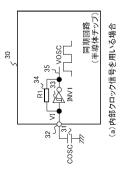

【図2】本発明の第2の実施形態に係るスイッチング電源の制御回路におけるクロック同期回路の構成例を示す図である。

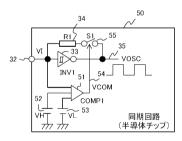

【図3】図2の回路の動作波形を示す図である。

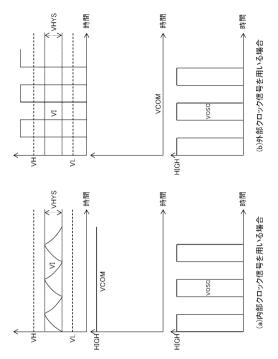

【 図 4 】図 2 に示したコンパレータ(COMP1)の第 1 の具体的構成例を示す図である。

【図 5 】図 2 に示したコンパレータ(COMP1)の第 2 の具体的構成例を示す図である。

【図6】従来から知られているスイッチング電源の一般的な構成を示すブロック図である

【発明を実施するための形態】

[0013]

以下、本発明の実施の形態について、詳細に説明する。

[実施形態1]

図1は、本発明の第1の実施形態に係るスイッチング電源の制御回路におけるクロック

10

20

30

40

10

20

30

40

50

同期回路の構成例を示す図である。この同期回路は、図6に示したスイッチング電源の制御回路におけるクロック同期回路300の構成を改善するものであり、同期回路以外は、図6に示した制御回路と同じであるためその説明を省略する。図1(a)は、スイッチング電源の制御回路におけるクロック同期回路に内部クロックを用いる第1の動作モードの場合の例であり、図1(b)は、スイッチング電源の制御回路におけるクロック同期回路に外部クロックを用いる第2の動作モードの場合の例である。

### [0014]

図 1 (a)に示すスイッチング電源の制御回路におけるクロック同期回路30に内部クロックを用いる場合は、図 1 (a)中のヒステリシスインバータ(INV1)33、抵抗(R1)34および外付けコンデンサ(COSC)31で内部クロックを生成する発振器を構成し、その出力信号(VOSC)35の発振周波数は外付けコンデンサ(COSC)31の値で任意に調整する。外付けコンデンサ(COSC)31は接続端子(入力端子)32を介してヒステリシスインバータ(INV1)33の入力端子と接続されている。スイッチング電源の制御回路を半導体集積回路により実現する場合、接続端子32は当該半導体集積回路が集積される半導体チップの外部接続端子となり、コンデンサ(COSC)31は半導体チップの外部に設けられ、外部接続端子32を介して半導体チップ内部のヒステリシスインバータ(INV1)33に接続されることになる。

## [0015]

また図 1 (b)に示すスイッチング電源の制御回路におけるクロック同期回路40に外部クロックを用いる場合は、図 1 (a)の外付けコンデンサ(COSC)31を接続端子32から外し、上記のヒステリシスインバータ(INV1)33の入力に外部クロック(CK)36を印加することで外部クロック(CK)36に同期した信号(VOSC)35を得る。

#### [0016]

以上のような構成にすることによって、内部クロックを用いる第1の動作モードもしくは外部クロックを用いる第2の動作モードを選択可能なクロック同期回路を実現することでき、かつ内部クロックと外部クロックの切替機能の搭載による回路構成の複雑化および端子の増加を抑制することができる。

## 「実施形態21

図 2 は、本発明の第 2 の実施形態に係るスイッチング電源の制御回路におけるクロック 同期回路の構成例を示す図である。図 1 の第 1 の実施形態では、外部クロック (CK) 36を用いる場合に、外部クロック (CK) 36は抵抗 (R1) 34を駆動できる電流容量が必要となる。すなわち、抵抗 (R1) 34はヒステリシスインバータ (INV1) 33の入出力間に接続されているので、両端に電圧 |VOSC-VI| が印加されてそれに応じた電流が流れている。その電流をソースにせよ、シンクにせよ、外部から供給できるようにしなければならない。しかし図 2 の構成では、このような問題が生じないよう構成している。すなわち図 2 では、コンパレータ (COMP1) 51 およびスイッチ (S1) 55を追加し、コンパレータ (COMP1) 51 およびスイッチ (S1) 55を追加し、コンパレータ (COMP1) 51 およびスイッチ (S1) 55をオフする信号を出力し、入力信号 (VI) が基準電源 VL53よりも高く基準電源 VH52より低い場合にスイッチ (S1) 55をオンする信号を出力する。

## [0017]

図3は、図2の回路の動作波形を示す図である。図3において、VHYSはヒステリシスインタバータ(INV1)51のヒステリシスの幅を示している。ここでは、スイッチ(S1)55はコンパレータ(COMP1)51の出力VCOM(54)がハイ(HIGH)のときにオン、コンパレータ(COMP1)51の出力VCOM(54)がロー(LOW)のときにオフとしているが、この論理を反転させても良い。また、図3において、(a)内部クロック信号を用いる場合では、入力信号(VI)が常に基準電源VL53よりも高く基準電源VH52より低い状態であるため、常にスイッチ(S1)55がオンし、回路内部でクロックが生成される。一方、(b)外部クロック信号を用いる場合では、外部クロック信号36のロー(LOW)レベルを基準電源VL53よりも低く、外部クロック信号36のハイ(HIGH)レベルを基準電源VH52よりも高い信号となるようにクロックの振幅を設定し、且つ、そのようになるように基準電源VH52および基準電源VL53を設定することで、スイッチ(S1)55が常にオフ状態(つまり出力VCOM(54)がロー)になるようにしておく。これにより、

外部クロック36は抵抗(R1)34を駆動する必要がなくなり、高インピーダンスの(電流駆動 能力の小さい)外部クロック信号を用いることができる。

## [0018]

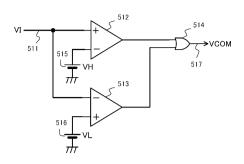

図 4 は、図 2 に示したコンパレータ(COMP1)の第 1 の具体的構成例を示す図である。図 4 に示す第1の具体的構成例では、入力信号(VI)511を比較器入力の(+)端に受ける第1比 較器512と、入力信号(VI)511を比較器入力の(-)端に受ける第2比較器513と、第1比較 器512及び第2比較器513の出力を受ける論理和回路(オア回路)514とで構成され、論理 和回路514の出力端からコンパレータ(COMP1)の出力(VCOM)517を得るものである。上記に おいて第1比較器512の比較器入力の(-)端には、基準電源VH(515)が接続され、また第2 比較器513の比較器入力の(+)端には、基準電源VL(516)が接続される。そして図4に示す 構成では、基準電源VL(516) < 入力信号(VI)(511) < 基準電源VH(515)ではコンパレータ(CO MP1)の出力(VCOM)517はローレベル(L)であり、それ以外ではハイレベル(H)となる。

#### [0019]

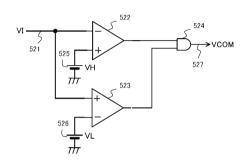

図5は、図2に示したコンパレータ(COMP1)の第2の具体的構成例を示す図である。図 5に示す第2の具体的構成例では、入力信号(VI)521を比較器入力の(-)端に受ける第3 比較器522と、入力信号(VI)521を比較器入力の(+)端に受ける第4比較器523と、第3比較 器522及び第4比較器523の出力を受ける論理積回路(アンド回路)524とで構成され、論 理積回路524の出力端からコンパレータ(COMP1)の出力(VCOM)527を得るものである。上記 において第3比較器522の比較器入力の(+)端には、基準電源VH(525)が接続され、また第 4 比較器523の比較器入力の(-)端には、基準電源VL(526)が接続される。そして図 5 に示 す構成では、基準電源VL(526)<入力信号(VI)(521)<基準電源VH(525)ではコンパレータ( COMP1)の出力(VCOM)527はハイレベル(H)であり、それ以外ではローレベル(L)となる。

## 【符号の説明】

### [0020]

- 30 クロック同期回路(内部クロック使用)

- 31 外付けコンデンサ(COSC)

- 32 接続端子(入力端子)

- 33 ヒステリシスインバータ

- 34 抵抗(R1)

- 35 クロック同期回路の出力信号(VOSC)

- 36 外部クロック(CK)

- 40 クロック同期回路(外部クロック使用)

- クロック同期回路(外部クロック使用) 50

- コンパレータ(COMP1) 51

- 52 基準電源 1 (VH)

- 53 基準電源 2 (VL)

- 54 コンパレータ出力(VCOM)

- スイッチ(S1) 55

- 511 入力信号(VI)

- 第1比較器 512

- 513 第2比較器

- 514 論理和回路(オア回路)

- 515 基準電源 1 (VH)

- 516 基準電源 2 (VL)

- 517 VCOM(コンパレータ出力)

- 521 入力信号(VI)

- 522 第3比較器

- 523 第4比較器

- 論理積回路(アンド回路) 524

- 525 基準電源 1 (VH)

20

10

30

40

526 基準電源 2 (VL)

527 VCOM(コンパレータ出力)

# 【図1】

本発明の第1の実施形態に係るスイッチング電源の 制御回路におけるクロック同期回路の構成例を示す図

# 【図2】

本発明の第2の実施形態に係るスイッチング電源の 制御回路におけるクロック同期回路の構成例を示す図

# 【図3】

## 図2の回路の動作波形を示す図

# 【図4】

図2に示したコンパレータ(COMP1)の第1の具体的構成例を示す図

# 【図5】

図2に示したコンパレータ(COMP1)の第2の具体的構成例を示す図

# 【図6】

従来から知られているスイッチング電源の一般的な構成を示すブロック図

## フロントページの続き

# (56)参考文献 特開昭 6 4 - 0 8 0 1 0 5 (JP, A)

特開昭59-51609(JP,A)

特開昭63-313909(JP,A)

特開昭56-168168(JP,A)

特集\*ワンチップ・マイコン実践入門 「クロック」,「トランジスタ技術 1999年5月号

」,日本,CQ出版社,1999年 5月,図4、図5,184~185頁

## (58)調査した分野(Int.CI., DB名)

H 0 3 K 3 / 0 3

H 0 3 K 4 / 5 0

H 0 3 K 5 / 0 0