#### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4088913号 (P4088913)

(45) 発行日 平成20年5月21日(2008.5.21)

(24) 登録日 平成20年3月7日(2008.3.7)

| (51) Int.Cl. |         |            | FΙ   |       |      |

|--------------|---------|------------|------|-------|------|

| HO1L         | 21/8242 | (2006.01)  | HO1L | 27/10 | 621Z |

| HO1L         | 27/108  | (2006.01)  | HO1L | 27/10 | 651  |

| HO1L         | 21/822  | (2006.01)  | HO1L | 27/10 | 621C |

| HO1L         | 27/04   | (2006, 01) | HO1L | 27/04 | C    |

請求項の数 16 (全8頁)

(21) 出願番号 特願2001-158695 (P2001-158695) (22) 出願日 平成13年5月28日 (2001.5.28) (65) 公開番号 特開2002-50700 (P2002-50700A) 平成14年2月15日 (2002.2.15) 審査請求日 平成17年12月9日 (2005.12.9)

(31) 優先権主張番号 2000-30085

(32) 優先日 平成12年6月1日 (2000.6.1)

(33) 優先権主張国 韓国 (KR)

||(73)特許権者 591024111

株式会社ハイニックスセミコンダクター HYNIX SEMICONDUCTOR INC.

大韓民国京畿道利川市夫鉢邑牙美里山13

6 - 1

San 136-1, Ami-Ri, Bu bal-Eup, Ichon-Shi, K youngki-Do, Korea

(74)代理人 100065215

弁理士 三枝 英二

(74)代理人 100076510

弁理士 掛樋 悠路

(74)代理人 100086427

弁理士 小原 健志

最終頁に続く

## (54) 【発明の名称】半導体素子のキャパシタ製造方法

## (57)【特許請求の範囲】

#### 【請求項1】

半導体基板上に下部電極を形成するステップと、

前記下部電極上に窒化膜を形成するステップと、

前記室化膜上にアモルファスTaON薄膜を形成するステップと、

前記アモルファスTaON薄膜を高温熱処理して結晶化させるステップと、

前記結晶化されたTaON薄膜上に上部電極用TiON薄膜及びドーピングされたシリコン膜の 積層構造を形成するステップとを含んでなることを特徴とする半導体素子のキャパシタ製 造方法。

### 【請求項2】

前記下部電極が、シリンダー型構造またはスタック型構造からなる請求項 1 記載の半導体素子のキャパシタ製造方法。

#### 【請求項3】

前記下部電極上への窒化膜の形成を、CVDチャンバ内で350~450 の温度で50~150sccmのNH $_3$ ガスを供給しつつ、プラズマを用いて1~10分間にわたり前記下部電極の表面に窒化膜を形成することにより行う請求項 1 記載の半導体素子のキャパシタ製造方法。

# 【請求項4】

前記アモルファスTaON薄膜の形成を、160~190 に保持された気化器におい<u>て原</u>料物質であるタンタルエチレート $(Ta(OC_2H_5)_5)$ を気相状態とした後、 $0.2 \sim 0.4 Torr$ の圧力及び350~450 の温度に保持され、かつ流量25~200sccmの $0_2$ ガスが供給されるCVDチャンバに気

相状態の前記原料物質を供給し、前記CVDチャンバ内で、 $O_2$ と前記原料物質から得られる T a 化学蒸気との表面化学反応により行う請求項 1 記載の半導体素子のキャパシタ製造方法。

#### 【請求項5】

前記アモルファスTaON薄膜の結晶化工程を、流量10~1000sccm $00_3$ ガスが注入されるCVDチャンバ内で750~900 の温度で1~60分間熱処理することにより行う請求項 1 記載の半導体素子のキャパシタ製造方法。

#### 【請求項6】

前記アモルファスTaON薄膜の結晶化工程を、バッチ形態のファーネス或いは急速熱処理工程を用いて、 $N_2$ Oおよび $O_3$ 雰囲気中 $750\sim900$  の温度で30秒~1時間熱処理することにより行う請求項 1 記載の半導体素子のキャパシタ製造方法。

#### 【請求項7】

<u>結</u>晶化された<u>前記</u>TaON薄膜上に形成される上部電極が、TiON膜及びドーピングされたポリシリコン膜の積層構造を有しており、前記アモルファスTaON薄膜の結晶化工程において $0_3$ が注入された<u>前記CVDチャンバ内で形</u>成される請求項<u>5</u>記載の半導体素子のキャパシタ製造方法。

#### 【請求項8】

前記TiON膜を、前駆体であるTiCl $_4$ を流量調節器を介して蒸発器へ送給し、150~200の温度で蒸発させてTiN化学蒸気を得た後、前記TiN化学蒸気と流量10~1000sccmのNH $_3$ ガスとを $0_3$ が注入されたチャンバ内に供給して300~600 の温度で表面化学反応により形成する請求項 1 記載の半導体素子のキャパシタ製造方法。

#### 【請求項9】

半導体基板上に導電性ポリシリコン膜または導電性アモルファスシリコン膜からなる下 部電極を形成するステップと、

前記下部電極上に窒化膜を形成するステップと、

前記室化膜上にアモルファスTaON薄膜を形成するステップと、

前記アモルファスTaON薄膜をバッチ形態のファーネス或いは急速熱処理工程を用いて結晶化させるステップと、

結晶化された<u>前記</u>TaON薄膜上に上部電極用TiON及びドーピングされたシリコン膜の積層構造を形成するステップとを含んでなることを特徴とする半導体素子のキャパシタ製造方法。

## 【請求項10】

前記下部電極が、シリンダー型またはスタック型構造からなる請求項9記載の半導体素子のキャパシタの製造方法。

#### 【請求項11】

前記下部電極上への窒化膜の形成を、CVDチャンバ内で350~450 の温度で50~150sccmのNH $_3$ ガスを供給しつつ、プラズマを用いて1~10分間にわたり前記下部電極の表面に窒化膜を形成することにより行う請求項 9 記載の半導体素子のキャパシタ製造方法。

#### 【請求項12】

前記アモルファスTaON薄膜の形成を、 $160 \sim 190$  に保持された気化器におい<u>て原</u>料物質であるタンタルエチレート  $(Ta(OC_2H_5)_5)$  を気相状態とした後、 $0.2 \sim 0.4$ Torrの圧力及び35 $0 \sim 450$  の温度に保持され、かつ流量25  $\sim 200$ sccmの $0_2$ ガスが供給されるCVDチャンバ<u>に気相状態の前記原料物質を供給し、前記CVDチャンバ</u>内で、 $0_2$ と<u>前記</u>原料物質から得られるTa化学蒸気との表面化学反応により行う請求項9記載の半導体素子のキャパシタ製造方法。

# 【請求項13】

前記アモルファスTaON薄膜の結晶化工程を、流量10~1000sccmの $O_3$ ガスが注入されるCV Dチャンバ内で750~900 の温度で1~60分間熱処理することにより行う請求項 9 記載の半導体素子のキャパシタ製造方法。

#### 【請求項14】

10

20

30

40

前記アモルファスTaON薄膜の結晶化工程を、 $N_2$ Oおよび $O_3$ 雰囲気中750~900 の温度で3 0秒~1時間熱処理することにより行う請求項 9 記載の半導体素子のキャパシタ製造方法。

#### 【請求項15】

<u>結</u>晶化された<u>前記</u>TaON薄膜上に形成される上部電極が、TiON膜及びドーピングされたポリシリコン膜の積層構造を有しており、前記アモルファスTaON薄膜の結晶化工程において $0_3$ が注入された<u>前記CVDチャンバ内で形</u>成される請求項<u>13</u>記載の半導体素子のキャパシタ製造方法。

#### 【請求項16】

前記TiON膜を、前駆体であるTiCl $_4$ を流量調節器を介して蒸発器へ送給し、150~200の温度で蒸発させてTiN化学蒸気を得た後、前記TiN化学蒸気と流量10~1000sccmのNH $_3$ ガスとを $0_3$ が注入されたチャンバ内に供給して300~600 の温度で表面化学反応により形成する請求項9記載の半導体素子のキャパシタ製造方法。

【発明の詳細な説明】

[00001]

【発明の属する技術分野】

本発明は、半導体素子のキャパシタ製造方法に関し、より詳細には、誘電体膜内での酸素 空乏及び漏洩電流を抑制し得る半導体素子のキャパシタ製造方法に関する。

[0002]

【従来の技術】

近来、半導体製造技術の進歩に伴って、メモリ素子の需要が急増している。半導体装置において、データ蓄積手段に用いられるキャパシタは、電極の面積、電極間の距離および電極間に挿設される誘電膜の誘電率に依存して、そのキャパシタンスが変わる。

[00003]

しかしながら、半導体装置が次第に高集積化するに従って、半導体装置内のキャパシタ形成領域が減少しており、その結果、キャパシタの電極面積が小さくなって、キャパシタのキャパシタンスを低下させている。

[0004]

この様な問題を解消するために、高誘電率を有するTaON薄膜を備えたキャパシタが提案されている。このキャパシタにおいて、TaON薄膜は、金属膜-絶縁膜-シリコン構造(以下、「MIS」とする)を有しており、前記TaON薄膜上の上部電極としてTiN膜/ポリシリコン膜の積層構造が使用されている。

[0005]

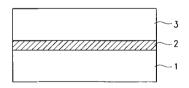

図1は、従来技術による半導体素子に関連して、TaON薄膜を備えたキャパシタの製造方法を示す断面図である。

[0006]

図1に示すように、従来の半導体素子のキャパシタ製造方法では、例えば、ポリシリコン膜からなる下部電極1上に高誘電率を有する薄膜のTaON膜2を蒸着する。

[0007]

次に、前記TaON薄膜 2 の上に積層構造を有するTiN / ポリシリコン膜 3 を蒸着により形成する。このTiN / ポリシリコン膜の蒸着操作においては、CVD チャンバ内で、前駆体である $TiCI_4$  と反応ガス $NH_3$  とを用いて、TiN 薄膜を形成し、MIS 構造のキャパシタを完成する。

[0008]

しかしながら、従来の半導体メモリ素子のキャパシタ製造方法には、次の問題がある。

[0009]

すなわち、従来技術においては、前記高誘電率を有するTaON薄膜の蒸着形成後に積層構造のTiN/ポリシリコン膜を形成するために、前駆体である $TiCI_4$ と反応ガスである $NH_3$ とを用いて、CVDチャンバ内でTiN薄膜を形成する過程において、前記CVDチャンバの温度が500付近でTiN膜とTaON薄膜との間で酸化反応が生じることがある。その結果、TaON薄膜中

付近でTIN膜とTaON薄膜との間で酸化反応か至しることがある。その結果、TaON薄膜中の酸素がTiN薄膜に移動して、TaON薄膜内に酸素空乏が生じるので、TaON薄膜を構成するキャパシタで、漏洩電流が増加することになる。

10

20

30

40

#### [0010]

### 【発明が解決しようとする課題】

本発明は、前述の様な従来技術の問題点に鑑みてなされたものであり、誘電体膜の特性劣化を防止するとともに漏洩電流の増加を抑制できる半導体素子のキャパシタ製造方法を提供することを主な目的とする。

#### [0011]

#### 【課題を解決するための手段】

本発明は、半導体基板上に導電性ポリシリコン膜または導電性アモルファスシリコン膜からなる下部電極を形成するステップと、前記下部電極上に窒化膜を形成するステップと、前記窒化膜上にアモルファスTaON薄膜を蒸着するステップと、前記アモルファスTaON薄膜を高温熱処理して結晶化させるステップと、前記結晶化されたTaON薄膜上に上部電極用TiON及びドーピングされたシリコン膜の積層構造を形成するステップとを含んでなることを特徴とする。

## [0012]

また、本発明は、半導体基板上に導電性ポリシリコン膜または導電性アモルファスシリコン膜からなる下部電極を形成するステップと、前記下部電極上に窒化膜を形成するステップと、前記室化膜上にアモルファスTaON薄膜を蒸着するステップと、前記アモルファスTaON薄膜をバッチ形態のファーネスまたは急速熱処理工程を用いて結晶化させるステップと、前記結晶化されたTaON薄膜上に上部電極用TiON及びドーピングされたシリコン膜の積層構造を形成するステップとを含んでなることを特徴とする。

#### [0013]

#### 【発明の実施の形態】

以下、本発明の好ましい実施態様の一例を示す添付図面を参照しつつ、本発明をさらに詳細に説明する。

#### [0014]

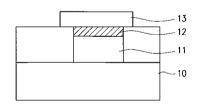

図2Aないし図2Fは、本発明による半導体素子のキャパシタ製造方法を説明するための 工程断面図である。

#### [0015]

先ず、図2Aに示すように、本発明に係る半導体素子のキャパシタ製造方法においては、周知の方法により、層間絶縁膜上のコンタクトホール(図示しない)内にプラグポリシリコン膜11とバリア金属膜12とが順次積層された構造を有する半導体基板10上に下部電極13を形成する。前記下部電極13は、シリンダー型構造或いはスタック型構造のいずれであっても良く、ポリシリコン膜またはMPS (Meta Poly Silicon)により形成されたアモルファスシリコン膜からなる。

# [0016]

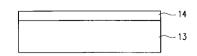

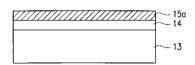

次に、前記下部電極 1 3 を拡大して示す図 2 B から明らかな様に、下部電極 1 3 上に薄膜の窒化膜 1 4 を形成する。前記下部電極 1 3 上への窒化膜 1 4 の形成は、CVD(chemical vapor deposition)チャンバ内において、300~450 程度(より好ましくは330~430 程度)の温度でNH<sub>3</sub>ガスを50~150sccm程度(より好ましくは60~130sccm程度)の定量を供給しながら、プラズマを用いて1~10分間程度(より好ましくは2~9分間程度)の時間をかけて、行う。前記窒化膜 1 4 は、後続の熱処理工程において、誘電体であるTaON薄膜(図示しない)と下部電極 1 3 との間に低誘電層であるSiO<sub>2</sub>が形成されることを抑える。

#### [0017]

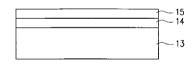

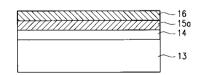

次に、図 2 C に示すように、前記室化膜 1 4 上に高誘電率を有するアモルファスTaON薄膜 1 5 を形成する。前記アモルファスTaON薄膜 1 5 は、インシトゥ方式によりCVDチャンバ内で蒸着形成させる。すなわち、原料物質である定量のタンタルエチレート  $(Ta(OC_2H_5)_5)$ を160~190 程度(より好ましくは165~185 程度)に保持された気化器内で気相状態として、 $0.2 \sim 0.4$ torr の低圧力及び350~450 程度(より好ましくは370~430 程度)の温度に保持され、流量25~200sccm程度(より好ましくは30~180sccm程度)の $0_2$ ガスを供給されるCVDチャンバに送給する。この様にして、CVDチャンバでは、原料物質であるタンタルエ

20

10

30

40

チレートと0っとの表面化学反応により、前記アモルファスTaON薄膜15が形成される。

### [0018]

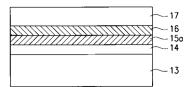

次に、図2Dに示すように、前記アモルファスTaON薄膜15の結合力を増加させ、漏洩電流を低減させ、TaON薄膜のわずかな収縮による誘電率を増加させるために、結晶化を行わせる。

#### [0019]

前記アモルファスTaON薄膜 1 5 の結晶化工程においては、10~1000sccm程度(より好ましくは30~900sccm程度)の流量で $0_3$ ガスが注入されたるVDチャンバ内で750~900 程度(より好ましくは770~860 程度)の温度で 1~60分間程度(より好ましくは3~55分間程度)熱処理を行って、結晶化されたTaON薄膜 1 5 a を形成させる。

#### [0020]

或いは、バッチ形態(batch type)のファーネス処理工程または急速熱処理(RTP)工程において、750~900 程度(より好ましくは770~860 程度)の温度で $N_2$ 0および $N_3$ 雰囲気で30秒~1時間程度(より好ましくは33~55秒間程度)熱処理を行うことにより結晶化されたTaON薄膜 1.5 a を形成することもできる。

#### [0021]

次に、図2 E に示すように、前記結晶化されたTaON薄膜 1 5 a 上に上部電極用金属膜であるTiON薄膜 1 6 を形成する。前記TiON薄膜 1 6 は、インシトゥ方式により、前記TaON薄膜の結晶化工程において、 $O_3$ が注入されたCVDチャンパー内で形成することができる。

## [0022]

或いは、前記TiON薄膜 1 6 は、流量調節器を介して、前駆体であるTiCl $_4$ の一定量を蒸発器へ送給し、150~200 程度(より好ましくは155~190 程度)の温度で蒸発させてTiN化学蒸気を得た後、前記TiN化学蒸気と流量10~1000sccm程度(より好ましくは30~900sccm程度)のNH $_3$ ガスとを、 $O_3$ が注入されたチャンバ内に供給して、300~600 程度(より好ましくは350~550 程度)の温度で表面化学反応により、TiON薄膜 1 6を形成することもできる。

#### [0023]

次に、図2Fに示すように、前記TiON薄膜16上にドーピングされたポリシリコン膜17 を蒸着して、TiON薄膜16とドーピングされたポリシリコン膜17とからなる上部電極を 形成して、半導体素子のキャパシタを完成する。

#### [0024]

本発明は、前記実施の形態により限定されるものではなく、その趣旨の範囲内で各種の変形乃至改良が可能である。

### [0025]

#### 【発明の効果】

前述のように、本発明にかかる半導体素子の製造方法によれば、次のような効果が達成できる。

#### [0026]

まず、本発明によれば、前記アモルファスTaON薄膜を結晶化させることにより、その結合力の強化及び漏洩電流の低減ならびにTaON薄膜の収縮による誘電率の増大が実現される。

## [0027]

また、反応性に優れた $0_3$ ガスを使用して、上部電極上にTiON薄膜を形成するので、従来技術において上部電極として使用されているTiN膜とTaON 薄膜との酸化反応による $TiO_2$ 層の形成を防止し、かつTaON膜の酸素空乏に起因する特性劣化及び漏洩電流を抑制して、TaON 薄膜キャパシタの電気的特性を向上させることができる。

## [0028]

さらに、前記アモルファスTaON膜の高温熱処理を $O_3$ が注入されたCVDチャンバ内で行って、インシトゥ方式により前記TiON薄膜を形成するので、工程が簡略化され、コストダウンが達成される。

#### 【図面の簡単な説明】

10

20

30

40

10

20

- 【図1】従来技術による半導体素子のキャパシタ製造方法を示すための断面図である。

- 【図2A】本発明による半導体素子のキャパシタ製造方法の第一段階を説明するための工程断面図である。

- 【図2B】本発明による半導体素子のキャパシタ製造方法の第二段階を説明するための工程断面図である。

- 【図2C】本発明による半導体素子のキャパシタ製造方法の第三段階を説明するための工程断面図である。

- 【図2D】本発明による半導体素子のキャパシタ製造方法の第四段階を説明するための工程断面図である。

- 【図2E】本発明による半導体素子のキャパシタ製造方法の第五段階を説明するための工程断面図である。

- 【図2F】本発明による半導体素子のキャパシタ製造方法の最終段階を説明するための工程断面図である。

## 【符号の説明】

- 1 下部電極

- 2 、 1 5 TaON薄膜

- 3 TiN/ポリシリコン膜

- 10 半導体基板

- 1 1 プラグポリシリコン膜

- 1 2 金属膜

- 13 下部電極

- 1 4 室化膜

- 16 TiON薄膜

- 17 ポリシリコン膜

### 【図1】

# 【図2A】

## 【図2B】

## 【図2C】

## 【図2D】

# 【図2E】

# 【図2F】

#### フロントページの続き

(74)代理人 100090066

弁理士 中川 博司

(74)代理人 100094101

弁理士 舘 泰光

(74)代理人 100099988

弁理士 斎藤 健治

(74)代理人 100105821

弁理士 藤井 淳

(74)代理人 100099911

弁理士 関 仁士

(74)代理人 100108084

弁理士 中野 睦子

(74)代理人 100114616

弁理士 眞下 晋一

(74)代理人 100096080

弁理士 井内 龍二

(72)発明者 韓 勝 奎

大韓民国ソウル江南區三成洞サンガアパートメント7 - 101

(72) 発明者 朴 東 洙

大韓民国京畿道利川市創前洞410-7ユジンヴィラ201號

## 審査官 粟野 正明

(56)参考文献 特開平05-167008(JP,A)

米国特許第05677015(US,A)

特開2000-058878(JP,A)

特開平07-263431(JP,A)

特開平07-263442(JP,A)

特開平11-074458(JP,A)

米国特許第06201276(US,B1)

特開平09-246477(JP,A)

特開2000-100806(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/8242

H01L 21/822

H01L 27/04

H01L 27/108

H01L 21/316

H01L 21/318