### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4756302号 (P4756302)

(45) 発行日 平成23年8月24日(2011.8.24)

(24) 登録日 平成23年6月10日(2011.6.10)

| (51) Int.Cl. | F I                          |            |                        |

|--------------|------------------------------|------------|------------------------|

| GO1R 19/00   | ( <b>2006.01</b> ) GO1R      | 19/00      | U                      |

| B60L 11/18   | ( <b>2006.01</b> ) GO1R      | 19/00      | В                      |

| GO1R 31/36   | <b>(2006.01)</b> B60L        | 11/18      | G                      |

| HO1M 10/48   | <b>(2006.01)</b> GO1R        | 31/36      | A                      |

| HO2J 7/00    | <b>(2006.01)</b> HO1M        | 10/48      | P                      |

|              |                              |            | 請求項の数 4 (全 9 頁) 最終頁に続く |

| (21) 出願番号    | 特願2001-289148 (P2001-289148) | (73) 特許権者  | <b>皆</b> 000004260     |

| (22) 出願日     | 平成13年9月21日 (2001.9.21)       |            | 株式会社デンソー               |

| (65) 公開番号    | 特開2003-14792 (P2003-14792A)  |            | 愛知県刈谷市昭和町1丁目1番地        |

| (43) 公開日     | 平成15年1月15日 (2003.1.15)       | (74) 代理人   | 100081776              |

| 審査請求日        | 平成19年10月9日 (2007.10.9)       |            | 弁理士 大川 宏               |

| (31) 優先権主張番号 | 特願2001-131940 (P2001-131940) | (72) 発明者   | 藤田 浩                   |

| (32) 優先日     | 平成13年4月27日 (2001.4.27)       |            | 愛知県刈谷市昭和町1丁目1番地 株式会    |

| (33) 優先権主張国  | 日本国(JP)                      |            | 社デンソー内                 |

|              |                              | (72) 発明者   | 小林 徹也                  |

|              |                              |            | 愛知県刈谷市昭和町1丁目1番地 株式会    |

|              |                              |            | 社デンソー内                 |

|              |                              | <br>   審査官 | 武田 知晋                  |

|              |                              |            | 最終頁に続く                 |

(54) 【発明の名称】フライングキャパシタ式組電池電圧検出装置

# (57)【特許請求の範囲】

# 【請求項1】

3以上のフライングキャパシタと、

互いに直列接続された多数の電池モジュールからなる組電池の各電極端子を所定の前記 フライングキャパシタの両端に順次接続して前記各電池モジュールの電圧を前記各フライ ングキャパシタに順次印加するマルチプレクサと、

一対の入力端子間の電位差を検出する差動電圧検出回路と、

前記各フライングキャパシタの蓄電電圧を前記差動電圧検出回路の前記一対の入力端子 間に順番に印加する出力側サンプリングスイッチと、

を備え、

10

前記3以上のフライングキャパシタのうち一つの前記フライングキャパシタが前記差動 増幅回路に蓄電電圧を読み出す電圧読み出し期間に設定され且つ他の一つの前記フライン グキャパシタが前記電池モジュールから電圧を読み込む電圧読み込み期間に設定されてい る所定期間の少なくとも一部において、残りの前記フライングキャパシタが電圧読み出し も電圧読み込みもしていないアイドル期間に設定されることを特徴とするフライングキャ パシタ式組電池電圧検出装置。

# 【請求項2】

請求項1記載のフライングキャパシタ式組電池電圧検出装置において、

前記フライングキャパシタの数は3であり、前記電圧読み出し期間と前記電圧読み込み 期間とアイドル期間との長さの比は、2:5:2であることを特徴とするフライングキャ パシタ式組電池電圧検出装置。

### 【請求項3】

請求項1<u>または2</u>記載のフライングキャパシタ式組電池電圧検出装置において、 前記差動電圧検出回路の前記一対の入力端間を短絡するリセットスイッチを有すること を特徴とするフライングキャパシタ式組電池電圧検出装置。

#### 【請求項4】

請求項1<u>から3のいずれか1項</u>記載のフライングキャパシタ式組電池電圧検出装置において、

前記各フライングキャパシタの前記電圧読み出し期間は、それぞれ等しく設定され、かつ、それぞれ等しい時間だけずれており、

前記各フライングキャパシタの前記電圧読み出し期間は、前記電圧読み込み期間の直後に設定され、かつ、次の前記フライングキャパシタの前記電圧読み出し期間の開始前に終了することを特徴とするフライングキャパシタ式組電池電圧検出装置。

#### 【発明の詳細な説明】

#### [0001]

### 【発明の属する技術分野】

本発明は、フライングキャパシタ式組電池電圧検出装置に関し、特に車両用組電池に用いるフライングキャパシタ式組電池電圧検出装置に関する。

#### [00002]

# 【従来の技術】

たとえばハイブリッド自動車や電気自動車、燃料電池車などでは、二次電池や燃料電池からなる組電池は互いに直列接続した多数の電池モジュールにより構成され、電池モジュールは所定数の単電池を直列接続して構成されている。

#### [0003]

各電池モジュールの電位が高くかつそれぞれ異なるために、各電池モジュールの電圧計測は、各電池モジュールを出力側の差動電圧検出回路の基準電位から絶縁可能なフライングキャパシタ式組電池電圧検出装置が好適である。

#### [0004]

## 【発明が解決しようとする課題】

しかしながら、各電池モジュールごとに電圧検出回路を装備することは装置の大規模化を招くとともに、各差動電圧検出回路間のオフセット誤差や電圧増幅率誤差も補償する必要があるため、マルチプレクサを用いて各電池モジュール電圧を時間順次にサンプリングして共通のフライングキャパシタに読み込むことによりフライングキャパシタや差動電圧検出回路の必要個数を低減したマルチプレクサ付きフライングキャパシタ式組電池電圧検出装置が好適な回路構成となる。

## [0005]

しかしながら、このマルチプレクサ付きフライングキャパシタ式組電池電圧検出装置によれば、全ての電池モジュール電圧を計測するのに必要な全計測時間は、各電池モジュールの電圧を差動電圧検出回路で検出する時間(モジュール電圧計測時間)の総和となる。このため、最初の電池モジュールの計測時点と、最後の電池モジュールの計測時点との間にかなるの時間が経過するため、この間に、充放電している組電池の状態が変化し、正確な組電池状態が計測できないという問題があった。

## [0006]

この問題は、フライングキャパシタのモジュール電圧読み込み、読み出し過程が本質的にコンデンサのCR充放電過程であり、その検出精度を向上するには時間を掛ける必要があるという点により一層助長される。

#### [0007]

本発明は、上記問題点に鑑みなされたものであり、回路構成の複雑化を抑止しつつ、組電池電圧の計測時間の短縮を実現可能なフライングキャパシタ式組電池電圧検出装置を提供することを、その目的としている。

10

20

30

40

## [0008]

## 【課題を解決するための手段】

本発明のフライングキャパシタ式組電池電圧検出装置は、<u>3以上</u>のフライングキャパシタと、互いに直列接続された多数の電池モジュールからなる組電池の各電極端子を所定の前記フライングキャパシタの両端に順次接続して前記各電池モジュールの電圧を前記各フライングキャパシタに順次印加するマルチプレクサと、一対の入力端子間の電位差を検出する差動電圧検出回路と、前記各フライングキャパシタの蓄電電圧を前記差動電圧検出回路の前記一対の入力端子間に順番に印加する出力側サンプリングスイッチとを備え、<u>前記3以上のフライングキャパシタのうち一つの前記フライングキャパシタが前記差動増幅回路に蓄電電圧を読み出す電圧読み出し期間に設定され且つ他の一つの前記フライングキャパシタが前記電池モジュールから電圧を読み込む電圧読み込み期間に設定されている所定期間の少なくとも一部において、残りの前記フライングキャパシタが電圧読み出しも電圧 読み込みもしていないアイドル期間に設定されることを特徴としている。</u>

#### [0009]

本構成によれば、回路構成の複雑化を抑止しつつ、組電池電圧の計測時間の短縮を実現することができる。フライングキャパシタ<u>の3つについて</u>以下に説明する。この場合、ある一つの電池モジュールから第一のフライングキャパシタにモジュール電圧を読み込む電圧読み込み期間は、第二のフライングキャパシタから差動電圧検出回路に蓄電電圧を読み出す電圧読み出し期間と<u>少なくとも一部</u>オーバーラップし、第三のフライングキャパシタからがら差動電圧検出回路に蓄電電圧を読み出す電圧読み出し期間と少なくとも一部オーバーラップしている。また、他の電池モジュールから第二のフライングキャパシタにモジュール電圧を読み込む電圧読み込み期間は、第一のフライングキャパシタから差動電圧検出回路に蓄電電圧を読み出す電圧読み出し期間と<u>少なくとも一部</u>オーバーラップし、第三のフライングキャパシタから差動電圧検出回路に蓄電電圧を読み出す電圧読み出し期間と

#### [0010]

好適な<u>態様</u>において、<u>フライングキャパシタの数は3であり、前記電圧読み出し期間と</u>前記電圧読み込み期間とアイドル期間との長さの比は、2:5:2とすることができる。

### [0013]

好適な態様においてにおいて更に、前記差動電圧検出回路の前記一対の入力端間を短絡するリセットスイッチを有することを特徴としているので、フライングキャパシタの蓄電電圧を差動電圧検出回路に読み込んだ後、差動電圧検出回路の入力端寄生容量やフライングキャパシタの蓄電電荷の消去を高速化するので、電圧読み出し期間に含まれる上記蓄電電荷消去時間を短縮して、全体としての電圧読み出し期間を短縮することができる。

# [0014]

なお、本構成では、リセットスイッチは、出力側サンプリングスイッチをオフし、差動電圧検出回路が信号電圧を出力した後でオンされることができる他、差動電圧検出回路が信号電圧を出力した後で、出力側サンプリングスイッチをオンした状態でリセットスイッチをオンしてフライングキャパシタの蓄電電荷を消去することも可能である。

#### [0015]

また、差動電圧検出回路の出力電圧は A / D コンバータにより所定タイミングにてサンプリングされて A / D 変換されることが好適であるが、この A / D コンバータのサンプリングタイミングは出力側サンプリングスイッチのオン期間の後期に設定されてもよく、出力側サンプリングスイッチのオフ後に設定されてもよい。

#### [0018]

<u>好適な態様において</u>更に、前記各フライングキャパシタの前記電圧読み込み期間は、それぞれ等しく設定され、かつ、それぞれ等しい時間だけずれており、前記各フライングキャパシタの前記電圧読み出し期間は、前記電圧読み込み期間の直後に設定され、かつ、次の前記フライングキャパシタの前記電圧読み出しの開始前に終了することを特徴としている。

10

20

30

40

#### [0019]

本構成によれば、各フライングキャパシタに順次読み込まれた蓄電電圧を互いにオーバーラップすることなく、一つの差動増幅回路に順次読み込むことが可能となる。また、各サンプリングスイッチの駆動信号及び差動増幅回路の出力電圧をサンプリングする A / Dコンバーターのサンプリングスイッチを単純化なクロックパルス信号で駆動することができ。回路構成及びその駆動を簡素化し、サンプリングレートの向上が容易となる。

#### [0020]

### 【発明の実施の形態】

以下、本発明のフライングキャパシタ式組電池電圧検出装置の好適な態様を以下の実施例により詳細に説明する。ただし、本発明は下記の実施例の構成に限定されるものではなく、置換可能な公知回路を用いて構成できることは当然である。

# 10

#### [0021]

#### 【実施例1】

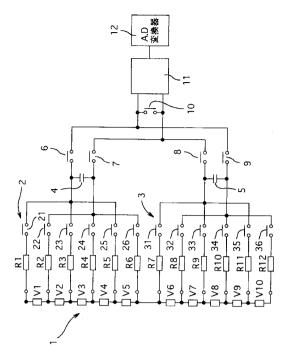

本発明を適用する組電池の電圧検出装置の一実施例を図1に示す回路図を参照して説明する。

### (回路構成)

組電池1は、2つの電池ブロックを構成している電池モジュールV1~V10を直列接続してなる。各電池モジュールV1~V10はそれぞれ等しい数の単電池を直列接続してなる。R1~R12は保護用の電流制限抵抗素子、2、3はマルチプレクサ、4、5はフライングキャパシタ、6~9は出力側サンプリングスイッチ、10はリセットスイッチ、11は差動電圧検出回路、12はA/Dコンバータである。

# 20

#### [0022]

マルチプレクサ2は、互いに異なる電流制限抵抗素子R1~R6を通じて高電位側の電池プロックを構成する電池モジュールV1~V5の各電極端子に個別に接続される合計6個のサンプリングスイッチ21~26を有している。更に詳しく説明すると、フライングキャパシタ4の一端は、サンプリングスイッチ21、23、25及び電流制限抵抗素子R1、R3、R5の各対を通じて電池モジュールV1、V3、V5の正極端子に接続され、フライングキャパシタ4の他端は、サンプリングスイッチ22、24、26及び電流制限抵抗素子R2、R4、R6の各対を通じて電池モジュールV1、V3、V5の負極端子に接続されている。

#### 30

#### [0023]

マルチプレクサ3は、互いに異なる電流制限抵抗素子R7~R12を通じて低電位側の電池プロックを構成する電池モジュールV6~V10の各電極端子に個別に接続される合計6個のサンプリングスイッチ31~36を有している。更に詳しく説明すると、フライングキャパシタ5の一端は、サンプリングスイッチ31、33、35及び電流制限抵抗素子R7、R9、R11の各対を通じて電池モジュールV6、V8、V10の正極端子に接続され、フライングキャパシタ5の他端は、サンプリングスイッチ32、34、36及び電流制限抵抗素子R8、R10、R12の各対を通じて電池モジュールV6、V8、V10の負極端子に接続されている。

### [0024]

40

50

出力側サンプリングスイッチ6、7は、フライングキャパシタ4の両端を差動電圧検出回路11の一対の入力端に接続し、出力側サンプリングスイッチ8、9は、フライングキャパシタ5の両端を差動電圧検出回路11の上記一対の入力端に接続している。

## [0025]

リセットスイッチ 1 0 は、差動電圧検出回路 1 1 の一対の入力端を短絡可能に接続され、 差動電圧検出回路 1 1 の出力電圧は A / D コンバータ 1 2 に所定のタイミングで読み込まれてデジタル信号に変換される。

## [0026]

# (動作説明)

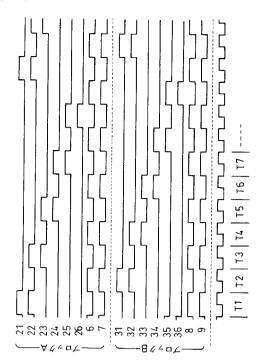

次に、この回路による電池モジュールV1~V10の電圧検出動作を以下に説明する。ま

た、各サンプリングスイッチの動作タイミングを図2に示す。

## [0027]

最初の第一期間T1において、サンプリングスイッチ21、22、出力側サンプリングスイッチ8、9をオンするとともに、サンプリングスイッチ35、36、出力側サンプリングスイッチ6、7をオフし、電池モジュールV1をフライングキャパシタ4に読み込むとともに、フライングキャパシタ5の蓄電電圧を差動電圧検出回路11に読み出す。この第一期間T1の後半において、リセットスイッチ10をオンし、フライングキャパシタ5や寄生容量の蓄電電荷を消去する。A/Dコンバータ12の信号電圧取り込みはこの第一期間T1内の前半のなるべく後期、すなわち、リセットスイッチ10のオン直前に実施される。

[0028]

次の第二期間T2において、サンプリングスイッチ31、32、出力側サンプリングスイッチ6、7をオンするとともに、サンプリングスイッチ21、22、出力側サンプリングスイッチ8、9をオフし、電池モジュールV6をフライングキャパシタ5に読み込むとともに、フライングキャパシタ4の蓄電電圧を差動電圧検出回路11に読み出す。この第一期間T2の後半において、リセットスイッチ10をオンし、フライングキャパシタ4や寄生容量の蓄電電荷を消去する。A/Dコンバータ12の信号電圧取り込みはこの第二期間T2内の前半のなるべく後期、すなわち、リセットスイッチ10のオン直前に実施される。

[0029]

次の第三期間T3において、サンプリングスイッチ22、23、出力側サンプリングスイッチ8、9をオン<u>するとともに、サンプリングスイッチ31、32、出力側サンプリングスイッチ6、7をオフし、</u>電池モジュールV2をフライングキャパシタ4に読み込むとともに、フライングキャパシタ5の蓄電電圧を差動電圧検出回路11に読み出す。この第三期間T3の後半において、リセットスイッチ10をオンし、フライングキャパシタ5や寄生容量の蓄電電荷を消去する。A/Dコンバータ12の信号電圧取り込みはこの第三期間T3内の前半のなるべく後期、すなわち、リセットスイッチ10のオン直前に実施される。

[0030]

次の第四期間T4において、サンプリングスイッチ32、33、出力側サンプリングスイッチ6、7をオン<u>するとともに、サンプリングスイッチ22、23、出力側サンプリングスイッチ8、9をオフし、</u>電池モジュールV7をフライングキャパシタ5に読み込むとともに、フライングキャパシタ4の蓄電電圧を差動電圧検出回路11に読み出す。この第四期間T4の後半において、リセットスイッチ10をオンし、フライングキャパシタ4や寄生容量の蓄電電荷を消去する。A/Dコンバータ12の信号電圧取り込みはこの第四期間T4内の前半のなるべく後期、すなわち、リセットスイッチ10のオン直前に実施される。

[0031]

以下、同様に、各電池モジュールのモジュール電圧をA/D変換する。

[0032]

本実施例によれば、一対のフライングキャパシタの<u>一方のフライングキャパシタの</u>モジュール電圧読み込み期間と<u>他方のフライングキャパシタの</u>蓄電電圧読みだし期間とがほぼ完全にオーバーラップしているので、差動電圧検出回路を複数化することなく計測時間を短縮することができる。

[0033]

更に、図2に示すように、マルチプレクサ2,3のサンプリングスイッチ駆動用のパルス電圧と、出力側サンプリングスイッチ6~9を駆動するパルス電圧を同時タイミングで電位遷移させているので、制御パルス発生回路を簡素化するとともに、A/Dコンバータの電圧取り込み期間にこれらパルス電圧が変化してノイズとなることを防止することができる。

10

20

30

#### [0034]

#### (変形態様)

上記実施例では、リセットスイッチ10を用いたが、放電抵抗により差動電圧検出回路11の一対の入力端間の電圧を消去してもよい。

#### [0035]

## (変形態様)

マルチプレクサの構成は、この実施例の回路に限定されるものではなく、組電池 1 の各電池モジュールのモジュール電圧を順番にフライングキャパシタ 4 、 5 に取り込めるものであれば、他の回路構成でもよいことはもちろんである。

### [0036]

10

20

30

40

## 【実施例2】

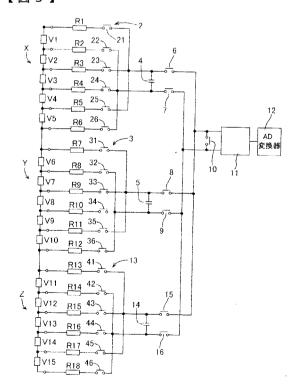

本発明を適用する組電池の電圧検出装置の一実施例を図3に示す回路図、及びその動作タイミングを示す図4のタイミングチャートを参照して説明する。

## [0037]

この実施例は、図1において更に、電池モジュール V1~V5により構成される高電位側の電池ブロック X、及び、電池モジュール V6~V10により構成される低電位側の電池ブロック Yの他に、上記2つの電池ブロックと直列に接続された第三の電池ブロック Zを組電池1に設け、電池ブロック Zを構成する電池モジュール V11~V15の電圧を順次サンプリングするマルチプレクサ13を設け、マルチプレクサ13の出力電圧を蓄電する第三のフライングキャパシタ14を設け、第三のフライングキャパシタ14の蓄電電圧を読み出す出力側サンプリングスイッチ15、16を設けたものである。R13~R18は保護用の電流制限抵抗素子である。マルチプレクサ13は、互いに異なる電流制限抵抗素子R13~R18を通じて高電池モジュールで11~V15の各電極端子に個別に接続される合計6個のサンプリングスイッチ41~46を有している。

#### [0038]

(動作説明)

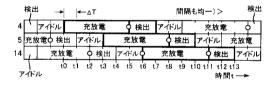

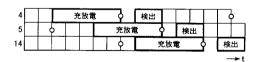

次に、この回路による電池モジュールV1~V15の電圧検出動作を図4に示す。

#### [0039]

図4中、「充放電」と記載された期間は、入力側サンプリングスイッチ対を動作させて電池モジュールからフライングキャパシタに電圧を読み込む電圧読み込み期間、「検出」と記載された期間は出力側サンプリングスイッチ対を動作させてフライングキャパシタから差動増幅回路11に蓄電電圧を読み出す電圧読み出し期間、「アイドル」と記載された電圧読み出し期間でも電圧読み込み期間でもない期間である。

#### [0040]

図4では、各サンプリングスイッチの動作タイミングは、クロックパルスにより決定される時点 t0~t13中の特定のタイミングで行われ、当然、各時点 t0~t13間は一定期間 t1に設定されている。

#### [0041]

「充放電」期間すなわち電圧読み込み期間は5 Tの時間幅、「検出」期間すなわち電圧 読み出し期間は2 Tの時間幅、「アイドル」期間も2 Tの時間幅に設定され、フライングキャパシタ4、5、14の電圧読み込み期間同士は3 Tだけずれて配置されている。このようにすれば、各「検出」期間すなわち電圧読み出し期間が重なることがなく、かつ、各スイッチの動作間隔が均一であるので、制御が容易となり、ADコンバータ12による信号処理も簡単となり、回路構成も簡素化することができる。なお、各「検出」期間が時間的に重複しない範囲で、アイドル期間の伸縮は可能である。

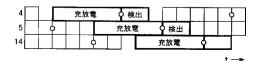

## [0042]

図5~図7に比較例を示す。これらの図の「充放電」期間や「検出」期間の配置では、「 検出」期間が時間的に重複したり、各間隔が不均一となって処理が面倒となったりする不 具合が生じる。

## (変形態様)

なお、 A D コンバータ 1 0 において各「検出」期間ごとに得られる電池モジュール電圧に対して電池モジュール総数に相当する数を掛けて組電池電圧とすることができる。もちろん、この場合、各電池モジュール電圧のばらつきに起因して組電池電圧が時間的に変動する不具合が発生する。

## [0043]

しかし、実施例 2 のように、一定の時間間隔で電池モジュール電圧をサンプリングする場合、上記のようにして得た組電池電圧の低域成分を抽出すれば、各電池モジュール電圧の平均電圧を抽出することができ、簡素な回路により簡単に組電池電圧を得ることができる

# 【図面の簡単な説明】

【図1】実施例1のフライングキャパシタ式組電池電圧検出装置を示す回路図である。

- 【図2】図1のフライングキャパシタ式組電池電圧検出装置の各スイッチの動作タイミングを示すタイミングチャートである。

- 【図3】実施例2のフライングキャパシタ式組電池電圧検出装置を示す回路図である。

- 【図4】図3のフライングキャパシタ式組電池電圧検出装置の各スイッチの動作タイミングを示すタイミングチャートである。

- 【図5】比較例のフライングキャパシタ式組電池電圧検出装置の各スイッチの動作タイミングを示すタイミングチャートである。

- 【図 6 】比較例のフライングキャパシタ式組電池電圧検出装置の各スイッチの動作タイミングを示すタイミングチャートである。

- 【図7】比較例のフライングキャパシタ式組電池電圧検出装置の各スイッチの動作タイミングを示すタイミングチャートである。

#### 【符号の説明】

- 1 組電池

- 2、3 マルチプレクサ

- 4、5 フライングキャパシタ

- 6~9 出力側サンプリングスイッチ

- 10 リセットスイッチ

- 11 差動電圧検出回路

- 12 A/Dコンバータ

20

10

【図1】

【図2】

【図3】

【図4】

【図5】

| フラインク キャハ・シタ | 4       |   | 充放電 🤇 |     |  |      |  | þ           |

|--------------|---------|---|-------|-----|--|------|--|-------------|

| フライング・キャバ・シタ | 5<br>14 | Ą |       | 充放電 |  | ♦ 検出 |  |             |

| フライングキャパシタ   |         |   |       | φ   |  | 充放電  |  | <b>夕</b> 検出 |

【図6】

【図7】

# フロントページの続き

(51) Int.CI. F I

**H 0 2 J 7/02 (2006.01)** H 0 2 J 7/00 3 0 2 C H 0 2 J 7/02 H

(56)参考文献 特開平09-001617(JP,A)

特開2000-171532(JP,A) 特開2000-184611(JP,A)

(58)調査した分野(Int.CI., DB名)

G01R 19/00

B60L 11/18

G01R 31/36

H01M 10/48

H02J 7/00

H02J 7/02