### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4901325号 (P4901325)

(45) 発行日 平成24年3月21日(2012.3.21)

(24) 登録日 平成24年1月13日(2012.1.13)

| (51) Int.Cl.  | F 1                            |                          |

|---------------|--------------------------------|--------------------------|

| HO1L 27/115   | <b>(2006.01)</b> HO1L          | <i>2</i> 27/10 4 3 4     |

| HO1L 21/824   | <b>7 <i>(2006.01)</i></b> HO1L | 29/78 3 7 1              |

| HO1L 29/788   | ( <b>2006.01)</b> G11C         | C 17/00 623B             |

| HO1L 29/792   | <b>(2006.01)</b> HO1L          | <u>27/10 481</u>         |

| G 1 1 C 16/04 | ( <b>2006.01</b> ) HO1L        | <u>27/10 461</u>         |

|               |                                | 請求項の数 25 (全 51 頁) 最終頁に続く |

| (21) 出願番号     | 特願2006-172115 (P2006-172115)   | (73) 特許権者 302062931      |

| (22) 出願日      | 平成18年6月22日 (2006. 6. 22)       | ルネサスエレクトロニクス株式会社         |

| (65) 公開番号     | 特開2008-4718 (P2008-4718A)      | 神奈川県川崎市中原区下沼部1753番地      |

| (43) 公開日      | 平成20年1月10日 (2008.1.10)         | (74) 代理人 100080001       |

| 審査請求日         | 平成21年6月11日 (2009.6.11)         | 弁理士 筒井 大和                |

|               |                                | (72) 発明者    志波    和佳     |

|               |                                | 東京都千代田区丸の内二丁目4番1号 株      |

|               |                                | 式会社ルネサステクノロジ内            |

|               |                                | (72) 発明者   岡 保志          |

|               |                                | 東京都千代田区丸の内二丁目4番1号 株      |

|               |                                | 式会社ルネサステクノロジ内            |

|               |                                | 審査官 須原 宏光                |

|               |                                |                          |

|               |                                | 最終頁に続く                   |

## (54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

## 【請求項1】

第1主面およびその裏側の第2主面を有する半導体基板と、

前記半導体基板の第1主面に配置された主回路形成領域と、

前記半導体基板の第1主面に配置された不揮発性メモリ領域とを備え、

前記不揮発性メモリ領域には、

前記半導体基板の第1主面に形成された第1導電型の第1ウエルと、

前記第1導電型とは反対の導電型を有する第2導電型のウエルであって、前記第1ウエルに内包されるように配置された第2ウエルと、

前記第 2 導電型のウエルであって、前記第 2 ウエルとは電気的に分離された状態で、前記第 1 ウエルに内包されるように配置された第 3 ウエルと、

前記第 2 導電型のウエルであって、前記第 2 ウエルおよび前記第 3 ウエルとは電気的に分離された状態で、前記第 2 ウエルと前記第 3 ウエルとの間に、前記第 1 ウエルに内包されるように配置された第 4 ウエルと、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように配置された不揮発性メモリセルとを備え、

前記不揮発性メモリセルは、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように第1方向に延在して配置された浮遊ゲート電極と、

前記浮遊ゲート電極が前記第4ウエルに平面的に重なる第1位置に形成された容量素子

٤,

前記浮遊ゲート電極が前記第3ウエルに平面的に重なる第2位置に形成されたデータ読み出し用の電界効果トランジスタと、

前記浮遊ゲート電極が前記第2ウエルに平面的に重なる第3位置に形成されたデータ書き込みおよび消去用の素子とを有し、

前記浮遊ゲート電極は、

前記第4ウエルに平面的に重なる第1部分と、

前記第1部分の第1の辺から前記第1方向に沿って前記データ読み出し用の電界効果トランジスタに向かって延びる第2部分と、

前記第1部分の前記第1の辺に沿う第2の辺から前記第1方向に沿って前記データ書き込みおよび消去用の素子に向かって延びる第3部分とを一体的に有しており、

前記第1部分は、前記第2部分と前記第3部分との間に設けられ、

前記第2部分および前記第3部分は、前記第1方向に交差する第2方向に沿って互いにずれた状態で設けられ、

前記容量素子は、

前記浮遊ゲート電極の前記第1部分の前記第1位置に形成される第1電極と、前記第1電極および前記半導体基板の間に形成される第1絶縁膜と、前記第4ウエル内に形成される第2導電型の半導体領域と、前記第4ウエルとを有し、

前記データ読み出し用の電界効果トランジスタは、

前記浮遊ゲート電極の前記第2部分の前記第2位置に形成される第2電極と、前記第2電極および前記半導体基板の間に形成される第2絶縁膜と、前記第3ウエル内において前記第2電極を挟み込む位置に形成された第1導電型の一対の半導体領域とを有し、

前記データ書き込みおよび消去用の素子は、

前記浮遊ゲート電極の前記第3部分の前記第3位置に形成される第3電極と、前記第3電極および前記半導体基板の間に形成される第3絶縁膜と、前記第2ウエル内に形成される第2導電型の半導体領域と、前記第2ウエルとを有することを特徴とする半導体装置。

#### 【請求頃2】

請求項1記載の半導体装置において、前記データ書き込みおよび消去用の素子でのデータの書き換えは、チャネル全面のFNトンネル電流により行うことを特徴とする半導体装置。

【請求項3】

請求項1記載の半導体装置において、前記浮遊ゲート電極の前記第1電極の前記第2方向の長さは、前記第2電極および前記第3電極の前記第2方向の長さよりも長いことを特徴とする半導体装置。

## 【請求項4】

請求項1記載の半導体装置において、前記データ書き込みおよび消去用の素子の前記第3電極の前記第2方向の長さと、前記データ読み出し用の電界効果トランジスタの前記第2電極の前記第2方向の長さとが異なることを特徴とする半導体装置。

## 【請求項5】

請求項4記載の半導体装置において、前記データ書き込みおよび消去用の素子の前記第3電極の前記第2方向の長さは、前記データ読み出し用の電界効果トランジスタの前記第2電極の前記第2方向の長さよりも短いことを特徴とする半導体装置。

### 【請求項6】

請求項1記載の半導体装置において、前記主回路形成領域には、第1動作電圧で駆動する低耐圧の電界効果トランジスタと、前記第1動作電圧よりも高い第2動作電圧で駆動する高耐圧の電界効果トランジスタとが配置されており、

前記データ読み出し用の電界効果トランジスタの前記一対の半導体領域の構成を、前記低耐圧の電界効果トランジスタのソース、ドレイン用の一対の半導体領域の構成と同一にしたことを特徴とする半導体装置。

### 【請求項7】

10

20

30

40

請求項1記載の半導体装置において、前記容量素子は、前記第4ウエル内に形成される 第1導電型の半導体領域を有することを特徴とする半導体装置。

#### 【請求項8】

請求項1記載の半導体装置において、前記データ書き込みおよび消去用の素子は、前記第2ウエル内に形成される第1導電型の半導体領域を有することを特徴とする半導体装置

### 【請求項9】

第1主面およびその裏側の第2主面を有する半導体基板と、

前記半導体基板の第1主面に配置された主回路形成領域と、

前記半導体基板の第1主面に配置された不揮発性メモリ領域とを備え、

前記不揮発性メモリ領域には、

前記半導体基板の第1主面に形成された第1導電型の第1ウエルと、

前記第1導電型とは反対の導電型を有する第2導電型のウエルであって、前記第1ウエルに内包されるように配置された第2ウエルと、

前記第2導電型のウエルであって、前記第2ウエルとは電気的に分離された状態で、前記第1ウエルに内包されるように配置された第3ウエルと、

前記第2導電型のウエルであって、前記第2ウエルおよび前記第3ウエルとは電気的に分離された状態で、前記第2ウエルと前記第3ウエルとの間に、前記第1ウエルに内包されるように配置された第4ウエルと、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように配置された複数の不揮発性メモリセルとを備え、

前記複数の不揮発性メモリセルの各々は、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように第1方向に延在して配置された浮遊ゲート電極と、

前記浮遊ゲート電極が前記第4ウエルに平面的に重なる第1位置に形成された容量素子と、

前記浮遊ゲート電極が前記第3ウエルに平面的に重なる第2位置に形成されたデータ読み出し用の電界効果トランジスタと、

前記浮遊ゲート電極が前記第2ウエルに平面的に重なる第3位置に形成されたデータ書き込みおよび消去用の素子とを有し、

前記浮遊ゲート電極は、

前記第4ウエルに平面的に重なる第1部分と、

前記第1部分の第1の辺から前記第1方向に沿って前記データ読み出し用の電界効果トランジスタに向かって延びる第2部分と、

前記第1部分の前記第1の辺に沿う第2の辺から前記第1方向に沿って前記データ書き込みおよび消去用の素子に向かって延びる第3部分とを一体的に有しており、

前記第1部分は、前記第2部分と前記第3部分との間に設けられ、

前記第2部分および前記第3部分は、前記第1方向に交差する第2方向に沿って互いにずれた状態で設けられ、

前記容量素子は、

前記浮遊ゲート電極の前記第1部分の前記第1位置に形成される第1電極と、前記第1電極および前記半導体基板の間に形成される第1絶縁膜と、前記第4ウエル内に形成される第2導電型の半導体領域と、前記第4ウエルとを有し、

前記データ読み出し用の電界効果トランジスタは、

前記浮遊ゲート電極の前記第2部分の前記第2位置に形成される第2電極と、前記第2電極および前記半導体基板の間に形成される第2絶縁膜と、前記第3ウエル内において前記第2電極を挟み込む位置に形成された第1導電型の一対の半導体領域とを有し、

前記データ書き込みおよび消去用の素子は、

前記浮遊ゲート電極の前記第3部分の前記第3位置に形成される第3電極と、前記第3電極および前記半導体基板の間に形成される第3絶縁膜と、前記第2ウエル内に形成され

10

20

30

40

る第2導電型の半導体領域と、前記第2ウエルとを有することを特徴とする半導体装置。

### 【請求項10】

請求項9記載の半導体装置において、前記データ書き込みおよび消去用の素子でのデータの書き換えは、チャネル全面のFNトンネル電流により行うことを特徴とする半導体装置。

## 【請求項11】

請求項9記載の半導体装置において、前記浮遊ゲート電極の前記第1電極の前記第2方向の長さは、前記第2電極および前記第3電極の前記第2方向の長さよりも長いことを特徴とする半導体装置。

### 【請求項12】

請求項9記載の半導体装置において、前記データ書き込みおよび消去用の素子の前記第3電極の前記第2方向の長さと、前記データ読み出し用の電界効果トランジスタの前記第2電極の前記第2方向の長さとが異なることを特徴とする半導体装置。

### 【請求項13】

請求項12記載の半導体装置において、前記データ書き込みおよび消去用の素子の前記第3電極の前記第2方向の長さは、前記データ読み出し用の電界効果トランジスタの前記第2電極の前記第2方向の長さよりも短いことを特徴とする半導体装置。

### 【請求項14】

請求項9記載の半導体装置において、前記主回路形成領域には、第1動作電圧で駆動する低耐圧の電界効果トランジスタと、前記第1動作電圧よりも高い第2動作電圧で駆動する高耐圧の電界効果トランジスタとが配置されており、

前記データ読み出し用の電界効果トランジスタの前記一対の半導体領域の構成を、前記低耐圧の電界効果トランジスタの一対の半導体領域の構成と同一にすることを特徴とする半導体装置。

#### 【請求項15】

請求項9記載の半導体装置において、前記第2方向に沿って配置される複数の前記データ書き込みおよび消去用の素子の隣接間に、前記第1ウエルよりも不純物濃度の高い第1導電型の第1半導体領域を設け、互いに隣接する複数の前記第2ウエルを分離したことを特徴とする半導体装置。

## 【請求項16】

請求項15記載の半導体装置において、前記主回路形成領域には、第1動作電圧で駆動する低耐圧の電界効果トランジスタと、前記第1動作電圧よりも高い第2動作電圧で駆動する高耐圧の電界効果トランジスタとが配置されており、

前記第1半導体領域は、前記低耐圧の電界効果トランジスタのソース、ドレイン用の一対の半導体領域の形成工程により形成されていることを特徴とする半導体装置。

#### 【請求項17】

請求項9記載の半導体装置において、前記複数の不揮発性メモリセルの各々の前記データ読み出し用の電界効果トランジスタには、前記複数の不揮発性メモリセルの各々を選択可能なように選択用の電界効果トランジスタが電気的に接続されていることを特徴とする半導体装置。

## 【請求項18】

請求項9記載の半導体装置において、前記容量素子は、前記第4ウエル内に形成される 第1導電型の半導体領域を有することを特徴とする半導体装置。

## 【請求項19】

請求項9記載の半導体装置において、前記データ書き込みおよび消去用の素子は、前記第2ウエル内に形成される第1導電型の半導体領域を有することを特徴とする半導体装置

## 【請求項20】

第1主面およびその裏側の第2主面を有する半導体基板と、 前記半導体基板の第1主面に配置された主回路形成領域と、 10

20

30

前記半導体基板の第1主面に配置された不揮発性メモリ領域とを備え、

前記不揮発性メモリ領域には、

前記半導体基板の第1主面に形成された第1導電型の第1ウエルと、

前記第1導電型とは反対の導電型を有する第2導電型のウエルであって、前記第1ウエルに内包されるように配置された第2ウエルと、

前記第2導電型のウエルであって、前記第2ウエルとは電気的に分離された状態で、前記第1ウエルに内包されるように配置された第3ウエルと、

前記第2導電型のウエルであって、前記第2ウエルおよび前記第3ウエルとは電気的に分離された状態で、前記第2ウエルと前記第3ウエルとの間に、前記第1ウエルに内包されるように配置された第4ウエルと、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように配置された複数の不揮発性メモリセルとを備え、

前記複数の不揮発性メモリセルの各々は、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように第1方向に延在して配置された浮遊ゲート電極と、

前記浮遊ゲート電極が前記第4ウエルに平面的に重なる第1位置に形成された容量素子と、

前記浮遊ゲート電極が前記第3ウエルに平面的に重なる第2位置に形成されたデータ読み出し用の電界効果トランジスタと、

前記浮遊ゲート電極が前記第2ウエルに平面的に重なる第3位置に形成されたデータ書き込みおよび消去用の素子とを有し、

前記浮遊ゲート電極は、

前記第4ウエルに平面的に重なる第1部分と、

前記第1部分の第1の辺から前記第1方向に沿って前記データ読み出し用の電界効果トランジスタに向かって延びる第2部分と、

前記第1部分の前記第1の辺に沿う第2の辺から前記第1方向に沿って前記データ書き 込みおよび消去用の素子に向かって延びる第3部分とを一体的に有しており、

前記第1部分は、前記第2部分と前記第3部分との間に設けられ、

前記第2部分および前記第3部分は、前記第1方向に交差する第2方向に沿って互いに ずれた状態で設けられ、

前記容量素子は、

前記浮遊ゲート電極の前記第1部分の前記第1位置に形成される第1電極と、前記第1電極および前記半導体基板の間に形成される第1絶縁膜と、前記第4ウエル内に形成される第2導電型の半導体領域と、前記第4ウエルとを有し、

前記データ読み出し用の電界効果トランジスタは、

前記浮遊ゲート電極の前記第2部分の前記第2位置に形成される第2電極と、前記第2電極および前記半導体基板の間に形成される第2絶縁膜と、前記第3ウエル内において前記第2電極を挟み込む位置に形成された第1導電型の一対の半導体領域とを有し、

前記データ書き込みおよび消去用の素子は、

前記浮遊ゲート電極の前記第3部分の前記第3位置に形成される第3電極と、前記第3電極および前記半導体基板の間に形成される第3絶縁膜と、前記第2ウエル内に形成される第2導電型の半導体領域と、前記第2ウエルとを有し、

前記複数の不揮発性メモリセルのうち、前記第1方向に沿って並んで配置された不揮発性メモリセル同士は互いに対称になるように配置されており、

前記第1方向に沿って並んで配置された不揮発性メモリセルの前記データ書き込みおよび消去用の素子は、共通の前記第2ウエルに形成されていることを特徴とする半導体装置

## 【請求項21】

請求項20記載の半導体装置において、前記データ書き込みおよび消去用の素子でのデータの書き換えは、チャネル全面のFNトンネル電流により行うことを特徴とする半導体

10

20

30

40

装置。

### 【請求項22】

請求項20記載の半導体装置において、前記データ書き込みおよび消去用の素子の前記第3電極の前記第2方向の長さと、前記データ読み出し用の電界効果トランジスタの前記第2電極の前記第2方向の長さとが異なることを特徴とする半導体装置。

#### 【請求項23】

請求項22記載の半導体装置において、前記データ書き込みおよび消去用の素子の前記第3電極の前記第2方向の長さは、前記データ読み出し用の電界効果トランジスタの前記第2電極の前記第2方向の長さよりも短いことを特徴とする半導体装置。

### 【請求項24】

請求項20記載の半導体装置において、前記容量素子は、前記第4ウエル内に形成される第1導電型の半導体領域を有することを特徴とする半導体装置。

#### 【請求項25】

請求項20記載の半導体装置において、前記データ書き込みおよび消去用の素子は、前記第2ウエル内に形成される第1導電型の半導体領域を有することを特徴とする半導体装置。

【発明の詳細な説明】

### 【技術分野】

#### [00001]

本発明は、半導体装置技術に関し、特に、不揮発性メモリ回路部を有する半導体装置に適用して有効な技術に関するものである。

#### 【背景技術】

## [0002]

半導体装置の中には、その内部に、例えばトリミング時、救済時およびLCD(Liquid Crystal Device)の画像調整時に使用する情報や半導体装置の製造番号情報等、比較的小容量の情報を記憶するための不揮発性メモリ回路部を有するものがある。

#### [00003]

この不揮発性メモリ回路部を有する半導体装置については、例えば特開2006-80247号公報(特許文献1参照)に記載がある。この特許文献1には、次のような不揮発性メモリセルの構成が開示されている。半導体基板の主面には、情報の記憶に寄与する電荷を蓄積する浮遊ゲート電極が配置されている。この浮遊ゲート電極は、相対的に幅広の部分と相対的に幅の狭い部分とを有している。浮遊ゲート電極の相対的に幅の広い部分は、容量素子の電極を形成している。また、浮遊ゲート電極の相対的に幅の狭い部分の一部は、情報書き込み用の電界効果トランジスタのゲート電極となっている。また、浮遊ゲート電極となっている。

## [0004]

さらに、例えばUSP6788574 (特許文献2)のFig.7には、容量部、書き込みトランジスタ、読み出しトランジスタが、それぞれnウエルで分離されている構成が開示されている。また、特許文献2のFig.4A-4C、column6-7には、書き込み/消去はFNトンネル電流で行う構成が開示されている。

【特許文献1】特開2006-80247号公報

【特許文献 2 】U S P 6 7 8 8 5 7 4 の F i g . 7 , F i g . 4 A - 4 C

## 【発明の開示】

【発明が解決しようとする課題】

### [0005]

ところが、近年は、半導体装置に設けられた上記不揮発性メモリ回路部のメモリ容量も増大する傾向にあるので、不揮発性メモリ回路部の配置領域が半導体装置の主回路の配置領域を圧迫することのないように、より大きなメモリ容量を確保しつつも不揮発性メモリ回路部の占有面積を如何にして小さくするかが重要な課題となっている。

10

20

30

40

#### [0006]

そこで、本発明の目的は、半導体装置に設けられた不揮発性メモリ回路部の面積を小さくすることのできる技術を提供することにある。

#### [0007]

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### [0008]

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のと おりである。

## [0009]

すなわち、本発明は、データ読み出し用のトランジスタと、容量素子と、データ書き込みおよび消去用の素子とを有する不揮発性メモリセルにおいて、

上記データ読み出し用のトランジスタと、上記データ書き込みおよび消去用の素子とは、その間に配置された上記容量素子により離れて配置されており、

上記容量素子の第1電極と、上記データ読み出し用のトランジスタの第2電極と、上記データ書き込みおよび消去用の素子の第3電極とは、上記データ読み出し用のトランジスタと、上記容量素子と、上記データ書き込みおよび消去用の素子との配置方向に沿って延在する共通の浮遊ゲート電極の一部で構成されており、

上記データ読み出し用のトランジスタの第2電極と、上記データ書き込みおよび消去用の素子の第3電極とは、その間に配置された上記容量の第1電極により離れているものである。

## 【発明の効果】

#### [0010]

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明 すれば以下のとおりである。

#### [0011]

すなわち、データ読み出し用のトランジスタと、容量素子と、データ書き込みおよび消去用の素子とを有する不揮発性メモリセルにおいて、上記データ読み出し用のトランジスタと、上記データ書き込みおよび消去用の素子とは、その間に配置された上記容量素子により離れて配置されており、上記容量素子の第1電極と、上記データ読み出し用のトランジスタの第2電極と、上記データ書き込みおよび消去用の素子の第3電極とは、上記データ読み出し用のトランジスタと、上記容量素子と、上記データ書き込みおよび消去用の素子の配置方向に沿って延在する共通の浮遊ゲート電極の一部で構成されており、上記データ読み出し用のトランジスタの第2電極と、上記データ書き込みおよび消去用の素子の第3電極とは、その間に配置された上記容量の第1電極により離れていることにより、半導体装置に設けられた不揮発性メモリ回路部の面積を小さくすることができる。

#### 【発明を実施するための最良の形態】

### [0012]

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。

10

20

30

40

このことは、上記数値および範囲についても同様である。また、本実施の形態を説明するための全図において同一機能を有するものは同一の符号を付すようにし、その繰り返しの説明は可能な限り省略するようにしている。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

#### [0013]

#### (実施の形態1)

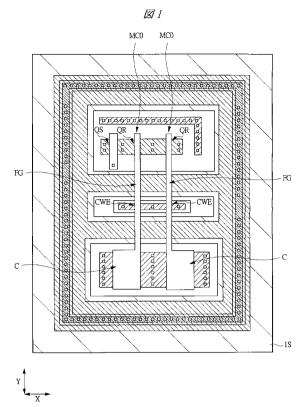

図1は本発明者が検討した半導体装置におけるフラッシュメモリの1ビット分のメモリセルMC0の平面図を示している。なお、図1は平面図であるが、図面を見易くするために一部にハッチングを付した。また、符号Yは第1方向でローカルデータ線の延在方向を示し、符号のXは第1方向Yに直交する第2方向でワード線の延在方向を示している。

#### [0014]

この構成では、1 ビットに2 つのメモリセルMC0 が配置されている(1 ビット/2 セル構成)。また、1 ビットに1 つの選択MIS・FET(Metal Insulator Semiconductor Field Effect Transistor)QSが配置されている。各メモリセルMC0 は、浮遊ゲート電極FGを共有するデータ読み出し用のMIS・FETQR、データ書き込み・消去用の電荷注入放出部CWEおよび容量部Cを有している。このデータ読み出し用のMIS・FETQR、データ書き込み・消去用の電荷注入放出部CWEおよび容量部Cは、図1の上から下に向かって順に並んで配置されている。

#### [0015]

図 2 は図 1 のメモリセルMC 0 を 1 ビット / 1 セル構成にした場合のメモリセルアレイの平面図を示している。なお、図 2 は平面図であるが、図面を見易くするために一部にハッチングを付した。

#### [0016]

メモリセルMC0は、第2方向Xに沿って複数並んで配置されている。各メモリセルMCは、データ読み出し用のMIS・FETQR、データ書き込み・消去用の電荷注入放出部CWE、容量部Cおよび選択MIS・FETQSを有している。データ読み出し用のMIS・FETQR、データ書き込み・消去用の電荷注入放出部CWEおよび容量部Cの配置順序は図1と同じである。

### [0017]

ここで、互いに隣接するメモリセルMC0のデータ読み出し用のMIS・FETQRおよび容量部Cの各々の半導体領域を共有させることでメモリセルアレイの面積を縮小することが考えられる。

#### [0018]

しかし、図1のメモリセルMC0の構成で、互いに隣接するメモリセルMC0のデータ 読み出し用のMIS・FETQRおよび容量部Cの各々の半導体領域を共有させるように 隣接間の距離を縮めると、図1のメモリセルMC0により1ビット/1セル構成を形成す る場合に分離を必要とする電荷注入放出部CWEの半導体領域同士も重なってしまう。

#### [0019]

このため、図1のメモリセルMC0により1ビット/1セル構成を形成する場合、互いに隣接するメモリセルMC0のデータ読み出し用のMIS・FETQRおよび容量部Cの各々の半導体領域を共有させることはできない。したがって、互いに隣接するメモリセルMC0同士を離さなければならず、メモリセルアレイの面積の縮小を阻害する課題がある

## [0020]

次に、本実施の形態1の半導体装置について説明する。本実施の形態1の半導体装置は、同一の半導体チップに、主回路と、その主回路に関する比較的小容量の所望の情報を記憶するフラッシュメモリ(不揮発性メモリ回路部)とが形成されているものである。

#### [0021]

上記主回路としては、例えばLCD(Liquid Crystal Device)ドライバ回路が形成されている。この場合、上記所望の情報には、例えばLCDの救済の際に使用する有効メモ

10

20

40

30

リセル(不良のないメモリセル)や有効 L C D 素子の配置アドレス情報、 L C D 画像調整時に使用する調整電圧のトリミングタップ情報や可変抵抗のデジタル情報等がある。この半導体装置(半導体チップ)の外部から供給される外部電源は、単一電源とされている。単一電源の電源電圧は、例えば3.3 V 程度である。

### [0022]

ただし、上記主回路は、LCDドライバ回路に限定されるものではなく種々変更可能であり、例えばDRAM(Dynamic Random Access Memory)やSRAM(Static RAM)等のようなメモリ回路、CPU(Central Processing Unite)やMPU(Micro Processing Unite)等のような論理回路、これらメモリ回路および論理回路の混在回路等がある。

### [0023]

また、上記所望の情報も上記したものに限定されるものではなく種々変更可能であり、例えば半導体チップ内のトリミングの際に使用する有効(使用)素子の配置アドレス情報、上記メモリ回路の救済の際に使用する有効メモリセル(不良のないメモリセル)の情報、内部の周波数発振器のバラツキを所望の範囲内に設定するためのトリミング情報、半導体装置の管理コードの情報、半導体装置の製造番号の情報等がある。

#### [0024]

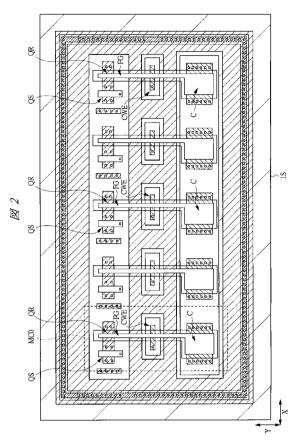

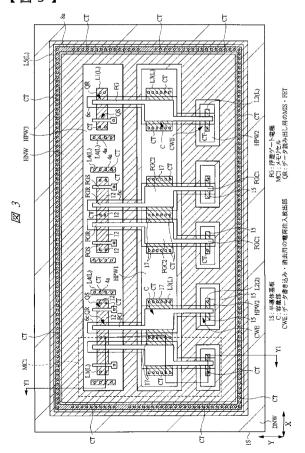

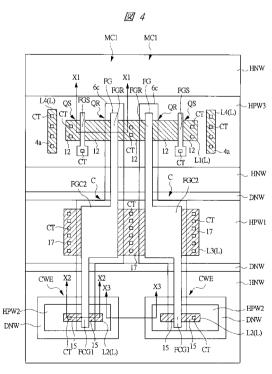

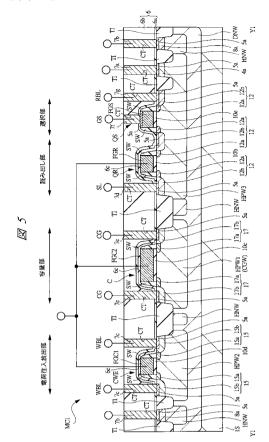

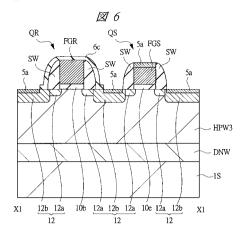

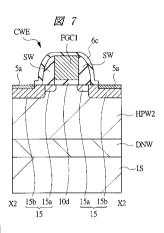

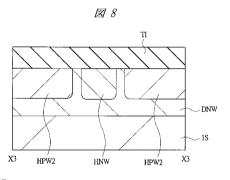

まず、本実施の形態 1 の半導体装置のフラッシュメモリについて説明する。図 3 は本実施の形態 1 の半導体装置におけるフラッシュメモリの平面図、図 4 は図 3 のフラッシュメモリの要部拡大平面図、図 5 は図 3 の Y 1 - Y 1 線の断面図、図 6 は図 4 の X 1 - X 1 線の断面図、図 7 は図 4 の X 2 - X 2 線の断面図、図 8 は図 4 の X 3 - X 3 線の断面図を示している。なお、図 3 および図 4 は平面図であるが、図面を見易くするために一部にハッチングを付した。

#### [0025]

本実施の形態1においては、半導体チップを構成する半導体基板(以下、単に基板という)1Sの主面(第1主面)のフラッシュメモリ領域に複数の上記メモリセルMC1が第2方向Xに沿って規則的に並んで配置されている。ここでは、1ビットに1つのメモリセルMC1が配置されている(1ビット/1セル構成)。

#### [0026]

上記基板 1 S は、例えば p 型 (第 2 導電型)のシリコン (S i )単結晶からなり、厚さ方向に沿って互いに反対側に位置する第 1 主面および第 2 主面を有している。

#### [0027]

この基板1Sの第1主面には分離部TIが配置されている。この分離部TIは、活性領域L(L1,L2,L3,L4,L5)を規定する部分である。ここでは分離部TIが、例えば基板1Sの主面に掘られた浅溝内に酸化シリコン等からなる絶縁膜を埋め込むことで形成された、いわゆるSGI(Shallow Groove Isolation)またはSTI(Shallow Trench Isolation)と称する溝形の分離部とされている。

## [0028]

上記基板1Sには、その主面から所望の深さに渡ってn型(第1導電型)の埋込ウエル(第1ウエル)DNWが形成されている。この埋込ウエルDNWには、p型のウエルHPW1,HPW2,HPW3およびn型のウエルHNWが内包された状態で形成されている。このp型のウエルHPW1,HPW2,HPW3は、第1方向Yに沿って隣接した状態で配置されている。p型のウエル(第4ウエル)HPW1は、p型のウエル(第2ウエル)HPW2とp型のウエル(第3ウエル)HPW3との間に配置されている。

## [0029]

このp型のウエルHPW1,HPW2,HPW3は、その隣接間に配置されたn型のウエルHNWと埋込ウエルDNWにより互いに電気的に分離されている。また、複数のp型のウエルHPW2同士も、その間に配置されたn型のウエルHNWおよび埋込ウエルDNWにより互いに電気的に分離されている。このn型のウエルHNWは、p型のウエルHPW3には接しているものの、耐圧を確保するためp型のウエルHPW1,HPW2には接しておらず、n型のウエルHNWとp型のウエルHPW1,HPW2との間には埋込ウエ

10

20

30

40

20

30

40

50

ルDNWが介在されている。

## [0030]

このp型のウエルHPW1,HPW2,HPW3には、例えばホウ素等のようなp型を示す不純物が含有されている。このうち、p型のウエルHPW3の上層一部には、p  $^+$ 型の半導体領域4aが形成されている。p  $^+$ 型の半導体領域4aには、p型のウエルHPW3と同じ不純物が含有されているが、p  $^+$ 型の半導体領域4aの不純物濃度の方が、p型のウエルHPW3の不純物濃度よりも高くなるように設定されている。このp  $^+$ 型の半導体領域4aの表層一部には、例えばコバルトシリサイド(CoSix)等のようなシリサイド層5aが形成されている。このp  $^+$ 型の半導体領域4aは、シリサイド層5aを介して、基板1Sの主面上の絶縁層6に形成されたコンタクトホールCT内の導体部7aに電気的に接続されている。絶縁層6は、絶縁層6aとその上に堆積された絶縁層6bとを有している。下層の絶縁層6aは、例えば窒化シリコン(Si3N4)からなり、上層の絶縁層6bは、例えば酸化シリコン(Si0。)からなる。

## [0031]

また、上記 n 型のウエル H N Wには、例えばリン( P )またはヒ素( A s )等のような n 型を示す不純物が含有されており、その不純物濃度は、上記の埋込ウエル D N W よりも高い濃度で形成されている。この n 型のウエル H N W の上層一部には、 n <sup>+</sup>型の半導体領域 8 a が形成されている。 n <sup>+</sup>型の半導体領域 8 a には、 n 型のウエル H N W と同じ不純物が含有されているが、 n <sup>+</sup>型の半導体領域 8 a の不純物濃度の方が、 n 型のウエル H N W の不純物濃度よりも高くなるように設定されている。この n <sup>+</sup>型の半導体領域 8 a は、その表層一部に形成されたシリサイド層 5 a を介して、上記絶縁層 6 に形成されたコンタクトホール C T 内の導体部 7 b に電気的に接続されている。

## [0032]

本実施の形態1のフラッシュメモリを構成する各メモリセルMC1は、浮遊ゲート電極 FGと、データ読み出し用のMIS・FETQRと、容量部Cと、データ書き込み・消去 用の電荷注入放出部CWEと、選択MIS・FETQSとを有している。

### [0033]

上記浮遊ゲート電極FGは、情報の記憶に寄与する電荷を蓄積する機能を有している。この浮遊ゲート電極FGは、例えば低抵抗な多結晶シリコン等のような導電体からなり、電気的に浮遊状態(他の導体と絶縁された状態)で形成されている。このようにメモリセルMC1のゲート構成を単層構成とすることにより、フラッシュメモリのメモリセルMCと主回路の素子との製造上の整合を容易にすることができるので、半導体装置の製造時間の短縮や製造コストの低減を図ることができる。

## [0034]

この浮遊ゲート電極FGの側面には、例えば酸化シリコンからなるサイドウォールSWが形成されている。この浮遊ゲート電極FGの上面およびサイドウォールSWの表面を覆うようにキャップ絶縁層6cが形成されている。このキャップ絶縁層6cは、例えば酸化シリコンからなり、窒化シリコンからなる絶縁層6aが浮遊ゲート電極FGの上面に直接接しないように、浮遊ゲート電極FGの上面と絶縁層6bとの間に形成されている。これは、以下の理由からである。すなわち、窒化シリコンからなる絶縁層6aをプラズマ化学気相成長(Chemical Vapor Deposition: C V D )法等により堆積する場合、絶縁層6aがったの堆積の初期段階においてシリコンリッチな膜になり易い。このため、絶縁層6aが浮遊ゲート電極FGの上面に直接接した状態で形成されていると、浮遊ゲート電極FG中の電荷が絶縁層6aのシリコンリッチな部分を通じて基板1S側に流れ、導体部を通じてあ出されてしまう場合がある。その結果、フラッシュメモリのデータ保持特性が低下する。キャップ絶縁層6cを形成することで、そのような不具合を抑制または防止することができる。

## [0035]

また、このキャップ絶縁層6cは、基板1Sの他の領域に設けられた抵抗素子(図示せず)の上にも形成されている。この抵抗素子は、例えば多結晶シリコン膜から成り、前記

20

30

40

50

浮遊ゲート電極 F G の形成工程と同工程で形成することができる。このような抵抗素子上にキャップ絶縁層 6 c を設けることで、抵抗素子上にシリサイド層 5 a が形成される領域と形成されない領域とを選択的に作り分けることができ、これにより所望の抵抗値を有する抵抗素子を形成することができる。すなわち、本実施の形態 1 では、キャップ絶縁層 6 c を用いることで、抵抗素子上にシリサイド層 5 a を作り分けるための絶縁層と、浮遊ゲート電極 F G 上の絶縁層 6 a との間に設ける絶縁層とを同工程で形成している。これにより、各々の絶縁層を別工程で形成する必要がなく、半導体装置の製造工程の簡略化を図ることができる。

## [0036]

また、図5に示すように、このキャップ絶縁層6 c は、浮遊ゲート電極 F G の上面およびサイドウォール S W の表面を覆うと共に、後述する n <sup>+</sup>型の半導体領域12 b、p <sup>+</sup>型の半導体領域15 b および p <sup>+</sup>型の半導体領域17 b の上まで延在して形成されている。これは、シリサイド層5 a を形成する際に、シリサイド層5 a が低濃度 n <sup>-</sup>型の半導体領域12 a、p <sup>-</sup>型の半導体領域15 a および p <sup>-</sup>型の半導体領域17 a 中にまで成長してしまうと、基板1S との接合リーク電流が発生する可能性が高くなる。本願では、キャップ絶縁層6 c によって、シリサイド層5 a を、低濃度 n <sup>-</sup>型の半導体領域12 a、p <sup>-</sup>型の半導体領域15 a および p <sup>-</sup>型の半導体領域17 a から離れるように形成することができるので、上述の接合リークの発生を防止することができる。

## [0037]

また、この浮遊ゲート電極 F G は、図 3 および図 4 に示すように、第 1 方向 Y に沿って互いに隣接する上記 p 型のウエル H P W 1 , H P W 2 , H P W 3 に平面的に重なるように第 1 方向 Y に沿って延在した状態で形成されている。すなわち、浮遊ゲート電極 F G は、p 型のウエル H P W 1 に平面的に重なる第 1 部分と、この第 1 部分の第 1 の辺から第 1 方向 Y に沿ってデータ読み出し用の M I S・F E T Q R に向かって延びる第 2 部分と、上記第 1 部分の上記第 1 の辺に沿う第 2 の辺から第 1 方向に沿ってデータ書き込みおよび消去用の電荷注入放出部 C W E に向かって延びる第 3 部分とを一体的に有している。

#### [0038]

上記 p 型のウエル H P W 3 には、複数のビット分のデータ読み出し用のM I S・F E T Q R および選択 M I S・F E T Q S が配置されている。すなわち、各データ読み出し用の M I S・F E T Q R は、上記浮遊ゲート電極 F G の第 2 部分が p 型のウエル H P W 3 の活性領域 L 1 に平面的に重なる位置(第 2 位置)に配置されている。データ読み出し用の M I S・F E T Q R は、ゲート電極(第 2 電極) F G R と、ゲート絶縁膜(第 2 絶縁膜) 1 0 b と、一対の n 型の半導体領域 1 2 , 1 2 とを有している。データ読み出し用の M I S・F E T Q R のチャネルは、上記ゲート電極 F G R と活性領域 L 1 とが平面的に重なる上記 p 型のウエル H P W 3 の表層に形成される。

### [0039]

ゲート電極 F G R は、上記浮遊ゲート電極 F G の一部により形成されている。上記ゲート絶縁膜 1 0 b は、例えば酸化シリコンからなり、ゲート電極 F G R と基板 1 S ( p 型のウエル H P W 3 ) との間に形成されている。ゲート絶縁膜 1 0 b の厚さは、例えば 1 3 . 5 n m 程度である。

## [0040]

上記一対の n 型の半導体領域 1 2 , 1 2 は、 p 型のウエル H P W 3 内においてゲート電極 F G R を挟み込む位置に形成されている。この一対の n 型の半導体領域 1 2 , 1 2 は、それぞれチャネル側の n 型の半導体領域 1 2 a と、その各々に接続された n \*型の半導体領域 1 2 b とを有している。この n 型の半導体領域 1 2 a および n \*型の半導体領域 1 2 b には、例えばリン ( P ) またはヒ素 ( A s ) 等のような同一導電型の不純物が含有されているが、 n 型の半導体領域 1 2 b の不純物濃度よりも高くなるように設定されている。

#### [0041]

この一対の半導体領域12,12の一方(ソース側)は、隣接する他のメモリセルMC

1のデータ読み出し用のMIS・FETQRの一対の半導体領域12の一方(ソース側)と共有とされている。このソース側の半導体領域12は、n<sup>+</sup>型の半導体領域12bの表層一部に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7dに電気的に接続されている。この導体部7dは、ソース線SLに電気的に接続されている。一方、上記一対の半導体領域12,12の他方は、上記選択MIS・FETQSのソースおよびドレイン用のn型の半導体領域12の一方と共有とされている。

### [0042]

選択MIS・FETQSは、ゲート電極FGSと、ゲート絶縁膜10eと、ソース・ドレイン用の一対のn型の半導体領域12,12とを有している。選択MIS・FETQSのチャネルは、上記ゲート電極FGSと活性領域L1とが平面的に重なる上記p型のウエルHPW3の表層に形成される。

#### [0043]

上記ゲート電極 F G S は、例えば低抵抗な多結晶シリコンにより形成されている。このゲート電極 F G S の側面にもサイドウォール S W が形成されている。このゲート電極 F G S の表層には、上記シリサイド層 5 a が形成されている。このゲート電極 F G S は、上記絶縁層 6 に形成されたコンタクトホール C T 内の導体部 7 f に電気的に接続されている。この導体部 7 f は、選択線 G S に電気的に接続されている。

#### [0044]

上記ゲート絶縁膜10 e は、例えば酸化シリコンからなり、ゲート電極FGSと基板1S(p型のウエルHPW3)との間に形成されている。このゲート絶縁膜10 e の厚さは、例えば13.5 n m 程度である。

## [0045]

また、選択MIS・FETQSの一対のn型の半導体領域12,12の構成は、上記データ読み出し用のMIS・FETQRのn型の半導体領域12と同じである。選択MIS・FETQSの他方のn型の半導体領域12は、その表層一部に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7gに電気的に接続されている。この導体部7gには、データ読み出し用のビット線RBLに電気的に接続されている。

## [0046]

また、複数のp型のウエルHPW2の各々には、データ書き込み・消去用の電荷注入放出部CWEが配置されている。すなわち、各データ書き込み・消去用の電荷注入放出部CWEは、上記浮遊ゲート電極FGの第3部分がp型のウエル(第2ウエル)HPW2の活性領域L2に平面的に重なる位置(第3位置)に配置されている。この電荷注入放出部CWEは、容量電極(第3電極)FGC1と、容量絶縁膜(第3絶縁膜)10dと、p型の半導体領域15,15と、p型のウエルHPW2とを有している。

## [0047]

容量電極FGC1は、上記浮遊ゲート電極FGの一部により形成されており、電荷注入放出部CWEの電極を形成する部分である。上記容量絶縁膜10dは、例えば酸化シリコンからなり、容量電極FGC1と基板1S(p型のウエルHPW2)との間に形成されている。容量絶縁膜10dの厚さは、例えば10nm以上、20nm以下とされている。

#### [0048]

ただし、本実施の形態1の電荷注入放出部CWEでは、データの書き換えにおいて、電子をp型のウエルHPW2から容量絶縁膜10dを介して容量電極FGC1に注入したり、容量電極FGC1の電子を容量絶縁膜10dを介してp型のウエルHPW2に放出したりするので、容量絶縁膜10dの厚さは薄く、具体的には、例えば13.5nm程度の厚さに設定されている。容量絶縁膜10dの厚さが10nmより薄いと容量絶縁膜10dの厚さを20nmより厚いと電子を通過させることが難しくなり、データの書き換えが上手くできないからである。

## [0049]

50

10

20

30

20

30

40

50

電荷注入放出部 CWE op 型 on 半導体領域 15 は、 p型 on ウェル HPW 2 内において容量電極 FGC 1 を挟み込む位置に形成されている。この半導体領域 15 は、それぞれチャネル側の p 型 on 半導体領域 15 a と、その各々に接続された p 型 on 半導体領域 15 b とを有している。この p 型 on 半導体領域 15 a および p 型 on 半導体領域 15 b には、例えばホウ素 <math>(B)等のような同一導電型の不純物が含有されているが、 (B)で、 (B)0年導体領域 15 a の不純物濃度の方が、 (B)1年 型 on 半導体領域 15 a の不純物濃度よりも高くなるように設定されている。

### [0050]

#### [0051]

このp型の半導体領域15は、p型のウエルHPW2と電気的に接続されている。p型の半導体領域15およびp型のウエルHPW2は、電荷注入放出部CWEの電極を形成する部分である。このp型の半導体領域15は、p  $^+$ 型の半導体領域15bの表層一部に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7cに電気的に接続されている。この導体部7cは、上記データ書き込み・消去用のビット線WBLに電気的に接続されている。

#### [0052]

また、上記 p 型のウエル H P W 1 には、複数のビット分の容量部 C が配置されている。すなわち、各容量部 C は、上記浮遊ゲート電極 F G の第 1 部分が上記 p 型のウエル H P W 1 に平面的に重なる位置(第 1 位置)に形成されている。この容量部 C は、制御ゲート電極 C G W と、容量電極(第 1 電極) F G C 2 と、容量絶縁膜(第 1 絶縁膜) 1 0 c と、 p 型の半導体領域 1 7 とを有している。

## [0053]

制御ゲート電極 C G W は、浮遊ゲート電極 F G が対向する p 型のウエル H P W 1 部分により形成されている。容量電極 F G C 2 は、上記制御ゲート電極 C G W に対向する浮遊ゲート電極 F G の第 1 部分により形成されている。この容量電極 F G C 2 の第 2 方向 X の長さは、上記データ書き込み・消去用の電荷注入放出部 C W E の容量電極 F G C 1 や上記データ読み出し用の M I S・F E T Q R のゲート電極 F G R の第 2 方向 X の長さよりも長くなるように形成されている。これにより、容量電極 F G C 2 の平面積を大きく確保できるので、カップリング比を高めることができ、制御ゲート電極 C G W からの電圧供給効率を向上させることが可能となっている。

### [0054]

上記容量絶縁膜10cは、例えば酸化シリコンからなり、上記制御ゲート電極CGWと容量電極FGC2との間に形成されている。この容量絶縁膜10cは、上記ゲート絶縁膜10b,10eおよび容量絶縁膜10dを形成する際の熱酸化工程により同時に形成されており、その厚さは、例えば13.5nm程度である。また、上記ゲート絶縁膜10b,10eおよび容量絶縁膜10c,10dは、主回路における相対的に厚いゲート絶縁膜を持つ高耐圧MISFETと相対的に薄いゲート絶縁膜を持つ低耐圧MISFETのうち、高耐圧MISFETのゲート絶縁膜と同工程により形成されている。これにより、フラッシュメモリの信頼性を向上させることができる。

## [0055]

上記 p 型の半導体領域 1 7 は、 p 型のウエル H P W 1 内において容量電極 F G C 2 を挟み込む位置に形成されている。この半導体領域 1 7 は、それぞれチャネル側の p ・型の半

導体領域17aと、その各々に接続されたp  $^+$ 型の半導体領域17bとを有している。このp  $^-$ 型の半導体領域17bには、例えばホウ素(B)等のような同一導電型の不純物が含有されているが、p  $^+$ 型の半導体領域17bの不純物濃度の方が、p  $^-$ 型の半導体領域17aの不純物濃度よりも高くなるように設定されている。

### [0056]

#### [0057]

このp型の半導体領域17は、p型のウエルHPW1と電気的に接続されている。p型の半導体領域17およびp型のウエルHPW1は、容量部Cの制御ゲート電極CGWを形成する部分である。このp型の半導体領域17は、p  $^+$ 型の半導体領域17bの表層に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7eに電気的に接続されている。この導体部7eは、上記制御ゲート配線CGに電気的に接続されている。

#### [0058]

ところで、本実施の形態1のメモリセルMC1においては、データ読み出し用のMIS・FETQR、容量部Cおよびデータ書き込み・消去用の電荷注入放出部CWEの配置が図1および図2に示したメモリセルMC0と異なっている。

#### [0059]

本実施の形態1のメモリセルMC1においては、データ読み出し用のMIS・FETQR、容量部Cおよびデータ書き込み・消去用の電荷注入放出部CWEが、図3および図4の上から下に向かって順に配置されている。すなわち、容量部Cが、データ読み出し用のMIS・FETQRと、電荷注入放出部CWEとの間に配置されている。

#### [0060]

また、本実施の形態1においては、上記のように浮遊ゲート電極FGの上記第1部分が上記第2部分と上記第3部分との間に設けられており、上記データ読み出し用のMIS・FETQRのゲート電極FGRを持つ上記第2部分と、上記データ書き込み・消去用の電荷注入放出部CWEの容量電極FGC1を持つ上記第3部分とが離れている。

#### [0061]

このため、本実施の形態 1 においては、浮遊ゲート電極 F G の第 2 部分の第 2 方向 X の長さと、第 3 部分の第 2 方向 X の長さとをそれぞれ別々に調整できる。これにより、フラッシュメモリの電気的特性を向上させることができる。

#### [0062]

ここでは、浮遊ゲート電極FGの第2部分(ゲート電極FGR)の第2方向Xの長さと、第3部分(容量電極FGC1)の第2方向Xの長さとが等しい場合が例示されている。ただし、浮遊ゲート電極FGの第3部分(容量電極FGC1)の第2方向Xの長さを、浮遊ゲート電極FGの第2部分(ゲート電極FGR)の第2方向Xの長さより短くしても良い(この構成については他の実施の形態で説明する)。また、浮遊ゲート電極FGの第2部分(ゲート電極FGR)の第2方向Xの長さを、浮遊ゲート電極FGの第3部分(容量電極FGC1)の第2方向Xの長さより短くしても良い(この構成についてはさらに他の実施の形態で説明する)。

### [0063]

また、本実施の形態1では、浮遊ゲート電極FGの第2部分の第1方向Yの長さと、第

10

20

30

40

20

30

40

50

3 部分の第 1 方向 Y の長さとをそれぞれ別々に調整できる。これにより、フラッシュメモリの電気的特性を向上させることができる。

#### [0064]

ここでは、浮遊ゲート電極 F G の第3部分の第1方向Yの長さが、第2部分の第1方向Yの長さより短い場合が例示されている。ただし、浮遊ゲート電極 F G の第3部分の第1方向Yの長さを、第2部分の第1方向Yの長さより長くしても良い。また、浮遊ゲート電極 F G の第3部分の第1方向Yの長さと、第2部分の第1方向Yの長さとを等しくしても良い。

### [0065]

また、本実施の形態1においては、浮遊ゲート電極FGにおいて容量電極FGC2からデータ読み出し用のMIS・FETQRまでの長さを、図1および図2のメモリセルMC0に比べて、間に電荷注入放出部CWEが介在されない分、短くすることができる。これにより、データ読み出し用のMIS・FETQRの電気的特性を向上させることができる

#### [0066]

また、本実施の形態 1 においては、上記のように浮遊ゲート電極 F G の第 2 部分と第 3 部分とを離したことにより、第 2 部分(ゲート電極 F G R )と第 3 部分(容量電極 F G C 1 )との第 2 方向 X の位置をそれぞれ別々に調整することができる。

#### [0067]

本実施の形態1においては、浮遊ゲート電極FGの第2部分(ゲート電極FGR)と第3部分(容量電極FGC1)とが第2方向Xに沿って互いに遠ざかる方向にずれて配置されている。ここでは、その第2部分と第3部分とが第1部分(容量電極FGC2)の対角に位置する場合が例示されているが、これに限定されるものではなく、第2部分と第3部分との一方または両方が第1部分(容量電極FGC2)の角(対角)から離れた部分に位置していても良い。

#### [0068]

さらに、本実施の形態 1 においては、互いに隣接するメモリセルMC1が、その各々の浮遊ゲート電極 F G の第 2 部分(ゲート電極 F G R )同士が近づき、各々の第 3 部分(容量電極 F G C 1)同士が遠ざかるように配置されている。これにより、互いに隣接するメモリセルMC1の電荷注入放出部CWEの半導体領域1 5 およびp型のウエルHPW2を分離させたまま、互いに隣接するメモリセルMC1のデータ読み出し用のMIS・FETQRの半導体領域1 2 を上記のように共有構成にすることができ、また、互いに隣接するメモリセルMC1の容量部Cの半導体領域1 7 を上記のように共有構成にすることができる。これにより、複数のメモリセルMC1の第 2 方向 X の隣接間隔をつめることができるので、メモリセルアレイ面積を縮小することができる。また、メモリの記憶容量を増大できる。

## [0069]

次に、本実施の形態1の半導体装置の主回路部について説明する。

#### [ 0 0 7 0 ]

本実施の形態1の主回路部であるLCDドライバ回路は、高耐圧部と低耐圧部とを有している。高耐圧部のMIS・FETの動作電圧は、例えば25V程度である。また、低耐圧部のMIS・FETには、例えば動作電圧が、6.0Vのものと、例えば1.5Vのものとの2種類がある。動作電圧が1.5VのMIS・FETは、動作電圧が6.0VのMIS・FETよりも高速に動作する目的で設けられている。また、動作電圧が1.5VのMIS・FETは、そのゲート絶縁膜が動作電圧が6.0VのMIS・FETのゲート絶縁膜よりも薄く、その膜厚が1~3nm程度で構成されている。

#### [0071]

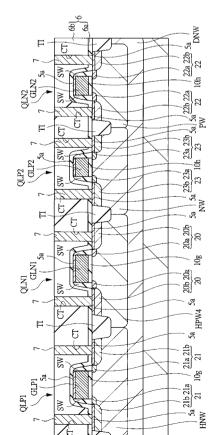

図9は本実施の形態1の半導体装置の主回路部の高耐圧部の断面図を示している。

#### [0072]

上記半導体チップの基板1Sの高耐圧部には、n型の埋込ウエルDNWおよびp型の埋

込ウエルDPWが形成されている。このp型の埋込ウエルDPWには、高耐圧のnチャネル型のMIS・FETQHNが形成され、n型の埋込ウエルDNWには、pチャネル型のMIS・FETQHPが形成されている。

### [0073]

p型の埋込ウエルDPWには、例えばホウ素(B)等のようなp型を示す不純物が含有されている。このp型の埋込ウエルDPWに形成されたnチャネル型のMIS・FETQHNは、ゲート電極GHNと、ゲート絶縁膜10fと、ソース・ドレイン用のn型の半導体領域18,18とを有している。

### [0074]

ゲート電極 G H N は、例えば低抵抗な多結晶シリコンからなり、その上面上にシリサイド層 5 a が形成されている。また、ゲート電極 G H N の側面には、サイドウォール S W が 形成されている。ゲート絶縁膜 1 0 f は、例えば酸化シリコンからなり、ゲート電極 G H N と基板 1 S との間に形成されている。ゲート絶縁膜 1 0 f の厚さは、後述の低耐圧部の M I S・F E T のゲート絶縁膜より厚く、例えば 5 0 ~ 1 0 0 n m程度である。また、このようなゲート絶縁膜 1 0 f は、熱酸化により形成した膜と、 C V D 法によって堆積した膜とを積層することで形成することもできる。

#### [0075]

## [0076]

このような半導体領域18a,18b,NVには、例えばリン(P)またはヒ素(As)等のような同一導電型の不純物が含有されているが、半導体領域18a,18bの不純物濃度の方が、n型の半導体領域NVの不純物濃度よりも高くなるように設定されている。このソース・ドレイン用の半導体領域18,18は、n <sup>+</sup>型の半導体領域18bの表層一部に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7に電気的に接続されている。

### [0077]

上記 p チャネル型の M IS・FETQHPは、ゲート電極 G HPと、ゲート絶縁膜 1 0 f と、ソース・ドレイン用の p 型の半導体領域 1 9 , 1 9 とを有している。

#### [0078]

ゲート電極GHPは、例えば低抵抗な多結晶シリコンからなり、その上面上にシリサイド層5aが形成されている。また、ゲート電極GHPの側面には、サイドウォールSWが形成されている。pチャネル型のMIS・FETQHPのゲート絶縁膜10fは、ゲート電極GHPと基板1Sとの間に形成されている。ゲート絶縁膜10fの材料および厚さは、上記と同じである。

#### [0079]

10

20

30

#### [080]

このような半導体領域19a,19b,PVには、例えばホウ素(B)等のような同一導電型の不純物が含有されているが、半導体領域19a,19bの不純物濃度の方が、p型の半導体領域PVの不純物濃度よりも高くなるように設定されている。このソース・ドレイン用の半導体領域19,19は、p <sup>+</sup>型の半導体領域19bの表層一部に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7に電気的に接続されている。

### [0081]

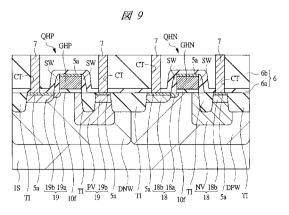

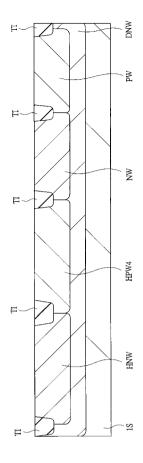

次に、図10は本実施の形態1の半導体装置の主回路部の低耐圧部の断面図を示している。

[0082]

上記半導体チップの基板1Sの低耐圧部には、p型のウエルPWおよびn型のウエルNWが形成されている。p型のウエルPWには、例えばホウ素(B)等のようなp型を示す不純物が含有されている。n型のウエルNWには、例えばリン(P)またはヒ素(As)等のようなn型を示す不純物が含有されている。このp型のウエルPWおよびn型のウエルNWは、n型の埋込ウエルDNWに内包されている。

[0083]

6 V系デバイス形成領域のp型のウエルHPW4には、低耐圧のnチャネル型のMIS・FETQLN1が形成されている。nチャネル型のMIS・FETQLN1は、動作電圧が6 Vのデバイスであり、ゲート電極GLN1と、ゲート絶縁膜10gと、ソース・ドレイン用の一対のn型の半導体領域20,20 とを有している。

[0084]

ゲート電極 G L N 1 は、例えば低抵抗な多結晶シリコンからなり、その上面上にシリサイド層 5 a が形成されている。また、ゲート電極 G L N 1 の側面には、サイドウォール S W が形成されている。ゲート絶縁膜 1 0 g は、例えば酸化シリコンからなり、ゲート電極 G L N 1 と基板 1 S との間に形成されている。ゲート絶縁膜 1 0 g の厚さは、上記高耐圧部の M I S・F E T のゲート絶縁膜より薄く、例えば 1 3 . 5 n m 程度である。

[0085]

上記ソース・ドレイン用の n 型の半導体領域 2 0 , 2 0 は、 p 型のウエル H P W 4 に内包されている。この n 型の半導体領域 2 0 , 2 0 は、チャネル側の n 型の半導体領域 2 0 a と、それに接続された n \* 型の半導体領域 2 0 b とを有している。このような半導体領域 2 0 a , 2 0 b には、例えばリン (P) またはヒ素 (A s) 等のような同一導電型の不純物が含有されているが、 n \* 型の半導体領域 2 0 b の不純物濃度の方が、 n \* 型の半導体領域 2 0 b の不純物濃度よりも高くなるように設定されている。

[0086]

このソース・ドレイン用の半導体領域 2 0 , 2 0 は、 n <sup>+</sup>型の半導体領域 2 0 b の表層一部に形成されたシリサイド層 5 a を介して、上記絶縁層 6 に形成されたコンタクトホール C T 内の導体部 7 に電気的に接続されている。

[0087]

6 V 系デバイス形成領域の n 型のウエルHNWには、低耐圧の p チャネル型のM I S・F E T Q L P 1 は、動作電圧が 6 V のデバイスであり、ゲート電極 G L P 1 と、ゲート絶縁膜 1 0 g と、ソース・ドレイン用の一対の p 型の半導体領域 2 1 , 2 1 とを有している。

[0088]

ゲート電極 G L P 1 は、例えば低抵抗な多結晶シリコンからなり、その上面上にシリサイド層 5 a が形成されている。また、ゲート電極 G L P 1 の側面には、サイドウォール S W が形成されている。ゲート絶縁膜 1 0 g は、例えば酸化シリコンからなり、ゲート電極 G L P 1 と基板 1 S との間に形成されている。ゲート絶縁膜 1 0 g の材料および厚さは、上記と同じである。

[0089]

10

20

30

40

20

30

40

50

上記ソース・ドレイン用の p 型の半導体領域 2 1 , 2 1 は、 n 型のウエル H N W に内包されている。この p 型の半導体領域 2 1 , 2 1 は、チャネル側の p 型の半導体領域 2 1 a と、それに接続された p \*型の半導体領域 2 1 b とを有している。このような半導体領域 2 1 a , 2 1 b には、例えばホウ素 (P) 等のような同一導電型の不純物が含有されているが、 p \*型の半導体領域 2 1 b の不純物濃度の方が、 p \*型の半導体領域 2 1 a の不純物濃度よりも高くなるように設定されている。

#### [0090]

このソース・ドレイン用の半導体領域21,21は、p<sup>+</sup>型の半導体領域21bの表層一部に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7に電気的に接続されている。

[0091]

1.5 V系デバイス形成領域のp型のウエルPWには、低耐圧のnチャネル型のMIS・FETQLN2が形成されている。nチャネル型のMIS・FETQLN2は、動作電圧が1.5 Vのデバイスであり、ゲート電極GLN2と、ゲート絶縁膜10hと、ソース・ドレイン用の一対のn型の半導体領域22,22を有している。

[0092]

ゲート電極GLN2は、例えば低抵抗な多結晶シリコンからなり、その上面上にシリサイド層5aが形成されている。ゲート電極GLN2の短方向の長さ(またはゲート長)は、上記低耐圧(動作電圧が6V)のnチャネル型のMIS・FETQLN1のゲート電極GLN1の短方向の長さ(またはゲート長)よりも小さい。このようなゲート電極GLN2の側面にも、サイドウォールSWが形成されている。

[0093]

ゲート絶縁膜10hは、例えば酸化シリコンからなり、ゲート電極GLN2と基板1Sとの間に形成されている。ゲート絶縁膜10hの厚さは、上記低耐圧部のMIS・FETのゲート絶縁膜よりも薄く、例えば3.7nm程度である。

[0094]

[0095]

また、ソース・ドレイン用の一対のn型の半導体領域22の構成として、上記n 型の半導体領域22aのチャネル側の端部近傍には、p型の半導体領域(p型のハロー領域またはp型のパンチスルーストッパ領域)が形成されている。これにより、上記nチャネル型のMIS・FETQLN2の短チャネル効果を抑制または防止することが可能になっている。

[0096]

このようなソース・ドレイン用の半導体領域22,22は、 n <sup>†</sup>型の半導体領域22 b の表層一部に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7に電気的に接続されている。

[0097]

1.5 V系デバイス形成領域のn型のウエルPWには、低耐圧のpチャネル型のMIS・FETQLP2が形成されている。pチャネル型のMIS・FETQLP2は、動作電圧が1.5 Vのデバイスであり、ゲート電極GLP2と、ゲート絶縁膜10hと、ソース・ドレイン用の一対のp型の半導体領域23,23とを有している。

[0098]

ゲート電極GLP2は、例えば低抵抗な多結晶シリコンからなり、その上面上にシリサイド層5aが形成されている。ゲート電極GLP2の短方向の長さ(またはゲート長)は

20

30

40

50

、上記低耐圧(動作電圧が6V)のpチャネル型のMIS・FETQLP1のゲート電極GLP1の短方向の長さ(またはゲート長)よりも小さい。このようなゲート電極GLP2の側面にも、サイドウォールSWが形成されている。pチャネル型のMIS・FETQLP2のゲート絶縁膜10hは、ゲート電極GLP2と基板1Sとの間に形成されている。このゲート絶縁膜10hの材料および厚さは、上記と同じである。

## [0099]

上記ソース・ドレイン用の p 型の半導体領域 2 3 , 2 3 は、 n 型のウエル N W に内包されている。この p 型の半導体領域 2 3 , 2 3 は、チャネル側の p 型の半導体領域 2 3 a と、それに接続された n 节型の半導体領域 2 3 b とを有している。このような半導体領域 2 3 a , 2 3 b には、例えばホウ素 (B) 等のような同一導電型の不純物が含有されているが、 p 节型の半導体領域 2 3 b の不純物濃度の方が、 p 型の半導体領域 2 3 a の不純物濃度よりも高くなるように設定されている。

#### [0100]

また、ソース・ドレイン用の一対のp型の半導体領域23の構成として、上記p 型の半導体領域23aのチャネル側の端部近傍には、n型の半導体領域(n型のハロー領域またはn型のパンチスルーストッパ領域)が形成されている。これにより、上記pチャネル型のMIS・FETQLP1よりも小さいpチャネル型のMIS・FETQLP2の短チャネル効果を抑制または防止することが可能になっている。

#### [0101]

このようなソース・ドレイン用の半導体領域23,23は、p<sup>+</sup>型の半導体領域23bの表層一部に形成されたシリサイド層5aを介して、上記絶縁層6に形成されたコンタクトホールCT内の導体部7に電気的に接続されている。

## [0102]

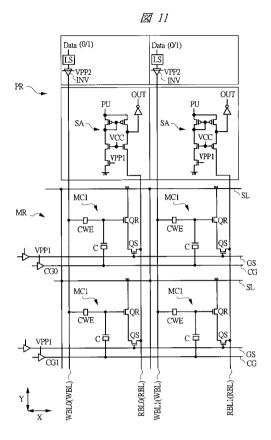

次に、図11は本実施の形態1の半導体装置におけるフラッシュメモリの要部回路図を示している。

#### [0103]

このフラッシュメモリは、上記メモリセルアレイMRと周辺回路領域PRとを有している。メモリセルアレイMRには、第1方向Yに延在する複数のデータ書き込み・消去用のビット線WBL(WBL0,WBL1・・・)と、データ読み出し用のビット線RBL(RBL0,RBL2・・・)とが第2方向Xに沿って配置されている。また、メモリセルアレイMRには、上記ビット線WBL,RBLに対して直交する第2方向Xに沿って延在する複数の制御ゲート配線(ワード線)CG(CG0,CG1・・・)と、複数のソース線SLと、複数の選択線GSとが第1方向Yに沿って配置されている。

## [0104]

各データ書き込み・消去用のビット線WBLは、上記周辺回路領域PRに配置されたデータ(0/1)入力用のインバータ回路INVに電気的に接続されている。また、各データ読み出し用のビット線RBLは、上記周辺回路領域PRに配置されたセンスアンプ回路SAに電気的に接続されている。センスアンプ回路SAは、例えばカレントミラー形とされている。そして、このようなビット線WBL,RBLと、制御ゲート配線CG、ソース線SLおよび選択線GSとの格子状交点の近傍に、1ビット分のメモリセルMC1が電気的に接続されている。ここでは、1ビットが1つのメモリセルMC1で構成されている場合が例示されている。

### [0105]

各メモリセルMC1は、データ書き込み・消去用の容量部(電荷注入放出部)CWEと、データ読み出し用のMIS・FETQRと、容量部Cと、選択MIS・FETQSとを有している。各ビットのデータ書き込み・消去用の電荷注入放出部CWEの一方の電極は、データ書き込み・消去用のビット線WBLに電気的に接続されている。また、データ書き込み・消去用の電荷注入放出部CWEの他方の電極(浮遊ゲート電極FG)に電気的に接続されるとともに、容量部Cの一方の電極(浮遊ゲート電極FG)に電気的に接続されている

20

30

40

50

。そして、その容量部 C は他方の電極(制御ゲート電極 C G W )は制御ゲート配線 C G に電気的に接続されている。一方、各ビットの 1 つのメモリセル M C のデータ読み出し用の M I S・F E T Q R のドレインは、選択 M I S・F E T Q Sを介してデータ読み出し用のビット線 R B L に電気的に接続され、ソースはソース線 S L に電気的に接続されている。選択 M I S・F E T Q S のゲート電極は、選択線 G S に電気的に接続されている。

#### [0106]

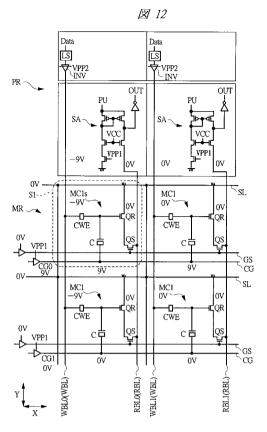

次に、このようなフラッシュメモリにおけるデータ書き込み動作例を図12~図15により説明する。

### [0107]

図12は図11のフラッシュメモリのデータ書き込み動作時における各部への印加電圧を示している。破線S1はデータ書き込み対象のメモリセルMC1(以下、選択メモリセルMC1sという)を示している。なお、ここでは、電子を浮遊ゲート電極に注入することをデータ書き込みと定義するが、その逆に浮遊ゲート電極の電子を抜き取ることをデータ書き込みと定義することもできる。

#### [0108]

データの書き込み時には、上記選択メモリセルMC1sの上記容量部Cの他方の電極が接続されている制御ゲート配線CG0(CG)に、例えば9V程度の正の制御電圧を印加する。それ以外の制御ゲート配線CG1(CG)には、例えば0Vの電圧を印加する。また、選択メモリセルMC1sの上記データ書き込み・消去用の電荷注入放出部CWEの一方の電極が電気的に接続されているデータ書き込み・消去用のビット線WBL0(WBL)に、例えば・9V程度の負の電圧を印加する。それ以外のデータ書き込み・消去用のビット線WBL1(WBL)には、例えば0Vの電圧を印加する。また、選択線GS、ソース線SLおよびデータ読み出し用のビット線RBLに、例えば0Vを印加する。これにより、選択メモリセルMC1sのデータ書き込み・消去用の電荷注入放出部CWEの浮遊ゲート電極にチャネル全面のFNトンネル電流により電子を注入し、データを書き込む。

#### [0109]

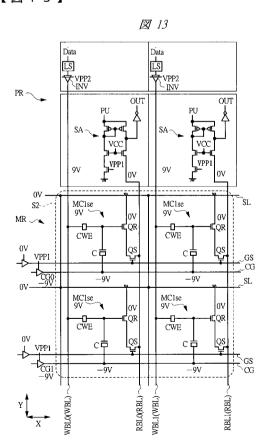

次に、図13は図11のフラッシュメモリのデーター括消去動作時における各部への印加電圧を示している。破線S2はデーター括消去対象の複数のメモリセルMC1(以下、選択メモリセルMC1seという)を示している。なお、ここでは、浮遊ゲート電極の電子を引き抜くことをデータ消去と定義するが、その逆に浮遊ゲート電極に電子を注入することをデータ消去と定義することもできる。

## [0110]

データー括消去時には、上記複数の選択メモリセルMC1seの上記容量部Cの他方の電極が接続されている制御ゲート配線CG0,CG1(CG)に、例えば・9V程度の負の制御電圧を印加する。また、選択メモリセルMC1seの上記データ書き込み・消去用の電荷注入放出部CWEの一方の電極が電気的に接続されているデータ書き込み・消去用のビット線WBL0,WBL1(WBL)に、例えば9V程度の負の電圧を印加する。また、選択線GS、ソース線SLおよびデータ読み出し用のビット線RBLに、例えば0Vを印加する。これにより、データー括消去を行う複数の選択メモリセルMC1seのデータ書き込み・消去用の電荷注入放出部CWEの浮遊ゲート電極に蓄積された電子をチャネル全面のFNトンネル電流により放出し、複数の選択メモリセルMC1seのデータを一括消去する。

### [0111]

次に、図14は図11のフラッシュメモリのデータ・ビット単位消去動作時における各部への印加電圧を示している。破線S3はデータ括消去対象のメモリセルMC(選択メモリセルMC1seという)を示している。

#### [0112]

20

30

40

50

加する。また、選択メモリセルMC1seの上記データ書き込み・消去用の電荷注入放出部CWEの一方の電極が電気的に接続されているデータ書き込み・消去用のビット線WBL0(WBL)に、例えば9V程度の正の電圧を印加する。それ以外のデータ書き込み・消去用のビット線WBL1(WBL)には、例えば0Vの電圧を印加する。また、選択線GS、ソース線SLおよびデータ読み出し用のビット線RBLに、例えば0Vを印加する。これにより、データ消去対象の選択メモリセルMC1seのデータ書き込み・消去用の電荷注入放出部CWE,CWEの浮遊ゲート電極に蓄積された電子をチャネル全面のFNトンネル電流により放出し、データ消去対象の選択メモリセルMC1seのデータを消去する。

### [0113]

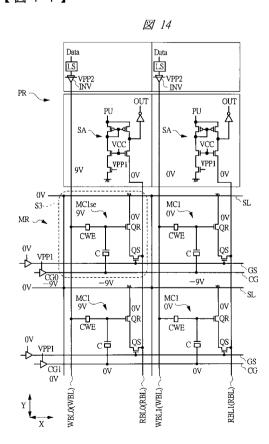

次に、図15は図11のフラッシュメモリのデータ読み出し動作時における各部への印加電圧を示している。破線S4はデータ読み出し対象のメモリセルMC1(以下、選択メモリセルMC1rという)を示している。

#### [0114]

データ読み出し時には、上記選択メモリセルMC1rの上記容量部Cの他方の電極が接続されている制御ゲート配線CG0(CG)に、例えば3V程度の制御電圧を印加する。それ以外の制御ゲート配線CG1(CG)には、例えば0Vの電圧を印加する。また、選択メモリセルMC1rの上記データ書き込み・消去用の電荷注入放出部CWEの一方の電極が電気的に接続されているデータ書き込み・消去用のビット線WBL0,WBL1(WBL)に、例えば0V程度の電圧を印加する。また、上記選択メモリセルMC1rの上記選択MIS・FETQSのゲート電極が電気的に接続されている選択線GSに、例えば3V程度の電圧を印加する。そして、データ読み出し用のビット線RBLに、例えば1V程度の電圧を印加する。さらに、ソース線SLに、例えば0Vを印加する。これにより、データ読み出し対象の選択メモリセルMC1rのデータ読み出し用のMIS・FETQRをオン条件とし、そのデータ読み出し用のMIS・FETQRのチャネルにドレイン電流が流れるか否かにより、選択メモリセルMC1rに記憶されているデータが0/1のいずれなのかを読み出す。

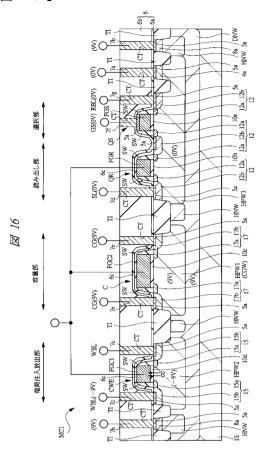

### [0115]

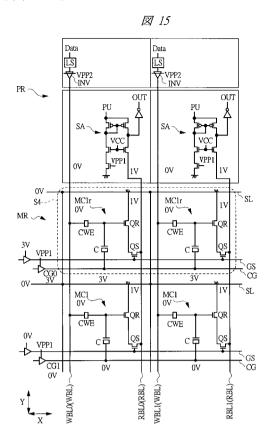

次に、本実施の形態 1 のフラッシュメモリの動作時のメモリセルM C 1 の様子を図 1 6 ~ 図 1 8 により説明する。なお、図中のかっこ内の数字は印加電圧を示している。

#### [0116]

図16は本実施の形態1のフラッシュメモリのデータ書き込み動作時の図3のY1-Y 1線の断面図を示している。

## [0117]

ここでは導体部7 b を通じて n 型のウエル H N W および n 型の埋込ウエル D N W に、例えば9 V 程度の電圧を印加して基板1 S と p 型のウエル H P W 1 ~ H P W 3 とを電気的に分離する。また、上記制御ゲート配線 C G から導体部7 e を通じて容量部 C の制御ゲート電極 C G W に、例えば9 V 程度の正の制御電圧を印加する。また、上記データ書き込み・消去用のビット線 W B L から導体部7 c を通じて電荷注入放出部 C W E の一方の電極( p 型の半導体領域15 および p 型のウエル H P W 2) に、例えば-9 V 程度の負の電圧を印加する。

#### [0118]

また、導体部7aを通じて、p型のウエルHPW3に、例えば0Vを印加する。また、上記選択線GSから導体部7fを通じて選択MIS・FETQSのゲート電極FGSに、例えば0Vを印加する。また、上記ソース線SLから導体部7dを通じてデータ読み出し用のMIS・FETQRの一方のn型の半導体領域12に、例えば0Vを印加する。また、データ読み出し用のビット線RBLから導体部7gを通じて、選択MIS・FETQSの一方のn型の半導体領域12に、例えば0Vを印加する。

#### [0119]

これにより、選択したメモリセルMC1のデータ書き込み・消去用の電荷注入放出部C

20

30

40

50

WEにおいて、p型のウエルHPW2の電子eを、チャネル全面のFNトンネル電流により容量絶縁膜10dを通じて容量電極FGC1(浮遊ゲート電極FG)に注入し、データを書き込む。

### [0120]

ここで、上記のように、電荷注入放出部 C W E の半導体領域 1 5 の片方を、 n ・型の半導体領域 1 5 a および n ・型の半導体領域 1 5 b で形成した場合の効果について説明する。 n 型の半導体領域 1 5 が存在する場合、データ書込み時には、 n 型の半導体領域 1 5 から延びる反転層の形成が促進される。電子は p 型半導体では少数キャリアであるのに対して n 型半導体では多数キャリアである。このため、注入電子を容量電極 F G C 1 の直下の反転層に容易に供給することができる。その結果、実効的なカップリング容量を増大させることができるので、容量電極 F G C 1 の電位を効率的にコントロールすることができる。したがって、データの書き込み速度を向上させることができる。また、データ書き込み速度のバラツキも低減できる。

## [0121]

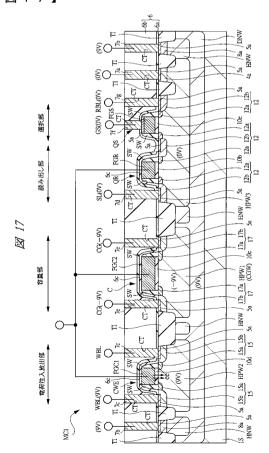

次に、図17は本実施の形態1のフラッシュメモリのデータ消去動作時の図3のY1 -Y1線の断面図を示している。

#### [0122]

ここでは導体部7 b を通じて n 型のウエル H N W および n 型の埋込ウエル D N W に、例えば9 V 程度の電圧を印加して基板1 S と p 型のウエル H P W 1 ~ H P W 3 とを電気的に分離する。また、上記制御ゲート配線 C G から導体部7 e を通じて容量部 C の制御ゲート電極 C G W に、例えば-9 V 程度の負の制御電圧を印加する。また、上記データ書き込み・消去用のビット線W B L から導体部7 c を通じて電荷注入放出部 C W E の一方の電極(p型の半導体領域15 およびp型のウエル H P W 2)に、例えば9 V 程度の正の電圧を印加する。

### [0123]

また、導体部7aを通じて、p型のウエルHPW3に、例えば0Vを印加する。また、上記選択線GSから導体部7fを通じて選択MIS・FETQSのゲート電極FGSに、例えば0Vを印加する。また、上記ソース線SLから導体部7dを通じてデータ読み出し用のMIS・FETQRの一方のn型の半導体領域12に、例えば0Vを印加する。また、データ読み出し用のビット線RBLから導体部7gを通じて、選択MIS・FETQSの一方のn型の半導体領域12に、例えば0Vを印加する。

## [0124]

これにより、選択したメモリセルMC1のデータ書き込み・消去用の電荷注入放出部CWEにおいて、容量電極FGC1(浮遊ゲート電極FG)に蓄積された電子eを、チャネル全面のFNトンネル電流により容量絶縁膜10dを通じてp型のウエルHPW2に放出し、データを消去する。

## [0125]

ここで、上記のように、容量部 C の半導体領域 1 7 の片方を、n ・型の半導体領域 1 7 a および n ・型の半導体領域 1 7 b で形成した場合の効果について説明する。データ消去時には、n型の半導体領域 1 7 を追加したことにより、電子を容量絶縁膜 1 0 c の直下にスムーズに供給することができる。このため、反転層を素早く形成することができるので、p型のウエルHPW 1 を素早く・9 V に固定することができる。その結果、実効的なカップリング容量を増大させることができるので、容量電極 F G C 2 の電位を効率的にコントロールすることができる。したがって、データ消去速度を向上させることができる。また、データ消去速度のバラツキも低減できる。

## [0126]

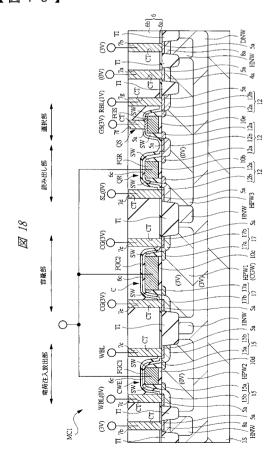

次に、図18は本実施の形態1のフラッシュメモリのデータ読み出し動作時の図3のY 1-Y1線の断面図を示している。

### [0127]

ここでは導体部7bを通じてn型のウエルHNWおよびn型の埋込ウエルDNWに、例

えば3V程度の電圧を印加して基板1Sとp型のウエルHPW1~HPW3とを電気的に分離する。

## [0128]

また、上記制御ゲート配線CGから導体部7eを通じて容量部Cの制御ゲート電極CGWに、例えば3V程度の正の制御電圧を印加する。これにより、データ読み出し用のMIS・FETORのゲート電極FGRに正の電圧を印加する。

#### [0129]

また、導体部7aを通じて、p型のウエルHPW3に、例えば0Vを印加する。また、上記選択線GSから導体部7fを通じて選択MIS・FETQSのゲート電極FGSに、例えば3Vを印加する。また、上記ソース線SLから導体部7dを通じてデータ読み出し用のMIS・FETQRの一方のn型の半導体領域12に、例えば0Vを印加する。また、データ読み出し用のビット線RBLから導体部7gを通じて、選択MIS・FETQSの一方のn型の半導体領域12に、例えば1Vを印加する。

## [0130]

また、上記データ書き込み・消去用のビット線WBLから導体部7cを通じて電荷注入放出部CWEの一方の電極(p型の半導体領域15およびp型のウエルHPW2)に、例えば0Vの電圧を印加する。

## [0131]

これにより、選択したメモリセルMC1のデータ読み出し用のMIS・FETQRをオン条件とし、そのデータ読み出し用のMIS・FETQRのチャネルにドレイン電流が流れるか否かにより、選択メモリセルMC1に記憶されているデータが0/1のいずれなのかを読み出す。

## [0132]

このような本実施の形態1によれば、データ書き換え領域(電荷注入放出部CWE)、データ読み出し領域(データ読み出し用のMIS・FETQR)および容量結合領域(容量部C)をそれぞれ別々のp型のウエルHPW1~HPW3内に形成し、それぞれをn型のウエルHNWおよびn型の埋込ウエルDNWにより分離する。データ書き換えは、容量素子で行う。

### [0133]

これにより、フラッシュメモリのデータ書き換え領域において、上記カットオフ用のトランジスタを設ける必要がなくなるので、半導体装置の小型化を推進できる。

## [0134]

また、データ書き換え用の素子を容量素子で形成し、チャネル全面のFNトンネル電流によるデータ書き換えにおいて、p型の半導体領域15とp型のウエルHPW2とは同電位になるので、接合耐圧の問題が生じることもない。このため、フラッシュメモリのメモリセルMC1の劣化を抑制または防止でき、フラッシュメモリの動作信頼性を向上させることができる。

#### [0135]

また、タイミング設計が不要となるので、フラッシュメモリの周辺回路の規模を小さく抑えることができるので、半導体装置の小型化を推進できる。また、データ書き換えを、最も消費電流が小さく、低電圧における単一電源書き換えに適したチャネル全面のFNトンネル電流により行えるので、内部昇圧回路による、単一電源化が容易である。

## [0136]

さらに、データ書き込みおよび消去において、ホール発生のないチャネルFNトンネル 電流を使用するため、データの書き換え回数を向上させることができる。

## [0137]

また、データ書き換え領域(電荷注入放出部CWE)と、データ読み出し領域(データ読み出し用のMIS・FETQR)とをそれぞれ別々のp型のウエルHPW2,HPW3内に形成したことにより、データ書き換えを安定化させることができる。このため、フラッシュメモリの動作信頼性を向上させることができる。

10

20

30

40

#### [0138]

(実施の形態2)

本実施の形態2においては、特に以下の構成が前記実施の形態1と異なる。

#### [0139]

第1は、メモリセルのデータ読み出し用のMIS・FETのソース・ドレイン用の一対の半導体領域の構成が、主回路の低耐圧部(1.5 Vデバイス)のnチャネル型のMIS・FETのソース・ドレイン用の一対の半導体領域の構成(上記p型のハロー領域を含む)と同一になっている。

### [0140]

第2は、メモリセルのデータ書き込み・消去用の電荷注入放出部のゲート長を短くし、 電荷注入放出部のp型の半導体領域の一部を容量電極の直下の基板の表層に延在(拡散) させている。

#### [0141]

第3は、メモリセルアレイ内において、互いに隣接する電荷注入放出部の p 型のウエルが、上記 n 型のウエルよりも不純物濃度の高い n  $^{+}$  型の半導体領域( n  $^{+}$  型の拡散層)により分離されている。

#### [0142]

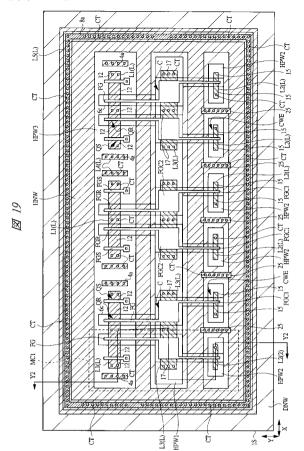

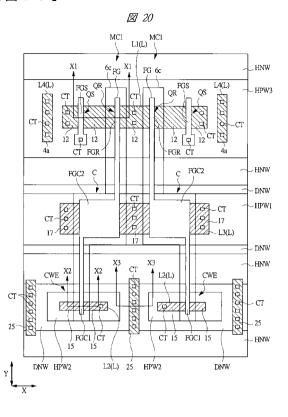

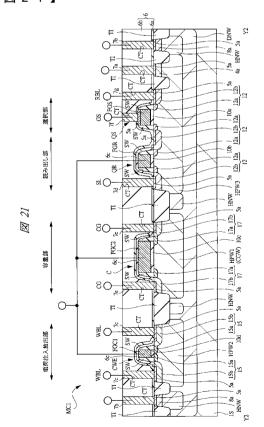

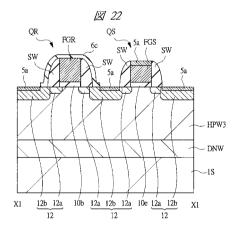

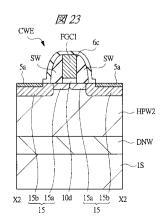

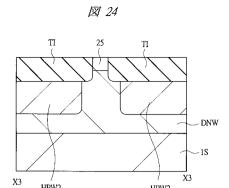

以下、本実施の形態2の半導体装置のフラッシュメモリの構成の具体例を図19~図24により説明する。図19は本実施の形態2の半導体装置におけるフラッシュメモリの平面図、図20は図19のフラッシュメモリの要部拡大平面図、図21は図19のY2-Y2線の断面図、図22は図20のX1-X1線の断面図、図23は図20のX2-X2線の断面図、図24は図20のX3-X3線の断面図を示している。なお、図19および図20は平面図であるが、図面を見易くするために一部にハッチングを付した。

#### [0143]

本実施の形態2においては、上記のように、メモリセルMC1のデータ読み出し用のMIS・FETQRのソース・ドレイン用の一対の半導体領域の構成が、主回路の低耐圧部(1.5Vデバイス)のnチャネル型のMIS・FETQLN2のソース・ドレイン用の一対の半導体領域の構成と同一になっている。

### [0144]

この場合、データ読み出し用のMIS・FETQRのソース・ドレイン用の一対の半導体領域は、前記実施の形態1で説明したようにn 型の半導体領域12 aとn 型の半導体領域12 bとで構成されるn型の半導体領域12を有する他に、n型の半導体領域12 aのチャネル側の端部近傍に形成されたp型の半導体領域(p型のハロー領域またはp型のパンチスルーストッパ領域)を有している。

# [0145]

これにより、データ読み出し用のMIS・FETQRでの短チャネル効果を抑制または防止できるので、データ読み出し用のMIS・FETQRを微細化できる。このため、メモリセルMC1のサイズを縮小することができるので、メモリセルアレイMRの面積を縮小することができる。また、メモリの記憶容量を増大できる。

#### [0146]

また、メモリセルMC1の選択MIS・FETQSのソース・ドレイン用の一対の半導体領域の構成も、主回路の低耐圧部(1.5Vデバイス)のnチャネル型のMIS・FETQLN2のソース・ドレイン用の一対の半導体領域の構成と同一になっている。

## [0147]

この場合、選択MIS・FETQSのソース・ドレイン用の一対の半導体領域は、前記実施の形態 1 で説明したように n 型の半導体領域 1 2 a と n 型の半導体領域 1 2 b とで構成される n 型の半導体領域 1 2 を有する他に、 n 型の半導体領域 1 2 a のチャネル側の端部近傍に形成された p 型の半導体領域( p 型のハロー領域または p 型のパンチスルーストッパ領域)を有している。

## [0148]

50

40

10

20

30

40

50

これにより、選択MIS・FETQSでの短チャネル効果を抑制または防止できるので、選択MIS・FETQSを微細化できる。このため、メモリセルMC1のサイズを縮小することができるので、メモリセルアレイMRの面積を縮小することができる。また、メモリの記憶容量を増大できる。

### [0149]

メモリセルMC1の動作時に、データ読み出し用のMIS・FETQRおよび選択MIS・FETQSのソース・ドレイン用の一対の半導体領域に0Vまたは1Vの電圧しか印加されないので、データ読み出し用のMIS・FETQRおよび選択MIS・FETQSを1.5V系のMIS・FETで形成することができる。

### [0150]

ただし、データ読み出し用のMIS・FETQRおよび選択MIS・FETQSのゲート絶縁膜10b,10eの厚さは、前記実施の形態1で説明したのと同じであり、主回路の低耐圧部(1.5 Vデバイス)のnチャネル型のMIS・FETQLN2のゲート絶縁膜10hよりも厚く形成されている。これは、動作時にゲート絶縁膜10b,10eに3V以上の電位差が発生するためである。

#### [0151]

また、本実施の形態 2 においては、メモリセルMC1のデータ書き込み・消去用の電荷注入放出部CWEの容量電極FGC1の第2方向Xの長さ(ゲート長)が、データ読み出し用のMIS・FETQRのゲート電極FGRの第2方向Xの長さ(ゲート長)よりも短くなっている。電荷注入放出部CWEの容量電極FGC1の第2方向Xの両側の一対のp型の半導体領域15 a ,15 a の一部)は、容量電極FGC1の直下の基板1Sの表層に延在(拡散)されている。ここでは、図21および図23に示すように、上記一対のp型の半導体領域15,15の各々のp~型の半導体領域15 a ,15 a のチャネル側の先端部が、容量電極FGC1の直下に入り込み、互いに接している場合が例示されている。

#### [0152]

前記実施の形態1のように、電荷注入放出部CWEのp型の半導体領域15の一部が容量電極FGC1の直下の基板1Sの表層まで延びていない場合、データ書き込みに際して電荷注入放出部CWEのp型のウエルHPW2に、例えば-9V程度の負電圧が印加されると、容量絶縁膜10dの直下の基板1Sの表層に空乏層が形成される。この結果、カップリング容量が低下し、データの書き込み速度が低下したり、データの書き込み速度にバラツキが生じたりする場合がある。

#### [0153]

これに対して、本実施の形態2のように容量電極FGC1の直下にp型の半導体領域15の一部が延在(拡散)している場合、容量電極FGC1の直下の基板15の表層におけるp型不純物の濃度を高くすることができるので、データ書き換え(書き込み・消去)に際して、容量電極FGC1の直下の基板15の表層に空乏層が形成されるのを抑制または防止することができる。これにより、実効的なカップリング容量を増大させることができるので、容量電極FGC1(浮遊ゲート電極FG)の電位を効率的にコントロールすることができる。したがって、データの書き込み速度を向上させることができる。また、データの書き込み速度のバラツキを低減することができる。

#### [0154]

また、本実施の形態 2 においては、メモリセルアレイMR内において、第 2 方向 X に沿って互いに隣接する電荷注入放出部 C W E の p 型のウエル H P W 2 が、その互いに隣接する p 型のウエル H P W 2 の間に形成された n  $^+$ 型の半導体領域( n  $^+$ 型の拡散層) 2 5 により分離されている。 n  $^+$ 型の半導体領域 2 5 の不純物濃度は、上記 n 型のウエル H N W および n 型の埋込ウエル D N W の不純物濃度よりも高い。

#### [0155]

前記実施の形態 1 のように、互いに隣接する電荷注入放出部 C W E の p 型のウエル H P W 2 , H P W 2 同士が n 型のウエル H N W および n 型の埋込ウエル D N W により分離され

20

30

40

50

ている場合、 p型のウエルHPW2,HPW2の隣接間に寄生MOS・FETが形成されるのを阻止する観点等から、 p型のウエルHPW2,HPW2の隣接間を狭くすることに限界がある。

### [0156]

これに対して、本実施の形態2のように、第2方向Xに沿って互いに隣接するp型のウエルHPW2がn<sup>+</sup>型の半導体領域(n<sup>+</sup>型の拡散層)25により分離されている場合、n<sup>+</sup>型の半導体領域25の不純物濃度が上記n型のウエルHNWおよびn型の埋込ウエルDNWの不純物濃度よりも高いので、p型のウエルHPW2,HPW2の隣接間を狭くしても寄生MOS・FETの形成を抑制または防止できる。したがって、第2方向Xに沿って互いに隣接するp型のウエルHPW2,HPW2の隣接間を前記実施の形態1の場合よりも狭くすることができる。このため、メモリセルアレイMRの面積を縮小することができる。また、メモリの記憶容量を増大できる。

#### [0157]

また、 n <sup>+</sup> 型の半導体領域 2 5 は、主回路のデバイスを形成する際に同時に形成する。これにより、 n <sup>+</sup> 型の半導体領域 2 5 を形成したからといって半導体装置の製造工程が増大することもない。したがって、半導体装置の製造時間の増大を防止でき、また、半導体装置のコストの増大を防止できる。

#### [0158]

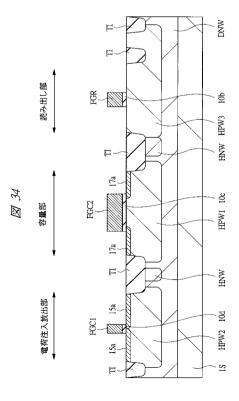

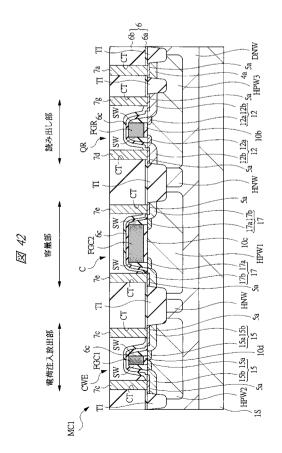

次に、本実施の形態の半導体装置の製造方法の一例を図25~図42により説明する。 なお、図25~図42は、本実施の形態の半導体装置の製造工程中の基板1S(この段階 ではウエハと称する略円形状の半導体薄板)の要部断面図を示している。また、ここでは 、低耐圧部とフラッシュメモリとを示し高耐圧部は図示しない。また、選択MISも省略 する。

#### [0159]

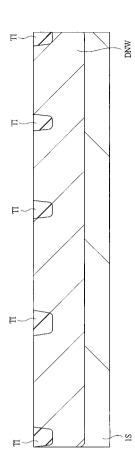

まず、図25および図26に示すように、p型の基板1S(ウエハ)を用意する。基板1Sは、厚さ方向に沿って互いに反対側に位置する第1主面および第2主面を有している

### [0160]

続いて、低耐圧部、フラッシュメモリのメモリセル形成領域および高耐圧部に、 n 型の埋込ウエル D N Wをフォトリソグラフィ(以下、単にリソグラフィという)工程およびイオン注入工程等により同時に形成する。上記リソグラフィ工程は、フォトレジスト(以下、単にレジストという)膜の塗布、露光および現像等により所望のレジストパターンを形成する一連の工程である。イオン注入工程では、リソグラフィ工程を経て基板 1 S の主面上に形成されたレジストパターンをマスクとして、基板 1 S の所望の部分に所望の不純物を選択的に導入する。ここでのレジストパターンは、不純物の導入領域が露出され、それ以外の領域が覆われるようなパターンとされている。

## [0161]

なお、高耐圧部においては、n型の埋込ウエルDNWの形成のための不純物導入工程に 先立ってp型の埋込ウエルDPWをフォトリソグラフィエ程およびイオン注入工程等によ り形成する。

## [0162]

その後、基板1Sの第1主面の分離領域に分離溝を形成した後、その分離溝内に絶縁膜を埋め込むことにより、溝形の分離部TIを形成する。これにより、活性領域を規定する。分離部TIはp型の埋込ウエルDPWおよびn型の埋込ウエルDNWの形成工程前に形成しても良い。

## [0163]

次いで、前記高耐圧部のnチャネル型のMIS・FET形成領域に、上記n型の半導体領域NVをリソグラフィ工程およびイオン注入工程等により形成し、高耐圧部のpチャネル型のMIS・FET形成領域に、上記p型の半導体領域PVをリソグラフィ工程およびイオン注入工程等により形成する(図9参照)。n型の半導体領域NVの不純物濃度はn

型の埋込ウエルDNWの不純物濃度よりも高く、p型の半導体領域PVの不純物濃度はp型の埋込ウエルDPWの不純物濃度よりも高い。

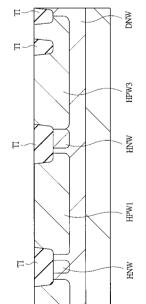

#### [0164]

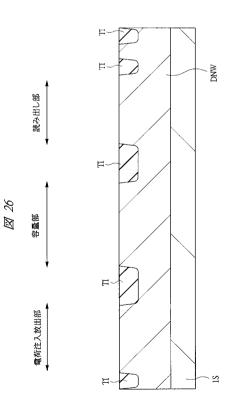

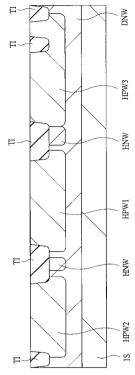

続いて、図27および図28に示すように、低耐圧部の6Vデバイス形成領域のpチャネル型のMIS・FET形成領域およびフラッシュメモリのメモリセル形成領域の分離領域に、n型のウエルHNWをリソグラフィ工程およびイオン注入工程等により形成する。

#### [0165]

続いて、低耐圧部の6Vデバイス形成領域のnチャネル型のMIS・FET形成領域およびフラッシュメモリのメモリセル形成領域に、p型のウエルHPW1~HPW4をリソグラフィ工程およびイオン注入工程等により同時に形成する。

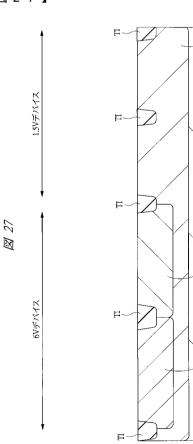

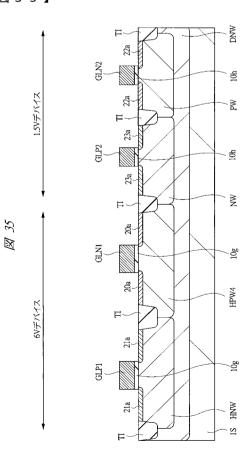

#### [0166]

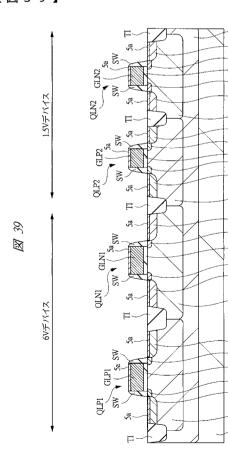

続いて、図29および図30に示すように、低耐圧部の1.5Vデバイス形成領域のpチャネル型のMIS・FET形成領域に、n型のウエルNWをリソグラフィエ程およびイオン注入工程等により形成する。

#### [0167]

続いて、低耐圧部の1.5Vデバイス形成領域のnチャネル型のMIS・FET形成領域に、p型のウエルPWをリソグラフィ工程およびイオン注入工程等により形成する。

## [0168]

その後、図31および図32に示すように、基板1Sの第1主面上に、ゲート絶縁膜10b,10g,10hおよび容量絶縁膜10c,10dを熱酸化法等により形成する。このゲート絶縁膜10b,10gおよび容量絶縁膜10c,10dは同時に形成されており、その厚さは、例えば10nm~20nmが好ましく、例えば13.5nmとされている

#### [0169]

一方、1.5 V デバイス形成領域の p チャネル型の M I S ・ F E T 形成領域および n チャネル型の M I S ・ F E T 形成領域のゲート絶縁膜 1 0 h は同時に形成されており、その厚さは、ゲート絶縁膜 1 0 b , 1 0 g および容量絶縁膜 1 0 c , 1 0 d よりも薄く、例えば 3 . 7 n m 程度である。

### [0170]

このように絶縁膜の厚さを変えるには、例えば次のようにする。基板1Sの第1主面に 熱酸化処理を施すことにより絶縁膜を形成した後、その絶縁膜のうち薄膜部のほうを選択 的に除去する。続いて、基板1Sの第1主面に2回目の熱酸化処理を施す。これにより、 厚膜部に厚い絶縁膜を形成し、薄膜部に薄い絶縁膜を形成する。上記2回目の熱酸化処理 に代えて、CVD(Chemical Vapor Deposition)法等を用い絶縁膜を堆積しても良い。

## [0171]

その後、基板1S(ウエハ)の第1主面上に、例えば低抵抗な多結晶シリコンからなる 導体膜をCVD法等により堆積した後、これをリソグラフィエ程およびエッチング工程に よりパターニングすることにより、ゲート電極GHP,GHN,GLP1,GLN1,G LP2,GLN2,FGSおよび浮遊ゲート電極FG(ゲート電極FGRおよび容量電極 FGC1,FGC2)を同時に形成する。

## [0172]

#### [0173]

続いて、低耐圧部の6Vデバイス形成領域のpチャネル型のMIS・FET形成領域、容量部Cの形成領域およびデータ書き込み・消去用の電荷注入放出部CWEの形成領域に、p ̄型の半導体領域21a,17a,15aをリソグラフィエ程およびイオン注入法等により同時に形成する。

## [0174]

50

40

10

20

20

30

40

50

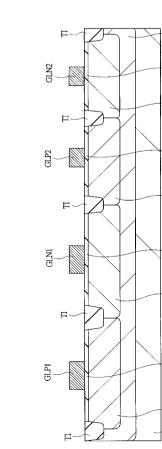

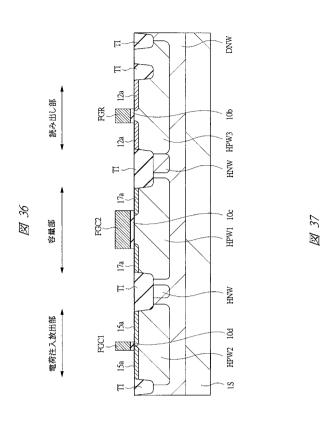

続いて、図35および図36に示すように、低耐圧部の1.5Vデバイス形成領域のnチャネル型のMIS・FET形成領域、データ読み出し用のMIS・FETQRの形成領域および選択MIS・FETQSの形成領域に、n゚型の半導体領域22a,12aをリソグラフィ工程およびイオン注入法等により同時に形成する。

### [0175]

ここでは、n 型の半導体領域22a,12aを形成するためのn型の不純物の導入の他に、上記p型の半導体領域(上記p型のハロー領域)を形成する。その場合、n 型の半導体領域22a,12aの形成時のレジスト膜をマスクとして、上記p型のハロー領域を形成するためのp型の不純物を、例えば基板1Sの第1主面に対して斜めの方向から基板1Sのn 型の半導体領域22a,12aのチャネル側の先端部の近傍(ゲート電極GLN2,FGR,FGSの下方の基板1S部分)に導入する。これにより、1.5Vデバイスのnチャネル型のMISFETおよびデータ読み出し用のMIS・FETQRにおいて短チャネル効果を抑制または防止できる。

#### [0176]

続いて、低耐圧部の1.5 Vデバイス形成領域のpチャネル型のMIS・FET形成領域に、p 型の半導体領域23aをリソグラフィエ程およびイオン注入法等により同時に形成する。

## [0177]

ここでは、 p 型の半導体領域 2 3 a を形成するための p 型の不純物の導入の他に、上記 n 型の半導体領域 (上記 n 型のハロー領域)を形成する。その場合、 p 型の半導体領域 2 3 a の形成時のレジスト膜をマスクとして、上記 n 型のハロー領域を形成するための n 型の不純物を、例えば基板 1 S の第 1 主面に対して斜めの方向から基板 1 S の p 型の半導体領域 2 3 a のチャネル側の先端部の近傍(ゲート電極 G L P 2 の下方の基板 1 S 部分)に導入する。これにより、 1 . 5 V デバイスの p チャネル型の M I S F E T において 短チャネル効果を抑制または防止できる。

## [0178]

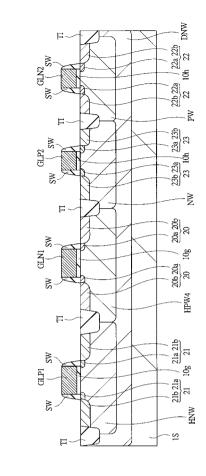

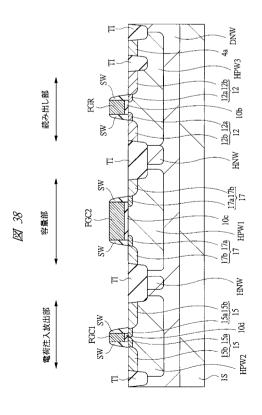

次いで、図37および図38に示すように、基板1Sの第1主面上に、例えば酸化シリコンからなる絶縁膜をCVD法等により堆積した後、これを異方性のドライエッチング法を用いてエッチバックすることにより、ゲート電極GHP,GHN,GLP1,GLN1,GLP2,GLN2,FGR,FGSおよび容量電極FGC1,FGC2の側面にサイドウォールSWを形成する。

## [0179]

続いて、高耐圧部、低耐圧部、データ読み出し部および選択部の n チャネル型の M I S ・ F E T 形成領域に、 n <sup>†</sup>型の半導体領域 1 8 b , 2 0 b , 2 2 b , 1 2 b をリソグラフィエ程およびイオン注入法等により同時に形成する。この時、同時に上記分離用の n <sup>†</sup>型の半導体領域 2 5 を形成する。

## [0180]

続いて、高耐圧部および低耐圧部の p チャネル型の M I S・F E T 形成領域と、容量部および書き込み・消去用の電荷注入放出部形成領域と、 p 型のウエル H P W 3 の引き出し領域とに、 p <sup>+</sup>型の半導体領域 1 9 b , 2 1 b , 2 3 b , 1 5 b , 1 7 b , 4 a をリソグラフィ工程およびイオン注入法等により同時に形成する。

#### [0181]

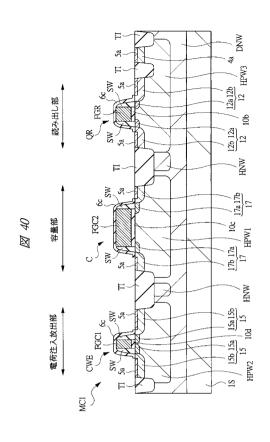

次いで、図39および図40に示すように、サリサイドプロセスにより、基板1Sの第1主面一部、ゲート電極GHP,GHN,GLP1,GLN1,GLP2,GLN2の上面および多結晶シリコン等で形成された抵抗や容量の電極部分にシリサイド層5aを選択的に形成する。

#### [0182]

このシリサイド層 5 a の形成工程に先立って、浮遊ゲート電極 F G (容量電極 F G C 1 , F G C 2 、ゲート電極 F G R ) およびゲート電極 F G S の上面、サイドウォール S W の表面およびその周囲の基板 1 S の第 1 主面一部を覆うようにキャップ絶縁層 6 c を形成す

20

30

50

る。これにより、キャップ絶縁層6cで覆われる浮遊ゲート電極FGの上面にシリサイド層5aが形成されないようにする。

#### [0183]

このようにして、高耐圧部に p チャネル型の M I S・F E T Q H P および n チャネル型の M I S・F E T Q H N を形成する。また、低耐圧部に p チャネル型の M I S・F E T Q L N 1 、Q L N 2 を形成する。また、メモリセル形成領域に、容量部 C、データ書き込み・消去用の電荷注入放出部 C W E およびデータ読み出し用の M I S・F E T Q R を形成する。

### [0184]

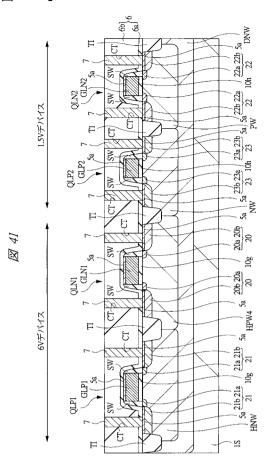

続いて、図41および図42に示すように、基板1S(ウエハ)の第1主面上に、例えば窒化シリコンからなる絶縁層6aをCVD法等により堆積した後、その上に、例えば酸化シリコンからなる絶縁層6bを絶縁層6aよりも厚くCVD法等により堆積する。その後、絶縁層6bに化学的機械的研磨(Chemical Mechanical Polishing:СМР)処理を施し絶縁層6bの上面を平坦化する。

#### [0185]

次いで、絶縁層6にコンタクトホールCTをリソグラフィエ程およびエッチング工程により形成する。続いて、基板1S(ウエハ)の第1主面上に、例えばタングステン(W)等からなる導体膜をCVD法等により堆積した後、それをCMP法等により研磨することでコンタクトホールCT内に導体部7,7a~7gを形成する。これ以降は通常の配線形成工程、検査工程および組立工程を経て半導体装置を製造する。

#### [0186]

本実施の形態2によれば、LCDドライバ回路用のMIS・FETQHP,QHN,QLP1,QLP2,QLN1,QLN2の構成部(一部)と、メモリセルMC1の容量部C、電荷注入放出部CWEおよびMIS・FETQR,QSの構成部(一部)とを同時に形成することができるので、半導体装置の製造工程を簡略化することができる。これにより、半導体装置の製造時間を短縮できる。また、半導体装置のコストを低減できる。

#### [0187]

#### (実施の形態3)

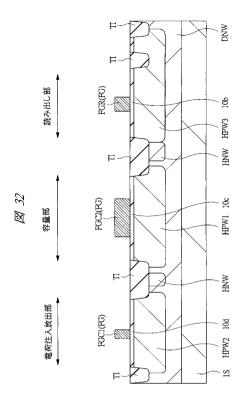

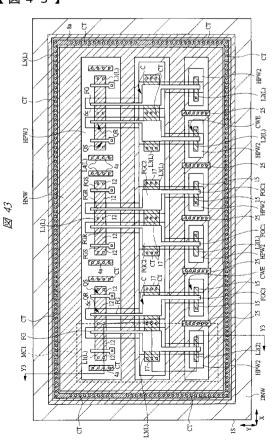

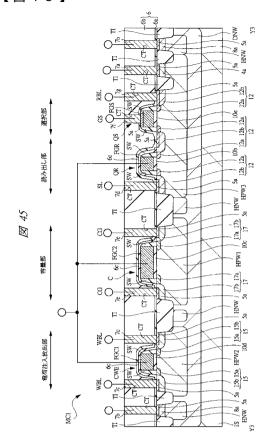

図43は本実施の形態3の半導体装置におけるフラッシュメモリの平面図、図44は図43のフラッシュメモリの要部拡大平面図、図45は図43のY3-Y3線の断面図を示している。なお、図43および図44は平面図であるが、図面を見易くするために一部にハッチングを付した。また、図44のX1-X1線、X2-X2線およびX3-X3線の断面図は、それぞれ図22、図7および図24と同じである。

## [0188]

本実施の形態3においては、電荷注入放出部CWEの容量電極FGC1の第2方向Xの長さ(ゲート長)が、データ読み出し用のMIS・FETQRの第2方向Xの長さ(ゲート長)よりも長い。これ以外の構成は、前記実施の形態1,2で説明したのと同じである

### [0189]

このように本実施の形態3においては、浮遊ゲート電極FGの第2部分(ゲート電極FGR)の第2方向Xの長さと、第3部分(容量電極FGC1)の第2方向Xの長さとを必要に応じて変える(調整する)ことができる。

### [0190]

## (実施の形態4)

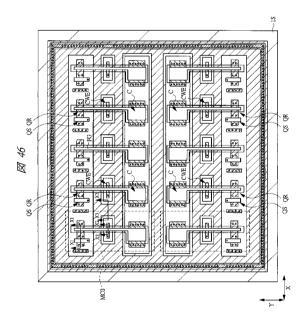

図 4 6 は図 2 の複数のメモリセルMC 0 を第 1 方向 Y にも配置した場合の一例を示している。なお、図 4 6 は平面図であるが、図面を見易くするために一部にハッチングを付した。また、図 4 6 の X 1 - X 1 線、 X 2 - X 2 線および X 3 - X 3 線の断面図は、それぞれ図 6 、図 7 および図 8 で示したものと同じである。

### [0191]

図46の上下のメモリセルMC0は、第1方向Yに沿って互いに対称(ミラー反転した

状態)になっている。このメモリセルMC0の配置の場合、上下のメモリセルMC0の各々の容量部Cが向かい合うような配置になるが、その上下のメモリセルMC0の容量部C 、C同士を電気的に絶縁する必要がある。

#### [0192]

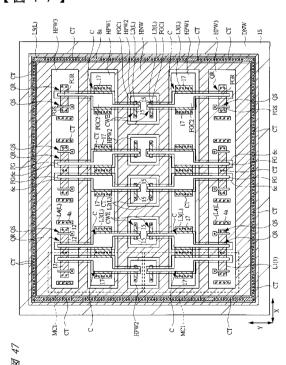

これに対して、図47は本実施の形態4の半導体装置におけるフラッシュメモリの平面図、図48は図47のフラッシュメモリの要部拡大平面図を示している。なお、図47および図48は平面図であるが、図面を見易くするために一部にハッチングを付した。また、図48の×1・×1線、×2・×2線および×3・×3線の断面図は、それぞれ図6、図7および図8で示したものと同じである。

### [0193]

本実施の形態4においても、図47および図48の上下(第1方向Y)のメモリセルMC1は、第1方向Yに沿って互いに対称(ミラー反転した状態)になっている。ただし、本実施の形態4においては、上記のようにメモリセルMC1の各素子の配置を変えたことにより、上下(第1方向Y)のメモリセルMC1のデータ書き込み・消去用の電荷注入放出部CWEが向かい合うようにすることができる。この場合、上下(第1方向Y)のメモリセルMC1の電荷注入放出部CWE同士を同電位にすることができるため、上下のメモリセルMC1の電荷注入放出部CWEが配置されるp型のウエルHPW2を共有させることができる。これにより、上下のメモリセルMC1の隣接間をつめることができるので、メモリセルアレイMRの第1方向Yの寸法を図46の場合よりも縮小する(セル高さを小さくする)ことができる。したがって、メモリセルアレイMRの面積を縮小できる。また、メモリの記憶容量を増大できる。

#### [0194]

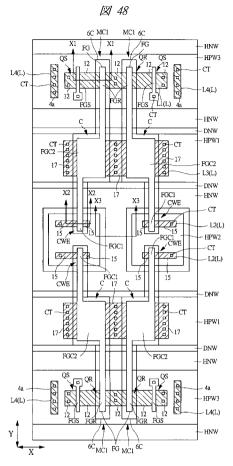

図49は図47のメモリセルアレイMRに配線を配置して示した平面図である。なお、図49は平面図であるが、図面を見易くするために一部にハッチングを付した。

#### [0195]

第1方向Yに沿って延びる配線(データ書き込み・消去用のビット線WBL、データ読み出し用のビット線RBL等を含む)は第1層配線を示し、第2方向Xに沿って延びる配線(制御ゲート配線CG、ソース線SLおよび選択線GS等を含む)は第2層配線を示している。符号のWSLはウエル給電配線を示している。

## [0196]

#### (実施の形態5)

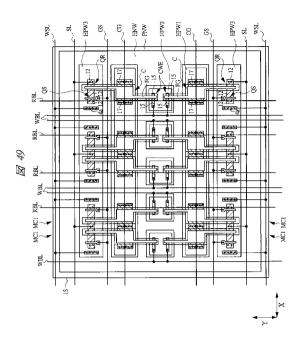

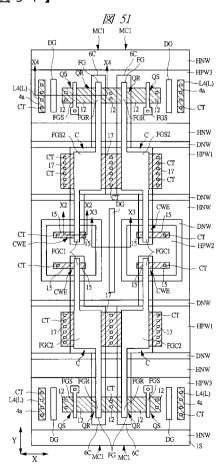

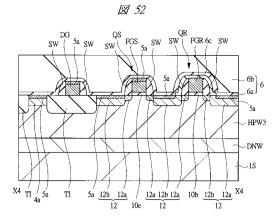

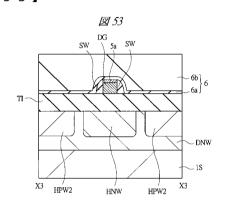

図50は本実施の形態5の半導体装置におけるフラッシュメモリの平面図、図51は図50のフラッシュメモリの要部拡大平面図、図52は図51のX4-X4線の断面図、図53は図51のX3-X3線の断面図を示している。なお、図50および図51は平面図であるが、図面を見易くするために一部にハッチングを付した。また、図51のX2-X2線の断面図は、図7と同じである。

## [0197]

本実施の形態 5 においては、メモリセルアレイMR等の基板 1 S の第 1 主面上の空き領域 (分離部TIの形成領域)にダミーゲートDGが配置されている。このダミーゲートDGは、絶縁層 6 の上面の平坦性やパターンの繰り返し配置を考慮したもので、他の部分とは特に電気的に接続されることのないパターンである。

#### [0198]

このようなダミーゲートDGを設けることにより、絶縁層6の上面の平坦性を向上させることができる。このため、例えば絶縁層6上に形成される配線や絶縁層6に形成されるコンタクトホールCTの加工精度を向上させることができる。

## [0199]

ダミーゲートDGの構成は、上記選択MIS・FETQSのゲート電極FGSの構成と同じである。ダミーゲートDGの上面にはシリサイド層5aが形成されている。また、ダミーゲートDGの側面にはサイドウォールSWが形成されている。

### [0200]

10

20

30

このようなダミーゲートDGは、例えば多結晶シリコンからなり、上記浮遊ゲート電極 FG、ゲート電極FGSおよび上記ゲート電極GLN1,GLN2,GLP1,GLP2 等の形成工程時に同時に形成されている。ダミーゲートDG上のシリサイド層 5 a も、上 記ゲート電極FGS等の上にシリサイド層5aを形成するためのサリサイド工程の際に同 時に形成されている。また、ダミーゲートDGの側面のサイドウォールSWもゲート電極 FGS等の側面にサイドウォールSWを形成する際に動じに形成されている。これにより 、ダミーゲートDGを設けたからといって半導体装置の製造工程が増大することもない。

#### [0201]

なお、ここでは、ダミーゲートDGが、活性領域L2,L4の間や第2方向Xに隣接す るp型のウエルHPW2の隣接間に配置されている場合が例示されているが、これに限定 されるものではない。これ以外の構成は前記実施の形態4と同じである。

10

### [0202]

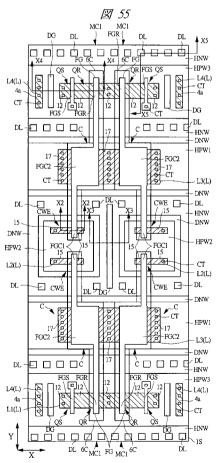

#### (実施の形態6)

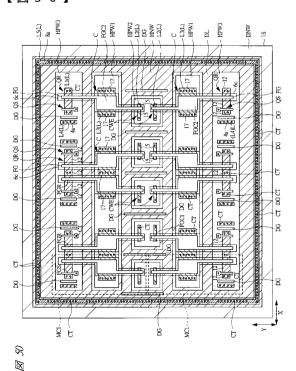

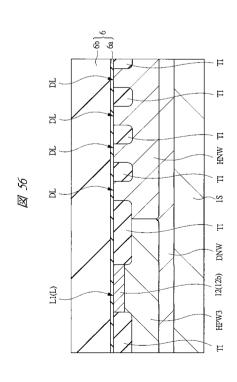

図54は本実施の形態6の半導体装置におけるフラッシュメモリの平面図、図55は図 5 4 のフラッシュメモリの要部拡大平面図、図 5 6 は図 5 5 の X 5 - X 5 線の断面図を示 している。なお、図54および図55は平面図であるが、図面を見易くするために一部に ハッチングを付した。また、図 5 5 の X 2 - X 2 線、 X 3 - X 3 線および X 4 - X 4 線の 断面図は、それぞれ図7、図53および図52と同じである。

[0203]

20

本実施の形態6においては、メモリセルアレイMR等の基板1Sの第1主面上の空き領 域(分離部TIの形成領域)にダミー活性領域DLが配置されている。このダミー活性領 域DLは、絶縁層6の上面の平坦性を考慮したもので、素子が形成されない領域である。

#### [0204]

このようなダミー活性領域DLを設けることにより、絶縁層6の上面の平坦性を向上さ せることができる。このため、例えば絶縁層6上に形成される配線や絶縁層6に形成され るコンタクトホールCTの加工精度を向上させることができる。

[0205]

ダミー活性領域DLの構成は、上記活性領域Lと同じである。また、ダミー活性領域D Lは、活性領域Lと同時に形成される。これにより、ダミー活性領域DLを設けたからと いって半導体装置の製造工程が増大することもない。

30

#### [0206]

なお、ここでは、平面正方形状の複数のダミー活性領域DLが配置されている場合が例 示されているが、これに限定されるものではなく、例えばダミー活性領域DLの平面形状 を長方形状や帯状にしても良い。これ以外の構成は前記実施の形態4,5と同じである。

[0207]

(実施の形態7)

本実施の形態7においては、前記実施の形態2で説明したメモリセルアレイを前記実施 の形態 4 で説明したのと同様に第 1 方向 Y に沿って 2 段に配置した場合について説明する 。これ以外の構成は、前記実施の形態2,4で説明したのと同じである。

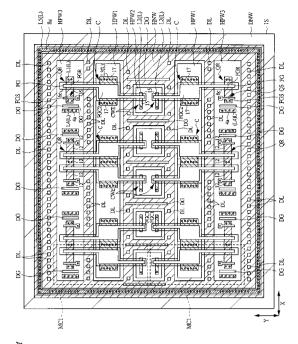

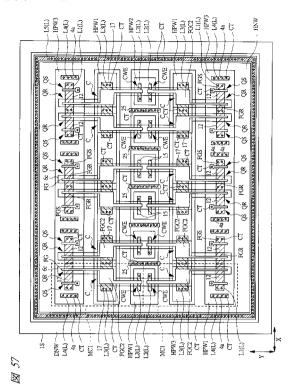

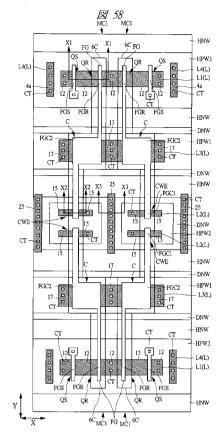

[0208]

40

図57は本実施の形態7の半導体装置におけるフラッシュメモリの平面図、図58は図 57のフラッシュメモリの要部拡大平面図を示している。なお、図57および図58は平 面図であるが、図面を見易くするために一部にハッチングを付した。また、図58のX1 - X 1 線、X 2 - X 2 線および X 3 - X 3 線の断面図は、それぞれ図 2 2 、図 2 3 および 図24と同じである。

# [0209]

本実施の形態7においては、前記実施の形態4と同様に、前記図57および図58の上 下(第1方向Y)のメモリセルMC1が、第1方向Yに沿って互いに対称(ミラー反転し た状態)になっている。また、前記実施の形態4と同様に、上下(第1方向Y)のメモリ セルMC1の電荷注入放出部CWE同士を同電位にすることができるため、上下のメモリ

20

30

40

50

セルMC1の電荷注入放出部CWEが配置されるp型のウエルHPW2を共有させることができる。これにより、上下のメモリセルMC1の隣接間をつめることができるので、メモリセルアレイMRの第1方向Yの寸法を図46の場合よりも縮小する(セル高さを小さくする)ことができる。

## [0210]

また、本実施の形態 7 においては、前記本実施の形態 2 と同様に、メモリセルアレイMR内において、第 2 方向 X に沿って互いに隣接する電荷注入放出部 C W E の p 型のウエル H P W 2 が、その隣接間に形成された n <sup>+</sup>型の半導体領域(n <sup>+</sup>型の拡散層) 2 5 により分離されている。これにより、第 2 方向 X に沿って互いに隣接する p 型のウエル H P W 2 の隣接間を前記実施の形態 1 の場合よりも狭くすることができるので、メモリセルアレイ M R の第 2 方向 X の寸法を縮小することができる。

#### [0211]

このように本実施の形態 7 においては、メモリセルアレイ M R の第 1 方向 Y および第 2 方向 X の両方の寸法を縮小できるので、メモリセルアレイ M R の面積を縮小できる。また、メモリの記憶容量を増大できる。

#### [0212]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

### [0213]

例えば容量部Cおよび電荷注入放出部CWEのp型のウエルHPW1,HPW2内にp型のウエルPWを形成しても良い。これにより、容量電極FGC1,FGC2の直下の基板1S部分のp型不純物の濃度を高くすることができるので、データ書き換え(書き込み・消去)時において、容量電極FGC1,FGC2の直下の基板1S部分の空乏化を抑制または防止することができる。このため、容量絶縁膜10c,10dに印加される電圧を高くすることができるので、データの書き換え速度を速くすることができる。

## [0214]

この場合、フラッシュメモリ領域におけるp型のウエルHPW1,HPW2内のp型のウエルPWは、LCDドライバ回路領域の低耐圧部のnチャネル型のMIS・FETQLN2の形成領域のp型のウエルPWを形成する際に同時に形成されている。これにより、p型のウエルHPW1,HPW2内にp型のウエルPWを形成するからといって製造工程が増えることもない。

#### [0215]

また、容量部 C、電荷注入放出部 CWE、データ読み出し用のMIS・FETQRおよび選択MIS・FETQSのウエルを、LCDドライバ回路領域の高耐圧部のpチャネル型のMIS・FETQHPのp型の半導体領域PVにより形成しても良い。この容量部 C、電荷注入放出部 CWE、データ読み出し用のMIS・FETQRおよび選択MIS・FETQSのウエルを形成するp型の半導体領域PVは、LCDドライバ回路領域の高耐圧部のpチャネル型のMIS・FETQHPのp型の半導体領域PVを形成する際に同時に形成されている。この場合、フラッシュメモリの上記p型のウエルHPW1~HPW3の形成のためのリソグラフィエ程(レジスト塗布、露光および現像等のような一連の処理および露光時に使用するフォトマスクの製造工程)を削減できるので、半導体装置の製造時間を短縮できる。また、半導体装置の製造コストを低減できる。

## [0216]

また、容量部 C および電荷注入放出部 C W E のウエルを形成する p 型の半導体領域 P V 内に、 p 型のウエル P W (または p 型のウエル H P W 1 , H P W 2 )を形成しても良い。これにより、容量部 C および電荷注入放出部 C W E の容量電極 F G C 1 , F G C 2 の直下の基板 1 S 部分の p 型不純物の濃度を高くすることができるので、データ書き換え(書き込み・消去)時における、容量電極 F G C 1 , F G C 2 の直下の基板 1 S 部分の空乏化を抑制または防止することができる。このため、容量絶縁膜 1 0 c , 1 0 d に印加される電

圧を高くすることができるので、データの書き換え速度を速くすることができる。

### [0217]

この場合、容量部Cおよび電荷注入放出部CWEのp型の半導体領域PV内のp型のウエルPW(またはp型のウエルHPW1,HPWL2)は、LCDドライバ回路領域の低耐圧部のnチャネル型のMIS・FETQLN2の形成領域のp型のウエルPW(または低耐圧のnチャネル型のMIS・FETQLN1の形成領域のp型のウエルHPW4)を形成する際に同時に形成されている。これにより、容量部Cおよび電荷注入放出部CWEのp型の半導体領域PV内にp型のウエルPW(またはp型のウエルHPW1,HPW2)を形成するからといって製造工程が増えることもない。

[0218]

10

以上の説明では主として本発明者によってなされた発明をその背景となった利用分野である半導体装置の製造方法に適用した場合について説明したが、それに限定されるものではなく種々適用可能であり、例えばマイクロマシンの製造方法にも適用できる。この場合、マイクロマシンが形成された半導体基板に上記フラッシュメモリを形成することでマイクロマシンの簡単な情報を記憶することができる。

【産業上の利用可能性】

[0219]

本発明は、不揮発性メモリ回路部を有する半導体装置の製造業に適用できる。

【図面の簡単な説明】

[0220]

20

- 【図1】本発明者が検討した半導体装置におけるフラッシュメモリの1ビット分のメモリセルの要部平面図である。

- 【図2】図1のメモリセルを1ビット/1セル構成にした場合のメモリセルアレイの平面図である。

- 【図3】本発明の一実施の形態である半導体装置におけるフラッシュメモリの平面図である。

- 【図4】図3のフラッシュメモリの要部拡大平面図である。

- 【図5】図3のY1-Y1線の断面図である。

- 【図6】図4のX1-X1線の断面図である。

- 【図7】図4のX2-X2線の断面図である。

- 【図8】図4のX3-X3線の断面図である。

- 【図9】本発明の一実施の形態である半導体装置の主回路部の高耐圧部の断面図である。

- 【図10】本発明の一実施の形態である半導体装置の主回路部の低耐圧部の断面図である

【図11】図3のフラッシュメモリの要部回路図である。

- 【図12】図11のフラッシュメモリのデータ書き込み動作時における各部への印加電圧を示した回路図である。

- 【図13】図11のフラッシュメモリのデーター括消去動作時における各部への印加電圧を示した回路図である。

- 【図14】図11のフラッシュメモリのデータ・ビット単位消去動作時における各部への 印加電圧を示した回路図である。

- 【図15】図11のフラッシュメモリのデータ読み出し動作時における各部への印加電圧 を示した回路図である。

- 【図16】図3のフラッシュメモリのデータ書き込み動作時のY1-Y1線の断面図である。

- 【図17】図3のフラッシュメモリのデータ消去動作時のY1-Y1線の断面図である。

- 【図18】図3のフラッシュメモリのデータ読み出し動作時のY1-Y1線の断面図であ る。

- 【図19】本発明の他の実施の形態である半導体装置におけるフラッシュメモリの平面図である。

\_\_

30

50

- 【図20】図19のフラッシュメモリの要部拡大平面図である。

- 【図21】図19のY2-Y2線の断面図である。

- 【図22】図20のX1-X1線の断面図である。

- 【図23】図20のX2-X2線の断面図である。

- 【図24】図20のX3-X3線の断面図である。

- 【図25】本発明の一実施の形態である半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

- 【図26】図25と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断面図である。

- 【図27】図25に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

- 【図28】図27と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断面図である。

- 【図29】図27に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

- 【図30】図29と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断面図である。

- 【図31】図29に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

- 【図32】図31と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断 20 面図である。

- 【図33】図31に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

- 【図34】図33と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断面図である。

- 【図35】図33に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

- 【図36】図35と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断面図である。

- 【図37】図35に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

- 【図38】図37と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断面図である。

- 【図39】図37に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

- 【図40】図39と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断面図である。

- 【図41】図39に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断 面図である。

- 【図42】図41と同一の製造工程時のフラッシュメモリ形成領域の半導体基板の要部断 40 面図である。

- 【図43】本発明の他の実施の形態である半導体装置におけるフラッシュメモリの平面図である。

- 【図44】図43のフラッシュメモリの要部拡大平面図である。

- 【図45】図43のY3-Y3線の断面図である。

- 【図46】図2の複数のメモリセルを第1方向にも配置した場合の一例のフラッシュメモリの平面図である。

- 【図47】本発明の他の実施の形態である半導体装置のフラッシュメモリの平面図である

- 【図48】図47のフラッシュメモリの要部拡大平面図である。

10

```

【図49】図47のメモリセルアレイに配線を配置して示した平面図である。

【図50】本発明の他の実施の形態である半導体装置のフラッシュメモリの平面図である

【図51】図50のフラッシュメモリの要部拡大平面図である。

【図52】図51のX4-X4線の断面図である。

【図53】図51のX3-X3線の断面図である。

【図54】本発明の他の実施の形態である半導体装置におけるフラッシュメモリの平面図

である。

【図55】図54のフラッシュメモリの要部拡大平面図である。

10

【図56】図55のX5-X5線の断面図である。

【図57】本発明の他の実施の形態である半導体装置のフラッシュメモリの平面図である

【図58】図57のフラッシュメモリの要部拡大平面図である。

【符号の説明】

[0221]

1 S 半導体基板

4 a p <sup>†</sup>型の半導体領域

5 a シリサイド層

6,6a,6b 絶縁層

6 c キャップ絶縁層

20

7,7a~7g 導体部

8 a n <sup>†</sup>型の半導体領域

10b ゲート絶縁膜(第2絶縁膜)

10c 容量絶縁膜(第3絶縁膜)

10d 容量絶縁膜(第1絶縁膜)

10e ゲート絶縁膜

10f ゲート絶縁膜

10g ゲート絶縁膜

10h ゲート絶縁膜

30

12 n型の半導体領域

12a n 型の半導体領域

1 2 b n <sup>+</sup>型の半導体領域

15 p型(n型)の半導体領域

15a p 型 (n 型)の半導体領域

15b p <sup>†</sup>型(n <sup>†</sup>型)の半導体領域

17 p型(n型)の半導体領域

17a p 型 (n 型)の半導体領域

1 7 b

p <sup>+</sup> 型 ( n <sup>+</sup> 型 ) の半導体領域

18 n型の半導体領域

40

18a n 型の半導体領域

18b n <sup>+</sup>型の半導体領域

19 p型の半導体領域

19a p 型の半導体領域

19b p <sup>†</sup>型の半導体領域

20 n型の半導体領域

20a n 型の半導体領域

20b n <sup>+</sup>型の半導体領域

2 1 p型の半導体領域

```

2 1 a p <sup>-</sup>型の半導体領域

2 1 b p <sup>+</sup>型の半導体領域

```

22 n型の半導体領域

22a n 型の半導体領域

2 2 b n <sup>+</sup>型の半導体領域

23 p型の半導体領域

23a p 型の半導体領域

2 3 b p <sup>†</sup>型の半導体領域

2 5 n <sup>†</sup>型の半導体領域

TI 分離部

MCዐ メモリセル

10

MC1 メモリセル

MC1s, MC1se, MC1r 選択メモリセル

MR メモリセルアレイ

PR 周辺回路領域

FG 浮遊ゲート電極

OR データ読み出し用のMIS・FET

FGR ゲート電極(第2電極)

QS 選択MIS·FET

FGS ゲート電極

CWE データ書き込み・消去用の電荷注入放出部

20

FGC1 容量電極(第3電極)

C 容量部

FGC2 容量電極(第1電極)

CGW 制御ゲート電極

DNW n型の埋込ウエル(第1ウエル)

DPW p型の埋込ウエル

HPW1 p型のウエル(第4ウエル)

HPW2 p型のウエル(第2ウエル)

HPW3 p型のウエル(第3ウエル)

HPW4 p型のウエル

30

HNW n型のウエル

L, L1~L5 活性領域

CT コンタクトホール

WBL, WBL0, WBL1 データ書き込み・消去用のビット線

RBL, RBL0, RBL1, RBL2 データ読み出し用のビット線

CG, CG0, CG1 制御ゲート配線

SL ソース線

GS 選択線

QHN nチャネル型のMIS・FET

QHP pチャネル型のMIS・FET

40

GHN,GHP ゲート電極

PV p型の半導体領域

NV n型の半導体領域

QLN1,QLN2 nチャネル型のMIS・FET

QLP1,QLP2 pチャネル型のMIS・FET

GLN1,GLN2,GLP1,GLP2 ゲート電極

PW p型のウエル

NW n型のウエル

DG ダミーゲート

```

DL ダミー活性領域

【図1】

【図2】

【図3】

【図4】

# 【図5】

# 【図6】

【図7】

【図8】

【図10】

DI 🖾

# 【図9】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

HPW2

HPW2

【図25】

DNW

HPW4

HNW

【図26】

【図27】

【図28】

DNW

読み出し部 Ø 28 容量部 電荷注入放出部

【図29】

DNW

10h

ΡW

10h

ΝM

HPW4

MNH

【図30】

読み出し部

容量部

電荷注入放出部

Ø 30

HPW2

【図31】

**⊠** 31

DNW

10h

ΡW

10h

ΜM

HPW4

10g

HNW

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

1.5Vデバイス

DNW

10h 22 I

22b 22a 22 1

$\frac{23b \ 23a}{23} \ | \ 23a \ 23b}{23 \ 10h} \ | \ 23$

20a 20b

/ 10g

20b 20a 20 1

HNW

-- M

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図53】

【図55】

### 【図54】

**X** 54

【図56】

# 【図57】

【図58】

# フロントページの続き

(51) Int.CI. F I

H 0 1 L 27/10 (2006.01)

(56)参考文献 特開2005-175411(JP,A)

特開2001-185633(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 27/115

H01L 21/8247

H01L 29/788

G11C 16/04