#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2010-263211 (P2010-263211A)

(43) 公開日 平成22年11月18日 (2010.11.18)

| (51) Int.Cl. |         |           | F I         |             | テーマコート    | (参考)   |

|--------------|---------|-----------|-------------|-------------|-----------|--------|

| HO1L         | 27/10   | (2006.01) | HO1L 27/10  | 471         | 4M119     |        |

| HO1L         | 21/8247 | (2006.01) | HO1L 27/10  | 371         | 5F083     |        |

| HO1L         | 27/115  | (2006.01) | HO1L 27/10  | 434         | 5 F 1 O 1 |        |

| HO1L         | 21/8246 | (2006.01) | HO1L 27/10  | 444         |           |        |

| HO1L         | 27/105  | (2006.01) | HO1L 27/10  | 448         |           |        |

|              |         |           | 審査請求 未請求 請求 | ド項の数 29 O L | (全 41 頁)  | 最終頁に続く |

(21) 出願番号 特願2010-103594 (P2010-103594) (22) 出願日 平成22年4月28日 (2010.4.28)

(31) 優先権主張番号 10-2009-0038949

(32) 優先日 平成21年5月4日 (2009.5.4)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2010-0004481

(32) 優先日 平成22年1月18日 (2010.1.18)

(33) 優先権主張国 韓国(KR)

(71) 出願人 390019839

三星電子株式会社

SAMSUNG ELECTRONICS CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞416 416,Maetan-dong,Yeo

n g t o n g - g u, S u w o n - s i, G y e o n g g i - d o 4 4 2 - 7 4 2

(KR)

(74)代理人 100064908

弁理士 志賀 正武

(74)代理人 100089037

弁理士 渡邊 隆

(74)代理人 100110364

弁理士 実広 信哉

最終頁に続く

### (54) 【発明の名称】積層メモリ素子

### (57)【要約】

【課題】高集積化が容易な積層メモリ素子を提供する。

【解決手段】本願発明の積層メモリ素子は、基板と、基板上に互いに積層された、少なくとも1層のメモリ層をそれぞれ含む複数のメモリグループと、該複数のメモリグループのうち、複数の隣接した2つのメモリグループ間に介在する複数のXデコーダ層と、前記複数の隣接した2つのメモリグループ間に、複数のXデコーダ層と交互に介在される複数のYデコーダ層と、を具備する積層メモリ素子である。

#### 【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

基板と、

前記基板上に互いに積層された、少なくとも 1 層のメモリ層をそれぞれ含む複数のメモリグループと、

前記複数のメモリグループのうち、複数の隣接した 2 つのメモリグループ間に、 1 層をおいて少なくとも 1 層ずつ介在する複数の X デコーダ層と、

前記複数の隣接した2つのメモリグループ間に、1層をおいて少なくとも1層ずつ、前記複数のXデコーダ層と交互に介在する複数のYデコーダ層と、

を含むことを特徴とする積層メモリ素子。

### 【請求項2】

各 X デコーダ層及び各 Y デコーダ層間には、前記複数のメモリグループのうち、少なくとも 1 つのメモリグループが介在することを特徴とする請求項 1 に記載の積層メモリ素子

#### 【請求項3】

前記複数のメモリグループは、同数のメモリ層をそれぞれ含むことを特徴とする請求項 1 に記載の積層メモリ素子。

### 【請求項4】

前記複数のXデコーダ層と前記複数のYデコーダ層は、前記複数の隣接した2つのメモリグループ間で、1層ずつ交互に配されたことを特徴とする請求項1に記載の積層メモリ素子。

【請求項5】

各 X デコーダ層は、前記複数の隣接した 2 つのメモリグループのうち、該 X デコーダ層の上下に隣接して配された 2 つのメモリグループに結合されることを特徴とする請求項 4 に記載の積層メモリ素子。

#### 【請求項6】

各 Y デコーダ層は、前記複数の隣接した 2 つのメモリグループのうち、該 Y デコーダ層の上下に隣接して配された 2 つのメモリグループに結合されたことを特徴とする請求項 4 に記載の積層メモリ素子。

# 【請求項7】

前記複数のYデコーダ層は、前記複数のXデコーダ層と交互に一対ずつ配された複数対の第1Yデコーダ層及び第2Yデコーダ層を含み、各対の第1Yデコーダ層及び第2Yデコーダ層は、互いに隣接して積層され、

前記複数のXデコーダ層は、前記複数の隣接した2つのメモリグループ間で、1層をおいて1層ずつ介在することを特徴とする請求項1に記載の積層メモリ素子。

### 【請求項8】

各対の第1Yデコーダ層及び第2Yデコーダ層は、前記複数の隣接した2つのメモリグループのうち、該2つのメモリグループにそれぞれ結合されることを特徴とする請求項7 に記載の積層メモリ素子。

#### 【請求項9】

各 X デコーダ層は、前記複数の隣接した 2 つのメモリグループのうち、該 X デコーダ層の上下に配された隣接した 2 つのメモリグループに結合されることを特徴とする請求項 7 に記載の積層メモリ素子。

# 【請求項10】

前記複数のXデコーダ層は、前記複数のYデコーダ層と交互に一対ずつ配された複数対の第1Xデコーダ層及び第2Xデコーダ層を含み、各対の第1Xデコーダ層及び第2Xデコーダ層は、互いに隣接して積層され、

前記複数のYデコーダ層は、前記複数の隣接した2つのメモリグループ間で、1層をおいて1層ずつ介在することを特徴とする請求項1に記載の積層メモリ素子。

### 【請求項11】

40

30

10

20

各 対 の 第 1 X デ コ ー ダ 層 及 び 第 2 X デ コ ー ダ 層 は 、 前 記 複 数 の 隣 接 し た 2 つ の メ モ リ グ ループのうち、該2つのメモリグループにそれぞれ結合されることを特徴とする請求項1 0 に記載の積層メモリ素子。

#### 【請求項12】

各 Y デコーダ層は、前記複数の隣接した 2 つのメモリグループのうち、該 Y デコーダ層 の上下に配された隣接した2つのメモリグループに結合されることを特徴とする請求項1 0 に記載の積層メモリ素子。

### 【請求項13】

各×デコーダ層は、各メモリグループに含まれたメモリ層の個数と同じ個数の×デコー ダ対を含み、

各Yデコーダ層は、各メモリグループに含まれたメモリ層の個数と同じ個数のYデコー ダ対を含むことを特徴とする請求項1に記載の積層メモリ素子。

#### 【 請 求 項 1 4 】

各メモリ層に含まれたメモリセルは、第1グループ及び第2グループに分類され、

各 X デ コ ー ダ 対 に 含 ま れ た X デ コ ー ダ は 、 対 応 す る メ モ リ 層 の 前 記 第 1 グ ル ー プ 及 び 第 2 グループにそれぞれ連結され、

各 Y デコーダ対に含まれた Y デコーダは、対応するメモリ層の前記第 1 グループ及び第 2 グループにそれぞれ連結されることを特徴とする請求項13 に記載の積層メモリ素子。

#### 【請求項15】

各Xデコーダ層は、各メモリグループに含まれたメモリ層の個数と同じ個数のXデコー ダを含み、

各 Y デコーダ層は、 各 メ モ リ グ ル ー プ に 含 ま れ た メ モ リ 層 の 個 数 と 同 じ 個 数 の Y デ コ ー ダを含むことを特徴とする請求項1に記載の積層メモリ素子。

#### 【請求項16】

基 板 上 に 配 列 さ れ た 複 数 の 積 層 メ モ リ ブ ロ ッ ク を 含 む 積 層 メ モ リ 素 子 で あ っ て 、 各 積 層 メモリブロックは、

前記基板上に互いに積層され、少なくとも1層のメモリ層をそれぞれ含む複数のメモリ グループと、

前 記 複 数 の メ モ リ グ ル ー プ 内 で 、 一 つ お い て 一 つ ず つ 介 在 す る 複 数 の X デ コ ー ダ ア レ イ と、

前記複数のメモリグループ内で、一つおいて一つずつ前記複数のXデコーダアレイと交 互に介在する複数のYデコーダアレイとを含むことを特徴とする積層メモリ素子。

#### 【請求項17】

各 積 層 メ モ リ ブ ロ ッ ク の 前 記 複 数 の X デ コ ー ダ ア レ イ は 、 当 該 積 層 メ モ リ ブ ロ ッ ク と 隣 接した積層メモリブロックの前記複数のYデコーダアレイと同一レベルに配されたことを 特徴とする請求項16に記載の積層メモリ素子。

#### 【請求項18】

各メモリグループは、少なくとも1本のワードラインに共通して結合され、

各積層メモリブロックの各Xデコーダアレイは、前記少なくとも1本のワードラインに 結合された少なくとも1つのXデコーダを含むことを特徴とする請求項16に記載の積層 メモリ素子。

#### 【請求項19】

各メモリグループは、少なくとも1対のワードラインに結合され、

各積層メモリブロックの各Xデコーダアレイは、前記少なくとも1対のワードラインに 結合された少なくとも1対のXデコーダを含むことを特徴とする請求項16に記載の積層 メモリ素子。

#### 【請求項20】

各 X デコーダアレイは、各メモリグループに含まれたメモリ層の個数の半分に該当する 個 数 の X デ コ ー ダ 対 を 含 み 、 各 X デ コ ー ダ 対 は 、 少 な く と も 2 層 の メ モ リ 層 に 共 通 に 連 結 され、

10

20

30

40

各Yデコーダアレイは、各メモリグループに含まれたメモリ層の個数の半分に該当する 個 数 の Y デ コ ー ダ 対 を 含 み 、 各 Y デ コ ー ダ 対 は 、 少 な く と も 2 層 の メ モ リ 層 に 共 通 に 連 結 されることを特徴とする請求項16に記載の積層メモリ素子。

#### 【請求項21】

各メモリ層に含まれたメモリセルは、第1グループ及び第2グループに分類され、

各×デコーダ対に含まれた×デコーダは、対応するメモリ層の前記第1グループ及び第 2 グループにそれぞれ連結され、

各 Y デコーダ対に含まれた Y デコーダは、対応するメモリ層の前記第 1 グループ及び第 2 グループにそれぞれ連結されることを特徴とする請求項20に記載の積層メモリ素子。

### 【請求項22】

各Xデコーダアレイは、各メモリグループに含まれたメモリ層の個数の半分に該当する 個数のXデコーダを含み、各Xデコーダは、少なくとも2層のメモリ層に共通に連結され

各Yデコーダアレイは、各メモリグループに含まれたメモリ層の個数の半分に該当する 個数のYデコーダを含み、各Yデコーダは、少なくとも2層のメモリ層に共通に連結され ることを特徴とする請求項16に記載の積層メモリ素子。

#### 【請求項23】

基板と、

1層またはそれ以上のメモリ層をそれぞれ含む、前記基板上に積層された複数のメモリ グループと、

前記複数のメモリグループ内の1層またはそれ以上のデコーダ層と、

前記1層またはそれ以上のデコーダ層は、

少なくとも 1 つの X デコーダを含む X デコーダアレイと、

少なくとも 1 つの Y デコーダを含む Y デコーダアレイと、

#### を含み、

各デコーダ層内の前記Xデコーダアレイ及び前記Yデコーダアレイは、格子状に配され ることを特徴とする積層メモリ素子。

### 【請求項24】

前記Xデコーダアレイは、複数のXデコーダを含み、

前記Yデコーダアレイは、複数のYデコーダを含むことを特徴とする請求項23に記載 の積層メモリ素子。

#### 【請求項25】

前 記 複 数 の X デ コ ー ダ 及 び 前 記 複 数 の Y デ コ ー ダ は 、 交 互 に 配 列 さ れ る こ と を 特 徴 と す る請求項24に記載の積層メモリ素子。

#### 【請求項26】

前 記 1 層 ま た は そ れ 以 上 の デ コ ー ダ 層 は 、 前 記 複 数 の メ モ リ グ ル ー プ 内 の 複 数 の デ コ ー ダ層を含むことを特徴とする請求項23に記載の積層メモリ素子。

### 【請求項27】

前記複数のデコーダ層のうち、隣接したメモリグループ内の1対のデコーダ層は、互い に相反した構造のデコーダ配置を有することを特徴とする請求項26に記載の積層メモリ 素子。

### 【請求項28】

前記複数のデコーダ層は、互いに相反した二種のデコーダ配置を交互に有することを特 徴とする請求項26に記載の積層メモリ素子。

### 【請求項29】

各メモリ層は、記録媒体として可変抵抗体を利用することを特徴とする請求項23に記 載の積層メモリ素子。

### 【発明の詳細な説明】

### 【技術分野】

50

20

10

30

#### [00001]

本発明は、半導体素子に係り、特に多層構造で積層されたメモリ素子に関する。

#### 【背景技術】

#### [0002]

半導体製品は、その体積がだんだん小さくなりつつも、高容量のデータ処理を要求している。したがって、このような半導体製品に使われる不揮発性メモリ素子の集積度を高める必要がある。このような点で、メモリ層を三次元に積層させて形成した多層構造のメモリ素子が考慮されている。

#### [00003]

しかし、多層構造のメモリ素子の動作を支援するための回路の配置が容易ではなく、集積度上昇に限界がある。

#### 【発明の概要】

【発明が解決しようとする課題】

#### [0004]

よって、本発明がなそうとする技術的課題は、高集積化が容易な積層メモリ素子を提供 するところにある。

#### [0005]

しかし、前述の本発明の技術的課題は、例示的に提示されたものであって、本発明がそれらに限定されるものではない。

### 【課題を解決するための手段】

#### [0006]

前記課題を解決するための本発明の一実施形態による積層メモリ素子は、基板と、前記基板上に互いに積層された、少なくとも1層のメモリ層をそれぞれ含む複数のメモリグループと、前記複数のメモリグループのうち、複数の隣接した2つのメモリグループ間で、1層をおいて少なくとも1層ずつ介在する複数のXデコーダ層と、前記複数のXデコーダ層と つのメモリグループ間で、1層をおいて少なくとも1層ずつ、前記複数のXデコーダ層と交互に介在する複数のYデコーダ層と、を含む。

#### [0007]

一部実施形態で、各 X デコーダ層及び各 Y デコーダ層間には、前記複数のメモリグループのうち、少なくとも 1 つのメモリグループが介在しうる。

#### [0008]

一部実施形態で、前記複数のメモリグループは、同数のメモリ層をそれぞれ含むことができる。

### [0009]

一部実施形態で、前記複数の X デコーダ層と前記複数の Y デコーダ層は、前記複数の隣接した 2 つのメモリグループ間で、 1 層ずつ交互に配されうる。各 X デコーダ層は、前記複数の隣接した 2 つのメモリグループのうち、当該 X デコーダ層の上下に隣接して配された 2 つのメモリグループに結合されうる。各 Y デコーダ層は、前記複数の隣接した 2 つのメモリグループのうち、当該 Y デコーダ層の上下に隣接して配された 2 つのメモリグループに結合されうる。

## [0010]

一部実施形態で、前記複数のYデコーダ層は、前記複数のXデコーダ層と交互に一対ずつ配された複数の対EI第1Yデコーダ層及び第2Yデコーダ層を含み、各対の第1Yデコーダ層及び第2Yデコーダ層を含み、各対の第1Yデコーダ層及び第2Yデコーダ層は、互いに隣接して積層され、前記複数のXデコーダ層は、前記複数の隣接した2つのメモリグループ間で、1層をおいて1層ずつ介在しうる。各対の第1Yデコーダ層及び第2Yデコーダ層は、前記複数の隣接した2つのメモリグループのうち、当該2つのメモリグループにそれぞれ結合されうる。各Xデコーダ層は、前記複数の隣接した2つのメモリグループのうち、当該Xデコーダ層の上下に配された隣接した2つのメモリグループに結合されうる。

### [0011]

50

10

20

30

一部実施形態で、前記複数の X デコーダ層は、前記複数の Y デコーダ層と交互に一対ずつ配された複数対の第 1 X デコーダ層及び第 2 X デコーダ層を含み、各対の第 1 X デコーダ層及び第 2 X デコーダ層を含み、各対の第 1 X デコーダ層は、互いに隣接して積層され、前記複数の Y デコーダ層は、前記複数の隣接した 2 つのメモリグループ間で、 1 層をおいて 1 層ずつ介在しうる。各対の第 1 X デコーダ層及び第 2 X デコーダ層は、前記複数の隣接した 2 つのメモリグループのうち、当該 2 つのメモリグループにそれぞれ結合されうる。各 Y デコーダ層は、前記複数の隣接した 2 つのメモリグループのうち、当該 Y デコーダ層の上下に配された隣接した 2 つのメモリグループに結合されうる。

### [0012]

一部実施形態で、各 X デコーダ層は、各 X モリグループに含まれたメモリ層の個数と同じ個数の X デコーダ対を含み、各 Y デコーダ層は、各 X モリグループに含まれたメモリ層の個数と同じ個数の Y デコーダ対を含むことができる。各 X モリ層に含まれたメモリセルは、第 1 グループ及び第 2 グループに分類され、各 X デコーダ対に含まれた X デコーダは、対応するメモリ層の前記第 1 グループ及び第 2 グループにそれぞれ連結され、各 Y デコーダ対に含まれた Y デコーダは、対応するメモリ層の前記第 1 グループ及び第 2 グループにそれぞれ連結されうる。

#### [0013]

一部実施形態で、各メデコーダ層は、各メモリグループに含まれたメモリ層の個数と同じ個数のメデコーダを含み、各Yデコーダ層は、各メモリグループに含まれたメモリ層の個数と同じ個数のYデコーダを含むことができる。

#### [0014]

また、前記課題を解決するための本発明の他の実施形態による積層メモリ素子は、基板上に配列された複数の積層メモリブロックを含み、各積層メモリブロックは、前記基板上に互いに積層され、少なくとも1層のメモリ層をそれぞれ含む複数のメモリグループと、前記複数のメモリグループ内で、一つおいて一つずつ介在された複数のメデコーダアレイと、前記複数のメモリグループ内で、一つおいて一つずつ前記複数のメデコーダアレイと交互に介在された複数のΥデコーダアレイとを含む。

#### [0015]

一部実施形態で、各積層メモリブロックの前記複数のXデコーダアレイは、当該積層メモリブロックと隣接した積層メモリブロックの前記複数のYデコーダアレイと同一レベルに配されうる。

# [0016]

一部実施形態で、各メモリグループは、少なくとも1本のワードラインに共通して結合され、各積層メモリブロックの各Xデコーダアレイは、前記少なくとも1本のワードラインに結合された少なくとも1つのXデコーダを含むことができる。

### [ 0 0 1 7 ]

一部実施形態で、各メモリグループは、少なくとも1対のワードラインに結合され、各積層メモリブロックの各 X デコーダアレイは、前記少なくとも1対のワードラインに結合された少なくとも1対の X デコーダを含むことができる。

#### [0018]

一部実施形態で、各 X デコーダアレイは、各 メモリグループに含まれたメモリ層の個数の半分に該当する個数の X デコーダ対を含み、各 X デコーダ対は、少なくとも 2 層のメモリ層に共通に連結され、各 Y デコーダアレイは、各 メモリグループに含まれたメモリ層の個数の半分に該当する個数の Y デコーダ対を含み、各 Y デコーダ対は、少なくとも 2 層のメモリ層に共通に連結されうる。各 メモリ層に含まれたメモリセルは、第 1 グループ及び第 2 グループに分類され、各 X デコーダ対に含まれた X デコーダは、対応するメモリ層の前記第 1 グループ及び第 2 グループにそれぞれ連結され、各 Y デコーダ対に含まれた Y デコーダは、対応するメモリ層の前記第 1 グループ及び第 2 グループにそれぞれ連結されうる。

# [0019]

10

20

30

一部実施形態で、各Xデコーダアレイは、各メモリグループに含まれたメモリ層の個数の半分に該当する個数のXデコーダを含み、各Xデコーダは、少なくとも2層のメモリ層に共通に連結され、各Yデコーダアレイは、各メモリグループに含まれたメモリ層の個数の半分に該当する個数のYデコーダを含み、各Yデコーダは、少なくとも2層のメモリ層に共通に連結されうる。

### [0020]

また、前記課題を解決するための本発明の他の実施形態による積層メモリ素子は、基板と、1層またはそれ以上のメモリ層をそれぞれ含み、前記基板上に積層された複数のメモリグループと、前記複数のメモリグループ内の1層またはそれ以上のデコーダ層を含み、前記1層またはそれ以上のデコーダ層は、少なくとも1つのXデコーダを含むXデコーダアレイと、少なくとも1つのYデコーダを含むYデコーダアレイと、を含み、各デコーダ層内の前記Xデコーダアレイ及び前記Yデコーダアレイは、格子状に配されうる。

[0021]

一部実施形態で、前記 X デコーダアレイは、複数の X デコーダを含み、前記 Y デコーダアレイは、複数の Y デコーダを含むことができる。前記複数の X デコーダ及び前記複数の Y デコーダは、交互に配列されうる。

[0022]

一部実施形態で、前記 1 層またはそれ以上のデコーダ層は、前記複数のメモリグループ内の複数のデコーダ層を含むことができる。前記複数のデコーダ層のうち、隣接したメモリグループ内の 1 対のデコーダ層は、互いに相反した構造のデコーダ配置を有することができる。前記複数のデコーダ層は、互いに相反した二種のデコーダ配置を交互に有することができる。

[0023]

一部実施形態で、各メモリ層は、記録媒体として可変抵抗体を利用できる。

【発明の効果】

[0024]

本発明の実施形態による積層メモリ素子によれば、XデコーダとYデコーダとが互いに 異なる層に互いに離隔されるように積層されうる。従って、XデコーダとYデコーダとが 1層に共に配される必要がないために、各層のXデコーダまたはYデコーダが占める面積 を大きく縮めることができる。かようなデコーダ配置を利用すれば、メモリ層の積層数に 対する制限が減り、積層メモリ素子の集積度が高まりうる。

[0025]

また、本発明の実施形態による積層メモリ素子によれば、複数のメモリブロックの同一レベルで、XデコーダアレイとYデコーダアレイとが格子状に配されうる。従って、メモリ層は、当該メモリブロックのXデコーダアレイまたはYデコーダアレイだけではなく、隣接するメモリブロックの同一レベルのXデコーダアレイまたはYデコーダアレイに連結されうる。かようなデコーダ配置を利用すれば、XデコーダまたはYデコーダと、メモリ層との連結ラインの長さを縮めることができる。

[0026]

また、本発明の実施形態による積層メモリ素子によれば、各メモリ層に含まれたメモリセルを少なくとも2つのグループに分類し、各メモリ層に対応する複数のXデコーダ対または複数のYデコーダ対を含むことができる。従って、各XデコーダまたはYデコーダでデコーディングするメモリセルの個数が減るので、各XデコーダまたはYデコーダの複雑度を低下させることができるため、その具現を簡単にできる。

【図面の簡単な説明】

[0027]

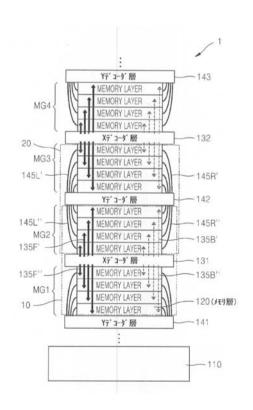

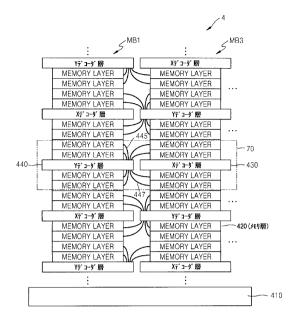

【図1】本発明の一実施形態による積層メモリ素子を示す断面図である。

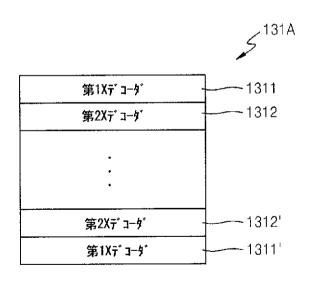

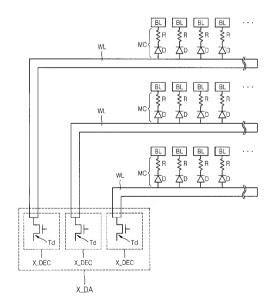

【 図 2 】 図 1 の 積 層 メモリ 素 子 に 含 ま れ た X デ コ ー ダ 層 の X デ コ ー ダ ア レ イ の 一 例 を 示 す 概 略 図 で あ る 。

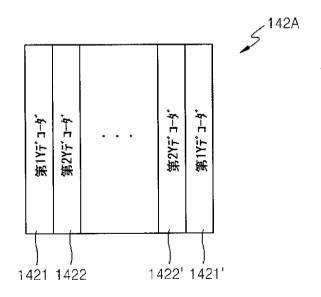

【図3】図1の積層メモリ素子に含まれたYデコーダ層のYデコーダアレイの一例を示す

10

20

30

40

概略図である。

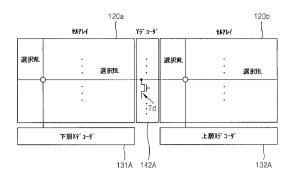

【図4】図1の積層メモリ素子で、メモリ層、Xデコーダアレイ及びYデコーダアレイの 連結を示す概略図である。

- 【図5】本発明の他の実施形態による積層メモリ素子を示す断面図である。

- 【図6】本発明のさらに他の実施形態による積層メモリ素子を示す断面図である。

- 【図7】本発明のさらに他の実施形態による積層メモリ素子を示す断面図である。

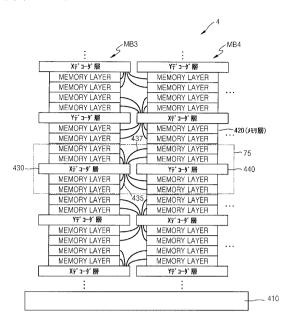

- 【図8】本発明の一実施形態による積層メモリ素子を示す平面図である。

- 【図9】図8の積層メモリ素子のA-A′線に沿って切り取った断面図の一例である。

- 【 図 1 0 】 図 8 の 積 層 メモリ 素 子 の B B '線 に 沿って 切 り 取 った 断 面 図 の 一 例 で あ る 。

- 【 図 1 1 】 図 8 の 積 層 メモリ 素 子 の A ・ A ' 線 に 沿 っ て 切 り 取 っ た 断 面 図 の 他 の 例 で あ る

【 図 1 2 】 図 8 の 積 層 メ モ リ 素 子 の B - B ' 線 に 沿 っ て 切 り 取 っ た 断 面 図 の 他 の 例 で あ る

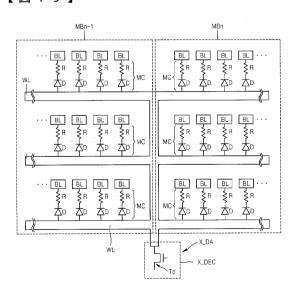

【図13】本発明の他の実施形態による積層メモリ素子を示す平面図である。

【 図 1 4 】 図 1 3 の 積 層 メモリ 素 子 の C - C ′線 に 沿 っ て 切 り 取 っ た 断 面 図 の 一 例 で あ る

【 図 1 5 】 図 1 3 の 積 層 メモリ 素 子 の D ・ D ' 線 に 沿 っ て 切 り 取 っ た 断 面 図 の 一 例 で あ る

【 図 1 6 】 図 1 3 の 積 層 メモリ 素 子 の C - C ' 線 に 沿 っ て 切 り 取 っ た 断 面 図 の 他 の 例 で あ

【 図 1 7 】 図 1 3 の積層メモリ素子の D - D ′線に沿って切り取った断面図の他の例であ

【図18】本発明の一部実施形態による積層メモリ素子で、メモリ層とXデコーダアレイ との物理的な連結を示す概略的な断面図である。

【図19】本発明の他の実施形態による積層メモリ素子で、メモリ層とXデコーダアレイ との物理的な連結を示す概略的な断面図である。

【図20】本発明の他の実施形態による積層メモリ素子で、メモリ層とXデコーダアレイ との物理的な連結を示す概略的な断面図である。

【図21】本発明のさらに他の実施形態による積層メモリ素子で、メモリ層とXデコーダ アレイとの物理的な連結を示す概略的な断面図である。

【図22】本発明の一実施形態によるメモリカードを示す概略図である。

【図23】本発明の一実施形態による電子システムを示すブロック図である。

【発明を実施するための形態】

[0028]

以下、添付した図面を参照しつつ、本発明による望ましい実施形態を介して、本発明の 原理について詳細に説明する。しかし、本発明は、以下で開示される実施形態に限定され るものではなく、互いに異なる多様な形態で具現されうる。図面での構成要素は、説明の 便宜のために、その大きさが誇張されうる。

[0029]

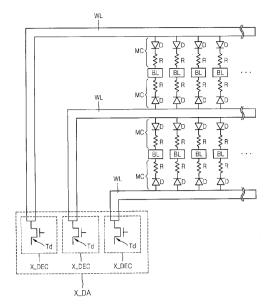

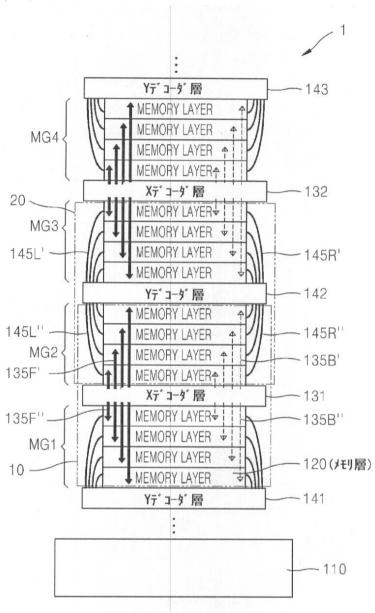

図1は、本発明の一実施形態による積層メモリ素子を示す断面図である。

[0030]

図 1 を参照すれば、積層メモリ素子 1 は、基板 1 1 0 、複数のメモリ層 1 2 0 、複数の X デコーダ層 1 3 1 , 1 3 2 及び複数の Y デコーダ層 1 4 1 , 1 4 2 , 1 4 3 を含むこと ができる。図1では、図解の便宜上、2層のXデコーダ層131,132と3層のYデコ ーダ 1 4 1 , 1 4 2 , 1 4 3 とを図示したが、積層メモリ素子 1 は、さらに多数の X デコ ー ダ 層 及 び Y デ コ ー ダ 層 を 含 む こ と が で き る 。 以 下 、 積 層 メ モ リ 素 子 1 に 含 ま れ た そ れ ぞ れの構成要素について詳述する。

[ 0 0 3 1 ]

基 板 1 1 0 上 に 、 複 数 の メ モ リ 層 1 2 0 が 積 層 さ れ う る 。 例 え ば 、 基 板 1 1 0 は 、 半 導 体ウェーハを含むことができる。かようなメモリ層120の積層構造は、メモリ素子の集 10

20

30

40

積度を高め、かつその容量を増やすのに効果的である。各メモリ層120は、マトリックス状に配列されたメモリセルアレイ(図示せず)を含むことができる。積層メモリ素子1に含まれるメモリ層120の数は、メモリ容量によって適切に選択され、この実施形態を制限するものではない。メモリ層120は、多様な形態のメモリ、例えば、DRAM(dynamic random access memory)、SRAM(static random access memory)、フラッシュメモリ(flash memory)、PRAM(phase change random access memory)、ReRAM(resistive random access memory)、FeRAM(ferroelectric random access memory)またはMRAM(magnetoresistive random access memory)によって構成されうる。

### [0032]

複数のメモリ層120は、複数のメモリグループMG1,MG2,MG3,MG4にグループ化され、各メモリグループMG1,MG2,MG3,MG4は、同数のメモリ層120を含むことができる。本実施形態で、各メモリグループMG1,MG2,MG3,MG4は、4個のメモリ層120を含むが、かような各メモリグループMG1,MG2,MG3,MG3,MG4に含まれたメモリ層120の数は、例示的に図示されており、本実施形態の範囲を制限するものではない。本実施形態の変形例で、メモリグループは、互いに異なる数のメモリ層120を含むこともできる。

#### [0033]

複数のメモリグループMG1,MG2,MG3,MG4間には、Xデコーダ層とYデコーダ層とが交互に配されうる。具体的には、積層メモリ素子1で、Yデコーダ層141、メモリグループMG1、Xデコーダ層131、メモリグループMG2、Yデコーダ層142、メモリグループMG3、Xデコーダ層132、メモリグループMG4及びYデコーダ層143が、基板110上に順次に積層される。このとき、Xデコーダ層131、及びXデコーダ層131を中心に上下に配されたメモリグループMG1,MG2は、第1基本積層構造10とし、Yデコーダ層142、及びYデコーダ層142を中心に上下に配されたメモリグループMG2,MG3は、第2基本積層構造20とする。以下、第1基本積層構造10及び第2基本積層構造20について詳述する。

#### [0034]

まず、積層メモリ素子1は、基板110上に積層される複数の第1基本積層構造10を含み、複数の第1基本積層構造10間には、複数のYデコーダ層141,142,143が介在される。第1基本積層構造10でXデコーダ層131は、その上部に隣接して積層されたメモリグループMG2のメモリ層120と、第1前面(front)連結ライン135F、及び第1背面(back)連結ライン135B、を介して連結され、その下部に隣接して積層されたメモリグループMG1のメモリ層120と、第2前面連結ライン135F、及び第2背面連結ライン135B、を介して連結されうる。具体的には、第1前面連結ライン135F、及び第2背面連結ライン135B、と第1背面連結ライン135B、及び第2背面連結ライン135B、は、各メモリ層120にそれぞれ連結されたXデコーダ用配線(図示せず)に連結されうるが、ここで、Xデコーダ用配線は、ワードラインでありうる。

### [0035]

これにより、 X デコーダ層 1 3 1 は、メモリグループ M G 1 , M G 2 のメモリ層 1 2 0 と電気的に信号を送受信することができる。例えば、 X デコーダ層 1 3 1 は、各メモリ層に含まれたメモリセルについての X 軸アドレス情報をデコーディングしてメモリ層 1 2 0 に伝達できる。 X デコーダ層 1 3 1 は、基板 1 1 0 上の X バッファまたは X ドライバ (図示せず)に電気的にさらに連結されうる。

# [0036]

ここで、実線矢印で表示された第1前面連結ライン135F ′ 及び第2前面連結ライン135F ″ は、 X デコーダ層131とメモリ層120との前面に配されて、図面の紙面を貫通する方向への連結関係を指示できる。一方、点線矢印で表示された第1背面連結ライン135B ″ は、 X デコーダ層131とメモリ層12

10

20

30

40

0 との背面に配され、図面の紙面を貫通する方向への連結関係を指示できる。従って、図1の断面方向では、第1背面連結ライン135B′及び第2背面連結ライン135B″は、見えないので、点線矢印で図示した。図2は、図1の積層メモリ素子に含まれたXデコーダ層のXデコーダアレイの一例を示す概略図である。

[0037]

図 1 及び図 2 を参照すれば、 X デコーダ層 1 3 1 は、少なくとも 1 つの X デコーダアレイ 1 3 1 A を含むことができ、 X デコーダアレイ 1 3 1 A は、複数の X デコーダ 1 3 1 1 , 1 3 1 2 , 1 3 1 1 ' , 1 3 1 2 ' を含むことができる。図 2 には、便宜上、 4 個の X デコーダ 1 3 1 1 , 1 3 1 2 , 1 3 1 1 ' , 1 3 1 2 ' が図示されているが、 X デコーダアレイ 1 3 1 A は、さらに多数の X デコーダを含むことができる。

[0038]

各メモリ層120に含まれたメモリセルは、2つのグループに分類されうるが、例えば、各メモリ層120に含まれたメモリセルのうち、奇数番目のメモリセルを第1グループに、偶数番目のメモリセルを第2グループに分類しうる。しかし、これは一例に過ぎず、各メモリ層120に含まれたメモリセルは、他の方式で分類されうる。このように、2つのグループに分類されたメモリセルについてのX軸アドレス情報のデコーディングのために、Xデコーダアレイ131Aは、各メモリグループに含まれたメモリ層120のそれぞれに対応する複数のXデコーダ対を含むことができる。従って、Xデコーダを含むことができる。

[0039]

本実施形態で、各メモリグループMG1,MG2,MG3,MG4は、4層のメモリ層120を含むので、Xデコーダアレイ131Aは、4個のXデコーダ対、換言すれば、8個のXデコーダを含むことができる。具体的には、Xデコーダアレイ131Aに含まれた2つの第1Xデコーダ1311,1311 ' は、第1Xデコーダ対をなし、2つの第2Xデコーダ1312 , 1312 ' は、第2Xデコーダ対をなすことができる。以下、各対のXデコーダとメモリ層120との連結関係について詳述する。

[0040]

第1×デコーダ1311,1311′は、×デコーダ層131の上部に最も隣接して位置するメモリ層120と、下部に最も隣接して位置するメモリ層120とに共通に連結されうる。ここで、第1×デコーダ1311は、第1前面連結ライン135F′を介して、メデコーダ層131の上部に最も隣接して位置するメモリ層120の第1グループに連結され、第2前面連結ライン135F″を介して、メデコーダ層131の下部に最も隣接して位置するメモリ層120の第1グループに連結されうる。また、第1×デコーダ1311′は、第1背面連結ライン135B′を介して、メデコーダ層131の上部に最も隣接して位置するメモリ層120の第2グループに連結され、第2背面連結ライン135B″を介して、メデコーダ層131の下部に最も隣接して位置するメモリ層120の第2グループに連結されうる。

[0041]

同様に、第2Xデコーダ1312,1312,は、Xデコーダ層131の上部から二番目に隣接して位置するメモリ層120と、下部から二番目に隣接して位置するメモリ層120とに共通に連結されうる。ここで、第2Xデコーダ1311は、第1前面連結ライン135F′を介して、Xデコーダ層131の上部から二番目に隣接して位置するメモリ層120の第1グループに連結され、第2前面連結ライン135F″を介して、Xデコーダ層131の下部から二番目に隣接して位置するメモリ層120の第1グループに連結されうる。また、第2Xデコーダ1312′は、第1背面連結ライン135B′を介して、Xデコーダ層131の上部から二番目に隣接して位置するメモリ層120の第2グループに連結され、第2背面連結ライン135B″を介して、Xデコーダ層131の下部から二番目に隣接して位置するメモリ層120の第2グループに連結されうる。

[0042]

10

20

30

20

30

40

50

本実施形態によれば、メモリ層120に含まれたメモリセルを2つのグループに分類し、1対のXデコーダが、Xデコーダ層131の上下部に対称的に位置するメモリ層120に共通に連結される。このとき、1対のXデコーダのうち一つは、対応するメモリ層120の第1グループに連結され、他の一つは、対応するメモリ層120の第2グループに連結されうる。これにより、Xデコーダ層131でデコーディングするメモリセルの個数が減ることになるので、Xデコーダ層131の複雑度を低下させることができるので、その具現も簡単にできる。

### [0043]

再び図1を参照すれば、積層メモリ素子1は、基板110上に積層される複数の第2基本積層構造20を含み、複数の第2基本積層構造20間には、複数のXデコーダ層131,132が介在される。第2基本積層構造20でYデコーダ層142は、その上部に隣接して積層されたメモリグループMG3のメモリ層120に、第1左側(left)連結ライン145L"及び第1右側(right)連結ライン145R"を介して連結され、その下部に隣接して積層されたメモリグループMG2に含まれたメモリ層120に、第2左側連結ライン145L"及び第2右側連結ライン145R"を介して連結されうる。具体的には、第1左側連結ライン145L"及び第2左側連結ライン145L"と第1右側連結ライン145R"は、各メモリ層120に連結されたYデコーダ用配線(図示せず)に連結されうるが、ここで、Yデコーダ用配線は、ビットラインでありうる。

#### [0044]

これにより、 Y デコーダ層 1 4 2 は、メモリグループ M G 2 , M G 3 のメモリ層 1 2 0 と電気的に信号を送受信することができる。例えば、 Y デコーダ層 1 4 2 は、各メモリ層に含まれたメモリセルについての Y 軸アドレス情報をデコーディングしてメモリ層 1 2 0 に伝達できる。 Y デコーダ層 1 4 2 は、基板 1 1 0 上の Y バッファまたは Y ドライバ (図示せず)に電気的にさらに連結されうる。

#### [0045]

ここで、実線で表示された第1左側連結ライン145L,及び第2左側連結ライン145L"並びに第1右側連結ライン145R,及び第2右側連結ライン145R"は、図面の紙面と平行した方向への連結関係を指示できる。従って、実線矢印で表示された第1前面連結ライン135F,及び第2前面連結ライン135F"並びに点線矢印で表示された第1背面連結ライン135B,及び第2背面連結ライン135B"は、実線で表示された第1左側連結ライン145L"なびに第1右側連結ライン145R"と互いに交差する方向の連結関係を表示できる。

#### [0046]

図3は、図1の積層メモリ素子に含まれたYデコーダ層のYデコーダアレイの一例を示す概略図である。

#### [0047]

図 1 及び図 3 を参照すれば、 Y デコーダ層 1 4 2 は、少なくとも 1 つの Y デコーダアレイ 1 4 2 A を含むことができ、 Y デコーダアレイ 1 4 2 A は、 複数の Y デコーダ 1 4 2 1 , 1 4 2 2 , 1 4 2 1 ' , 1 4 2 2 ' を含むことができる。図 3 には、便宜上、 4 個の Y デコーダ 1 4 2 1 , 1 4 2 2 , 1 4 2 1 ' , 1 4 2 2 ' が図示されているが、 Y デコーダアレイ 1 4 2 A は、さらに多数の Y デコーダを含むことができる。

# [0048]

各メモリ層120に含まれたメモリセルは、2つのグループに分類できるが、例えば、各メモリ層120に含まれたメモリセルのうち、奇数番目のメモリセルを第1グループに、偶数番目のメモリセルを第2グループに分類しうる。しかし、これは一例に過ぎず、各メモリ層120に含まれたメモリセルは、他の方式で分類されうる。このように、2つのグループに分類されたメモリセルについてのY軸アドレス情報のデコーディングのために、Yデコーダアレイ142Aは、各メモリグループに含まれたメモリ層120のそれぞれ

に対応する複数の Y デコーダ対を含むことができる。 従って、 Y デコーダアレイ 1 4 2 A は、各メモリグループに含まれたメモリ層 1 2 0 の個数の 2 倍の Y デコーダを含むことができる。

#### [0049]

本実施形態で、各メモリグループMG1,MG2,MG3,MG4は、4層のメモリ層120を含むので、Yデコーダアレイ142Aは、4個のYデコーダ対、換言すれば、8個のYデコーダを含むことができる。具体的には、Yデコーダアレイ142Aに含まれた2つの第1Yデコーダ1421,1421,は第1Yデコーダ対をなし、2つの第2Yデコーダ1422,1422′は、第2Yデコーダ対をなすことができる。以下、各対のYデコーダとメモリ層120との連結関係について詳述する。

#### [0050]

第1Yデコーダ1421,1421,は、Yデコーダ層142の上部に最も隣接して位置するメモリ層120と、下部に最も隣接して位置するメモリ層120とに共通に連結されうる。ここで、第1Yデコーダ1421は、第1左側連結ライン145L,を介して、Yデコーダ層142の上部に最も隣接して位置するメモリ層120の第1グループに連結され、第2左側連結ライン145L "を介して、Yデコーダ層142の下部に最も隣接して位置するメモリ層120の第1グループに連結されうる。また、第1Yデコーダ1421,は、第1右側連結ライン145R,を介して、Yデコーダ層142の上部に最も隣接して位置するメモリ層120の第2グループに連結され、第2右側連結ライン145R "を介して、Yデコーダ層142の所部に最も隣接して位置するメモリ層120の第2グループに連結されうる。

#### [0051]

同様に、第2Yデコーダ1422,1422,は、Yデコーダ層142の上部から二番目に隣接して位置するメモリ層120と、下部から二番目に隣接して位置するメモリ層120とに共通に連結されうる。ここで、第2Yデコーダ1422は、第1左側連結ライン145L"を介して、Yデコーダ層142の上部から二番目に隣接して位置するメモリ層120の第1グループに連結され、第2左側連結ライン145L"を介して、Yデコーダ層142の下部から二番目に隣接して位置するメモリ層120の第1グループに連結されうる。また、第2Yデコーダ1422,は第1右側連結ライン145R、を介して、Yデコーダ層142の上部から二番目に隣接して位置するメモリ層120の第2グループに連結され、第2右側連結ライン145R"を介して、Yデコーダ層142の下部から二番目に隣接して位置するメモリ層120の第2グループに連結されうる。

#### [0052]

本実施形態によれば、メモリ層120に含まれたメモリセルを2つのグループに分類し、1対のYデコーダが、Yデコーダ層142の上下部に対称的に位置するメモリ層120に共通に連結される。このとき、1対のYデコーダのうち一つは、対応するメモリ層120の第1グループに連結され、他の一つは、対応するメモリ層120の第2グループに連結されうる。これにより、Yデコーダ層142でデコーディングするメモリセルの個数が減ることになるので、Yデコーダ層142の複雑度を低下させることができるので、その具現も簡単にできる。

# [ 0 0 5 3 ]

図4は、図1の積層メモリ素子で、メモリ層、Xデコーダアレイ及びYデコーダアレイの連結を示す概略図である。

# [0054]

図 1 及び図 4 を参照すれば、下層メモリ層 1 2 0 a 及び上層メモリ層 1 2 0 b は、セルアレイをそれぞれ有することができる。下層メモリ層 1 2 0 a 及び上層メモリ層 1 2 0 b 間の Y デコーダアレイ 1 4 2 A は、下層メモリ層 1 2 0 a 及び上層メモリ層 1 2 0 b に共通して連結されうる。例えば、下層メモリ層 1 2 0 a 及び上層メモリ層 1 2 0 b の選択ビットライン B L は、Y デコーダアレイ 1 4 2 A のデコーディング・トランジスタ T d に連結されうる。

10

20

30

20

30

40

50

[0055]

下層メモリ層120a下の下層 X デコーダアレイ131Aは、下層メモリ層120aの選択ワードラインW L に連結されうる。上層メモリ層120b上の上層 X デコーダアレイ132Aは、上層メモリ層120bの選択ワードラインW L に連結されうる。

[0056]

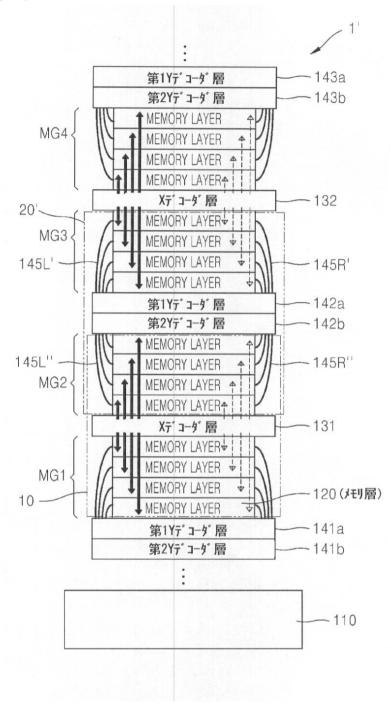

図5は、本発明の他の実施形態による積層メモリ素子を示す断面図である。

[ 0 0 5 7 ]

図5を参照すれば、積層メモリ素子1'は、基板110、複数のメモリ層120、複数のメデコーダ層131,132及び/または複数対の第1Yデコーダ層141a,142 a,143a)及び/または第2Yデコーダ層141b,142b,143bを含む。この実施形態の積層メモリ素子1'は、図1ないし図4の積層メモリ素子1で、一部構成を変形したものであり、従って、重複する説明は省略する。

[0058]

複数のメモリグループMG1,MG2,MG3,MG4間には、Xデコーダ層と1対の第1Yデコーダ層及び第2Yデコーダ層とが互いに入れ違いながら配されうる。具体的には、積層メモリ素子1,で、1対の第1Yデコーダ層141a及び第2Yデコーダ層141b、メモリグループMG1、Xデコーダ層131、メモリグループMG2、1対の第1Yデコーダ層142a及び第2Yデコーダ層142b、メモリグループMG3、Xデコーダ層132、メモリグループMG4、及び/または1対の第1Yデコーダ層143a及び第2Yデコーダ層143bが、基板110上に順次に積層される。このとき、Xデコーダ層131及びXデコーダ層131を中心に上下に配されたメモリグループMG1,MG2は、第1基本積層構造10とし、Yデコーダ層対142a,142b、及びYデコーダ層対142a,142b、及びYデコーダ層対142a,142bを中心に上下に配されたメモリグループMG2,MG3は、第2基本積層構造20~とする。第1基本積層構造10は、図1に含まれた構成と実質的に同一なので、これについての説明は省略する。

[0059]

積層メモリ素子1,は、基板110上に積層される複数の第2基本積層構造20,を含み、複数の第2基本積層構造20,間には、複数のXデコーダ層131,132が介在される。第2基本積層構造20,で第1Yデコーダ層142aは、その上部に隣接して積層されたメモリグループMG3のメモリ層120に、第1左側連結ライン145L,及び第1右側連結ライン145R,を介して連結され、第2Yデコーダ層142bは、その下部に隣接して積層されたメモリグループMG2のメモリ層120に、第2左側連結ライン145L,及び第2右側連結ライン145R,を介して連結されうる。

[0060]

これにより、第1Yデコーダ層142aは、その上部に隣接して積層されたメモリグループMG3のメモリ層120と電気的に信号を送受信でき、第2Yデコーダ層142bは、その下部に隣接して積層されたメモリグループMG2のメモリ層120と電気的に信号を送受信することができる。

[0061]

本実施形態によれば、隣接した2つのメモリグループは、その間に配されるXデコーダ層は共有するが、その間に配されるYデコーダ層は共有しない。換言すれば、複数のメモリグループ間に、Xデコーダ層と1対のYデコーダ層とが交互に配され、隣接した2つのメモリグループ間には、1つのXデコーダ層が存在し、隣接した2つのメモリグループ間には、2層のYデコーダ層が存在する。これにより、隣接した2つのメモリグループに含まれたメモリ層に対して、個別的にY軸アドレスをデコーディングすることができる。

[0062]

図6は、本発明のさらに他の実施形態による積層メモリ素子を示す断面図である。

[0063]

図 6 を参照すれば、積層メモリ素子 1 "は、基板 1 1 0 、複数のメモリ層 1 2 0 、複数 対の第 1 X デコーダ層 1 3 1 a , 1 3 2 a , 1 3 3 a 及び / または第 2 X デコーダ層 1 3

20

30

40

50

1 b , 1 3 2 b , 1 3 3 b 及び / または複数の Y デコーダ層 1 4 1 , 1 4 2 を含む。この実施形態の積層メモリ素子 1 " は、図 1 ないし図 4 の積層メモリ素子 1 で、一部構成を変形したものであり、従って、重複する説明は省略する。

### [0064]

複数のメモリグループMG1,MG2,MG3,MG4の間には、Yデコーダ層及び / または1対の第1Xデコーダ層及び第2Xデコーダ層が、互いに入れ違いながら配されうる。具体的には、積層メモリ素子1"で、1対の第1Xデコーダ層131a及び第2Xデコーダ層131b、メモリグループMG1、Yデコーダ層131a及び第2Xデコーダ層131g、メモリグループMG2、1対の第1Xデコーダ層132a及び第2Xデコーダ層132b、メモリグループMG3、Yデコーダ層142、メモリグループMG4、及び / または1対の第1Xデコーダ層133bが、基板110上に順次に積層される。このとき、Yデコーダ層141及びYデコーダ層141を中心に上下に配されたメモリグループMG1,MG2は、第2基本積層構造20とし、Xデコーダ層対132a,132b及びXデコーダ層対132a,132bを中心に上下に配されたメモリグループMG2,MG3は、第1基本積層構造10′とする。第2基本積層構造20は、図1に含まれた構成と実質的に同一なので、これについての説明は省略する。

#### [0065]

積層メモリ素子1"は、基板110上に積層される複数の第1基本積層構造10′を含み、複数の第1基本積層構造10′間には、複数のYデコーダ層141,142が介在される。第1基本積層構造10′で第1Xデコーダ層132aは、その上部に隣接して積層されたメモリグループMG3のメモリ層120に、第1前面連結ライン135F′及び第1背面連結ライン135B′を介して連結され、第2Xデコーダ層132bは、その下部に隣接して積層されたメモリグループMG2のメモリ層120に、第2前面連結ライン135F″及び第2背面連結ライン135B″を介して連結されうる。

#### [0066]

これにより、第1Xデコーダ層132aは、その上部に隣接して積層されたメモリグループMG3のメモリ層120と電気的に信号を送受信でき、第2Xデコーダ層132bは、その下部に隣接して積層されたメモリグループMG2のメモリ層120と電気的に信号を送受信することができる。

# [0067]

本実施形態によれば、隣接した2つのメモリグループは、その間に配されるYデコーダ層は共有するが、その間に配されるXデコーダ層は共有しない。換言すれば、複数のメモリグループ間に、Yデコーダ層と1対のXデコーダ層とが交互に配され、隣接した2つのメモリグループ間には、1層のYデコーダ層が存在し、隣接した2つのメモリグループ間には、2層のXデコーダ層が存在する。これにより、隣接した2つのメモリグループに含まれたメモリ層に対して、個別的にX軸アドレスをデコーディングすることができる。

# [0068]

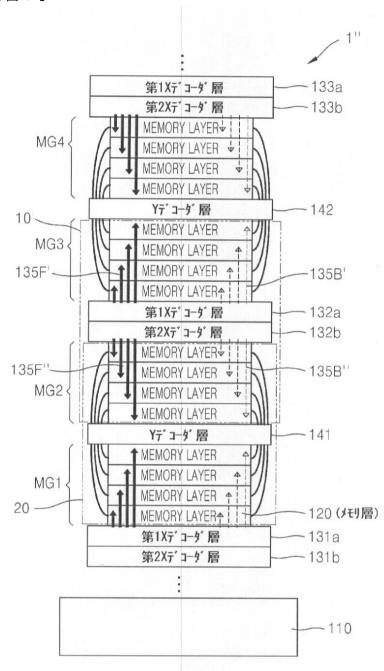

図7は、本発明の他の実施形態による積層メモリ素子を示す断面図である。

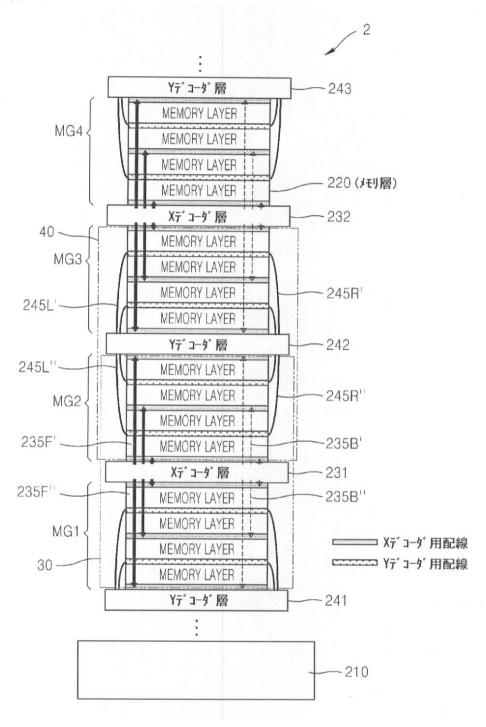

#### [0069]

図7を参照すれば、積層メモリ素子2は、基板210、複数のメモリ層220、複数のXデコーダ層231,232及び複数のYデコーダ層241,242,243を含むことができる。図7では、図解の便宜上、2層のXデコーダ層231,232と3層のYデコーダ層241,242,243とを図示したが、積層メモリ素子2は、さらに多数のXデコーダ層及びYデコーダ層を含むことができる。この実施形態の積層メモリ素子2は、図1の積層メモリ素子1で、一部構成を変形したものであり、従って、重複する説明は省略する。

#### [0070]

基板 1 1 0 上に複数のメモリ層 2 2 0 が積層され、複数のメモリ層 2 2 0 は、複数のメモリグループ M G 1 , M G 2 , M G 3 , M G 4 にグループ化されうる。複数のメモリグループ M G 1 , M G 2 , M G 3 , M G 4 間には、Y デコーダ層 2 4 1 , 2 4 2 , 2 4 3 と X

デコーダ層 2 3 1 , 2 3 2 とが交互に配されうる。このとき、 X デコーダ層 2 3 1 、及び X デコーダ層 2 3 1 を中心に上下に配されたメモリグループ M G 1 , M G 2 は、第 1 基本 積層構造 3 0 とし、 Y デコーダ層 2 4 2 、及び Y デコーダ層 2 4 2 を中心に上下に配されたメモリグループ M G 2 , M G 3 は、第 2 基本積層構造 4 0 とする。以下、第 1 基本積層構造 3 0 及び第 2 基本積層構造 4 0 について詳述する。

### [0071]

まず、積層メモリ素子2は、基板220上に積層される複数の第1基本積層構造30を含み、複数の第1基本積層構造30間には、複数のYデコーダ層241,242,243が介在される。第1基本積層構造30でXデコーダ層231は、その上部に隣接して積層されたメモリグループMG2のメモリ層220と、第1前面連結ライン235F"及び/または第1背面連結ライン235B"を介して連結され、その下部に隣接して積層されたメモリグループMG1のメモリ層220と、第2前面連結ライン235F"及び/または第2背面連結ライン235B"を介して連結されうる。

### [0072]

このとき、各メモリグループに含まれたメモリ層 2 2 0 のうち一部は、 X デコーダ用配線を共有できるが、 X デコーダ用配線は、 ワードラインでありうる。本実施形態で、各メモリグループに含まれたメモリ層 2 2 0 のうち、二番目のメモリ層と三番目のメモリ層は、 X デコーダ用配線を共有できる。従って、 X デコーダ層 2 3 1 は、その上部に隣接して積層されたメモリグループ M G 2 のメモリ層 2 2 0 との連結のために、 3 本の第 1 前面連結ライン 2 3 5 F 7 及び 3 本の第 1 背面連結ライン 2 3 5 F 7 及び 3 本の第 2 背面連結ライン 2 3 5 F 7 及び 3 本の第 2 背面連結ライン 2 3 5 F 7 及び 3 本の第 2 背面連結ライン 2 3 5 F 7 及び 3 本の第 2 背面連結ライン 2 3 5 F 7 及び 3 本の第 2 背面連結ライン 2 3 5 F 7 及び 3 本の第 2 背面連結ライン 2 3 5 F 7 及び 3 本の第 2 背面連結ライン 2 3 5 F 7 及び 3 本の第 2 背面連結ライン 2 3 5 F 7 を必要とすることになる。

#### [0073]

次に、積層メモリ素子2は、基板210上に積層される複数の第2基本積層構造40を含み、複数の第2基本積層構造40間には、複数のXデコーダ層231,232が介在される。第2基本積層構造40でYデコーダ層242は、その上部に隣接して積層されたメモリグループMG3のメモリ層220と、第1左側連結ライン245L,及び第1右側連結ライン245R,を介して連結され、その下部に隣接して積層されたメモリグループMG2のメモリ層220と、第2左側連結ライン245L,及び/または第2右側連結ライン245R,を介して連結されうる。

### [0074]

このとき、各メモリグループに含まれたメモリ層 2 2 0 のうち一部は、 Y デコーダ用配線を共有できるが、 Y デコーダ用配線は、 ビットラインでありうる。本実施形態で、 各メモリグループに含まれたメモリ層 2 2 0 のうち、最初のメモリ層と二番目のメモリ層は、 Y デコーダ用配線を共有でき、 三番目のメモリ層と四番目のメモリ層は、 Y デコーダ用配線を共有できる。従って、 Y デコーダ層 2 4 2 は、その上部に隣接して積層されたメモリグループ M G 3 のメモリ層 2 2 0 との連結のために、 2 本の第 1 左側連結ライン 2 4 5 L 7 及び 2 本の第 2 右側連結ライン 2 4 5 L 7 を必要とすることになり。また、 Y デコーダ層 2 4 2 は、 その下部に隣接して積層されたメモリグループ M G 2 のメモリ層 2 2 0 との連結のために、 2 本の第 2 左側連結ライン 2 4 5 L 7 及び 2 本の第 2 右側連結ライン 2 4 5 R 7 を必要とすることになる。

### [0075]

本実施形態によれば、各メモリグループに含まれたメモリ層 2 2 0 のうち一部は、 X デコーダ用配線 / Y デコーダ用配線を共有するので、 X デコーダ層 2 3 1 / Y デコーダ層 2 4 2 と各メモリグループに含まれたメモリ層 2 2 0 との連結ラインの本数が減ることになる。また、 X デコーダ層 2 3 1 / Y デコーダ層 2 4 2 でデコーディングするメモリセルの個数が減ることになるので、 X デコーダ層 2 3 1 / Y デコーダ層 2 4 2 の複雑度を低下させることができるので、 その具現も簡単にできる。

### [0076]

50

10

20

30

また、本実施形態の変形された実施形態によれば、積層メモリ素子は、複数のメモリグループ間に、メデコーダ層及び1対のYデコーダ層が交互に介在しうる。このとき、メデコーダ層は、その上下部に積層されたメモリグループに共通に連結されるが、1対のYデコーダ層は、その上部に積層されたメモリグループ及びその下部に積層されたメモリグループにそれぞれ連結されうる。また、本実施形態の他の変形された実施形態によれば、積層メモリ素子は、複数のメモリグループ間に、Yデコーダ層及び1対のXデコーダ層が交互に介在しうる。このとき、Yデコーダ層は、その上下部に積層されたメモリグループに共通に連結されるが、1対のXデコーダ層は、その上部に積層されたメモリグループ及びその下部に積層されたメモリグループにそれぞれ連結されうる。

### [0077]

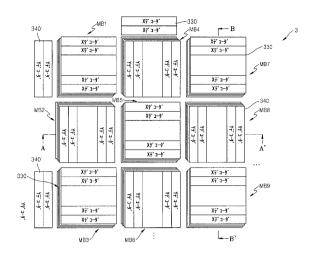

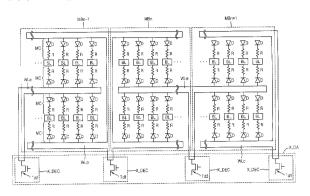

図8は、本発明の一実施形態による積層メモリ素子を示す平面図である。

### [0078]

図8を参照すれば、積層メモリ素子3は、基板(図示せず)上に配される複数の積層メモリブロックである第1メモリブロックMB1ないし第9メモリブロックMB9を含むことができる。図8には、便宜上、9個のメモリブロックMB1ないしMB9が図示されているが、積層メモリ素子3は、さらに多数のメモリブロックを含むことができる。

#### [0079]

各メモリブロックMB1ないしMB9は、複数のメモリ層及び複数のデコーダ層を含むことができるが、各メモリブロックMB1ないしMB9の所定レベルに配されるデコーダ層は、隣接したメモリブロックの同一レベルに配されるデコーダ層と交互に配されうる。具体的には、各メモリブロックMB1ないしMB9の所定レベルに、Xデコーダ層330が配されれば、隣接したメモリブロックの同一レベルには、Yデコーダ層340が配されうる。これにより、複数のメモリブロックMB1ないしMB9の同一レベルで、Xデコーダ層330とYデコーダ層340は、格子構造をなすことができる。

#### [080]

各メモリブロックMB1ないしMB9内の各メモリ層に含まれたメモリセルは、第1グループ及び第2グループに分類されうる。ここで、各Xデコーダ層330は、複数のXデコーダアレイを含むことができるが、このとき、Xデコーダアレイは、図2に図示されたXデコーダアレイと類似した構造を有することができる。また、各Yデコーダ層340は、複数のYデコーダアレイを含むことができるが、このとき、Yデコーダアレイは、図3に図示されたYデコーダアレイと類似した構造を有することができる。

# [0081]

具体的には、第2メモリブロックMB2内の各メモリ層の第1グループ及び第2グループは、第2メモリブロックMB2に含まれたYデコーダ層340に連結され、第2メモリブロックMB2内の各メモリ層の第1グループは、第1メモリブロックMB1に含まれたXデコーダ層330に連結され、各メモリ層の第2グループは、第3メモリブロックMB3に含まれたXデコーダ層330に連結されうる。このように、各メモリブロックMB1ないしMB9内のメモリ層は、当該メモリブロック内に含まれたデコーダ層及び隣接したメモリブロック内に含まれたデコーダ層に連結され、メモリ層の動作に必要なX軸アドレス及びY軸アドレスをデコーディングすることができる。

# [ 0 0 8 2 ]

一方、第1メモリブロックMB1内の各メモリ層の第1グループ及び第2グループは、第1メモリブロックMB1に含まれたXデコーダ層330に連結され、第1メモリブロックMB1に含まれたXデコーダ層330に連結され、第1メモリブロックMB1の含まれたYデコーダ層340に連結され、各メモリ層の第2グループは、第1メモリブロックMB1の左側に隣接して配されたYデコーダ層340′に連結されうる。また、第4メモリブロックMB4に含まれたYデコーダ層340に連結され、第4メモリブロックMB4内の各メモリ層の第1グループは、第4メモリブロックMB4下で記され、第1グループは、第5メモリブロックMB5に含まれたXデコーダ層330に連結され、各メモリ層の第2グループは、第4メモリブロックMB4の上側に隣接して配されたXデコ

10

20

30

40

20

30

40

50

ーダ層330′に連結されうる。このように、積層メモリ素子3で、最外郭に配されて隣接するメモリブロックのないメモリブロックの場合には、X軸アドレス情報またはY軸アドレス情報を受信するための追加的なデコーダ層330′,340′の配置が要求される

### [0083]

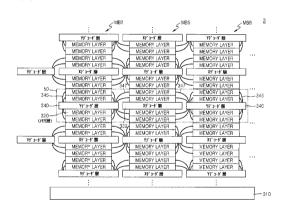

図9は、図8の積層メモリ素子で、A-A'線に沿って切り取った断面図の一例である。図10は、図8の積層メモリ素子で、B-B'線に沿って切り取った断面図の一例である。

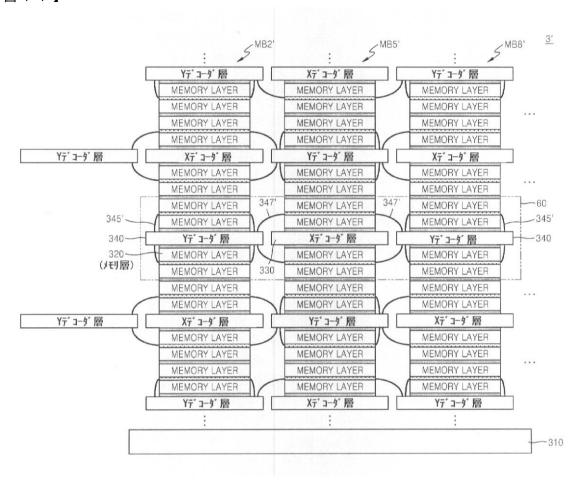

#### [0084]

図9及び図10を参照すれば、基板310上にA-A'線方向に、第2メモリブロックMB2、第5メモリブロックMB5及び第8メモリブロックMB8が隣接して配され、B-B'線方向に、第7メモリブロックMB7、第8メモリブロックMB8及び第9メモリプロックMB9が隣接して配される。ここで、各メモリブロックは、図1に図示された積層メモリ素子1に対応しうる。積層メモリ素子3では、基板310上に、複数の第1基本積層構造50が反復的に形成されると見ることができ、複数の第2基本積層構造55が反復的に形成されるとも見ることができ、複数の第2基本積層構造55が反復的に形成されるとも見ることができる。一方、理解を助けるために図9では、Xデコーダ連結ラインが省略され、図10では、Yデコーダ連結ラインが省略された状態で図式化されている。図9のYデコーダ連結状態と図10のXデコーダ連結状態とを結合したものが、本実施形態によるメモリ素子の全体的な構造となる。

#### [0085]

まず、図9を使用しつつ、Yデコーダ連結構造と関連したメモリ構造について説明すれば、次の通りである。

#### [0086]

第1基本積層構造50は、同一レベルに交互に配されるYデコーダ層340及びXデコーダ層330と、Yデコーダ層340及びXデコーダ層330それぞれの上下に隣接して配されるメモリ層320と、を含む。具体的には、第1基本積層構造50は、第2メモリブロックMB2に含まれたYデコーダ層340、及びYデコーダ層340の上下部に隣接して配されたメモリ層320と、第5メモリブロックMB5に含まれたXデコーダ層330、及びXデコーダ層330の上下部に隣接して配されたメモリ層320と、第8メモリブロックMB8に含まれたYデコーダ層340、及びYデコーダ層340の上下部に隣接して配されたメモリ層320と、を含むことができる。本実施形態で、第1基本積層構造50で、各デコーダ層330,340の上部と下部とには、それぞれ2層のメモリ層320が配されうる。

### [0087]

第1基本積層構造50で、第2メモリブロックMB2及び第8メモリブロックMB8のメモリ層320間には、Yデコーダ層340が含まれ、第5メモリブロックMB5のメモリ層320間には、Xデコーダ層330が含まれる。従って、第2メモリブロックMB2及び第8メモリブロックMB8のメモリ層320は、当該メモリブロックに含まれたYデコーダ層340に連結されてY軸アドレス情報を受信することができ、第5メモリブロックMB5のメモリ層320は、隣接するメモリブロックに含まれたYデコーダ層340に連結されてY軸アドレス情報を受信することができる。

#### [0088]

具体的には、第2メモリブロックMB2に含まれた各メモリ層320の第1グループ及び第2グループは、第2メモリブロックMB2に含まれたYデコーダ層340と、第1連結ライン345を介して連結され、第8メモリブロックMB2に含まれた各メモリ層320の第1グループ及び第2グループは、第8メモリブロックMB8に含まれたYデコーダ層340と、第1連結ライン345を介して連結されうる。一方、第5メモリブロックMB5に含まれたYデコーダ層340と、第2連結ライン347を介して連結され、第2グループは、第8メモリブロックMB8に含まれたYデコーダ層340と、第2連結ライン347を介し

て連結されうる。

#### [0089]

次に、図10を参照しつつ、 X デコーダ連結構造と関連したメモリ構造について説明すれば、次の通りである。

### [0090]

第2基本積層構造55は、同一レベルに交互に配されるXデコーダ層330及びYデコーダ層340と、Xデコーダ層330及びYデコーダ層340それぞれの上下に隣接して配されるメモリ層320と、を含む。具体的には、第2基本積層構造55は、第7メモリプロックMB7に含まれたXデコーダ層330、及びXデコーダ層330の上下部に隣接して配されたメモリ層320と、第8メモリプロックMB8に含まれたYデコーダ層340、及びYデコーダ層340の上下部に隣接して配されたメモリ層320と、第9メモリプロックMB9に含まれたXデコーダ層330、及びXデコーダ層330の上下部に隣接して配されたメモリ層320を、を含むことができる。本実施形態で、第2基本積層構造55で、各デコーダ層330,340の上部と下部とには、それぞれ2層のメモリ層320が配されうる。

#### [0091]

第2基本積層構造55で、第7メモリブロックMB7及び第9メモリブロックMB9のメモリ層320間には、Xデコーダ層330が含まれ、第8メモリブロックMB8のメモリ層320間には、Yデコーダ層340が含まれる。従って、第7メモリブロックMB7及び第9メモリブロックMB9のメモリ層320は、当該メモリブロックに含まれたXデコーダ層330に連結されてX軸アドレス情報を受信することができ、第8メモリブロックMB8のメモリ層320は、隣接するメモリブロックに含まれたXデコーダ層330に連結されてX軸アドレス情報を受信することができる。

具体的には、第7メモリブロックMB7に含まれた各メモリ層320の第1グループ及び第2グループは、第7メモリブロックMB7に含まれたXデコーダ層330と、第3連結ライン335を介して連結され、第9メモリブロックMB9に含まれたXデコーダ層320の第1グループ及び第2グループは、第9メモリブロックMB9に含まれたXデコーダ層330と、第3連結ライン335を介して連結されうる。一方、第8メモリブロックMB8に含まれた各メモリ層320の第1グループは、第7メモリブロックMB7に含まれたXデコーダ層330と、第4連結ライン337を介して連結され、第2グループは、第9メモリブロックMB9に含まれたXデコーダ層330と、第4連結ライン337を介して連結されうる。

#### [0092]

本実施形態で、各メモリブロックで、複数のメモリグループ間にXデコーダ層とYデコーダ層は、互いに交互に介在され、複数のメモリブロックの同一レベルには、Xデコーダ層とYデコーダ層とが交互に配されうる。これにより、各メモリブロックのXデコーダ層は、それと隣接したメモリブロックで、同一レベルに位置するYデコーダ層によって取り囲まれるように配されうる。同様に、各メモリブロックのYデコーダ層は、それと隣接したメモリブロックで、同一レベルに位置するXデコーダ層によって取り囲まれるように配されうる。従って、基板310上の同一レベルには、メモリブロックを横切ってXデコーダ層とYデコーダ層とが交互に配されうる。

#### [0093]

本実施形態によれば、第1基本積層構造50または第2基本積層構造55で、各メモリブロックに含まれたメモリ層320は、当該メモリブロック内のデコーダ層及び隣接したメモリブロックで、同一レベルに位置するデコーダ層に連結されうる。従って、連結ラインの長さを短く具現できるので、信号の干渉を減らすことができ、連結効率を向上させることができる。

### [0094]

また、各メモリ層320に含まれたメモリセルは、2つのグループに分類されるので、第1基本積層構造50または第2基本積層構造55で、各デコーダ層330,340は、

10

20

30

40

20

30

40

50

当該メモリブロック内のメモリ層320の数の1/2に該当する複数のデコーダ対を含む。1つのデコーダ対は、1つの連結ライン対を介して各メモリ層320に連結されることによって、各メモリ層320に含まれたメモリセルを2つのグループに分けてデコーディングすることができる。従って、各デコーダ層330,340に含まれたデコーダの複雑度を減らすことができるので、結果的に、積層メモリ素子3の集積効率を向上させることができる。

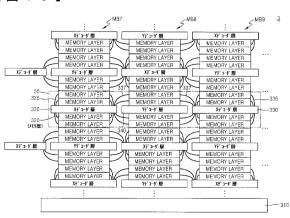

#### [0095]

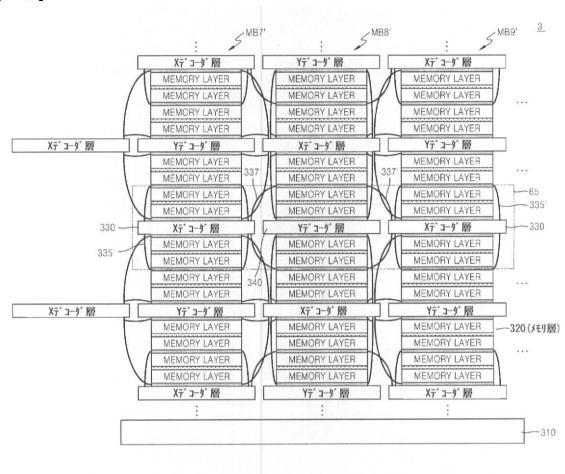

図11は、図8の積層メモリ素子で、A-A'線に沿って切り取った断面図の他の例である。図12は、図8の積層メモリ素子で、B-B'線に沿って切り取った断面図の他の例である。

[0096]

図11及び図12を参照すれば、基板310上にA-A,線方向に、第2メモリブロックMB2,、第5メモリブロックMB5,及び第8メモリブロックMB8,が隣接して配され、B-B,線方向に、第7メモリブロックMB7,、第8メモリブロックMB8,及び第9メモリブロックMB9,が隣接して配される。ここで、各メモリブロックMB8,及に図示された積層メモリ素子2に対応しうる。積層メモリ素子3,では、基板310上に、複数の第1基本積層構造60が反復的に形成されると見ることができ、複数の第2基本積層構造65が反復的に形成されるとも見ることができる。一方、理解を助けるために、図11では、Xデコーダ連結ラインが省略され、図12では、Yデコーダ連結ラインが省略された状態で図式化されている。図11のYデコーダ連結状態と図12のXデコーダ連結状態とを結合したものが、本実施形態によるメモリ素子の全体的な構造となる。

[0097]

まず、図11を使用しつつ、Yデコーダ連結構造と関連したメモリ構造について説明すれば、次の通りである。

[0098]

第1基本積層構造60は、同一レベルに交互に配されるYデコーダ層340及びXデコーダ層330と、Yデコーダ層340及びXデコーダ層330それぞれの上下に隣接して配されるメモリ層320と、を含む。具体的には、第1基本積層構造60は、第2メモリブロックMB2′に含まれたYデコーダ層340、及びYデコーダ層340の上下部に隣接して配されたメモリ層320と、第5メモリブロックMB5′に含まれたXデコーダ層330、及びXデコーダ層330の上下部に隣接して配されたメモリ層320と、第8メモリブロックMB8′に含まれたYデコーダ層340、及びYデコーダ層340の上下部に隣接して配されたメモリ層320と、を含むことができる。本実施形態で、第1基本積層構造60で、各デコーダ層330,340の上部と下部とには、それぞれ2層のメモリ層320が配されうる。

[0099]

第1基本積層構造60で、第2ブロックメモリMB2、及び第8メモリブロックMB8、のメモリ層320間には、Yデコーダ層340が含まれ、第5メモリブロックMB5、のメモリ層320間には、Xデコーダ層330が含まれる。従って、第2ブロックメモリMB2、及び第8メモリブロックMB8、のメモリ層320は、当該メモリブロックに含まれたYデコーダ層340に連結されてY軸アドレス情報を受信することができ、第5メモリブロックMB5、のメモリ層320は、隣接するメモリブロックに含まれたYデコーダ層340に連結されてY軸アドレス情報を受信することができる。

[0100]

具体的には、第2メモリブロックMB2 ′ に含まれた各メモリ層320の第1グループ及び第2グループは、第2メモリブロックMB2 ′ に含まれたYデコーダ層340と、第1連結ライン345 ′ を介して連結され、第8メモリブロックMB8 ′ に含まれた各メモリ層320の第1グループ及び第2グループは、第8メモリブロックMB8 ′ に含まれたYデコーダ層340と、第1連結ライン345′を介して連結されうる。一方、第5メモリブロックMB5′に含まれた各メモリ層320の第1グループは、第2メモリブロック

20

30

40

50

M B 2 ' に含まれた Y デコーダ層 3 4 0 と、 第 2 連結ライン 3 4 7 ' を介して連結され、 第 2 グループは、 第 8 メモリブロック M B 8 ' に含まれた Y デコーダ層 3 4 0 と、 第 2 連結ライン 3 4 7 ' を介して連結されうる。

#### [ 0 1 0 1 ]

このとき、各メモリグループの最初のメモリ層320と二番目のメモリ層320は、Yゴーダ用配線を共有し、三番目のメモリ層320と四番目のメモリ層320は、Yコーダ用配線を共有できる。従って、第2メモリプロックMB2,でYデコーダ層340は、1対の第1連結ライン345,を介して、その上部に配されたメモリ層320間のYデコーダ用配線に共通に連結され、他の対の第1連結ライン345,を介して、第2々でリプロックMB2,のYデコーダ層340は、1本の第2連結ライン347,を介して、第1000円で、メデコーダ層340は、1本の第2連結ライン347,を介して、第のYデコーダ用配線に共通に連結され、他の1本の第2連結ライン347,を介して、おこののYデコーダ層340は、1本の第2連結ライン347,を介して、第5メモリプロックMB5,で、メデコーダ層330の下部に配されたメモリ層320間のYデコーダ層310は、1本の第2連結ライン347,を介して、第5メモリプロックMB5,で、メデコーダ層330のの第2連結ライン347,を介して、第5メモリプロックMB5,で、メデコーダ層330の下部に配されたメモリ層320間のYデコーダ層310間のYデコーダ用配線に共通に連結されうる。

### [0102]

次に、図12を参照しつつ、 X デコーダ連結構造と関連したメモリ構造について説明すれば、次の通りである。

#### [0103]

第2基本積層構造65は、同一レベルに交互に配されるメデコーダ層330及びYデコーダ層340と、メデコーダ層330及びYデコーダ層340それぞれの上下に隣接して配されるメモリ層320と、を含む。具体的には、第2基本積層構造65は、第7メモリブロックMB7′に含まれたメデコーダ層330、及びメデコーダ層330の上下部に隣接して配されたメモリ層320と、第8メモリブロックMB8′に含まれたYデコーダ層340、及びYデコーダ層340の上下部に隣接して配されたメモリ層320と、第9メモリブロックMB9′に含まれたXデコーダ層330、及びXデコーダ層330の上下部に隣接して配されたメモリ層320と、を含むことができる。本実施形態で、第2基本積層構造65で、各デコーダ層330,340の上部と下部とには、それぞれ2層のメモリ層320が配されうる。

# [ 0 1 0 4 ]

第2基本積層構造65で、第7メモリブロックMB7′及び第9メモリブロックMB9′のメモリ層320間には、Xデコーダ層330が含まれ、第8メモリブロックMB8′のメモリ層320間には、Yデコーダ層340が含まれる。従って、第7メモリブロックMB3′及び第9メモリブロックMB9′のメモリ層320は、当該メモリブロックに含まれたXデコーダ層330に連結されてX軸アドレス情報を受信することができ、第8メモリブロックMB5′のメモリ層320は、隣接するメモリブロックに含まれたXデコーダ層330に連結されてX軸アドレス情報を受信することができる。

#### [0105]

具体的には、第7メモリブロックMB7′に含まれた各メモリ層320の第1グループ及び第2グループは、第7メモリブロックMB7′に含まれたXデコーダ層330と、第3連結ライン335′を介して連結され、第9メモリブロックMB9′に含まれた各メモリ層320の第1グループ及び第2グループは、第9メモリブロックMB9′に含まれたXデコーダ層330と、第3連結ライン335′を介して連結されうる。一方、第8メモリブロックMB8′に含まれた各メモリ層320の第1グループは、第7メモリブロックMB7′に含まれたXデコーダ層330と、第4連結ライン337′を介して連結され、第2グループは、第9メモリブロックMB9′に含まれたXデコーダ層330と、第4連

結ライン337′を介して連結されうる。

### [0106]

このとき、各メモリグループの二番目のメモリ層320と三番目のメモリ層320は、 X デコーダ用配線を共有できる。従って、第 7 メモリブロック M B 7 ′ で X デコーダ層 3 3 0 は、 1 対の第 3 連結ライン 3 3 5 'を介して、その上部に配されたメモリ層 3 2 0 間 のXデコーダ用配線に共通に連結され、他の対の第3連結ライン335′を介して、その 下部に配されたメモリ層320間のXデコーダ用配線に共通に連結されうる。また、第7 メモリブロックMB7′のXデコーダ層330は、1本の第4連結ライン337′を介し て、第8メモリブロックMB8′で、Yデコーダ層330の上部に配された二番目のメモ リ層 3 2 0 と三番目のメモリ層 3 2 0 との間の X デコーダ用配線に共通に連結され、他の 1 本の第 4 連結ライン 3 3 7 'を介して、 Y デコーダ層 3 3 0 の下部に配された二番目の メモリ層 3 2 0 と三番目のメモリ層 3 2 0 との間の X デコーダ用配線に共通に連結されう る。また、 第 9 メモリブロック M B 9 ' の X デコーダ層 3 3 0 は、 1 本の第 4 連結ライン 3 3 7 ′を介して、第 8 メモリブロック M B 8 ′で、 Y デコーダ層 3 4 0 の上部に配され た二番目のメモリ層 3 2 0 と三番目のメモリ層 3 2 0 との間の X デコーダ用配線に共通に 連 結 さ れ 、 他 の 1 本 の 第 4 連 結 ラ イ ン 3 3 7 ' を 介 し て 、 Y デ コ ー ダ 層 3 4 0 の 下 部 に 配 された二番目のメモリ層320と三番目のメモリ層320との間のXデコーダ用配線に共 通に連結されうる。

#### [ 0 1 0 7 ]

図12には図示されていないが、第2基本積層構造65で、第7メモリブロックMB7 '及び第9メモリブロックMB9'に含まれたメモリ層320は、それぞれ第7メモリブロックMB7'及び第9メモリブロックMB9'の背面に配されたメモリブロック(図示せず)に含まれたYデコーダ層からY軸アドレス情報を受信することができる。

#### [0108]

本実施形態で、各メモリブロックで、複数のメモリグループ間のおけるメデコーダ層と Yデコーダ層は、互いに交互に介在され、複数のメモリブロックの同一レベルには、メデ コーダ層とYデコーダ層とが交互に配されうる。これにより、各メモリブロックのメデコー ダ層は、それと隣接したメモリブロックで、同一レベルに位置するYデコーダ層によっ て取り囲まれるように配されうる。同様に、各メモリブロックのYデコーダ層は、それと 隣接したメモリブロックで、同一レベルに位置するXデコーダ層によって取り囲まれるように配されうる。従って、基板310上の同一レベルには、メモリブロックを横切ってX デコーダ層とYデコーダ層とが交互に配されうる。

#### [0109]

本実施形態によれば、第1基本積層構造60または第2基本積層構造65で、各メモリブロックに含まれたメモリ層320は、当該メモリブロック内のデコーダ層及び隣接したメモリブロックで、同一レベルに位置するデコーダ層に連結されうる。従って、連結ラインの長さを短く具現できるので、信号の干渉を減らすことができ、連結効率を向上させることができる。

### [0110]

また、各メモリ層320に含まれたメモリセルは、2つのグループに分類されるので、第1基本積層構造60または第2基本積層構造65で各デコーダ層330,340は、当該メモリグループ内のメモリ層320の数の1/2に該当する複数のデコーダ対を含む。1つのデコーダ対は、1本の連結ライン対を介して、各メモリ層320に連結されることによって、各メモリ層320に含まれたメモリセルを2つのグループに分けてデコーディングすることができる。従って、各デコーダ層330,340に含まれたデコーダの複雑度を減らすことができるので、結果的に、積層メモリ素子3の集積効率を向上させることができる。

### [0111]

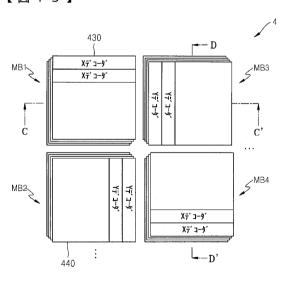

図13は、本発明の他の実施形態による積層メモリ素子を示す平面図である。

### [0112]

50

10

20

30

20

30

40

50

図13を参照すれば、積層メモリ素子4は、基板(図示せず)上に配される複数の積層メモリプロックの第1メモリプロックMB1ないし第4メモリプロックMB4を含むことができる。図13には、便宜上、4個のメモリブロックMB1ないしMB4が図示されているが、積層メモリ素子4は、さらに多数のメモリブロックを含むことができる。この実施形態は、図8の積層メモリ素子3で、一部構成を変形したものであり、従って、重複する説明は省略する。

#### [0113]

各メモリブロックMB1ないしMB4は、複数のメモリ層及び複数のデコーダ層を含むことができるが、各メモリブロックMB1ないしMB4の所定レベルに配されるデコーダ層は、隣接したメモリブロックの同一レベルに配されるデコーダ層と交互に配されうる。具体的には、各メモリブロックMB1ないしMB4の所定レベルに、Xデコーダ層430が配されれば、隣接したメモリブロックの同一レベルには、Yデコーダ層440が配されうる。これにより、複数のメモリブロックMB1ないしMB4の同一レベルで、Xデコーダ層430とYデコーダ層440は、格子構造をなすことができる。

#### [0114]

ここで、各 X デコーダ層 4 3 0 は、一つまたはそれ以上の X デコーダアレイを含むことができ、各 Y デコーダ層 4 4 0 は、一つまたはそれ以上の Y デコーダアレイを含むことができる。

### [0115]

具体的には、第1メモリブロックMB1内の各メモリ層は、第1メモリブロックMB1に含まれたXデコーダ層430に連結され、第1メモリブロックMB1内の各メモリ層は、第3メモリブロックMB1に含まれたYデコーダ層440に連結されうる。また、第2メモリブロックMB2内の各メモリ層は、第2メモリブロックMB2に含まれたYデコーダ層440に連結され、第2メモリブロックMB2内の各メモリ層は、第4メモリブロックMB4に含まれたXデコーダ層430に連結されうる。従って、積層メモリ素子4で、最外郭に配されて隣接するメモリブロックのないメモリブロックの場合にも、X軸アドレス情報またはY軸アドレス情報を受信するための追加的なデコーダ層の配置が要求されない。これにより、積層メモリ素子4の全体具現面積を縮めることができる。

### [0116]

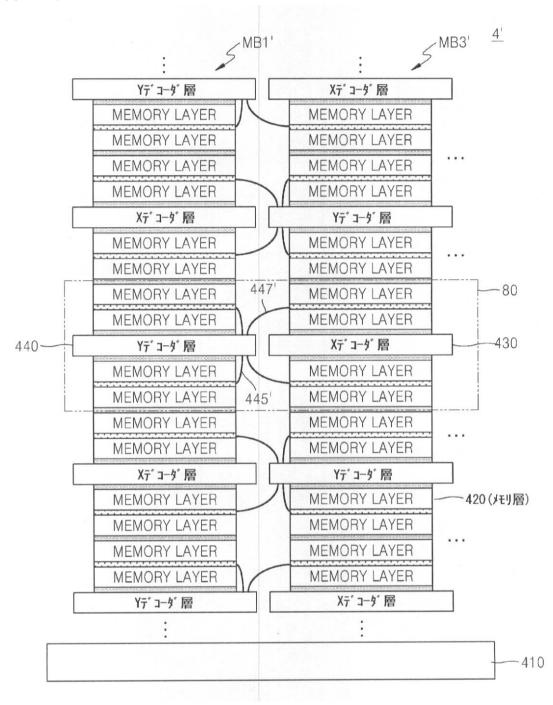

図14は、図13の積層メモリ素子で、C-C′線に沿って切り取った断面図の一例である。図15は、図13の積層メモリ素子で、D-D′線に沿って切り取った断面図の一例である。

#### [0117]

図14及び図15を参照すれば、基板410上にC-C,線方向に、第1メモリブロックMB1及び第3メモリブロックMB3が隣接して配され、D-D,線方向に、第3目盛るブロックMB3及び第4メモリブロックMB4が隣接して配される。ここで、各メモリブロックは、図1に図示された積層メモリ素子1に対応しうる。積層メモリ素子4では、基板410上に複数の第1基本積層構造70が反復的に形成されると見ることができ、複数の第2基本積層構造75が反復的に形成されるとも見ることができる。一方、理解を助けるために図14では、Xデコーダ連結ラインが省略され、図15では、Yデコーダ連結けるために図14では、Xデコーダ連結ラインが省略された状態で図式化されている。図14のYデコーダ連結状態と図15のXデコーダ連結状態とを結合したものが、本実施形態によるメモリ素子の全体的な構造となる。

# [0118]

まず、図14を使用しつつ、Yデコーダ連結構造と関連したメモリ構造について説明すれば、次の通りである。

#### [0119]

第1基本積層構造70は、同一レベルに交互に配されるYデコーダ層440及びXデコーダ層430と、Yデコーダ層440及びXデコーダ層430それぞれの上下に隣接して配されるメモリ層420と、を含む。具体的には、第1基本積層構造70は、第1メモリ

ブロックMB1に含まれたYデコーダ層440、及びYデコーダ層440の上下部に隣接して配されたメモリ層420と、第3メモリブロックMB3に含まれたXデコーダ層43 0、及びXデコーダ層430の上下部に隣接して配されたメモリ層420と、を含むことができる。本実施形態で、第1基本積層構造70で、各デコーダ層430,440の上部と下部とには、それぞれ2層のメモリ層420が配されうる。

[0120]

第1基本積層構造 70で、第1メモリブロックMB1のメモリ層 420間には、 Y デコーダ層 440 が含まれ、第3メモリブロックMB3のメモリ層 420間には、 X デコーダ層 430 が含まれる。従って、第1メモリブロックMB1のメモリ層 420は、当該メモリブロックに含まれた Y デコーダ層 440に連結されて Y 軸アドレス情報を受信することができ、第3メモリブロックMB3のメモリ層 420は、隣接するメモリブロックに含まれた Y デコーダ層 440に連結されて Y 軸アドレス情報を受信することができる。

[0121]

具体的には、第1メモリブロックMB1に含まれた各メモリ層420は、第1メモリブロックMB1に含まれたYデコーダ層440と、第1連結ライン445を介して連結され、第3メモリブロックMB3に含まれた各メモリ層420は、第1メモリブロックMB1に含まれたYデコーダ層440と、第2連結ライン447を介して連結されうる。

[0122]

次に、図15を参照しつつ、 X デコーダ連結構造と関連したメモリ構造について説明すれば、次の通りである。

20

10

[0123]

第2基本積層構造 7 5 は、同一レベルに交互に配される X デコーダ層 4 3 0 及び Y デコーダ層 4 4 0 と、 X デコーダ層 4 3 0 及び Y デコーダ層 4 4 0 それぞれの上下に隣接して配されるメモリ層 4 2 0 と、を含む。具体的には、第2基本積層構造 7 5 は、第3メモリブロック M B 3 に含まれた X デコーダ層 4 3 0 、及び X デコーダ層 4 3 0 の上下部に隣接して配されたメモリ層 4 2 0 と、第4 メモリブロック M B 4 に含まれた Y デコーダ層 4 4 0 、及び Y デコーダ層 4 4 0 の上下部に隣接して配されたメモリ層 4 2 0 と、を含むことができる。本実施形態で、第2基本積層構造 7 5 で、各デコーダ層の上部と下部とには、それぞれ 2 層のメモリ層 4 2 0 が配されうる。

[0124]

30

第2基本積層構造 75で、第3メモリブロックMB3のメモリ層 420間には、Xデコーダ層 430が含まれ、第4メモリブロックMB4のメモリ層 420間には、Yデコーダ層 440が含まれる。従って、第3メモリブロックMB3のメモリ層 420は、当該メモリブロックに含まれた X デコーダ層 430に連結されて X 軸アドレス情報を受信することができ、第4メモリブロックMB4のメモリ層 420は、隣接するメモリブロックに含まれた X デコーダ層 430に連結されて X 軸アドレス情報を受信することができる。

[0125]

具体的には、第3メモリブロックMB3に含まれた各メモリ層420は、第1メモリブロックMB1に含まれたXデコーダ層430と、第3連結ライン435を介して連結され、第4メモリブロックMB4に含まれた各メモリ層420は、第3メモリブロックMB3に含まれたXデコーダ層430と、第4連結ライン437を介して連結されうる。

40

[0126]

本実施形態で、各メモリブロックで、複数のメモリグループ間におけるメデコーダ層と Yデコーダ層は、互いに交互に介在され、複数のメモリブロックの同一レベルには、メデ コーダ層とYデコーダ層とが交互に配されうる。これにより、各メモリブロックのXデコー ダ層は、それと隣接したメモリブロックで、同一レベルに位置するYデコーダ層によっ て取り囲まれるように配されうる。同様に、各メモリブロックのYデコーダ層は、それと 隣接したメモリブロックで、同一レベルに位置するXデコーダ層によって取り囲まれるように配されうる。従って、基板410上の同一レベルには、メモリブロックを横切ってX デコーダ層とYデコーダ層とが交互に配されうる。

20

30

40

50

#### [0127]

本実施形態によれば、第1基本積層構造70または第2基本積層構造75で、各メモリブロックに含まれたメモリ層420は、当該メモリブロック内のデコーダ層及び隣接したメモリブロックで、同一レベルに位置するデコーダ層に連結されうる。従って、連結ラインの長さを短く具現できるので、信号の干渉を減らすことができ、連結効率を向上させることができる。

#### [ 0 1 2 8 ]

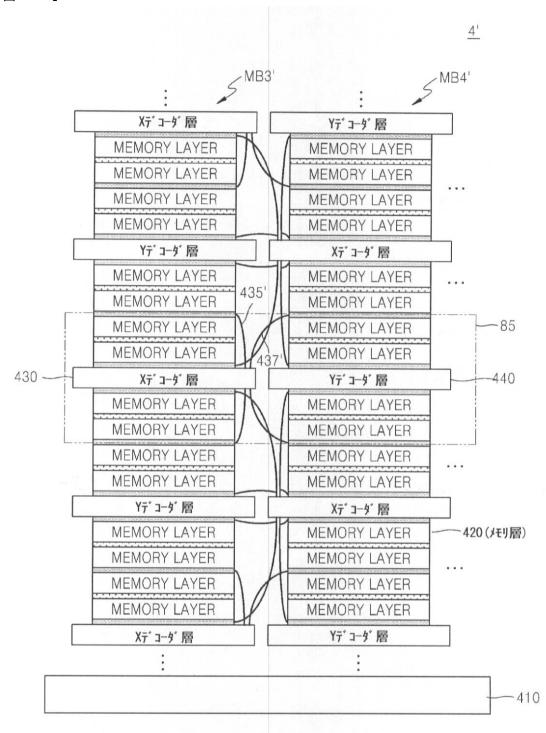

図16は、図13の積層メモリ素子で、C - C '線に沿って切り取った断面図の他の例である。図17は、図13の積層メモリ素子で、D - D '線に沿って切り取った断面図の他の例である。

[0129]

図16及び図17を参照すれば、基板410上にC-C,線方向に、第1メモリブロックMB1,及び第3メモリブロックMB3,が隣接して配され、D-D,線方向に、第3メモリブロック3,及び第4メモリブロックMB4,が隣接して配される。ここで、各メモリブロックは、図7に図示された積層メモリ素子2に対応しうる。積層メモリ素子4では、基板410上に複数の第1基本積層構造80が反復的に形成されると見ることができ、複数の第2基本積層構造85が反復的に形成されるとも見ることができる。一方、理解を助けるために、図16では、Xデコーダ連結ラインが省略され、図17では、Yデコーダ連結ラインが省略された状態で図式化されている。図16のYデコーダ連結状態と図16のXデコーダ連結状態とを結合したものが、本実施形態によるメモリ素子の全体的な構造となる。

[0130]

まず、図16を使用しつつ、Yデコーダ連結構造と関連したメモリ構造について説明すれば、次の通りである。

[0131]

第1基本積層構造80は、同一レベルに交互に配されるYデコーダ層440及びXデコーダ層430と、Yデコーダ層440及びXデコーダ層430それぞれの上下に隣接して配されるメモリ層420と、を含む。具体的には、第1基本積層構造80は、第1メモリブロックMB1′に含まれたYデコーダ層440、及びYデコーダ層440の上下部に隣接して配されたメモリ層420と、第3メモリブロックMB3′に含まれたXデコーダ層430、及びXデコーダ層430の上下部に隣接して配されたメモリ層420と、を含むことができる。本実施形態で、第1基本積層構造80で、各デコーダ層430,440の上部と下部とには、それぞれ2層のメモリ層420が配されうる。

[ 0 1 3 2 ]

第 1 基本積層構造 8 0 で、第 1 メモリブロック M B 1 'のメモリ層 4 2 0 間には、 Y デコーダ層 4 4 0 が含まれ、第 3 メモリブロック M B 3 'のメモリ層 4 2 0 間には、 X デコーダ層 4 3 0 が含まれる。従って、第 1 メモリブロック M B 1 'のメモリ層 4 2 0 は、当該メモリブロックに含まれた Y デコーダ層 4 4 0 に連結されて Y 軸アドレス情報を受信することができ、第 3 メモリブロック M B 3 'のメモリ層 4 2 0 は、隣接するメモリブロックに含まれた Y デコーダ層 4 4 0 に連結されて Y 軸アドレス情報を受信することができる

[ 0 1 3 3 ]

具体的には、第1メモリブロックMB1′に含まれた各メモリ層420は、第1メモリブロックMB1′に含まれたYデコーダ層440と、第1連結ライン445′を介して連結され、第3メモリブロックMB3′に含まれた各メモリ層320は、第1メモリブロックMB1に含まれたYデコーダ層440と、第2連結ライン447′を介して連結されうる。

[0134]

図16には図示されていないが、第2メモリブロックMB2′の各メモリグループで、 二番目のメモリ層と三番目のメモリ層は、第2メモリブロックMB2′の背面に配された

20

30

40

50

メモリブロック(図示せず)に含まれた X デコーダ層から、 X 軸アドレス情報を受信することができる。また、第 8 メモリブロック M B 8 'の各メモリグループで、二番目のメモリ層と三番目のメモリ層は、第 8 メモリブロック M B 8 'の背面に配されたメモリブロック(図示せず)に含まれた X デコーダ層から、 X 軸アドレス情報を受信することができる

### [0135]

次に、図17を参照しつつ、Xデコーダ連結構造と関連したメモリ構造について説明すれば、次の通りである。

#### [0136]

第2基本積層構造 8 5 は、同一レベルに交互に配される X デコーダ層 4 3 0 及び Y デコーダ層 4 4 0 と、 X デコーダ層 4 3 0 及び Y デコーダ層 4 4 0 それぞれの上下に隣接して配されるメモリ層 4 2 0 と、を含む。具体的には、第2基本積層構造 8 5 は、第3メモリブロック M B 3 'に含まれた X デコーダ層 4 3 0、及び X デコーダ層 4 3 0の上下部に隣接して配されたメモリ層 4 2 0 と、第4 メモリブロック M B 4 'に含まれた Y デコーダ層 4 4 0、及び Y デコーダ層 4 4 0の上下部に隣接して配されたメモリ層 4 2 0 と、を含むことができる。本実施形態で、第2基本積層構造 8 5 で、各デコーダ層の上部と下部とには、それぞれ 2 層のメモリ層 4 2 0 が配されうる。

#### [ 0 1 3 7 ]

第2基本積層構造85で、第3メモリブロックMB3,のメモリ層420間には、Xデコーダ層430が含まれ、第4メモリブロックMB4,のメモリ層420間には、Yデコーダ層440が含まれる。従って、第3メモリブロックMB3,のメモリ層420は、当該メモリブロックに含まれたXデコーダ層430に連結されてX軸アドレス情報を受信することができ、第4メモリブロックMB4,のメモリ層420は、隣接するメモリブロックに含まれたXデコーダ層430に連結されてX軸アドレス情報を受信することができる

### [0138]

具体的には、第3メモリブロックMB3′に含まれた各メモリ層420は、第3メモリブロックMB3′に含まれたXデコーダ層430と、第3連結ライン435′を介して連結され、第4メモリブロックMB4′に含まれた各メモリ層420は、第3メモリブロックMB3′に含まれたXデコーダ層430と、第4連結ライン437′を介して連結されうる。

# [0139]

図17には図示されていないが、第2基本積層構造85で、第7メモリブロックMB7 ′及び第9メモリブロックMB9′に含まれたメモリ層420は、それぞれ第7メモリブ ロックMB7′及び第9メモリブロックMB9′の背面に配されたメモリブロック(図示 せず)に含まれたYデコーダ層から、Y軸アドレス情報を受信することができる。

# [0140]

本実施形態で、各メモリブロックで、複数のメモリグループ間におけるメデコーダ層と Yデコーダ層は、互いに交互に介在され、複数のメモリブロックの同一レベルには、メデ コーダ層とYデコーダ層とが交互に配されうる。これにより、各メモリブロックのメデコー ダ層は、それと隣接したメモリブロックで、同一レベルに位置するYデコーダ層によっ て取り囲まれるように配されうる。同様に、各メモリブロックのYデコーダ層は、それと 隣接したメモリブロックで、同一レベルに位置するXデコーダ層によって取り囲まれるよ うに配されうる。従って、基板410上の同一レベルには、メモリブロックを横切ってX デコーダ層とYデコーダ層とが交互に配されうる。

# [0141]

本実施形態によれば、第1基本積層構造80または第2基本積層構造85で、各メモリブロックに含まれたメモリ層420は、当該メモリブロック内のデコーダ層及び隣接したメモリブロックで、同一レベルに位置するデコーダ層に連結されうる。従って、連結ラインの長さを短く具現できるので、信号の干渉を減らすことができ、連結効率を向上させる

20

30

40

50

ことができる。

#### [0142]

図18は、本発明の一実施形態による積層メモリ素子で、メモリ層とXデコーダアレイとの物理的な連結を示す概略的な断面図である。図1ないし図6の実施形態による積層メモリ素子は、図18に図示されているように、物理的に具現されうる。

### [0143]

図18を参照すれば、複数のメモリセルMCが複数層、例えば、3層に配列されうる。例えば、各メモリセルMCは、可変抵抗体R及びダイオードDを含むことができる。可変抵抗体Rは、印加される電圧によって高抵抗状態と低抵抗状態とを有することができ、従って、データ記録媒体として利用されうる。各層のメモリセルMCは、アレイ構造に配されうる。

[0144]

ワードラインWLは、当該層のメモリセルMCと結合するように、一方向に伸張されうる。従って、他層のメモリセルMCは、他のワードラインWLに結合されうる。ビットラインBLは、メモリセルMCを挟んでワードラインWLと交差するように伸張されうる。本実施形態によれば、1つのメモリセルMCには、対応するワードラインWLとビットラインBLとがそれぞれ連結される。

[0145]

ワードラインW L は、 X デコーダアレイ X \_\_ D E C と結合されうる。 X デコーダアレイ X \_\_ D A は、メモリセル M C の積層数と同数の X デコーダ X \_\_ D E C を含むことができる。各 X デコーダ X \_\_ D E C は、デコーディング・トランジスタ T d を含むことができる。 X デコーダアレイ X \_\_ D A に含まれた X デコーダ X \_\_ D E C は、ワードラインW L と一対一で結合されうる。

[ 0 1 4 6 ]

図19は、本発明の他の実施形態による積層メモリ素子で、メモリ層とXデコーダアレイとの物理的な連結を示す概略的な断面図である。図8ないし図10、図13ないし図15の実施形態による積層メモリ素子は、図19に図示されているように、物理的に具現されうる。

[0147]

図19を参照すれば、メモリブロックMBn-1,MBn内のメモリセルMCは、複数層、例えば、3層に積層されうる。この実施形態は、図18の積層メモリ素子をメモリブロックの単位で拡張して一部変形したものであり、従って、重複する説明は省略する。

[0148]

ワードラインW L は、当該層のメモリセル M C と結合するように一方向に伸張されうる。ビットライン B L は、メモリセル M C を挟んでワードラインW L と交差するように伸張されうる。このとき、隣接するメモリブロック M B n - 1 , M B n に含まれたワードラインW L は一本に連結され、一本に連結されたワードラインW L は、 X デコーダアレイ X \_ D A に結合されうる。

[0149]

X デコーダアレイ X \_\_ D A は、 1 つの X デコーダ X \_\_ D E C を含むことができ、 1 つの X デコーダ X \_\_ D E C と、一本に連結されたワードライン W L の連結を介して、各メモリセル M C をデコーディングすることができる。従って、 X デコーダ X \_\_ D E C の具現が簡単であり、各メモリセル M C に対するデコーディング速度を大きく向上させることができる。

[0150]

図 2 0 は、本発明の他の実施形態による積層メモリ素子で、メモリ層と X デコーダアレイとの物理的な連結を示す概略的な断面図である。図 7 の実施形態による積層メモリ素子は、図 2 0 に図示されているように、物理的に具現されうる。

[0151]

図20を参照すれば、複数のメモリセルMCが複数層、例えば、4層に配列されうる。

20

30

40

50

この実施形態は、図18の積層メモリ素子の構成を一部変形したものであり、従って、重複する説明は省略する。

[0152]

ワードラインW L は、隣接する 2 層のメモリセルMCと共通して結合するように一方向に伸張されうる。例えば、 2 層と 3 層とに含まれたメモリセルMCは、 1 本のワードラインW L を共有できる。また、ビットラインB L は、メモリセルMCを挟んでワードラインW L と交差するように伸張されうる。例えば、 1 層と 2 層とに含まれたメモリセルMCは、ビットラインB L をそれぞれ共有でき、 3 層と 4 層とに含まれたメモリセルMCは、ビットラインB L をそれぞれ共有できる。本実施形態によれば、ワードラインW L 及びビットライン B L の共有によって、全体的に、ワードラインW L とビットライン B L との個数を減らすことができる。従って、工程コストを減らすことができ、デコーダが占める領域も減少させられる。

[ 0 1 5 3 ]

ワードラインW L は、 X デコーダアレイ X \_\_ D A と結合されうる。 X デコーダアレイ X \_\_ D A は、メモリセル M C の積層数よりも小さい数の X デコーダ X \_\_ D E C を含むことができる。 X デコーダ X \_\_ D E C は、ワードラインW L と結合されうる。この実施形態によれば、共有構造を利用し、 X デコーダ X \_\_ D E C の数を減らすことができる。

[0154]

図21は、本発明のさらに他の実施形態による積層メモリ素子で、メモリ層とXデコーダアレイとの物理的な連結を示す概略的な断面図である。図8、図11ないし図13、図16、図17の実施形態による積層メモリ素子は、図21に図示されているように、物理的に具現されうる。

[0155]

図 2 1 を参照すれば、メモリブロック M B n - 1 , M B n , M B n + 1 内のメモリセル M C は、複数層、例えば、 4 層に積層されうる。この実施形態は、図 2 0 の積層メモリをメモリブロックの単位で拡張して一部変形したものであり、従って、重複する説明は省略する。

[0156]

ワードラインWLe,WLoは、隣接する各2層のメモリセルMCと共通して結合するように交互に配されうる。例えば、第2層と第3層とのメモリセルMCは、その間のワードラインWLeに共通して結合されうる。一方、第1層と第4層とのメモリセルMCは、それに隣接したワードラインWLoに共通して結合されうる。ビットラインBLは、メモリセルMCを挟んでワードラインWLe,WLoと交差するように伸張されうる。

[ 0 1 5 7 ]

ワードラインWLe,WLoは、XデコーダアレイX\_DAと結合されうる。XデコーダアレイX\_DAは、XデコーダX\_DECを含むことができる。例えば、隣接したメモリブロックMBn・1,MBn内のワードラインWLoは、互いに連結されてXデコーダX\_DECに共通して結合されうる。他の隣接したメモリブロックMBn,MBn+1内のワードラインWLeは、互いに連結されてXデコーダX\_DECに共通して結合されうる。ここで、XデコーダアレイX\_DAは、同一レベルに位置すると図示されているが、XデコーダアレイX\_DAに含まれたXデコーダX\_DECは、互いに異なる層に位置することもでき、互いに異なるメモリブロックMBn・1,MBn,MBn+1に含まれもする。

[0158]

図22は、本発明の一実施形態によるメモリカードを示す概略図である。

[0159]

図22を参照すれば、メモリカード2200は、ハウジング2230内に、制御器22 10とメモリ部2220とを含むことができる。制御器2210とメモリ部2220は、電気的な信号を交換できる。例えば、制御器2210の命令によって、メモリ部2220 と制御器2210は、データを授受することができる。これによって、メモリカード22 0 0 は、メモリ部 2 2 2 0 にデータを保存し、またはメモリ部 2 2 2 0 からデータを外部 に出力できる。

### [0160]

例えば、メモリ部 2 2 2 0 は、図 1 ないし図 2 1 の積層メモリ素子の少なくとも一つを含むことができる。かようなメモリカード 2 2 0 0 は、多様な携帯用機器のデータ記録媒体として利用されうる。例えば、メモリカード 2 2 0 0 は、マルチメディアカード ( M M C : multi media card ) または S D メモリカードを含むことができる。

#### [0161]

図23は、本発明の一実施形態による電子システムを示すブロック図である。

### [0162]

図23を参照すれば、電子システム2300は、プロセッサ2310、入力/出力装置2330及びメモリ部2320を含むことができ、それらは、バス2340を利用して互いにデータ通信できる。プロセッサ2310は、プログラムを実行して電子システム2300を制御する役割を行える。入力/出力装置2330は、電子システム2300のデータを入力または出力するのに利用できる。電子システム2300は、入力/出力装置2330を利用し、外部装置、例えば、パソコン(PC)またはネットワークに連結され、外部装置と互いにデータを交換できる。メモリ部2320は、プロセッサ2310の動作のためのコード及びデータを保存することができる。例えば、メモリ部2320は、図1ないし図21の積層メモリ素子の少なくとも一つを含むことができる。

### [0163]

例えば、かような電子システム 2 3 0 0 は、メモリ部 2 3 2 0 を必要とする多様な電子制御装置を構成でき、例えば、モバイルホン (mobile phone)、 M P 3 プレーヤ、ナビゲーション (navigation)、フラッシュメモリドライブ (SSD: solid state drive)または家電製品 (household appliances) に利用されうる。

#### [0164]

発明の特定実施形態についての以上の説明は、例示及び説明を目的に提供された。従って、本発明は、前記実施形態に限定されるものではなく、本発明の技術的思想内で、当該分野で当業者によって、前記実施形態を組み合わせて実施するなど、さまざまな多くの修正及び変更が可能であることは明白である。

### 【符号の説明】

[0165]

- 1,2,3,4 積層メモリ素子

- 10,30,50,70,80 第1基本積層構造

- 20,40,55,75,85 第2基本積層構造

- 110,210,310,410 基板

- 131,132,231,232,330,430 Xデコーダ層

- 1311 第1Xデコーダ層

- 1312 第2Xデコーダ層

- 1 3 5 B ' 第 1 背面連結ライン

- 1 3 5 B " 第 2 背面連結ライン

- 1 3 5 F ' 第 1 前 面 連 結 ラ イ ン

- 135 F " 第2前面連結ライン

- 1 4 1 , 1 4 2 , 1 4 3 , 2 4 1 , 2 4 2 , 2 4 3 , 3 4 0 , 4 4 0 Yデコーダ層

- 1421 第17デコーダ層

- 1 4 2 2 第 2 Y デコーダ層

- 1 4 5 L ' 第 1 左 側 連 結 ラ イ ン

- 1 4 5 L " 第 2 左 側 連 結 ラ イ ン

- 1 4 5 R ' 第 1 右 側 連 結 ラ イ ン

- 1 4 5 R " 第 2 右側連結ライン

20

10

30

40

# 【図2】

# 【図3】

【図4】

【図8】

【図9】

【図10】

【図13】

【図14】

【図15】

【図18】

【図19】

# 【図20】

# 【図21】

【図22】

# 【図23】

【図1】

【図5】

【図6】

【図7】

### 【図11】

### 【図12】

### 【図16】

### 【図17】

# フロントページの続き

5F101 BE07 BH23

| (51) Int.CI.                     |            |              | FΙ              |              | テーマコード(参考) |  |  |  |

|----------------------------------|------------|--------------|-----------------|--------------|------------|--|--|--|

| H 0 1 L                          | 21/8242    | (2006.01)    | H 0 1 L 2       | 7/10 4 5 1   |            |  |  |  |

| H 0 1 L                          | 27/108     | (2006.01)    | H 0 1 L 2       | 7/10 6 0 1   |            |  |  |  |

| H 0 1 L                          | 29/788     | (2006.01)    | H 0 1 L 2       | 9/78 3 7 1   |            |  |  |  |

| H 0 1 L                          | 29/792     | (2006.01)    | H 0 1 L 2       | 7/10 4 4 7   |            |  |  |  |

| H 0 1 L                          | 27/00      | (2006.01)    | H 0 1 L 2       | 7/00 3 0 1 A |            |  |  |  |

|                                  |            |              |                 |              |            |  |  |  |

| (72)発明者                          | 安 承彦       |              |                 |              |            |  |  |  |

|                                  | 大韓民国京      | 畿道龍仁市器興      | 區農書洞山14-1       | 番地 三星綜合技術院内  |            |  |  |  |

| (72)発明者                          | 金 鎬正       |              |                 |              |            |  |  |  |

|                                  | 大韓民国京      | 畿道龍仁市器興      | 區農書洞山14-1       | 番地 三星綜合技術院内  |            |  |  |  |

| (72)発明者                          | 朴 哲佑       |              |                 |              |            |  |  |  |

|                                  | 大韓民国京      | 畿道龍仁市器興      | 區農書洞山14-1       | 番地 三星綜合技術院内  |            |  |  |  |

| (72)発明者                          | 姜 尚範       |              |                 |              |            |  |  |  |

|                                  | 大韓民国京      | 畿道龍仁市器興      | 區農書洞山14-1       | 番地 三星綜合技術院内  |            |  |  |  |

| (72)発明者                          | 崔 賢鎬       |              |                 |              |            |  |  |  |

| 大韓民国京畿道龍仁市器興區農書洞山14-1番地 三星綜合技術院内 |            |              |                 |              |            |  |  |  |

| Fターム(参                           | 考) 4M119 A | A11 GG10 HHC | 7               |              |            |  |  |  |

|                                  | 5F083 A    | DOO BSOO EPO | 0 FR00 FZ10 GA1 | 0 LA04 LA05  |            |  |  |  |