### (19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12) 特 許 公 報(B2)

FL

(11)特許番号

特許第6411279号 (P6411279)

(45) 発行日 平成30年10月24日(2018.10.24)

(24) 登録日 平成30年10月5日(2018.10.5)

| (51) 1111.01. | 1 1                           |           |                        |

|---------------|-------------------------------|-----------|------------------------|

| C23C 18/18    | (2006.01) C 2 3 C             | 18/18     |                        |

| C23C 18/32    | (2006.01) C 2 3 C             | 18/32     |                        |

| C23C 28/02    | (2006.01) C 2 3 C             | 28/02     |                        |

| C25D 5/30     | (2006.01) C 2 5 D             | 5/30      |                        |

| C25D 7/12     | (2006.01) C 2 5 D             | 7/12      |                        |

|               |                               |           | 請求項の数 3 (全 9 頁) 最終頁に続く |

| (21) 出願番号     | 特願2015-96756 (P2015-96756)    | (73) 特許権者 | 音 000219967            |

| (22) 出願日      | 平成27年5月11日 (2015.5.11)        |           | 東京エレクトロン株式会社           |

| (65) 公開番号     | 特開2016-211044 (P2016-211044A) |           | 東京都港区赤坂五丁目3番1号         |

| (43) 公開日      | 平成28年12月15日 (2016.12.15)      | (74) 代理人  | 100091982              |

| 審査請求日         | 平成29年8月9日(2017.8.9)           |           | 弁理士 永井 浩之              |

|               |                               | (74) 代理人  | 100117787              |

|               |                               |           | 弁理士 勝沼 宏仁              |

|               |                               | (74) 代理人  | 100106655              |

|               |                               |           | 弁理士 森 秀行               |

|               |                               | (72) 発明者  | 水谷信崇                   |

|               |                               |           | 東京都港区赤坂五丁目3番1号 赤坂Bi    |

|               |                               |           | z タワー 東京エレクトロン株式会社内    |

|               |                               | (72) 発明者  | 岩 下 光 秋                |

|               |                               |           | 東京都港区赤坂五丁目3番1号 赤坂Bi    |

|               |                               |           | z タワー 東京エレクトロン株式会社内    |

|               |                               |           | 最終頁に続く                 |

|               |                               | •         |                        |

(54) 【発明の名称】めつき処理方法および記憶媒体

## (57)【特許請求の範囲】

## 【請求項1】

表面に<u>凹部を有する基板であって、前記凹部の底面に、</u>アルミニウムまたはアルミニウム合金からなるA1配線層が露出している前記基板を準備する工程と、

その後、前記基板に対してジンケート処理を施し、前記 A 1 <u>配線</u>層の表面にジンケート 皮膜を形成する工程と、

その後、アルカリ性であってかつ錯化剤を含む無電解めっき液を用いて、前記A1<u>配線</u>層の前記表面に第1無電解めっき層を形成する第1無電解めっき工程と、

その後、前記凹部の少なくとも側面に触媒層を形成する工程と、

その後、前記凹部の前記底面および前記側面に、アルカリ性であってかつ錯化剤を含む 無電解めっき液を用いて、第2無電解めっき層を形成する第2無電解めっき工程と、 を備えためっき処理方法。

### 【請求項2】

前記第2無電解めっき工程の後に、前記凹部の内部に銅または銅合金からなるCuめっきを埋め込む工程をさらに備えた、請求項1記載のめっき処理方法。

### 【請求項3】

めっき処理システムの動作を制御するためのコンピュータにより実行されたときに、前記コンピュータが前記めっき処理システムを制御して請求項<u>1または2</u>記載のめっき処理方法を実行させるプログラムが記録された記憶媒体。

## 【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、例えば半導体装置のA1配線層等のA1層の表面上にCoめっきを形成する技術に関する。

### 【背景技術】

#### [0002]

LSI等の半導体装置のBEOLで用いられる配線材料の多くは銅(Cu)である。Cu配線層を形成するには、Cuが絶縁層中に拡散することを防止するためのバリア層の形成、Cuの電気めっきを円滑に行うためのバリア層上への無電解Cuめっきによるシード層の形成等が必要であり、コストがかさむ。このため、配線材料にCuほどの低電気抵抗が求められない部分については、低コストのアルミニウム(Al)配線材料が用いられている。

#### [0003]

A1配線層に接続されるCu配線層を形成する場合、Cu配線層の周囲のシリコン系材料からなる絶縁層にCuが拡散しないようにバリア層を形成する必要がある。

#### [0004]

Cu配線層をTSV等の深い穴内に埋め込む前に当該穴の内表面にバリア層を形成する方法として、PVD法等の成膜装置を用いる方法が知られている(特許文献1を参照)。深穴内表面にバリア層を形成する別の方法として、無電解めっき法も知られている。無電解めっき法により形成することができ、かつ、Cuに対する高いバリア性を有する実用材料の一つとして、コバルトまたはコバルト合金(以下、Co系材料とも呼ぶ)がある(特許文献2を参照)。

### [00005]

A1配線層に接続されるCu配線層のためのバリア層にCo系の無電解めっきを適用することを本発明者が検討したところ、以下の問題点が明らかとなった。すなわち、Co系無電解めっき液はアルミニウムを侵しやすいアルカリ性であり、かつ、アルミニウムに対する攻撃性が非常に高い錯化材を含んでいる。このため、アルミニウム配線層上に直接Co系の無電解めっきを施そうとしても、めっきの成長よりも下地のアルミニウムの溶解が優先的に生じてしまい、Co系めっき層を形成することは事実上不可能である。

## 【先行技術文献】

#### 【特許文献】

## [0006]

【特許文献1】特許第4246706号公報

【特許文献 2 】特開 2 0 1 3 - 1 9 4 3 0 6 号公報

## 【発明の概要】

【発明が解決しようとする課題】

## [0007]

本発明は、アルカリ性であってかつ錯化材を含む無電解めっき液を用いてアルミニウムまたはその合金からなるA1層の上に無電解めっきを施す技術を提供することを目的としている。

## 【課題を解決するための手段】

#### [0008]

本発明の一実施形態によれば、表面にアルミニウムまたはその合金からなるアルミニウム層が露出している基板を準備する工程と、その後、前記基板に対してジンケート処理を施し、前記アルミニウム層の表面にジンケート皮膜を形成する工程と、その後、アルカリ性であってかつ錯化剤を含む無電解めっき液を用いて、前記アルミニウム層の前記表面に第1無電解めっき層を形成する工程と、を備えためっき処理方法が提供される。

#### [0009]

本発明の他の実施形態によれば、めっき処理システムの動作を制御するためのコンピュータにより実行されたときに、前記コンピュータが前記めっき処理システムを制御して上

10

20

30

40

記のめっき処理方法を実行させるプログラムが記録された記憶媒体。

#### 【発明の効果】

#### [0010]

本発明によれば、ジンケート皮膜により無電解めっき皮膜の成長が速やかに進行するので、また、無電解めっき液によりアルミニウム層がダメージを受けたとしても、アルミニウム層の上に問題なく無電解めっき層を形成することができる。

【図面の簡単な説明】

### [0011]

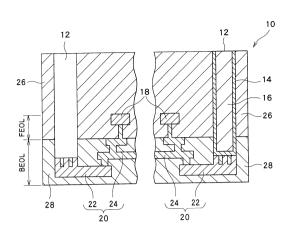

【図1】本発明の一実施形態に係るめっき処理方法によって処理される半導体装置の一例の構成を簡略化して示した断面図である。

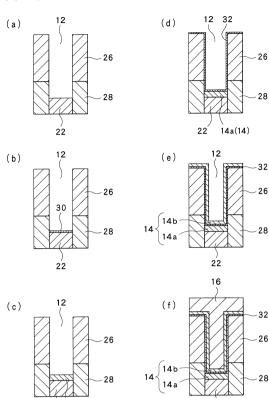

【図2】上記めっき処理方法の工程について説明するTSV近傍の概略断面図である。

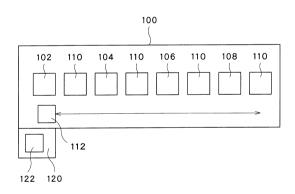

【図3】上記めっき処理方法を実施するためのめっき処理システムの構成を概略的に示す図である。

【発明を実施するための形態】

#### [0012]

以下に図面を参照して本発明の好適な実施形態について説明する。

#### [0013]

以下に説明する実施形態は、基板10に形成された凹部であるTSV12(Through Si Licon Via)内に無電解めっき法により形成されたコバルトまたはコバルト合金からなる Coバリア層14と、めっき法により形成された銅または銅合金からなるCu配線層(埋め込み配線)16とを形成する方法に関する。

[0014]

図1において、左半分はTSV12内にCoバリア層14およびCu配線層16を形成する前の状態を示しており、右半分はCoバリア層14およびCu配線層16を形成した後の状態を示している。

[0015]

図 1 は、 3 次元高集積化( 3 D I )技術が適用された半導体メモリ装置を構成する複数層のチップのうちの一つを大幅に単純化して示したものである。このチップは、 F E O L (front end of line) で形成されたトランジスタなどの回路素子 1 8 と、 B E O L (back end of line) により形成された配線層 2 0 を有する。

[0016]

配線層 2 0 には、アルミニウムまたはアルミニウム合金からなる(通常は、数%程度の C u を含有するアルミニウム合金である)A 1 配線層 2 2 と銅または銅合金からなる C u 配線層 2 4 とが含まれる。実際には C u 配線層 2 4 の下層としてバリア層、シード層等が 存在するが、図面の簡略化のため図 1 には表示していない。本明細書冒頭の背景技術の項でも述べたように、A 1 配線層 2 2 は比較的低コストで形成することができるので、配線容積が十分にある等の理由により、低電気抵抗であるが高価な銅を使用する必要の無い部位に用いられている。

[0017]

図1左半分に示したデバイス構造を製造する方法は、当業者に良く知られており、本明細書ではその説明を省略する。以下、本明細書においては、TSV12内へのCoバリア層14およびCu配線層16に関連する技術的事項についてのみ説明する。

[0018]

TSV12は、基板10を構成する基材としてのシリコン基板(シリコンウエハ)26 およびシリコン基板26の下面上に形成されたTEOS層28の中を通って延びている。シリコン基板26およびTEOS層28はともにシリコンを含有する絶縁性材料(誘電性材料)からなる。TEOS層28に代えて、SiO2層またはSiOC層が設けられていてもよい。

### [0019]

このようなシリコン含有絶縁性材料中には銅が拡散しやすいので、TSV12内にСи

20

10

30

50

配線層16を埋め込む場合には、銅拡散防止用のバリア層を形成する必要がある。先に背景技術の項でも述べたように、高アスペクト比の凹部であるTSV12内に確実に形成することができ、かつ、銅拡散防止機能を有するバリア層として、無電解めっき法により形成されたコバルトまたはコバルト合金からなるCoバリア層14を用いる方法が既に提案されている(特許文献2(特開2013-194306号公報)を参照)。

#### [0020]

TSV12の底面には、A1配線層22が露出している。先に背景技術の項でも述べたように、A1配線層22の上に、無電解めっき法によりCoバリア層14を形成することは困難である。本実施形態は、その問題を解決できるめっき処理方法に関する。

#### [0021]

以下に図2を参照して、TSV12内にCoバリア層14およびCu配線層16を形成する一連の工程について説明する。なお、図2には、TSV12近傍の構造が図1よりもさらに簡略化されて示されている。つまり、図2(a)は、図1の左側のTSV12周囲をさらに簡略化して示したものである。

### [0022]

#### 「酸化皮膜除去工程 ]

まず、アルカリ性洗浄液(NaOHを主成分とするもの)を基板10に供給して、TSV12内に露出しているA1配線層22の表面にある酸化皮膜を除去する。その後、純水(DIW)によるリンス処理を行い、アルカリ性洗浄液および反応副生成物を基板10から除去する。

#### [0023]

### 「スマット除去工程]

次に、基板10にスマット除去用の酸性薬液を供給して、酸化皮膜除去工程によりA1 配線層22の表面に生じたスマット(A1(OH)<sub>3</sub>)を除去する。その後、純水による リンス処理を行い、酸性薬液および反応副生成物を基板10から除去する。

### [0024]

なお、半導体装置のA1配線層22(埋め込み配線層)には、通常、数%程度のCuを含有したアルミニウム合金が用いられる。このため、スマットにはSi、Mg等の不純物が含まれないため、ここで用いられるスマット除去用の酸性薬液は、(一般的なスマット除去用の薬液に通常含まれている)フッ酸を含んでいる必要はなく、硝酸を水で希釈したものでよい。このことは、シリコン基板26およびTEOS層28へのダメージが低減されるという意味で有利である。スマット除去工程は、例えば、常温の濃度30%の硝酸(HNO3(aq))に30秒程度の間基板10の表面が覆われている状態を維持することにより実施することができる。

## [0025]

### 「ジンケート処理工程 ]

次に、基板にジンケート処理を施し、A1配線層22の表面に亜鉛(Zn)皮膜(ジンケート皮膜)30(図2(b)参照)を形成する。ここでは、ダブルジンケート処理を行うものとする。

ダブルジンケート処理は、

ジンケート処理液を基板10に供給して、A1配線層22の表面にZn粒子を析出させる第1ジンケート工程と、

その後、純水によりジンケート液および反応副生成物を基板 1 0 から除去する第 1 リンス工程と、

その後、硝酸(スマット除去工程で用いたものと同じものでよい)を基板に供給して、 第1ジンケート工程で析出せたZn粒子を一旦剥離させるZnストリップ工程と、

その後、純水により硝酸および反応副生成物を基板10から除去する第2リンス工程と

ジンケート処理液を基板10に供給して、A1配線層22の表面にZn粒子を析出させる第2ジンケート工程と、

10

20

30

40

その後、純水によりジンケート液および反応副生成物を基板 1 0 から除去する第 3 リンス工程と、

から構成される。

#### [0026]

ダブルジンケート処理を行うことにより、シングルジンケート処理を行う場合(第1リンス工程まででジンケート処理を終了する場合)と比較して、より微細なZn粒子をより緻密に析出させることができる。高品質なZn皮膜を形成するにはダブルジンケート処理を行うことが好ましいが、シングルジンケート処理を行ってもかまわない。

### [0027]

ジンケート処理はアルミニウムまたはアルミニウム合金からなる下地の上にニッケルまたはニッケル合金からなるNiめっき(電解、無電解を問わない)を形成する際に、広く用いられているものである。発明者の実験により、Niめっきの前処理としてのジンケート処理と実質的に同じ条件で酸化物除去工程からジンケート処理工程までの工程(処理条件は公知である)を行うことにより、アルミニウムまたはアルミニウム合金からなる下地の上に、Co系無電解めっきを良好な状態で形成することができることが確認されている

### [0028]

「Coバリア層形成工程(1回目)]

## [0029]

このとき、A1配線層22の表面を覆うZn皮膜30がコバルト(またはコバルト合金)に置換され、A1配線層22の表面上にコバルト(またはコバルト合金)が析出する。このとき、アルカリ性でありかつアルミニウムへの攻撃性が高い錯化剤を含むCo系無電解めっき液によりA1配線層22の表面が若干のダメージは受けるものの、Coバリア層14aが十分に高速度で析出してA1配線層22の表面を覆うようになるため、A1配線層22の表面に問題無くCoバリア層14を形成することができる。Coバリア層14aを形成した後、その後、純水によるリンス処理を行い、めっき液および反応副生成物等の残渣を基板10から除去する。

## [0030]

Coバリア層形成工程においては、A1配線層22の表面にのみジンケート皮膜(Zn粒子)が形成され、かつ、シリコン基板26およびTEOS層28の表面にはジンケート皮膜が形成されていない状態で無電解めっきが行われるため、TSV12内においてCoバリア層14aはA1配線層22の表面のみから成長する。シリコン基板26およびTEOS層28の表面には、Coバリア層は析出しない。

### [0031]

C o バリア層形成工程(1回目)が終了すると、C o 系無電解めっき液に侵されやすい A 1 配線層 2 2 の表面はもはや T S V 1 2 内に露出していないので、その後の処理(下記の触媒層形成工程以降の工程)は、公知の通常の手順で行うことができる。

#### [0032]

### 「触媒層形成工程]

次に、TSV12内に触媒層32(図2(d)参照)を形成する。触媒層は、例えば、基板10にシランカップリング剤またはチタンカップリング剤等の適当なカップリング剤を供給することによりSAM(自己組織化単分子膜)を形成する工程と、その後、基板10に塩化パラジウム液等の触媒イオン含有液を供給する工程と、その後、DMAB(ジメチルアミンボラン)等の還元剤を基板に供給する工程とを順次実行することにより行うことができる。この触媒層形成工程により、TSV12の内表面(TSV12内に露出しているシリコン基板26およびTEOS層28の表面を含む)を含む基板10の表面全体に

10

20

30

40

10

20

30

40

50

触媒層 3 2 が形成される。触媒層を形成した後、純水によるリンス処理を行い、最後に使用した薬液(DMAB)および反応副生成物を基板 1 0 から除去する。触媒層 3 2 の形成方法は、上記のものに限定されるものではなく、公知の任意の方法を採用することができる。触媒層 3 2 に含まれる触媒金属は、パラジウムに限定されるものではなく、無電解めっきの還元析出反応の触媒として機能しうる他の金属、例えば金(Au)、白金(Pt)、ルテニウム(Ru)等であってもよい。

#### [0033]

## [ С o バリア層形成工程(2回目)]

次に、Co系無電解めっき液を基板10に供給して、無電解めっき法により、TSV12内にCoバリア層14のうちの別の一部(14b)(図2(e)参照)を形成する。すなわち、TSV12内に露出しているシリコン基板26およびTEOS層28の表面にCoバリア層14bが析出する。なお、このときA1配線層22の表面に既に形成されているCoバリア層14a上にも、さらにCoバリア層14bが析出する。また、基板10の表面全体に触媒層が形成されているため、基板10の表面全体にCoバリア層14bが形成される。Coバリア層14bを形成した後、純水(DIW)によるリンス処理を行い、めっき液および反応副生成物等の残渣を基板10から除去する。

### [0034]

## [ C u 配線層形成工程]

次に、Cu系無電解めっき液を基板10に供給して、Coバリア層14上にシード層としての銅または銅合金(以下、Cuと記す)(図2(f)参照)を析出させる。次いで、電解めっきにより、TSV12内をCuめっきで埋め込んでCu配線層16を形成する。基板10の全表面にCoバリア層14が形成されているため、基板10の全表面にCu配線層16が形成される。なお、穴または凹部(TSV12)のサイズ次第では無電解めっきのみによりCu配線層16を形成してもよい。Cu配線層16を形成した後、純水によるリンス処理を行い、めっき液および反応副生成物等の残渣を基板10から除去する。

### [0035]

その後、CMP(化学機械研磨)により、基板10の表面(TSV12の外側)にある不要なCuめっきを除去する。以上により、一連の工程が終了し、図1の右側に示した状態となる。

## [0036]

上記実施形態によれば、ジンケート処理を行うことにより、アルミニウムまたはその合金の表面に形成することが困難であるコバルトまたはその合金からなるめっき皮膜を、無電解めっき法により問題無く形成することができる。

## [0037]

このため、半導体装置の絶縁層内に形成された高アスペクト比の凹部の内表面に露出した A 1 配線層を、 C o バリア層 1 4 を介して、凹部に埋め込まれた C u 配線層 1 6 に電気的に良好に接続することができる。

### [0038]

上記の酸化皮膜除去工程から C o バリア層形成工程(1回目)までの工程を(つまり、A 1 配線層 2 2 が C o バリア層 1 4 a に完全に覆われるまでの工程)を実行するためのめっき処理システムの構成例について簡単に説明する。第 1 の例として、めっき処理システムはバッチ式液処理槽を組み合わせて構成することができる。この場合、図 3 に概略的に示すように、めっき処理システム 1 0 0 は、酸化皮膜除去工程のためのアルカリ洗浄槽 1 0 2、スマット除去工程および Z n ストリップ工程のための酸洗浄槽 1 0 4、第 1 および第 2 ジンケート工程を行うためのジンケート処理槽 1 0 6、C o バリア層形成工程(1回目)のための C o 無電解めっき槽 1 0 8、上記各薬液処理工程の後のリンス工程のための複数のリンス処理槽 1 1 0 を備える。

## [0039]

各槽は、半導体装置製造、特に薬液洗浄、ウエットエッチング等の分野で広く用いられているバッチ式液処理槽と同じ構成を採用することができる。すなわち、各槽には、複数

枚の基板10(半導体ウエハ)を直立姿勢で水平方向に間隔を空けて保持するウエハボートなどと呼ばれる基板保持具(図示せず)が設けられ、基板保持具におけるウエハの配列状態を維持したまま基板搬送機112のアームが各槽の基板保持具間で基板10の搬送および受け渡しを行う。基板保持具により保持された状態で各槽に貯留された処理液(薬液、リンス液、めっき液等)に予め定められた時間だけ順次浸漬されることにより、基板10に対して上述した各工程が実施される。

#### [0040]

上述しためっき処理システム100の全体の動作は、コンピュータからなる制御装置120により制御される。制御装置120は、記憶媒体122に記録された各種のプログラムを読み出して実行することにより、めっき処理システム100の各部の動作を制御して、前述した各工程を実行させる。記憶媒体122は、上述した一連の工程を実行するために必要なプロセスレシピおよび制御プログラム等の各種のプログラムを格納している。記憶媒体122としては、コンピュータで読み取り可能なROMやRAM等のメモリ装置、ハードディスク、CD-ROM、DVD-ROM、フレキシブルディスクなどのディスク記憶媒体など任意のものを使用することができる。

#### [0041]

上記の酸化皮膜除去工程から Coバリア層形成工程(1回目)までの一連の処理を1つまたは2つ以上の枚葉式の液処理ユニット(図示せず)を用いて行ってもよい。枚葉式の液処理ユニットは、基板10を水平姿勢で保持して回転させるスピンチャックと、スピンチャックにより保持されて回転する基板10に上述した薬液、リンス液、めっき液等の処理液を供給するノズルを備えて構成することができる。上記の酸化皮膜除去工程からCoバリア層形成工程(1回目)までの一連の処理を一つの液処理ユニットにより行ってもよく、複数の液処理ユニットで分担して行わせてもよい。

#### 【符号の説明】

## [0042]

- 10 基板

- 12 凹部(TSV)

- 2 2 A 1 層 ( A 1 配線層 )

- 30 ジンケート皮膜

- 14a(14) 第1無電解めっき層(Coバリア層)

- 14b(14) 第2無電解めっき層(Coバリア層)

- 16 Cuめっき(Cu配線層)

- 3 2 触媒層

- 100 めっき処理システム

- 120 制御装置

- 1 2 2 記憶媒体

10

20

【図1】

【図2】

14a(14)

【図3】

## フロントページの続き

(51) Int.CI. F I

H 0 1 L

21/288

(2006.01)

H 0 1 L

21/288

E

H 0 1 L

21/3205

(2006.01)

H 0 1 L

21/88

J

H 0 1 L 21/768 (2006.01) H 0 1 L 23/522 (2006.01)

(72)発明者 田 中 崇

東京都港区赤坂五丁目3番1号 赤坂Bizタワー 東京エレクトロン株式会社内

#### 審査官 菅原 愛

(56)参考文献 特表昭60-502057(JP,A)

特開昭64-039041(JP,A)

特開平09-118985(JP,A)

特表2007-523263(JP,A)

特開2013-211427(JP,A)

米国特許出願公開第2006/0246217(US,A1)

## (58)調査した分野(Int.CI., DB名)

C 2 3 C 1 8 / 0 0 - 2 0 / 0 8

C25D 5/00- 7/12

H01L21/28-21/288

H01L21/44-21/445

H01L21/88-21/90

H01L29/40-29/64