### (19)**日本国特許庁(JP)**

# (12)特許公報(B2)

(11)特許番号 特許第7374795号 (P7374795)

(45)発行日 令和5年11月7日(2023.11.7)

(24)登録日 令和5年10月27日(2023.10.27)

| (51)国際特許分                          | 類                                     | FΙ       |           |                     |   |

|------------------------------------|---------------------------------------|----------|-----------|---------------------|---|

| H 0 1 L                            | 29/78 (2006.01)                       | H 0 1 L  | 29/78     | 6 5 2 K             |   |

| H 0 1 L                            | 29/12 (2006.01)                       | H 0 1 L  | 29/78     | 6 5 3 C             |   |

| H 0 1 L                            | 29/06 (2006.01)                       | H 0 1 L  | 29/78     | 6 5 2 T             |   |

| H 0 1 L                            | 29/861 (2006.01)                      | H 0 1 L  | 29/78     | 6 5 2 M             |   |

| H 0 1 L                            | 29/868 (2006.01)                      | H 0 1 L  | 29/06     | 3 0 1 F             |   |

|                                    |                                       |          | 請求項       | 頁の数 15 (全22頁) 最終頁に続 | < |

| (21)出願番号 特願2020-18037(P2020-18037) |                                       | (73)特許権者 | 000003078 |                     |   |

| (22)出願日                            | 令和2年2月5日(2020.2                       | .5)      |           | 株式会社東芝              |   |

| (65)公開番号                           | 65)公開番号    特開2021-125559(P2021-125559 |          |           | 東京都港区芝浦一丁目1番1号      |   |

|                                    | A)                                    |          | (73)特許権者  | 317011920           |   |

| (43)公開日                            | 令和3年8月30日(2021.                       | 8.30)    |           | 東芝デバイス&ストレージ株式会社    |   |

| 審査請求日                              | 令和4年3月14日(2022.                       | 3.14)    |           | 東京都港区芝浦一丁目1番1号      |   |

|                                    |                                       |          | (74)代理人   | 110004026           |   |

|                                    |                                       |          |           | 弁理士法人 i X           |   |

|                                    |                                       |          | (72)発明者   | 小林 勇介               |   |

|                                    |                                       |          |           | 東京都港区芝浦一丁目1番1号 株式会  |   |

|                                    |                                       |          |           | 社東芝内                |   |

|                                    |                                       |          | (72)発明者   | 雁木 比呂               |   |

|                                    |                                       |          |           | 東京都港区芝浦一丁目1番1号 株式会  |   |

|                                    |                                       |          |           | 社東芝内                |   |

|                                    |                                       |          | (72)発明者   | 井口 智明               |   |

|                                    |                                       |          |           | 最終頁に続っ              | < |

### (54)【発明の名称】 半導体装置

### (57)【特許請求の範囲】

#### 【請求項1】

第1電極と、

第2電極であって、前記第1電極から前記第2電極への方向は、第1方向に沿う、前記 第2電極と、

第1部分領域、第2部分領域及び第3部分領域を含む第1導電形の第1半導体領域であって、前記第2部分領域から前記第1部分領域への第2方向は、前記第1方向と交差した、前記第1半導体領域と、

前記第1導電形の第2半導体領域であって、前記第3部分領域は、前記第1方向において、前記第2部分領域と前記第2半導体領域との間にある、前記第2半導体領域と、

前記第3部分領域と前記第2半導体領域との間に設けられた第2導電形の第3半導体領域と、

第3電極であって、前記第3半導体領域から前記第3電極への方向は、前記第2方向に 沿う、前記第3電極と、

第1部材であって、前記第1部分領域から前記第1部材への方向は、前記第1方向に沿い、前記第1部材は、前記第1方向において前記第1部分領域と前記第3電極との間にあり、前記第3部分領域から前記第1部材への方向は、前記第2方向に沿う、前記第1部材と、

第1 絶縁領域及び第2 絶縁領域を含む第1 絶縁部材であって、前記第1 絶縁領域は、前記第2 方向において前記第3 部分領域と前記第1 部材との間にあり、前記第2 絶縁領域は

、前記第2方向において、前記第3半導体領域と前記第3電極との間にある、前記第1絶 縁部材と、

#### を備え、

前記第1部材は、前記第1部分領域と電気的に接続され、

前記第1部材は、前記第2電極と電気的に接続された、または、前記第2電極と電気的 に接続されることが可能であり、

前記第1部材は、第1材料、第2材料、第3材料、第4材料、第5材料及び第6材料よ りなる群から選択された少なくとも1つを含み、

前記第1材料は、Si、N及びOを含み、

前記第2材料は、Si-Nの結合、N-Oの結合、及び、N-Nの結合を含み、

前記第3材料は、Si-Nの結合、N-Hの結合、及び、N-Nの結合を含み、

前記第4材料は、Siと、Cと、第1元素と、を含み、前記第1元素は、B及びNより なる群から選択された少なくとも1つを含み、

前記第5材料は、Siと、Oと、第2元素と、を含み、前記第2元素は、Fe、Au、 Ni、Ta、W及びTiよりなる群から選択された少なくとも1つを含み、

前記第6材料は、第3元素及び第4元素を含み、前記第3元素は、In、A1及びGa よりなる群から選択された少なくとも1つを含み、前記第4元素は、P、As、B、Fe 、Au、Ni、Ti、Ta、W及びTiよりなる群から選択された少なくとも1つを含む 、半導体装置。

#### 【請求項2】

第1対向部材をさらに備え、

前記第3部分領域は、前記第2方向において前記第1対向部材と前記第1部材との間に あり、

前記第1絶縁部材は、第1対向絶縁領域をさらに含み、前記第1対向絶縁領域は、前記 第2方向において、前記第1対向部材と前記第3部分領域との間にあり、

前記第1半導体領域は、第1対向部分領域をさらに含み、前記第2部分領域は、前記第 2方向において前記第1対向部分領域と前記第1部分領域との間にあり、

前記第1対向部分領域から前記第1対向部材への方向は、前記第1方向に沿い、

前記第1対向部材は、前記第1対向部分領域と電気的に接続され、

前記第1対向部材は、前記第1材料、前記第2材料、前記第3材料、前記第4材料、前 記第5材料及び前記第6材料よりなる群から選択された少なくとも1つを含む、請求項1 記載の半導体装置。

### 【請求項3】

前記第1絶縁領域の前記第2方向に沿う長さは、20nm以上250nm以下である、 請求項1または2に記載の半導体装置。

### 【請求項4】

前記第1部材と前記第2電極とを電気的に接続する第1導電部をさらに備えた、請求項 1~<u>3</u>のいずれか1つに記載の半導体装置。

#### 【請求項5】

前記第1部材と電気的に接続された端子をさらに備えた、請求項1~<u>3</u>のいずれか1つ に記載の半導体装置。

#### 【請求項6】

前記第1部材は、第1端と、第2端と、を含み、

前記第2端は、前記第1方向において前記第1部分領域と前記第1端との間にあり、

前記第1端の前記第1方向における位置は、前記第3部分領域と前記第3半導体領域と の境界の前記第1方向における位置と、前記第2端の前記第1方向における位置との間に ある、請求項1~5のいずれか1つに記載の半導体装置。

### 【請求項7】

前記第1部材の少なくとも一部は、前記第1方向において、前記第1部分領域と、前記 第3電極の少なくとも一部と、の間にあり、

10

20

30

前記第1 絶縁部材は、第3 絶縁領域を含み、

前記第3絶縁領域は、前記第1部材と前記第3電極との間にある、請求項1~6のいず れか1つに記載の半導体装置。

#### 【請求項8】

前記第1部分領域と前記第1部材との間に設けられた前記第1導電形の第6半導体領域 をさらに備え、

前記第6半導体領域は、前記第1部分領域及び前記第1部材と電気的に接続され、

前記第6半導体領域における前記第1導電形の不純物の濃度は、前記第1半導体領域に おける前記第1導電形の不純物の濃度よりも高い、請求項7記載の半導体装置。

#### 【請求項9】

前記第3部分領域における前記第1導電形の不純物の濃度は、前記第1部分領域におけ る前記第1導電形の不純物の濃度よりも低い、請求項1記載の半導体装置。

前記第3部分領域と前記第3半導体領域との間に設けられた前記第1導電形の第7半導 体領域をさらに備え、

前記第7半導体領域における前記第1導電形の不純物の濃度は、前記第3部分領域にお ける前記第1導電形の不純物の濃度よりも低い、請求項7~9のいずれか1つに記載の半 導体装置。

### 【請求項11】

前記第1半導体領域は、第4部分領域をさらに含み、

前記第2部分領域は、前記第2方向において、前記第4部分領域と前記第1部分領域と の間にあり、

前記第3電極は、前記第1方向において、前記第4部分領域と前記第2電極との間にあ 1)、

前記第1絶縁部材は、第3絶縁領域をさらに含み、

前記第3絶縁領域は、前記第1方向において前記第4部分領域と前記第3電極との間に ある、請求項1~5のいずれか1つに記載の半導体装置。

#### 【請求項12】

前記第2電極と電気的に接続された第2導電部をさら<u>に備</u>え、

前記第2導電部は、前記第1方向において、前記第4部分領域と前記第3電極との間に あり、

前記第1絶縁部材は、第4絶縁領域をさらに含み、

前記第4絶縁領域は、前記第1方向において前記第4部分領域と前記第2導電部との間 にあり、

前記第3絶縁領域は、前記第1方向において前記第2導電部と前記第3電極との間にあ る、請求項11記載の半導体装置。

#### 【請求項13】

前記第2電極と電気的に接続された第4半導体領域をさらに備え、

前記第4半導体領域は前記第2導電形であり、

前記第4半導体領域における前記第2導電形の不純物の濃度は、前記第3半導体領域に おける前記第2導電形の前記不純物の濃度よりも高い、請求項1~1<u>2</u>のいずれか1つに 記載の半導体装置。

### 【請求項14】

前記第1電極と前記第1半導体領域との間に設けられた第5半導体領域をさらに備え、 前記第5半導体領域は前記第1導電形であり、

前記第5半導体領域における前記第1導電形の不純物の濃度は、前記第1半導体領域に おける前記第1導電形の前記不純物の濃度よりも高い、請求項1~13のいずれか1つに 記載の半導体装置。

#### 【請求項15】

前記第2半導体領域における前記第1導電形の不純物の濃度は、前記第1半導体領域に

10

20

30

おける前記第1導電形の前記不純物の前記濃度よりも高い、請求項1<u>4</u>記載の半導体装置。 【発明の詳細な説明】

【技術分野】

[00001]

本発明の実施形態は、半導体装置に関する。

【背景技術】

[0002]

例えば、トランジスタなどの半導体装置において、特性の向上が望まれる。

【先行技術文献】

【特許文献】

[0003]

【文献】特許第6400545号公報

【発明の概要】

【発明が解決しようとする課題】

[0004]

本発明の実施形態は、特性を向上できる半導体装置を提供する。

【課題を解決するための手段】

[0005]

本発明の実施形態によれば、半導体装置は、第1電極、第2電極、第3電極、第1半導 体領域、第2半導体領域、第3半導体領域、第1部材及び第1絶縁部材を含む。前記第1 電極から前記第2電極への方向は、第1方向に沿う。前記第1半導体領域は、第1部分領 域、第2部分領域及び第3部分領域を含み、第1導電形である。前記第2部分領域から前 記第1部分領域への第2方向は、前記第1方向と交差する。前記第2半導体領域は、前記 第1導電形である。前記第3部分領域は、前記第1方向において、前記第2部分領域と前 記第2半導体領域との間にある。前記第3半導体領域は、前記第3部分領域と前記第2半 導体領域との間に設けられ、第2導電形である。前記第3半導体領域から前記第3電極へ の方向は、前記第2方向に沿う。前記第1部分領域から前記第1部材への方向は、前記第 1 方向に沿う。前記第 3 部分領域から前記第 1 部材への方向は、前記第 2 方向に沿う。前 記第1絶縁部材は、第1絶縁領域及び第2絶縁領域を含む。前記第1絶縁領域は、前記第 2 方向において前記第 3 部分領域と前記第 1 部材との間にある。前記第 2 絶縁領域は、前 記第2方向において、前記第3半導体領域と前記第3電極との間にある。前記第1部材は 、前記第1部分領域と電気的に接続される。前記第1部材は、前記第2電極と電気的に接 続された、または、前記第2電極と電気的に接続されることが可能である。前記第1部材 の抵抗率は、前記第1部分領域の抵抗率よりも高く、前記第1絶縁部材の抵抗率よりも低 L1.

【図面の簡単な説明】

[0006]

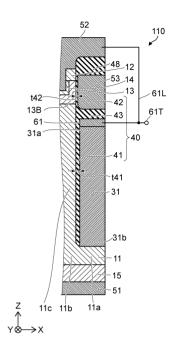

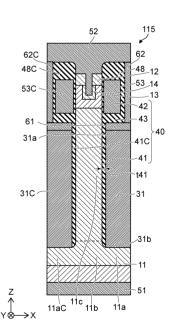

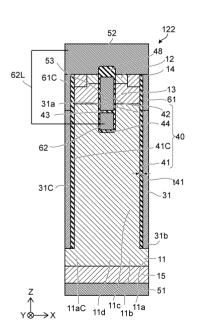

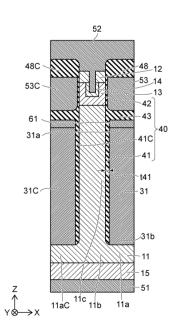

【図1】図1は、第1実施形態に係る半導体装置を例示する模式的断面図である。

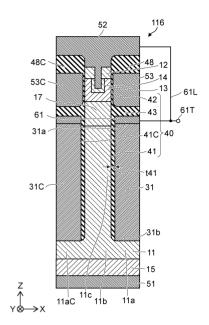

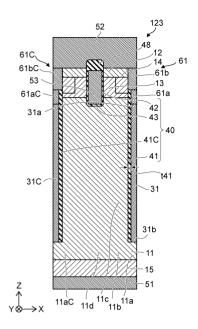

【図2】図2は、第1実施形態に係る半導体装置を例示する模式的断面図である。

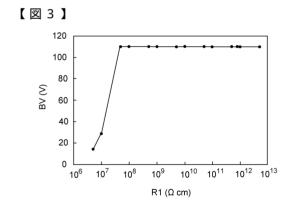

【図3】図3は、半導体装置の特性を例示するグラフ図である。

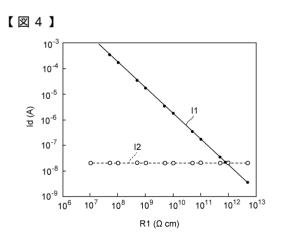

【図4】図4は、半導体装置の特性を例示するグラフ図である。

【図5】図5は、半導体装置の特性を例示するグラフ図である。

【図6】図6は、半導体装置の特性を例示するグラフ図である。

【図7】図7は、半導体装置の特性を例示するグラフ図である。

【図8】図8は、半導体装置の特性を例示するグラフ図である。

【図9】図9は、半導体装置の特性を例示するグラフ図である。

【図10】図10は、半導体装置の特性を例示するグラフ図である。

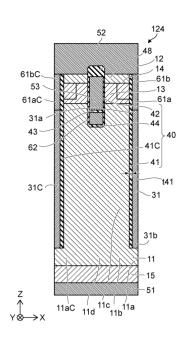

【図11】図11は、第1実施形態に係る半導体装置を例示する模式的断面図である。

【図12】図12は、第1実施形態に係る半導体装置を例示する模式的断面図である。

【図13】図13は、第1実施形態に係る半導体装置を例示する模式的断面図である。

10

20

30

40

- 【図14】図14は、第1実施形態に係る半導体装置を例示する模式的断面図である。

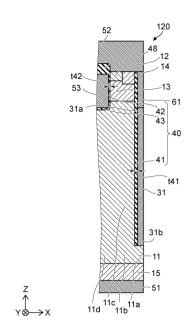

- 【図15】図15は、第1実施形態に係る半導体装置を例示する模式的断面図である。

- 【図16】図16は、第1実施形態に係る半導体装置を例示する模式的断面図である。

- 【図17】図17は、第1実施形態に係る半導体装置を例示する模式的断面図である。

- 【図18】図18は、第1実施形態に係る半導体装置を例示する模式的断面図である。

- 【図19】図19は、第1実施形態に係る半導体装置を例示する模式的断面図である。

- 【図20】図20は、第1実施形態に係る半導体装置を例示する模式的断面図である。

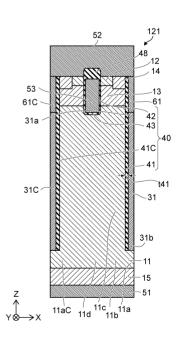

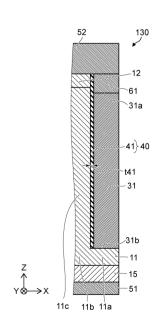

- 【図21】図21は、第2実施形態に係る半導体装置を例示する模式的断面図である。

- 【図22】図22は、第2実施形態に係る半導体装置を例示する模式的断面図である。

- 【図23】図23(a)及び図23(b)は、実施形態に係る半導体装置の製造方法を例示する模式的断面図である。

【図24】図24(a)及び図24(b)は、実施形態に係る半導体装置の製造方法を例示する模式的断面図である。

【図25】図25(a)及び図25(b)は、実施形態に係る半導体装置の製造方法を例示する模式的断面図である。

【図26】図26は、実施形態に係る半導体装置の製造方法を例示する模式的断面図である。

### 【発明を実施するための形態】

#### [0007]

以下に、本発明の各実施の形態について図面を参照しつつ説明する。

図面は模式的または概念的なものであり、各部分の厚さと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

#### [00008]

### (第1実施形態)

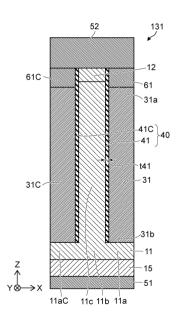

図1は、第1実施形態に係る半導体装置を例示する模式的断面図である。

図1に示すように、実施形態に係る半導体装置110は、第1電極51、第2電極52、第3電極53、第1半導体領域11、第2半導体領域12、第3半導体領域13、第1部材31、及び、第1絶縁部材40を含む。

### [0009]

第1電極51から第2電極52への方向は、第1方向に沿う。第1方向をZ軸方向とする。Z軸方向に対して垂直な1つの方向をX軸方向とする。Z軸方向及びX軸方向に対して垂直な方向をY軸方向とする。

#### [0010]

第1半導体領域11は、第1部分領域11a、第2部分領域11b及び第3部分領域11cを含む。第2部分領域11bから第1部分領域11aへの第2方向は、第1方向(Z軸方向)と交差する。第2方向は、例えば、X軸方向である。第1半導体領域11は、第1導電形である。

#### [0011]

第2半導体領域12は、第1導電形である。第1半導体領域11の第3部分領域11c は、第1方向(Z軸方向)において、第2部分領域11bと第2半導体領域12との間に ある。

### [0012]

第3半導体領域13は、Z軸方向において、第3部分領域11cと第2半導体領域12 との間に設けられる。第3半導体領域13は、第2導電形である。

#### [0013]

例えば、第1導電形はn形であり第2導電形はp形である。第1導電形がp形で第2導電形がn形でもよい。以下では、第1導電形がn形であり第2導電形がp形であるとする。

10

20

30

40

#### [0014]

第3半導体領域13から第3電極53への方向は、第2方向(例えば、X軸方向)に沿う。例えば、第2半導体領域12の一部から第3電極53の一部への方向がX軸方向に沿ってもよい。第3部分領域11cの一部から第3電極53の一部への方向がX軸方向に沿ってもよい。

#### [0015]

第1部分領域11aから第1部材31への方向は、第1方向(Z軸方向)に沿う。第3部分領域11cから第1部材31への方向は、第2方向(X軸方向)に沿う。

#### [0016]

第1 絶縁部材40は、第1 絶縁領域41及び第2 絶縁領域42 を含む。第1 絶縁領域41は、第2方向(X軸方向)において、第3部分領域11 cと第1部材31との間にある。第2 絶縁領域42は、第2方向において、第3半導体領域13と第3電極53との間にある。

#### [0017]

第1電極51は、例えば、ドレイン電極である。第2電極52は、例えば、ソース電極である。第3電極53は、例えば、ゲート電極である。第3電極53の電位を制御することで、第1電極51と第2電極52との間に流れる電流を制御できる。第3電極53の電位は、例えば、第2電極52の電位を基準にしたときの電位である。半導体装置110は、例えば、トランジスタである。第2絶縁領域42は、例えば、ゲート絶縁膜として機能する。

#### [0018]

この例では、半導体装置110は、第4半導体領域14及び第5半導体領域15を含む。第4半導体領域14は、第2電極52と電気的に接続される。第4半導体領域14は、第2導電形(例えば、p形)である。例えば、第4半導体領域14における第2導電形の不純物の濃度は、第3半導体領域13における第2導電形の不純物の濃度よりも高い。

### [0019]

第5半導体領域15は、第1電極51と第1半導体領域11との間に設けられる。第5半導体領域15は第1導電形(例えば、n形)である。例えば、第5半導体領域15における第1導電形の不純物の濃度は、第1半導体領域11における第1導電形の不純物の濃度よりも高い。

### [0020]

例えば、第2半導体領域12における第1導電形の不純物の濃度は、第1半導体領域1 1における第1導電形の不純物の濃度よりも高い。

### [0021]

第1~第5半導体領域11~15は、例えば、シリコンを含む。これらの半導体領域は、化合物半導体を含んでもよい。第1~第5半導体領域11~15がシリコンを含む場合、第1導電形(n形)の不純物は、例えば、As及びPよりなる群から選択された少なくとも1つを含む。第2導電形(p形)の不純物は、例えば、B及びAlよりなる群から選択された少なくとも1つを含む。

### [0022]

第1半導体領域11における第1導電形の不純物の濃度は、例えば、1×10<sup>16</sup>/cm $^3$ 以上1×10<sup>17</sup>/cm $^3$ 以下である。第2半導体領域12における第1導電形の不純物の濃度は、例えば、1×10<sup>18</sup>/cm $^3$ 以下である。第3半導体領域13における第2導電形の不純物の濃度は、例えば、5×10 $^{1.6}$ /cm $^3$ 以上1×10 $^{1.8}$ /cm $^3$ 以下である。第4半導体領域14における第2導電形の不純物の濃度は、例えば、1×10 $^{1.8}$ /cm $^3$ 以上5×10 $^{1.9}$ /cm $^3$ 以下である。第5半導体領域15における第1導電形の不純物の濃度は、例えば、5×10 $^{1.8}$ /cm $^3$ 以上5×10 $^{1.9}$ /cm $^3$ 以下である。

#### [0023]

第1半導体領域11は、例えば、n領域である。第2半導体領域12は、例えば、n<sup>+</sup>

10

20

30

領域である。第3半導体領域13は、例えば、p領域である。第4半導体領域14は、例えば、p<sup>+</sup>領域である。第5半導体領域15は、例えば、n<sup>+</sup>領域である。

[0024]

第2電極52は、例えば、第2半導体領域12及び第4半導体領域14と接する。

[0025]

この例では、第1部材31の少なくとも一部は、第1方向(Z軸方向)において、第1部分領域11aと、第3電極53の少なくとも一部と、の間にある。第1絶縁部材40は、第3絶縁領域43を含む。第3絶縁領域43は、Z軸方向において、第1部材31と第3電極53とを電気的に絶縁する。

[0026]

この例では、半導体装置110は、第2絶縁部材48をさらに含む。第2絶縁部材48 は、第3電極53と第2電極52との間を電気的に絶縁する。

[0027]

第 1 絶縁部材 4 0 及び第 2 絶縁部材 4 8 は、例えば、酸化シリコン(例えば、  $SiO_2$ )を含む。第 1 絶縁部材 4 0 及び第 2 絶縁部材 4 8 は、例えば、酸化シリコン、窒化シリコン、酸窒化シリコン、酸化アルミニウム、及び、酸化ハフニウムよりなる群から選択された少なくとも 1 つを含んでもよい。

[0028]

第1部材31は、第1部分領域11aと電気的に接続される。例えば、第1部材31は、第1部分領域11aと接する。

[0029]

第1部材31は、第2電極52と電気的に接続される。または、第1部材31は、第2電極52と電気的に接続されることが可能である。図1の例では、半導体装置110は、第1導電部61を含む。第1導電部61は、第1部材31と第2電極52とを電気的に接続する。図1の例では、配線61Lが設けられる。配線61Lは、図1の断面とは異なる位置を通って、第1部材31と第2電極52とを電気的に接続する。図1に示すように、端子61Tが設けられてもよい。端子61Tは、第1導電部61と電気的に接続される。半導体装置110に含まれない配線などにより、端子61Tが第2電極52と電気的に接続されてもよい。

[0030]

例えば、第1部材31の抵抗率は、第1部分領域11aの抵抗率よりも高く、第1絶縁部材40の抵抗率よりも低い。例えば、第1部材31の抵抗率は、第1半導体領域11の抵抗率よりも高い。第1部材31の抵抗率は、第1~第3電極51~53の抵抗率よりも高くてもよい。第1部材31は、例えば、「高抵抗膜」である。

[0031]

実施形態によれば、例えば、オフ時に第1部材31に微小な電流が流れることが可能である。これにより、例えば、第3部分領域11c(例えばメサ領域)における電界を均一化できる。例えば、ソース・ドレイン間の電荷量Qossを低減できる。これにより、例えば、損失を抑制できる。例えば、消費電力を低減できる。例えば、ゲート絶縁膜に印加される電界を低減できる。例えば、高い信頼性が得られる。実施形態によれば、例えば、特性を向上できる半導体装置を提供できる。

[0032]

第1部材31は、以下のような各種の材料を含んでもよい。第1部材31は、例えば、第1材料、第2材料、第3材料、第4材料、第5材料及び第6材料よりなる群から選択された少なくとも1つを含む。第1材料は、例えば、Si、N及びOを含む。

[0033]

第2材料は、例えば、Si、N及びOを含む。第2材料は、例えば、Si-Nの結合、N-Oの結合、及び、N-Nの結合を含む。第2材料は、例えば、酸素ドープされたSIPOS (Semi-insulating Poly-crystalline Silicon)を含む。第2材料は、例えば、S

10

20

30

40

i H<sub>4</sub>、N<sub>2</sub>O、及び、N<sub>2</sub>の混合材料である。

#### [0034]

第3材料は、Si、N及びOを含む。第3材料は、例えば、Si-Nの結合、N-Hの結合、及び、N-Nの結合を含む。第3材料は、例えば、窒素ドープされたSIPOSである。第3材料は、SiH4、NH3、及び、N2の混合材料である。

#### [0035]

第4材料は、例えば、Siと、Cと、第1元素と、を含む。第1元素は、B及びNよりなる群から選択された少なくとも1つを含む。第5材料は、例えば、Siと、Oと、第2元素と、を含む。第2元素は、E0と、第2元素と、を含む。第2元素は、E1、E2、E3、E3、E3、E3、E4、E3、E3、E4、E4、E4、E5 がいる群から選択された少なくともE4、E5 がいる群から選択された少なくともE7 がいる群から選択された少なくともE8 がいる群から選択された少なくともE9 がいる群から選択された少なくともE9 がいるさい。

#### [0036]

このような材料により、例えば、第1部材31は、適切な抵抗率を有することができる。 。これにより、上記のように、特性を向上できる半導体装置を提供できる。

#### [0037]

1つの例において、第1部材31の抵抗率は、 $5 \times 10^{7}$  <u>c</u>m以上 $8 \times 10^{11}$  <u>c</u>m以下である。

### [0038]

図1に例示する半導体装置110の構成は、例えば、半導体装置の端(周辺領域)に設けられてもよい。または、図1に例示する半導体装置110の構成は、例えば、半導体装置の内側部分に設けられてもよい。

#### [0039]

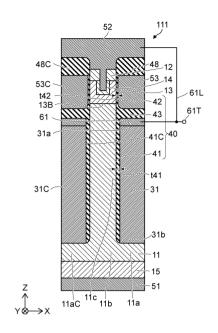

図2は、第1実施形態に係る半導体装置を例示する模式的断面図である。

図2に示すように、実施形態に係る半導体装置111は、第1電極51、第2電極52、第3電極53、第1半導体領域11、第2半導体領域12、第3半導体領域13、第1部材31、及び、第1絶縁部材40に加えて、第1対向部材31Cを含む。半導体装置111について以下に説明する部分を除いて、半導体装置111は、半導体装置110と同様の構成を有してよい。

### [0040]

図 2 に示すように、第 3 部分領域 1 1 c は、第 2 方向 (X 軸方向)において第 1 対向部材 3 1 C と第 1 部材 3 1 との間にある。

### [0041]

第1 絶縁部材 4 0 は、第1 対向絶縁領域 4 1 C をさらに含む。第1 対向絶縁領域 4 1 C は、第2 方向(X 軸方向)において、第1 対向部材 3 1 C と第3部分領域 1 1 c との間にある。第1 半導体領域 1 1 は、第1 対向部分領域 1 1 a C をさらに含む。第2部分領域 1 1 b は、第2 方向において第1 対向部分領域 1 1 a C と第1部分領域 1 1 a との間にある。第1 対向部分領域 1 1 a C から第1 対向部材 3 1 C への方向は、第1 方向(Z 軸方向)に沿う。

### [0042]

第1対向部材31Cは、第1対向部分領域11aCと電気的に接続される。例えば、第1対向部材31Cは、第1対向部分領域11aCと接する。

#### [0043]

例えば、第1対向部材31Cの抵抗率は、第1部分領域11aの抵抗率よりも高く、第1絶縁部材40の抵抗率よりも低い。例えば、第1対向部材31Cの抵抗率は、第1対向部分領域11aCの抵抗率よりも高い。例えば、第1対向部材31Cは、上記の、第1材料、第2材料、第3材料、第4材料、第5材料及び第6材料よりなる群から選択された少なくとも1つを含む。

#### [0044]

10

20

30

例えば、第3部分領域11cは、第1絶縁領域41及び第1対向絶縁領域41Cを介して、第1部材31及び第1対向部材31Cに挟まれる。

#### [0045]

半導体装置111において、例えば、オフ時に第1部材31及び第1対向部材31Cに微小な電流が流れることが可能である。これにより、例えば、第3部分領域11c(例えばメサ領域)における電界を均一化できる。例えば、ソース・ドレイン間の電荷量Qossを低減できる。これにより、例えば、損失を抑制できる。例えば、消費電力を低減できる。例えば、ゲート絶縁膜に印加される電界を低減できる。例えば、高い信頼性が得られる。実施形態によれば、例えば、特性を向上できる半導体装置を提供できる。

#### [0046]

図2に示すように、半導体装置111は、第3対向電極53Cをさらに含んでもよい。この例では、第3対向電極53Cは、第1対向部材31Cと第2電極52との間に設けられる。第3対向電極53Cは、例えば、ゲート電極として機能する。この例では、第3対向電極53Cと第2電極52との間に第2対向絶縁部材48Cが設けられている。

#### [0047]

図 2 に例示した構造(第 1 部材 3 1 及び第 3 電極 5 3 を含む構造)が複数設けられてもよい。複数のこのような構造は、例えば、X 軸方向に沿って並ぶ。

#### [0048]

例えば、第1部材31及び第1対向部材31Cは、Y軸方向に延びる帯状である。例えば、第3電極53及び第3対向電極53Cは、Y軸方向に延びる帯状である。Y軸方向は、例えば、第1方向及び第2方向を含む平面と交差する。

#### [0049]

図1及び図2に示すように、第1部材31は、第1端31aと、第2端31bと、を含む。第2端31bは、第1方向(Z軸方向)において第1部分領域11aと第1端31aとの間にある。第1端31aの第1方向(Z軸方向)における位置は、第3部分領域11cと第3半導体領域13との境界13Bの第1方向における位置と、第2端31bの第1方向における位置と、の間にある。例えば、第1端31aは、例えば、第1部材31の上端である。境界13Bは、第3半導体領域13の下端である。例えば、第1部材31の上端は、第3半導体領域13の下端より、pn接合の部分での電界が上昇することが抑制できる。

### [0050]

図1に示すように、第1絶縁領域41の第2方向(X軸方向)に沿う長さを長さt41とする。第2絶縁領域42の第2方向(X軸方向)に沿う長さを長さt42とする。長さt42は、長さt41よりも短い。ゲート絶縁膜に対応する第2絶縁領域42の長さt42(厚さ)が短いことで、適切な電気的な特性(例えばしきい値電圧など)が得やすくなる。

## [0051]

#### [0052]

以下、半導体装置 1 1 1 の特性の例について説明する。以下の例では、第 1 対向部材 3 1 とは第 1 部材 3 1 と同様の構成及び特性を有し、第 3 対向電極 5 3 C は、第 3 電極 5 3 と同様の構成及び特性を有する。

### [0053]

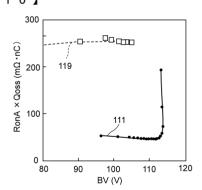

図3及び図4は、半導体装置の特性を例示するグラフ図である。

図3は、第1部材31の抵抗率とブロッキング電圧との関係のシミュレーション結果の例を示している。図3の横軸は、第1部材31の抵抗率R1である。図3の縦軸は、ブロッキング電圧BVである。図3に示すように、第1部材31の抵抗率R1が、5×10<sup>7</sup>

10

20

30

cm以上において、高いブロッキング電圧BVが得られる。

#### [0054]

図4は、第1部材31の抵抗率とドレイン電流との関係のシミュレーション結果の例を示している。図4の横軸は、第1部材31の抵抗率R1である。図4の縦軸は、ドレイン電流 Idである。図4には、第1部材31を流れる電流成分 I1と、第3部分領域11cを流れる電流成分 I2と、が示されている。図4に示すように、抵抗率R1が低くなると、電流成分 I1は増大する。例えば、抵抗率R1が8×10 $^{1}$  cm以下において、電流成分 I1は、電流成分 I2よりも大きくなる。

#### [0055]

実施形態において、第 1 部材 3 1 の抵抗率は、例えば、  $5 \times 10^{7}$  <u>c</u>m以上  $8 \times 10^{11}$  <u>c</u>m以下であることが好ましい。これにより、例えば、高いブロッキング電圧  $B \times 10^{11}$  で 以下であることが好ましい。これにより、例えば、高いブロッキング電圧  $B \times 10^{11}$  で は で さ 、例えば、第 3 部分領域 1 1 c における電界を効果的に均一化できる。例えば、ソース・ドレイン間の電荷量  $Q \circ S$  S を 効果的に低減できる。

#### [0056]

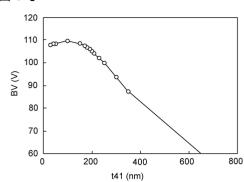

図5は、半導体装置の特性を例示するグラフ図である。

図5は、第1部材31の厚さ(長さt41)とブロッキング電圧との関係のシミュレーション結果の例を示している。図5の横軸は、第1部材31の厚さ(長さt41)である。図5の縦軸は、ブロッキング電圧BVである。図5に示すように、第1部材31の厚さ(長さt41)が薄くなると、ブロッキング電圧BVが上昇する。例えば、長さt41が20nm以上250nm以下において、特に高いブロッキング電圧BVが得られる。実施形態において、長さt41は20nm以上250nm以下であることが好ましい。これにより、高いブロッキング電圧BVが得やすくなる。長さt41は20nm以上200nm以下でもよい。

#### [0057]

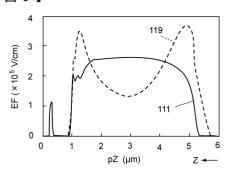

図6は、半導体装置の特性を例示するグラフ図である。

### [0058]

図6に示すように、参考例の半導体装置119においては、第1部材31の上端及び下端の位置において、電界EFのピークが生じる。これに対して、半導体装置111においては、電界EFは実質的に均一である。このように、実施形態においては、電界EFを均一にし易い。

### [0059]

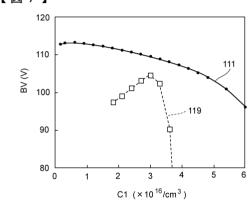

図7は、半導体装置の特性を例示するグラフ図である。

図7は、第1半導体領域11における第1導電形(n形)の不純物の濃度とブロッキング電圧との関係のシミュレーション結果の例を示している。図7の横軸は、不純物の濃度C1である。縦軸は、ブロッキング電圧BVである。図7には、半導体装置111と半導体装置119とにおける特性が例示されている。

### [0060]

図7に示すように、半導体装置119においては、不純物の濃度C1が高くなると、ブロッキング電圧BVが急激に低下する。半導体装置111においては、濃度C1が高い場合も、高いブロッキング電圧BVを維持できる。これは、実施形態においては、電界EFの均一性が高いことに起因する。

### [0061]

10

20

30

- -

実施形態においては、例えば、参考例と同じブロッキング電圧が得られるときの不純物の濃度 C 1 を高くできる。実施形態においては、同じ濃度 C 1 において、参考例よりも高いブロッキング電圧 B V が得られる。

#### [0062]

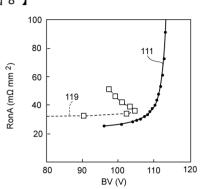

図8~図10は、半導体装置の特性を例示するグラフ図である。

これらの図は、第1半導体領域11における不純物の濃度C1を変えたときの特性のシミュレーション結果の例を示している。図8~図10の横軸は、ブロッキング電圧BVである。図8の縦軸は、ゲート電圧が10Vのときのオン抵抗RonAである。図9の縦軸は、ドレイン電圧が0Vから50Vの範囲で放出される、ソース・ドレイン間の電荷量Qossである。図10の縦軸は、オン抵抗RonA及び電荷量Qossの積である。これらの図には、半導体装置111の特性と、参考例の半導体装置119の特性と、が示されている。

### [0063]

図8に示すように、半導体装置111においては、半導体装置119と比べて、高いブロッキング電圧BV及び低いオン抵抗RonAの少なくともいずれかが得られる。図9に示すように、半導体装置111においては、半導体装置119と比べて、高いブロッキング電圧BV及び小さい電荷量Qossの少なくともいずれかが得られる。図10に示すように、半導体装置111においては、半導体装置119と比べて、高いブロッキング電圧BV、及び、小さいオン抵抗RonA及び電荷量Qossの積の少なくともいずれかが得られる。

#### [0064]

例えば、ブロッキング電圧 B V が 1 0 4 V の時に着目する。半導体装置 1 1 1 においては、参考例を基準にして、オン抵抗 R o n A を 2 3 % 低減できる。これは、例えば、半導体装置 1 1 1 においては、均一な電界 E F が得られるため、第 1 半導体領域 1 1 における不純物の濃度 C 1 を高くすることができることに起因する。例えば、ブロッキング電圧 B V が 1 0 4 V の時に着目すると、半導体装置 1 1 1 においては、参考例を基準にして、電荷量 Q o s s を 7 4 % 低減できる。例えば、ブロッキング電圧 B V が 1 0 4 V の時に着目すると、半導体装置 1 1 1 においては、参考例を基準にして、オン抵抗 R o n A 及び電荷量 Q o s s の積を 8 0 % 低減できる。

#### [0065]

このように、実施形態によれば、ブロッキング電圧BVとオン抵抗RonAとのトレードオフを改善できる。実施形態によれば、ブロッキング電圧BVと電荷量Qossとのトレードオフを改善できる。実施形態によれば、ブロッキング電圧BVと、オン抵抗RonA及び電荷量Qossの積と、のトレードオフを改善できる。

### [0066]

以下、実施形態に係る半導体装置のいくつかの例について説明する。以下の説明において、半導体装置110または半導体装置111と同様の部分については、適宜省略される。 【0067】

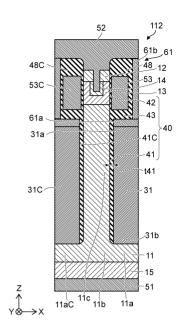

図11~図15は、第1実施形態に係る半導体装置を例示する模式的断面図である。

図11に示すように、実施形態に係る半導体装置112において、第1導電部61は、第1導電領域61a及び第2導電領域61bを含む。第1導電領域61aは、例えば、第1端31aと接する。第2導電領域61bは、Z軸方向に延びる。第2導電領域61bは、第1導電領域61a及び第2電極52と接する。このような第1導電部61により第1部材31と第2電極52とが電気的に接続されてもよい。

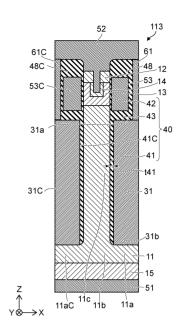

### [0068]

図12に示す実施形態に係る半導体装置113のように、第1導電部61は、Z軸方向に沿って延びてもよい。第1導電部61は、例えば、第1部材31及び第2電極52と接する。図12に示すように、第1対向導電部61Cにより、第1対向部材31Cが第2電極52と電気的に接続されてもよい。

### [0069]

10

20

30

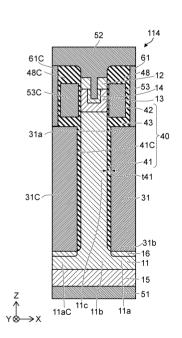

図13に示すように、実施形態に係る半導体装置114は、第6半導体領域16を含む。第6半導体領域16は、第1部分領域11aと第1部材31との間に設けられる。第6半導体領域16は、第1導電形である。第6半導体領域16は、第1部分領域11a及び第1部材31と電気的に接続される。第6半導体領域16における第1導電形の不純物の濃度よりも高い。第6半導体領域16は、例えば、n+領域である。第6半導体領域16を設けることで、第1部分領域11a及び第1部材31が、低いコンタクト抵抗で、安定して電気的に接続される。

#### [0070]

図14に示すように、実施形態に係る半導体装置115においては、第1半導体領域11において、第1部分領域11a、第2部分領域11b及び第1対向部分領域11aCにおける不純物の濃度は、第3部分領域11c(例えば、n領域)よりも高い。このように、第3部分領域11cにおける第1導電形の不純物の濃度は、第1部分領域11aにおける第1導電形の不純物の濃度よりも低くてもよい。

#### [0071]

図15に示すように、実施形態に係る半導体装置116は、第7半導体領域17を含む。第7半導体領域17は、第3部分領域11cと第3半導体領域13との間に設けられる。第7半導体領域17は、記第1導電形である。第7半導体領域17における第1導電形の不純物の濃度は、第3部分領域11cにおける第1導電形の不純物の濃度よりも低い。第7半導体領域17は、例えば、n<sup>-</sup>領域である。第7半導体領域17を設けることで、例えば、ゲート電圧が負のときのブロッキング電圧BVが改善できる。

#### [0072]

半導体装置112~116においても、特性を向上できる半導体装置を提供できる。

#### [0073]

図16は、第1実施形態に係る半導体装置を例示する模式的断面図である。

図16に示すように、実施形態に係る半導体装置120においては、第1半導体領域11は、第4部分領域11dをさらに含む。第2部分領域11bは、第2方向(X軸方向)において、第4部分領域11dと第1部分領域11aとの間にある。第3電極53は、第1方向(Z軸方向)において、第4部分領域11dと第2電極52との間にある。第1絶縁部材40は、第3絶縁領域43を含む。第3絶縁領域43は、第1方向(Z軸方向)において、第4部分領域11dと第3電極53との間にある。

### [0074]

図17は、第1実施形態に係る半導体装置を例示する模式的断面図である。

図17に示すように、実施形態に係る半導体装置121においては、半導体装置120 の構成において、第1対向部材31Cがさらに設けられる。

### [0075]

半導体装置120及び121においては、第3電極53は、X軸方向において、第1部材31とは異なる位置にある。半導体装置120及び121においても、例えば、オフ時に第1部材31及び第1対向部材31Cに微小な電流が流れることが可能である。これにとり、例えば、第3部分領域11c(例えばメサ領域)における電界を均一化できる。例えば、ソース・ドレイン間の電荷量Qossを低減できる。これにより、例えば、損失を抑制できる。例えば、消費電力を低減できる。例えば、ゲート絶縁膜に印加される電界を低減できる。例えば、高い信頼性が得られる。半導体装置120及び121においても、例えば、特性を向上できる半導体装置を提供できる。

#### [0076]

図18~図20は、第1実施形態に係る半導体装置を例示する模式的断面図である。

図18に示すように、実施形態に係る半導体装置122は、第2導電部62を含む。第2導電部62は、第2電極52と電気的に接続される。図18の例のように、例えば、配線62Lにより、第2導電部62が第2電極52と電気的に接続されてもよい。

### [0077]

第2導電部62は、第1方向(Z軸方向)において、第4部分領域11dと第3電極5

20

10

30

40

3との間にある。第1絶縁部材40は、第4絶縁領域44を含む。第4絶縁領域44は、第1方向(Z軸方向)において第4部分領域11dと第2導電部62との間にある。第3 絶縁領域43は、第1方向において第2導電部62と第3電極53との間にある。第2導電部62により、例えば、帰還容量を低減することができる。

#### [0078]

図19に示す実施形態に係る半導体装置123のように、第1導電部61は、第1導電 領域61a及び第2導電領域61bを含んでもよい。第1対向導電部61Cは、第1対向 導電領域61aC及び第2対向導電領域61bCを含んでもよい。

#### [0079]

図20に示す実施形態に係る半導体装置124のように、半導体装置123において、第2導電部62が設けられてもよい。半導体装置124において、配線62L(図18参照)が設けられてもよい。

#### [0800]

半導体装置122~124においても、特性を向上できる半導体装置を提供できる。

#### [0081]

(第2実施形態)

図21は、第2実施形態に係る半導体装置を例示する模式的断面図である。

図21に示すように、実施形態に係る半導体装置130は、第1電極51、第2電極52、第1半導体領域11、第2半導体領域12、第1部材31、及び、第1絶縁部材40を含む。

#### [0082]

第1電極51から第2電極52への方向は、第1方向(例えばZ軸方向)に沿う。第1半導体領域11は、第1部分領域11a、第2部分領域11b及び第3部分領域11cを含む。第1半導体領域11は、第1導電形である。第2部分領域11bから第1部分領域11aへの第2方向は、第1方向と交差する。第2方向は、例えば、X軸方向である。

#### [0083]

第2半導体領域12は、第2導電形である。第3部分領域11cは、第1方向(Z軸方向)において、第2部分領域11bと第2半導体領域12との間にある。

### [0084]

第1部分領域11aから第1部材31への方向は、第1方向(Z軸方向)に沿う。第3部分領域11cから第1部材31への方向は、第2方向(X軸方向)に沿う。第1絶縁部材40は、第1絶縁領域41を含む。第1絶縁領域41は、第2方向(X軸方向)において、第3部分領域11cと第1部材31との間にある。第1部材31は、第1部分領域11aと電気的に接続される。または、第1部材31は、第2電極52と電気的に接続されることが可能である。例えば、図1及び図2に関して説明した配線61L及び端子61Tの少なくともいずれかが設けられてもよい。これにより、第1部材31は、第2電極52と電気的に接続されることが可能である。半導体装置130は、例えば、ダイオードである。

### [0085]

第1部材31の抵抗率は、例えば、第1部分領域11aの抵抗率よりも高く、第1絶縁部材40の抵抗率よりも低い。例えば、第1部材31は、上記の、第1材料、第2材料、第3材料、第4材料、第5材料及び第6材料よりなる群から選択された少なくとも1つを含んでもよい。

#### [0086]

このような第1部材31を設けることで、例えば、電界の集中が抑制できる。これにより、特性を向上できる半導体装置を提供できる。

#### [0087]

図22は、第2実施形態に係る半導体装置を例示する模式的断面図である。

図 2 2 に示す実施形態に係る半導体装置 1 3 1 のように、第 1 対向部材 3 1 C 及び第 1 対向導電部 6 1 C を含んでもよい。第 1 絶縁部材 4 <u>0</u> は、第 1 対向絶縁領域 4 1 C を含ん

10

20

30

でもよい。半導体装置131においても、特性を向上できる半導体装置を提供できる。

#### [0088]

以下、実施形態に係る半導体装置の製造方法の例について説明する。以下では、半導体 装置111の製造方法の例について説明する。

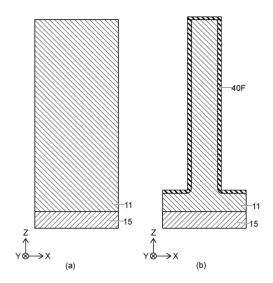

図 2 3 ( a )、図 2 3 ( b )、図 2 4 ( a )、図 2 4 ( b )、図 2 5 ( a )、図 2 5 ( b )、及び、図 2 6 は、実施形態に係る半導体装置の製造方法を例示する模式的断面図である。

図23(a)に示すように、例えば、第5半導体領域15(例えば半導体基板)の上に、第1半導体領域11となるn形半導体層を形成する。n形半導体層の厚さは、例えば、8.75μmである。n形半導体層は、例えば、エピタキシャル成長により形成される。

### [0089]

図23(b)に示すように、マスクとなるシリコン酸化膜を形成した後、 n 形半導体層の一部を除去し、トレンチを形成し、熱酸化により、 n 形半導体層の表面部分から絶縁膜40F(例えばSiO2膜)を形成する。絶縁膜40Fは、第1絶縁部材40の少なくとも一部となる。絶縁膜40Fの厚さは、例えば、20nm以上250nm以下である。

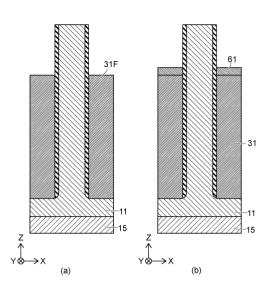

#### [0090]

図24(a)に示すように、ドライエッチングにより、トレンチの底部及び n 形半導体層の頂部の上に位置する絶縁膜40Fを除去し、この後、第1部材31となる膜31Fを形成する。膜31Fは、例えば、低濃度で不純物を含むポリシリコンでもよい。膜31F は、例えば、Feを含むInP膜でもよい。膜31Fの一部をエッチングにより除去する。

#### [0091]

図 2 4 (b)に示すように、第 1 導電部 6 1 として、例えば、高濃度で不純物を含むポリシリコン膜を形成する。

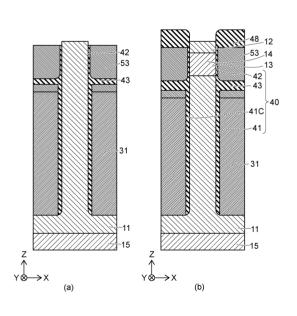

#### [0092]

図25(a)に示すように、第3絶縁領域43及び第2絶縁領域42となる絶縁膜(例えば、SiO2膜)を形成し、さらに、第3電極53を形成する。必要に応じて、不要な膜を除去する。

#### [0093]

図 2 5 (b)に示すように、第 2 絶縁部材 4 8 を形成し、 p 形の不純物を導入し、 n 形の不純物を導入して、第 3 半導体領域 1 3 及び第 2 半導体領域 1 2 を形成する。

### [0094]

図 2 6 に示すように、第 1 電極 5 1 及び第 2 電極 5 2 を形成する。これにより、例えば、半導体装置 1 1 1 が得られる。

### [0095]

実施形態によれば、特性を向上できる半導体装置を提供できる。

### [0096]

以上、具体例を参照しつつ、本発明の実施の形態について説明した。しかし、本発明は、これらの具体例に限定されるものではない。例えば、半導体装置に含まれる電極、半導体領域、部材、絶縁部材及び導電部などの各要素の具体的な構成に関しては、当業者が公知の範囲から適宜選択することにより本発明を同様に実施し、同様の効果を得ることができる限り、本発明の範囲に包含される。

### [0097]

また、各具体例のいずれか2つ以上の要素を技術的に可能な範囲で組み合わせたものも、本発明の要旨を包含する限り本発明の範囲に含まれる。

#### [0098]

その他、本発明の実施の形態として上述した半導体装を基にして、当業者が適宜設計変更して実施し得る全ての半導体装置も、本発明の要旨を包含する限り、本発明の範囲に属する。

### [0099]

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想

10

20

\_ \_

30

到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

#### [0100]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。 【符号の説明】

#### [0 1 0 1]

1 1 ~ 1 7 … 第 1 ~ 第 7 半導体領域、 1 1 a ~ 1 1 d … 第 1 ~ 第 4 部分領域、 1 1 a C … 第 1 対向部分領域、 1 3 B … 境界、 3 1 … 第 1 部材、 3 1 C … 第 1 対向部材、 3 1 F … 膜、 3 1 a、 3 1 b … 第 1、第 2 端、 4 0 … 第 1 絶縁部材、 4 0 F … 絶縁膜、 4 1 ~ 4 4 … 第 1 ~ 第 4 絶縁領域、 4 1 C … 第 1 対向絶縁領域、 4 8 … 第 2 絶縁部材、 4 8 C … 第 2 対向絶縁部材、 5 1 ~ 5 3 … 第 1 ~ 第 3 電極、 5 3 C … 第 3 対向電極、 6 1、 6 2 … 第 1、第 2 導電部、 6 1 C、 6 2 C … 第 1、第 2 対向導電部、 6 1 L、 6 2 L … 配線、 6 1 T … 端子、 6 1 a、 6 2 b … 第 1、第 2 導電領域、 6 1 a C、 6 2 b C … 第 1、第 2 対向導電領域、 1 1 0 ~ 1 1 6、 1 1 9、 1 2 0 ~ 1 2 4 , 1 3 0、 1 3 1 … 半導体装置、 B V … プロッキング電圧、 C 1 … 濃度、 E F … 電界、 I 1、 I 2 … 電流成分、 I d … ドレイン電流、 Q o s s … 電荷量、 R 1 … 抵抗率、 R o n A … オン抵抗、 p Z … 位置、 t 4 1、 t 4 2 … 長さ

30

10

20

【図面】

【図1】

【図2】

20

10

40

# 【図5】

# 【図6】

10

【図7】

【図8】

20

# 【図9】

【図10】

30

【図11】

【図12】

30

10

【図13】

【図14】

【図15】

【図16】

30

10

【図17】

【図18】

【図19】

【図20】

10

【図21】

【図22】

40

【図23】

【図24】

10

【図25】

【図26】

40

```

フロントページの続き

(51)国際特許分類

FΙ

H 0 1 L 21/336 (2006.01)

H 0 1 L

29/06

3 0 1 V

H 0 1 L 29/41 (2006.01)

H 0 1 L

6 5 2 H

29/78

H 0 1 L

29/78

6 5 2 J

H 0 1 L

29/91

D

H 0 1 L

658F

29/78

H 0 1 L

29/44

Υ

東京都港区芝浦一丁目1番1号 株式会社東芝内

下條 亮平

(72)発明者

東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内

審査官

多賀 和宏

(56)参考文献

特表2004-519848(JP,A)

特表2013-503491(JP,A)

特開2017-055102(JP,A)

特表2007-529115(JP,A)

特開2002-217415(JP,A)

特開2019-091822(JP,A)

特開2007-189192(JP,A)

特開2003-031821(JP,A)

特表2003-523087(JP,A)

特表2003-523088(JP,A)

特表2003-523086(JP,A)

特開平07-099307(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H01L 29/06, 29/12, 29/41, 29/78, 29/861, 29/86

```

H01L 21/329, 21/336