# (19) 대한민국특허청(KR) (12) 특허공보(B1)

(51) Int. CI.<sup>6</sup> G11C 11/407

(45) 공고일자 1997년04월10일

(11) 공고번호 특1997-0004996

| (21) 출원번호                      | ≒1990-0008353                                      | (65) 공개번호<br>(43) 공개인되 | ≒1991-0001769 |

|--------------------------------|----------------------------------------------------|------------------------|---------------|

| <u>(22) 출원일자</u><br>(30) 우선권주장 | 1990년06월07일<br>1-143413 1989년06월06일<br>후지쓰 가부시끼가이샤 | ( , ,                  | 1991년01월31일   |

| (73) 특허권자                      | 일본국 가나가와껜 가와사                                      | 끼시 나까하라꾸 가미고다          | 나나까 1015반지    |

| (72) 발명자                       | 일본국 가나가와껜 가와사<br>가와노 도오루                           | 끼시 나까하라꾸 가미고다          | 나나까 1015반지    |

|                                | 일본국 가나가와껜 가와사<br>쓰 가부시끼가이샤 내                       | 끼시 나까하라꾸 가미고다          | 나마 1015반지 후지  |

| (74) 대리인                       | 나까노 마사오<br>장용식                                     |                        |               |

# 심사관 : 김재홍 (책자공보 제4933호)

## (54) 비트 고장을 정정할 수 있는 반도체 기억 장치

#### 요약

내용 없음.

#### 叫丑도

# 도1

# 명세서

[발명의 명칭]

비트 고장을 정정할 수 있는 반도체 기억 장치

[도면의 간단한 설명]

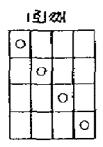

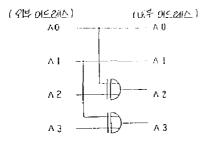

제1도는 본 발명의 원리설명도.

제2도는 본 발명의 제1실시예의 블록도.

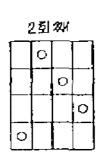

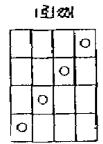

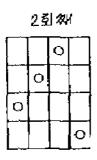

제3도(a), (b), (c) 및 (d)는 시프티드다이아고널방식의 데이타 꺼내기 설명도.

제4도는 본 발명의 제2실시예의 블록도.

제5도는 데이타 실렉터의 회로도.

제6도는 데이타 래치의 실렉터의 어드레스의 설명도.

제7도(a)도 및 제7(b)도는 데이타 래치의 주사의 설명도.

제8도는 본 발명의 제3실시예의 블록도.

제9도는 본 발명의 제4실시예의 블록도.

제10도는 열디코더의 종래예의 블록도.

제11도는 제1의 종래예의 블록도.

제12도는 제2의 종래예의 블록도.

\* 도면의 주요 부분에 대한 부호의 설명

MAO, MA1, …, MAn : 메모리 셀어레이 WLOOWL10, …WLnO : 워드선

BL00, BL10, …, BLn0 : 비트선 DX0~DXn : 행선택구동회로

DY0~DYn : 열선택구동회로 BUS : 데이타버스

DLO~DLn: 데이타래치 SA00, SA10, …, SA30: 센스앰프

CL0~CL3 : 열선택선

[발명의 상세한 설명]

본 발명은 반도체 기억장치에 관한 것으로, 특히 복수의 비트 입력 출력구성의 다이나믹 RAM에 있어서의 메모리셀을 선택하는 선택장치에 관한 것이다.

근년의 반도체 기억장치의 대용량화를 위한 미세화 프로세스의 발전에 따라 프로세스 및 제조되는 반도체 기억장치의 신뢰성의 향상이 희망되고 있다.

이중에서 반도체 기억장치 자체의 신뢰성 향상을 위해 시스템상에 사용된 오류정정회로(ECC ; Error Correction Circuit)가 채용되고 있다.

일반적으로 ECC회로는 1비트 오류를 검출하고 정정하는 구성으로 되어있다.

이 ECC회로를 복수의 비트 입출력구성의 반도체 기억장치에 적응했을 경우 복수비트가 고장(fail)이면, 오류의 검출·정정을 할 수 없게 되는 문제점이 있다.

제11도에 복수의 비트 입출력구성되는 반도체 기억장치의 제1의 예를 도시한다.

이 반도체장치는 4개의 메모리 셀어레이(MAO, MA1, MA2, MA3)를 갖는 8비트의 입출력구성으로 되어 있다. 각 메모리 셀어레이는, 예컨대 메모리 셀어레이(MAO)로 설명하면, 복수의 워드선(WLOO~WLOj)과 복수의 비트선(BLOO~BLOm) 이 매트릭스상에 교차하여 배선되고, 각 워드선(WLOO~WLOj)과 비트선(BLOO~BLOm)과의 교점의 각각에는 트랜스퍼 트랜지스터(TT) 및 메모리셀(CELOO~CELOm)이 접속되어 있다.

각 워드선(WLOO~WLOj)은 행디코더(DXO)에 의해 선택되고, 행드라이버(DRXO)에 의해 구동된다. 각 열디코더(DYO, DY1)에 부여되는 어드레스신호는 동일어드레스를 지정하고, 각 행디코더(DXO, DX1, DX2, DX3)도 역시 동일어드레스를 지정한다.

각 비트선(BL00~BL0m)은 각 메모리셀(CEL00~CEL0m)의 신호의 변화를 검지 및 증폭하기 위한 센스 앰프(SA00)에 2개가 한쌍으로 배선되어 있다. 이 센스앰프(SA00)의 검지신호는 트랜스퍼게이트(TG)를 통하여 데이타버스(BUS) 상에서 판독되고 2비트가 데이타래치(DL0, DL1)에 래치되도록 되어 있다.

트랜스퍼게이트(TGO, TG1)는 열선택선(CLOO)을 통하여 열드라이버(DRYO) 및 열디코더(DYO)에 의해 ON/OFF 제어된다. 이 트랜스퍼게이트(TGO, TG1)의 ON/OFF에 의해 비트선(BLOO, BLO1 및 BL10, BL1 1)의 선택동작이 행하여진다.

이상의 구성은 다른 메모리 셀어레이(MA1, MA2, MA3)에 대하여도 같기 때문에 설명은 생략한다. 또, 열디코더(DY0)는 메모리 셀어레이(MA0)와 메모리 셀어레이(MA1)에 공용(share)되고, 열디코더(DY1) 는 메모리 셀어레이(MA2)와 메모리 셀어레이(MA3)에 공용된다.

다음에 기억데이타의 판독동작을 간단하게 설명한다.

판독에 있어서는 메모리 셀어레이(MAO~MA3)의 센스앰프(SA)열중에서 각각 2비트씩 판독되고, 합계 8비트의 데이타가 데이타버스(BUS)를 통하여 데이타래치(DLO~DL7)에 래치된다. 이때 임의의 센스앰프(SA)열에 속하는 열선택선(CL)이 고장일 경우, 출력데이타 8비트중 2비트가 오류로 되고 시스템상에서 2비트의 검출·정정을 행할 수는 없고 ECC 회로의 적용은 불가능하다.

한편, 최근에는 배선기술 및 제조프로세스의 진보에 의해 금속층 배선의 반도체 기억장치가 등장하고 있다. 제12도에 그 예를 도시한다. 제12도에 있어서도 제11도와 같은 부재에는 동일부호를 부기하여 이하에서 설명한다.

이 반도체 기억장치는 8개의 메모리 셀어레이(MAO~MA7)를 1방향(도면상 열방상)에 배열하고, 기판 (도시하지 않음)상의 금속 제2층에 각 센스앰프(SA)열을 가로질러 통과하도록 열선택선(CL)을 연장 시켜서 각 센스앰프(SA)열 (따라서, 메모리 셀어레이(MAO~MA7)에 있어서 열선택선(CL)을 공용화하도록 한 것이다. 각 행디코더(DXO~DX7) 및 행드라이버(DRXO~DRX7)는 각 메모리 셀어레이(MAO~MA7) 마다에 독립하여 설치되어있다.

각 DR은 서로 쌍을 이루는 메모리(MAO)와 메모리 셀어레이(MA1), 메모리 셀어레이(MA2)와 메모리 셀어레이(MA3), …, 메모리 셀어레이(MA6)와 메모리 셀어레이(MA7)에 있어서 어느 한쪽을 선택하여 대응하는 센스앰프(SA)에 접속하기 위한 트랜스퍼게이트(TG)를 구동하는 드라이버이다.

이와같이 금속 제2층으로 열선택선(DL)을 배선하는 다층배선으로 구성함으로써 복수의 메모리 셀어 레이(MAO~MA7)에 대하여 1개의 열디코더(DY)로 메모리셀(CEL)의 선택동작이 가능하도록 하고 또한 복수의 센스앰프(SA)에 대하여 열선택선(CL)을 공용할 수 있기 때문에 고집적화가 가능하게 되어 있 다.

판독에 있어서는 각 센스앰프(SA)열중에서 각 비트가 판독되고, 각각 데이타래치(DL0~DL3)에 1비트씩 래치되고, 합계 4비트가 데이타버스를 통하여 출력된다.

이상의 반도체 기억장치에 있어서, 임의의 센스앰프(SA)열에 속하는 열선택선(CL)이 고장일 경우에는 출력 4비트전부가 고장으로 되고, 이 반도체 기억장치치도 제11도의 반도체 기억장치와 같이ECC 회로가 적용될 수 없다.

상기 제11도의 반도체 기억장치, 제12도의 반도체 기억장치와 같이 각 메모리 셀어레이내에서 선택된 동일 워드선상의 메모리셀을 통하여 연결되는 복수의 비트선을 동일열선택선으로 동시에 활성화하려고 하는 반도체 기억장치에 있어서는, 열선택선이 고장일 경우, 복수의 비트가 동시에 고장으로되어 1비트 구제기능의 ECC회로로는 이미 적용불가능하게 된다.

본 발명은 복수의 비트 입출력구성의 반도체 기억장치에 있어서, 고장이 발생했을 경우에 1비트의

고장으로 끝나도록 하고, 시스템상의 ECC호로의 적응을 가능하게 하는 반도체 기억장치를 제공하는 것을 목적으로 하다

본 발명은 복수의 비트 입출력구성의 다이나믹 RAM(이하 DRAM이라 함)에 있어서의 메모리셀의 선택장치에 관한 것이며, 복수의 비트 입출력구성의 반도체 기억장치에 있어서는 고장이 발생한 경우에 1비트의 고장으로 끝나도록 하고 시스템사의 ECC회로의 적응을 가능하게 하는 반도체 기억장치를 제공하는 것을 목적으로 하고 ; 복수의 워드선과 비트선과 메모리셀을 갖는 메모리 셀어레이를 구비한 반도체 기억장치에 있어서, 복수의 워드선을 동시에 활성화하는 행선택장치와, 복수의 열선택선을 동시에 독립적으로 활성화하고 복수의 비트선을 동시에 선택하는 열선택장치와, 선택된 메모리셀중에서 서로 다른 비트선과 워드선의 조합에 의해 메모리셀을 선택하는 데이타 실렉터 장치를 구비한 것으로 구성한다.

여기서는 입출력비트구성이 2비트의 경우를 설명한다.

본 발명은 제1도에 도시한 바와같이 매트릭스상으로 배선된 복수의 워드선(WLOO~WLOj)과 비트선 (BLOOO~BLOOM, BLO10~BLO1m)과의 각 교점에 각각 메모리셀(CELOOO~CELOOM, CELO10~CELO1m)이 접속되어 이루는 메모리 셀어레이를 복수(MAO~MA1)개 갖는 반도체 기억장치에 있어서, 상기 각 메모리 셀어레이(WLO) 내에 있어서 선택되는 동일워드선(WLOO)상의 메모리셀(CELOOO~CELOOOM, CELO10~CELO1m)을 통하여 연결되는 비트선(BLOOO~BLOOM, BLO10~BLO1m)중, 어느 복수의 비트선(BLOOO, BLO10)을 동시에 구동하는 열선택구동회로(SDYO, SDY1)를 구비하여 구성한다.

여기서는 입출력비트구성이 2비트의 경우를 설명한다.

각 메모리 셀어레이(MAO, MA1)의 각각에 있어서 각 행선택구동회로(DXO, DX1)에 의해 워드선(WLOO, WL10)이 선택되었다고 가정한다. 메모리 셀어레이(MAO)에 있어서는 워드선(WLOO)상에 메모리셀 (CELOOO~CELOOm, CELO10~CELO1m)이 접속되어 있는데, 그의 메모리셀(CELOOO~CELOOm, CELO10~CELO1m)에는 각각 비트선(BLOOO~BLOOm, BLO10~BLO1m)중 어느 복수의 비트선(예컨대 BLOOO~BLO10)이 열선택구동회로(SDY, SDY2)에 의해 동시에 또한 서로 독립하여 선택된다.

그와 동시에 선택된 비트선(BL000, BL010)의 데이타가 각각 데이타래치(DL1, DL0)에 의해 래치된다. 메모리 셀어레이(MA1)에 있어서는 워드선(WL1) 상의 메모리셀(CEL100~CEL10m, CEL110~CEL11m)에 접속된 비트선(BL100~BL10m, BL110~BL11m)중 복수비트(BL100~BL110)가 열선택구동회로(SDY0, SDY1)에 의해 동시에 또한 독립하여 선택되고, 비트선(BL100, BL110)의 데이타가 각각 데이타래치(DL2, DL3)에 래치된다.

각 메모리 셀어레이(MAO, MA1)에서 출력된 데이타는 데이타래치(DLO~DL3)에 래치된 후에 입출력비트 구성이 2비트이기 때문에 데이타래치(DLO, DL1)로부터 1비트, (DL2, DL3)로부터 1비트 각각이 선택되고 합계 2비트(BO, B1)로서 입출력된다. 예컨대, 열선택선(CL00)이 고장인 경우, DL1과 DL2로의데이타가 판독되지 않으나, 실렉터(BSEL)의 선택에 의해 DL1과 DL2의 동시판독은 없이 DL1 및 DL2중에는 것인가의 판독으로 되고 1비트의 오류로 된다. 이와같이 선택되기 때문에 워드선, 비트선의 어느 1개가 고장이라고 하여도 입출력데이타(BO, B1)로서는 그의 1비트만이 고장나는 것뿐이고, 외부시스템에 있어서 1비트 오류 정정 ECC회로가 적응가능하게 된다. 여기서는 입출력비트구성이 2비트의 경우를 설명하였으나 다른 복수의 비트구성에 있어서도 같다.

다음에 본 발명의 실시예를 도면에 의거하여 설명한다.

제1실시예

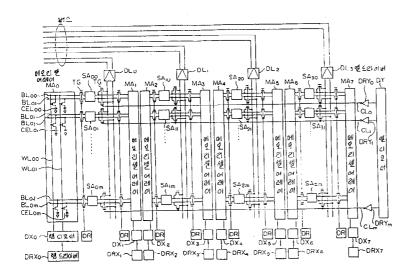

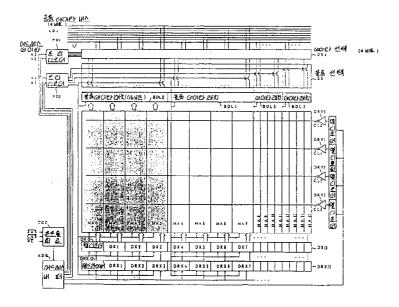

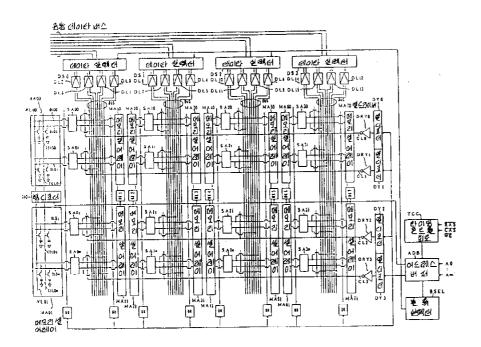

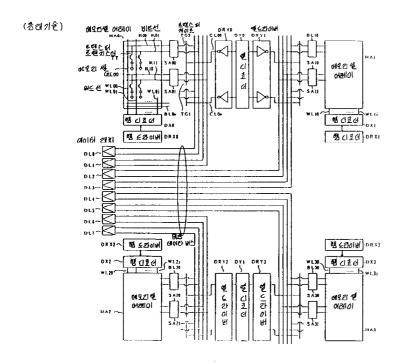

제2도에 본 발명의 제1의 실시예를 도시한다.

이 실시예는 제12도의 반도체 기억장치에 본 발명을 적응한 것이다.

이 반도체 기억장치는 금속 제2층 배선에 의해 열선택선(CL)을 각 메모리 셀어레이(MAO~MA7)의 각센스앰프(SA)열에 공용화한 것이고, 이 점에 대하여는 제12도의 반도체 기억장치와 같다.

본질적으로 다른 것은 서로 독립한 열디코더(DYO~DY3)가 사용되고, 각 메모리 셀어레이(MAO~MA7)에 각각 독립한 행디코더(DXO~DX7)가 접속되고, 행디코더(DXO~DX7)가 블록실렉터(BSEL)에 의해 선택적으로 전환되고, 또한 열디코더(DYO~DY3) 및 행디코더(DXO~DX7)가 어드레스버퍼(ADB)에서 어드레스신호에 의해 어드레스제어를 받는 점이다. 어드레스 버퍼(ADB)는 행어드레스스트로우브신호

$(\overline{RAS})$  , 열어드레스스트로우브신호 $(\overline{CAS})$  및 리드/라이트이네이블신호 $(\overline{WE})$  를 입력하는 타이밍콘트롤회로(TCC)에 의해 제어된다. 메모리어레이 $(MAO\sim MA7)$ 의 내부구성은 메모리어레이(MAO)로 대표하여 도시하고 있는 바와같이, 매트릭스상 워드선 및 비트선과의 교점에 각 메모리셀이 배치되어 있고, 제11도 및 제12도에 도시한 것과 같다.

각 센스앰프열(SAOO~SAOm, SA1O~SA1m, SA2O~SA2m, SA3O~SA3m)은 독립인 행디코더(DXO~DX7) 및 행드라이버(DRXO~DRX7)를 가지고, 동시에 선택되는 워드선은 입출력 복수의 비트구성의 비트수 이 상(예컨대, 4비트 입출력이면 16비트)이 선택된다.

여기서는, 4비트 입출력구성을 생각하고 있기 때문에 4개의 워드선이 동시에 선택된다. 예컨대, WL00, WL20, WL40, WL60이 동시에 선택된다.

한편, 각 센스앰프열은 공통의 열선택선(CLO~CLm)를 가지고, 동시에 선택되는 열선택선은 복수의 입출력 비트구성의 비트수 이상으로 선택된다.

여기서는 4비트 입출력구성을 생각하고 있기 때문에 4개의 열선택선이 동시에 선택된다. 예컨대CLO, CL1, CL2, CL3이 동시에 선택된다. 따라서 4(행)×4(열)로 합계 16비트의 데이타가 데이타래치(DL0~DL15)에 각 1비트씩 래치된다.

본 반도체 기억장치의 메모리셀 선택장치는 최종적으로 4비트를 출력하는 것이어서 16비트의 데이타의 4비트의 데이타를 꺼내지 않으면 안 된다. 이 경우에 있어서는 1개의 워드선 또는 열선택선이 고장일 경우에 ECC회로를 적응하기 위하여는 출력 4비트중 1비트만의 고장으로 끝나는 데이타의 꺼내기 방법을 하지 않으면 안 된다.

그를 위하여는 다른 워드선과 다른 열선택선에 의해 동시에 4비트의 데이타를 4회 꺼내면 좋다. 이 것을 수행하는 것이 데이타래치(DL2, DL3, DL1, DL0)에 접속된 데이타 실렉터(DS0), 데이타래치 (DL6, DL7, DL5, DL4)에 접속된 데이타 실렉터(DS1), 데이타래치(DL10, DL11, DL9, DL8)에 접속된 데이타 실렉터(DS2) 및, 데이타래치(DL14, DL15, DL13, DL12)에 접속된 데이타 실렉터(DS3)이다. 그리고, 데이타 실렉터(DS0, DS1, DS2, DS3)에 의해 16비트의 데이타에서 1타이밍에 4비트가 선택되고공통데이타버스에서 출력된다.

이 데이타 실렉터(DSO, DS1, DS2, DS3)로 행하여지는 데이타의 꺼내는 방법으로서는 시프티드다이어 고널방식을 들 수 있다. 제3도에 시프티드다이어고널방식의 데이타 억세스의 예를 3개 도시한다.

즉 제3도(a)로 도시한 데이타 래치(DLO~DL15)의 합계 16개의 데이타래치에서 4개의 데이타를 4회로나누어서 꺼내는 방식의 제1의 예를 제3도(b), 제2의 예를 동도(c), 제3의 예를 제3도(d)에 도시한다. 제3도(b)와 (c)와 시프트 방향이 서로 역일 뿐이고 본질적으로는 같고, (d)에 표시한 방향은 2비트씩 2회째와 3회째로 교차하고 있는 점에서 변형 시프티드다이어고널방식이라 말할 수 있다.

예컨대, 제3도(a)에 있어서 DLO, DL4, DL8, DL12의 1행째의 데이타는 동일의 열선택선(CL3)의 활성화에 의해 동시에 판독되는 내용이지만 그 열선택선(CL0)이 고장된 경우에는 이 제1행째의 데이타는모두 오류정보가 래치되게 된다.

그때문에 16비트중에서 4비트를 4회로 나누어서 판독하는 경우, 각 주기에 있어서, DLO, DL4, DL8, DL12의 고장데이타중 1비트만이 판독을 허락하고 고장데이타의 2비트이상의 판독을 방지하는 시프티드다이어고널방식이 제3도 (b), (c), (d)에 도시되어 있다.

예컨대(b)에서는 제1행째의 열선택선이 고장이라고 하면, 1회째의 타이밍에 있어서는(1, 1) 요소의 데이타는 오류상태이나, (2, 2), (3, 3) 및 (4, 4) 요소의 데이타는 정정된다. 따라서 1비트의 오류로 끝난다.

2회째의 타이밍에 있어서는 (1, 2)요소는 오류상태이고, (2, 3), (3, 4) 및 (4, 1)요소의 데이타는 올바르게 판독된다.

2회째의 타이밍으로는 (1, 3)요소의 판독데이타는 오류상태이고, (2, 4), (3, 1), (4, 2)요소의 판독데이타는 올바르다.

4회때의 타이밍에 있어서는 (1, 4)요소의 판독은 오류상태이고, (2, 1), (3, 2), (4, 3)요소의 판독에이타는 올바르다. 따라서 각 타이밍에 있어서는 1비트의 오류를 가지고 4비트의 데이타가 판독되고, 외부의 ECC회로에 의해 정정가능하기 때문에 4비트로 정정된 정보로 하는 것이 가능하게 된다. 따라서 각 타이밍에 있어서 ECC가 활성화하면 제3도(a)에 도시한 16비트중 제1행째의 4비트가 모두오류가 있어도 16비트같이 정정된 정보로소 ECC회로의 출력이 얻어진다. 즉 16비트중, 4비트가 정정된 것으로 된다. 제3(c) 및 (d)의 경우도 같다.

이상 요약하면 제2도에 있어서 각 메모리 셀어레이(MAO와 MA1, MA2와 MA3, MA4와 MA5, MA6과 MA7)중에서 임의의 워드선을 선택하고, 또한 공통열선택선중에서 임의의 열선택선을 선택함으로써 복수비트를 동시에 출력하며, 또한 그의 데이타중에서 당해 반도체 기억장치의 데이타 실렉터의 입력비트수에 적합하도록 각 메모리셀에서 1비트씩을 출력하도록 구성하였기 때문에 출력데이타의 전 비트가고장되는 일은 없고 워드선이나 열선택선의 고장중 반드시 1비트를 정지시키게 된다. 따라서, ECC회로를 사용하는 것이 가능하게 되고 복수의 비트 입출력 구성의 반도체 기억장치에 대해서 신뢰성이향상된다.

### 제2실시예

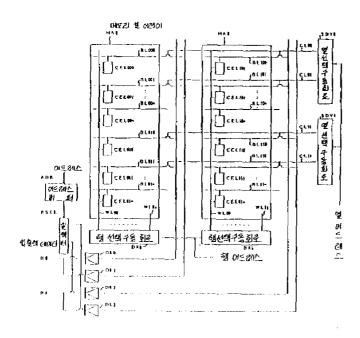

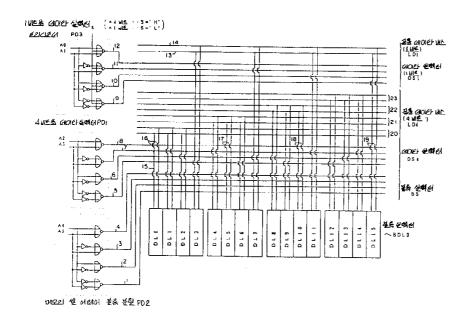

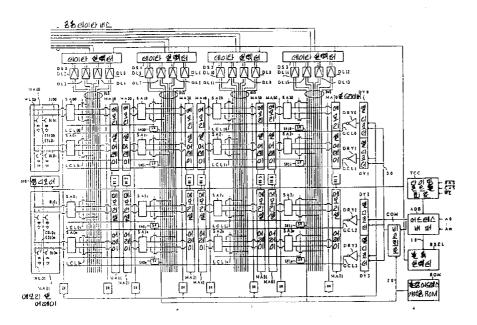

다음에 본 발명의 제2의 실시예를 제4도에 도시한다. 이 반도체 기억장치는 메모리 셀어레이가 MAO ~MA15의 16개의 메모리 셀어레이에서 이루는 DRAM에 본 발명을 적응한 예를 도시한 것이다. 도시 상 센스앰프는 각 메모리 셀어레이(MAO~MA15)의 각각의 메모리 셀어레이내에 존재하는 것으로서 도시를 생략하고 있다.

각 메모리 셀어레이(MAO~MA15)에는 각각 독립된 행디코더(DXO~DX15)와 행드라이버(DRXO~DRX15)가 배치되어 있다. 각 메모리 셀어레이(MAO~MA15)의 16개의 메모리 셀어레이의 4개의 블록으로 분할되고 1/4 블록동작하는 것이다.

이 분할동작은 2비트의 어드레스(A4, A5)가 입력되는 제2프리디코더(PD2)에 의해 블록실렉터(BS)를 선택하고, 그리고 제2프리디코더(PD2)의 출력을 행드라이버(DRXO~DRX15)에 입력하는 것으로 16회로 인 행드라이버중 1/4을 선택적으로 활성화하여 행해진다. 따라서 1/8록동작으로 하는 경우는 제2프 리디코더(PD2)의 입력어드레스를 3비트로 하면 좋다.

각 블록(MAO~MA3, MA4~MA7, MA8~MA11, MA12~MA15)의 각각에는 16비트를 래치하는 블록데이타래치(BDL0, BDL1, BDL2, BDL3)의 4개의 래치가 접속되어 있으나, 제2의 프리디코더(PD2)의 출력에 의해 1개의 블록데이타래치(예컨대, BDL0)만이 활성화되고 활성화된 블록에서 판독되는 16비트의 데이타를 블록실렉터(BS)를 통하여 데이타 실렉터(DS4)에 출력된다. 데이타 실렉터(DS4)로는 제1프리디코더(PD1)에 의해 16비트중에서 4비트를 선택하여 출력한다.

이상의 구성에 있어서, 제2프리디코더(PD2)에 의해 활성화된 각 메모리 셀어레이에 1개, 합계 4개의 워드선을 동시에 구동하고 또한 공통열선택선(예컨대 CL0, CL1, CL2, CL3)의 4개를 동시에 구동한다. 그러면 다른 워드선과 다른 공통열선택선과의 교점에서 활성화되는 메모리셀의 데이타, 합계 16비트의 데이타가 선택되어 있는 블록내에서 출력되며, 선택된 데이타래치회로(예컨대, BDL 0)에 래치되고, 다음에 데이타 실렉터(DS4)에서 4비트가 최종적으로 출력되어진다.

여기에 제5도에 데이타 실렉터(DS4)의 회로예를 도시한다.

이 회로는 변형시프티드다이어고널(제3도(d) 참조)에 적합한 예이다.

도면중 이 4비트 입력출구성의 장치를 본딩옵션이나 AL, 마스터슬라이스등의 수법에 의해 1비트 입력구성으로 하는 경우의 데이타 실렉터(DS1)와 프리디코더(PD3)의 예도 합쳐서 도시하고 있다.

이 프리디코더(PD3)는 2비트 어드레스(AO, A1)를 입력하고, 전환신호 S+H레벨일때 4비트 입력출구성, 전환신호 S+L 레벨일때 1비트 입출력구성으로 되도록 구성되고, 4비트의 데이타를 1비트로 변환하는 것이다. 블록데이타래치신호(예컨대 BDLO)는 16개의 데이타래치회로(DLO~DL15)에서 이루어지고 어드레스(AO~A3)에 의해 선택된다. 제5도의 데이타 실렉터의 동작을 보다 구체적으로 설명한다. 블록데이타래치(DLO에서 DL15)의 16비트의 데이타를 공통데이타버스(LD4)의 4비트의 판독의 선택을 데이타 실렉터(DS4)에 의해 선택하는 것이다. 그 선택방식의 제3도(d)의 시프티드다이어고널방식으로 되어있다. 우선, DLO에서의 DL15까지의 데이타는 블록데이타래치(BDLO)에 속하는 것이고, 다른 블록은 아니며, 이 BDLO의 데이타판독을 유효하게 선택하는 것이 블록실렉터(BS)이다. 이 블록선택을 행하는 데는 어드레스(A4, A5)가 같이 0일때 프리디코더(PD2)의 출력선(A, 3, 2, 1)중, 4만이 논리 1에 활성화되고 패스트랜지스터(15) 및 그의 우측에 있는 모든 패스트랜지스터를 온상태로 함으로써, DLO에서 DL15의 내용이 데이타 실렉터(DS4)에 유효하게 입력된다. 데이타 실렉터(DS4)로는 프리디코더(PD1)에 입력되는 어드레스신호(A2, A3)의 정보에 의해 그의 출력선(B, 7, 6, 5)중 1개만을 논리 1에 활성화함으로써 16비트중에서 4비트를 선택하는 것이 가능하게 되어있다. 프리디코더(PD1)로는 (A2, A3)이 (0, 0)일때 선8이 1로 되고, (A2, A3)이 (1, 0)일때 선7이 1로 되고, (A2, A3)이 (0, 1)일때 선6이 1로되고, (A2, A3)이 (1, 1)일때 선5이 1로 된다. 데이타 실렉터(DS4)로는 도면에 도시된 바와 같은 위치에 패스트랜지스터의 1의 경속되어 있다. 이와같은 트랜지스터의 배치에 의해 예컨대 선(B)이 논리 1의 경우에는 거기에 접속되어 있다. 이와같은 트랜지스터의 배치에 의해 예컨대 선(B)이 논리 1의 경우에는 거기에 접속되어 있다. 이와같은 트랜지스터의 배치에 의해 예컨대 보은 위치에 패스트랜지스터의 소오스, 드레인사이를 통하여 DLO, DL15의 4비트가 공통데이타버스(20, 21, 22, 23)에 각각 판독된다. 이 경우, 제3도(a)의 도면으로는 대각성분(DLO, DL5, DL10, DL15)이고 (d)의 도면의 제1회째의 도면에 대응한다.

선7이 1의 경우에는 DL1, DL4, DL11, DL14가 공통데이타버스(20, 21, 22, 23)에 판독된다. 이것은 제3도(a)에 있어서는 (2, 1)요소, (1, 2)요소, (4, 3)요서, (3, 4)요소에 대응하고, 이것은 제3(d)의 2회째의 도면에 대응한다. 선6이 1의 경우에는 DL2, DL7, DL8, DL13이 공통데이타버스(20, 21, 22, 23)에 판독된다. 이것은 제3도(a)에 있어서는 (3, 1)요소, (4, 2)요소, (1, 3)요소, (2, 4)요소에 대응하고, 이것은 제3도(d)의 3회째의 도면에 대응한다. 선5가 1의 경우에는 DL3, DL6, DL9, DL12가 공통데이타버스(20, 21, 22, 23)에 판독된다. 이것은 제3도(a)에 있어서는 (4, 1)요소, (3, 2)요소, (2, 3)요소, 및 (1, 4)요소에 대응하고, 이것은 제3도(d)의 4회째의 도면에 대응한다. 즉,데이타 실렉터(DS4)에 의해 시프티드다이어고널이 실현되고 있다.

이상은 16비트에서 4비트를 선택하는 방식이지만, 16비트에서 1비트를 선택하는 경우 데이타 실렉터 (DS1)에 의해 4비트의 공통데이타버스의 데이타선에 20, 21, 22, 23중 2개의 데이타를 또 1개의 공통데이타버스(LD1)에 접속하도록 제어된다.

이 선택은 프리디코더(PD3)에 의해 행하여지고, 어드레스신호(AO, A1)가 각각 (0, 0), (1, 0), (0, 1), (1, 1)일때, 제어선(S)이 0일때에 한하여 행선(12, 11, 10, 9)을 각각 활성화함으로써 행하여진다.

이상의 어드레스신호(A0~A3)는 내부어드레스이고, 칩외에 입력되는 어드레스신호(A0~A3)에 대하여 후술되는 바와같이 제7도에 도시되는 (a), (b)의 방식에 따라서 외부어드레스신호를 교체한, 즉 스크램블된 것에 의해 얻어진 것이다.

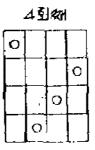

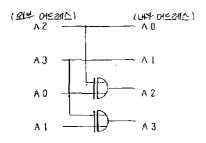

데이타래치의 선택의 관계를 제6도에 도시한다.

여기서, 메모리 셀어레이 분할에 사용하는 어드레스(A4, A5)는 지금 선택된 블록(예컨대 메모리 셀어레이(MA0~MA3), 블록데이타래치(BDL0))에 주목하고 있는 것이고, 제6도에는 도시하고 있지 않다. 이 데이타래치·매트릭스를 1비트 입출력구성으로 하는 경우에 있어서 세로에 주사, 즉 외부어드레스의 A0를 최하위비트, A3를 최상위비트로 하여 순차카운트 업했을 때 데이타 실렉터를 DL0, DL1, DL2, DL3, DL4, …DL15로 선택하는 경우와, 가로주사 즉 외부어드레스를 순차카운트업했을 경우, 데이타 실렉터를 DL0, DL4, DL8, DL12, DL1, …DL15로 선택하는 경우에 있어서의 외부어브레스와 내부어드레스와의 관계를 도시한 진리치표와 그것을 실현하는 어드레스 스크랩블러회로를 제7도(a) 및제7도(b)에 도시한다.

가로주사에 대하여 제7도(b)를 참조하여 구체적으로 설명한다.

A4, A5는 제5도에 있어서 (0, 0)으로 선4를 활성화하고, 제4도의 메모리 셀어레이(MAO, MA1, MA2, MA3)에서의 출력을 블록데이타래치(BDL0)에 가하고, 데이타래치(DL0~DL15)의 출력을 선택하는 것이다. 제6도에 도시하는 데이타래치·매트릭스를 가로에 주사했을 때, 데이타 실렉터를 DL0, DL4, DL8, DL12, DL1, …, DL15로 선택하고, 또한 1비트 입출력구성으로 하는 경우, 예컨대 내부어드레스(A3, A2, A1, A0)가 (0, 1, 1, 0)일때 제5도에 있어서는 A3, A2의 (0, 1)에 의해 출력선 7이 활성화되고 래치(DL1, DL4, DL11, DL14)가 선택된다. 또한 A1, A0의 (1, 0)에 의해 출력선 10에 의해 공통데이타버스(LD1)에는 데이타래치(DL11)의 내용이 출력된다. 즉, 칩의 외부에서 핀을 통하여 외부어드레스(11)를 지정하는 경우에는 외부어드레스는 그의 11에 대응하는 2진코드(1, 0, 1, 1)로 되서내부어드레스는 상술의(0, 1, 1, 0)으로 되고, 제5도의 데이타 실렉터의 회로로는 DL11의 내용이 판독된다. 즉, 1비트출력의 경우에는 외부의 어드레스의 어드레스치와 데이타래치의 번호와는 일치한다. 4비트출력의 경우는 내부어드레스(A0, A1)에 관계없이 예컨대(A3, A2)가 (0, 0)인 경우에는 데

이타래치의 DLO, DL5, DL10, DL15가 선택된다.

또 이것은 제3도(d)의 제1회째의 타이밍에 대응한다. 내부어드레스는 데이타 실렉터에 있어서 시프 티드다이어고널방식에 따라서 출력하도록 트랜지스터를 선택하기 위해 사용되는 것이다.

따라서 제3(d)의 제1회째의 타이밍의 판독 즉 DLO, DL5, DL10, DL15의 4비트의 정보를 외부어드레스를 사용하여 출력하기 위하여는 내부어드레스의 A3, A2가 0, 0일 필요가 있고, 제7도(b)의 진리치표에 의해 외부어드레스는 0000번지든가 0101번지든가 1010번지든가 1111번지의 어느 1개를 지정한다. 따라서 외부어드레스수는 4비트 출력의 경우는 1비트출력의 경우의 1/4로 감소한다.

세로주사의 경우는 내부어드레스와 데이타 실렉터 번호의 관계는 가로주사와 같고, 외부어드레스와 내부어드레스의 관계는 제7도(a)에 도시하게 된다.

이와같이 4비트 입출력구성의 다른 4개의 워드선과 다른 4개의 열선택선을 동시에 구동하여 4비트데 이타를 4회 꺼내는 방법은 제5도의 회로에 의해 가능하고, 또한 S단자를 본딩옵션, AL마스터슬라이 스등에 의해 1비트 입출력구성으로 한 경우에 있어서도 제7도와 같은 간단한 스크램블러에 의해 세 로가로의 주사가 가능하다는 것을 알 수 있다.

#### 제3실시예

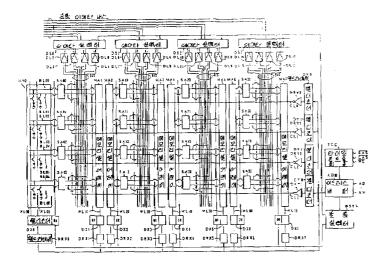

다음에 본 발명의 제3실시예를 제8도에 도시한다.

- 이 반도체 기억장치는 행방향에 한쌍으로 설치된 메모리 셀어레이(MA00와 MA01, MA10과 MA11, MA20과 MA21, …, MA70과 MA71)의 각 쌍에 있어서 중간에 행디코더(DX0, DX1, …, DX7)을 각각 개재시켜 행디코더의 공용화를 도모한 타입의 DRAM에 본 발명을 적응시킨 예이고, 제2도(제1실시예)의 변형이다. 같은 부분에 대하여는 동일부호를 부기하여 이하 설명한다.

- 이 반도체 기억장치에 있어서는 예컨대, 1개의 행선택 구동회로(DXO)에 의해 메모리 셀어레이(MAO 0)와 메모리 셀어레이(MAO1)의 동일 행어드레스신호(MAO)에 의해 각각 대응하는 워드선(WLOO)과 워드선(WLO1)이 선택되는 이 워드선(WLOO)에 접속되어 있는 메모리셀(CEL $\sim$ CELOi)에 접속되는 비트선(BLOO $\sim$ BLOi)에 대응하는 열선택선중, 예컨대 2개의 열선택선(CLO와 CL1)이 동시에 구동되고 2비트의 데이타가 데이타래치(DL2, DL3)에 출력된다. 또 워드선(WLO1)에 접속되어 있는 메모리셀(CELOj $\sim$ CELOm)에 접속되어 있는 비트선(BLOj $\sim$ BLOm)에 대응하는 열선택선중 예컨대, 2개의 열선택선(CL2와 CL3)이 동시에 구동되고 2비트의 데이타가 데이타래치(DL0, DL1)에 출력된다. 따라서 한쌍의 메모리셀어레이(MAOO와 MAO1)에서 합계 4비트의 데이타가 데이타래치(DL0 $\sim$ DL3)에 출력된다.

- 이 경우, 주의할 것은 선택된 워드선(WL00)과 워드선(WL01)과는 동일의 어드레스이기는 하나 동일의 워드선은 아니라는 점이다.

이하 동일한 각 메모리 셀어레이(MA)블록 쌍에서 4비트의 데이타가 출력되고 전 데이타래치로는 16 비트의 데이타가 출력된다. 이어서 이 16비트 데이타는 제3도의 시프티드다이어고널에 의해 각각의 열선택선에 접속된 4비트의 각각에서 1비트씩 합계 4비트의 데이타가 출력된다. 이 경우, 데이타래치(DLO~DL3)에 있어서 열선택선 또는 워드선의 고장이 생겼다 하여도 그의 일선택선 또는 워드선에 접속된 전 데이타는 고장이지만 최종적으로 출력되는 4비트 데이타에 있어서는 1비트의 데이타에 지나지 않는다. 따라서 ECC회로의 적응이 가능하다.

#### 제4실시여

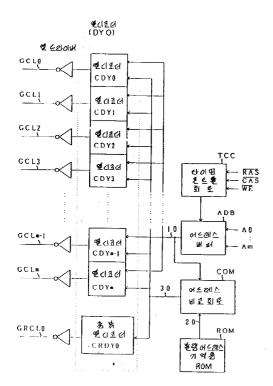

다음에 본 발명의 제4실시예를 제9도에 도시한다.

- 이 반도체 기억장치는 열선택선을 글로발열선택선(GCLO, GCL1, GCL2, …, GCLm)과 로컬열선택선(LCLOO, CLCOi, LCLOi, CLCOm과 LCL10, LCL1i, LCL1j, LCL1m)로 2중분할하고, 그 사이에 스위치(SWOO, SWOi, SWOj, SWOm과 SW10, SW1i, SW1j, SW1m)를 통하여 접속하고 있다. 또한 열선택구동회로(DYO, DY1, DY2, DY3)내에 불량을 일으킨 열선택선, 행디코더를 전환하는 예비의 열디코더(이하중복(redundant) 열 디코더라 부름, 제10도 참조)와, 각 메모리 셀어레이(MAOO~MAOM, MA10~MA1m)내에 불량 혹은 장해를 일으킨 메모리셀을 전환하는 예비의 메모리 셀어레이(이하 중복메모리 셀어레이라 부름, 도시하지 않음)를 여분으로 가지고 있고, 외부에서 입력된 어드레스(AO~Am)가 불량어드레스로 인식된 경우는 중복열디코더로 중복메모리셀을 선택하도록한 타입의 DRAM에 본 발명을 적응시킨 예이고, 제8도(제3실시예)의 변형이다. 같은 부분에 대하여는 동일부호를 부기하여 이하설명한다

- 이 반도체장치에 있어서는 행선택구동회로(DXO)에 의해 메모리 셀어레이(MAOO)와 메모리 셀어레이 (MAO1)의 각각에 대응하는 워드선(WLOO와 WLO1)이 선택되고 이 워드선(WLOO, WLO1)에 접속되어 있는 메모리셀(CELOO~CELOM)에서 각각에 대응하는 비트선(BLOO~BLOM)에 데이타가 출력된다. 여기까지의 동작은 제8도(제3의 실시예)와 같다. 한편 열선택선중 예컨대 4개의 글로발열선택선(GCLO, GCL1, GCL2, GCL3)이 동시에 선택되고 스위치(SWOO, SWOi, SWOj, SWOM)을 통하여 선택된 로컬열선택선 (LCLOO, LCLOi, LCLOj, LCLOM)에 의해 데이타가 데이타래치(DLO, DL1, DL2, DL3)에 래치된다. 제8도 (제3실시예)와 다른 것은 스위치(SWOO~SWOi)를 통하여 선택된 로컬열선택선(LCLOO~LCLOM)에 의해 데이타가 버스에 출력되고 데이타래치(DLO~DL3)에 래치되는 점이고, 이하 데이타 실렉터로 각 그룹에서 판독된 16비트의 데이타를 시프티드다이어고널방식(제3도(d) 참조)에 의해 각 그룹에서 1비트씩 제4비트의 데이타가 최종적으로 출력되는 것은 제8도(제3의 실시예)와 같고, 서로 다른 워드선과다른 로컬열선택선에 의해 출력되는 4비트이기 때문에 ECC회로의 적응이 가능하다는 것은 말할 필요도 없다.

- 이 로컬열선택선은 다층배선에서의 제3의 배선층을 사용하여 복수의 메모리 셀어레이(예컨대 MAOO, MA1O, MA2O)로 공용하고 있다. 물론 다층배선에서의 제2의 배선층을 사용하여 메모리 셀어레이를 공용하지 않아도 좋다.

이 반도체 기억장치의 열디코더(DYO~DY3)에는 중복열디코더(제10도 참조)를 각각 여분으로 가지고 있고, 또 메모리 셀어레이에도 여분으로 배치되어 있다.

또 중복메모리셀은 통상의 메모리셀의 구송뿐만 아니라 열선택선에 대응하는 메모리셀의 수도 같기 때문에 도면으로의 표시는 생략하고 있다.

제10도에는 1개의 열디코더(예컨대 DYO)와 불량어드레스로 전환하는 수단에 대하여 상세히 도시되어 있다. 불량을 일으키지 않는 메모리셀을 판독하는 정상어드레스가 입력된 경우에 동작하는 열디코 더(CDYO~CDYm)외에 불량어드레스가 입력되었을 때에 동작하는 중복열디코더(CRDYO)가 여분으로 배 치되어있다.

지금 외부에서 입력되는 어드레스신호(A0~Am)를 어드레스버퍼(ADB)로 증폭한 어드레스신호(10)와 미리 불량어드레스가 기억되어 있는 불량어드레스 기억용 ROM(ROM)에서 출력되는 불량어드레스신호(20)가 비교회로(COM)로 비교되고, 불일치했을 경우 즉 외부어드레스가 불량을 일으키지 않는 메모리셀을 판독하는 정상어드레스로 인식된 경우는, 어드레스버퍼(ADB)의 출력(10)에 따라서 글로발열선택선(GCL~GCLm)중 1개를 선택한다. 한편 외부에서 입력되는 어드레스신호(A0~Am)를 어드레스버퍼(ADB)로 증폭한 어드레스신호(10)와, 미리 불량어드레스가 기억되어 있는 불량어드레스기억용 ROM(ROM)에서 출력되는 불량어드레스신호(20)가 비교회로(COM)에서 비교되고, 일치했을 경우 즉 외부입력어드레스가 불량메모리셀을 판독하는 불량어드레스라고 인식된 경우는 비교회로(COM)의 출력신호(30)에서 각 열디코더(CDYO~CDYm)의 동작을 정지시키게 함과 동시에 중복디코더(CRDYO)를 활성화하여 중복글로발열선택선(GRCLO)을 선택한다.

요컨대 불량어드레스가 입력되었을 때는 예비의 중복디코더가 활성화하여 거기에 대응하는 예비의 중복메모리셀(도시하지 않음)이 선택된다. 따라서 외부에서 본 경우 마치 불량이 전혀 없는 것처럼 보인다. 제10도에서는 중복디코더는 단지 1회로만의 예이지만 복수회로를 구비하여도 좋은 것은 명 백하다.

이와같이 불랴메모리셀을 구제하기 위해 불량메모리셀에 대응하는 열선택선을 중복열선택으로 전환하는 방식은 행선택선에도 유효한 수단이다. 또 중복성의 효율을 높이는 수단으로서 메모리 셀어레이(예컨대 MAOO)단위로 불량어드레스를 검출하여 불량어드레스기억용 ROM에 기억시켜 불량어드레스이 판정을 각각 메모리 셀어레이에 대하여 행한다.

이 반도체 기억장치로 또한 글로발열선택선과 로컬열선택선을 연결하는 스위치(SW00~SW0m, SW10~SW1m)를 닫은 채로 각각의 메모리 셀어레이 단위에 중복이 발생되기 위한 경우, 열선택선이 복수의메모리 셀어레이에 대하여 공용하고 있기 때문에 중복의 효율이 저하한다고 하는 문제가 있다. 예컨대 글로발열선택선(GCL0)이 선택되고 그로부터 분기한 로컬열선택선(LCL00)이 메모리 셀어레이(MA00)내에서 불량을 일으켜 쇼트하였다고 한다. 그 경우 메모리셀이 정상인 메모리 셀어레이(MA40, MA50)도 불량으로 간주되어 메모리 셀어레이(MA40, MA50)가 선택되었을때도 중복열디코더(CRDYO)로전환하지 않으면 안 된다.

따라서, 이 반도체 기억장치로는 불량어드레스 기억용 ROM(ROM)의 출력(20)에 의해 글로발열선택선과 로컬열선택선을 연결하는 스위치를 개폐하도록 하고 있다.

예컨대 글로발열선택선(GCL0)이 선택되고 겨기에서 분기한 로컬열선택선(LCL00)이 메모리 셀어레이 (MA00)내에서 불량을 일으키고, 쇼트하여도 불량어드레스기억용 ROM(ROM)의 출력(20)에 의해 스치 (SW00)를 열고 글로발열선택선과 로컬열선택선을 분리한다. 이와같이 분리함으로서 글로발열선택선 (GCL0)에 대응한 메모리 셀어레이(MA00)의 불량어드레스를 선택한 경우는 중복열디코더의 전환이 행하여지지만 메모리 셀어레이(MA40)가 선택된 경우는 지금까지대로 글로발열선택선(GCL0)이 사용이가능하게 된다.

이상과 같이 열선택선을 2중화함으로써 2개의 열선택선이 고장되어도 본 발명에 따라서 1비트 오류의 출력을 얻을 수가 있고, ECC회로로 정정가능하게 된다.

이상은 열선택선의 2중화의 경우로 설명되었으며 또한 동시에 행선택선 즉 워드선을 2중화하면 더욱효과가 증가하게 된다. 또 스위치(SWOO~SWOm, SW10~SW1m)의 대신에 휴즈를 사용하여 불량어드레스에 대응한 휴즈를 절단함으로써 글로발열선택선과 로컬열선택선을 분리하여도 좋다.

이상과 같이 본 발명에 의하면 복수의 비트 입출력 구성의 반도체 기억장치에 있어서, 워드선, 열선 택선(비트선) 또는 메모리셀의 불량 혹은 결함에 의한 고장이 생겨도 복수의 비트의 모두가 고장되 는 일이 없이 반드시 1비트 오류로 할 수가 있고 ECC회로의 적응이 가능하므로 시스템의 신뢰성을 향상시킬 수가 있다.

## (57) 청구의 범위

# 청구항 1

복수의 메모리 셀어레이를 포함하며, 각각의 어레이가 복수의 워드선 및 비트선에 접속된 메모리셀을 갖는 반도체 기억장치에 있어서, 복수의 워드선을 동시에 활성화하는 행선택수단을 포함하고 ; 복수의 열선택선을 서로간에 독립적으로 동시에 활성화하는 복수의 열선택구동수단을 포함하며, 상기 열선택구동수단중 다른 하나에 각각의 상기 활성화된 열선택선이 접속되고 ; 동시에 활성화된 워드선과 열 서브선택선에 의해 선택된 메모리셀중에서 선택하는 복수의 데이타 실렉터 수단을 포함하며, 상기 데이타 실렉터 수단에 의해 선택되는 소정의 메모리셀중에서 상이한 워드선과 상이한 열서 브선택선에 각각의 상기 메모리셀이 연결되며, 상기 복수의 데이타 셀렉터 수단 각각에 연결되는 각각의 선택된 메모리셀은 소정의 데이타 실렉터 수단에 연결되는 선택된 메모리셀로써 동일한 워드선 및 동일한 열 서브선택선에 연결되는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 2

제1항에 있어서, 상기 행 선택수단은 공통 행 어드레스를 수신하는 복수의 행디코더를 포함하고, 각 각의 상기 열선택 구동수단은 공통 열 어드레스를 수신하는 열 디코더를 포함하는 것을 특징으로 하 는 반도체 기억장치.

## 청구항 3

제1항에 있어서, 각각의 상기 열선택선이 제1의 배선층을 형성하고, 상기 워드선이 제2배선층을 형성한 것을 특징으로 하는 반도체 기억장치.

#### 청구항 4

제1항에 있어서, 상기 열선택 구동수단에 의해 선택된 n개의 메모리셀 내용을 래치하는 래치수단을 추가로 구비하고, 상기 데이타 실렉터 수단은 상기 래치수단의 출력에 접속되어 상기 n개의 메모리셀 내용을 보다 n보다 작은 m개의 내용으로 선택하는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 5

제1항에 있어서, 상기 데이타 실렉터 수단에 의해 선택된 하나의 메모리셀의 데이타에 포함된 비트 오류를 정정하는 오류 정정회로를 추가로 포함한 것을 특징으로 하는 반도체 기억장치.

#### 청구항 6

제4항에 있어서, m 판독데이타는 n/m배의 시분할 방법으로 판독되며, n데이타가 판독되도록 사용가능한 것을 특징으로 하는 반도체 기억장치.

#### 청구항 7

제4항에 있어서, 상기 데이타 실렉터 수단은 상호간의 인접 행 및 인접열에 다이아고널 구성으로 위치된 트랜지스터의 온 및 오프 제어를 수행함으로써 데이타를 선택하고, 상기 다이아고널 구성은 어드레스 신호의 일부를 디코딩하여 취해진 신호를 사용함으로써 각각의 온 및 오프 제어동작으로 시프트되는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 8

제7항에 있어서, 16비트 메모리의 일부를 구성하는 4행 4열의 메모리셀에서 4비트 데이타가 출력되는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 9

제4항에 있어서, 상기 데이타 실렉터 수단의 선택을 제어하는 어드레스 신호는 외부어드레스를 변환하여 생성된 것을 특징으로 하는 반도체 기억장치.

# 청구항 10

제2항에 있어서, 행방향에 제공된 1쌍의 메모리셀 사이에 행 디코더가 제공되며, 그 행 디코더를 공용화하는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 11

제4항에 있어서, 상기 데이타 실렉터 수단은 n비트의 데이타에서 n보다도 작은 m1비트를 선택하는 제1데이타 실렉터와, m1비트 데이타에서 m1비트보다도 작은 m2데이타를 선택하는 제2데이타 실렉터를 구비하는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 12

제4항에 있어서, 상기 래치수단과 데이타 실렉터 수단과의 사이에 접속되며, 복수개의 데이타 래치 블록으로부터 1개의 데이타 래치블록을 선택하는 블록실렉터 수단을 추가로 포함하는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 13

제4항에 있어서, 상기 데이타 실렉터 수단에는 복수의 비트를 동시에 출력하는 복수개의 공통 데이 타버스선이 접속되고, 상기 공통데이타 버스선에는 1개의 공통데이타 버스선을 선택하는 1비트 출력 데이타 실렉터가 접속되는 것을 특징으로 하는 반도체 기억장치.

# 청구항 14

제1항에 있어서, 중복 메모미셀을 갖는 중복 열선택 회로를 추가로 포함하는 것을 특징으로 하는 반도체 기억장치.

### 청구항 15

제14항에 있어서, 외부 어드레스와 칩내부에 기억되어 있는 중복 어드레스를 비교하고, 일치한 경우는 중복 메모리셀을 선택하는 중복 선택수단을 활성화하고, 보통의 메모리셀을 선택하는 열선택수단을 비활성으로 하는 것을 특징으로 하는 반도체 기억장치.

## 청구항 16

제15항에 있어서, 외부어드레스와 칩내부에 기억되어 있는 중복 어드레스를 비교하고, 일치한 경우는 외부 어드레스에 대응하는 서브 선택선의 스위치를 오프로 하는 것을 특징으로 하는 반도체 기억 장치.

## 청구항 17

제1항에 있어서, 상기 반도체 기억장치는 복수의 비트의 입력 및 출력데이타선 구성을 형성하고, 입력 및 출력 데이타선 구성 이상의 개수의 상기 복수의 열선택선중 하나를 상호간에 독립적으로 동시에 선택하는 열선택수단을 추가로 구비하고, 데이타를 동시에 출력 또는 입력하는 복수의 메모리셀이 각각 다른 워드션에서 제공하는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 18

제1항에 있어서, 상기 행 선택수단은 중복 메모리셀을 선택하기 위해 행 선택회로를 포함하는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 19

제18항에 있어서, 외부 어드레스와 칩내부에 기억되어 있는 중복 어드레스를 비교하고, 일치한 경우는 중복 메모리셀을 선택하는 중복 행 선택선을 활성화하고, 보통의 메모리셀을 선택하는 행 선택회로를 비활성으로 하는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 20

제18항에 있어서, 외부 어드레스와 칩내부에 기억되어 있는 중복 어드레스를 비교하고, 일치한 경우는 외부 어드레스에 대응하는 서브선택선의 스위치를 오프로 하는 것을 특징으로 하는 반도체 기억 장치

#### 청구항 21

반도체 기억장치에 있어서, 각각의 복수의 워드선과 비트선에 접속되는 메모리셀을 가진 복수의 메모리 셀어레이를 포함하고; 각각의 메모리 셀어레이내에서 선택된 워드선상의 메모리셀에 연결되는 열선택선을 활성화하며 복수의 열 서브선택선을 상호간에 독립적으로 동시에 활성화하는 복수의 열선택 구동수단을 포함하고, 상기 열서브선택선이 그 서브선택선에서 스위치를 통하여 상기 열선택선에 접속되며 동시에 복수의 비트선을 선택하며, 각각의 상기 활성화된 서브선택선이 상기 열선택 구동수단중 다른 하나에 접속되며; 동시에 활성화된 워드선과 열서브선택선에 의해 선택된 메모리셀을 선택하는 데이타 실렉터 수단을 포함하고, 데이타 판독주기동안 상기 데이타 선택수단에 의해 선택된 소정의 메모리셀중에서 상이한 워드선과 상이한 열서브선택선상에 상기 판독주기동안 선택된 각각의 메모리셀이 연결되는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 22

제21항에 있어서, 상기 열선택선이 스위치를 통하여 접속되는 서브열선택선을 구비한 것을 특징으로 하는 반도체 기억장치.

#### 청구항 23

제22항에 있어서, 외부 어드레스와 중복 어드레스를 비교하고, 일치한 경우는 외부어드레스에 대응하는 서브선택선에 대한 스위치를 오프로 하는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 24

반도체 기억장치에 있어서, 매트릭스로 배선된 복수의 워드선과 비트선과의 교차점에 접속되는 메모리셀을 가진 복수의 어레이를 포함하고; 각각의 메모리 셀어레이에서 선택된 워드선상의 메모리셀에 연결되는 열선택선을 활성화하며 복수의 서브선택선을 상호간에 독립적으로 동시에 활성화하는 복수의 열선택 구동수단을 포함하고, 상기 서브선택선이 그 휴즈를 통하여 상기 열선택선에 접속되며, 동시에 복수의 비트선을 선택하며, 각각의 상기 활성화된 서브선택선이 상기 열선택 구동수단중 다른 하나에 접속되며; 동시에 활성화된 워드선과 열서브선택선에 의해 선택된 메모리셀을 선택하는 데이타 실렉터 수단을 포함하고, 데이타 판독주기동안 상기 데이타 선택수단에 의해 선택된 소정의메모리셀중에서 상이한 워드선과 열 서브선택선상에 상기 판독주기동안 선택된 각각의 메모리셀이 연결되는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 25

제24항에 있어서, 불량셀을 선택하는 서브열선택선은 휴즈를 단락하는 것을 특징으로 하는 반도체 기억장치.

# 청구항 26

반도체 기억장치에 있어서, 매트릭스로 배선된 복수의 워드선과 비트선에 접속되는 메모리셀을 가진 복수의 메모리 셀어레이를 포함하고 ; 복수의 열선택선을 상호간에 독립적으로 동시에 활성화하고 상기 각각의 메모리 셀어레이에서 동일한 워드선에 의해 메모리셀에 접속되는 비트선중에서 선택된 복수의 상기 비트선을 동시에 선택하는 복수의 수단을 포함하고, 각각의 상기 열선택선이 상기 복수 의 수단중 다른 하나에 접속되며; 동시에 활성화된 워드선과 열선택선에 의해 선택된 메모리셀을 선 택하는 데이타 실렉터 수단을 포함하고, 데이타 판독주기동안 상기 데이타 선택수단에 의해 선택된 소정의 메모리셀중에서 상이한 워드선과 상이한 열선택선상에 상기 판독주기동안 선택된 각각의 메 모리셀이 연결되는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 27

제26항에 있어서, 독립적으로 활성화된 열선택선은 복수의 메모리셀에 접속된 비트선의 데이타를 소오스드레인 경로를 통하여 버스에 전달하는 트랜스퍼 수단에 접속하는 것을 특징으로 하는 반도체기억장치.

#### 청구항 28

어레이에서 복수의 워드선과 복수의 비트선에 접속된 복수의 메모리셀을 가진 반도체 기억장치에 잇어서, 상기 워드선중 하나를 활성화함으로써 상기 워드선중 하나에 접속된 메모리셀에 기억되는 정보가 상기 비트선중 하나에 전달되는 경우에 복수의 열선택선을 상호간에 독립적으로 동시에 활성화하는 복수의 열선택수단과; 상기 복수의 열선택수단에 의해 n개의 메모리셀에 기억되는 정보를 래치하는 래치수단과; 상기 래치수단의 출력에 접속되어 n개의 메모리셀에서 m개에 기억되는 정보를 선택하는 데이타 선택수단을 포함하며, 데이타 판독주기동안 상기 데이타 선택수단에 의해 선택된 m개의 메모리셀중에서 상이한 워드선과 상이한 열선택선상에 상기 판독주기동안 선택된 각각의 상기 m개의 메모리셀이 연결되는 것을 특징으로 하는 반도체 기억장치.

#### 청구항 29

반도체 기억장치에 있어서, 병렬적으로 입력 및 출력하는 비트수 P보다도 많은 수의 메모리셀을동시에 선택하는 수단과; 상기 수 P보다도 많은 수의 상기 선택된 메모리셀을 데이타 버스에 접속하는 수단을 포함하며, 데이타 판독주기동안 상기 수단에 의해 선택된 소정의 메모리셀중에서 상이한 행선 및 상이한 열선상에 주기 판독주기동안 각각의 선택된 메모리셀이 연결되는 것을 특징으로 하는 반도체 기억장치.

# 도면

도면3-a

| enoier suxi d fo | DL4           | DL8    | D L 13 |

|------------------|---------------|--------|--------|

| 0 ()             | DU\$          | Dly    | DL I3  |

| DLZ              | D 1.6         | Ð L.10 | DLII   |

| DLI              | D L- <b>7</b> | OLH    | DL 15  |

# 도면3-b

도면3-c

도면3-d

CHOICEANXI

| D1.0                   | DL4                    | D1.3                   | D,L 1 2                |

|------------------------|------------------------|------------------------|------------------------|

| A3 A2 A1 A0<br>0 0 0 0 | A3 A2 A1 A0<br>0 1 0 1 | A3 A2 A1 A0<br>1 0 1 0 | A3 A2 A1 A0<br>1 1 1 1 |

| DLI                    | DL5                    | DL9                    | DL13                   |

| A3 A2 A1 A0<br>0 1 0 0 | A3 A2 A1 A0<br>0 0 0 1 | A3 A2 A1 A0<br>1 1 1 0 | A3 A2 A1 A0<br>1 0 1 1 |

| DL2                    | DL6                    | DLIO                   | DL14                   |

| A3 A2 A1 A0<br>1 0 0 0 | A3 A2 A1 A0            | ^3 ^2 ^1 ^0<br>0 0 1 0 | A3 A2 A1 A0<br>0 1 1 1 |

| DL3                    | DL7                    | DLII                   | DL15                   |

| A3 A2 A1 A0<br>L + O O | A3 A2 A1 A0<br>1 0 0 1 | A3 A2 A1 A0<br>0 1 1 0 | A3 A2 A1 A0<br>0 0 1 1 |

# 도*면7a*

(a) CHOICH ZHÀISH MISE PAPSECON

| A3  | /<br>八之 | 0152<br>1 A | V ()   |    |    | и <u>с</u> ен<br>Л 1 | <u>Λ</u> θ | संबं (10 हर 24 रा)<br>सं <u>इ</u> |

|-----|---------|-------------|--------|----|----|----------------------|------------|-----------------------------------|

| 0   | 0       | 0           | 0      | 0  | 0  | 0                    | 0          | 0                                 |

| 0   | 0       | 0           | l<br>C | 0  | 1  | 0                    | 0          | } 2                               |

| ŏ   | Ü       | ì           | 1      | lí | i  | ŏ                    | Ö          | 3                                 |

| 0   | 1       | 0           | 0      | 0  | 1  | 0                    | 1          | 4                                 |

| 0   | 1       | 0           | 1      | 0  | 0  | 0                    | l          | 5                                 |

| 0   | 1       | ı           | 0      | ì  | 1  | 0                    | 1          | 6                                 |

| 0   | 1       | •           | i      | [1 | 0  | 0                    | I          | 7                                 |

| 1   | Ü       | 0           | 0      | 1  | () | 1                    | 0          | 8                                 |

| 1   | Ð       | 0           | Ì      | l  | l  | 1                    | 0          | 9                                 |

| 1   | 0       | l           | 0      | t) | 0  | 1                    | 0          | 10                                |

| 1   | D       | ì           | j      | 10 | Ţ  | 1                    | 0          | 1 1                               |

| 1   | į.      | ()          | 0      | 1  | 1  | 1                    | 1          | 1.2                               |

| 1 1 | 1       | G.          | 1      | 1  | 0  | 1                    | Ţ          | 1.3                               |

| 1   | l       | l           | i)     | 1) | 1  | Ţ                    | ]          | 1.4                               |

| 1   | _ t     | l           | ì      | D  | 0  | 1                    | - 1        | 1.5                               |

# 도면7b

## (b) GIOIET EHZISI MERZHECON

|                                                          |                     | 11A                                            | / <u>^</u>                           |                                      | 学 (<br>ハ2                            |                                                | AU<br>AU                                       | ल्बा लावार आया<br>म् इ                            |

|----------------------------------------------------------|---------------------|------------------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|------------------------------------------------|------------------------------------------------|---------------------------------------------------|

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1 | 0 0 0 0 1 1 1 0 0 0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>1<br>0<br>1<br>0<br>1<br>0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>3<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 0<br>4<br>8<br>12<br>1<br>5<br>9<br>1 3<br>2<br>6 |

| 1 1 1                                                    | 0<br>1<br>1<br>1    | 1<br>0<br>0<br>1<br>1                          | 1<br>0<br>1<br>6<br>1                | 0<br>1<br>0<br>6                     | 1<br>0<br>1<br>0                     | 1<br>0<br>0<br>1<br>1                          | )<br>0<br>1<br>0                               | 1 4<br>3 7<br>4 1<br>1 5                          |

(名1171包)