## (19) 中华人民共和国国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 113242344 A (43) 申请公布日 2021. 08. 10

- (21) 申请号 202110680651.X

- (22) 申请日 2021.06.18

- (71) 申请人 0PP0广东移动通信有限公司 地址 523860 广东省东莞市长安镇乌沙海 滨路18号

- (72) 发明人 杨鑫

- (74) 专利代理机构 广州华进联合专利商标代理 有限公司 44224

代理人 熊文杰

(51) Int.CI.

HO4M 1/02 (2006.01)

**HO4N** 5/225 (2006.01)

HO4N 5/341 (2011.01)

HO4N 5/355 (2011.01)

HO4N 5/378 (2011.01)

权利要求书4页 说明书17页 附图17页

#### (54) 发明名称

图像传感器、摄像头组件和移动终端

#### (57) 摘要

本申请涉及一种图像传感器、摄像头组件和移动终端,其中,图像传感器,包括:像素阵列,像素阵列包括多个像素,每个像素包括多个子像素,其中,同一像素中的各子像素共享同一浮动扩散区;像素包括配置有多个输出端的像素电路,像素电路用于将同一像素中至少一个光电转换元件产生的电荷转移到浮动扩散区进行累积,并根据累积的电荷选择像素电路的至少一个输出端输出浮动扩散区中电荷对应的模拟信号;多个第一转换电路,第一转换电路,用于对同一像素电路的输出的各模拟信号进行模数转换,并和像素电路共同基于全分辨率输出模式或第一级合并输出模式读出转换后的数字信号,可以适用于不同的成像场景,并在不同场景下均能够具有好的成像质量。

1.一种图像传感器,其特征在于,包括:

像素阵列,所述像素阵列包括多个像素,每个所述像素包括多个子像素,其中,同一所述像素中的各所述子像素共享同一浮动扩散区;所述像素包括配置有多个输出端的像素电路,所述像素电路包括多个与所述子像素一一对应的光电转换元件,所述像素电路用于将同一所述像素中至少一个所述光电转换元件产生的电荷转移到所述浮动扩散区进行累积,并根据累积的电荷选择所述像素电路的至少一个输出端输出所述浮动扩散区中所述电荷对应的模拟信号;

多个第一转换电路,分别与多个所述像素电路的多个输出端对应连接,所述第一转换电路,用于对同一所述像素电路的输出的各所述模拟信号进行模数转换,并和所述像素电路共同基于全分辨率输出模式或第一级合并输出模式读出转换后的数字信号,其中,所述全分辨模式用于以所述子像素为单位的读出所述数字信号,所述第一级合并输出模式用于以所述像素为单位的读出所述数字信号。

- 2.根据权利要求1所述的图像传感器,其特征在于,每个所述像素包括n\*m个呈矩阵分布所述子像素,每个所述像素均配置有m条列控制线,所述像素电路包括m个输出端,其中,所述m个输出端与m条列控制线——对应连接,所述m条列控制线还与分别与所述第一转换电路连接,以形成m个输出通路,所述像素电路还用于根据累积的电荷选择导通至少一个所述输出通路输出所述浮动扩散区中所述电荷对应的模拟信号;其中,n、m中的一个为大于1的正整数,n、m中的另一个为大于或等于1的正整数。

- 3.根据权利要求2所述的图像传感器,其特征在于,m=n=2,各所述像素均包括2\*2个子像素,其中,每个所述像素电路包括第一输出端、第二输出端,且每个所述像素配置有第一列控制线和第二列控制线,其中,第一输出端经第一开关与所述第一列控制线连接以形成第一输出通路,所述第二输出端经第二开关与所述第二列控制线连接以形成第二输出通路。

- 4.根据权利要求2所述的图像传感器,其特征在于,所述第一转换电路包括:

m个第一转换单元,分别与m条列控制线一一对应连接,所述第一转换单元包括模数转换器,与所述列控制线连接,用于对接收的模拟信号进行模数转换以输出数字信号;

第一开关单元,分别与各所述第一转换单元连接;其中,当所述第一开关单元导通时, 所述第一转换电路对m个所述数字信号执行平均操作。

5.根据权利要求4所述的图像传感器,其特征在于,所述第一转换单元还包括:

存储单元,与所述第一开关单元连接,用于将位于同一列的各所述像素对应所述数字信号进行分区存储;

第二开关单元,与所述存储单元连接,用于对分区存储的所述数字信号进行平均操作。

- 6.根据权利要求5所述的图像传感器,其特征在于,m=n=2,所述存储单元包括第一电容、第二电容,所述第二开关单元包括两个开关,其中,两个所述开关中的一个的第一端与所述模数转换器的输出端连接,所述两个所述开关中的一个的两个第二端分别与所述第一电容的第一端、所述第二电容的第一端连接,两个所述开关中的另一个连接于所述第一电容的第二端、所述第二电容的第二端。

- 7.根据权利要求1所述的图像传感器,其特征在于,所述第一级合并输出模式包括相加模式、数字平均模式和混合模式中的至少一种,其中,

所述相加模式为:对同一像素中的所有子像素在所述浮动扩散区累积的总电荷进行模数转换后读出:

所述数字平均模式为:对同一像素中各子像素分时产生的各电荷分别进行模数转换, 并对转换后的各所述数字信号进行平均后读出:

所述混合模式为:对同一像素中第一部分子像素在所述浮动扩散区累积的第一模拟信号经过模数转换后输出的第一数字信号,和对同一像素中第二部分子像素在所述浮动扩散区累积的第二模拟信号经过模数转换后输出第二数字信号进行平均后读出;其中所述第一部分子像素和所述第二部分子像素共同构成所述像素。

8.根据权利要求7所述的图像传感器,其特征在于,

若所述浮动扩散区在同一曝光时间内累积的所述电荷为一个所述光电转换元件的电荷,则所述像素电路导通所有所述输出端,以将各所述光电转换元件的电荷对应的模拟信号分时输出至所述第一转换电路,以使所述第一转换电路对多个所述模拟信号执行所述全分辨率输出模式或所述数字平均模式的操作:

若所述浮动扩散区在同一曝光时间内累积的所述电荷为同一像素中所有所述光电转换元件的电荷,则所述像素电路导通任一所述输出端,以将累积的所述电荷对应的模拟信号输出至所述第一转换电路,以使所述第一转换电路对所述模拟信号执行所述相加模式的操作:

若所述浮动扩散区在第一曝光时间内累积的所述电荷为所述第一部分子像素对应的 所述光电转换元件累积的第一累积电荷,或,所述浮动扩散区在第二曝光时间内累积的所 述电荷为所述第二部分子像素的对应的所述光电转换元件累积的第二累积电荷,则所述像 素电路导通多个所述输出端,以分别将所述第一累积电荷、第二累积电荷对应的模拟信号 分时输出至所述第一转换电路,以使所述第一转换电路对所述模拟信号执行所述混合模式 的操作。

9.根据权利要求1-3任一项所述的图像传感器,其特征在于,所述像素阵列包括呈一维阵列设置的多个像素单元,在所述像素单元中包括2\*2阵列设置的第一像素、第二像素、第三像素和第四像素,其中,所述第一像素和第四像素为全色像素,且设置在第一对角线方向,所述第二像素和第三像素为彩色像素,且设置在第二对角线方向;所述彩色像素具有比所述全色像素更窄的光谱响应,所述第一对角线方向与所述第二对角线方向不同;其中,

同一像素单元中,位于同一列的两个所述像素共用同一所述第一转换电路,且位于同一行的两个所述像素的所述第一转换电路连接,彼此连接的两个所述第一转换电路还用于基于第二级合并输出模式读出数字信号,其中,所述第二级合并输出模式用于以所述第二对角线方向上的所有所述像素为单位的读出所述数字信号。

10.根据权利要求9所述的图像传感器,其特征在于,所述像素包括2\*2阵列排布的4个子像素,其中,所述像素单元配置有第一列控制线、第二列控制线、第三列控制线和第四列控制线,其中,所述像素单元还包括设置在两个所述第一转换电路输出端的第三开关单元,其中,所述第三开关单元包括两个开关,一个所述开关连接在所述第一列控制线和所述第三列控制线之间,另一个所述开关连接在所述第二列控制线和所述第四列控制线之间。

11.根据权利要求10所述的图像传感器,其特征在于,同一所述像素单元的两个所述第一转换电路包括:四个模数转换器以及设置在所述模数转换器输出端的两个第三开关,其

中,四个所述模数转换器的输入端分别与四个所述列控制线连接,两个第三开关中的一个连接在所述第一列控制线和所述第二列控制线之间,两个第三开关中的另一个连接在所述第三列控制线和所述第四列控制线之间。

12.根据权利要求10所述的图像传感器,其特征在于,所述像素阵列包括呈阵列设置的多个像素组,各所述像素组包括呈2\*1阵列设置的第一像素单元和第二像素单元,其中,所述第一像素单元对应的第一转换电路与第二像素单元对应的第一转换电路连接;其中,所述像素组还包括:

开关阵列,分别与各所述列控制线、各所述第一转换电路连接,用于选择导通所述第一像素单元、第二像素单元中各所述像素电路的任一所述输出端与目标模数转换器组之间的通路,其中,所述目标模数转换器组包括第一像素单元对应的一个模数转换器,以及第二像素单元对应的一个模数转换器。

13.根据权利要求12所述的图像传感器,其特征在于,同一所述像素组被配置有第一列控制线组和第二列控制线组,各所述列控制线组均包括四个所述列控制线;同一所述像素组包括第一模数转换器组和第二模数转换器组,各所述模数转换器组均包括四个模数转换器,其中,

所述开关阵列用于选择导通任所述第一列控制线组中任一列控制线与所述第一模数转换器组中一个所述模数转换器或所述第二模数转换器组中一个所述模数转换器之间的通路;还用于选择导通所述第二列控制线组中任一列控制线与所述第一模数转换器组中一个所述模数转换器或所述第二模数转换器组中一个所述模数转换器之间的通路;

所述像素组还包括设置在所述第一转换电路输出端的第五开关单元,其中,所述第五 开关单元连接所述第一模数转换器组的一个数模转换器和所述第二模数转换器组的一个 模数转换器;其中,当所述第五开关单元导通时,用于执行对连接的两个所述模数转换器输 出的所述数字信号的平均操作。

- 14.根据权利要求12所述的图像传感器,其特征在于,当所述多个像素组沿像素阵列的列方向一维阵列排布时,每一行的所述像素组采用并行读出方式读出各所述像素组的数字信号,所述并行读出方式为每一行的所述像素组彼此独立读出各所述像素组的数字信号。

- 15.根据权利要求1-3任一项所述的图像传感器,其特征在于,所述像素阵列包括呈一维阵列设置的多个像素单元,在所述像素单元中包括2\*2阵列设置的第一像素、第二像素、第三像素和第四像素,其中,所述第一像素和第四像素为全色像素,且设置在第一对角线方向,所述第二像素和第三像素为彩色像素,且设置在第二对角线方向;所述彩色像素具有比所述全色像素更窄的光谱响应,所述第一对角线方向与所述第二对角线方向不同;其中,

- 同一像素单元中,位于同一行的两个所述像素的所述第一转换电路彼此连接。

- 16.根据权利要求1所述的图像传感器,其特征在于,所述第一级合并输出模式包括模拟平均模式,所述图像传感器还包括:

- 第二转换电路,分别与像素电路的多个输出端、第一转换电路的输入端连接,用于对所述像素电路输出的多个所述模拟信号执行模拟平均模式的操作。

- 17.根据权利要求1所述的图像传感器,其特征在于,所述像素电路还包括:

- 多个转移晶体管,分别与多个光电转换元件连接,用于将各所述光电转换元件产生的 电荷转移到所述浮动扩散区;

读出电路,包括输入端和多个输出端,其中,所述读出电路的输入端与所述浮动扩散区连接,用于将转移到所述浮动扩散区中的电荷经多个所述输出端中的至少一个输出。

18.一种摄像头组件,其特征在于,包括:

镜头;及

权利要求1-17任意一项所述的图像传感器,所述图像传感器能够接收穿过所述镜头的 光线。

19.一种移动终端,其特征在于,包括:

壳体;及

权利要求18所述的摄像头组件,所述摄像头组件与所述壳体结合。

## 图像传感器、摄像头组件和移动终端

#### 技术领域

[0001] 本申请涉及影像技术领域,特别是涉及一种图像传感器、摄像头组件和移动终端。

### 背景技术

[0002] 手机等终端中可以设置有摄像头以实现拍照功能。摄像头内可以设置用于接收光线的图像传感器。

[0003] 随着对图像传感器需求的增加,正在开发用于提高图像传感器生成的图像的质量的技术。一般的图像传感器在高亮场景下和暗光场景下成像质量难以兼顾。

## 发明内容

[0004] 本申请实施例提供了一种图像传感器、摄像头组件和移动终端,可以适用于不同的成像场景,并在不同场景下均能够具有好的成像质量。

[0005] 一种图像传感器,包括:

[0006] 像素阵列,所述像素阵列包括多个像素,每个所述像素包括多个子像素,其中,同一所述像素中的各所述子像素共享同一浮动扩散区;所述像素包括配置有多个输出端的像素电路,所述像素电路包括多个与所述子像素——对应的光电转换元件,所述像素电路用于将同一所述像素中至少一个所述光电转换元件产生的电荷转移到所述浮动扩散区进行累积,并根据累积的电荷选择所述像素电路的至少一个输出端输出所述浮动扩散区中所述电荷对应的模拟信号;

[0007] 多个第一转换电路,分别与多个所述像素电路的多个输出端对应连接,所述第一转换电路,用于对同一所述像素电路的输出的各所述模拟信号进行模数转换,并和所述像素电路共同基于全分辨率输出模式或第一级合并输出模式读出转换后的数字信号,其中,所述全分辨模式用于以所述子像素为单位的读出所述数字信号,所述第一级合并输出模式用于以所述像素为单位的读出所述数字信号。

[0008] 一种摄像头组件,包括:

[0009] 镜头:及

[0010] 前述的图像传感器,所述图像传感器能够接收穿过所述镜头的光线。

[0011] 一种移动终端,包括:

[0012] 壳体;及

[0013] 前述的摄像头组件,所述摄像头组件与所述壳体结合。

[0014] 上述图像传感器、摄像头组件和移动终端,图像传感器包括像素阵列和多个第一转换电路。其中,所述像素阵列包括多个像素,每个所述像素包括呈矩阵排布的多个子像素,其中,同一所述像素中的各所述子像素共享同一浮动扩散区,像素的像素电路用于将同一所述像素中至少一个所述光电转换元件产生的电荷转移到所述浮动扩散区进行累积,并根据累积的电荷选择所述像素电路的至少一个输出端输出所述浮动扩散区中所述电荷对应的模拟信号;第一转换电路可用于对同一所述像素电路的输出的各所述模拟信号进行模

数转换,并基于全分辨率输出模式或第一级合并输出模式读出转换后的数字信号,其中,所述全分辨模式用于以所述子像素为单位的读出所述数字信号,所述第一级合并输出模式用于以所述像素为单位的读出所述数字信号。也即本申请提供的图像传感器可以提供多种输出模式,示例性的,在暗光下成像时可采用第一级合并输出模式实现以像素为单位的合并输出,得到信噪比较高的图像,而在光线较为充足的场景下,可采用全分辨率输出模式实现以子像素为单位的单独输出,从而得到清晰度和信噪比均较高的图像。

#### 附图说明

[0015] 为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

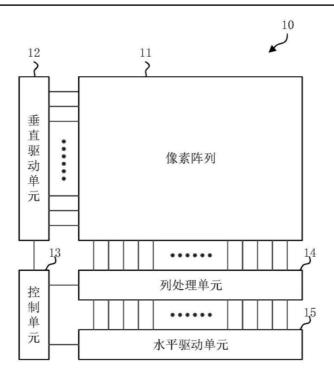

[0016] 图1为一个实施例中图像传感器的示意图:

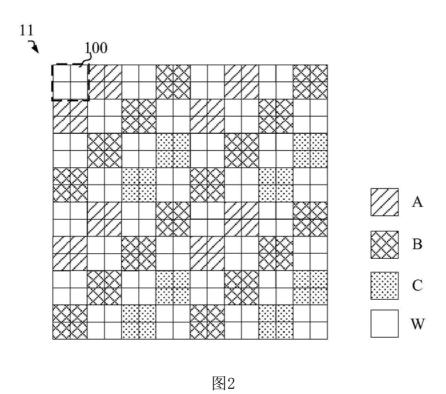

[0017] 图2为一个实施例中像素阵列的排布示意图;

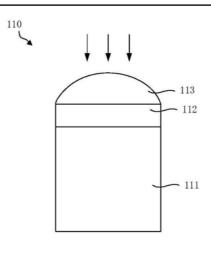

[0018] 图3为一个实施例中像素的截面示意图;

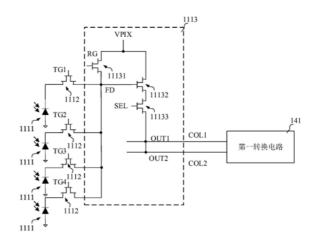

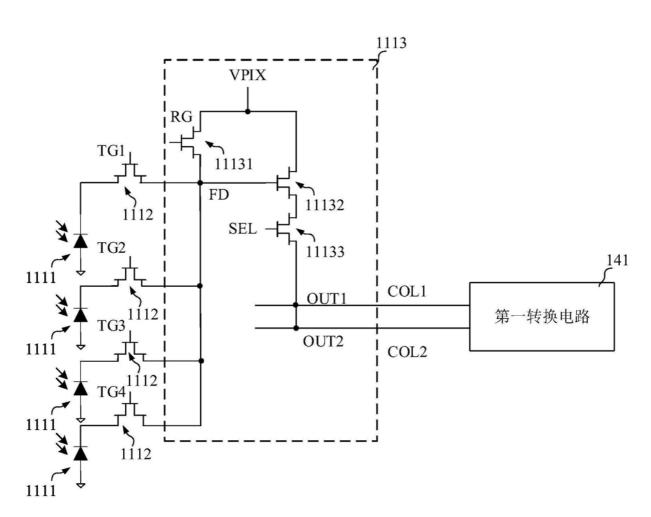

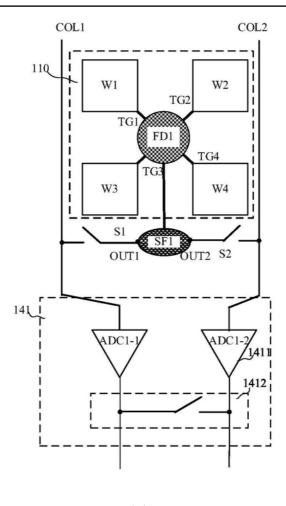

[0019] 图4为一个实施例中像素电路的电路示意图;

[0020] 图5为另一个实施例中像素电路的电路示意图;

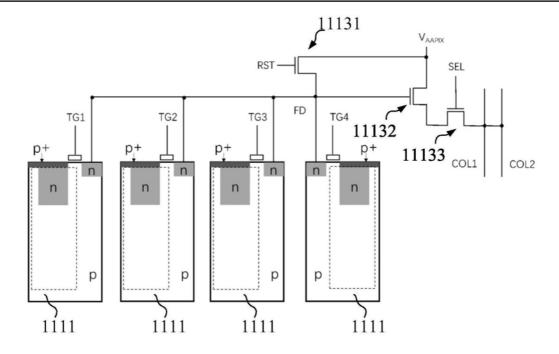

[0021] 图6为一个实施例中像素的第一转换电路的电路图;

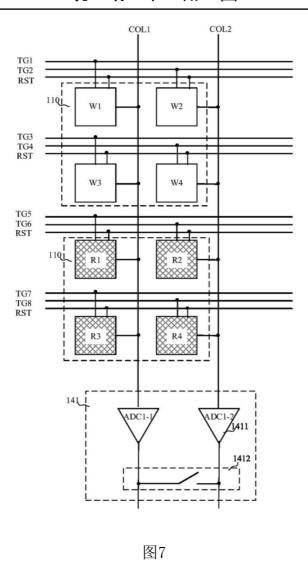

[0022] 图7为一个实施例中两个像素共用同一第一转换电路的电路图:

[0023] 图8至图10为一些实施例中像素基于第一转换电路的工作原理图:

[0024] 图11为一个实施例中像素的第二转换电路的电路图;

[0025] 图12为一个实施例中像素阵列中最小重复单元的排布示意图:

[0026] 图13为一个实施例中像素单元的电路示意图;

[0027] 图14至图15为一些实施例中像素单元基于第一转换电路的工作原理图:

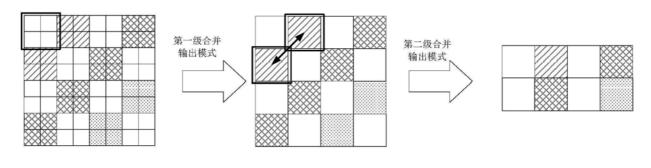

[0028] 图16为一个实施例中由第一级合并输出模式转换为第二级合并输出模式的转换示意图:

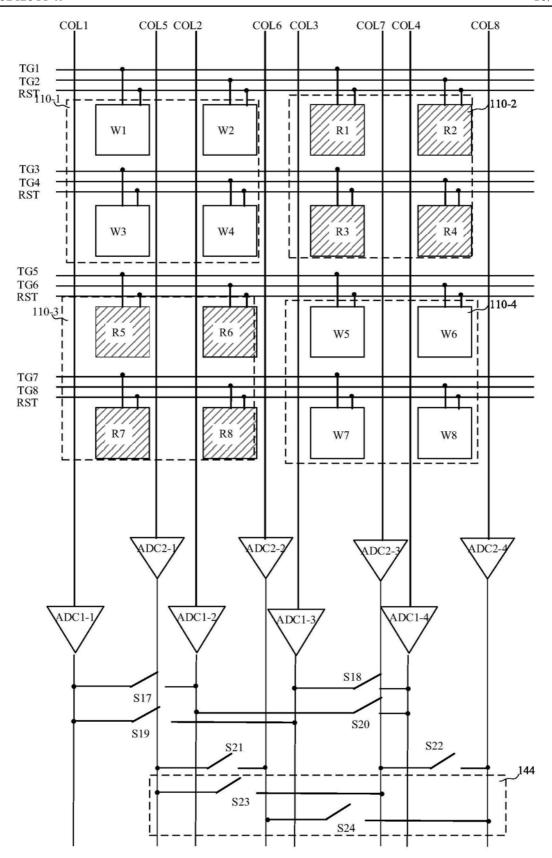

[0029] 图17为另一个实施例中像素单元的电路示意图:

[0030] 图18为另一个实施例中像素单元的基于第一转换电路的工作原理图:

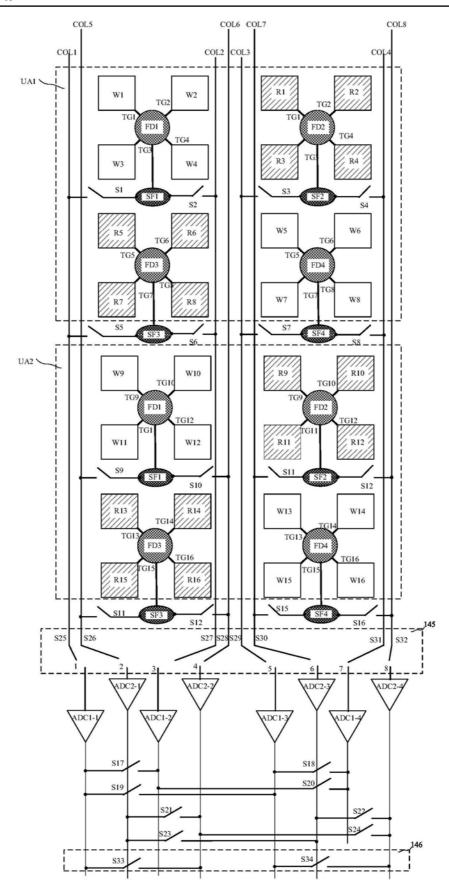

[0031] 图19为一个实施例中像素组的电路示意图:

[0032] 图20为另一个实施例中像素组的基于第一转换电路的工作原理图;

[0033] 图21为一个实施例中摄像头组件的示意图:

[0034] 图22为一个实施例中的移动终端的示意图。

#### 具体实施方式

[0035] 为了使本申请的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本申请进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本申请,并不用于限定本申请。

[0036] 可以理解,本申请所使用的术语"第一"、"第二"等可在本文中用于描述各种元件,但这些元件不受这些术语限制。这些术语仅用于将第一个元件与另一个元件区分。举例来

说,在不脱离本申请的范围的情况下,可以将第一转换电路称为第二转换电路,且类似地,可将第二转换电路称为第一转换电路。第一转换电路和第二转换电路两者都是转换电路,但其不是同一转换电路。

[0037] 如图1所示,本申请实施例提供一种图像传感器。图像传感器10包括像素阵列11、垂直驱动单元12、控制单元13、列处理单元14和水平驱动单元15。

[0038] 其中,图像传感器10可以采用互补金属氧化物半导体(CMOS,Complementary Metal Oxide Semiconductor)感光元件或者电荷耦合元件(CCD,Charge-coupled Device)感光元件。

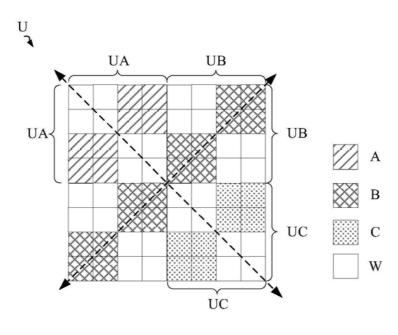

[0039] 如图2所示,像素阵列11包括以阵列形式二维排列(即二维矩阵形式排布)的多个像素110,每个像素110可包括多个子像素。具体的,每个像素110中可包括n\*m个子像素。其中,n、m中的一个为大于或等于1的正整数,m、n中的另一个为大于或等于2的正整数,其中,n可以理解为同一像素110中子像素的行数、m为同一像素110中子像素的列数。示例性的,每个像素110包括4个子像素,其4个子像素以2\*2阵列排布,也即,m=n=2。在本申请实施例中,对m、n的取值范围不做进一步的限定。

[0040] 同一像素110包括的各子像素的颜色均相同,各子像素可以为全色子像素W、第一颜色子像素A、第二颜色子像素B、第三颜色子像素C中的一种。示例性的,第一颜色子像素A可以为红色子像素R;第二颜色子像素B可以为绿色子像素G;第三颜色子像素C可以为蓝色子像素Bu。

[0041] 垂直驱动单元12包括移位寄存器和地址译码器。垂直驱动单元12包括读出扫描和复位扫描功能。读出扫描是指顺序地逐行扫描单位像素110,从这些单位像素110逐行地读取信号。例如,被选择并被扫描的像素110行中的每一像素110输出的信号被传输到列处理单元14。复位扫描用于复位电荷,光电转换元件的光电荷被丢弃,从而可以开始新的光电荷的积累。

[0042] 例如,由列处理单元14执行的信号处理是相关双采样(CDS)处理。在CDS处理中,取出从所选像素110行中的每一像素110输出的复位电平和信号电平,并且计算电平差。因而,获得了一行中的像素110的信号。列处理单元14可以具有用于将模拟像素110信号转换为数字格式的模数(A/D)转换功能,以及对模数转后的多个数字信号进行平均操作的功能。

[0043] 例如,水平驱动单元15包括移位寄存器和地址译码器。水平驱动单元15顺序逐列扫描像素阵列11。通过水平驱动单元15执行的选择扫描操作,每一像素110列被列处理单元14顺序地处理,并且被顺序输出。

[0044] 例如,控制单元13根据操作模式配置时序信号,利用多种时序信号来控制垂直驱动单元12、列处理单元14和水平驱动单元15协同工作。

[0045] 如图3所示,像素110包括像素电路111、滤光片112、及微透镜113。沿像素110的收光方向,微透镜113、滤光片112、及像素电路111依次设置。微透镜113用于汇聚光线,滤光片112用于供某一波段的光线通过并过滤掉其余波段的光线。像素电路111用于将接收到的光线转换为电信号,并将生成的电信号提供给图1所示的列处理单元14。

[0046] 如图4和图5所示,图4和图5中像素电路111可应用在图2所示的像素阵列11内的每个像素110中。下面结合图2至图5对像素电路的工作原理进行说明。

[0047] 像素电路111用于将同一所述像素110中至少一个所述光电转换元件1111累积产

生的电荷转移到所述浮动扩散区FD,并根据累积的电荷选择导通至少一个所述输出端输出 所述浮动扩散区FD中所述电荷对应的模拟信号。像素电路111包括多个与子像素一一对应 的光电转换元件1111、多个转移晶体管1112以及一个读出电路1113。

[0048] 光电转换元件1111的数量及排布方式与子像素的数量、排布方式相同。每个光电转换元件1111根据入射在其上的光的强度将光转换为电荷。转移晶体管1112的数量与光电转换元件1111的数量相等。多个转移晶体管1112分别与多个光电转换元件1111—一对应连接。同一像素110中的多个光电转换元件1111共用像素电路111中的浮动扩散区FD。例如,光电转换元件1111包括光电二极管,光电二极管的阳极例如连接到地,光电二极管的阴极经由转移晶体管1112连接到浮动扩散区FD,转移晶体管1112用于将各所述光电转换元件1111产生的电荷转移到所述浮动扩散区FD。

[0049] 读出电路1113可配置有多个输出端,输出端的数量与像素110中所包括的子像素的列数m相同。若m=2时,其读出电路1113可包括两个输出端0UT1、0UT2。读出电路1113的输入端与所述浮动扩散区FD连接,用于将转移到所述浮动扩散区FD中的电荷经多个所述输出端(例如0UT1、0UT2)中的至少一个输出。具体的,读出电路1113包括复位晶体管11131、放大晶体管(也可称之为跟随晶体管)11132、选择晶体管11133。其中,复位晶体管11131,与所述浮动扩散区FD连接,用于复位所述浮动扩散区FD;放大晶体管11132,与所述浮动扩散区FD连接,用于放大所述浮动扩散区FD中的电荷,得到放大的电荷;选择晶体管11133,与所述放大晶体管11132连接,用于读出所述放大的电荷到输出电路。

[0050] 为了便于说明,以像素110包括四个呈2\*2排布的子像素为例进行说明。具体的,像素电路111可包括四个光电转换元件1111、四个转移晶体管1112、浮动扩散区FD、复位晶体管11131、放大晶体管11132、选择晶体管11133。像素电路111还可配置四个用于提供曝光控制信号的曝光控制线,每个曝光控制线可对应与四个转移晶体管1112的栅极(TG1、TG2、TG3、TG4)连接。当有效电平(例如,VPIX电平)的脉冲通过曝光控制线传输到转移晶体管1112的栅极时,转移晶体管1112导通,转移晶体管1112将光电二极管光电转换的电荷传输到浮动扩散区FD。

[0051] 复位晶体管11131的漏极连接到像素110电源VPIX。复位晶体管11131的源极连接到浮动扩散区FD。在电荷被从光电二极管转移到浮动扩散区FD之前,有效复位电平的脉冲经由复位线传输到复位晶体管11131的栅极RG,复位晶体管11131导通。复位晶体管11131将浮动扩散区FD复位到像素110电源VPIX。

[0052] 放大晶体管11132的栅极连接到浮动扩散区FD。放大晶体管11132的漏极连接到像素110电源VPIX。在浮动扩散区FD被复位晶体管11131复位之后,放大晶体管11132经由选择晶体管11133通过输出端输出复位电平以及电荷对应的模拟信号。在光电二极管的电荷被转移晶体管1112转移之后,放大晶体管11132经由选择晶体管11133通过输出端输出模拟信号。

[0053] 每个像素电路111可被配置有两条列控制线COL1、COL2。选择晶体管11133的栅极 SEL用于接收选择控制信号,选择晶体管11133的漏极连接到放大晶体管11132的源极,选择晶体管11133的漏极可设有两个输出端OUT1、OUT2,两个输出端分别与两个列控制线COL1、COL2——对应连接。其中,选择晶体管11133的源极对应的两个输出端可经相应的列控制线连接到图1中的列处理单元14。当选择控制信号的脉冲通过选择线被传输到选择晶体管

11133的栅极时,选择晶体管11133导通。放大晶体管11132输出的信号通过选择晶体管11133传输到列处理单元14。

[0054] 若四个转移晶体管1112的栅极TG1、TG2、TG3、TG4接收的曝光控制信号TG使得四个转移晶体管1112同时导通,四个光电转换元件1111产生的电荷分别转移到对应的浮动扩散区FD中,并在浮动扩散区FD进行累积;若第一个和第三个转移晶体管1112的栅极TG1、TG3接收的曝光控制信号TG使得对应转移晶体管1112同时导通,则与之对应连接的第一个和第三个光电转换元件1111产生的电荷分别转移到对应的浮动扩散区FD中,并在浮动扩散区FD进行累积。

[0055] 需要说明的是,本申请实施例中像素电路111的像素110结构并不限于图5所示的结构。例如,像素电路111也可以具有三晶体管像素结构,其中放大晶体管11132和选择晶体管11133的功能由一个晶体管完成。

[0056] 请继续参考图4,图1中的列处理单元14可包括多个第一转换电路141。多个第一转换电路141可对应与多个像素电路112的多个输出端连接。具体的,第一转换电路141包括多个输入端,多个输入端分别与同一像素电路112的多个所述输出端一一对应连接。其中,第一转换电路141用于对多个所述输入端接收的各所述模拟信号进行模数转换,并和像素电路111共同基于全分辨率输出模式或第一级合并输出模式读出转换后的数字信号,其中,所述全分辨模式用于以所述子像素为单位读出像素110中的电荷数据。也即,第一转换电路141和像素电路111可以共同对同一像素110中单个光电二极管产生的电荷对应的数字信号单独输出。所述第一级合并输出模式用于以所述像素110为单位读出像素110中的电荷数据,也即,第一转换电路141和像素电路111可以共同对同一像素110中四个光电二极管产生的电荷进行相加和/或平均处理后的数字信号合并输出。

[0057] 在本申请实施例中,图像传感器包括像素阵列和多个第一转换电路。其中,所述像素阵列包括多个像素,每个所述像素包括呈矩阵排布的多个子像素,其中,同一所述像素中的各所述子像素共享同一浮动扩散区,像素的像素电路用于将同一所述像素中至少一个所述光电转换元件产生的电荷转移到所述浮动扩散区进行累积,并根据累积的电荷选择所述像素电路的至少一个输出端输出所述浮动扩散区中所述电荷对应的模拟信号;第一转换电路可用于对同一所述像素电路的输出的各所述模拟信号进行模数转换,并和像素电路共同基于全分辨率输出模式或第一级合并输出模式读出转换后的数字信号,其中,所述全分辨模式用于以所述子像素为单位的读出所述数字信号。也即,上述实施例中的图像传感器可以提供多种输出模式,示例性的,在暗光下成像时可采用第一级合并输出模式实现以像素为单位的合并输出,得到信噪比较高的图像,而在光线较为充足的场景下,可采用全分辨率输出模式实现以子像素为单位的单独输出,从而得到清晰度和信噪比均较高的图像。

[0058] 在其中一个实施例中,第一级合并输出模式可包括相加模式、数字平均模式和混合模式中的至少一种。

[0059] 相加模式可以理解为对同一像素中的所有子像素的电荷均在浮动扩散区FD中进行累积,并对累积后的总电荷进行模数转换后读出。

[0060] 数字平均模式可以理解为对同一像素中各子像素分时产生的各电荷分别进行模数转换,并对转换后的各数字信号进行平均后读出。

[0061] 混合模式可以理解为对同一像素中第一部分子像素产生的第一电荷在浮动扩散 区FD中进行累积产生第一模拟信号,其第一模拟信号经过模数转换后输出第一数字信号,和分时对同一像素中第二部分子像素产生的第二电荷在浮动扩散区FD中进行累积产生第二模拟信号,其第二模拟信号经过模数转换后输出第二数字信号,然后对第一数字信号、第二数字信号进行平均后读出。其中所述第一部分子像素和所述第二部分子像素共同构成所述像素。

[0062] 具体的,若所述浮动扩散区FD在同一曝光时间内累积的所述电荷为一个所述光电转换元件1111的电荷,则所述像素电路111导通所有所述输出端,以将各所述光电转换元件1111的电荷对应的模拟信号分时输出至所述第一转换电路141,以使所述第一转换电路141对多个所述模拟信号执行所述全分辨率输出模式或所述数字平均模式的操作。其中,分时输出可以理解为可对不同曝光时间内,不同个光电转换元件1111累积的电荷进行分时输出。示例性的,可以对第一曝光时间内光电转换元件111累积的电荷在第一时刻进行输出;可以对第二曝光时间内光电转换元件111累积的电荷在第二时刻进行输出,其中,第一时刻和第二时刻的时间点不同。

[0063] 若所述浮动扩散区FD在同一曝光时间内累积的所述电荷为同一像素110中所有所述光电转换元件1111的电荷,所述像素电路111导通任一所述输出端,以将累积的所述电荷对应的模拟信号输出至所述第一转换电路141,以使所述第一转换电路141对所述模拟信号执行所述相加模式的操作。

[0064] 若所述浮动扩散区FD在第一曝光时间内累积的所述电荷为所述第一部分子像素对应的所述光电转换元件1111累积的第一累积电荷,或,所述浮动扩散区FD在第二曝光时间内累积的所述电荷为所述第二部分子像素的对应的所述光电转换元件1111累积的第二累积电荷,则所述像素电路111导通多个所述输出端,以分别将所述第一累积电荷、第二累积电荷对应的模拟信号分时输出至所述第一转换电路141,以使所述第一转换电路141对所述模拟信号执行所述混合模式的操作。示例性的,若像素111包括两列子像素,则第一部分子像素包括位于第一列的各子像素,第二部分子像素包括位于第二列的各子像素。

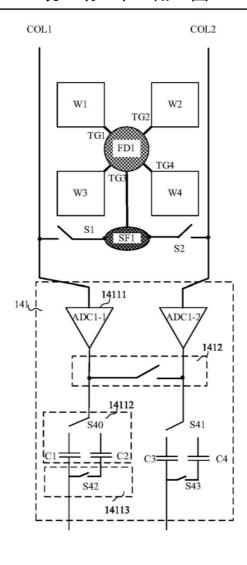

[0065] 如图6-8所示,在其中一个实施例中,所述第一转换电路141包括:m个第一转换单元1411和第一开关单元1412。其中,m个第一转换单元1411分别与m条列控制线(例如,COL1、COL2)——对应连接,各所述第一转换单元用于将接收的所述模拟信号转换为数字信号。也就是说,第一转换单元1411的数量与同一像素110中子像素的列数相等,同一像素110中的同一列子像素可共同第一转换单元1411。具体的,第一转换单元1411可包括模数转换器,每一模数转换器可对应与一条列控制线连接,用于将像素电路111输出的模拟信号转换为数字信号。

[0066] 第一开关单元1412,分别与各所述第一转换单元1411连接;其中,当所述第一开关单元1412导通时,所述第一转换电路141对m个所述数字信号执行平均操作。其中,数字信号可以为一个光电转换元件1111产生的电荷对应的数字信号,也可以为同一像素110中位于同一列的多个光电转换元件1111在浮动扩散区累积的电荷对应的数字信号。当第一开关单元1412断开时,所述第一转换电路141可分时输出m个所述数字信号,以实现全分辨模式的输出。

[0067] 为了便于说明以下实施例中均以每个像素110均包括四个子像素W1-W4,四个子像

素呈2\*2矩阵排布,且像素110被配置有四个曝光控制线TG1、TG2、TG3、TG4、两个复位控制线RST、第一列控制线COL1和第二列控制线COL2,每个像素110单元被配置有第一输出端OUT1、第二输出端OUT2为例,对全分辨率输出模式、第一级合并输出模式的工作原理进行说明。具体的,第一输出端OUT1经第一开关S1、所述第一列控制线COL1与第一转换电路141连接以形成第一输出通路,所述第二输出端经所述第二开关S2、所述第二列控制线COL2与第一转换电路141连接以形成第二输出通路。

[0068] 全分辨率输出模式:在第一曝光时间内,第一曝光控制线TG1输入高电平,相对应的子像素W1的转移晶体管打开,其对应的子像素W1产生的电荷分别转移到对应的浮动扩散区FD1中;随后曝光控制线TG1输入低电平,相对应的子像素W1的转移晶体管断开,浮动扩散区FD1中的电荷经过放大晶体管SF1后转化成模拟信号(也称之为模拟电压信号)。同时,通过控制第一开关S1闭合,第二开关S2断开,经过第一列控制线COL1输入到模数转换器ADC1-1中,经过模数转换器ADC1-1的模数转换后输出子像素W1对应的数字信号。相应的,复位晶体管高电平复位后,清空浮动扩散区FD1中的电荷,可在第二曝光时间内,可通过控制曝光控制线TG1输入的电平信号,将子像素W2产生的电荷转移到浮动扩散区FD1中,并通过控制第一开关S1、第二开关S2的通断情况,可经第二列控制线COL2将子像素W2产生的电荷对应的模拟信号输入到模数转换器ADC1-2中,经过模数转换器ADC1-2的模数转换后输出子像素W2对应的数字信号。其中,子像素W3和读出过程可以参考子像素W1的读出过程,子像素W4和读出过程可以参考子像素W2的读出过程,在此,不再赘述。在全分辨率输出模式中,上一个子像素读出完成后,都需要在清空当前浮动扩散区FD中的存储的电荷后才可以进行下一子像素的读出。

[0069] 第一级合并输出模式中的相加模式:四个曝光控制线TG1、TG2、TG3、TG4同时输入高电平,此时四个子像素W1、W2、W3、W4的转移晶体管的同时导通,四个子像素W1、W2、W3、W4中的电荷都汇聚到共用的浮动扩散区FD1中。然后,四个曝光控制线TG1、TG2、TG3、TG4同时输入低电平,此时四个子像素W1、W2、W3、W4的转移晶体管处于关断状态,浮动扩散区FD1中存储着四个子像素W1、W2、W3、W4的电荷叠加,经过放大晶体管SF1后转换成模拟信号,通过控制第一开关S1闭合,第二开关S2断开,经过第一列控制线COL1输入到模数转换器ADC1-1中,经过模数转换器ADC1-1的模数转换后可输出四个子像素W1、W2、W3、W4在浮动扩散区FD1累积电荷对应的数字信号。

[0070] 第一级合并输出模式中的混合模式:两个曝光控制线TG1、TG3同时输入高电平,此时两个子像素W1、W3的转移晶体管打开,子像素W1、W3的电荷累加到浮动扩散区FD1,经过一段时间后两个子像素W1、W3的转移晶体管栅极同时输入低电平,两个子像素W1、W3的转移晶体管断开,此时通过控制第一开关S1闭合,第二开关S2断开,浮动扩散区FD1中的累积的电荷经过放大器晶体管SF通过第一列控制线COL1转移到模数转换器ADC1-1中,经过模数转换器ADC1-1的模数转换后输出两个子像素W1、W3累积电荷对应的第一数字信号。复位晶体管高电平复位后,清空浮动扩散区FD1中的累积的电荷,两个曝光控制线TG2、TG4同时输入高电平,此时两个子像素W2、W4的转移晶体管打开,两个子像素W2、W4产出的电荷累加到浮动扩散区FD1,经过一段时间后,两个曝光控制线TG2、TG4同时输入低电平,两个子像素W2、W4的转移晶体管断开,此时通过控制第二开关S2闭合,第一开关S1断开,浮动扩散区FD1中的累积的电荷信号经过放大器晶体管SF1通过第二列控制线COL2转移到模数转换器ADC1-2

中,经过模数转换器ADC1-2的模数转换后输出两个子像素W2、W4累积的第二数字信号。具体的,当第一开关单元1412闭合导通时,两个模数转换器ADC1-1和ADC1-2彼此连通,可以对模数转换器ADC1-1输出的第一数字信号和模数转换器ADC1-2输出的第二数字信号进行平均操作。

[0071] 如图9所示,在其中一个实施例中,所述第一转换单元1411包括:模数转换器14111、存储单元14112和第二开关单元14113。其中,模数转换器14111与所述列控制线连接,用于对接收的模拟信号进行模数转换以输出数字信号。存储单元1411,与所述第一开关单元1412连接,用于将位于同一列的各所述像素110对应所述数字信号进行分区存储。具体的,存储单元1411能够实现对每个子像素产生的电荷的分区存储。具体的,存储单元1411可包括n个存储电容C1、C2。第二开关单元14113,与所述存储单元1411中的每个存储电容分别对应连接,用于对分区存储的所述数字信号进行平均操作。

[0072] 请继续参考图9,第一级合并输出模式中的数字平均模式原理如下:

[0073] 在第一曝光时间内,将子像素W1产生的电荷转移到对应的浮动扩散区FD1中,浮动扩散区FD1中的电荷经过放大晶体管SF1后转化成模拟信号。同时,通过控制第一开关S1闭合,第二开关S2断开,经过第一列控制线COL1将模拟信号输入到模数转换器ADC1-1中,通过控制存储单元中开关S40导通,可将模数转换器ADC1-1的模数转换后输出的数字信号传输至存储电容C1中进行存储。相应的,复位晶体管高电平复位后,清空浮动扩散区FD1中的电荷,可在第二曝光时间内,将子像素W2产生的电荷对应的模拟信号输入到模数转换器ADC1-2中,通过控制存储单元中开关S41导通,经过模数转换器ADC1-2的模数转换后输出子像素W2对应的数字信号至存储电容C3进行存储。相应的,可将子像素W3产生的电荷对应的数字信号传输至存储电容C2中进行存储;可将子像素W4产生的电荷对应的数字信号传输至存储电容C4中进行存储。然后,通过控制第二开关单元14113中的开关S42、开关S43导通,以实现对四个子像素W1、W2、W3、W4对应的四个数字信号的平均输出。在全分辨率输出模式中,上一个子像素电荷读出完成后,都需要在清空当前浮动扩散区FD1中的存储的电荷后才可以进行下一子像素电荷的读出。

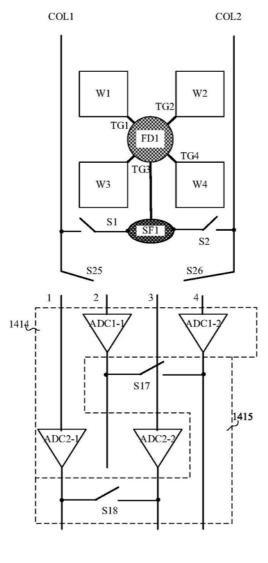

[0074] 如图10所示,在其中一个实施例中,第一转换电路141可包括第二转换单元1414、开关S17、开关S18。其中,第二转换单元1414可包括n\*m个模数转换器。示例性,当n=m=2时,第二转换单元1414可包括四个模数转换器ADC1-1、ADC1-2、ADC2-1、ADC2-2。其中,第一列控制线COL1可通过开关S25连接至模数转换器ADC1-1、ADC2-1,第二列控制线COL2可通过开关S26连接至模数转换器ADC1-2、ADC2-2。具体的,开关S17可连接在模数转换器ADC1-1、ADC1-2之间,开关S18可连接在模数转换器ADC2-1、ADC2-2之间,一个开关可连接在ADC1-1、ADC2-2之间。

[0075] 第一级合并输出模式中的数字平均模式:曝光控制线TG1输入高电平,以使子像素W1的转移晶体管导通,子像素W1产生的电荷可转移至浮动扩散区FD1,并通过放大晶体管SF1后转化成模拟信号经第一列控制线COL1、开关S25连通至触点1,以传输至模数转换器ADC1-1读出;复位晶体管复位后,曝光控制线TG2输入高电平,以使子像素W2的转移晶体管导通,子像素W2产生的电荷可转移至浮动扩散区FD1,并通过放大晶体管SF1后转化成模拟信号经第一列控制线COL1、开关S25连通至触点2以传输至模数转换器ADC2-1读出。复位晶体管复位后,曝光控制线TG3输入高电平,以使子像素W3的转移晶体管导通,子像素W3产生

的电荷可转移至浮动扩散区FD1,并通过放大晶体管SF1后转化成模拟信号经第二列控制线COL2、S26连通至触点3以传输至模数转换器ADC1-2读出;复位晶体管复位后,曝光控制线TG4输入高电平,以使子像素W4的转移晶体管导通,子像素W4产生的电荷可转移至浮动扩散区FD1,并通过放大晶体管SF1后转化成模拟信号经第二列控制线COL2、S26连通至触点4以传输至模数转换器ADC2-2读出。然后,通过导通开关S17、开关S18,以使两个模数转换器ADC1-1、ADC1-2读出后的数字信号进行第一次平均,以输出第一平均数字信号,两个模数转换器ADC2-1、ADC2-2读出后的数字信号进行第一次平均,以输出第二平均数字信号,然后在对第一平均数字信号和第二数字平均信号进行第二次平均,以输出以该像素110为单元的的平均数字信号。需要说明的是,本实施例中的第一转换电路141也可以支持对全分辨率输出模式、第一级合并输出模式中任一模式的读出。其中,当支持对全分辨率输出模式、相加模式、第一级合并输出模式中任一模式的读出。其中,当支持对全分辨率输出模式、相加模式、混合模式时,读出过程中参与的模数转换器可以包括模数转换器ADC1-1、ADC1-2,其具体的读出过程可参考前述实施例,在此,不再赘述。

[0076] 在本实施例中,通过配置四个模数转换器,可以提供图像传感器执行数字平局模式的效率。另外,四个模数转换器还可以与像素阵列中其他像素110的第一转换电路141的模数转换器进行复用,其复用过程可在后续实施例中进行阐述。

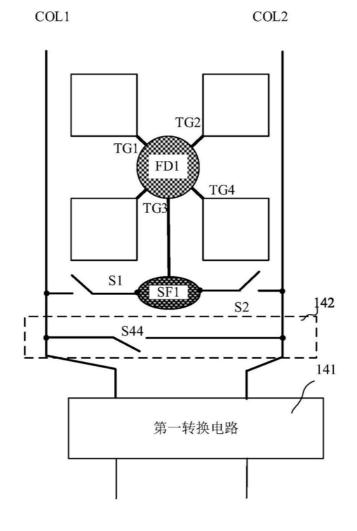

[0077] 如图11所示,在其中一个实施例中,所述第一级合并输出模式包括模拟平均模式。具体的,图像传感器还包括与每一像素对应的第二转换电路142,该第二转换电路142设置在像素电路111的输出端与第一转换电路141的输入端之间。也即,第二转换电路142,分别与像素电路111的多个输出端、第一转换电路141的输入端连接。第二转换电路142可用于对所述像素电路111输出的多个所述模拟信号执行模拟平均模式的操作。具体的,第二转化电路可包括连接在第一列控制线COL1和第二列控制线COL2之间的开关S44。第二转换电路142可以对第一列控制线COL1和第二列控制线COL2上传输的模拟信号进行平均。其模拟信号可以为同一像素110中任一子像素产生的电荷对应的模拟信号,也可以为同一像素110中位于同一列的多个子像素在浮动扩散区FD累计产生的电荷对应的模拟信号。

[0078] 本实施例中,通过设置第二转换电路142,可以实现对像素电路111中输出的多个模拟信号的平均操作,拓展了对各像素110产生的电荷的输出模式,可以时图像传感器适用于更多的应用场景。

[0079] 图12是本申请某些实施方式的像素阵列中的像素的排布示意图。像素110包括两类,一类为全色像素W,另一类为彩色像素。其中,彩色像素具有比全色像素更窄的光谱响应。具体的,全色像素中可包括多个全色子像素W,彩色像素中可包括多个具有相同单颜色的子像素。

[0080] 最小重复单元在行和列上多次复制,即可形成像素阵列11。每个最小重复单元均由多个全色像素W和多个彩色像素组成。每个最小重复单元包括多个像素单元U。每个像素单元U内包括多个单颜色像素和多个全色像素W。

[0081] 具体地,图12为本申请一个实施例的最小重复单元中像素的排布示意图。其中,最小重复单元为4行4列16个像素,像素单元U为2行2列4个像素。排布方式为:

[0082] W A W B W W B W C B W C W

[0083] W表示全色像素;A表示多个彩色像素中的第一颜色像素;B表示多个彩色像素中的第二颜色像素;C表示多个彩色像素中的第三颜色像素。

[0084] 对于每个像素单元U,全色像素W和单颜色像素交替设置。

[0085] 如图12所示,像素单元U的类别包括三类。其中,第一类像素单元UA包括多个全色像素W和多个第一颜色像素A;第二类像素单元UB包括多个全色像素W和多个第二颜色像素B;第三类像素单元UC包括多个全色像素W和多个第三颜色像素C。每个最小重复单元包括四个像素单元U,分别为一个第一类像素单元UA、两个第二类像素单元UB及一个第三类像素单元UC。其中,一个第一类像素单元UA与一个第三类像素单元UC设置在第一对角线方向D1(例如图12中左上角和右下角连接的方向),两个第二类像素单元UB设置在第二对角线方向D2(例如图12中右上角和左下角连接的方向)。第一对角线方向D1与第二对角线方向D2不同。例如,第一对角线和第二对角线垂直。示例性的,最小重复单元中,第一颜色像素A可以为红色像素R;第二颜色像素B可以为绿色像素G;第三颜色像素C可以为蓝色像素Bu。

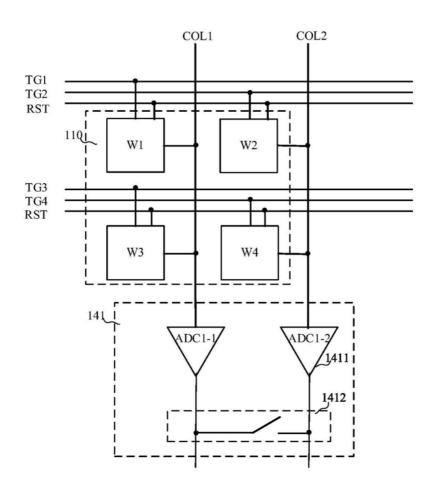

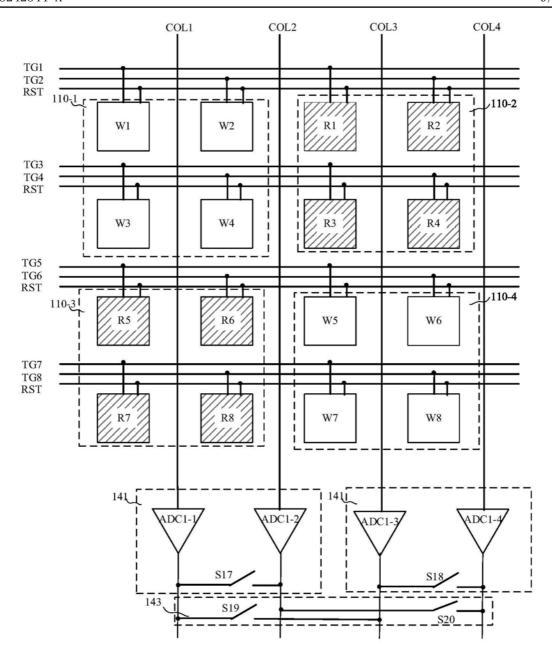

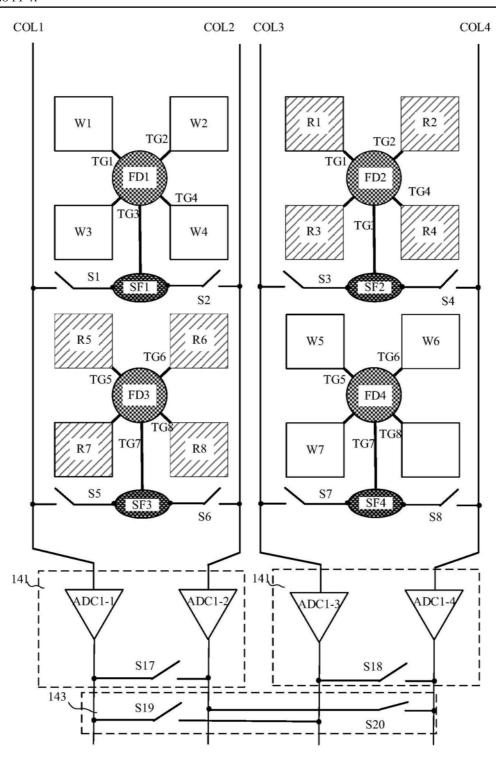

[0086] 如图13和图14所示,为了方便说明,以下实施例均以第一类像素单元UA为例进行说明。其中,第一类像素单元UA中可包括2\*2阵列设置的第一像素110-1、第二像素110-2、第三像素110-3和第四像素110-4,其中,所述第一像素110-1和第四像素110-4为全色像素,且设置在第一对角线方向,所述第二像素110-2和第三像素110-3为彩色像素,且设置在第二对角线方向。

[0087] 需要说明的是,在其他实施方式中,第一对角线方向D1也可以是右上角和左下角连接的方向,第二对角线方向D2也可以是左上角和右下角连接的方向。另外,这里的"方向"并非单一指向,可以理解为指示排布的"直线"的概念,可以有直线两端的双向指向。

[0088] 第一类像素单元UA可对应包括两个第一转换电路141。其中,位于同一列的两个像素110可共用同一所述第一转换电路141,且位于同一行的两个所述像素110的所述第一转换电路141连接。也即,第一像素110-1和第三像素110-3可共用一个第一转换电路141,第二像素110-2、第四像素110-4可共用一个第一转换电路141,且两个第一转换电路141的输出端彼此电连接。当两个第一转换的电路彼此电连接时,彼此连接的两个所述第一转换电路141还用于基于第二级合并输出模式读出数字信号,其中,所述第二级合并输出模式用于以所述第一对角线或第二对角线方向上的所有所述像素为单位的读出所述数字信号。也即,第二级合并输出模式可以理解为对第一像素110-1采用第一级合并输出模式输出的第一数字信号和第三像素110-3采用第一级合并输出的第三数字信号,然后对第一数字信号和第四数字信号再次执行平均操作,以读出第一对角线上所有像素110的数字平均信号;同时,也可以对第二像素110-2采用第一级合并输出模式输出的第二数字信号和第四像素110-4采用第一级合并输出的第四数字信号和第四数字信号和第四数字信号执行平均操作,以读出第二对角线上所有像素的数字平均信号。

[0089] 在其中一个实施例中,所述像素单元U配置有第一列控制线C0L1、第二列控制线C0L2、第三列控制线C0L3和第四列控制线C0L4。其中,所述像素单元U还包括设置在两个所

述第一转换电路141输出端的第三开关单元143。其中,所述第三开关单元143包括两个开关S19、S20,一个开关S19连接在所述第一列控制线C0L1和所述第三列控制线C0L3之间,另一个所述开关S20连接在所述第二列控制线C0L2和所述第四列控制线C0L4之间。

[0090] 具体的,位于第一列的像素的第一输出端均通过开关(例如,开关S1、开关S5)连接至所述第一列控制线C0L1,位于第一列的像素的第二输出端均通过开关(例如,开关S2、开关S6)连接至所述第二列控制线C0L2,位于第二列的像素的第一输出端均通过开关(例如,开关S3、开关S7)连接至所述第三列控制线C0L3,位于第二列的像素的第二输出端均通过开关(例如,开关S4、开关S8)连接至所述第四列控制线C0L4。

[0091] 同一所述像素单元U的两个所述第一转换电路141包括:四个模数转换器ADC1-1、ADC1-2、ADC1-3、ADC1-4,以及设置在所述模数转换器14111输出端的两个第三开关(例如,开关S17、开关S18),其中,四个所述模数转换器14111的输入端分别与四个所述列控制线连接,两个第三开关中的一个(例如,开关S17)连接在所述第一列控制线COL1和所述第二列控制线COL2之间,两个第三开关中的另一个(例如,开关S18)连接在所述第三列控制线COL3和所述第四列控制线COL4之间。

[0092] 为了便于说明,以如图13、14所示的图像传感器为例,对全分辨率输出模式、第一级合并输出模式、第二级合并输出模式的工作原理进行说明。其中,像素单元配置有用于传输曝光控制信号的曝光控制线TG1-TG8以及用于传输复位控制信号的多个复位控制线RST,还配置有多个列控制线COL1-COL4,每个列控制线可对应第一转换电路141连接。

[0093] 全分辨率输出模式:曝光控制线TG1、TG5输入高电平,相对应的子像素W1、R1、R5、W5对应的转移晶体管导通,子像素W1、R1、R5、W5产生的电荷分别转移到对应的浮动扩散区中,随后曝光控制线TG1和TG5输入低电平,相对应的子像素W1、R1、R5、W5的转移晶体管断开,通过控制开关S1、S3、S6和S8闭合,以及控制开关S2、S4、S5、S7、S17-S20断开。其中,子像素W1转移至浮动扩散区FD1中的电荷经放大晶体管SF1转化成的模拟信号经列控制线COL1输入到模数转换器ADC1-1中;子像素R1转移至浮动扩散区FD2中的电荷经跟随晶体管SF2转化成的模拟信号经过列控制线COL3输入到模数转换器ADC1-3中,子像素R5转移至浮动扩散区FD3的电荷经跟随晶体管SF3转化成的模拟信号经列控制线COL2输入到模数转换器ADC1-2,子像素W5像素110转移至浮动扩散区FD4的电荷经跟随晶体管SF4化成的模拟信号经过列控制线COL4输入到模数转换器ADC1-4,以读出每个子像素W1、R1、R5、W5产生的电荷对应的数字信号。然后,曝光控制线TG1和TG5输入高电平,与子像素W1、R1、R5、W5的读出方式类似,可以读出子像素W2、R2、R6、W6所产生的电荷对应的数字信号,以此类推,可以对应读出像素单元U中每个子像素所产生的电荷对应的数字信号。在此过程中,第一转换电路141中的开关S17、S18,以及第三开关单元143的开关S19、S20处于断开状态。

[0094] 第一级合并输出模式中的相加模式:曝光控制线TG1、TG2、TG3、TG4同时输入高电平,子像素W1、W2、W3、W4、R1、R2、R3、R4对应的转移晶体管打开,四个子像素W1、W2、W3、W4的电荷转移到共用的浮动扩散区FD1中,四个子像素R1、R2、R3、R4的电荷转移到共用的浮动扩散区FD2中。然后,曝光控制线TG1、TG2、TG3、TG4同时输入低电平,子像素W1、W2、W3、W4、R1、R2、R3、R4对应的转移晶体管处于关断状态,四个子像素W1、W2、W3、W4产生的电荷在浮动扩散区FD1中累积叠加形成第一电荷,经过放大晶体管SF1后转换成模拟信号,然后通过控制开关S1闭合,控制开关S2断开,经列控制线COL1输出至模数转换器ADC1-1。四个子像素R1、

R2、R3、R4产生的电荷在浮动扩散区FD2中累积叠加形成第二电荷,经过跟随晶体管SF2后转换成模拟信号,然后通过控制开关S3闭合,控制开关S4断开,经列控制线C0L3输出至模数转换器ADC1-3,在此过程中,第一转换电路141中的开关S17、S18,以及第三开关单元143的开关S19、S20处于断开状态。

[0095] 在曝光控制线TG1、TG2、TG3、TG4输入高电平的同时,也可以控制曝光控制线TG5、TG5、TG7、TG8同时输入高电平,子像素R5、R6、R7、R8、W5、W6、W7、W8对应的转移晶体管打开,四个子像素R5、R6、R7、R8的电荷转移到共用的浮动扩散区FD3中,四个子像素W5、W6、W7、W8的电荷转移到共用的浮动扩散区FD4中。然后,曝光控制线TG5、TG5、TG7、TG8同时输入低电平,子像素R5、R6、R7、R8、W5、W6、W7、W8对应的转移晶体管处于关断状态,四个子像素R5、R6、R7、R8产生的电荷在浮动扩散区FD2中累积叠加形成第三电荷,经过跟随晶体管SF3后转换成模拟信号,然后通过控制开关S6闭合,控制开关S5断开,经列控制线C0L2输出至模数转换器ADC1-2;同时,四个子像素W5、W6、W7、W8产生的电荷在浮动扩散区FD4中累积叠加形成第四电荷,经过跟随晶体管SF4后转换成模拟信号,然后通过控制开关S8闭合,控制开关S7断开,经列控制线C0L4输出至模数转换器ADC1-4。在此过程中,第一转换电路141中的开关S17、S18,以及第三开关单元143的开关S19、S20处于断开状态。

[0096] 第一级合并输出模式中的混合模式:曝光控制线TG1、TG3同时输入高电平,子像素W1、W3、R1、R3对应的转移晶体管打开,两个子像素W1、W3的电荷转移到共用的浮动扩散区FD1中,两个子像素R1、R3的电荷转移到共用的浮动扩散区FD2中。然后,曝光控制线TG1、TG3、TG5、TG7同时输入低电平,子像素W1、W3、R1、R3对应的转移晶体管处于关断状态,两个子像素W1、W3产生的电荷在浮动扩散区FD1中累积叠加形成第一电荷,经过放大晶体管SF1后转换成模拟信号,然后通过控制开关S1闭合、开关S2断开,经列控制线COL1输出至模数转换器ADC1-1。相应的,两个子像素R1、R3产生的电荷在浮动扩散区FD2中累积叠加形成第二电荷,经过跟随晶体管SF2后转换成模拟信号,然后通过控制开关S3闭合、开关S4断开,经列控制线COL3输出至模数转换器ADC1-3。

[0097] 复位控制线RST输入高电平,以对复位晶体管进行复位,清空浮动扩散区FD1、FD2中累积的电荷。然后,曝光控制线TG2、TG3先输入高电平,在输入低电平,以将两个子像素W2、W3产生的电荷在浮动扩散区FD1中累积叠加形成第三电荷,将两个子像素R2、R3产生的电荷在浮动扩散区FD1中累积叠加形成第四电荷。通过控制开关S2闭合、开关S1断开,经列控制线COL2将第三电荷输出至模数转换器ADC1-2,控制开关S4闭合、开关S3断开,经列控制线COL2将第四电荷输出至模数转换器ADC1-4。同时,通过控制第一转换电路141中的开关S17闭合,以对模数转换器ADC1-1读出的第一电荷的数字信号以及模数转换器ADC1-2读出的第三电荷的数字信号进行平均操作。通过控制第一转换电路141中的开关S18闭合,以对模数转换器ADC1-3读出的第二电荷的数字信号以及模数转换器ADC1-4读出的第四电荷的数字信号进行平均操作。在此过程中,第三开关单元143的开关S19、S20处于断开状态。

[0098] 如图15所示,第一级合并输出模式中的数字平均模式可以对应参考前述实施例中的第一级合并输出模式中的数字平均模式的读出过程,在此,不再赘述。

[0099] 第二级合并输出模式:请继续参考图13和图14,以八个子像素W1-W4、以及W5-W8为例进行说明。例如,四个子像素W1-W4的第一级合并输出模式(相加模式或混合模式)的输出结果可经模数转换器ADC1-1读出,四个子像素W5-W8的第一级合并输出模式(相加模式或混

合模式)的输出结果可经模数转换器ADC1-3读出;然后,通过控制开关S19闭合,开关S17断开,以使模数转换器ADC1-1和ADC1-3短接,从而可以将实现对模数转换器ADC1-1读出的第一数字信号和模数转换器ADC1-3读出的第二数字信号进行平均,进而可以实现对第一对角线的所有像素110为单位的电荷数据的读出。需要说明的是,像素阵列中每个像素的第一级合并输出模式相同。第二级合并输出模式也包括相加模式、混合模式、数字平均模式和模拟平均模式。其中,第一级合并输出模式与第二级合并输出模式相同。

[0100] 如图16所示,本申请实施例中,图像传感器可以在第一级合并输出模式的输出结果的基础上,还可以采用第二级合并输出模式对像素阵列11中各像素的电荷数据进行合并输出。因此,本申请实施例中的图像传感器可以支持对全分辨率输出模式、第一级合并输出模式和第二级合并输出模式对各像素单元中的各子像素的电荷数据的读出,可以拓展图像传感器的输出模式的灵活性,进而可以适用于更多的使用场景。

[0101] 在本申请实施例中,为了便于说明,表1为全分辨率输出模式、第一级合并输出模式和第二级合并输出模式的优势分析对比表。

[0102] 表1为全分辨率输出模式、第一级合并输出模式和第二级合并输出模式的优势分析对比表

|      | 模式  | 全分辨模 | 第一级合并输出模式 |       |       | 第二级合并输出模式 |         |         |

|------|-----|------|-----------|-------|-------|-----------|---------|---------|

|      |     | 式    | 相加模式      | 混合模式  | 平均模式  | 相加模式      | 混合模式    | 平均模式    |

|      | 分辨率 | 1x   | 0.25x     | 0.25x | 0.25x | 0.0625x   | 0.0625x | 0.0625x |

|      | 信噪比 | 0    | 6dB       | 4.5dB | 3dB   | 12dB      | 9dB     | 6dB     |

|      | 帧率  | 1x   | 4x        | 2x    | 1x    | 16x       | 4x      | 1x      |

|      | 功耗  | 1x   | 0.25x     | 0.5x  | 1x    | 0.0625x   | 0.25x   | 1x      |

| 103] | 特点  | 分辨率高 | 分辨率中      | 分辨率中  | 分辨率中  | 分辨率低      | 分辨率低    | 分辨率低    |

|      |     | 信噪比低 | 信噪比中      | 信噪比中  | 信噪比中  | 信噪比高      | 信噪比中    | 信噪比中    |

|      |     | 帧率低  | 帧率中高      | 低     | 帧率低   | 帧率高       | 高       | 帧率低     |

|      |     | 功耗高  | 功耗低       | 帧率中   | 功耗高   | 功耗低       | 帧率中高    | 功耗高     |

|      |     | 动态范围 | 动态范围      | 功耗中   | 动态范围  | 动态范围      | 功耗低     | 动态范围    |

|      |     | 中    | 低         | 动态范围  | 高     | 低         | 动态范围    | 高       |

|      |     |      |           | 中     |       |           | 中       |         |

[0103]

[0104] 基于如表1所示的各输出模式的优势分析表可知,不同的输出模式可以应用在不同的使用场景。

[0105] 示例性的,对于图片拍摄场景,当需要采集高清晰度场景(例如,纹理比较多的场景,如草地等)或者高亮场景(例如晴天室外)的图像时,可以控制图像传感器以全分辨模式读出像素阵列的数据,以进行全尺寸的图片拍摄。当需要采集低亮场景(例如,室内场景或者阴天室外)的图像时,可以控制图像传感器以中等分辨率的输出模式(例如,第一级合并输出模式)读出像素阵列的数据,以进行图片拍摄;当需要采集暗光场景(例如,夜晚)的图像时,可以控制图像传感器以具有高进光量和高信噪比的输出模式(例如,第二级合并输出模式)读出像素阵列的数据,以进行图片拍摄。

[0106] 示例性的,对于视频拍摄场景,当需要拍摄4K2K视频,则可以切换到第一级合并输出模式读出像素阵列的数据;当需要拍摄1080P视频,则可以切换到第二级合并输出模式读出像素阵列的数据。而对于一般的预览模式则可以采用第二级合并输出模式读出像素阵列的数据。

[0107] 进一步的,针对第一级合并输出模式、第二级合并输出模式中对相加模式、混合模

式和平均模式的选择可以遵循以下原则:

[0108] 当需要高信噪比场景,例如暗光场景、夜晚场景;或需要低功耗场景,例如,长时间 预览或者拍摄视频;或需要高帧率场景,例如,拍摄HDR视频或者HDR预览或者拍摄慢动作视 频时,可以采用相加模式读出像素阵列的数据。

[0109] 当需要兼顾分辨率和信噪比的场景,例如室内场景(商场),阴天等大部分场景下,则可以采用混合模式读出像素阵列的数据。

[0110] 当需要高动态范围场景,例如晴天室外场景,则可以采用数字平均或模拟平均模式读出像素阵列的数据。

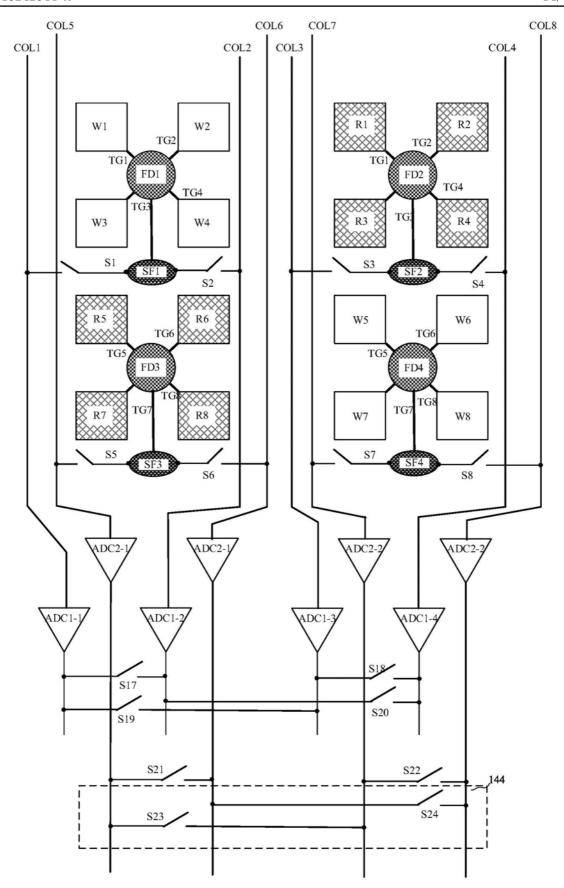

[0111] 如图17和图18所示,在其中一个实施例中,同一像素单元中,位于同一行的两个所述像素的所述第一转换电路彼此连接,位于同一列的两个所述像素的所述第一转换电路彼此独立,不共用。具体的,每个像素单元配置八个列控制线COL1-COL8,同一所述像素单元的四个所述第一转换电路141包括:八个模数转换器ADC1-1、ADC1-2、ADC1-3、ADC1-4、ADC2-1、ADC2-2、ADC2-3、ADC2-4以及开关S17、开关S18、开关S21、开关S22。像素单元还包括用于连接位于同一行的两个第一转换电路141的第四开关单元144,其中,第三开关单元143包括开关S23、开关S24。

[0112] 其中,每个列控制线对应与一个模数转换器连接,也即,同一行的各像素110的输出端可对应连接至同一行的各模数转换器。其中,模数转换器ADC1-1、ADC1-2、ADC1-3、ADC1-4位于同一行,模数转换器ADC2-1、ADC2-2、ADC2-3、ADC2-4位于同一行。具体的,第一像素110-1输出的模拟信号可经过列控制线COL1、控制线COL2对应一一传输至模数转换器ADC1-1、ADC1-2;第二像素110-2输出的模拟信号可经过列控制线COL3、控制线COL4对应一一传输至模数转换器ADC1-3、ADC1-4;第三像素110-3输出的模拟信号可经过列控制线COL5、控制线COL6对应一一传输至模数转换器ADC2-1、ADC2-2;第四像素110-4输出的模拟信号可经过列控制线COL5、控制线COL6对应一一传输至模数转换器ADC2-1、ADC2-2;第四像素110-4输出的模拟信号可经过列控制线COL5、控制线COL7、控制线COL8对应一一传输至模数转换器ADC2-3、ADC2-4。

[0113] 本实施例中如图17、18所示的图像传感器也可以采用全分辨率输出模式、第一级合并输出模式来对应读出像素阵列中各像素的电荷对应的模拟信号,其各输出模式的具体过程与前述实施例相似,可以参看前述实施例,在此,不再赘述。本实施例中,针对每个像素单元,通过增加列控制线的数量和模数转换器的数量,可以对应增加对像素单元中各像素的读出速度,提高了像素阵列的读出效率。

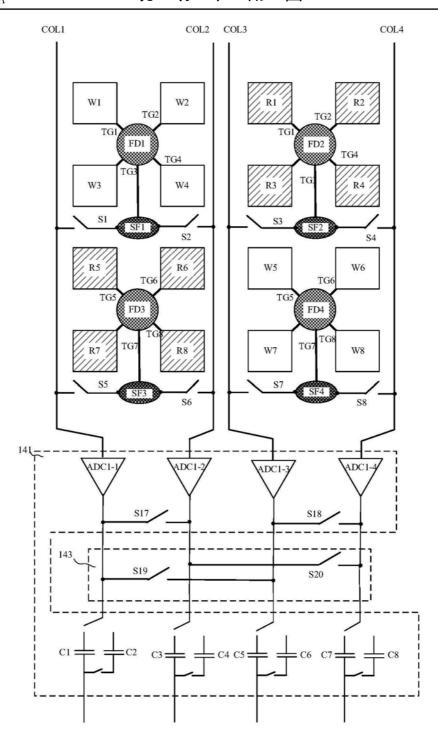

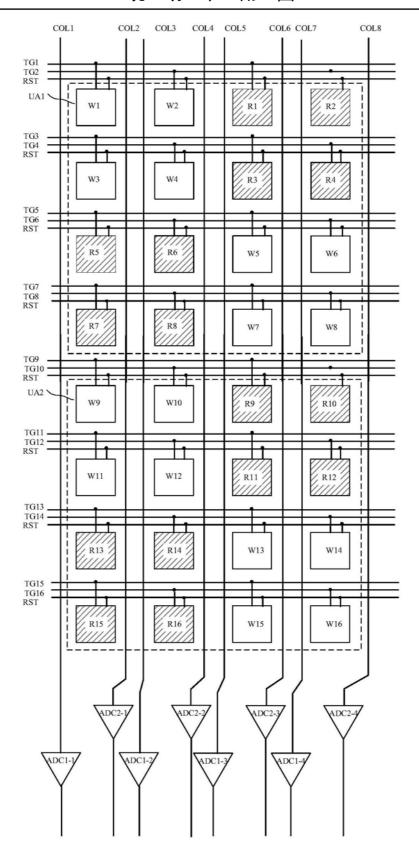

[0114] 在其中一个实施例中,所述像素阵列包括呈阵列设置的多个像素组,各所述像素组包括呈2\*1阵列设置的第一像素单元UA1和第二像素单元UA2,如图19和图20所示。其中,所述第一像素单元UA1对应的第一转换电路141与第二像素单元UA2对应的第二转换器电路连接。所述像素组还包括开关阵列145,其中,开关阵列145分别与各所述列控制线、各所述第一转换电路141连接,用于选择导通所述第一像素单元UA1、第二像素单元UA2中各所述像素电路111的任一所述输出端与目标模数转换器组之间的通路。目标模数转换器组包括第一像素单元UA1对应的一个模数转换器,以及第二像素单元UA2对应的一个模数转换器。

[0115] 在以下各实施例中,以第一像素单元UA1和第二像素单元UA2均为第一类像素单元U为例进行说明。

[0116] 在其中一个实施例中,同一所述像素组被配置有第一列控制线组和第二列控制线组,各所述列控制线组均包括四个所述列控制线。其中,第一列控制线组可包括列控制线

COL1、COL2、COL3、COL4,第一列控制线组中的各列控制线可用于传输第一像素单元UA1中的各像素输出的模拟信号;第二列控制线组可包括列控制线COL5、COL6、COL7、COL8,第二列控制线组中的各列控制线可用于传输第二像素单元UA2中的各像素输出的模拟信号。

[0117] 同一所述像素组可包括四个第一转换电路,其中,四个第一转换电路可包括第一模数转换器组、第二模数转换器组、开关S17、开关S18、开关S21、开关S22。各所述模数转换器组均包括四个模数转换器。具体的,第一模数转换器组可包括位于同一行的模数转换器ADC1-1、ADC1-2、ADC1-3、ADC1-4;第二模数转换器组可包括位于同一行的模数转换器ADC2-1、ADC2-2、ADC2-3、ADC2-4。

[0118] 其中,开关阵列145的第一侧可分别与八个列控制线COL1-COL8连接,开关阵列145的第二侧可分别与八个模数转换器ADC1-1-ADC2-4连接,开关阵列145用于选择导通任所述第一列控制线组中任一列控制线与所述第一模数转换器组中一个所述模数转换器或所述第二模数转换器组中一个所述模数转换器之间的通路;以及还用于选择导通所述第二列控制线组中任一列控制线与所述第一模数转换器组中一个所述模数转换器或所述第二模数转换器组中一个所述模数转换器之间的通路。

[0119] 在其中一个实施例中,开关阵列145可包括八个开关,例如开关S25、S26、S27、S28、S29、S30、S31、S32。具体的,八个开关可以为单刀双掷开关,例如,各单刀双掷开关的单端子对应与一个列控制线连接,各单刀双掷开关的两个选择端中的一个选择端与第一模数转换器组中一个所述模数转换器组中一个所述模数转换器。示例性的,八个开关S25-S32的单端子分别对应与八个列控制线C0L1-C0L8连接;开关S25、开关S26的两个选择端分别与模数转换器ADC1-1、ADC2-1连接;开关S27、开关S28的两个选择端分别与模数转换器ADC1-2、ADC2-2连接;开关S29、开关S30的两个选择端分别与模数转换器ADC1-4、ADC2-5连接。

[0120] 所述像素组还包括设置在所述第一转换电路141输出端的第五开关单元146,其中,所述第五开关单元146连接所述第一模数转换器组的一个数模转换器和所述第二模数转换器组的一个模数转换器之间。具体的,第五开关单元146可包括开关S33、开关S34。其中,当所述第五开关单元146导通时,用于执行对连接的两个所述模数转换器输出的所述数字信号的平均操作,具体的,当开关S33导通时,可以对模式转换器ADC1-1、ADC2-3读出的两个数字信号进行平均;当开关S34导通时,可以对模式转换器ADC1-3、ADC2-4读出的两个数字信号进行平均。

[0121] 为了便于说明,以如图19、20所示的图像传感器为例,对全分辨率输出模式、第一级合并输出模式中的数字平均模式的工作原理进行说明。

[0122] 全分辨率输出模式:曝光控制线TG1、TG5、TG9、TG13输入高电平,相对应的子像素W1、R1、R5、W5、W9、R9、R13、W13的转移晶体管打开,其对应的子像素W1、R1、R5、W5、W9、R9、R13、W13产生的电荷分别转移到对应的浮动扩散区FD1-FD8;随后曝光控制线TG1、TG5、TG9、TG13输入低电平,相对应的子像素W1、R1、R5、W5、W9、R9、R13、W13的转移晶体管断开。通过控制开关S1、S3、S6、S8、S17、S19、S22、S24闭合,控制开关S2、S4、S5、S7、S18、S20、S21、S23、S17-S24处于断开状态。通过控制开关S2-S32按照顺序依次连接触点1-8,也即依次连接至八个模数转换器ADC1-1-ADC2-4。具体的,子像素W1像素转移至浮动扩散区FD1中的电荷经

放大晶体管SF1转化成的模拟信号经列控制线COL1输入到模数转换器ADC1-1中,子像素R1像素转移至浮动扩散区FD2中的电荷经跟随晶体管SF2转化成的模拟信号经列控制线COL3输入到模数转换器ADC1-3中,子像素R5转移至浮动扩散区FD3的电荷经过跟随晶体管SF3转化成的模拟信号经过COL2到模数转换器ADC1-2,子像素W5转移至浮动扩散区FD4的电荷经过跟随晶体管SF4转化成的模拟信号经过列控制线COL4到模数转换器ADC1-4;子像素W9转移至浮动扩散区FD5中的电荷经过跟随晶体管SF5后转化成的模拟信号经过列控制线COL5输入到模数转换器ADC2-1中,子像素R9转移至浮动扩散区FD6中的电荷经过跟随晶体管SF6后转化成的模拟信号经过列控制线COL7入到模数转换器ADC2-3中,子像素R13像素110转移至浮动扩散区FD7的电荷经过跟随晶体管SF7转化成的模拟信号经过列控制线COL6到模数转换器ADC2-2,子像素W13像素110转移至浮动扩散区FD8电荷经过跟随晶体管SF8化成的模拟信号经过列控制线COL6到模数转换器ADC2-4。因此,可以同时读出子像素W1、R1、R5、W5、W9、R9、R13、W13的数据,也即可以同时读出两行像素单元U中的部分子像素的电荷数据。

[0123] 在此过程中,模数转换器输出的各开关可以均处于断开状态。依次类推,可以通过输出至各曝光控制线、复位控制线的电平状态,开关S1-S24的通断状态,以及开关阵列145中各开关的导通状态,可以实现对像素组中各像素以子像素为单位的方式读出各子像素的电荷数据。

[0124] 第一级合并输出模式中的数字平均模式:以子像素W1、W2、W3、W4为例进行说明。其 中,曝光控制线TG1输入高电平,以使转移晶体管导通,同时,控制开关S1导通、开关S25连通 至触点1,子像素W1转移至浮动扩散区FD1的电荷经过放大晶体管SF1转化成的模拟信号经 过列控制线COL1传输到模数转换器ADC1-1;然后对复位晶体管进行复位,以清除浮动扩散 区FD1的电荷;再控制子像素W2的转移晶体管2导通,控制开关S1导通、开关S25连通至触点 2,子像素W2转移至浮动扩散区FD1的电荷经过放大晶体管SF1转化成的模拟信号经过列控 制线COL1传输到模数转换器ADC2-1;然后对复位晶体管进行复位,以清除浮动扩散区FD1的 电荷:再控制子像素W3的转移晶体管3导通,控制开关S2导通、开关S27连通至触点3,子像素 W3转移至浮动扩散区FD1的电荷经过放大晶体管SF1转化成的模拟信号经过列控制线COL2 传输到模数转换器ADC1-2;然后对复位晶体管进行复位,以清除浮动扩散区FD1的电荷;再 控制子像素W4的转移晶体管4导通,控制开关S2导通、开关S27连通至触点4,子像素W4转移 至浮动扩散区FD1的电荷经过放大晶体管SF1转化成的模拟信号经过列控制线COL2传输到 模数转换器ADC2-2。最后,通过控制开关S17、S21、S33同时闭合,可以对模数转换器ADC1-1、 ADC1-2和ADC2-1、ADC2-2读出的各数字信号进行平均处理,以输出四个子像素W1、W2、W3、W4 的平均数字电压信号。

[0125] 本实施例中的图像传感器,通过设置开关阵列145,以及为每一行像素单元U都设置相对应的模数转换器组,可以同时读出两行像素单元U的电荷数据,进而可以提高对像素阵列中各像素110数据的读出效率。

[0126] 在其中一个实施例中,当所述多个像素组沿像素阵列的列方向一维阵列排布时,各行的所述像素组采用并行读出方式读出各所述像素组的电荷数据。示例性的,若像素组的数量为两个,可分别记为第一像素组、第二像素组,其中,第一像素组位于一行,第二像素组位于另一行。其中,位于第一像素组行的第一像素组以及位于第二像素组行的第二像素组可以采用并行读出方式同时读出第一像素组、第二像素组的电荷数据。其中,并行读出方

式可以理解为每一行的所述像素组彼此独立读出各所述像素组的数字信号。示例性的,第一像素组和第二像素组彼此独立,例如,各像素组中包括的第一转换电路、开关、列控制线等都是彼此独立分开的。也即,第二像素组可以通过复制第一像素组获得。

[0127] 需要说明的是,在本申请实施例中,多个像素组也可以在行方向进行排布,位于同一行的各子像素可连接至同一曝光控制线以及同一复位控制线。

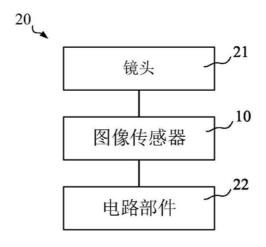

[0128] 如图21所示,本申请实施例还提供一种摄像头组件。其中,摄像头组件20包括本申请任一实施例的图像传感器10和镜头21。镜头21用于成像到图像传感器10上,例如,被摄目标的光线通过镜头21成像到图像传感器10,图像传感器10设置在镜头21的焦平面上。摄像头组件20还可包括电路部件22。电路部件22用于获取电能及与外部传输数据,例如,电路部件可与我部电源连接以获取电能,也可以和存储器、处理器连接,以传输图像数据或控制数据。

[0129] 其中,摄像头组件20可以设置在手机的背面而作为后置摄像头。可以理解地,摄像头组件20也可以设置在手机的正面作为前置摄像头。

[0130] 如图22所示,本申请实施例还提供一种移动终端。移动终端100包括本申请任一实施例的摄像头组件20和壳体80。摄像头组件20与壳体80结合。具体的,射像头组件20设置在壳体80上,壳体80包括中框和背板,摄像头组件20固定设置在中框或背板上。

[0131] 移动终端100还包括通过系统总线连接的处理器和存储器。其中,该处理器用于提供计算和控制能力,支撑整个电子设备的运行。存储器可包括非易失性存储介质及内存储器。非易失性存储介质存储有操作系统和计算机程序。内存储器为非易失性存储介质中的操作系统计算机程序提供高速缓存的运行环境。该电子设备可以是手机、平板电脑、PDA (Personal Digital Assistant,个人数字助理)、POS (Point of Sales,销售终端)、车载电脑、穿戴式设备等任意终端设备。

[0132] 以上所述实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请专利的保护范围应以所附权利要求为准。

图1

图3

图4

图5

图6

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19

图20

图21

图22