# (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) Int. Cl.

**H01L 29/786** (2006.01)

(21) 출원번호 10-2006-0052101

(22) 출원일자 **2006년06월09일** 심사청구일자 **2006년06월09일**

(56) 선행기술조사문헌 KR 1020060094479 A (뒷면에 계속) (45) 공고일자 2007년12월12일

(11) 등록번호 10-0785020

(24) 등록일자 2007년12월05일

(73) 특허권자

#### 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

#### 임혁

서울 마포구 서교동 334-13

## 박영수

경기 수원시 영통구 망포동 동수원엘지빌리지2차 204동 502호

(뒷면에 계속)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 15 항

심사관 : 최광섭

#### (54) 하부 게이트 박막 트랜지스터 및 그 제조방법

## (57) 요 약

간단하고 쉬운 공정에 의해 입경(Grain Size)이 큰 다결정 채널 영역이 형성될 수 있는 하부 게이트 박막 트랜지스터(Bottom gate TFT) 및 그 제조방법이 개시된다. 본 발명에 따른 하부 게이트 박막 트랜지스터의 제조방법은, 기판 상에 하부 게이트 전극을 형성하는 단계, 상기 게이트 전극을 덮도록 상기 기판 상에 게이트 절연막을 형성하는 단계, 상기 게이트 전극을 형성하는 단계, 상기 게이트 전극을 현상하는 단계, 상기 게이트 전극하는 순차로 형성하는 단계, 상기 게이트 전극 위에 위치된 전극층 부분 및 N형 반도체층 부분을 순차로 식각하여 상기 비정질 반도체층의 일부분을 노출시키는 단계, 상기 노출된 비정질 반도체층을 레이저 어닐링에 의해 용육시키는 단계 및 상기 용육된 비정질 반도체층을 결정화시켜 횡방향 성장된(lateral growth) 다결정 채널 영역을 형성하는 단계를 포함한다.

## **대표도** - 도1e

(72) 발명자

## 선우문욱

경기 수원시 영통구 영통동 신나무실5단지아파트 501-304

## 차영관

경기 수원시 영통구 영통동 1036-12 301호

(56) 선행기술조사문헌

KR 1020060048219 A

KR 1020000001169 A

KR 1020040031314 A

KR 1020030087560 A

KR 1020040038785 A

JP 15-123087 A

JP 07-235490 A

JP 13-320056 A

JP 14-231959 A

JP 11-274095 A

JP 02-689596 A

## 특허청구의 범위

#### 청구항 1

기판 상에 하부 게이트 전극을 형성하는 단계;

상기 게이트 전극을 덮도록 상기 기판 상에 게이트 절연막을 형성하는 단계;

상기 게이트 절연막 상에 비정질 반도체층, N형 반도체층 및 전극층을 순차로 형성하는 단계;

상기 게이트 전극 위에 위치된 전극층 부분 및 N형 반도체층 부분을 순차로 식각하여 상기 비정질 반도체층의 일부분을 노출시키는 단계;

상기 노출된 비정질 반도체층을 레이저 어닐링에 의해 용융시키는 단계; 및

상기 용융된 비정질 반도체층을 결정화시켜 횡방향 성장된(lateral growth) 다결정 채널 영역을 형성하는 단계;를 포함하는 것을 특징으로 하는 하부 게이트 박막 트랜지스터의 제조방법.

## 청구항 2

제 1 항에 있어서,

상기 비정질 반도체층은 Si 또는 SiGe으로 형성되는 것을 특징으로 하는 하부 게이트 박막 트랜지스터의 제조방 번

#### 청구항 3

제 1 항에 있어서,

상기 비정질 반도체층은 500Å 내지 1000Å의 두께로 형성되는 것을 특징으로 하는 하부 게이트 박막 트랜지스터의 제조방법.

#### 청구항 4

제 1 항에 있어서,

상기 노출된 비정질 반도체층 부분은 2 $\mu$ m 내지 5 $\mu$ m의 폭길이로 형성되는 것을 특징으로 하는 하부 게이트 박막트랜지스터의 제조방법.

#### 청구항 5

제 1 항에 있어서,

상기 N형 반도체층은 N형 불순물이 도핑된 비정질 실리콘 또는 N형 불순물이 도핑된 다결정 실리콘으로 형성된 것을 특징으로 하는 하부 게이트 박막 트랜지스터의 제조방법.

#### 청구항 6

제 1 항에 있어서,

상기 레이저 어닐링시에 레이저의 에너지 밀도는  $700 \text{mJ/cm}^2$  내지  $1000 \text{mJ/cm}^2$ 으로 제어되는 것을 특징으로 하는 하부 게이트 박막 트랜지스터의 제조방법.

## 청구항 7

제 1 항에 있어서,

상기 게이트 절연막은  ${

m SiO_2}$  또는  ${

m SiNOz}$  형성되는 것을 특징으로 하는 하부 게이트 박막 트랜지스터의 제조방법.

#### 청구항 8

제 1 항에 있어서,

상기 게이트 전극은 Al, Cr, Cu 및 Mo으로 이루어지는 그룹에서 선택된 어느 하나로 형성되는 것을 특징으로 하는 하부 게이트 박막 트랜지스터의 제조방법.

#### 청구항 9

제 1 항에 있어서,

상기 전극층은 Al, Cr, Cu 및 Mo으로 이루어지는 그룹에서 선택된 어느 하나로 형성되는 것을 특징으로 하는 하부 게이트 박막 트랜지스터의 제조방법.

#### 청구항 10

제 1 항에 있어서,

상기 기판으로 글라스 또는 플라스틱 재질의 투명기판을 이용하는 것을 특징으로 하는 하부 게이트 박막 트랜지 스터의 제조방법.

#### 청구항 11

기판 상에 형성된 하부 게이트 전극;

상기 게이트 전극을 덮도록 상기 기판 상에 형성된 게이트 절연막;

상기 게이트 절연막 상에 형성되는 것으로 상기 하부 게이트에 대응하는 것으로 다결정 채널 영역; 그리고

상기 다결정 채널 영역의 양측에 마련되는 소스 영역과 드레인 영역;을 구비하고,

상기 소스 영역과 드레인 영역 각각은, 상기 다결정 채널 영역의 양측에 마련되는 비정질 실리콘에 의한 소오스 및 드레인과, 상기 소오스와 드레인 각각 위에 마련되는 N형 반도체층 및 전극층을 구비하고,

상기 다결정 채널 영역, 소오스 및 드레인은 상기 비정질 반도체층으로부터 형성되며, 상기 다결정 채널 영역은 횡방향으로 성장되어 있는 것을 특징으로 하는 하부 게이트 박막 트랜지스터.

#### 청구항 12

제 11 항에 있어서,

상기 비정질 반도체층은 Si 또는 SiGe으로 형성되는 것을 특징으로 하는 하부 게이트 박막 트랜지스터.

## 청구항 13

제 11 항에 있어서,

상기 비정질 반도체층은 500Å 내지 1000Å의 두께로 형성되는 것을 특징으로 하는 하부 게이트 박막 트랜지스터.

## 청구항 14

제 11 항에 있어서,

상기 다결정 채널 영역의 2 $\mu$ m 내지 5 $\mu$ m의 폭 길이로 형성되는 것을 특징으로 하는 하부 게이트 박막트랜지스터.

## 청구항 15

제 11 항에 있어서,

상기 N형 반도체층은 N형 불순물이 도핑된 비정질 실리콘 또는 N형 불순물이 도핑된 다결정 실리콘으로 형성된 것을 특징으로 하는 하부 게이트 박막 트랜지스터.

## 명 세 서

## 발명의 상세한 설명

#### 발명의 목적

## 발명이 속하는 기술 및 그 분야의 종래기술

- <10> 본 발명은 박막 트랜지스터(Thin Film Transistor, 이하 'TFT'이라 함) 및 그 제조방법에 관한 것으로, 보다 상세하게는 비교적 간단하고 쉬운 공정에 의해 입경(Grain Size)이 큰 다결정 채널 영역이 형성될 수 있는 하부게이트 박막 트랜지스터(Bottom gate TFT) 및 그 제조방법에 관한 것이다.

- <11> 최근 유기발광디스플레이나 액정디스플레이의 등에 사용되는 LTPS TFT (Low termpature poly-Si)에 대한 연구가 활발히 진행되어 외부의 드라이버 IC를 완전히 없앤 SOG(System on Glass)에 대한 연구가 증가하고 있다. 외부의 드라이버 IC를 디스플레이 패널 자체에 같이 형성하여 패널과 외부 드라이버 IC 사이의 연결선이 필요 없게 되어 디스플레이의 불량이 감소하고 신뢰성이 크게 향상될 수 있다. 궁극적으로 데이터 및 게이트 드라이버 IC 뿐만 아니라 콘트롤러(controller)를 포함한 모든 디스플레이 시스템이 패널에 집적되는 SOG가 최종목표일 것이다. 이러한 목표를 달성하기 위하여 LTPS의 이동도가 400cm²/Vsec 보다 크며, 균일성도 우수 하여야 한다. 그러나 현재의 알려져 있는 ELA(Excimer Laser Annealing), SLS(Sequential Lateral Solidification), MILC(Metal-Induced Lateral Crystallization)등의 방법은 아직 소망하는 품질의 LTPS의 제조에 이르지 못하고 있다.

- <12> 다결정성 실리콘을 제조하는 방법에는 다결정성 실리콘을 직접 증착하는 방법과 비정질 실리콘을 증착한 후 이를 결정화하는 방법이 있다. 결정화에 의해 얻어진 다결정 실리콘은 입경(Grain size)이 클 수록 높은 전계 이동도(Field Effect Mobility)를 나타내며, 반면에 입경의 고른 정도 즉 균일성(Uniformity)이 떨어진다. 기존의 ELA 방법은 다결정 실리콘의 입경을 크게 하는데 한계가 있다. 이러한 한계를 넘어 수 卿의 입경을 가지는 다결정 실리콘의 제조방법이 김 등(Kim et al., ,IEEE ELECTRON DEVICE LETTERS, VOL 23, P315-317)에 의해 제시되었다. 새로운 결정화 방법은 4.6㎞ 길이의 횡적 입자(lateral grain)의 제조에 성공하였다. 이 방법은 비정질 실리콘의 결정화 속도를 제어하기 위하여 비정질 실리콘 상하의 산화물 캡핑 레이어 및 에어갭을 필요로 한다. 따라서 이 방법은 추가 공정을 요구하는데 특히 에어 갭을 얻기 위하여 별도의 희생층 형성 및 제거의 과정이 필요하고, 그리고 캡핑 레이어는 마지막 공정에서 제거되어야 한다. 이러한 추가적인 공정은 제품 양산에 부적합하며 특히 수율에 나쁜 영향을 미칠 수 있으며 나아가서는 생산 단가를 상승시키게 된다.

## 발명이 이루고자 하는 기술적 과제

<13> 본 발명이 이루고자 하는 기술적 과제는 상술한 종래기술의 문제점을 개선하기 위한 것으로, 비교적 간단하고 쉬운 공정에 의해 입경(Grain Size)이 큰 다결정 채널 영역이 형성될 수 있는 하부 게이트 박막 트랜지스터 (Bottom gate TFT) 및 그 제조방법을 제공함에 있다.

#### 발명의 구성 및 작용

- <14> 본 발명에 따른 하부 게이트 박막 트랜지스터의 제조방법은,

- <15> 기판 상에 하부 게이트 전극을 형성하는 단계;

- <16> 상기 게이트 전극을 덮도록 상기 기판 상에 게이트 절연막을 형성하는 단계;

- <17> 상기 게이트 절연막 상에 비정질 반도체층, N형 반도체층 및 전극층을 순차로 형성하는 단계;

- <18> 상기 게이트 전극 위에 위치된 전극층 부분 및 N형 반도체층 부분을 순차로 식각하여 상기 비정질 반도체층의 일부분을 노출시키는 단계;

- <19> 상기 노출된 비정질 반도체층을 레이저 어닐링에 의해 용융시키는 단계; 및

- <20> 상기 용융된 비정질 반도체층을 결정화시켜 횡방향 성장된(lateral growth) 다결정 채널 영역을 형성하는 단계;를 포함한다.

- <21> 상기 비정질 반도체층은 Si 또는 SiGe으로 형성되며, 500Å 내지 1000Å의 두께로 형성된다. 그리고, 상기 노출된 비정질 반도체층 부분은 2½m 내지 5½m의 폭길이로 형성되는 것이 바람직하며, 상기 레이저의 에너지 밀도는 700mJ/c㎡ 내지 1000mJ/c㎡으로 제어될 수 있다. 그리고, 상기 게이트 절연막은 SiO<sub>2</sub> 또는 SiN으로 형성되며, 상기 게이트 전극 및 전극층은 Al, Cr, Cu 및 Mo으로 이루어지는 그룹에서 선택된 어느 하나로 형성될 수 있다. 그리고, 상기 N형 반도체층은 N형 불순물이 도핑된 비정질 실리콘 또는 N형 불순물이 도핑된 다결정 실리콘으

로 형성될 수 있으며, 상기 기판으로 글라스 또는 플라스틱 재질의 투명기판을 이용하는 것이 바람직하다.

- <22> 본 발명에 따르면, 간단하고 쉬운 제조공정으로 전계 이동도(Field Effect Mobility) 특성이 종래보다 향상된 하부 게이트 박막 트랜지스터를 얻을 수 있다.

- <23> 이하에서는, 본 발명에 따른 하부 게이트 박막 트랜지스터의 제조방법의 바람직한 실시예를 첨부된 도면을 참조하여 상세히 설명하기로 한다. 이 과정에서 도면에 도시된 층이나 영역들의 두께는 명세서의 명확성을 위하여 과장되게 도시된 것이다.

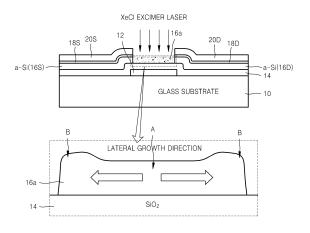

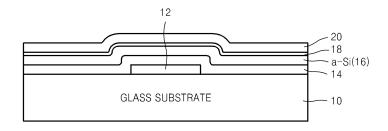

- <24> 도 1a 내지 도 1f는 본 발명에 따른 하부 게이트 박막 트랜지스터의 제조방법을 보여주는 공정도이다. 본 발명의 실시예에서, 각각의 물질층은 CVD(chemical vapor deposition) 또는 PVD(physical vapor deposition)와 같은 다양한 박막증착 방법에 의해 증착될 수 있으며, 이들 방법은 이미 널리 알려져 있으므로 이에 대한 상세한설명은 생략하기로 한다.

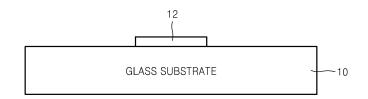

- <25> 도 1a 내지 도 1c를 함께 참조하면, 먼저 기판(10) 상에 Al, Cr, Cu 또는 Mo 등과 같은 게이트 금속을 증착/패터님하여 하부 게이트 전극(12)을 형성한다. 여기에서, 상기 기판(10)으로 글라스 또는 플라스틱 재질의 투명기판을 이용하는 것이 바람직하나, 이러한 기판의 재질은 본 발명의 범위를 제한하지 않는 것으로 한다.

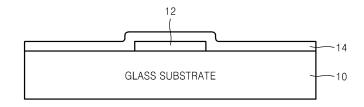

- <26> 그 다음에, 상기 게이트 전극(12)을 매립하도록 상기 기판(10) 상에 게이트 절연막(14)을 형성한 후, 상기 게이트 절연막(14) 상에 비정질 반도체층(16), N형 반도체층(18) 및 전극층(20)을 순차로 형성한다. 상기 비정질 반도체층(16)은 Si 또는 SiGe으로 형성될 수 있으며, 바람직하게 500Å 내지 1000Å의 두께로 형성된다. 이러한 두께범위는 후속되는 레이저 어닐링 공정에서 상기 비정질 반도체층(16)의 용융 및 결정화를 더 유리하게 할 뿐만 아니라, TFT 소자의 채널 영역을 형성하기 위한 가장 바람직한 두께범위일 수 있다. 상기 게이트 절연막(14)은 SiO<sub>2</sub> 또는 SiN와 같은 절연물질로 형성될 수 있다.

- <27> 상기 N형 반도체충(18)은 N형 불순물이 도핑된 비정질 실리콘 또는 N형 불순물이 도핑된 다결정 실리콘으로 형성된다. 여기에서, 상기 N형 불순물은 Sb(antimony), P(phosphorus) 또는 As(arsenic) 등과 같은 원소를 포함한다. 그리고, 상기 전극충(20)은 Al, Cr, Cu 또는 Mo 등과 같은 금속물질로 형성될 수 있다.

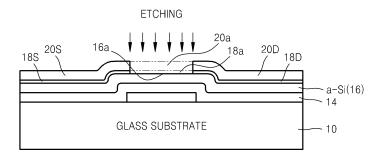

- <28> 도 1d를 참조하면, 상기 게이트 전극(12) 위에 위치된 전극층 부분(20a) 및 N형 반도체층 부분(18a)을 순차로 식각하여 상기 비정질 반도체층의 일부분(16a)을 노출시킨다. 또한, 이러한 식각공정의 진행과정에서, 상호 이 격되는 소오스 영역과 드레인 영역이 형성되는데, 이에 대하여는 후술하기로 한다.

- <29> 상기 노출된 비정질 반도체층 부분(16a)은 2/m 내지 5/m의 폭길이로 형성되는 것이 바람직하다. 이러한 길이범위는 후속되는 노출된 비정질 반도체층 부분(16a)의 결정화 공정에서 그레인(Grain) 내에 보다 적은 수의 그레인 바운더리(Grain Boundary)를 형성시키는데에 유리할 수 있다. 상기 그레인 바운더리는 채널 내에서 전자의이동도 특성에 악영향을 미치므로, 가능한 적은 수의 그레인 바운더리를 포함하도록 채널 영역을 형성하는 것이중요하다.

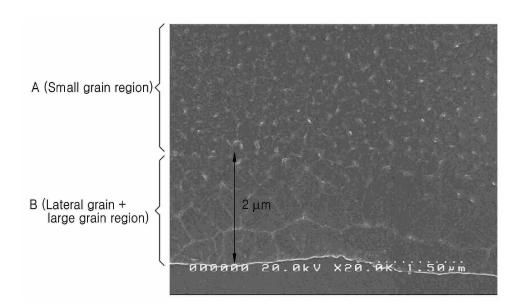

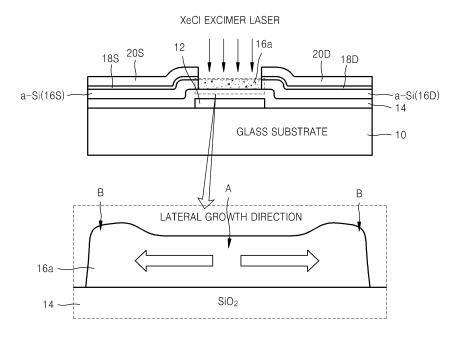

- <30> 도 1e 및 도 1f를 함께 참조하면, 상기 노출된 비정질 반도체층 부분(16a)을 레이저 어닐링에 의해 용용 (melting)시켜 결정화를 유도한다. 308mm의 파장을 가지는 XeCl 엑시머 레이저가 조사되어 상기 노출된 비정질 반도체층 부분(16a)이 가열 및 용용되면, 도시된 바와 같이 용용된 상태에서 상기 용용된 비정질 반도체층 부분 (16a)의 가운데 부분(A)과 양단 부분(B)에 있어서 두께차가 발생된다. 구체적으로 용융된 상태에서, 상기 B 부분이 A 부분 보다 더 두껍게 형성되며, 이러한 두께차는 냉각속도에 영향을 주게되어, 상기 B 부분에서 보다 상기 A 부분에서 더 빨리 냉각 및 응고(solidification) 과정이 진행될 수 있다. 따라서, 상기 A 부분에서 먼저 결정핵이 생성되며, 생성된 결정핵은 시간이 지남에 따라 A 부분에서 B 부분으로 점차 성장해 나간다. 이와 같은 결정성장의 결과로, 횡방향 성장된(lateral growth) 다결정 채널 영역(16C)이 용이하게 형성될 수 있으며, 또한 그 형성위치 및 크기도 쉽게 제어될 수 있다. 이해를 돕기 위해 도 2에 첨부된 상기 다결정 채널 영역(16C)의 SEM 사진이 함께 참조될 수 있다.

- <31> 상기 횡방향 성장 채널 영역(16C)은 큰 입경(Grain Size)으로 형성되어 높은 이동도(high mobility) 특성과 낮은 결함 밀도(low defect density)를 가진다. 따라서, 누설전류(leakage current)가 작고 스위칭 특성이 우수한 TFT 소자의 제조를 가능하게 할 수 있다. 어닐링의 효율을 높이기 위해, 상기 레이저의 에너지 밀도는 700mJ/cm² 내지 1000mJ/cm²으로 제어되는 것이 바람직하다.

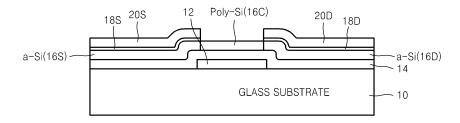

- <32> 본 발명에 따른 하부 게이트 박막 트랜지스터에서 소오스 영역은 소오스 전극(20S) 및 상기 소오스 전극(20S)과 다결정 채널 영역(16C)의 사이에 개재되어 오믹컨택을 형성하는 소오스(16S, 18S)를 포함한다. 그리고, 드레인

영역은 드레인 전극(20D) 및 상기 드레인 전극(20D)과 다결정 채널 영역(16C)의 사이에 개재되어 오믹컨택을 형성하는 드레인(16D, 18D)을 포함한다. 이와 같은 공정과정에 의해, 전계 이동도(Field Effect Mobility) 특성이 종래보다 향상된 하부 게이트 박막 트랜지스터(Bottom gate TFT) 소자를 얻을 수 있다.

## 발명의 효과

- <33> 본 발명에 따르면, 추가공정 없이 비교적 간단하고 쉬운 공정에 의해 입경(Grain Size)이 큰 다결정 채널 영역을 형성하는 것이 가능하며, 또한 그 형성되는 위치의 제어가 용이하다. 특히, 본 발명에 따르면, 횡방향 성장된(lateral growth) 다결정 채널 영역이 용이하게 형성될 수 있는데, 상기 횡방향 성장 채널 영역은 높은 이동도(high mobility) 특성과 낮은 결함 밀도(low defect density)를 가질 수 있기 때문에, 본 발명에 따라 제조되는 하부 게이트 박막 트랜지스터(Bottom gate TFT)의 전계 이동도(Field Effect Mobility) 특성이 종래보다향상될 수 있다.

- <34> 이러한 본 발명의 제조방법은 AMLCD, AMOLED, 태양전지, 반도체 메모리 소자 등의 제조에 적용되기에 적합하다. 특히 높은 이동도와 응답성을 요구하며 유리나 플라스틱을 기판으로 사용하는 TFT의 제조에 매우 적합하다. 이 러한 제조방법은 상기와 같은 AMLCD, AMOLED 외에 TFT를 스위칭 소자 또는 증폭소자 등으로 이용하는 어떤한 전 자 장치의 제조에도 적용될 수 있다.

- <35> 이상에서, 이러한 본원 발명의 이해를 돕기 위하여 몇몇의 모범적인 실시예가 설명되고 첨부된 도면에 도시되었으나, 이러한 실시예들은 예시적인 것에 불과하며 당해 분야에서 통상적 지식을 가진 자라면 상기 실시예로부터 다양한 변형 및 균등한 타 실시예가 가능하다는 점이 이해되어야 할 것이다. 따라서, 본 발명은 도시되고 설명된 구조와 공정순서에만 국한되는 것은 아니며, 특허청구범위에 기재된 발명의 기술사상을 중심으로 보호되어야할 것이다.

## 도면의 간단한 설명

- <!> 도 1a 내지 도 1f는 본 발명에 따른 하부 게이트 박막 트랜지스터의 제조방법을 보여주는 공정도이다.

- <2> 도 2는 도 1e에서 레이저 어닐링에 의해 얻은 다결정 실리콘 채널 영역의 SEM 사진이다.

- <3> < 도면의 주요부분에 대한 부호의 설명>

- <4> 10:기판 12:하부 게이트 전극

- <5> 14:게이트 절연막 16:비정질 반도체층

- <6> 16a:비정질 채널 영역 16C:다결정 채널 영역

- <7> 16S, 18S:소오스 16D, 18D:드레인

- <8> 18:N형 반도체층 20:전극층

- <9> 20S:소오스 전극 20D:드레인 전극

## 도면

## 도면1a

# 도면1b

# 도면1c

## 도면1d

# *도면1e*

## 도면1f

# 도면2