## (12) UK Patent Application (19) GB (11) 2088631 A

- (21) Application No 8135419

- (22) Date of filing 24 Nov 1981

- (30) Priority data

- (31) 212181

- (32) 2 Dec 1980

- (33) United States of America (US)

- (43) Application published 9 Jun 1982

- (51) INT CL3 H01L 29/68

- (52) Domestic classification **H1K** 1AB9 1CA 4C14 4C2D 4H3A 4H3X 9B1 9B1A 9C2 9D2 9E 9N1A 9N2 9R2 ABX CAX

- (56) Documents cited

- GB 2072422A

- GB 2050054A

- GB 2034114A

- GB 2026239A

- GB 1367325

- GB 1356670 GB 1094336

- GB 1055682

- (58) Field of search H1K

- (71) Applicant

- General Electric Company

1 River Road

Schenectady

12305

- State of New York United States of America

- (72) Inventor

Bantval Jayant Baliga

- (74) Agents

Michael Burnside & Partners

2 Serjeants' Inn

Fleet Street

London EC4Y 1HL

- (54) Field effect controlled semiconductor rectifier

- (57) A high power field effect controlled semiconductor rectifier is constructed so that the rectifier is normally off and can be switched on by applying a bias signal to a

gate 68 of a metal-insulator-semi-conductor structure monolithically integrated with the rectifier in such a manner as to induce a contacting channel including inversion layer 78 and accumulation layer 79, between the anode 62 and cathode 70 of the rectifier. The device has both forward and reverse blocking capability and a low forward voltage drop when in the conducting state. The device has a very high turn-off gain and both high dV/dt and di/dt capabilities.

ÿ

4/6

F16-15

## **SPECIFICATION**

## Gate enhanced rectifier

5 This invention relates to power field effect semi-conductor devices, and more particularly, to field controlled semiconductor rectifiers having a field effect control structure monolithically integrated with the rectifier structure.

For power switching applications, in such electrical systems as motor drives and low to medium frequency (0–2000 Hz) power supplies, high speed and low loss performance at high current and high voltage levels is desir-

15 able. Prior art three terminal devices which can be used to control power delivered to a load include the MOSFET and the MOS gated thyristor. Prior art power MOSFET's include those described in U.S. Patent No.

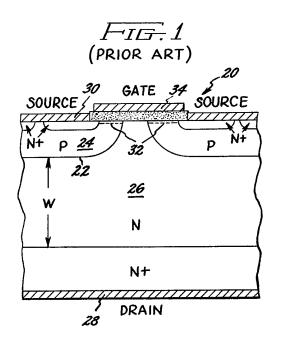

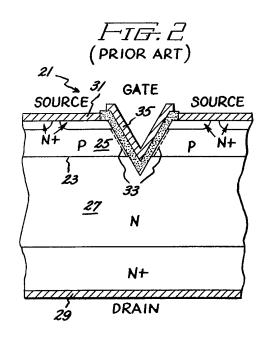

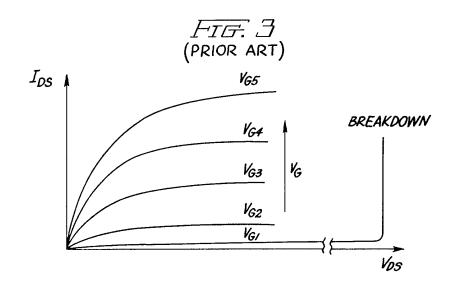

20 4,072,975, issued February 7, 1978 to Ishitani and U.S. Patent No. 4,145,703, issued March 20, 1979 to Blanchard. Typical cross sections of power MOSFET devices are shown schematically in Figs. 1 and 2 and their

25 operating characteristics are shown in Fig. 3. These devices have been fabricated by using either planar diffusion techniques to form a DMOS structure 20 as shown in Fig. 1, or by etching V-grooves to form a VMOS structure

30 21 as shown in Fig. 2. In each case, for positive voltages applied to the drain, the junctions 22, 23 between the P-base regions 24, 25 and the N-drift regions 26, 27 in Figs. 1 and 2, respectively, block current flow be-

tween the drains 28, 29 and the sources 30, 31 in the absence of gate biases. Application of a sufficiently large positive gate bias with reference to the source results in the formation of an n-type inversion layer 32, 33 in the

40 respective p-base regions under the gate electrodes 34, 35, respectively. This inversion layer allows conduction of electrical current from the drain to the source producing the forward conduction characteristics shown in

45 Fig. 3. Increasing the gate bias, e.g., from V<sub>G1</sub> through V<sub>G5</sub>, increases the conductivity of the inversion layer and thus allows higher drain current I<sub>Ds</sub> to flow. For negative voltages applied to the drain, the device conducts current

50 like a forward biased p - n junction diode and cannot block current flow. As a result, these devices are operated with only positive voltages applied to the drain.

In MOSFET devices, only majority carrier (electron) current flow occurs between drain and source. This current flow is consequently limited by the majority carrier (electrons here) concentration in the channel and drift regions which determines their resistivity. For devices

60 designed for operation at greater than 100 volts, the resistance of the drift region becomes large because the majority carrier concentration in the drift region must be small and the drift region width (W) must be large 65 in order to support the device blocking vol-

tages. Due to the high drift region resistance, high voltage MOSFET devices must be operated at low current densities to obtain low forward voltage drops. A typical current density of operation is about 50 A/cm² at a

forward voltage drop of 1.5 volts for a device capable of blocking up to 600 volts.

Despite this drawback of a high on-resistance, power MOSFET's have the advantage 75 of requiring lower gate drive power levels than bipolar transistors since the gate voltage signal is applied across an insulating film. In these devices the drain current can also be turned off by bringing the gate voltage down

80 to the source potential. This gate turn-off can be achieved with a higher current gain than for bipolar transistors.

Another type of prior art device is the MOS gated thyristor. Typical devices are disclosed 85 in British patent No. 1,356,670, published June 12, 1974, U.S. Patent No. 3,753,055, issued August 14 1973 to Yamashita et al., and U.S. Patent No. 3,831,187, issued August 20, 1974 to Neilson. A MOS gated

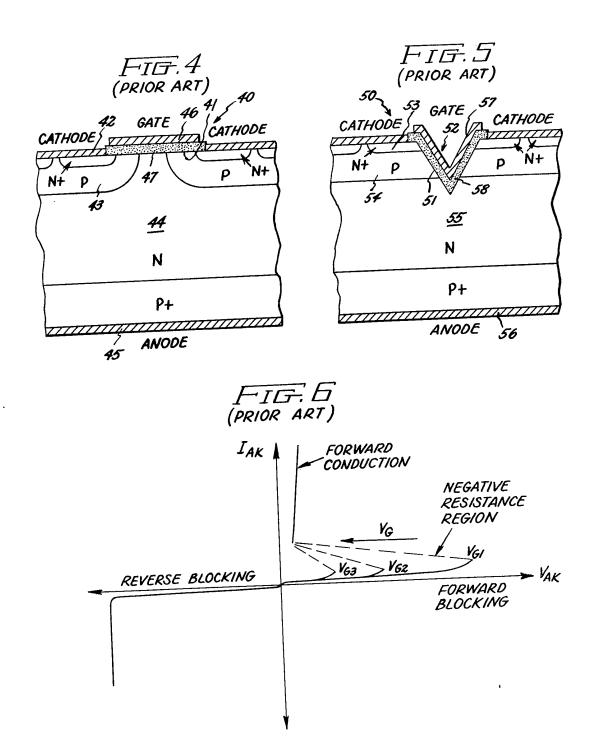

90 thyristor is a pnpn thyristor structure, shown schematically in Figs. 4 and 5, in which regenerative turn-on can be initiated by application of a voltage to an MOS gate. In the device 40 of Fig. 4, the MOS gate is formed

95 on a surface 41 extending from the N + cathode 42 through the P-base 43 into a small portion of the N-base 44. In the device 50 of Fig. 5, the MOS gate is formed on a surface 51 extending along V-groove 52 from

100 the N + cathode 53 through the P-base layer 54 into N-base 55. These devices will block current flow with either positive or negative voltages applied to their respective anodes 45, 56 in the absence of the gate bias.

105 However, for positive anode voltages the devices can be triggered into the conducting mode by application of a suitable positive voltage on the respective gates 46, 57. When a positive gate voltage is applied, the electric

110 field across the gate oxide layers 47, 58 produces a depletion of carriers in the p-base under the gate electrode. As a result, the depletion layer in the p-base extends closer to the N + cathode region under the gate. This

115 reduces the thickness of the undepleted pbase region of the upper NPN transistor under the gate electrode and thus increases its current gain. It is well known that a pnpn thyristor structure will switch from a current block-

120 ing state to a current conducting state when the sum of the current gains of the NPN and PNP transistors.  $\alpha_{\text{NPN}}$  and  $\alpha_{\text{PNP}}$ , respectively, exceeds unity. In the MOS gated thyristor, as the gate bias is increased, the gain of the

125 upper NPN transistor increases until  $\alpha_{\text{NPN}}$  +  $\alpha_{\text{PNP}}$  exceeds unity. At this point strong injection of carriers must occur from the N + cathode into the p-base for the device to switch to the on-state. This requires that the 130 N + P junction become forward biased by

ŧ

more than 0.5 volts. Once this takes place, the device switches to the conducting state and removal of the gate bias voltage will not cause the device to return to the blocking state because of the self-sustaining regenerative action inherent in the pnpn thyristor structure. Thus, these devices have the advantage of requiring low gate power to turn-on the thyristor via the MOS gate, but do not exhibit gate turn-off capability. Thus, the device must be returned to the blocking state by reversal of the anode polarity. The characteristics of the MOS gated thyristor are shown in Fig. 6, which show that these devices exhibit a negative resistance characteristic.

An object of the instant invention is to provide a field effect controlled, high current capacity rectifier that has both forward and reverse blocking capabilities and a low forward voltage drop, which can be switched on and off with a small gate voltage with very low current, and therefore, low power requirement. A further object is to provide a device which will have a very high gate turnoff gain, high di/dt capability, and a high dV/dt capability. Further objects include providing a device which will operate at elevated temperature and radiation levels without damage.

Accordingly, the instant invention incorpo-30 rates a monolithically integrated combination of a rectifier with a field effect control structure to control the on-off state of the rectifier by inducing a channel of conductivity within a region of the rectifier to control the on-off 35 condition of pn junctions with the rectifier. The rectifier includes a multiple layer structure within a body of semiconductor material having one contact on one surface of the body and another contact on another surface of the 40 body. The field effect control structure induces a channel of conductivity through one element of the rectifier to provide an electrically conductive path connecting one of the contacts with a second element of the recti-45 fier.

Embodiments of the invention will now be described, by way of example, with reference to the accompanying drawings in which like reference characters refer to like elements throughout, and in which:

Figures 1 and 2 are schematic partial crosssectional views of power MOS gated field effect transistors;

Figure 3 is a graphical illustration of the device characteristics of the transistors shown schematically in Figs. 1 and 2;

Figures 4 and 5 are schematic partial crosssectional views of MOS gated thyristors;

Figure 6 is a graphical illustration of typical device characteristics of the thyristors illustrated in Figs. 4 and 5;

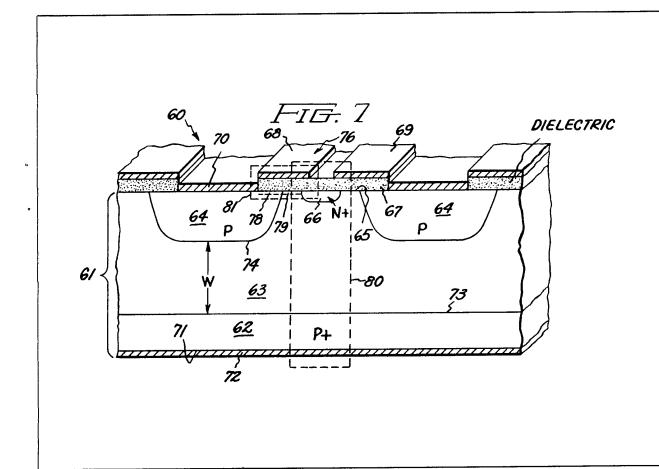

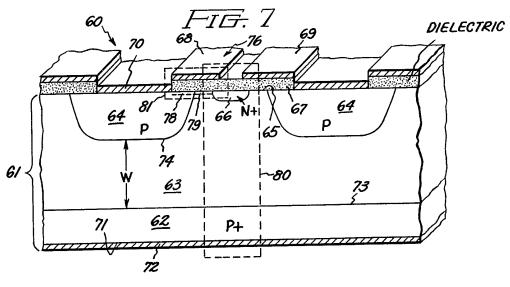

Figure 7 is a pictorial schematic partial cross-sectional view of a gate controlled rectifier according to the instant invention;

Figures 8-13 are schematic partial cross-

65

sectional views of alternate embodiments of the gate controlled rectifier according to the instant invention;

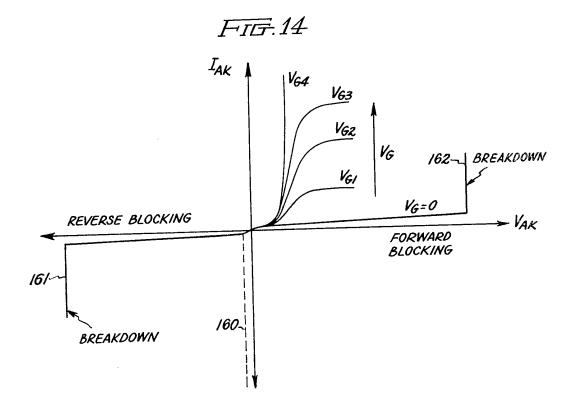

Figure 14 is a graphical representation of 70 the device characteristics of the gate controlled rectifier of the instant invention; and

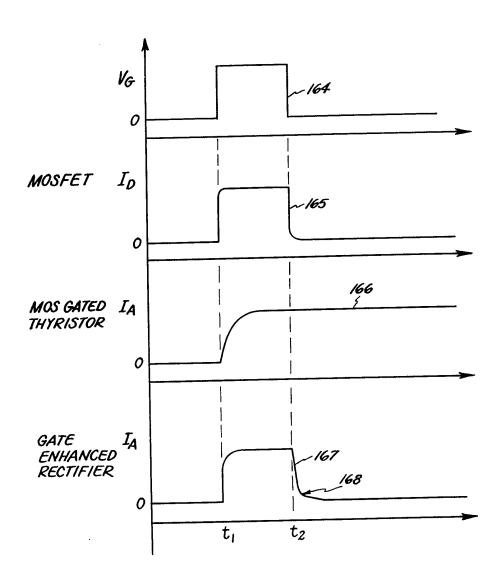

Figure 15 is a comparative graphical illustration of typical switching wave forms for the prior art devices and the gate controlled recti-75 fier of the instant invention.

One form of the basic device structure of the instant invention is illustrated in Fig. 7. The device 60 includes a body 61 of semiconductor material, such as silicon, in which a

80 first layer 62 of one type conductivity, P in Fig. 7, and a base region 63 of opposite conductivity, N in Fig. 7, is included. A first layer 62 can be made by diffusion into a body to produce the anode-base structure of the

85 device, or a body of the conductivity type desired may have a layer grown epitaxially thereover to produce the two-layer combination. A plurality of islands 64, here of P type conductivity, is provided by diffusion or other

90 suitable technique within layer 63 in spaced relationship contiguous with the free surface 65 of the body 61. Adjacent island 64, an N + island 66 is formed within the base layer 63. Typical doping levels for the N type layer

95 63 are in the range of 10<sup>13</sup> to 10<sup>16</sup> cm<sup>-3</sup> of N type carriers; for the p type anode layer 62 typical doping concentrations are in the range of 10<sup>18</sup> to 10<sup>20</sup> cm<sup>-3</sup> of P type carriers; for the P type islands 64 typical doping concen-

100 trations are 10<sup>16</sup> to 10<sup>18</sup> cm<sup>-3</sup>; and for the N + islands 66 typical doping concentrations are 10<sup>18</sup> to 10<sup>20</sup> cm<sup>-3</sup>. A layer 67 of dielectric material is formed over a portion of free surface 65 including part of the outer surface

105 of adjacent ones of the islands 64 and the region of base layer 63 separating the adjacent islands 64 including island 66. A contact 68, 69 of conductive material, such as aluminum or conductive polycrystalline silicon, is

110 formed over the dielectric layer 67 each overlapping a part of an island 64 and a part of the base layer 63 adjacent the island 64 to serve as a gate electrode. A layer 70 of conductive material such as aluminum or con-

115 ductive polycrystalline silicon is deposited over the center of each of the islands 64 to form an ohmic contact thereto. On the surface 71 of the body 61 a layer 72 of conductive material, such as aluminum or conductive

120 polycrystalline silicon, is deposited to form an ohmic contact to the layer 62. Although stripes are shown for the upper surface pattern of the conductive contacts 68, 69 and 70 in Fig. 7, it will be appreciated by those

125 skilled in the art that many repetitive geometric contact patterns, such as small contact pads arranged on the surface in closely spaced relationship, could be used. The device is highly interdigitated, e.g., the width of 130 individual stripes is small and the total num-

ber of stripes large. The pattern is repeated in the lateral direction to cover the entire semi-conductor device. Each of the conductive contacts extends to one lateral edge of the device, where the contacts 68, 69 are connected to a source of electrical potential, contacts 70 are connected to a source of electrical potential of a polarity different from that of the source connected to a source of electrical potential of a polarity different from that of the source connected to contacts 70.

the source connected to contacts 70. The device shown in Fig. 7 exhibits the operating characteristics shown in Fig. 14 and 15 operates as follows. With the contact 70 at ground potential, and no bias supplied to the gate electrode 68, negative voltages applied to the contact 72 result in no current flow because the junction 73 is reversed biased. 20 This provides reverse blocking capability. With no bias supplied to the gate electrode 68, positive voltages supplied to the contact 72 will again result in no current flow because the junction 74 will be reversed biased. This 25 provides the forward blocking capability as well as a desired normally off device characteristic. However, if a positive bias is applied to the gate electrode 68, an inversion layer extending from the ohmic contact 70 to the 30 N-base 63 can be formed under the gate in the p-phase in the region 78 of island 64 immediately beneath the insulating layer 67, and an N accumulation layer of charge carriers can be formed in the region 79 of the N

island 66 in the middle of the device. A

40 positive bias applied to the contact 72 will

now result in current flow from the P + layer

62 functioning as an anode to the N + island

66 and then via the N-type accumulation layer

79 and the N-type inversion layer 78 to the

35 base 63. The N-type inversion layer now in

connect the ohmic contact 70 to the N +

region 78 of P island 64 and the accumula-

tion layer in the region 79 of the N base now

45 contact 70 functioning as a cathode. The path from the layer 62 to the N + island 66

functions analogously to a p-i-n diode, shown at 80 in Fig. 7, and the field effect control region is outlined at 81. The conductivity of 50 the current path through the N-base 63 between the P + layer 62 and the N + island

66 will be modulated (increased) by the current flow due to injection of a high concentration of minority carriers (holes here) into the N-base 63 from the layer 62. Since the voltage is supported across the N base 63 in the forward and reverse blocking modes, the

width W of the path between the P + layer 62 and the P island 64 determines the maxi-60 mum blocking voltages. For high voltage performance this width must be increased. The conductivity modulation flow is consequently very important for achieving a low forward voltage drop at high forward current densities

65 in high voltage devices. A typical forward

current density of operation is about 500 A/cm² at a forward voltage dop of 1.5 volts for a device capable of blocking up to 600 volts. If all the conductivity types are re-

70 versed, similar performance characteristics can be obtained with electrical potentials of opposite polarities applied to the conductive contacts.

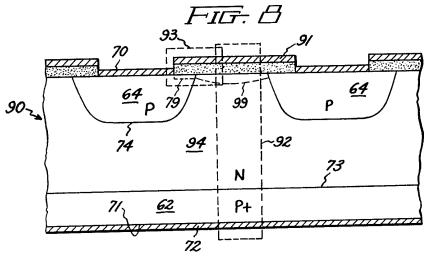

An alternative embodiment of the gate con-75 trolled rectifier of the instant invention is shown schematically in Fig. 8. The device 90 of Fig. 8 differs from that of Fig. 7 in omitting N + island 66. The elimination of the island 66 requires that adequate potential be applied

80 to gate contact 91 to create an accumulation layer 99 under dielectric layer 67 to produce a region of N type carriers below the gate. To accomplish this with the lowest spreading resistance in the path of current flow beneath

85 the gate requires that a gate contact 91 extend across the entire width of the gate region connecting the adjacent islands 64. A contact of lesser width would create the necessary accumulation layer 99 of N carriers

90 beneath the gate to provide the function of the N + islands 66, when adequate potential is applied to the gate. This decrease in the area of the gate will result in a decrease in the gate capacitance. When a positive bias is

95 applied to the gate of the field effect control structure outlined at 93, a three layer structure is formed in the region outlined by dashed rectangle 92 which functions as a pin structure. The current path through the

100 rectifier includes the layer 62, n base region 94, n accumulation layer 99, an inversion layer 79 and ohmic contact 70.

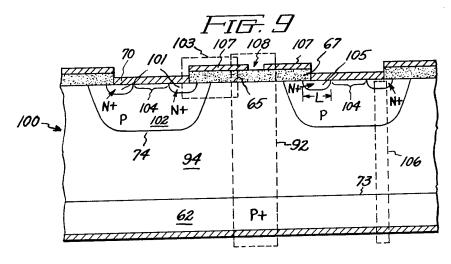

A further alternative embodiment of my invention is schematically illustrated in Fig. 9.

105 The device 100 includes P region 62, base region 94, P islands 102 and a plurality of N + islands 101 within each of the P islands 102. In this embodiment, the islands 101 provide a contact between the inversion layer

110 in the islands 102 and the conductive contact 70. A pair of conductive contacts 107 separated by gap 108 is disposed on dielectric layer 67 to overlap a portion of the islands 101, a region of the islands 102 and a

115 portion of the base 94. Application of a positive gate bias to a control electrode 107 within dashed outline 103 will produce an accumulation layer in the N base region immediately under the gate, and an inversion

120 layer in the P island 102 immediately under the dielectric layer 67 extending from the N + island 101 to the N-base 94 completing the current path from the N base through the P island 102 to the N + island 101. This

125 structure includes a parasitic p-n-p-n thyristor through the anode 62, base 94, P island 102 and n + islands 101 in the region outlined at 106. To achieve the desired device performance of this device in switching off removal

130 of the gate bias, it is very important that the

regenerative turn-on mechanism in this parasitic thyristor be suppressed.

This can be accomplished by preventing the N + islands 101 from injecting electrons into 5 the respective P islands 102, consequently preventing the initiation of the regenerative turn-on mechanism of the p-n-p-n thyristor. The suppression of the injection of carriers from the N + islands 101 can be accom-10 plished by forming the N + islands 101 with a small lateral dimension (L). The lateral dimension (L) of the N + islands 101 must be small enough so that, when the device is conducting current from the channel 78 to the 15 cathode contact 70, the forward bias of the junction 105 between the N + islands 101 and the P-island 102 does not exceed 0.5 volts. Another technique which could be used to suppress the regenerative turn-on of the p-20 n-p-n thyristor is the introduction of recombination centers in the p-region 102 and the Nbase 94 so as to reduce the gains  $\alpha_{\text{NPN}}$  and  $\alpha_{\text{PNP}}$ . Recombination centers can be provided by diffusion of deep level impurities, such as 25 gold, into the substrate or by irradiation of the substrate with high energy particles such as electrons.

Distinguishing features between an MOS gated thyristor, such as that shown in Fig. 4, 30 and the device of this invention, shown in Fig. 9, are firstly, that the device of this invention, contains N + regions 101 of much smaller lateral dimension (L) to prevent the regenerative turn-on action characteristic of the MOS 35 gated thyristor. Secondly, in the gate enhanced rectifier, the anode current flows solely via the conductive channel formed in the P-island 102 to the cathode contact 70 when the device is conducting current, while 40 the current of the MOS gated thyristor flows vertically throughout the P-island 102 underneath the N + island 101. Thirdly, in the gate enhanced rectifier, the anode current can be terminated by removal of the gate voltage 45 applied to induce the conducting channel in the P-islands 102, while the anode current of the MOS gated thyristor will continue to flow after removal of the gate voltage due to the self-sustaining nature of the regenerative pnpn 50 thyristor action. It is noted that the embodiment in Fig. 8 avoids this problem by elimination of the N + islands within the P islands 102.

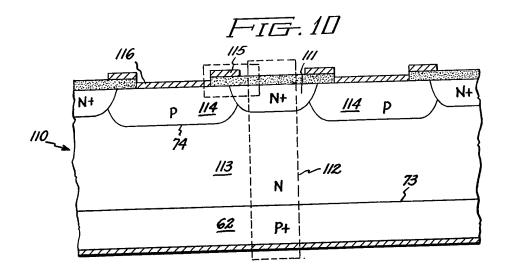

In the alternative embodiment shown in Fig. 10, N + island 111 filling the entire width between adjacent P islands 114 and the N base 113 and impinging upon a portion of the P islands is formed in the N base. When a positive bias is applied to the gate 115 an inversion layer is created in the region of the P islands immediately under the gate and the current path from the N + island 111 to the cathode contact 116 is completed, thereby turning the device on and allowing current to flow through the p-i-n diode out-

lined at 112 and via the inversion layer to the cathode contact 116.

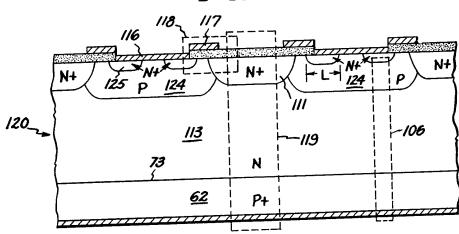

In the embodiment shown in Fig. 11, N + islands 125 have been added to the P islands 70 124 of the device 120 which provide current flow paths from the inversion layer in P-islands 124 to the conductive contact 116, when a positive bias is applied to electrode 117 in gate structure 118 to turn on the p-i-n

75 diode 119. This embodiment also contains the parasitic pnpn thyristor described with reference to the embodiment shown in Fig. 9. As discussion earlier with reference to Fig. 9, the regenerative turn-on mechanism of this

80 parasitic thyristor must be suppressed by maintaining a small lateral dimension (L) for the N + island 125 and by providing recombination centers in the P-islands 124 and the N-base 113. It is noted that the embodiment 85 of Fig. 10 avoids this problem by elimination

of the n + islands within the p islands 102.

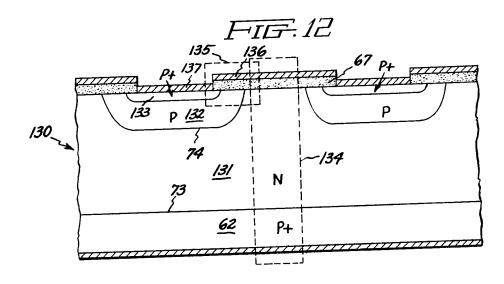

In device 130 shown schematically in Fig.

12, highly doped P + islands 133 have been added to the P islands 132 in the N base

90 131. The current path includes the p-i-n diode 134 created when a positive bias relative to the conductive contact 137 is applied to the gate 136 in the gate controlled structure 135 to produce an accumulation layer immediately

95 under the dielectric layer 67. An inversion layer is produced in P island 132 between the P + island 133 and the N-base 131 to allow current flow from the anode to the cathode.

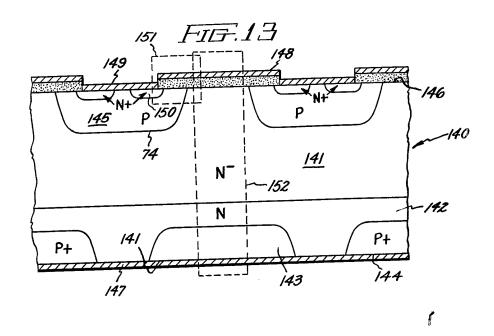

A further alternative device structure em-100 ploying my invention is shown schematically in Fig. 13. The body of semiconductor material for device 140 has a lightly doped N-base region 141 and a more heavily doped N region 142. Within base region 142 P +

105 islands 143 are formed adjacent to one major free surface 144 of the body. P islands 145 are formed into the N-region 141 and the N + islands 150 are formed into the P islands 145 adjacent the other major surface

110 146 of the body. For a given forward conduction current density this structure provides a lower forward voltage drop in the diode 152 than the previously described embodiments for the same forward blocking capability.

115 However, the reverse blocking capability is reduced due to the shorting of the islands 143 by conductive contact 147. The operating characteristics of this device are similar to those of the other embodiments when a for-

120 ward bias is applied. When a reverse bias is applied to the conductive contact 147 in the absence of a bias on gate electrode 148 in gate controlled structure 151, a substantially different characteristic is produced as shown

125 at 160 in Fig. 14, in that breakdown occurs at a much lower reverse bias.

The operating characteristics of the gate controlled rectifier are shown in Fig. 14. In this device, the junction 73 blocks current 130 flow when negative voltages are applied to

the anode contact 72 providing the device with reverse blocking capability up to the level at which breakdown occurs as seen at 161. When positive voltages are applied to the 5 anode contact 72, the junction 74 becomes reverse biased and blocks current flow, thus providing the forward blocking capability in the absence of gate bias up to the level at which breakdown occurs as seen at 162.

10 However, if a positive bias is applied to the gate a path is greated for the current to flow

However, if a positive bias is applied to the gate, a path is created for the current to flow from the anode junction 73 to the cathode contact 70 producing the characteristics shown for each of the gate voltages V<sub>G1</sub>-V<sub>G4</sub>.

At large gate voltages (V<sub>G4</sub>) the inversion layer

conductivity will be high and the device will exhibit characteristics like those of a pn junction diode. In this case the anode P + region injects minority carriers into the n-base and strongly modulates (increases) the conductivity

ity of the n-base. As a result of this, the device can be operated at high current densities (typically 500 A/cm²) with a low forward voltage drop (about 1.5 volts). At lower gate

voltages (V<sub>G1</sub>, V<sub>G2</sub>, V<sub>G3</sub>), the current flow can become limited by the conductivity of the inversion layer producing the current saturation shown in Fig. 14. These device characteristics are distinguishable from those of other

prior art devices. When compared with the

MOSFET, the gate enhanced rectifier can be operated at much higher current densities due to the modulation of the conductivity of the N-base by the anode current flow. Unlike the

35 MOSFET, these devices also exhibit reverse blocking capability. When compared with the MOS gated thyristor, the gate enhanced rectifier is distinguished by the absence of a negative resistance region in the forward char-

O acteristics. This negative resistance region in the thyristor arises from the regenerative turnon phenomenon which is absent in the gate enhanced rectifier.

Unlike the MOS gated thyristor, no selfsustaining regenerative turn-on occurs in the

gate enhanced rectifier device. Consequently,

if the gate voltage is reduced to the cathode

potential while the device is conducting current, the inversion layer under the gate electrode will cease to exist and the anode current

will turn off. This turn-off occurs in two

stages. First, most of the injected stored

charge in the N-base is removed by current

flow across the junction 74 to P region 145

until it becomes reverse biased. After this

point, the rest of the minority carrier stored

charge will decay by recombination.

A comparison of the switching characteristic of the MOSFET, the MOS gated thyristor and the gate enhanced rectifier can be done with the aid of Fig. 15. In this figure, the gate voltage is turned on at times t<sub>1</sub> and turned off at time t<sub>2</sub> for all three cases as shown by trace 164. At time t<sub>2</sub>, the MOSFET turns off rapidly as seen in trace 165 the duration of the turn-

off transient being determined by the charging of the gate capacitance. However, the MOS gated thyristor continues to conduct current even after the gate voltage is reduced to zero

70 at time t<sub>2</sub> as shown by trace 166, because the current flow is sustained by the internal regenerative mechanism in these devices. In contrast, the gate enhanced rectifier turns off at time t<sub>2</sub> as shown by trace 167 because the

75 inversion layer under the gate electrode will cease to exist when the gate voltage is reduced to zero and this will interrupt the current flow path between the anode and cathode terminals. In this case, the minority carri-

80 ers injected by the anode into the N-base to modulate its conductivity during forward current conduction will be removed by conduction across junction 74 until it becomes reverse biased as shown at point 168. Any

85 remaining minority carriers will then decay by combination. Consequently, the gate enhance rectifier turns off at time t<sub>2</sub> like the MOSFET but does so more slowly due to the bipolar current conduction. It should be noted that

90 this slower switching speed of the gate enhanced rectifier is adequate for many applications such as motor drives, while its low forward voltage drop when compared with the MOSFET is a major advantage, because it

95 reduces the power dissipated and thus improves the power switching efficiency. Other advantages are better surge current handling capability, higher operating temperature capability and elevated radiation level tolerance

100 made possible by the suppression of regenerative turn-on described above.

## **CLAIMS**

A gate enhanced rectifier apparatus

comprising:

a body of semiconductor material;

a rectifier disposed within said body and having a first electrically conductive means contacting a first free surface of said body and

110 a second electrically conductive means contacting a second free surface of said body; and

a field effect control means disposed adjacent said rectifier such that a control electrode 115 of said control means is disposed adjacent a region of said rectifier of one type conductivity for controlling the on-off condition of said rectifier by inducing a channel of opposite conductivity through said region of said recti-120 fier.

2. The rectifier apparatus as claimed in claim 1, wherein rectifier comprises;

a first layer of said body of semiconductor material adjacent said first free surface of said

125 body and having one type conductivity; a second layer of said body of semiconductor material disposed contiguous with said first layer and having a conductivity type opposite that of said first layer;

130 a first island formed within said second

layer spaced from said first layer; said first island having said one type conductivity;

said first electrically conductive means contacting a free surface of said first layer;

said second electrically conductive means contacting a free surface of said first island; and

a third electrically conductive means comprising said control electrode of said control means

- The rectifier apparatus as claimed in claim 2, wherein said field effect control means comprises a gate electrode disposed proximate said first island of said rectifier for inducing a channel of opposite type conductivity through said first island; said gate electrode being separated from said first island by a layer of dielectric material.

- The rectifier apparatus as claimed in

claim 3, wherein said field effect control means comprises means for generating a channel of opposite type conductivity within said first island extending from said second electrically conductive means to said second

layer of said body of said semiconductor material upon application of a bias signal to said gate electrode.

- The rectifier apparatus as claimed in claim 3 or 4 further including a second island

of semiconductor material of said opposite type conductivity disposed within said second layer and immediately adjacent said dielectric layer.

- 6. The rectifier apparatus as claimed in 35 claim 5, wherein said second island impinges upon said first island.

- 7. The rectifier apparatus as claimed in any one of claims 3-6, wherein said field effect control means further includes means

40 for inducing an accumulation layer of said opposite type conductivity within said second layer and immediately adjacent said dielectric layer

- 8. The rectifier apparatus as claimed in 45 claim 5, 6 or 7, further including a third island of semiconductor material of said opposite type conductivity disposed within said first island and continguous with said second electrically conductive means.

- 9. The rectifier apparatus as claimed in any one of claims 4 to 8, further including a heavily doped island of said one type conductivity disposed within said first island contiguous with said second electrically conductive means.

- 10. The rectifier apparatus as claimed in claim 1, wherein

- said body of semiconductor material has a first layer contiguous with a first free face of said body and a second layer contiguous with a second free face of said body opposite said first free face and contiguous with said first layer;

- a first island within said second layer 65 spaced from said first layer and contiguous

with said second free face of said body;

said field effect control means forming a

conductive channel within said first island

adjacent said second free face of said body in

response to the application of a control signal

to said gate controlled means;

a first electrically conductive means for electrically contacting said first layer;

a second electrically conductive means for 75 electrically contacting said first island; and a third electrically conductive means for applying said control signal to said field effect control means.

11. The rectifier apparatus as claimed in 80 claim 10, wherein:

said first layer comprises a semiconductor material of one type conductivity;

said second layer comprises a semiconductor material of an opposite type conductivity 85 to that of said first layer;

said first island comprises a region of semiconductor material of said one type conductivity within said second layer; and

said field effect control means comprises

90 field effect means for forming a channel of

said opposite type conductivity within said

first island adjacent said field effect control

means; said channel connecting said second

electrically conductive means to said second

95 laver.

12. The rectifier apparatus as claimed in claim 11, wherein said field effect control means comprises a layer of dielectric material partially overlying said first island and overly-

- 100 ing a gate region of said second layer adjacent said first island and said third electrically conductive means overlying at least part of said layer of dielectric material and partially overlying said first island and at least partially 105 overlying said gate region.

- 13. The rectifier apparatus as claimed in claim 11, further including:

- a second island of semiconductor material heavily doped with carriers of said opposite 110 type conductivity disposed adjacent said first island within said gate region adjacent said field effect control means.

- 14. The rectifier apparatus as claimed in claim 13, wherein said second island of semi115 conductor material adjacent said first island is spaced therefrom; and said field effect control means further includes means for forming an accumulation layer of current carriers of said opposite type conductivity for making electri120 cal connection between said channel and said

- second island.

15. The rectifier apparatus as claimed in claim 13, wherein said second island im-

- pinges upon said first island and said field 125 effect control means comprises means for inducing a channel of said opposite type conductivity within said first island electrically connecting said second electrically conductive means and said second island.

- 130 16. The rectifier apparatus as claimed in

:

5

Ě

claim 12, further including:

a plurality of said first islands disposed in spaced relationship within said second layer contiguous with said second free face of said body; each of said first islands extending in a stripe along one full dimension of said body; a plurality of said second electrically conductive means each extending in a strip contiguous with and overlying a part of one of said first 10 islands, respectively, and each of said second electrically conductive means being connected to a common source of electrical potential;

a plurality of said field effect control means each overlying a part of one of said first

15 islands, respectively; each of said field effect control means including one of a plurality of said electrically conductive control electrodes connected to a common source of electrical potential; each of said control electrodes

20 formed upon a respective one of a plurality of stripes of dielectric material formed upon said second free face of said body and each extending in a stripe overlying at least a part of a respective one of a plurality of said gate

25 regions; and each of said control electrodes overlying a part of the respective one of said first islands adjacent said one of said gate regions.

17. The rectifier apparatus as claimed in 30 claim 16, wherein:

said first electrically conductive means comprises a layer of aluminum formed upon said free face of said body;

each of said second electrically conductive 35 means comprises a stripe of aluminum formed upon an outermost surface of a respective one of said plurality of said first islands; and

said third electrically conductive means comprises a stripe of aluminum formed upon 40 an outermost surface of a respective one of said stripes of dielectric material.

18. The rectifier apparatus as claimed in claim 16 wherein:

said first electrically conductive means comprises a layer of conductive polycrystalline silicon formed upon said one free face of said body;

each of said second electricaly conductive means comprises a stripe of conductive poly-50 crystalline silicon formed upon an outermost surface of a respective one of said plurality of said first islands; and

each of said third electrically conductive means comprises a stripe of conductive poly-55 crystalline silicon formed upon an outermost surface of a respective one of said stripes of dielectric material.

19. The rectifier apparatus as claimed in claim 1, wherein

60 said body of semiconductor material comprises a first region of one type conductivity and a second region doped heavily relative to said first region with carriers of said one type conductivity;

65

a first island of a conductivity type opposite

that of said one type conductivity is disposed contiguous with a first free face of said body within said second region,

a second island of said opposite type con-70 ductivity disposed within said first region spaced from said second region and contiguous with a second free face of said body opposite said first free face;

a first electrically conductive means contact-75 ing said one free face of said body;

a second electrically conductive means contacting said second island; and

said field effect control means for induces a channel of said one type conductivity in said 80 second island adjacent said field effect control

means and extends from said second conductive means to said first region upon application of a field effect control signal to said field effect control means.

85 20. A gate enhanced rectifier substantially as described herein with reference to Figs. 7 to 15 of the accompanying drawings.

Printed for Her Majesty's Stationery Office by Burgess & Son (Abingdon) Ltd.—1982. Published at The Patent Office, 25 Southampton Buildings, London, WC2A 1AY, from which copies may be obtained.