# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2011/0153657 A1 **Pandya**

### (54) FSA EXTENSION ARCHITECTURE FOR PROGRAMMABLE INTELLIGENT SEARCH **MEMORY**

(76) Inventor: Ashish A. Pandya, El Dorado Hills,

CA (US)

13/006,265 (21) Appl. No.:

(22) Filed: Jan. 13, 2011

## Related U.S. Application Data

Continuation of application No. 11/952,110, filed on Dec. 6, 2007, now Pat. No. 7,899,976.

(60) Provisional application No. 60/965,267, filed on Aug. 17, 2007, provisional application No. 60/965,170, filed on Aug. 17, 2007, provisional application No. 60/963,059, filed on Aug. 1, 2007, provisional application No. 60/961,596, filed on Jul. 23, 2007, provisional application No. 60/933,313, filed on Jun. 6, 2007, provisional application No. 60/933,332, filed on Jun. 6, 2007, provisional application No. 60/930,607, filed on May 17, 2007, provisional application No. 60/928,883, filed on May 10, 2007, provisional application No. 60/873,632, filed on Dec. 8, 2006, provi-

Jun. 23, 2011 (43) Pub. Date:

sional application No. 60/873,889, filed on Dec. 8, 2006.

#### **Publication Classification**

(51) Int. Cl. G06F 17/30 (2006.01)

(52)**U.S. Cl.** ...... 707/769; 707/E17.014

(57)**ABSTRACT**

Memory architecture provides capabilities for high performance content search. The architecture creates an innovative memory that can be programmed with content search rules which are used by the memory to evaluate presented content for matching with the programmed rules. When the content being searched matches any of the rules programmed in the Programmable Intelligent Search Memory (PRISM) action (s) associated with the matched rule(s) are taken. Content search rules comprise of regular expressions which are converted to finite state automata (FSA) and then programmed in PRISM for evaluating content with the search rules. PRISM architecture comprises of a plurality of programmable PRISM Search Engines (PSE), each capable of supporting a predetermined size FSAs. FSA extension architecture is created to extend the predetermined size limit of an FSA supported by PSE, by coupling multiple PSEs together to behave as a composite PSE to support larger FSAs.

**PRISM Memory Cluster Block Diagram**

Fig. 5a State transition logic (STL) for a state in Left-biased FSA

Fig. 5b State transition logic (STL) for a state in Right-biased FSA

Fig. 7 PRISM Block Diagram

Fig. 8a PRISM Memory Cluster Block Diagram

Fig. 8b PRISM Memory Cluster Detailed Block Diagram

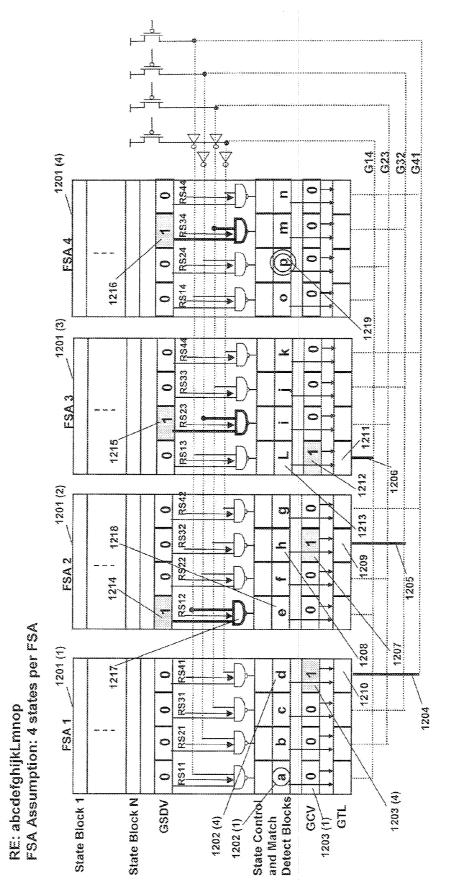

Fig. 11 PRISM Row-Wise FSA Extension

Fig. 12 PRISM Row-Wise FSA Extension Example #1

~1313 G23 G23 G41 1301 (4) FSA 4 0 1312 0 1301 (3) 1311 RS4 RS33 1310 0 1304 FSA 3 1309 RS13 0 1301 (2) RS4 FSA 2 1315 1308 RS12 T RE: (abc | defghi)+ jkl. FSA Assumption: 4 states per FSA 1303 1301 (1) 1307 RS4 O RS31 1306 RS21 0 0 RS11 (R State Control and Match Detect Blocks State Block 1 State Block N GSDV SCV GTE 1302

Fig. 13 PRISM Row-wise FSA Extension Example #2

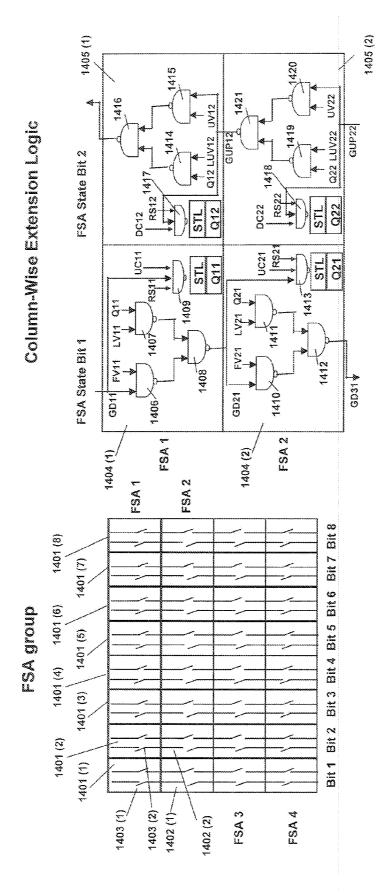

Fig. 14 PRISM Column-Wise FSA Extension

Forward Vector - Down

Local Forward Vector - Down Forward Vector - Up ÖĞĞĞĞĞĞ

Local Forward Vector -- Up

Up Control Vector Down Control Vector

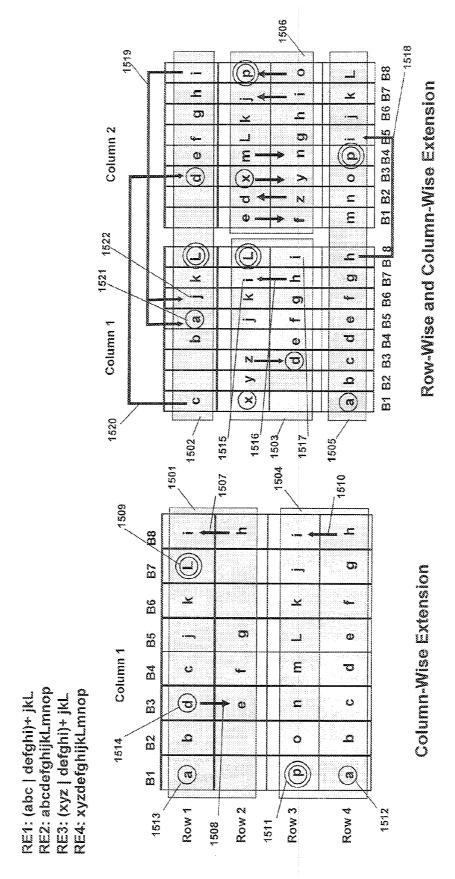

Fig. 15 PRISM FSA Extension Example #1

RE: (abc | defghi | Lmnopqrstuv)+ jkL

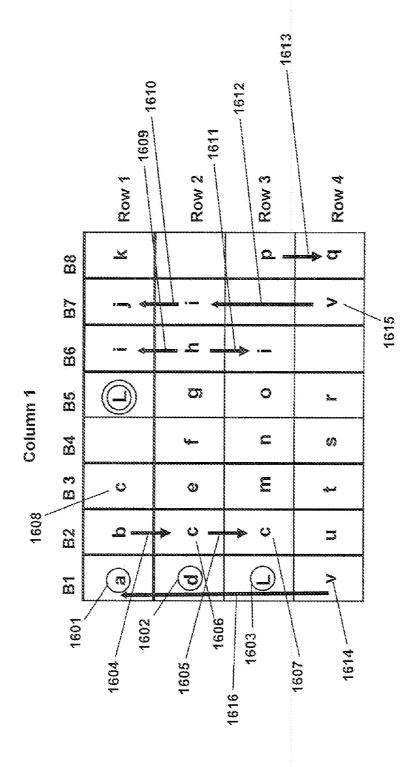

Fig. 16a Column-Wise PRISM FSA Extension Example

RE: (abc | defghi | Lmnopqrstuv)+ jkL

Fig. 16b Row-wise and Column-Wise PRISM FSA Extension Example

# FSA EXTENSION ARCHITECTURE FOR PROGRAMMABLE INTELLIGENT SEARCH MEMORY

#### RELATED APPLICATIONS

[0001] This application is a continuation of U.S. patent application Ser. No. 11/952,110, filed Dec. 6, 2007, which claims priority to Provisional Application Serial No. 60/965, 267 filed on Aug. 17, 2007 entitled "Embedded programmable intelligent search memory", Provisional Application Serial No. 60/965,170 filed on Aug. 17, 2007 entitled "100 Gbps security and search architecture using programmable intelligent search memory", Provisional Application Ser. No. 60/963,059 filed on Aug. 1, 2007 entitled "Signature search architecture for programmable intelligent search memory", Provisional Application Serial No. 60/961,596 filed on Jul. 23, 2007 entitled "Interval symbol architecture for programmable intelligent search memory", Provisional Application Ser. No. 60/933,313 filed on Jun. 6, 2007 entitled "FSA context switch architecture for programmable intelligent search memory", Provisional Application Ser. No. 60/933, 332 filed on Jun. 6, 2007 entitled "FSA extension architecture for programmable intelligent search memory", Provisional Application Ser. No. 60/930,607 filed on May 17, 2007 entitled "Compiler for programmable intelligent search memory", Provisional Application Ser. No. 60/928,883 filed on May 10, 2007 entitled "Complex symbol evaluation for programmable intelligent search memory", Provisional Application Ser. No. 60/873,632 filed on Dec. 8, 2006 entitled "Programmable intelligent search memory", Provisional Application Ser. No. 60/873,889 filed on Dec. 8, 2006 entitled "Dynamic programmable intelligent search memory", which are all incorporated herein by reference in their entirety as if fully set forth herein.

[0002] U.S. patent application Ser. No. 11/952,110, filed Dec. 6, 2007 also claims priority to U.S. patent application Ser. No. 11/952,028 filed on Dec. 6, 2007 entitled "Embedded programmable intelligent search memory", U.S. patent application Ser. No. 11/952,043 filed on Dec. 6, 2007 entitled "100 Gbps security and search architecture using programmable intelligent search memory"; U.S. patent application Ser. No. 11/952,103 filed on Dec. 6, 2007 entitled "Signature search" architecture for programmable intelligent search memory", U.S. patent application Ser. No. 11/952,104 filed on Dec. 6, 2007 entitled "Interval symbol architecture for programmable intelligent search memory", U.S. patent application Ser. No. 11/952,108 on Dec. 6, 2007 entitled "FSA context switch architecture for programmable intelligent search memory", U.S. patent application Ser. No. 11/952,111 filed on Dec. 6, 2007 entitled "Compiler for programmable intelligent search memory", U.S. patent application Ser. No. 11/952,112 filed on Dec. 6, 2007 entitled "Complex symbol evaluation for programmable intelligent search memory", U.S. patent application Ser. No. 11/952,114 filed on Dec. 6, 2007 entitled "Programmable intelligent search memory"; U.S. patent application Ser. No. 11/952,117 filed on Dec. 6, 2007 entitled "Dynamic programmable intelligent search memory" which are all co-pending U.S. patent applications of common ownership.

## BACKGROUND OF THE INVENTION

[0003] This invention relates generally to memory technology and in particular to a new high performance intelligent content search memory and a regular expression compiler for it.

[0004] Many modem applications depend on fast information search and retrieval. With the advent of the world-wideweb and the phenomenal growth in its usage, content search has become a critical capability. A large number of servers get deployed in web search applications due to the performance limitations of the state of the art microprocessors for regular expression driven search.

[0005] There have been significant research and development resources devoted to the topic of searching of lexical information or patterns in strings. Regular expressions have been used extensively since the mid 1950s to describe the patterns in strings for content search, lexical analysis, information retrieval systems and the like. Regular expressions were first studied by S. C. Kleene in mid-1950s to describe the events of nervous activity. It is well understood in the industry that regular expression (RE) can also be represented using finite state automata (FSA). Non-deterministic FSA (NFA) and deterministic FSA (DFA) are two types of FSAs that have been used extensively over the history of computing. Rabin and Scott were the first to show the equivalence of DFA and NFA as far as their ability to recognize languages in 1959. In general a significant body of research exists on regular expressions. Theory of regular expressions can be found in "Introduction to Automata Theory, Languages and Computation" by Hoperoft and Ullman and a significant discussion of the topics can also be found in book "Compilers: Principles, Techniques and Tools" by Aho, Sethi and Ullman.

[0006] Computers are increasingly networked within enterprises and around the world. These networked computers are changing the paradigm of information management and security. Vast amount of information, including highly confidential, personal and sensitive information is now being generated, accessed and stored over the network. This information needs to be protected from unauthorized access. Further, there is a continuous onslaught of spam, viruses, and other inappropriate content on the users through email; web access, instant messaging, web download and other means, resulting in significant loss of productivity and resources.

[0007] Enterprise and service provider networks are rapidly evolving from 10/100 Mbps line rates to 1 Gbps, 10 Gbps and higher line rates: Traditional model of perimeter security to protect information systems pose many issues due to the blurring boundary of an organization's perimeter. Today as employees, contractors, remote users, partners and customers require access to enterprise networks from outside, a perimeter security model is inadequate. This usage model poses serious security vulnerabilities to critical information and computing resources for these organizations. Thus the traditional model of perimeter security has to be bolstered with security at the core of the network. Further, the convergence of new sources of threats and high line rate networks is making software based perimeter security to stop the external and internal attacks inadequate. There is a clear need for enabling security processing in hardware inside core or end systems beside a perimeter security as one of the prominent means of security to thwart ever increasing security breaches and attacks.

[0008] FBI and other leading research institutions have reported in recent years that over 70% of intrusions in organizations have been internal. Hence a perimeter defense relying on protecting an organization from external attacks is not sufficient as discussed above. Organizations are also required to screen outbound traffic to prevent accidental or malicious disclosure of proprietary and confidential information as well

as to prevent its network resources from being used to proliferate spam, viruses, worms and other malware. There is a clear need to inspect the data payloads of the network traffic to protect and secure an organization's network for inbound and outbound security.

[0009] Data transported using TCP/IP or other protocols is processed at the source, the destination or intermediate systems in the network or a combination thereof to provide data security or other services like secure sockets layer (SSL) for socket layer security, Transport layer security, encryption/ decryption, RDMA, RDMA security, application layer security, virtualization or higher application layer processing, which may further involve application level protocol processing (for example, protocol processing for HTTP, HTTPS, XML, SGML, Secure XML, other XML derivatives, Telnet, FTP, IP Storage, NTS, CIFS, DAPS, and the like). Many of these processing tasks put a significant burden on the host processor that can have a direct impact on the performance of applications and the hardware system. Hence, some of these tasks need to be accelerated using dedicated hardware for example SSL, or TLS acceleration. As the usage of XML increases for web applications, it is creating a significant performance burden on the host processor and can also benefit significantly from hardware acceleration. Detection of spam, viruses and other inappropriate content require deep packet inspection and analysis. Such tasks can put huge processing burden on the host processor and can substantially lower network line rate. Hence, deep packet content search and analysis hardware is also required.

[0010] Internet has become an essential tool for doing business at small to large organizations. HTML based static web is being transformed into a dynamic environment over last several years with deployment of XML based services. XML is becoming the lingua-franca of the web and its usage is expected to increase substantially. XML is a descriptive language that offers many advantages by making the documents self-describing for automated processing but is also known to cause huge performance overhead for best of class server processors. Decisions can be made by processing the intelligence embedded in XML documents to enable business to business transactions as well as other information exchange. However, due to the performance overload on the best of class server processors from analyzing XML documents, they cannot be used in systems that require network line rate XML processing to provide intelligent networking. There is a clear need for acceleration solutions for XML document parsing and content inspection at network line rates which are approaching 1 Gbps and 10 Gbps, to realize the benefits of a dynamic web based on XML services.

[0011] Regular expressions can be used to represent the content search strings for a variety of applications like those discussed above. A set of regular expressions can then form a rule set for searching for a specific application and can be applied to any document, file, message, packet or stream of data for examination of the same. Regular expressions are used in describing anti-spam rules, anti-virus rules, anti-spyware rules, anti-phishing rules, intrusion detection rules, extrusion detection rules, digital rights management rules, legal compliance rules, worm detection rules, instant message inspection rules, VOIP security rules, XML document security and search constructs, genetics, proteomics, XML based protocols like XMPP, web search, database search, bioinformatics, signature recognition, speech recognition, web indexing and the like. These expressions get converted

into NFAs or DFAs for evaluation on a general purpose processor. However, significant performance and storage limitations arise for each type of the representation. For example an N character regular expression can take up to the order of  $2^N$  memory for the states of a DFA, while the same for an NFA is in the order of N. On the other hand the performance for the DFA evaluation for an M byte input data stream is in the order of M memory accesses and the order of (N\*M) processor cycles for the NFA representation on modern microprocessors.

[0012] When the number of regular expressions increases, the impact on the performance deteriorates as well. For example, in an application like anti-spam, there may be hundreds of regular expression rules. These regular expressions can be evaluated on the server processors using individual NFAs or DFAs. It may also be possible to create a composite DFA to represent the rules. Assuming that there are X REs for an application, then a DFA based representation of each individual RE would result up to the order of  $(X*2^N)$  states however the evaluation time would grow up to the order of (X\*N) memory cycles. Generally, due to the potential expansion in the number of states for a DFA they would need to be stored in off chip memories. Using a typical access time latency of main memory systems of 60 ns, it would require about (X\*60 ns\*N\*M) time to process an X RE DFA with N states over an M byte data stream. This can result in tens of Mbps performance for modest size of X, N & M. Such performance is obviously significantly below the needs of today's network line rates of 1 Gbps to 10 Gbps and beyond. On the other hand, if a composite DFA is created, it can result in an upper bound of storage in the order of  $2^{N*X}$  which may not be within physical limits of memory size for typical commercial computing systems even for a few hundred REs. Thus the upper bound in memory expansion for DFAs can be a significant issue. Then on the other hand NFAs are nondeterministic in nature and can result in multiple state transitions that can happen simultaneously. NFAs can only be processed on a state of the art microprocessor in a scalar fashion, resulting in multiple executions of the NFA for each of the enabled paths. X REs with N characters on average can be represented in the upper bound of (X\*N) states as NFAs. However, each NFA would require M iterations for an M-byte stream, causing an upper bound of (X\*N\*M\* processor cycles per loop). Assuming the number of processing cycles are in the order of 10 cycles, then for a best of class processor at 4 GHz, the processing time can be around (X\*N\*M\*2.5 ns), which for a nominal N of 8 and X in tens can result in below 100 Mbps performance. There is a clear need to create high performance regular expression based content search acceleration which can provide the performance in line with the network rates which are going to 1 Gbps and 10 Gbps.

[0013] The methods for converting a regular expression to Thompson's NFA and DFA are well known. The resulting automata are able to distinguish whether a string belongs to the language defined by the regular expression however it is not very efficient to figure out if a specific sub-expression of a regular expression is in a matching string or the extent of the string. Tagged NFAs enable such queries to be conducted efficiently without having to scan the matching string again. For a discussion on Tagged NFA refer to the paper "NFAs with Tagged Transitions. their Conversion to Deterministic Automata and. Application to Regular Expressions", by Ville Laurikari, Helsinki University of Technology, Finland.

#### SUMMARY OF THE INVENTION

[0014] A programmable intelligent search memory (PRISM) is a memory technology that supports orders of

magnitude larger number of regular expressions in a single chip for current and emerging content search applications. PRISM memory supports FSAs of a number of states 'n' which may be any integer like 8, 16, 32 and the like. However, at times there may be a need to support regular expressions with number of states which are more than that represented in a single PRISM FSA. For such cases it may be necessary to allow multiple PRISM FSAs to be coupled together to support the bigger REs. Further, there are certain applications where the rules are specified as a group of rules that are evaluated together and there may be nesting amongst the rule groups. Such applications may have groups of rules that may be evaluated simultaneously or one after the other and need a means of communicating from one FSA to another. My invention describes an architecture that enables creation of extensible FSAs to support needs such as the ones described above and the like. There is a need for creating a compiler flow that can target converting regular expression rules in to a form that PRISM based search engines can use to process input data for content specified by the regular expression rules. My invention describes a compiler for regular expressions that can be used for PRISM.

[0015] I describe an FSA extension architecture and a compiler .for a high performance Programmable Intelligent Search Memory<sup>TM</sup> (PRISM<sup>TM</sup>) for searching content with regular expressions as well as other pattern searches. Prograrn.mable intelligent search memory of this patent can have many uses wherever any type of content needs to be searched for example in networking, storage, security, web search applications, XML processing, bio informatics, signature recognition, genetics, proteomics, speech recognition, database search, enterprise search and the like. The programmable intelligent search memory of my invention may be embodied as independent PRISM memory integrated circuits working with or may also be embodied within microprocessors, multi-core processors, network processors, TCP Offload Engines, network packet classification engines, protocol processors, regular expression processors, content search processors, network search engines, content addressable memories, mainframe computers, grid computers, servers, workstations, personal computers, laptops, notebook computers, PDAs, handheld devices, cellular phones, wired or wireless networked devices, switches, routers, gateways, unified threat management devices, firewalls, VPNs, intrusion detection and prevention systems, extrusion detection systems, compliance management systems, wearable computers, data warehouses, storage area network devices, storage systems, data vaults, chipsets and the like or their derivatives or any combination thereof.

[0016] The regular expressions may optionally be tagged to detect sub expression matches beside the full regular expression match. The regular expressions are converted into equivalent FSAs that may optionally be NFAs and may optionally be converted into tagged NFAs. The PRISM memory also optionally provides ternary content addressable memory functionality. So fixed string searches may optionally be programmed into the PRISMTM memory of my invention. PRISM memory of this invention enables a very efficient and compact realization of intelligent content search using FSA to meet the needs of current and emerging content search applications. For clarity, as used in this patent the terms "programmable intelligent search memory", "search memory", "content search memory", or "PRISM memory" are used interchangeably and have the same meaning unless

specifically noted. Further for clarity, as used in this patent the term "memory" when used independently is used to refer to random access memory or RAM or Dynamic RAM (DRAM) or DDR or QDR or RLDRAM or RDRAM or FCRAM or Static RAM (SRAM) or read only memory (ROM) or FLASH or cache memory or the like or any future derivatives of such memories.

[0017] The PRISM memory performs simultaneous search of regular expressions and other patterns (also referred to as "rules" or "regular expression rules" or "pattern search rules" or "patterns" or "regular expressions" in this patent) against the content being examined. The content may be presented to the search memory by a companion processor or PRISM controller or content stream logic or a master processor or the like which may be on the same integrated circuit chip as the PRISM memory or may be on a separate device. The content to be searched may be streaming content or network packets or data from a master processor or data from a disk or a file or reside in on-chip memory or off-chip memory or buffers or the like from which a controller may present it to the search memory arrays for examination. The content search memory arrays may initially be configured with the regular expression rules converted into NFAs or tagged NFAs and optionally other pattern search rules. I describe a compiler for converting regular expressions into rules supported by PRISM. PRISM memory may optionally comprise of configuration control logic which may be distributed or central or a combination thereof. The configuration control logic may optionally address PRISM memory cells to read and/or write FSA rules or other patterns to be searched. Once the PRISM memory is setup with all the related information about the NFAs and other rules, the content to be examined can be presented to the PRISM memory. PRISM memory provides capabilities to update rules or program new rules or additional rules, in line with the content examination within a few clock cycles unlike the current regular expression processors which require the content evaluation to stop for long periods of time until large tables of composite DFAs are updated in an external or internal memory. Typically the content is presented as a stream of characters or symbols which get examined against the rules in the PRISM memory simultaneously and whenever a rule is matched the PRISM memory array provides that indication as a rule match signal which is interpreted by the control logic of the PRISM. There may be multiple rule matches simultaneously in which case a priority encoder which may also be prottrammable is used to select one or more matches as the winner(s). The priority encoder may then provide a tag or an address or an action or a combination that may have already been programmed in the priority encoder which may be used to look-up related data from associated on-chip or off-chip memory that may optionally determine the next set of actions that may need to be taken on the content being examined. For example, in case of a security application if a set of regular expressions are defined and programmed for spain detection, then if one or more of these rules when matched can have action(s) associated with them that the message or content may need to quarantined for future examination by a user or it can have an action that says the content should be dropped or enable a group of regular expressions in the PRISM memory to be applied to the content or the like depending on the specific application. The PRISM memory architecture comprises of means or circuits or the like for programming and reprogramming of the FSA rules and optionally CAM signatures and masks. It further comprises of means or circuits or the like to stream the content to be searched to the PRISM memory arrays. It May further comprise of priority encoder which may optionally be programmable. The PRISM memory may optionally comprise of random access memory (on-chip or off-chip) which is used to store actions associated with specific rule matches. The PRISM memory may optionally comprise of database extension ports which may be optionally used when the number of rules is larger than those that may fit in a single integrated circuit chip. The PRISM memory may optionally comprise of clusters of PRISM memory cells that enable a group of FSA rules to be programmed per cluster. The PRISM clusters may optionally comprise of memory for fast storage and retrieval of FSA states for examination of content that belongs to different streams or contexts or flows or sessions or the like as described below referred to as context memory. For clarity, context memory or global context memory or local context memory or cluster context memory, all comprise of memory like random access memory or RAM or Dynamic RAM (DRAM) or DDR or QDR or RLDRAM or RDRAM or FC.RAM or Static RAM (SRAM) or read only memory (ROM) or FLASH or cache memory or the like or any future derivatives of such memories as discussed above. The PRISM memory may optionally comprise of global context memory beside the local cluster context memory for storage and retrieval of FSA states of different contexts and enable supporting a large number of contexts. The cluster context memory may optionally cache a certain number of active contexts while the other contexts may be stored in the global context memory. There may optionally be off-chip context memory as well, which can be used to store and retrieve FSA states for much larger number of contexts. The PRISM memory may optionally comprise of cache or context control logic (also referred as "context controller") that manages the cluster, global or external context memory or cache or a combination thereof. The cache or context control logic may optionally be distributed per cluster or may be central for the PRISM memory or any combination thereof. The PRISM controller or the content stream logic that streams the content to be searched may be provided with an indication of the context of the content being searched or it may detect the context of the content or a combination thereof, and may optionally direct the context memory and associated control logic i.e. the context controller to get the appropriate context ready. Once the context memory has the required context available an indication may be provided to PRISM configuration control logic that it may program or load the context states in the PRISM memory. The PRISM configuration control logic (also referred as "configuration controller" in this patent) may optionally first save the current context loaded in the set of active FSA blocks before loading the new context. The configuration controller(s) and the context controller(s) may thus optionally store and retrieve appropriate contexts of the FSAs and start searching the content against the programmed rules with appropriate context states of the FSAs restored. Thus PRISM memory may optionally dynamically reconfigure itself at run-time based on the context of the content or the type of the application or the like or a combination thereof enabling run-time adaptable PRISM memory architecture. The contexts as referred to in this patent may, as examples without limitation, be related to specific streams, or documents, or network connections or message streams or sessions or the like. The PRISM memory may process content from multiple contexts arriving in data groups or packets or the like. For content search in applications where the content belonging to one context may arrive interspersed with content from other contexts, it may be important to maintain the state of the content searched for a context up to the time when content from a different context gets searched by PRISM memory. The context memory or cache with the associated controllers as described in this patent enable handling of multiple contexts.

[0018] For clarification, the description in this patent application uses term NFA to describe the NFAs and optionally, when tagging is used in regular expressions, to describe tagged NFA unless tagged NFA is specifically indicated. All NFAs may optionally be tagged to form tagged NFAs, hence the description is not to be used as a limiter to apply only to tagged NFAs. The descriptions of this patent are applicable for non-tagged NFAs as well and tagging is an optional function which may or may not be implemented or used, and thus non-tagged NFAs are covered by the teachings of this patent as will be appreciated by one skilled in the art. At various places in this patent application the term content search memory, content search memory, search memory and the like are used interchangeably for programmable intelligent search memory or PRISM memory. These usages are meant to indicate the content search memory or PRISM memory of this invention without limitation.

[0019] Berry and Sethi in their paper "From Regular Expressions to Deterministic Automata" Published in Theoretical Computer Science in 1986, showed that regular expressions (REs) can be represented by NFAs such that a given state in the state machine is entered by one symbol, unlike the Thompson NFA. Further, the Berry-Sethi NFAs are c-free. A 'V' term RE can be represented using 'V+1' states NFA using Berry-Sethi like NFA realization method. The duality of Berry-Sethi method also exists where all transitions that lead the machine out of a state are dependent on the same symbol. This is shown in the paper "A Taxonomy of finite automata construction algorithms" by Bruce Watson published in 1994 in section 4.3. I show a method of creating NFA search architecture in a memory leveraging the principles of Berry-Sethi's NFA realization and the dual of their construct. The NFA search memory is programmable to realize an arbitrary regular expression using the compiler flow of this invention to convert a regular expression to that usable by PRISM. The compiler of this invention follows the principles of Berry-Sethi FSA construction to convert regular expressions into an FSAs and creates various data structures that are required for PRISM to operate as a programmable regular expressions engine.

[0020] This PRISM memory and the compiler for PRISM of this patent may be used for many applications like those for detecting intrusions, extrusions and confidential information disclosure (accidental or malicious or intended), regulatory compliance search using hardware for regulations like HIPAA, Sarbanes-Oxley, Graham-Leach-Bliley act, California security bills, security bills of various states and/or countries and the like, deep packet inspection, detecting spam, detecting viruses, detecting worms, detecting spyware, detecting digital rights management information, instant message inspection, URL matching, application detection, detection of malicious content, and other content, policy based access control as well as other policy processing, content based switching, load balancing, virtualization or other application layer content inspection for application level protocol analysis and processing for web applications based on

HTTP, XML and the like and applying specific rules which may enable anti-spam, anti-virus, other security capabilities like anti-spyware, anti-phishing and the like capabilities. The content inspection memory may be used for detecting and enforcing digital rights management rules for the content. The content inspection memory may also be used for URL matching, string searches, genetic database searches, proteomics, bio informatics, web indexing, content based load balancing, sensitive information search like credit card numbers or social security numbers or health information or the like.

[0021] Classification of network traffic is another task that consumes up to half of the processing cycles available on packet processors leaving few cycles for deep packet inspection and processing at high line rates. The described content search memory can significantly reduce the classification overhead when deployed as companion search memory to packet processors or network processors or TOE or storage network processors or the like.

#### BRIEF DESCRIPTION OF THE DRAWINGS

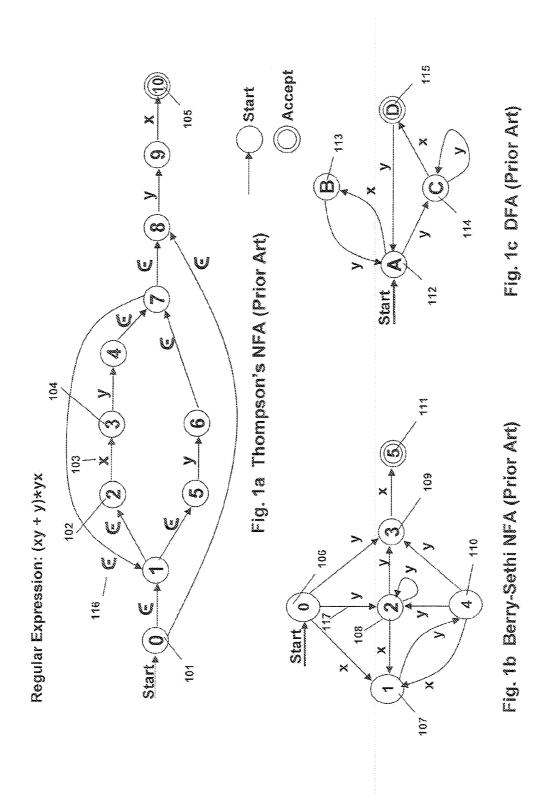

[0022] FIG. 1a illustrates Thompson's NFA (prior art)

[0023] FIG. 1b illustrates Berry-Sethi NFA (prior art)

[0024] FIG. 1c illustrates DFA (prior art)

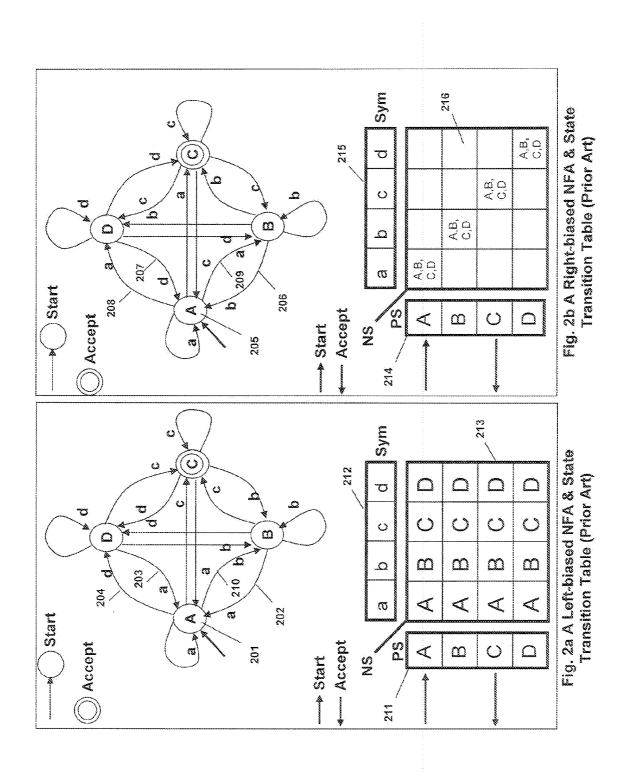

[0025] FIG. 2a illustrates a left-biased NFA and state transition table (prior art)

[0026] FIG. 2b illustrates a right-biased NFA and state transition table (prior art)

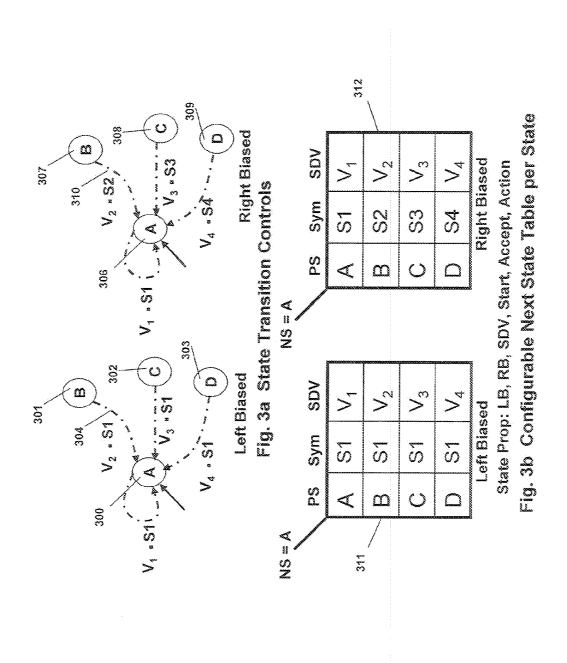

[0027] FIG. 3a illustrates state transition controls

[0028] FIG. 3b illustrates configurable next state tables per state

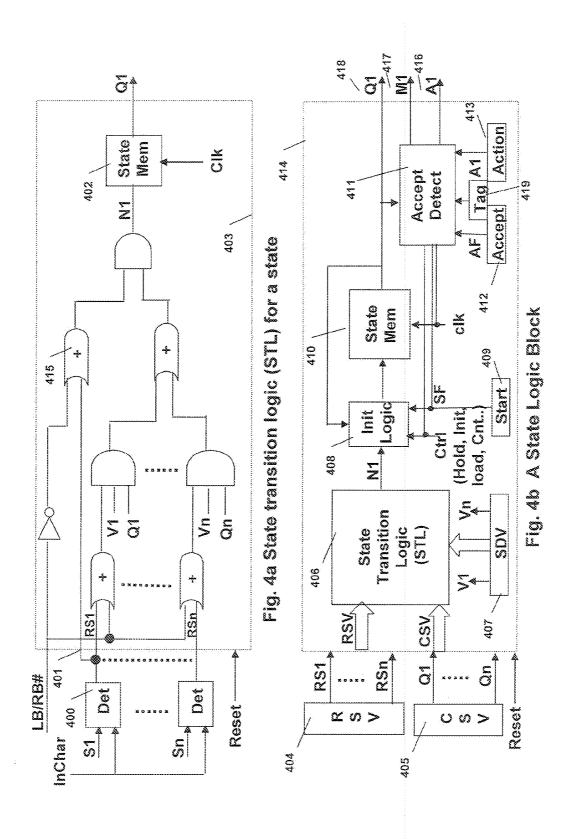

[0029] FIG. 4a illustrates state transition logic (STL) for a state

[0030] FIG. 4b illustrates a state logic block

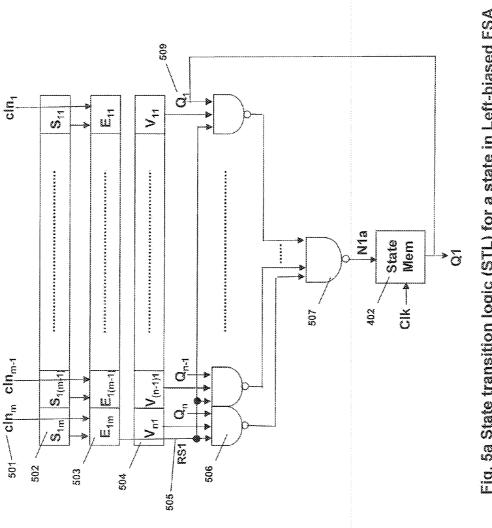

[0031] FIG. 5a illustrates state transition logic (STL) for a state :in Left-Biased FSA

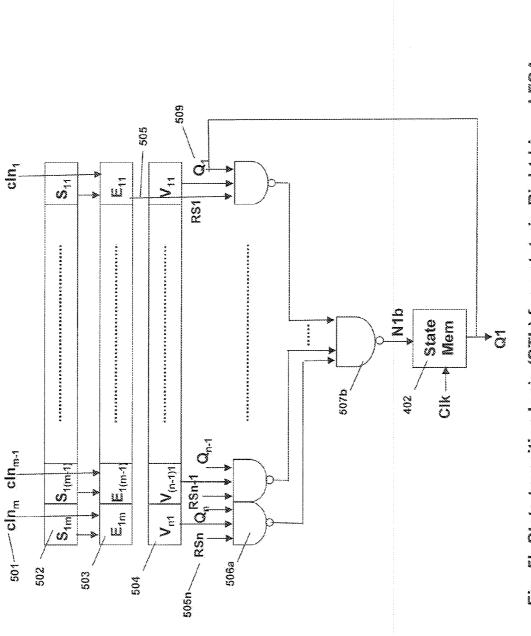

$[0032]~{\rm FIG.}~5b$  illustrates state transition logic (STL) for a state in Right-Biased FSA

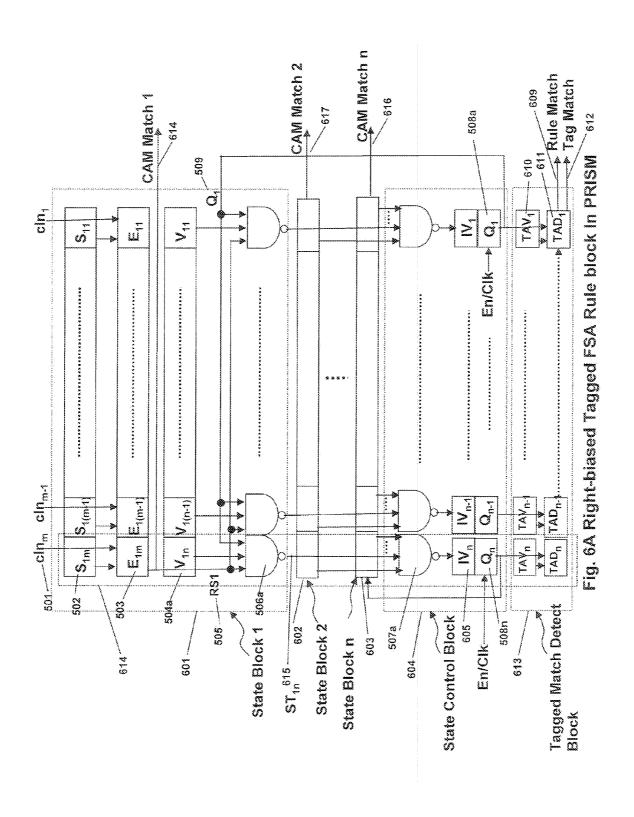

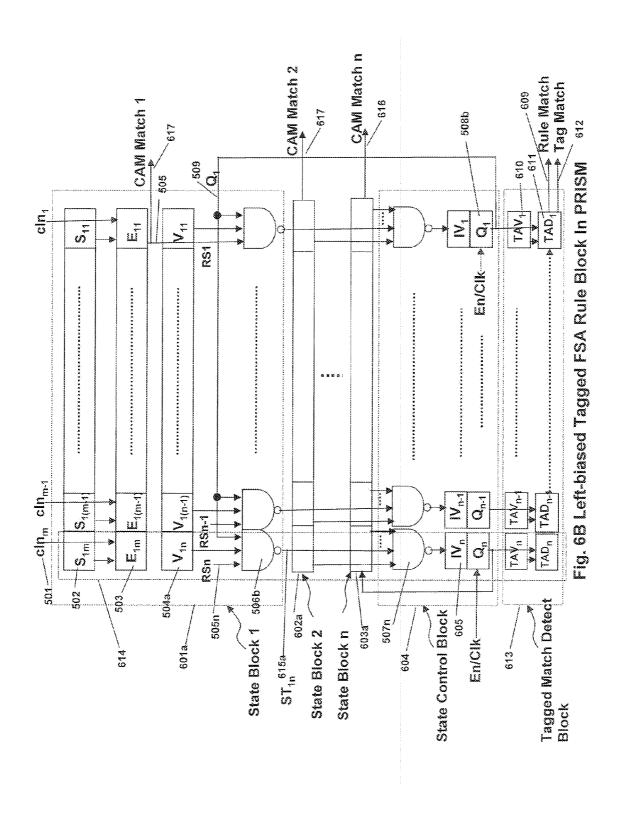

[0033] FIG. 6A illustrates Right-biased Tagged FSA Rule block in PRISM

[0034] FIG. 6B illustrates Left-biased Tagged FSA Rule block in PRISM

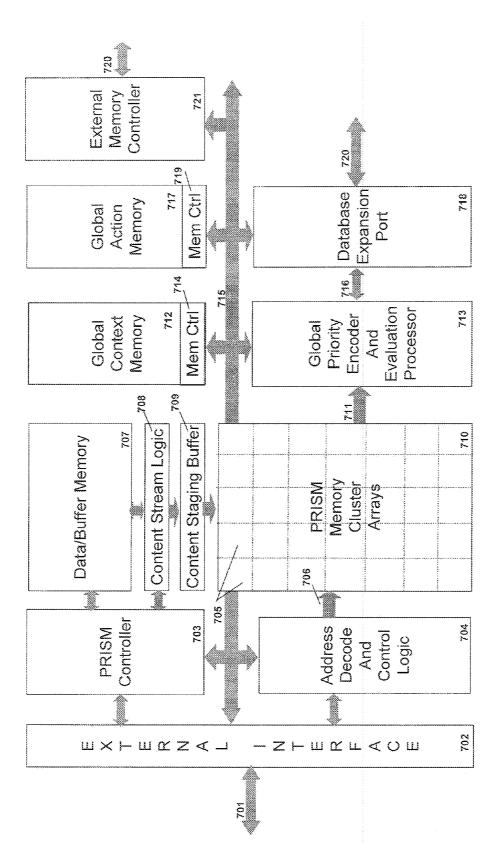

[0035] FIG. 7 illustrates PRISM Block Diagram

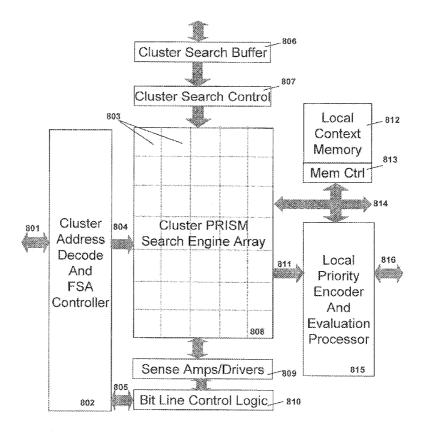

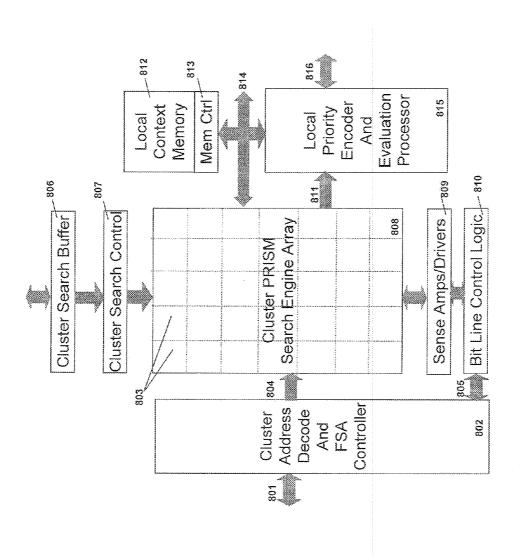

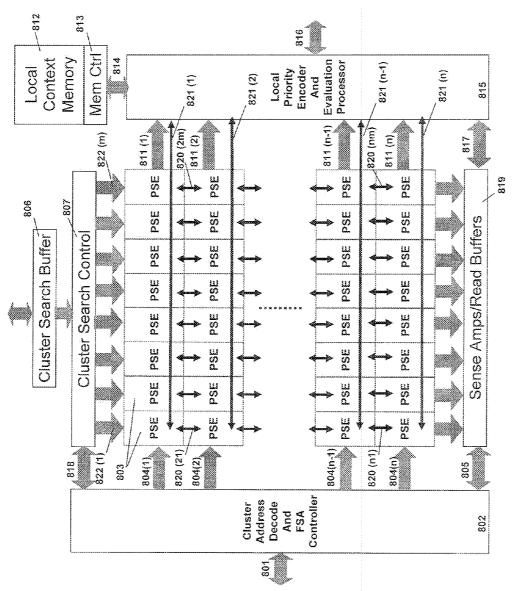

[0036] FIG. 8a illustrates PRISM Memory Cluster Block Diagram

[0037] FIG. 8b illustrates PRISM Memory Cluster Detailed Block Diagram

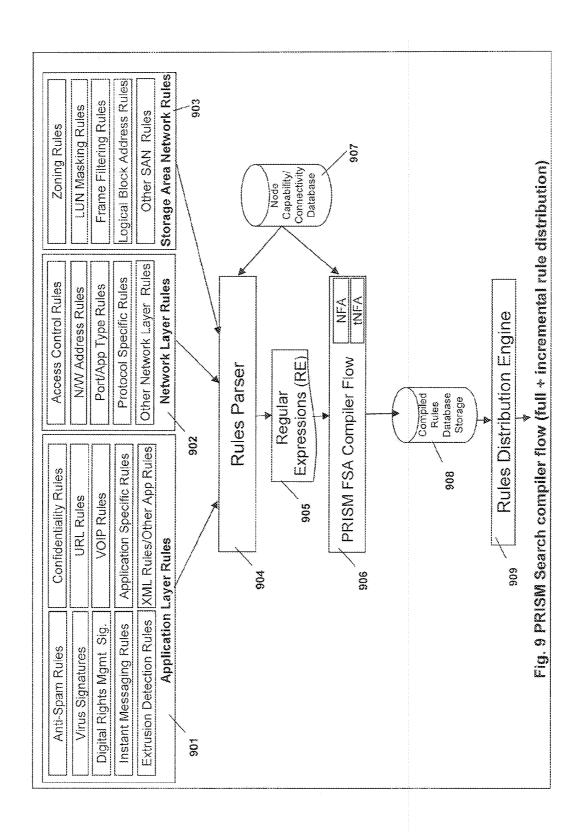

[0038] FIG. 9 illustrates PRISM search compiler flow (full+incremental rule distribution)

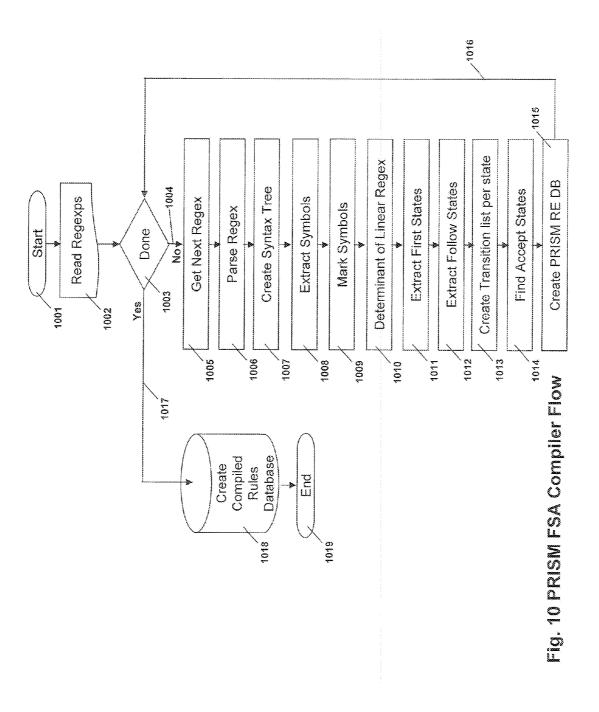

[0039] FIG. 10 illustrates PRISM HA Compiler flow

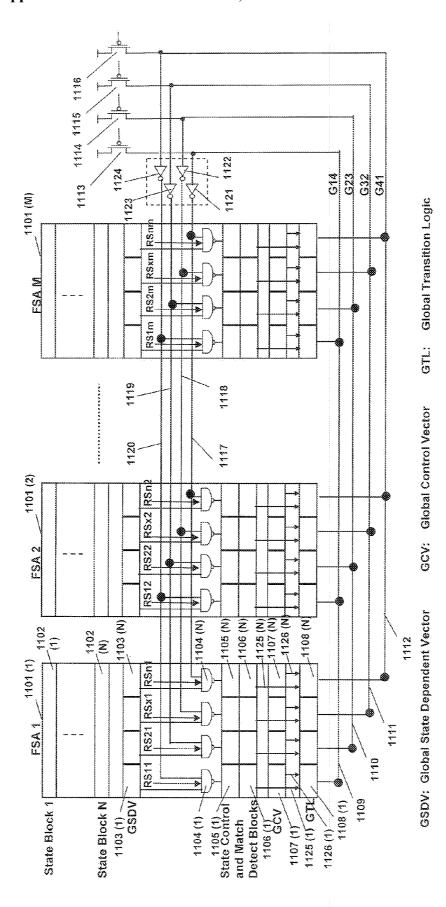

[0040] FIG. 11 illustrates PRISM Row-Wise FSA Extension

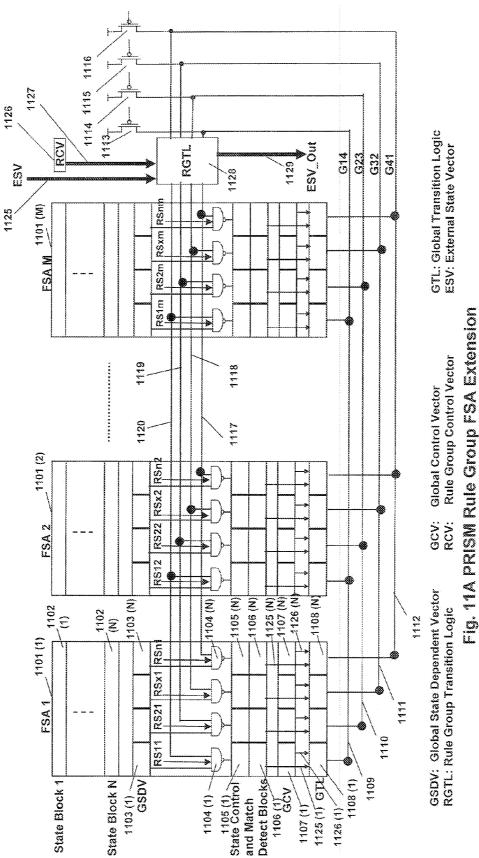

[0041] FIG. 11A illustrates PRISM Rule Group FSA Extension.

${\bf [0042]}$  FIG. 12 illustrates PRISM. Row-Wise FSA Extension Example #1

[0043] FIG. 13 illustrates PRISM Row-Wise FSA Extension Example #2

[0044] FIG. 14 illustrates PRISM Column-Wise FSA Extension

[0045] FIG. 15 illustrates PRISM FSA Extension Example #1

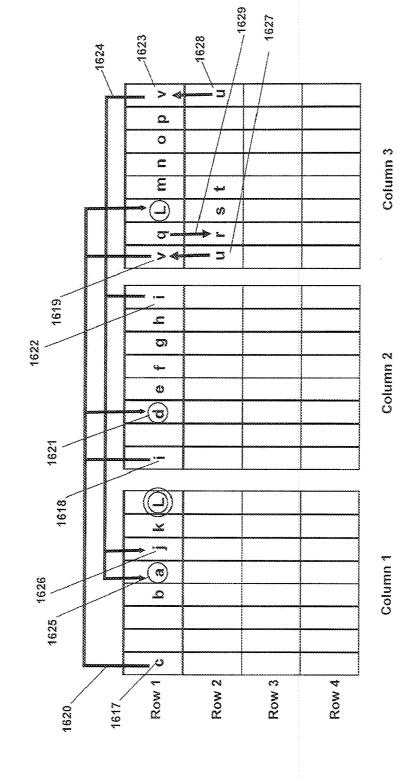

[0046] FIG. 16a illustrates Column-Wise PRISM FSA Extension Example

[0047] FIG. 16b illustrates Row-Wise and Column-Wise PRISM BA Extension Example

#### DESCRIPTION

[0048] I describe a FSA extension architecture and a regular expression compiler for high performance Programmable Intelligent Search Memory for searching content with regular expressions as well as other pattern searches. The regular expressions may optionally be tagged to detect sub expression matches beside the full regular expression match. The regular expressions are converted into equivalent FSAs that may optionally be NFAs and may optionally be converted into tagged NFAs. The PRISM memory also optionally supports ternary content addressable memory functionality. So fixed string searches may optionally be programmed into the PRISM memory. PRISM memory enables a very efficient and compact realization of intelligent content search using FSA to meet the needs of current and emerging content search applications. Unlike a regular expression processor based approach, the PRISM memory can support tens of thousands to hundreds of thousands of content search rules defined as regular expressions as well as patterns of strings of characters. A compiler for compiling these regular expression rules into PRISM. compatible data structure is described in this invention to enable PRISM to perform the content inspection using the compiled rules. The PRISM memory performs simultaneous search of regular expressions and other patterns. The content search memory can perform high speed content search at line rates from 1 Gbps to 10 Gbps and higher, when the best of class server microprocessor can only perform the same tasks at well below 100 Mbps. The content search memory can be used not only to perform layer 2 through layer 4 searches that may be used for classification and security applications, it can also be used to perform deep packet inspection and layer 4 through layer 7 content analysis.

[0049] Following are some of the embodiments, without limitations, that can implement PRISM memory:

[0050] The PRISM memory may be embodied inside network interface cards of servers, workstations, client PCs, notebook computers, handheld devices, switches, routers and other networked devices. The servers may be web servers, remote access servers, file servers, departmental servers, storage servers, network attached storage servers, database servers, blade servers, clustering servers, application servers, content /media servers, VOIP servers and systems, grid computers/servers, and the like. The PRISM memory may also be used inside an I/O chipset of one of the end systems or network core systems like a switch or router or appliance or the like.

[0051] The PRISM memory may also be embodied on dedicated content search acceleration cards that may be used inside various systems described in this patent. Alternatively, PRISM memory may also be embodied as a content search memory inside a variety of hardware and/or integrated circuits like ASSPs, ASICs, FPGA, microprocessors, multi-core processors, network processors, TCP Offload Engines, network packet classification engines, protocol processors, regular expression processors, content search processors, mainframe computers, grid computers, servers, workstations, personal computers, laptops, handheld devices, cellular phones, wired, or wireless networked devices, switches, routers, gateways, XML accelerators, VOIP servers, Speech recognition systems, bio informatics systems, genetic and proteomics search systems, web search servers, electronic vault

application networks and systems, Data Warehousing systems, Storage area network systems, content indexing appliances like web indexing, email indexing and the like, chipsets and the like or any combination thereof Alternatively, PRISM memory blocks may be embedded inside other memory technologies like DRAM, SDRAM, DDR DRAM, DDR II DRAM, RLDRAM, SRAM, RDRAM, RDRAM, QDR SRAM, DDR SRAM, CAMs, Boundary Addressable Memories, Magnetic memories, Flash or other special purpose memories or a combination thereof or future derivates of such memory technologies to enable memory based content search.

[0052] One preferred embodiment of the invention is in an integrated circuit memory chip that may support around 128, 000 8-symbol regular expression rules in current process technologies. A second preferred embodiment of the PRISM technology is an integrated circuit memory chip that may support around 8,000 regular expression rules in current process technologies to support applications where a lower content search memory cost is required. Each process generation may provide ability to store around twice as many PRISM memory bits as the previous generation. Thus in one preferred embodiment the PRISM memory would be able to support tens of thousands of eight state FSA and can, potentially support over 100,000 FSAs. There are many variations of the PRISM memory architecture that can be created that can support more or less FSAs depending upon various factors like the number of states per FSA, the chip die area, cost, manufacturability expectations and the like which will be appreciated by a person with ordinary skill in the art.

#### DETAILED DESCRIPTION

[0053] describe a FSA extension architecture and a regular expression compiler for a high performance Programmable Intelligent Search Memory for searching content with regular expressions as well as other pattern searches. The regular expressions may optionally be tagged to detect sub expression matches beside the full regular expression match. The regular expressions are converted into equivalent FSAs or NFAs and optionally into tagged NFAs. The PRISM memory also optionally supports ternary content addressable memory functionality. So fixed string searches may optionally be programmed into the PRISM memory of my invention. PRISM memory of this invention enables a very efficient and compact realization of intelligent content search using FSA to meet the needs of current and emerging content search applications. Unlike a regular expression processor based approach, the PRISM memory can support tens of thousands to hundreds of thousands of content search rules defined as regular expressions as well as patterns of strings of characters. The PRISM memory performs simultaneous search of regular expressions and other patterns. The content search memory can perform high speed content search at line rates from 1 Gbps to 10 Gbps and higher using current process technologies. The description here is with respect to one preferred embodiment of this invention in an integrated circuit (IC) chip, it will be appreciated by those with ordinary skill in the art that changes in these embodiments may be made without departing from the principles and spirit of the invention. The illustrations are made to point out salient aspects of the invention and do not illustrate well understood IC design elements, components and the like implementation of the invention in integrated circuits so as not to obscure the invention.

[0054] Ability to perform content search has become a critical capability in the networked world. As the network line rates go up to 1 Gbps, 10 Gbps and higher, it is important to be able to perform deep packet inspection for many applications at line rate. Several security issues, like viruses, worms, confidential information leaks and the like, can be detected and prevented from causing damage if the network traffic can be inspected at high line rates. In general, content search rules can be represented using regular expressions. Regular expression rules can be represented and computed using FSAs. NFAs and DFAs are the two types of FSAs that are used for evaluation of regular expressions. For high line rate applications a composite DFA can be used, where each character of the input stream can be processed per cycle of memory access. However, this does have a limit on how fast the search can be performed dictated by the memory access speed. Another limiter of such approach is the amount of memory required to search even a modest number of regular expression rules. As discussed above, NFAs also have their limitations to achieve high performance on general purpose processors. In general, today's best of class microprocessors can only achieve less than 100 Mbps performance using NFAs or DFAs for a small number of regular expressions. Hence, there is a clear need to create targeted content search acceleration hardware to raise the performance of the search to the line rates of 1 Gbps and 10 Gbps. PRISM memory is such a high performance content search hardware that can be targeted for high line rates. The invention of this patent describes a compiler to make PRISM memory structures useful for processing content against a large number of regular expressions compiled to leverage PRISM capabilities.

[0055] As described earlier, regular expression can be represented using FSA like NFA or DFA. FIG. 1a illustrates Thompson's construction for the regular expression (xy+y) \*yx. Thompson's construction proceeds in a step by step manner where each step introduces two new states, so the resulting NFA has at most twice as many states as the symbols or characters and operators in the regular expression. An FSA is comprised of states, state transitions, and symbols that cause the FSA to transition from one state to another. An FSA comprises at least one start state, and at least one accept state where the start state is where the FSA evaluation begins and the accept state is a state which is reached when the FSA recognizes a string. Block 101 represent the start state of the FSA, while block 105 is an accept state. Block 102 represents state 2 and 104 represents state 3. The transition from state 2 to state 3 is triggered on the symbol x, 103 and is represented as a directed edge between the two states. Thompson's NFA comprises of '\(\epsilon\)' transitions, 116, which are transitions among states which may be taken without any input symbol.

[0056] FIG. 1b illustrates Berry-Sethi NFA for the regular expression  $(xy+y)^*yx$ . Berry and Sethi described an algorithm of converting regular expressions into .FSA using a technique called 'marking' of a regular expression. It results in an NFA which has a characteristic that all transitions into any state are from the same symbol. For example, all transitions into state 1, 107, are from symbol 'x'. The other characteristic of the Berry-Sethi construct is that number of NFA states are the same as the number of symbols in the regular expression and one start state. In this type of construction, each occurrence of a symbol is treated as a new symbol. The construction converts the regular expression  $(xy+y)^*yx$  to a marked expression  $(x_1y_2+y_3)^*y_4x_5$  where each  $x_1$  leads to the same state, 107. The figure does not illustrate the markings.

Once the FSA is constructed the markings are removed. The FIG. 1b illustrates the NFA with the markings removed. As can be seen from the figure, in Berry-Sethi construction all incoming transitions into a state are all dependent on the same symbol. Similarly, a duality of Berry-Sethi construct also has been studied and documented in the literature as discussed earlier, where instead of all incoming transitions being dependent on the same symbol, all outgoing transitions from a state are dependent on the same symbol. The Berry-Sethi construct is also called a left-biased type of construct, where as its dual is called a right-biased construct.

[0057] Finite State Automaton can evaluate incoming symbols or characters against the regular expression language of the automaton and detect when an input string is one of the strings recognized by it. However, it is advantageous in certain conditions to know if a certain sub-expression of the regular expression is also matched. That may be enabled by tagging the NFA as described in the paper by Ville Laurikari referred earlier. Following description illustrates how the inventions of this patent enable tagged NM realization in PRISM memory. The tagging for sub-expression checking may involve further processing of the FSA to uniquely identify sub-expression matching. However for illustration purpose, if in the regular expression "(xy+y)\*yx" done desires to detect if the sub-expression "xy" is in the recognized string, one can tag the state 4, 110, as a tagged state. Thus, whenever the regular expression transitions through state 4, 110, the sub-expression match or tag match may be indicated. There may also be need to detect if a specific transition leads the regular expression through a desired sub-expression. In such a case a tag start state and a tag end state may be marked. For instance, if it is desired to detect if the transition from state 0 to state 2, 117, is taken then the state 0 may be marked as a tag start state and state 2 may be marked as a tag end state. The tagged FSA implementation may then indicate the beginning of the tag transition when the FSA reaches the tag start state and then indicate the end of the tag transition when the FSA reaches the tag end state. If the FSA moves from the tag start state immediately followed by transitioning into tag end state, then the tagged FSA can indicate the match of a tagged transition. The illustrations in the description below do not illustrate this aspect of tagged NFA, though it may optionally be supported in PRISM and may be easily implemented as follows or other means for example by adding a tag start and tag end state flags (as memory bits or flip-flops) and the logic for the tag transition detection to follow the steps described above as can be appreciated by those with ordinary skill in the art. The patent of this disclosure enables detection of subexpressions using tagging.

[0058] FIG. 1c illustrates a DFA for the same regular expression (xy+y)\*yx. DFA is deterministic in that only one of its states is active at a given time, and only one transition is taken dependent on the input symbol. Whereas in an NFA, multiple states can be active at the same time and transitions can be taken from one state to multiple states based on one input symbol. There are well known algorithms in the literature, like subset construction, to convert a RE or NFA to a DFA. This DFA may be realized in the PRISM Memory using the constructs described below to represent an FSA, using a left-biased realization. Thus PRISM memory of this invention may also be used to program certain DFAs where all incoming transitions to each state are with the same symbol like the DFA of this illustration.

[0059] FIG. 2a illustrates a left-biased NFA and its state transition table (prior art). The illustration is a generic four state Berry-Sethi like NFA with all transitions from each node to the other shown with the appropriate symbol that the transition depends on. For example, state A, 201 has all incoming transitions dependent on symbol 'a' as illustrated by example transitions labeled 202 and 203. When the FSA is in State A, 201, an input symbol 'd', transitions the FSA to state D with the transition, 204, from state A to state D. The table in the figure illustrates the same FSA using a state transition table. The column 'PS', 211, is the present state of the FSA, while the row 'sym', 212, is a list of all the symbols that the state transitions depend on. The table 213, illustrates the next state (NS) that the FSA will transition to from the present state (PS) when an input symbol from those in the sym header row is received. In this FSA, state 'A' is the start state and state C is an accept state. Hence, if the FSA is in the present state 'A' and an input symbol 'b' is received, the FSA transitions to the next state 'B'. So when the next input symbol is received, the FSA is in present state 'B' and is evaluated for state transition with the row corresponding to present state 'B'.

[0060] FIG. 2b illustrates a right-biased NFA and its state transition table (prior art). The illustration is a generic four state dual of Berry-Sethi NFA with all transitions from each node to the other shown with the appropriate symbol that the transition depends on. For example, state 'A', 205 has all outgoing transitions dependent on symbol 'a' as illustrated by example transitions labeled 208 and 209 where as unlike the left-biased NFA described above, each incoming transition is not on the same symbol, for example transitions labeled 206 and 207 depend on symbols 'b' and 'd' respectively. The state transition table in this figure is similar to the left biased one, except that the FSA transitions to multiple states based on the same input symbol. For example if the FSA is in the present state 'B' and a symbol 'b' is received, then the FSA transitions to all states 'A', 'B', 'C' and 'D'. When an input symbol is received which points the FSA to an empty box, like 216, the FSA has received a string which it does not recognize. The FSA can then be initialized to start from the start state again to evaluate the next string and may indicate that the string is not recognized.

[0061] The FIG. 2a and FIG. 2b, illustrate generic four state NFAs where all the transitions from each state to the other are shown based on the left-biased or right-biased construct characteristics. However not all four state NFAs would need all the transitions to be present. Thus if a symbol is received which would require the FSA to transition from the present state to the next state when such transition on the received input symbol is not present, the NFA is said to not recognize the input string. At such time the NFA may be restarted in the start state to recognize the next string. In general, one can use these example four state NFAs to represent any four state RE in a left-biased (LB) or right-biased (RB) form provided there is a mechanism to enable or disable a given transition based on the resulting four states NFA for the RE.

[0062] FIG. 3a illustrates state transition controls for a left-biased and right-biased NFA. The figure illustrates a left-biased NFA with a state 'A', 300, which has incoming transitions dependent on receiving input Symbol 'S1' from states 'B', 301, 'C', 302, and 'D', 303. However, the transitions from each of the states 'B', 'C' and 'D' to state 'A', occur only if the appropriate state dependent control is set besides receiving the input symbol 'S1'. The state dependent control for transition from state 'B' to state 'A' is  $V_2$  while those from

states 'C' and 'D' to state 'A' is  $V_3$  and  $V_4$  respectively. Transition to the next state 'A' is dependent on present state 'A' through the state dependent control  $V_1$ . Thus transition into a state 'A' occurs depending on the received input symbol being 'S1' and if the state dependent control for the appropriate transition is set. Thus, one can represent any arbitrary four states NFA by setting or clearing the state dependent control for a specific transition. Thus, if a four states left biased NFA comprises of transition into state 'A', from state 'B' and 'C' but not from the states 'A' or 'D', the state dependent controls can be set as  $V_1$ =0,  $V_2$ =1,  $V_3$ =1 and  $V_4$ =0. Hence if the NFA is in state 'D' and a symbol 'S1' is received, the NFA will not transition into state 'A', however if the NFA is in state 'B' and a symbol 'S1' is received the NFA will transition into state 'A'.

[0063] Similarly, FIG. 3a also illustrates states and transitions for a right-biased NFA. The figure illustrates a rightbiased NFA with a state 'A', 306, which has incoming transitions from state 'B', 307, state 'C', 308, and state 'D', 309, on receiving input symbols 'S2', 'S3' and 'S4' respectively. However, the transitions from each of the states 'B', 'C' and 'D' to state 'A', occur only if the appropriate state dependent control is set besides receiving the appropriate input symbol. The state dependent control for transition from state 'B' to state 'A' is V<sub>2</sub> while those from states 'C' and 'D' to state 'A' is V<sub>3</sub> and V<sub>4</sub> respectively. Transition to the next state 'A' is dependent on present state 'A' through the state dependent control V<sub>1</sub>. Thus transition into a state 'A' occurs based on the received input symbol and if the state dependent control for the appropriate transition is set. Thus, one can represent any arbitrary four states right-biased NFA by setting or clearing the state dependent control for a specific transition. All state transition controls for a given state form a state dependent vector (SDV), which is comprised of  $V_1, V_2, V_3$ , and  $V_1$  for the illustration in FIG. 3a for the left-biased and the rightbiased NFAs.

[0064] FIG. 3b illustrates configurable next state table per state. The left-biased state table for 'NS=A', is shown by the table 311, whereas the right-biased state table for 'NS=A', is shown by the table 312. The state dependent vector for both left-biased and right-biased NFA state is the same, while the received input symbol that drive the transition are different for the left-biased vs. right-biased NFA states. Thus a state can be represented with properties like left-biased (LB), right-biased (RB), start state, accept state, SDV as well as action that may be taken if this state is reached during the evaluation of input strings to the NFA that comprises this state.

[0065] FIG. 4a illustrates state transition logic (STL) for a state. The STL is used to evaluate the next state for a state. The next state computed using the STL for a state depends on the current state of the NFA, the SDV, and the received symbol or symbols for a left-biased NFA and right-biased NFA respectively. The InChar input is evaluated against symbols 'SI through 'Sn' using the symbol detection logic, block 400, where 'n' is an integer representing the number of symbols in the RE of the NFA. The choice of 'n' depends on how many states are typically expected for the NFAs of the applications that may use the search memory. Thus, 'n' may be chosen to be 8, 16, 32 or any other integer. The simplest operation for symbol detection may be a compare of the input symbol with 'S1' through 'Sn'. The output of the symbol detection logic is called the received symbol vector (RSV) comprised of individual detection signals 'RS1' through 'RSn'. LB/RB# is a signal that indicates if a left-biased NFA or a right-biased NFA is defined. LB/RB# is also used as an input in evaluating state transition. The STL for a state supports creation of a left-biased as well as right-biased NFA constructs. The LB/RB# signal controls whether the STL is realizing a leftbiased or a right-biased construct. The state dependent vector in the form of 'V1' through 'Vn', is also applied as input to the STL. The SDV enables creation of arbitrary 'n'-state NFAs using STL as a basis for a state logic block illustrated in FIG. 4b. Present states are fed into STL as a current state vector (CSV) comprised of 'Q1' through 'Qn'. STL generates a signal 'N1' which gets updated in the state memory, block 402, on the next input clock signal. 'N1' is logically represented as N1=((V1 and Q1 and (LB/RB# OR RS1)) OR (V2 and Q2 and (LB/RB# OR RS2)) OR . . . (Vn and Qn and (LB/RB# OR RSn)) AND ((NOT LB/RB# OR RS1). Similar signal for another state 'n', would be generated with similar logic, except that the signal 401, feeding into the OR gate, 415, would be 'RSn', which is the output of the 'n'-th symbol detection logic, changing the last term of the node 'N1' logic from ((NOT LB/RB# OR RS 1) to ((NOT LB/RB# OR RSn). The state memory, 402, can be implemented as a single bit flip-flop or a memory bit in the state logic block discussed below.

[0066] FIG. 4b illustrates a state logic block (SLB). The SLB comprises the STL. 406, Init logic. 408, state memory, 410, the accept state detect logic, 411, the SDV for this state, 407, start flag, 409, accept flag, 412, tag associated with this state, 419, or action associated with this state, 413 or a combination of the foregoing. The SLB receives current state vector and the received symbol vector which are fed to STL to determine the next state. The realization of a state of an arbitrary NFA can then be done by updating the SDV for the state and selecting the symbols that the NFA detects and takes actions on. Further, each state may get marked as a start state or an accept state or tagged NFA state or a combination or neither start or accept or tagged state through the start, tag and accept flags. The init logic block, 408, receives control signals that indicate if the state needs to be initialized from the start state or cleared or disabled from updates, or loaded directly with another state value, or may detect a counter value and decide to accept a transition or not and the like. The init block also detects if the FSA has received a symbol not recognized by the language of the regular expression and then may take the FSA into a predefined initial state to start processing the stream at the next symbol and not get into a state where it stops recognizing the stream. The Init block can be used to override the STL evaluation and set the state memory to active or inactive state. The STL, 406, provides functionality as illustrated in FIG. 4a, except that the state memory is included in the SLB as independent functional block, **410**. The state memory, 410, can be implemented as a single bit flip-flop or a memory bit. When the state memory is set it indicates-that the state is active otherwise the state is inactive. The accept detect logic, 411, detects if this state has been activated and if it is an accept state of the realized NFA. If the state is an accept state, and if this state is reached during the NFA evaluation, then the associated action is provided as an output of the SLB on the A1 signal, 416, and an accept state activation indicated on M1, 417. If the FSA reaches a state which is flagged as a tagged state using the tag flag, then the match detect logic may indicate a tag match, not illustrated, which another circuit can use to determine the action to be taken for the particular tag. The action could be set up to be output from the

SLB on the state activation as an accept state as well as when the state is not an accept state, like a tagged state, as required by the implementation of the NFA. This can enable the SLB to be used for tagged NFA implementation where an action or tag action can be associated with a given transition into a state.

[0067] If there are 'n' states supported per FSA rule, then each SLB needs 'n'-bit SDV which can be stored as a n-bit memory location, 3-bits allocated to start, tag and accept flags, 1-bit for LB/RB#, m-bit action storage. Thus if n=16 and m=6, then the total storage used per SLB would be a 26-bit register equivalent which is a little less than 4 bytes per state. If tag start flag and tag end flags are supported, not illustrated, then the number of memory bits would be 28-bits. If multiple tagged expressions need to be enabled then the number of bits for tagging may be appropriately increased. When the number of states in a resulting FSA of a RE is more than 'n' supported by the FSA of PRISM, a mechanism is required that would allow the PRISM memory to support such rules. The patent of this application describes such a mechanism and, an architecture described below.

[0068] FIG. 5a illustrates State transition logic (STL) for a state in a left-biased FSA. This figure illustrates state transition logic for a state of an FSA when the logic illustrated above for FIG. 4a is simplified with the LB/RB# set to active and symbol detection logic for one of the states illustrated. The symbol bits are illustrated as 'm-bit' wide as  $S_{1m} \dots S_{11}$ illustrated in block 502. The input character symbol bits are labeled as  $CIn_m ... CIn_1$ , 501. The symbol detection logic illustrated in FIG. 4a, 400, is illustrated as individual bits labeled  $E_m \dots E_1$ , 503, and is also referred to as symbol evaluation logic in this patent. The symbol dependent vector is labeled  $V_{n_1} \dots V_{11}$ , 504 which indicates the symbol dependent vector bit enabling transition into state 1 from each of the 'n' states that represent the CSV,  $Q_n \dots Q_1$ , 509, of the FSA. RS1, 505, is the result of the evaluation of the input character symbol with one symbol of the FSA,  $S_{tm} \dots S_{11}$  illustrated in block 502. The logic gates, 506 and 507, are NAND gates that form the logic function to generate the next state, Q1, based on the RS1, SDV,  $V_{n1} \dots V_{11}$ , and CSV,  $Q_n \dots Q_1$ . States  $Q_n$  $\dots$  Q<sub>2</sub> would be generated using similar circuit structure as the one illustrated in FIG. 5a, except the .RSV bit, SDV and the symbol specific to the particular state will be used. For example, for the generation of state  $Q_n$  the Symbol would be  $S_{nm} ext{...} S_{n1}$ , the SDV vector would be  $V_{nm} ext{...} V_{1n}$ , and the RSV bit would be RSn instead of RS1.

[0069] FIG. 5b illustrates State transition logic (STL) for a state in a right-biased FSA. This figure illustrates state transition logic for a state when the logic illustrated above for FIG. 4a is simplified with the LB/RB# set to inactive state and symbol detection logic for one of the states illustrated. Key differences between the right biased FSA circuit illustrated in this figure and the left-biased FSA illustrated in FIG. 5a, is that the next state generation logic depends on all received symbol vector bits, RS1, 505, through RSn, 505n, which are the result of the evaluation of the input character symbol with each of the 'n' symbols of the FSA instead of only one RSV bit, RS1, 505, illustrated in FIG. 5a. The logic gates. 506a and 507b, represent the right-biased FSA logic function to generate the next state based on the RSV, RS1, 505, through RSn, **505**n, SDV,  $V_{n1} cdots V_{11}$ , and CSV,  $Q_n cdots Q_1$ . States  $Q_n cdots Q_2$ would be generated using similar circuit structure as the one illustrated in FIG. 5b, except the SDV and the symbol specific to the particular state will be used. For example, for the generation of state  $Q_n$  the Symbol would be  $S_{nm} \dots S_n$ , the SDV vector would be  $V_{nn} \dots V_{1n}$ , and the RSV vector would be the same, RS1, 505, through RSn, 505n.

[0070] PRISM memory allows various elements of the ESA blocks to be programmable such that the compiler of this invention can accept a regular expression and compile it with information for various PRISM state elements to make the general purpose programmable state machine of PRISM FSA to implement the specific regular expression rule. The compiler can compile other rules and later replace the current rule with another rule in the same PRISM FSA or may use another PRISM FSA or a combination of the like.

[0071] FIG. 6A illustrates Right-biased Tagged FSA Rule block in PRISM. As discussed earlier the FSA of. PRISM are optionally Tagged. For clarity, FSA rule block, PRISM FSA rule block, PRISM FSA rule memory block, rule block, rule memory block, are used interchangeable in this application. Further, NFA rule block or PRISM NFA rule block or NFA rule memory block, are also used interchangeably and mean a PRISM FSA rule block where the FSA type is an NFA in this patent. The discussion below is with respect to tagged NFA, though it is also applicable for non-tagged NFAs or other FSA types where the tagging elements, described below, are not used or not present. This figure illustrates a state block 1, 601, which comprises of some elements of the state transition logic illustrated in FIG. 5b. The figure illustrates other state blocks, 602 and 603, that represent state blocks 2 through n, where 'n' is the number of states of the NFA or FSA programmed in this PRISM FSA rule block. These blocks are illustrated without details unlike state block 1. The primary difference between the blocks is that each state block generates its own RSV bit and uses only its own state bit from the CSV. For instance state block 2, generates RS2 by evaluating the received character with the symbol programmed in its symbol logic block which is similar to block 502. The state blocks are organized slightly differently than the illustration in FIG. 5b. The logic for one state illustrated in FIG. 5b, is illustrated to be organized in a vertical slice like, 614, where each state block holds portion of the logic necessary to form the final state. In this illustration the state Qn, 508n, is generated by processing the outputs from each state blocks'n'-th slice. The SDV vector bits held in each state block are for transition control from the specific state to all other states. For instance the blocks, like 504a, hold different members of the SDV vectors compared to the blocks, like 504. Thus the SDV for each state is distributed amongst multiple state blocks unlike that illustrated in FIG. 5b. For example state block 1, holds SDV vector bits  $V_{1n}$ ,  $V_{1(n-1)}$  through  $V_{11}$  indicating state transition vector bits for transitioning out of state 1 to the 'n' states, unlike FIG. 5b which are transposed where the state transition logic for a state holds bits  $V_{n1}, V_{(n-1)1}$  through  $V_{11}$  for transition into state 1. The indices  $V_{XY}$  indicate the state dependent vector bit that enables or disables transition from state X to state Y where each X and Y may have a range from 1 through where n is the number of states of the FSA. Thus the SDV of a state indicates the controls for enabling transitions from any state to itself as illustrated in 504, which indicates SDV transition controls from states n through 1 to state 1. As can be noticed the indices of the vector bits are reversed between the FIG. 5b and FIG. 6a. Thus a specific state's SDV is distributed in multiple state blocks and is illustrated aligned vertically like slice 614. This figure also illustrates the initialization logic, 408, illustrated in FIG. 4b as block 605 that affects what value gets loaded in the state memory bit, 508n,

under different conditions.like initialization, startup, error state, store and load or context switch and the like. Thus SDV vectors for an FSA are written to the FSA rule block in a state transposed manner as described above. The initialization block comprises of initialization/start state vector memory bits. Thus the input into the init block, 605, is logically equivalent to the node Nth in FIG. 5b, adjusted for the appropriate state bit. The state control block, 604, comprises of the logic gates, 507a, which logically NANDs the partial state output, like 615, from the state blocks 1 through state block n. The state control block, 604, further comprises of the init logic blocks, like 605, and the state memory blocks, like 508a. The FSA Rule block also comprises of tagged match detect block, 613, which may optionally comprise of tagging elements for supporting. tagged NFAs. The tagged match detect block comprises of Accept vector blocks, like 610, which comprise of accept vector memory bits and may optionally comprise of tag memory bits. The tagged match detect block further comprises of accept detect blocks, like 611, which comprise of accept state detection and may optionally comprise of tagged state or state transition detection logic. The state memory blocks, like 508, may be controlled be clock or enable or a combination signals to step the FSA amongst its states as new input characters are evaluated. The clocked enable signals may provide more control over simple clock by enabling when the FSA should be evaluated. For instance upon finding a match, the FSA controller, 802, described below may be programmed to hold further evaluation of any symbols for this FSA until the match information is processed. The FSA rule block generates multiple output signals that can be used to indicate the progress of the FSA. The FSA rule block outputs comprise of a Rule Match, 609, which indicates when the regular expression rule programmed in the FSA rule block is matched with characters of the input stream. The Rule Match signal may be used by the local or global priority encoder and evaluation processor, blocks 815 and 713 respectively described below, to decide on next steps to be taken based on user programmed actions and/or policies. The priority encoder and evaluation processors may optionally comprise of counters that may be triggered upon specific rule matches. The counters may be used for several purposes like statistical events monitoring, match location detection in the input stream and the like. The priority encoders may also decide the highest priority winner if multiple matches are triggered and then the output may be used to find the appropriate action associated with the matched regular expression rule. The FSA rule block output may optionally comprise of Tag Match signal(s) that may be used by the priority encoders and evaluation processors to detect partial regular expression matches. The number of tag match signals per FSA rule block may depend on the number of sub-expressions that are allowed to be detected in a given NFA. The FSA rule block is organized as a series of memory locations that each hold a portion of the NFA rule evaluation information using memory circuits like the SDV memory, Symbols memory, Mask vectors (discussed below) memory, initialization or start state vector memory, accept state vector memory, optionally tag state flag or vector memory, the FSA states memory or current state vector memory and the like. The FSA rule block comprises of FSA evaluation circuits interspersed amongst the memory blocks storing the FSA programmable information like the SDV, start state, accept state, symbols and the like. The FSA rule blocks evaluate multiple symbols against input stream for matches to step the FSA. Each symbol evaluation block, like 503, may optionally output an indication of a pattern comparison between the input character or symbol and the programmed symbol. These output signals, like 617, 614, 616, can be treated as local content addressable memory match signals. The PRISM memory may optionally support logic that enables generating merged CAM match signals from multiple FSA rule blocks organized in PRISM memory clusters, which may in turn be laid out in rows and columns of PRISM FSA rule blocks, to support larger width pattern matches. Thus the PRISM memory can be used as content addressable memory when enabled to process the CAM match signals. The PRISM memory can be optionally configured such that portions of the memory support CAM functionality while other portions may support FSA functionality or the entire PRISM memory may optionally be configured to behave like FSA memory or CAM memory. The CAM memories typically support functionality to detect 4 byte patterns, 18 byte patterns or even 144 byte patterns. PRISM memory may optionally provide configuration mechanisms to support similar large pattern evaluation by chaining multiple FSA rule blocks' CAM match signals using appropriate logic to generate composite CAM match signals for desired pattern width.

[0072] FIG. 6B illustrates Left-biased Tagged FSA Rule block in PRISM. As discussed earlier the FSA of PRISM are optionally Tagged. The discussion below is with respect to tagged NFA, though it is also applicable for non-tagged NFAs or other FSA types where the tagging elements, described below, are not used or not present. Left-biased FSA Rule blocks are similar in functionality as those discussed above for the Right-biased FSAs except for a few minor differences that enable the FSA rule block to behave as a Left-biased FSA. The state blocks, 601a, 602a, 603a, in the left-biased NFAs receive all RSV vector bits, like 505n, unlike a specific RSV bit per state block in the right-biased NFA. The input to NAND gates like **506**b, is. the specific RSV bit depending on the bit slice at the bit location in the state block of the NAND gate. Thus bit location 'p' where 'p' can range from 1 through 'n', uses RSp (Received Symbol Vector bit 'p') to generate the partial state block output, 615a. By making such a change in the blocks the NFA may now function as a left-biased NFA. The rest of the blocks perform similar functions as described above for a right-biased NFA.

[0073] PRISM memory may comprise of left-biased NFAs, right-biased NFAs or left-biased FSA or right-biased FSA or a combination of them or may be comprised as selectable left-biased or right-biased NFAs with logic similar to FIG. 4a. All such variations are within the scope of this invention, as may be appreciated by one with ordinary skill in the art.

[0074] FIG. 9 illustrates PRISM search compiler flow which is used for full and incremental rules distribution. For clarity, the PRISM search compiler is also referred to as search compiler or compiler in this patent application and the terms are used interchangeably. The search compiler of FIG. 9 allows an IT manager or user to create and compile the search and security rules of different types as illustrated by 901, 902 and 903, without limitations. Even though, the illustrated rules list primarily security type rules there may be regular expression rules for any other application that needs content search like many applications listed in this patent application. The compiler flow would optionally be provided with information about the specific nodes or networked systems or otherwise that may use PRISM and the characteristics of these nodes, like the security capability, the rules commu-

nication method, the size of the rule base supported, the performance metrics of the node, deployment location e.g. LAN or SAN or WAN or other, or the like for specific security or network related search applications. The compiler flow may optionally use this knowledge to compile node specific rules from the rule set(s) created by the IT manager or the user. The compiler comprises a rules parser, block 904, for parsing the rules to be presented to the PRISM FSA Compiler Flow, block 906, illustrated further in FIG. 10, which analyzes the rules and creates rules database that needs to be programmed into PRISM memory of the specific nodes or systems for analyzing the content. The rule parser may read the rules from files of rules or directly from the command line or a combination depending on the output of the rule engines like blocks 901, 902 and 903. The rules for a specific node are parsed to recognize the language specific tokens used to describe the rules or regular expression tokens and outputs regular expression (RE) rules, 905. The parser then presents the REs to the PRISM FSA compiler flow which processes the REs and generates NFA for RE. Optionally if tagging is supported by the specific PRISM instance, and if REs use tagging, the PRISM FSA compiler then decides whether the RE will be processed as a NFA or tagged NFA based on the PRISM memory capability. It then generates the NFA or tNFA rule in a format loadable or programmable into PRISM memory and stores the database in the compiled rules database storage, 908.