(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5543402号 (P5543402)

(45) 発行日 平成26年7月9日(2014.7.9)

(24) 登録日 平成26年5月16日 (2014.5.16)

(51) Int.Cl. F 1

HO4L

25/02

(2006.01)

HO4L

25/02

V

HO4L

25/03

(2006.01)

HO4L

25/03

Z

HO3K

19/0175

(2006.01)

HO3K

19/00

101F

請求項の数 11 (全 16 頁)

(21) 出願番号 特願2011-109326 (P2011-109326)

(22) 出願日 平成23年5月16日 (2011.5.16) (65) 公開番号 特開2012-244220 (P2012-244220A)

(43) 公開日 平成24年12月10日 (2012.12.10) 審査請求日 平成25年4月2日 (2013.4.2) ||(73)特許権者 000004695

株式会社日本自動車部品総合研究所 愛知県西尾市下羽角町岩谷14番地

||(73)特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

|(74)代理人 110000567

特許業務法人 サトー国際特許事務所

|(72)発明者 森 寛之|

愛知県西尾市下羽角町岩谷14番地 株式

会社日本自動車部品総合研究所内

(72) 発明者 前田 登

愛知県西尾市下羽角町岩谷14番地 株式

会社日本自動車部品総合研究所内

最終頁に続く

(54) 【発明の名称】リンギング抑制回路

# (57)【特許請求の範囲】

### 【請求項1】

一対の高電位側信号線,低電位側信号線によりハイ,ローの 2 値レベルに変化する差動信号を伝送する伝送線路に接続され、前記信号の伝送に伴い発生するリンギングを抑制するリンギング抑制回路において、

前記一対の信号線間に直列に接続される電圧駆動型の第1及び第2線間スイッチング素 子と、

前記差動信号のレベルが変化したことを検出すると、前記第 1 及び第 2 線間スイッチング素子を同時に一定期間オンさせる<u>ことで信号線間のインピーダンスを低下させる</u>制御手段とを備えることを特徴とするリンギング抑制回路。

10

# 【請求項2】

前記制御手段は、前記差動信号のレベルを反転して出力する反転回路と、

前記差動信号のレベルを前記一定期間遅延させて出力する遅延回路とを備え、

前記第1及び第2線間スイッチング素子の一方を前記反転回路より出力される信号によりターンオンさせ、前記第1及び第2線間スイッチング素子の他方を前記遅延回路より出力される信号によりターンオフさせることを特徴とする請求項1記載のリンギング抑制回路。

# 【請求項3】

前記反転回路は、電位基準側導通端子が前記一対の信号線の一方に接続され、制御端子

が前記差動信号がハイレベルを示すと導通状態となるように接続され、非基準側導通端子が前記線間スイッチング素子の一方の制御端子に接続される電圧駆動型の制御用スイッチング素子で構成され、

前記遅延回路は、前記一対の信号線間に接続される抵抗素子及びコンデンサの直列回路で構成され、前記抵抗素子及びコンデンサの共通接続点が前記線間スイッチング素子の他方の制御端子に接続されることを特徴とする請求項2記載のリンギング抑制回路。

#### 【請求項4】

前記制御用スイッチング素子を、ソースが前記低電位側信号線に接続され、ドレインが抵抗を介してプルアップされると共に前記線間スイッチング素子の制御端子に接続されるNチャネルMOSFETで構成し、

前記NチャネルMOSFETのゲートは、前記高電位側信号線に接続されることを特徴とする請求項3記載のリンギング抑制回路。

#### 【請求項5】

前記制御用スイッチング素子を、ソースが前記低電位側信号線に接続され、ドレインが抵抗を介してプルアップされると共に前記線間スイッチング素子の制御端子に接続されるNチャネルMOSFETで構成し、

前記反転回路は、前記高電位側信号線と前記低電位側信号線との間に接続される抵抗素子及びコンデンサの直列回路を備え、

前記NチャネルMOSFETのゲートは、前記直列回路の共通接続点に接続されていることを特徴とする請求項3記載のリンギング抑制回路。

#### 【請求項6】

前記反転回路は、アノードが前記低電位側信号線を向く方向で前記抵抗素子に並列接続されるダイオードを備えることを特徴とする請求項5記載のリンギング抑制回路。

#### 【請求項7】

前記制御用スイッチング素子を、ソースが前記高電位側信号線に接続され、ドレインが抵抗を介してプルダウンされると共に前記線間スイッチング素子の制御端子に接続されるPチャネルMOSFETで構成し、

前記 P チャネル M O S F E T のゲートは、前記低電位側信号線に接続されることを特徴とする請求項 3 記載のリンギング抑制回路。

# 【請求項8】

前記制御用スイッチング素子を、ソースが前記高電位側信号線に接続され、ドレインが抵抗を介してプルダウンされると共に前記線間スイッチング素子の制御端子に接続される PチャネルMOSFETで構成し、

前記反転回路は、前記高電位側信号線と前記低電位側信号線との間に接続されるコンデンサ及び抵抗素子の直列回路を備え、

前記PチャネルMOSFETのゲートは、前記直列回路の共通接続点に接続されていることを特徴とする請求項3記載のリンギング抑制回路。

#### 【請求項9】

前記反転回路は、アノードが前記低電位側信号線を向く方向で前記抵抗素子に並列接続されるダイオードを備えることを特徴とする請求項8記載のリンギング抑制回路。

# 【請求項10】

前記第1及び第2線間スイッチング素子を、それぞれ異なる導電型のスイッチング素子で構成し、

前記一対の信号線間に、前記第1及び第2線間スイッチング素子の直列回路を2組並列に接続し、それらの一方を第1直列回路、他方を第2直列回路とすると、

前記制御手段を、前記第1直列回路を制御する第1制御手段と、前記第2直列回路を制御する第2制御手段との2組備え、

前記第1及び第2制御手段を構成する第1及び第2制御用スイッチング素子を、それぞれの制御端子及び電位基準側導通端子と、前記一対の信号線との接続関係が互いに逆になる異なる導電型の素子で構成し、

10

20

30

40

前記第1及び第2制御用スイッチング素子の非基準側導通端子は、それぞれ抵抗素子を介してプルアップ又はプルダウンされると共に、前記第1及び第2直列回路における同じ 導電型の線間スイッチング素子の制御端子に接続され、

前記遅延回路を構成する直列回路は、抵抗素子が、それぞれ前記第1及び第2制御用スイッチング素子の基準電位側導通端子と共通の信号線側に接続されることを特徴とする請求項3乃至9の何れかに記載のリンギング抑制回路。

#### 【請求項11】

前記第1及び第2線間スイッチング素子は、互いのドレインが共通に接続され、ソースが前記高電位側信号線、低電位側信号線にそれぞれ接続されるPチャネルMOSFET及びNチャネルMOSFETで構成されることを特徴とする請求項1乃至10の何れかに記載のリンギング抑制回路。

【発明の詳細な説明】

### 【技術分野】

#### [0001]

本発明は、一対の高電位側信号線,低電位側信号線により差動信号を伝送する伝送線路に接続され、前記信号の伝送に伴い発生するリンギングを抑制する回路に関する。

#### 【背景技術】

#### [0002]

伝送線路を介してデジタル信号を伝送する場合、受信側においては、信号レベルが変化するタイミングで信号エネルギーの一部が反射することで、オーバーシュートやアンダーシュートのような波形の歪み,すなわちリンギングが生じる問題がある。そして、従来、波形歪みを抑制する技術については様々な提案がされている。例えば特許文献1では、伝送路の終端回路11において、信号の電圧レベルがロー,ハイ間で遷移する場合に、遅延回路20において付与される遅延時間の間、終端5のインピーダンスを一時的に低下させる技術が開示されている。

# [0003]

特許文献1では、従来使用されている終端切換回路40に対して並列に補助切換回路41を接続しており、補助切換回路41では、電源Vccとグランドとの間に4個のMOSFETを直列に接続し、それらのスイッチング制御を、終端5に伝送された信号と、当該信号を3直列のインバータ21~23により遅延させ、且つ反転させた信号とにより行っている。しかしながら、このような構成では、終端5を電源Vcc又はグランドに一時的に接続する際に過渡的に、両者の間に複数のMOSFETのオン抵抗が直列に、若しくは直列及び並列に接続される状態となる。このため、終端5のインピーダンスを十分に低下させることができない。オン抵抗を低下させるにはMOSFETのサイズを大きくする必要があるが、そうすると、終端回路11が大型化することになる。

#### [0004]

また、特許文献2では、差動信号を伝送する高電圧信号線路102,低電圧信号線路103の間にスイッチ202を接続し、波形歪検出部201が線路102,103間電圧の大小関係が逆転したことを検出すると、スイッチ202を閉じて線路102,103間を短絡させる構成が開示されている。

【先行技術文献】

#### 【特許文献】

# [0005]

【特許文献1】特開2001-127805号公報(図1参照)

【特許文献2】特開2010-103944号公報(図8参照)

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0006]

特許文献 2 のように、線路 1 0 2 , 1 0 3 間を短絡させれば線路間インピーダンスはゼロになり、伝送された信号を受信するノードの近傍では信号波形の歪みを低減することが

10

20

30

40

できる。しかしながら、短絡の場合は波形の歪み成分のエネルギーが消費されないため、 そのエネルギーは短絡点より反射して信号を送信したノードの側に到達することになる。 したがって、他のノードに悪影響を及ぼす結果となる。

#### [0007]

本発明は上記事情に鑑みてなされたものであり、その目的は、より簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供することにある。

#### 【課題を解決するための手段】

#### [0008]

請求項1記載のリンギング抑制回路によれば、一対の信号線間に、電圧駆動型の第1及び第2線間スイッチング素子を直列に接続し、制御手段は、差動信号のレベルが変化したことを検出すると、第1及び第2線間スイッチング素子を同時に一定期間オンさせる。すなわち、差動信号のレベルが遷移する期間に2つの線間スイッチング素子が導通することで信号線間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーを吸収させてリンギングの発生をより確実に抑制することができる。

#### [0009]

請求項2記載のリンギング抑制回路によれば、制御手段を、差動信号のレベルを反転して出力する反転回路と、差動信号のレベルを一定期間遅延させて出力する遅延回路とを備えて構成し、第1及び第2線間スイッチング素子の一方を反転回路より出力される信号によりターンオンさせ、第1及び第2線間スイッチング素子の他方を前記遅延回路より出力される信号によりターンオフさせる。すなわち、差動信号のレベルが変化する以前の状態で、一方の線間スイッチング素子がオフ,他方の線間スイッチング素子がオンしていれば、差動信号のレベルが変化すると前者が直ちにターンオンすることで双方の線間スイッチング素子がオン状態になる。その時点から一定期間が経過すれば他方の線間スイッチング素子がターンオフするので、リンギング抑制動作が停止する。

#### [0010]

請求項3記載のリンギング抑制回路によれば、反転回路を、電位基準側導通端子が一対の信号線の一方に接続され、制御端子が、差動信号がハイレベルを示すと導通状態となるように接続され、非基準側導通端子が線間スイッチング素子の一方の制御端子に接続される電圧駆動型の制御用スイッチング素子で構成する。すなわち、前記制御用スイッチング素子は、差動信号がハイレベルを示すと導通状態となることで非基準側導通端子、つまり一方の線間スイッチング素子の制御端子をローレベルにする。

# [0011]

また、遅延回路を、一対の信号線間に接続される抵抗素子及びコンデンサの直列回路で構成し、抵抗素子及びコンデンサの共通接続点を、線間スイッチング素子の他方の制御端子に接続する。すなわち、差動信号がローレベルであればコンデンサは放電状態であり、差動信号がハイレベルになるとコンデンサの充電が開始される。そして、一定期間が経過すると、直列回路の共通接続点の電位はハイレベルとなる。これにより、差動信号のレベルが変化してから一定期間の間は、反転回路,遅延回路より出力される各信号の論理が異なる状態となる。したがって、第1,第2線間スイッチング素子の導電型が互いに異なるようにすれば、各信号の論理が異なる一定期間に双方のスイッチング素子が同時にオンになる。

### [0012]

請求項4記載のリンギング抑制回路によれば、制御用スイッチング素子を、ソースが低電位側信号線に接続され、ドレインが抵抗を介してプルアップされると共に線間スイッチング素子の制御端子に接続されるNチャネルMOSFETで構成し、当該NチャネルMOSFETのゲートを高電位側信号線に接続する。これにより、差動信号レベルの反転信号が、NチャネルMOSFETのドレインに、すなわち、一方の線間スイッチング素子の制御端子に出力される。

### [0013]

20

10

30

20

30

40

50

請求項5記載のリンギング抑制回路によれば、制御用スイッチング素子を、ソースが低電位側信号線に接続され、ドレインが抵抗を介してプルアップされると共に線間スイッチング素子の制御端子に接続されるNチャネルMOSFETで構成する。また、反転回路として、高電位側信号線と低電位側信号線との間に接続される抵抗素子及びコンデンサの直列回路を備え、前記NチャネルMOSFETのゲートを直列回路の共通接続点に接続する。このように構成すれば、差動信号レベルがハイになった場合にNチャネルMOSFETのゲート電位の上昇を直列回路の時定数により遅延させることができる。したがって、差動信号波形が立下った後にオーバーシュートが発生した場合、そのオーバーシュートに追従してNチャネルMOSFETがターンオンすることを抑制し、線間スイッチング素子が一時的にターンオフすることを防止できる。

[0014]

請求項6記載のリンギング抑制回路によれば、反転回路を構成する抵抗素子に、アノードが低電位側信号線を向く方向でダイオードを並列接続する。これにより、オーバーシュートの発生に対する追従動作を遅延させる直列回路を設けた場合でも、差動信号レベルがハイからローに遷移する際の信号の反転を急速に行うことができる。

[0015]

請求項7記載のリンギング抑制回路によれば、制御用スイッチング素子を、ソースが高電位側信号線に接続され、ドレインが抵抗を介してプルダウンされると共に線間スイッチング素子の制御端子に接続されるPチャネルMOSFETで構成し、PチャネルMOSFETのゲートを低電位側信号線に接続する。これにより、差動信号レベルの反転信号が、PチャネルMOSFETのドレインに、すなわち、一方の線間スイッチング素子の制御端子に出力される。

[0016]

請求項8記載のリンギング抑制回路によれば、制御用スイッチング素子を、ソースが高電位側信号線に接続され、ドレインが抵抗を介してプルダウンされると共に線間スイッチング素子の制御端子に接続されるPチャネルMOSFETで構成する。また、反転回路に、高電位側信号線と低電位側信号線との間に接続されるコンデンサ及び抵抗素子の直列回路を備え、PチャネルMOSFETのゲートを前記直列回路の共通接続点に接続する。このように構成すれば、差動信号レベルがハイになった場合にPチャネルMOSFETのソース・ゲート間電位の上昇を直列回路の時定数により遅延させることができる。したがって、差動信号波形が立下った後にオーバーシュートが発生した場合、そのオーバーシュートに追従してPチャネルMOSFETがターンオンすることを抑制し、線間スイッチング素子が一時的にターンオフすることを防止できる。

[0017]

請求項9記載のリンギング抑制回路によれば、反転回路を構成する抵抗素子に、アノードが低電位側信号線を向く方向でダイオードを並列接続する。これにより、オーバーシュートの発生に対する追従動作を遅延させる直列回路を設けた場合でも、差動信号レベルがハイからローに遷移する際の信号の反転を急速に行うことができる。

[ 0 0 1 8 ]

請求項10記載のリンギング抑制回路によれば、一対の信号線間に、第1及び第2線間スイッチング素子の直列回路を2組並列に接続し、それらの一方を第1直列回路、他方を第2直列回路とし、制御手段も、第1直列回路を制御する第1制御手段と、第2直列回路を制御する第2制御手段との2組備える。そして、第1及び第2制御手段を構成する第1及び第2制御用スイッチング素子を、それぞれの制御端子及び電位基準側導通端子と、一対の信号線との接続関係が互いに逆になる異なる導電型の素子で構成する。また、第1及び第2制御用スイッチング素子の非基準側導通端子は、それぞれ抵抗素子を介してプルアップ又はプルダウンされ、第1及び第2直列回路における同じ導電型の線間スイッチング素子の制御端子に接続される。

[0019]

ここで、電圧駆動型のスイッチング素子は、電位基準側導通端子との制御端子との電位

差(端子間電位差と称す)に応じてスイッチング動作する。したがって、電源電圧と低電位側信号線との電位差、又は高電位側信号線とグランドとの電位差が変化すると、各スイッチング素子の導電型や接続状態によっては、端子間電位差が拡がる場合と狭まる場合とがある。伝送線路を介して差動信号を伝送する構成では、送信側のノードは、自身のグランド電位を基準に信号線をドライブすることで信号を送信する。しかしながら、伝送線路が長くなり、送信側のノードと受信側のノード若しくは終端回路との距離が離れている状態では、各ノードにおけるグランド電位が数V程度相違することがある。

#### [0020]

第1及び第2直列回路において、第1及び第2制御用スイッチング素子とそれぞれ同じ 導電型の線間スイッチング素子の制御端子は、何れか一方がプルアップされ、他方がプル ダウンされている。したがって、制御端子がプルアップされている線間スイッチング素子 については、差動信号がハイレベルとなった際の高電位側信号線の電位が、リンギング抑 制回路側のグランドレベル基準でより高くなっていればスイッチング動作し易くなり、よ り低くなっていればスイッチング動作し難くなる。一方、制御端子がプルダウンされてい る線間スイッチング素子については、差動信号がハイレベルとなった際の低電位側信号線 の電位がリンギング抑制回路側の電源レベル基準でより高くなっていればスイッチング動 作し難くなり、より低くなっていればスイッチング動作し易くなる。

# [0021]

そして、上述のように、各ノード間のグランド電位に差があることで、差動信号がハイレベルとなる時の低電位側信号線の電位が抑制回路側のグランドレベルに対して通常よりも高くなっていれば、電源電圧と低電位側信号線との電位差が狭まることで第1及び第2直列回路の一方のスイッチング素子はスイッチング動作し難くなる。しかしこの時、高電位側信号線の電位も、抑制回路側のグランドレベルに対して通常より高くなっているため、他方のスイッチング素子はスイッチング動作し易くなる。

#### [0022]

逆に、差動信号がハイレベルとなる時の低電位側信号線の電位が抑制回路側のグランドレベルに対して通常よりも低くなっていれば、電源電圧と低電位側信号線との電位差が拡がることで一方のスイッチング素子はスイッチング動作し易くなるが、高電位側信号線の電位も抑制回路側のグランドレベルに対して通常より低くなっているため、他方のスイッチング素子はスイッチング動作し難くなる。そこで、一対の信号線間に第1及び第2直列回路を並列に接続してそれぞれを第1及び第2制御手段により制御すれば、ノード間のグランド電位に差がある状態でも何れか一方が確実に動作するようになり、リンギングの抑制を確実に行うことができる。

# [0023]

請求項11記載のリンギング抑制回路によれば、第1及び第2線間スイッチング素子を、互いのドレインが共通に接続され、ソースが高電位側信号線、低電位側信号線にそれぞれ接続されるPチャネルMOSFET及びNチャネルMOSFETで構成するので、PチャネルMOSFETのゲート電位を高電位側信号線に対してローレベルとし、NチャネルMOSFETのゲート電位を低電位側信号線に対してハイレベルとすることで、双方を同時にオンにできる。

【図面の簡単な説明】

#### [0024]

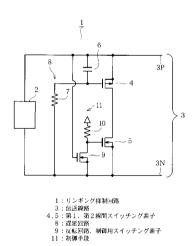

- 【図1】第1実施例であり、リンギング抑制回路の構成を示す図

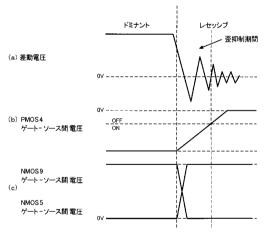

- 【図2】リンギング抑制回路の動作を示すタイミングチャート

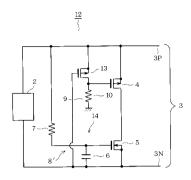

- 【図3】第2実施例を示す図1相当図

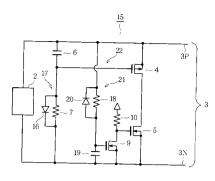

- 【図4】第3実施例を示す図1相当図

- 【図5】第4実施例を示す図1相当図

- 【図6】第5実施例を示す図1相当図

- 【図7】回路動作のシミュレーション結果を示す図(その1)

- 【図8】図7相当図(その2)

10

20

30

20

30

40

50

#### 【図9】図7相当図(その3)

【図10】第5実施例を示す図1相当図

【図11】回路動作のシミュレーション結果を示す図

【発明を実施するための形態】

# [0025]

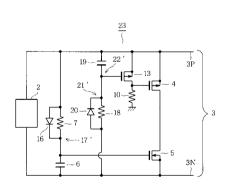

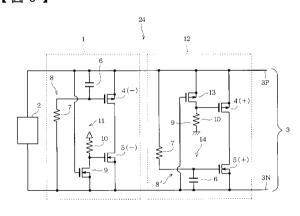

#### (第1実施例)

以下、第1実施例について図1及び図2を参照して説明する。図1は、リンギング抑制回路の構成を示している。リンギング抑制回路1は、送信回路(又は受信回路でも良い)2と共に、高電位側信号線3P,低電位側信号線3Nよりなる伝送線路3の間に並列に接続されている。リンギング抑制回路1は、伝送線路3の間にドレイン(非基準側導通端子)を共通にして直列に接続されるPチャネルMOSFET4及びNチャネルMOSFET5(第1及び第2線間スイッチング素子)を備えている。

#### [0026]

また、伝送線路3の間には、コンデンサ6及び抵抗素子7の直列回路が接続されており、両者の共通接続点はPチャネルMOSFET4のゲート(制御端子)に接続されている。上記直列回路は、遅延回路8を構成している。NチャネルMOSFET9(反転回路,制御用スイッチング素子)のソース(電位基準側導通端子)は、低電位側信号線3Nに接続されており、ドレインは抵抗素子10を介してハイレベル(電源レベル)にプルアップされ、ゲートは高電位側信号線3Pに接続されている。尚、遅延回路8,NチャネルMOSFET9,抵抗素子10は、制御回路(制御手段)11を構成している。

#### [0027]

次に、第1実施例の作用について図2を参照して説明する。伝送線路3は、例えば車載LANの1つであるCANのように、伝送線路3によりハイレベル,ローレベルの2値信号を差動信号として伝送する。例えば電源電圧が5Vの場合、高電位側信号線3P(CAN-H),低電位側信号線3N(CAN-L)は、非ドライブ状態において何れも中間電位である2.5Vに設定され、差動電圧は0Vであり、差動信号はローレベル(レセッシブ)となる。

# [0028]

そして、例えば送信回路2が伝送線路3をドライブすると、高電位側信号線3Pは例えば3.5V以上に、低電位側信号線3Nは例えば1.5V以下にドライブされ、差動電圧は2V以上となり、差動信号はハイレベル(ドミナント)となる。また、図示しないが、高電位側信号線3P,低電位側信号線3Nの両端は120 の抵抗素子により終端されている。したがって、差動信号レベルがハイからローに変化する際には、伝送線路3が非ドライブ状態となり伝送線路3のインピーダンスが高くなることから、差動信号波形にリンギングが発生する。

# [0029]

図2は、(a)差動信号レベルがハイからローに変化する際の各MOSFET4,5,9のゲート電位,すなわちオンオフ状態を示している。差動信号レベルがハイの場合、(c)NチャネルMOSFET9はオンしているので、NチャネルMOSFET5はオフしている。また、(b)PチャネルMOSFET4のソース基準のゲート電位(負電位)は、コンデンサ6の充電電圧分あるので、PチャネルMOSFET4はオンしている。

#### [0030]

この状態から、(a)差動信号レベルがハイからローに変化すると、(c)NチャネルMOSFET9がターンオフしてNチャネルMOSFET5がターンオンする。すると、高電位側信号線3P,低電位側信号線3N間はPチャネルMOSFET4及びNチャネルMOSFET5のオン抵抗を介して接続されることになり、インピーダンスが低下する。これにより、差動信号レベルがハイからローに変化する立下り期間に発生する波形歪みのエネルギーが上記オン抵抗により消費され、リンギングが抑制される。

#### [0031]

そして、(b)コンデンサ6の充電電荷が抵抗素子7を介して放電されるので、Pチャ

ネルMOSFET4のゲート・ソース間電圧の絶対値は次第に低下し、閾値を下回るとターンオフする。したがって、高電位側信号線3P,低電位側信号線3Nは、PチャネルMOSFET4及びNチャネルMOSFET5が双方ともオンしている歪み抑制期間だけ、それらのオン抵抗を介して接続されてインピーダンスが低下する。

### [0032]

以上のように本実施例によれば、一対の信号線3P,3N間に、PチャネルMOSFET4及びNチャネルMOSFET5の直列回路を接続し、制御回路11は、差動信号のレベルがハイからローに変化したことを検出すると、PチャネルMOSFET4及びNチャネルMOSFET5を同時に一定期間オンさせるようにした。これにより、差動信号のレベルが遷移する期間に信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーをFET4及び5のオン抵抗により吸収させてリンギングの発生を確実に抑制することができる。

#### [0033]

そして、制御回路11を、差動信号のレベルを反転して出力するNチャネルMOSFET9と、差動信号のレベルを一定期間遅延させて出力する遅延回路8とを備えて構成し、NチャネルMOSFET9をターンオフさせてNチャネルMOSFET5をターンオンさせ、遅延回路8を、信号線3P,3N間に接続されるコンデンサ6及び抵抗素子7の直列回路で構成し、両者の共通接続点を、PチャネルMOSFET4のゲートに接続するようにした。

# [0034]

すなわち、差動信号がハイレベルの状態では、コンデンサ6が充電状態でPチャネルMOSFET4はオン,NチャネルMOSFET9がオンしているのでPチャネルMOSFET5はオフであり、差動信号のレベルがローに変化すると後者が直ちにターンオンして双方のFET4及び5がオン状態になる。その時点から一定期間が経過すればPチャネルMOSFET4がターンオフしてリンギング抑制動作が停止する。したがって、遅延回路8の時定数によりリンギング抑制動作が有効となる期間を調整できる。

# [0035]

#### (第2実施例)

図3は第2実施例であり、第1実施例と同一部分には同一符号を付して説明を省略し、以下異なる部分について説明する。第2実施例のリンギング抑制回路12は、PチャネルMOSFET5とのオンオフ状態が第1実施例と逆になるように構成したものである。

#### [0036]

すなわち、NチャネルMOSFET9に替わるPチャネルMOSFET(反転回路,制御用スイッチング素子)13のソースは高電位側信号線3Pに、ゲートは低電位側信号線3Nに接続され、ドレインはPチャネルMOSFET4のゲートに接続されると共に、抵抗素子10を介してグランド電位にプルダウンされている。また、NチャネルMOSFET5のゲートは、抵抗素子7を介して高電位側信号線3Pに接続されると共に、コンデンサ6を介して低電位側信号線3Nに接続されている。そして、抵抗素子7及びコンデンサ6の直列回路は、遅延回路8'を構成している。そして、遅延回路8'とNチャネルMOSFET13とは制御回路(制御手段)14を構成している。

#### [0037]

次に、第2実施例の作用について説明する。差動信号レベルがハイの場合、 Pチャネル MOSFET 13はオンしているので、 Pチャネル MOSFET 4はオフしている。また、 Nチャネル MOSFET 5のゲート電位は、 コンデンサ 6の充電電圧; ハイレベル相当分になっているので、 Nチャネル MOSFET 5はオンしている。この状態から差動信号レベルがハイからローに変化すると、 Pチャネル MOSFET 13がターンオフして Pチャネル MOSFET 4がターンオンする。すると、 高電位側信号線 3 P, 低電位側信号線 3 N間は Pチャネル MOSFET 5のオン抵抗を介して接続されることになり,差動信号の立下り期間に発生する波形歪みのエネルギーが上記オン

10

20

30

40

20

抵抗により消費され、リンギングが抑制される。

# [0038]

そして、コンデンサ6の充電電荷が抵抗素子7を介して放電されるので、NチャネルMOSFET5のゲート電位は次第に低下し、閾値を下回るとターンオフする。したがって、高電位側信号線3P,低電位側信号線3Nは、第1実施例と同様に、PチャネルMOSFET4及びNチャネルMOSFET5が双方ともオンしている期間だけ、それらのオン抵抗を介して接続される。

#### [0039]

以上のように第2実施例によれば、反転回路を、ソースが高電位側信号線3Pに接続され、ドレインが抵抗素子10を介してプルダウンされると共にPチャネルMOSFET4のゲートに接続されるPチャネルMOSFET13で構成し、PチャネルMOSFET13のゲートを低電位側信号線3Nに接続した。これにより、差動信号レベルの反転信号が、PチャネルMOSFET13のドレインに、すなわち、PチャネルMOSFET4のゲートに出力されるので、第1実施例と同様の効果が得られる。

### [0040]

#### (第3実施例)

図4は第3実施例であり、第1実施例と異なる部分について説明する。第3実施例のリンギング抑制回路15は、第1実施例のリンギング抑制回路1において、抵抗素子7にダイオード16を並列に接続することで遅延回路17を構成している。また、NチャネルMOSFET9のゲートを抵抗素子18を介して高電位側信号線3Pに接続すると共に、コンデンサ19を介して低電位側信号線3Nに接続し、抵抗素子18にはダイオード20を並列に接続している。

#### [0041]

ここで、NチャネルMOSFET9,抵抗素子10及び18,コンデンサ19及びダイオード20は、反転回路21を構成している。尚、ダイオード16は、アノードが高電位側信号線3P側となるように、ダイオード20は、アノードが低電位側信号線3N側となるように接続されている。そして、遅延回路17及び反転回路21が制御回路(制御手段)22を構成している。

### [0042]

次に、第3実施例の作用について説明する。第1実施例の構成では、差動信号レベルがハイからローに変化する際に信号波形が立下がった後にオーバーシュートが発生すると、NチャネルMOSFET9がターンオンしてNチャネルMOSFET5がターンオフするため、リンギング抑制効果が低減することが想定される。そこで、NチャネルMOSFET9のゲートを高電位側信号線3Pに直接接続せず、抵抗素子18及びコンデンサ19の共通接続点に接続する。

### [0043]

これにより、差動信号レベルがローからハイに変化する場合は、コンデンサ19の充電が抵抗素子18を介して行われるのでゲート電位の上昇が緩やかになり、差動信号レベルがハイからローに変化する場合は、コンデンサ19の放電はダイオード20を介して急速に行われる。したがって、差動信号の立ち下りに対しては直ちにリンギングを抑制するように作用させ、その立ち下りに続いてオーバーシュートが発生しても、PチャネルMOSFET4及びNチャネルMOSFET5のオン状態を極力維持するようにして、リンギング抑制作用を継続させる。

# [0044]

また、遅延回路17の作用により、差動信号レベルがローからハイに変化する場合は、コンデンサ6の充電は、抵抗素子7の端子電圧が順方向電圧以上となる期間は、ダイオード16を介して急速に行われ、コンデンサ6の充電が進んで上記端子電圧が順方向電圧未満になると、充電電流は抵抗素子7を介して流れるので充電が遅くなる。したがって、付与される遅延時間が第1実施例の場合よりも若干短くなる。

# [0045]

50

20

30

40

50

以上のように第3実施例によれば、反転回路21として、高電位側信号線3Pと低電位側信号線3Nとの間に接続される抵抗素子18及びコンデンサ19の直列回路を備え、NチャネルMOSFET9のゲートを上記直列回路の共通接続点に接続した。したがって、差動信号波形が立下った後にオーバーシュートが発生した場合、そのオーバーシュートに追従してNチャネルMOSFET9がターンオンすることを抑制し、NチャネルMOSFET5を一時的にターンオフさせることを防止できる。

#### [0046]

また、抵抗素子18に、アノードが低電位側信号線3N側となる方向でダイオード20を並列接続したので、オーバーシュートの発生に対する追従動作を遅延させる直列回路を設けた場合でも、差動信号レベルがハイからローに遷移する際の信号の反転を急速に行うことができる。加えて、遅延回路17を構成する抵抗素子7に、ダイオード16を並列に接続することで、付与される遅延時間を調整できる。

# [0047]

(第4実施例)

図5は第4実施例であり、第2又は第3実施例と異なる部分について説明する。第4実施例のリンギング抑制回路23は、第2実施例のリンギング抑制回路12について、第3実施例と同様に遅延回路を付加した構成となっている。すなわち、抵抗素子7の両端には、ダイオード16が第3実施例と同様の方向に接続されて遅延回路17,を構成している。また、第3実施例の遅延回路21について、抵抗素子16及びコンデンサ17の接続順を逆にしたものが遅延回路21,を構成しており、両者の共通接続点は、PチャネルMOSFET13のゲートに接続されている。そして、遅延回路17,及び反転回路21,が制御回路(制御手段)22,を構成している。

以上のように構成される第4実施例によれば、第2実施例の構成についても第3実施例と同様の効果が得られる。

#### [0048]

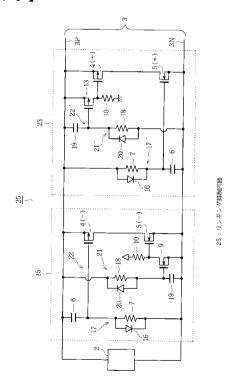

(第5実施例)

図6ないし図9は第5実施例である。第5実施例は、伝送線路3の間に、第1実施例のリンギング抑制回路1と、第2実施例のリンギング抑制回路12とを並列に接続したもので、リンギング抑制回路24を構成している。また、リンギング抑制回路1,12で同一の符号を付したものについて、前者の符号には(-)を、後者の符号には(+)を付して区別する。この場合、PチャネルMOSFET4(-)及びNチャネルMOSFET5(-)の直列回路は第1直列回路に相当し、PチャネルMOSFET4(+)及びNチャネルMOSFET5(+)の直列回路は第1直列回路に相当する。また、リンギング抑制回路1の制御回路11は第1制御手段に相当し、リンギング抑制回路12の制御回路14は第2制御手段に相当する。

#### [0049]

斯様な構成を採用することで、以下のような効果が得られる。車載LANの伝送線路3のように車両の各部に通信ノードが配置される構成の場合、各通信ノードにおいて接続されているグランドの電位が異なること(グランドオフセット)が想定される。リンギング抑制回路1の場合、PチャネルMOSFET5のゲートは電源レベルにプルアップされている。したがって、差動信号がハイレベルを示した際の低電位側信号線3Nの電位が上昇すると、つまり、自ノードのグランドレベルよりも送信ノードのグランドレベルが高い状態にあるとすれば、ゲート・ソース間電位差が小さくなり、PチャネルMOSFET5はオン状態を維持し難くなる。しかしこの時、リンギング抑制回路12では、差動電圧で動作するNチャネルMOSFET5の動作に影響は無く、且つ、ゲートが自ノードのグランドレベルにプルダウンされているPチャネルMOSFET4については、ソース電位が上昇することに等しいので、問題なく動作できる。

#### [0050]

そして、上記の関係は、自ノードのグランドレベルよりも送信ノードのグランドレベルが低い場合は逆転し、リンギング抑制回路1のPチャネルMOSFET5のゲート・ソー

ス間電位差が大きくなることで動作に問題が無く、一方でリンギング抑制回路11の P チャネルMOSFET4はゲート・ソース間電位差が小さくなり動作し難くなる。したがって、リンギング抑制回路1,12を並列に接続することで、通信ノード間にグランドオフセットが存在する場合でも、少なくともリンギング抑制回路1,12の何れか一方が確実に動作するので、リンギング抑制効果が確実に得られる。

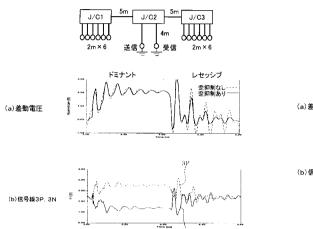

#### [0051]

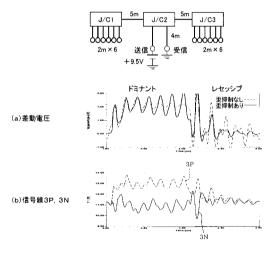

図7ないし図9は、リンギング抑制回路24の動作をシミュレーションした結果を示す。図7には、シミュレーションに用いたCANのネットワークモデルを示している。3つのジャンクションコネクタ」/C1, J/C3の間は5mの伝送線路で接続されており、ジャンクションコネクタ」/C1, J/C3には、それぞれ6つの通信ノードが何れも2mの伝送線路を介して接続されている。そして、ジャンクションコネクタ」/C2には、送信ノード, 受信ノードがそれぞれ4mの伝送線路を介して接続されており、受信ノード側の伝送線路にリンギング抑制回路24を接続している。

### [0052]

図7(a)は、送信ノード,受信ノードのグランドレベルにオフセットが存在しない場合のシミュレーション結果であり、リンギング抑制回路24を接続した場合(実線;歪抑制あり)と接続しない場合(破線;歪抑制なし)との双方を示している。図7(a)は差動信号がドミナントからレセッシブに変化する場合の電圧波形であり、図7(b)はその際の信号線3P,3N(CAN-H,CAN)-Lそれぞれの電圧波形である。図7(a)に示すように「歪抑制あり」の方が、レセッシブに移行した後の電圧波形の振動がより早く収束していることが分かる。

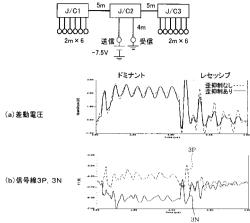

#### [0053]

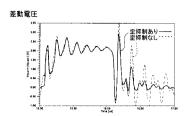

図8は、送信ノードのグランドレベルが受信ノードのグランドレベルより7.5 V低い場合の図7相当図であり、図8(b)に示すように、信号線3P,3Nの電圧波形は、-5 Vを中心とする差動電圧となっている。また、図9は、送信ノードのグランドレベルが受信ノードのグランドレベルより9.5 V高い場合の図7相当図であり、図9(b)に示すように、信号線3P,3Nの電圧波形は、12 Vを中心とする差動電圧となっている。これらの結果より、通信ノード間のグランドに電位差がある場合でも、リンギング抑制回路24が動作してリンギングを抑制していることが分かる。

以上のように第5実施例によれば、信号線3P,3N間に、リンギング抑制回路1,12を並列に接続することでリンギング抑制回路24を構成した。したがって、各通信ノード間のグランド電位に差がある状態でも何れか一方が確実に動作するようになり、リンギングの抑制を確実に行うことができる。

# [0054]

# (第6実施例)

図10及び図11は第6実施例である。第6実施例は、信号線3P,3N間に、第3実施例のリンギング抑制回路15と第4実施例のリンギング抑制回路23とを並列に接続してリンギング抑制回路25を構成している。リンギング抑制回路15,23は、何れも差動信号波形の立下り後に発生するオーバーシュートの抑制対策を施したもので、図11には、グランドオフセットが無い場合のシミュレーション結果を示している。図7(a)と図11とを比較すると、前者のオーバーシュートの波高値は3Vを超えているが、後者の波高値は3V未満となっている。そして、全体的にリンギング波形の振幅が低下し、且つ変動が収束する時間も短くなっており、総じてリンギング抑制効果がより高くなっていると言える。

以上のように構成される第6実施例によれば、信号線3P,3N間に、リンギング抑制 回路15,23を並列に接続したので、第5実施例よりも高いリンギング抑制効果を得る ことができる。

#### [0055]

本発明は上記し又は図面に記載した実施例にのみ限定されるものではなく、以下のような変型又は拡張が可能である。

10

20

30

40

リンギング抑制回路は、伝送線路の何れか1か所以上に接続すれば良いが、各通信ノードの近傍にそれぞれ接続しても良い。

第1,第2線間スイッチング素子を同じ導電型の素子で構成しても良い。

反転回路21を構成するダイオード20は、必要に応じて接続すれば良い。

スイッチング素子はMOSFETに限ることなく、電圧駆動型の素子であれば良い。

リンギング抑制回路を、差動信号レベルがローからハイに変化する場合に発生するリンギングを抑制するように構成しても良い。

CANに限ることなく、1対の信号線により差動信号を伝送する通信プロトコルであれば適用が可能である。

# 【符号の説明】

# [0056]

図面中、1はリンギング抑制回路、3は伝送線路、3Pは高電位側信号線、3Nは低電位側信号線、4はPチャネルMOSFET(第1線間スイッチング素子)、5はNチャネルMOSFET(第2線間スイッチング素子)、6はコンデンサ、7は抵抗素子、8は遅延回路、9はNチャネルMOSFET(反転回路,制御用スイッチング素子)、10は抵抗素子、11は制御回路(制御手段)、12はリンギング抑制回路、13はPチャネルMOSFET(反転回路,制御用スイッチング素子)、14は制御回路(制御手段)、15はリンギング抑制回路、16はダイオード、17は遅延回路、20はダイオード、21は反転回路、22は制御回路(制御手段)、23~25はリンギング抑制回路を示す。

# 【図1】

# 【図2】

# 【図3】

- 12: リンギング抑制回路 13: 反転回路、制御用スイッチング素子 14:制御手段

# 【図4】

- 15:リンギング抑制回路 17:遅延同路 21:反転回路 22:制御回路

# 【図5】

23:リンギング抑制回路

# 【図6】

24:リンギング抑制回路

【図7】

【図8】

【図9】

【図10】

# 【図11】

# フロントページの続き

(72)発明者 小畑 洋幸

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 北川 昌宏

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 岸上 友久

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 小池 智札

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

# 審査官 白井 亮

(56)参考文献 特開2005-236915(JP,A)

特開平11-154045(JP,A)

特開2008-294682(JP,A)

特開2003-258605(JP,A)

実開昭63-081518(JP,U)

(58)調査した分野(Int.CI., DB名)

H04L 25/02

H03K 19/0175

H04L 25/03