СОЮЗ СОВЕТСНИХ СОЦИАЛИСТИЧЕСНИХ РЕСПУБЛИН

## (19) <u>SU(11)</u> <u>1370611</u> <u>A1</u>

(51) 4 GO1 R 27/18

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

## ОПИСАНИЕ ИЗОБРЕТЕНИЯ

## К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

(21) 4059074/24-21

(22) 18.04.86

(46) 30.01.88. Бюл. № 4

(71) Витебское областное производственно-техническое управление связи и Витебское производственное объединение "Электроизмеритель"

(72) В.Н. Брызгало, Л.Н. Карпиловский, И.М. Матвеев и В.Ф. Шуляев

(53) 621.317.735(088.8)

(56) Авторское свидетельство СССР

№ 978073, кл. G 01 R 27/18, 1980. Авторское свидетельство СССР

№ 1118939, кл. G 01 R 27/18, 1983. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРО-ТИВЛЕНИЯ И ЕМКОСТИ ЭЛЕКТРИЧЕСКИХ И СИГНАЛЬНЫХ СЕТЕЙ ОТНОСИТЕЛЬНО ЗЕМЛИ (57) Изобретение относится к электроизмерительной технике и служит для повышения помехозащищенности передаваемого по контролируемой сети информационного сигнала от спектра контролирующего сигнала. Устройство содержит генератор 1 импульсов, образцовый резистор 2, конденсатор 3, программный блок 6, блок 7 фиксации уровней. Введение конденсатора 4. развязывающего блока 5, вычислителя 8, аналоговых ключей 9 и 10, индикаторов 11 и 12, блока 13 коррекции и образование новых функциональных связей позволяет использовать контролирующий сигнал специальной формы. В описании приведены примеры реализации генератора l импульсов, развязывающего блока 5, програминого блока 6, блока 7 фиксации уровней, вычислителя 8 и блока 13 коррекции. 6 з.п.ф-лы, 7 ил.

фиг.1

10

Изобретение относится к электроизмерительной технике и может быть использовано для измерения сопротивления и емкости электрических или сигнальных сетей относительно земли.

1

Цель изобретения - повышение помехозащищенности передаваемого по контролируемой сети информационного сигнала от спектра контролирующего сигнала за счет использования контролирующего сигнала специальной формы.

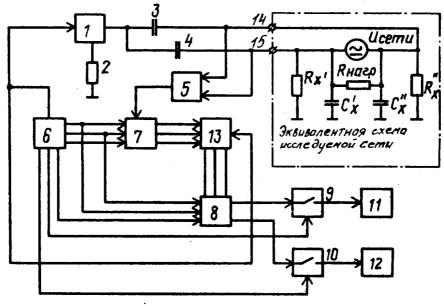

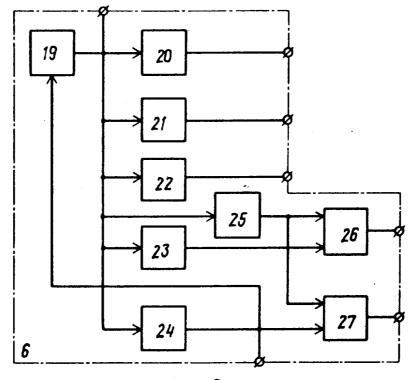

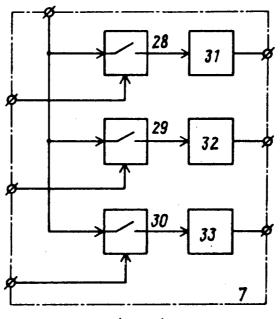

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема развязывающего блока; на фиг. 3 - фун-15 кциональная схема программного блока; на фиг. 4 - функциональная схема блока фиксации уровней; на фиг. 5 - функциональная схема вычислителя; на фиг. 6 - функциональная схема блока 20 коррекции; на фиг. 7 - диаграммы напряжений в основных точках устройства.

На фиг. 1 обозначены генератор 1 импульсов, образцовый резистор 2, 25 первый 3 и второй 4 конденсаторы, развязывающий блок 5, программный блок 6, блок 7 фиксации уровней, вычислитель 8, первый 9 и второй 10 аналоговые 30 ключи, первый 11 и второй 12 индикаторы, блок 13 коррекции, первая 14 и вторая 15 клеммы для подключения к объекту измерений, причем первый выход генератора 1 подключен к первому выводу резистора 2, второй вывод которого соединен с общей шиной, второй выход генератора 1 соединен с первым выводом первого конденсатора 3, второй вывод которого соединен с первой клеммой 14, первый вывод програм- 40 много блока 6 соединен с первым вход дом блока 7 фиксации уровней, второй выход программного блока соединен с входом генератора 1, первый вывод н второго конденсатора 4 соединен с вторым выходом генератора 1, а второй - с второй клеммой 15, третий и четвертый выходы программного блока 6 подключены соответственно к второму и третьему входам блока 7 фиксации уровней, первый, второй и третий выходы которого подключены соответственно к первому, второму и третьему входам блока 13 коррекции, первый, второй и третий выходы которого соедине- 55 ны соответственно с первым, вторым и третьим входами вычислителя 8, четвертый, пятый и шестой входы которого подключены соответственно к перво-

му, третьему и пятому выходам программного блока 6, шестой и седьмой выходы которого соединены с коммутирующими входами соответственно первого 9 и второго 10 аналоговых ключей. входы которых соединены соответственно с первым и вторым выходами вычислителя 8, а выходы - с входами соответственно первого 11 и второго 12 индикаторов, четвертый вход блока 13 коррекции соединен с третьим выходом программного блока 6, четвертый вход блока 7 фиксации уровней соединен с выходом развязывающего блока 5, первый и второй входы которого соединены соответственно с первой 14 и второй 15 клеммами.

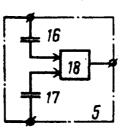

На фиг. 2 обозначены первый 16 и второй 17 развязывающие конденсаторы и сумматор 18, причем первые выводы первого 16 и второго 17 развязывающих конденсаторов соединены соответственно с первым и вторым входами блока 5, а вторые - соответственно с первым и вторым входами сумматора 18, выход которого соединен с выходом блока 5.

Программный блок (фиг. 3) содержит генератор 19 тактовых импульсов, с первого по пятый элементы 20-24 задержки, триггер 25 и первый 26 и второй 27 элементы И, причем выход генератора 19 соединен с входом каждого из элементов 20-24 задержки и счетным 35 входом триггера 25, инверсный выход которого соединен с первыми входами первого 26 и второго 27 элементов И. вторые входы которых соединены с выходами соответственно четвертого 23 и пятого 24 элементов задержки, выходы первого 20, второго 21 и третьего 22 элементов задержки соединены соответственно с седьмым, первым и третьим выходами блока 6, выходы пер-45 вого 26 и второго 27 элементов И соединены соответственно с пятым и шестым выходами блока 6, четвертый выход которого соединен с выходом пятого элемента 24 задержки и входом 50 генератора 19.

На фиг. 4 обозначены первый 28. второй 29 и третий 30 аналоговые ключи и первый 31, второй 32 и третий 33 элементы аналоговой памяти, причем информационные входы первого 28, второго 29 и третьего 30 ключей соединены с четвертым выходом блока 7, улравляющие входы - соответственно с первым, вторым и третьим входами бло-

2

ка 7, а выходы - с входами соответственно первого 31, второго 32 и третьего 33 элементов памяти, выходы которых соединены соответственно с первым, вторым и третьим выходами блока 7.

3

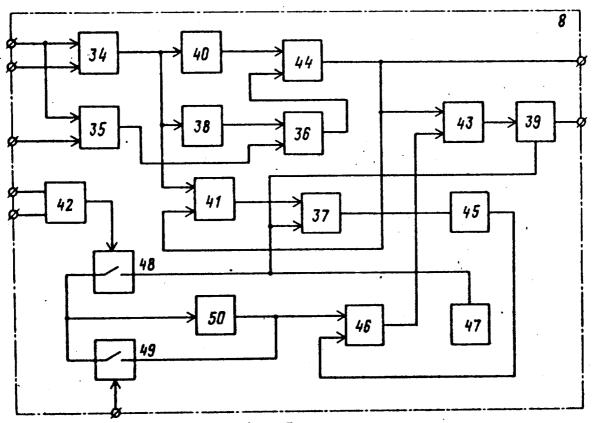

Вычислитель 8 содержит (фиг. 5) с первого по четвертый дифференциальные усилители 34-37, масштабный 38 10 усилитель, сумматор 39, квадратор 40, первый блок 41 деления, триггер 42, второй 43 и третий 44 блоки деления, логарифмический усилитель 45, четвертый блок 46 деления, источник 47 опор-15 ного напряжения, первый 48 и второй 49 аналоговые ключи и интегратор 50, причем первый вход вычислителя 8 соединен с инвертирующими входами первого 34 и второго 35 дифференциаль-20 ных усилителей, неинвертирующие входы которых соединены соответственно с вторым и третьим входами вычислителя 8, выход первого дифференциального усилителя 34 соединен с входами 25 квадратора 40, масштабного усилителя 38 и первым входом первого блока 41 деления, выход которого соединен с первым входом четвертого дифференциального усилителя 37, выход кото-30 рого соединен с входом логарифмического усилителя 45, выход источника 47 опорного напряжения соединен с инвертирующим входом четвертого дифференциального усилителя 37, информа-35 ционным входом первого ключа 48 и первым входом сумматора 39, выход которого соединен с вторым входом вычислителя 8, а вход - с выходом второго блока 43 деления, первый вход 40 которого соединен с выходом четвертого блока 46 деления, а второй - с вторым входом первого блока 41 деления, первым выходом вычислителя 8 и выходом третьего блока 44 деления, пер-45 вый вход которого соединен с выходом квадратора 40, а второй - с выходом третьего дифференциального усилителя 36, инвертирующий вход которого соединен с выходом второго дифферен-50 циального усилителя 35, а неинвертирующий - с выходом масштабного усилителя 38, четвертый и пятый входы вычислителя 8 соединены с входами соответственно установки в "1" и установ-55 ки в "О" триггера 42, инверсный выход которого соединен с управляющим входом первого ключа 48, выход которого соединен с входом интегратора 50 и

информационным входом второго ключа 49, управляющий вход которого соединен с шестым входом вычислителя 8, а выход – с выходом интегратора 50 и первым входом четвертого блока 46 деления, второй вход которого соединен с выходом логарифмического усилителя 45.

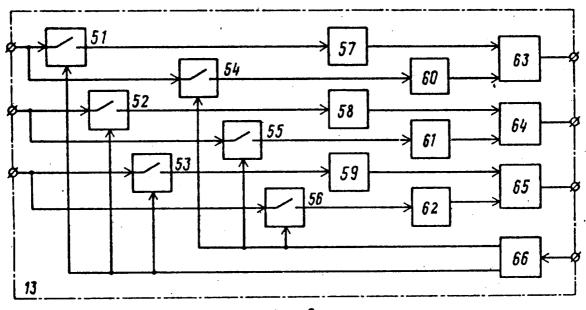

На фиг. 6 обозначены с первого по шестой аналоговые ключи 51-56. с первого по шестой аналоговые элементы 57-62 памяти, первый 63, второй 64 и третий 65 дифференциальные усилители и триггер 66 со счетным входом, причем информационные входы первого 51 и четвертого 54 ключей соединены с первым входом блока 13, информационные входы второго 52 и пятого 55 ключей соединены с вторым входом блока 13, информационные входы третьего 53 и шестого 56 ключей соединены с третьим входом блока 13, выходы ключей 51-56 соединены соответственно с входами элементов 57-62

памяти, выходы первого 57, второго 58 и третьего 59 элементов памяти соединены с инвертирующими входами соответственно первого 63, второго 64 и третьего 65 усилителей, выходы чет-

вертого 60, лятого 61 и шестого 62 элементов памяти соединены с неинвертирующими входами соответственно первого 63, второго 64 и третьего 65 усилителей, выходы которых соединены соответственно с первым, вторым и третьим выходами блока 13, четвертый вход которого соединен со счетным входом триггера 66, прямой выход которого соединен с управляющими входами первого 51, второго 52 и третьего 53 ключей, а инверсный - с управляющими входами четвертого 54, пятого 55 и шестого 56 ключей.

Устройство работает следующим образом.

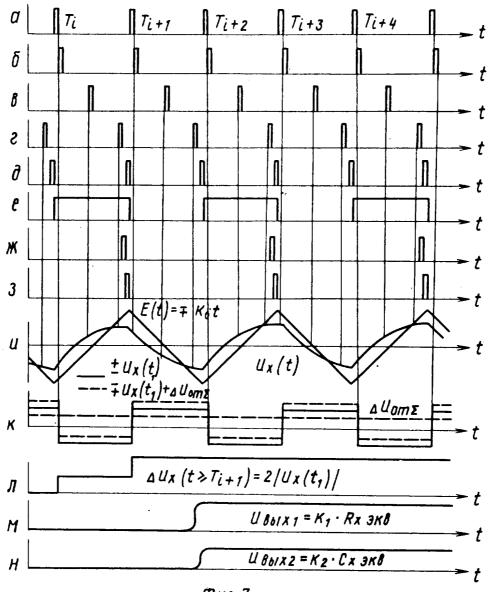

От генератора 1 тестовое двухполярное напряжение пилообразной формы  $\pm E$  (t) (фиг.7) последовательно через образцовый резистор 2 и конденсаторы 3 и 4 поступает одновременно на оба полюса контролируемой сети. При этом на импеданс изоляции выделяется информационный сигнал U<sub>x</sub> (t) (фиг.7), напряжение которого в оперативной форме запишем в виде

$$U_{\mathbf{x}}(\mathbf{P}) = \pm \frac{K_{0}}{\mathbf{P}} \quad \frac{C_{0}}{C_{0} + C_{\mathbf{x}}} \quad \frac{1}{\mathbf{P} + \frac{1}{\varepsilon_{\mathbf{x}}}}, \quad (1)$$

где  $C_x = C_x^i / / C_x^{\mu} =$ =  $C_x^i + C_x^{\nu}$

- эквивалентная ем-

£ x = R x(Co+Cx) - постоянная времетии переходного

процесса установ-10

ления реакции

сети на тестовое

воздействие;

$$R_{x} = \frac{R_{x}}{R_{x}} / \frac{R_{x}}{R_{x}} = \frac{R_{x}}{R_{x}} - \frac{R_{x}}{R_{x}}$$

эквивалентное со-15 противление изоляции сети;

К<sub>о</sub> - скорость нарастания фронтов тестового сигнала 20 Е (t).

Во временной форме напряжение  $U_{*}(t)$  запишется тогда как

$$U_{x}(t) = \pm K_{o} \frac{C}{C_{o} + C_{x}} \mathcal{L}_{x} (1 - C^{\frac{1}{T_{x}}}) = 25$$

=  $\pm K_{o} C_{o} R_{x} (1 - e^{-t/T_{x}}).$  (2)

Контролируемое сопротивление изоляции определяют исходя из измеренных в фиксированные моменты  $t_i$  и  $t_2 = 30$ = n·t, мгновенных значений информационного сигнала  $U_x(t_i) = U_{x_i}$  и  $U_x(t_2) = U_{x_2}$ . Действительно, эти значения на основании (2) можно записать как 35

$$U_{x_{1}} = \pm K_{o}C_{o}R_{x}(1 - e^{-\frac{1}{\widehat{c}_{x}}});$$

$$U_{x_{0}} = \pm K_{o}C_{o}R_{x}(1 - e^{-\frac{1}{\widehat{c}_{x}}}),$$

(3)

откуда имеем

$$1 - \left| \frac{U_{x_1}}{K_o C_o R_x} \right| = \sqrt[n]{\left(1 - \left| \frac{U_{x_2}}{K_o C_o R_x} \right|\right), (4)}$$

где n =  $t_2/t_1 > 1$  - любое действитель-45 ное положительное число.

При n = 2 решение уравнения (4) несложно при аппаратурной реализации. Величину сопротивления изоляции определяют из соотношения

$$R_{x} = \frac{U_{x_{*}}^{2}}{/K_{o}/\cdot C_{o}/2U_{x_{*}} - U_{x_{2}}/}.$$

(5)

Уравнение преобразования (5) инвариантно к выбору длительности цикла изменения. Методическая погрешность определяется только погрешностью установления отношения  $n = t_2/t_1 = 2$ .

Это поэволяет в широких пределах варьировать быстродействие измерения путем изменения частоты тестового генератора 1 без изменения схемы предлагаемого устройства.

Информационный сигнал  $U_x(t)$ , выделенный на полюсах контролируемой сети, поступает на оба входа развязывающего блока 5. При этом дифференциальная (относительно полюсов сети) составляющая сигнала, обусловленная изменениями рабочего напряжения сети  $U_{\rm POG}$ , взаимно компенсируется на выходе блока 5, а сумма синфазных информационных сигналов поступает на первый вход блока 7.

Процесс измерения синхронизируется программным блоком 6, на первом выходе которого имеется последовательность импульсов, поступающая на вход генератора I (фиг. 7) и переключающая полярность фронтов пилообраз~ ного напряжения ± E (t), а на седьмом, первом и третьем выходах блока 6 импульсы, фиксирующие моменты времени измерения мгновенных значений информационного сигнала U<sub>x</sub> (t;) начальный t<sub>o</sub> (фиг. 76), t<sub>1</sub> (фиг.7в) t<sub>2</sub>=2 t, (фиг. 7г), поступающие н на первый, второй и третий входы блока 7 соответственно. Три мгновенных значения напряжения U<sub>x</sub>(t<sub>i</sub>), где i=1,2,3, запоминаются на первом, втором и третьем выходах блока 7 на время периода измерения Т<sub>о</sub> (соответственно  $U_x(t_0)$ ,  $U_x(t_1) \rtimes U_x(t_2)$ ).

Измеренные мгновенные значения информационного сигнала поступают на 40 первый, второй и третий входы блока 13 коррекции, где за полный цикл измерения (два полупериода генератора 1) определяется модуль их алгебраической суммы. На выходах блока 13 45 имеются тогда напряжения:  $U_{x_0} = = [U_x(t_{0,i})/ + /U_x(t_{0,i+1})/ - на первом; U_{x_1} = /U_x(t_{1,i})/ + /U_x(t_{1,i+1})/ - на вто$  $ром; <math>U_{x_2} = /U_x(t_{2,i})/ + /U_x(t_{2,i+1})/$ на третьем.

Это позволяет за два полупериода работы устройства компенсировать на выходе блока однополярное напряжение ощибки измерения, обусловленное смещениями нулей реальных элементов схемы, а также инфранизкочастотной синфазной качкой рабочего напряжения сети (фиг. 7).

Блок 13 коррекции управляется последовательностью тактирующих ра- '

10

боту устройства импульсов с второго выхода программного блока 6 (фиг. 7а). Сигналы с первого, второго и третьего выходов блока 13 коррекции поступают на первый, второй и третий входы вычислителя 8.

7

Вычислитель 8 определяет величину контролируемого сопротивления изоляции R, на основании уравнения преобразования (5), используя в качестве аргументов измеренные перепады напряжений информационного сигнала U, U, и U, (фиг. 7л):

$$\begin{cases} U_{1} = |U_{x_{1}} - U_{x_{0}}| \\ U_{2} = |U_{x_{2}} - U_{x_{0}}| \end{cases}$$

(6) 15

Емкость контролируемой сети определяют на основании алгоритма, выведенного из (3) и 5):

$$C_{x} = - \frac{\frac{t_{i}}{R_{x}}}{\frac{U_{i}}{K_{o}/.C_{o}R_{x}}} - C_{o}.$$

(7)

Вычисленный в конце каждого цикла измерения параметр R<sub>x</sub> является аргументом уравнения преобразования (7). На управляемые четвертый, пятый и шестой входы вы~ числителя 8 поступают синхронизирующие его работу импульсы соответственно с первого (фиг. 7в), третьего (фиг. 7г) и пятого (фиг. 7д) выходов программного блока 6.

В конце каждого цикла измерения напряжение, пропорциональное сопротивлению изоляции R, на основании (5), с первого выхода вычислителя 8 через открытый ключ 9 поступает на 40 индикатор 11, а с второго выхода вычислителя 8 напряжение, пропорциональное емкости сети С<sub>х</sub> на основании (7), через открытый ключ 10 поступает на индикатор 12. Управление ключами 45 осуществляется с шестого (фиг. 7ж) и седьмого (фиг. 7з) выходов программного блока 6. На фиг. 7м, н приведены временные диаграммы установления показаний индикаторов 11 и 12 50 в процессе измерения.

Развязывающий блок 5 (фиг. 2) обеспечивает гальваническую развязку устройства от постоянного рабочего напряжения контррлируемой сети посредством разделительных конденсато- 55 ров 16 и 17. Кроме того, симметричное подключение устройства к обоим полюсам сети обеспечивает на выходе.

сумматора 18 компенсацию дифференциальной составляющей рабочего напряжения сети U<sub>раб</sub> и бросков напряжений полюсов сети в динамических режимах и в режимах включение-выключение рабочего напряжения. Синфазный (относительно полюсов сети) информационный сигнал U, (t) при этом усиливается в два раза.

Программный блок 6 (фиг. 3) работает следующим образом. Генератор 19 тактовых импульсов вырабатывает импульсную последовательность (фиг. 7а), синхронизующую работу генератора 1 и элементов 20-24 задержки блока 6. При этом на седьмом, первом и третьем выходах блока формируются одиночные импульсы в моменты t, t, 20 и t<sub>2</sub>=2.t, соответственно (фиг. 7б, в, г), стробирующие процесс фиксации мгновенных значений информационного сигнала U<sub>x</sub>(t) в блоке 7. На пятый и шестой выходы программного блока 6 управляющие импульсы поступают только в четные полупериоды работы устройства, что обеспечивается разрешающим сигналом с выхода триггера 25 (фиг. 7е) на элементы И 26 и 27.

30 Импульсы с пятого и шестого выходов блока 6 (фиг. 7ж, з) управляют ключами 9 и 10 соответственно и разрешают прохождение в конце каждого цикла измерения результатов вычисления

контролируемых параметров R<sub>x</sub> и C<sub>x</sub> 35 на выходные индикаторы устройства. Импульсы с четвертого выхода блока 6 синхронизируют работу вычислителя 8 и тактового генератора 19 (фиг.7д).

В блоке 7 (фиг. 4) осуществляется фиксация трех мгновенных значений апериодического информационного сигнала  $U_{x}(t_{0})$ ,  $U_{x}(t_{1})$  и  $U_{x}(t_{2}=2t_{1})$ через ключи 28-30 на входы элементов 31-32 аналоговой памяти соответственно.

Вычислитель 8 (фиг. 5) реализует уравнения преобразований (5) и (7). На первый, второй и третий входы блока 8 поступают напряжения, пропорциональные аргументам системы уравнений (6), а на четвертый, пятый и шестой входы - имульсы, синхронизирующие его работу. При этом на перя вом и втором выходах вычислителя 8 в конце каждого цикла измерения выделяются напряжения, пропорциональные текущим значениям контролируе-

25

мых сопротивления изоляции R<sub>x</sub> и емкости сети C<sub>x</sub> соответственно.

Вычислитель 8 работает следующим образом. Напряжения U, и U, являю-5 аргументами уравнения преобщиеся разования (5), определяются на выходах первого 34 и второго 35 дифференциальных усилителей. Напряжение, пропорциональное искомому сопротив-10 лению изоляции R<sub>x</sub>, имеется на выходе системы решающих блоков: квадратора 40, масштабного усилителя 38, третьего дифференциального усилителя 36 и третьего блока 44 деления, 15 реализующих алгоритмы преобразования (5).

Емкость сети С<sub>х</sub> определяется на втором выходе вычислителя 8 в виде пропорционального ей напряжения на основании алгоритма (7). При этом знаменатель уравнения преобразования (7) определяется на выходе системы решающих блоков: первого блока 41 деления, четвертого дифференциаль-25 ного усилителя 37 и логарифмирующего усилителя 45. Аргументами системы блоков являются напряжение U,, напряжение - результат вычисления эквивалентной изоляции R x сети с перво-30 го выхода блока 8 и опорное напряжение U c выхода источника 47. Значение числителя уравнения; (7) имеется на выходе интегратора 50, подключенного к источнику 47 опорно-35 го напряжения в течение интервала Тинт ≠t,-t₀.Это обеспечивается управляемым ключом 48 и триггером 42 с установочными входами, управляемым синхроимпульсами с первого и третье- 40 го выходов программного блока 6 (фиг. 76, в). Окончательно алгоритм преобразования (7) реализуется на выходе системы решающих блоков: четвертого 46 и второго 43 блоков де-45 ления и сумматора 39. В конце каждого полупериода измерения интегратор 50 сбрасывается в нулевое состояние посредством ключа 49, управляемого синхроимпульсом с четвертого выхода 50 программного блока 6 (фиг.7д). Это необходимо для подготовки интегратора 50 к новому полупериоду измерения.

Блок 13 коррекции (фиг.б) предназначен для компенсации напряжения ошибки U<sub>оы</sub> (фиг. 7и) измерения уровней информационного сигнала U<sub>x</sub>(t), вызванного процессом медлен-

55

но протекающего перераспределения рабочего напряжения сети между полюсами в динамических режимах коммутации потребителей с несимметричной изоляцией полюсов и дрейфом нулей реальных усилительных элементов схемы. Коррекция осуществляется за два полупериода работы схемы, причем в четные полупериоды открыты ключи 51-53 блока 13 и мгновенные значения информационного сигнала  $U_{x}(t_{0,1}^{\dagger})$ ,  $U_x(t_1^{i})$  и  $U_x(t_2^{i}=2,t_1^{i})$  запоминаются элементами 57-59 аналоговой памяти соответственно, а в нечетные значе-ния  $U_x(t_0^{i+1}), U_x(t_1^{i+1})$  и  $U_x(t_2^{i+2}-t_1^{i+1})$  через ключи 54-56 запоминаются элементами 60-62 аналоговой памяти. Управление ключами осуществляется с проти-20 вофазных выходов триггера 66 со счетным входом, переключающегося синхроимпульсами с второго выхода программного блока 6 (фиг. 7а). При этом запомненные информационные сигналы с выходов первой и второй группы элементов 57-59 и 60-62 аналоговой памяти поступают на дифференциальные входы соответствующих усилителей 63-65 в противофазе. Это обеспечивает удвоение уровня информационных сигналов в соответствующие моменты  $t_0$ ,  $t_4$ ,  $t_2=2 \cdot t_1$ , измеренные в четные и нечетные полупериоды работы устройства, а также компенсирует на выходах дифференциальных усилителей 63-65 синфазное напряжение ошибки U<sub>ощ</sub> (фиг. 7к).

Формула изобретения

1. Устройство для измерения сопротивления и емкости электрических и сигнальных сетей относительно земли, содержащее генератор импульсов, образцовый резистор, первый конденсатор, программный блок, блок фиксации уровней, первую клемму для подключения к объекту измерения, первый выход генератора импульсов соединен с первым выводом образцового резистора, второй вывод которого соединен с общей шиной, второй выход генератора импульсов соединен с первым выводом первого конденсатора, второй вывод которого соединен с первой клеммой для подключения к объекту измерения, первый выход программного блока соединен с первым входом блока фиксации уровней, второй выход программного

блока соединен с входом генератора импульсов, отличающееся тем, что, с целью повышения помехозащищенности передаваемого по контролируемой сети информационного сигнала от спектра контролируемого сигнала, в него введены второй конденсатор, развязывающий блок, блок коррекции, вычислитель, первый и второй 10 аналоговые ключи, первый и второй индикаторы и вторая клемма для подключения к объекту измерений, причем первый вывод второго конденсатора соединен с вторым выходом генера- 15 тора импульсов, а второй - с второй клеммой для подключения к объекту измерений, третий и четвертый выходы программного блока подключены соответственно к второму и третьему входам блока фиксации уровней, первый, второй и третий выходы которого подключены соответственно к первому, второму и третьему входам блока коррекции, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами вычислителя, четвертый, пятый и шестой входы которого подключены соответственно к первому, третьему и 30 пятому выходам программного блока, шестой и седьмой выходы которого соединены с коммутирующими входами соответственно первого и второго аналогового ключей, входы которых 35 соединены соответственно с первым и вторым выходами вычислителя, а выходы - с входами соответственно первого и второго индикаторов, четвертый вход блока коррекции соединен с третьим выходом программного блока, четвертый вход блока фиксации уровней соединен с выходом развертывающего блока, первый и второй входы которого соединены соответственно с первой и второй клеммой для подключе~ ния объекта измерения.

2. Устройство по п. 1, о т л и чающееся тем, что генератор импульсов выполнен в виде генератора двухполярного пилообразного напря. 50 жения, линейно изменяющегося во времени.

3. Устройство по п. 1, от ли чающееся тем, что развязыблок содержит два развязывающий вающих конденсатора и сумматор, причем первые выводы первого и второго развязывающих конденсаторов соединены соответственно с первым и вторым входами блока, а вторые - соответственно с первым и вторым входами сумматора, выход которого соединен с выходом блока.

4. Устройство по п. 1, о т л и чающееся тем, что программный блок содержит генератор тактовых импульсов, пять элементов задержки, триггер и два элемента И, причем, выход генератора тактовых импульсов соединен с входом каждого из элементов задержки и счетным входом триггера, инверсный выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с выходами соответственно четвертого и пятого элементов задержки, выходы

20 первого, второго и третьего элементов задержки соединены соответственно с седьмым, первым и третьим выходами блока, выходы первого и второго элементов И соединены соответственно 25 с пятым и шестым выходами блока, четвертый выход которого соединен с выходом пятого элемента задержки и входом генератора тактовых импульсов.

5. Устройство по п. 1, о т л и чающееся тем, что блок фиксации уровней содержит три аналоговых ключа и три аналоговых элемента памяти, причем информационные входы первого, второго и третьего аналоговых ключей соединены с четвертым входом блока, управляющие входы - соответственно с первым, вторым и тре-

тьим входами блока, а выходы - с входами соответственно первого, второго и третьего аналоговых элементов памяти, выходы которых соединены соответственно с первым, вторым и третьим выходами блока. 45

6. Устройство по п. 1, о т л и чающееся тем, что вычислитель содержит четыре дифференциальных усилителя, масштабный и логарифмический усилители, четыре блока деления, квадратор, сумматор, источник опорного напряжения, триггер, два интегратор, прианалоговых ключа и чем первый вход вычислителя соеди-55 нен с инвертирующими входами первого и второго дифференциальных усилителей, неинвертирующие входы которых соединены соответственно с вто-

- **4**0

рым и третьим входами вычислителя, выход первого дифференциального усилителя соединен с входами квадратора, масштабного усилителя и первым 5 входом первого блока деления, выход которого соединен с первым входом четвертого дифференциального усилителя, выход которого соединен с входом логарифмического усилителя, вы-10 ход источника опорного напряжения соединен с инвертирующим входом четвертого дифференциального усилителя, информационным входом первого аналогового ключа и первым входом сумматора, выход 15 которого соединен с вторым выходом вы-числителя, а вход - с выходом второго блока деления, первый вход которого соединен с выходом четвертого блока деления, а второй - с вторым вхо- 20 дом первого блока деления, первым выходом вычислителя и выходом третьего блока деления, первый вход которого соединен с выходом квадратора, а второй - с выходом третьего диф-25 ференциального усилителя, инвертирующий вход которого соединен с выходом второго дифференциального усилителя, а неинвертирующий - с выходом масштабного усилителя, четвер-30 тый и пятый входы вычислителя соединены с входами соответственно установки в "1" и установки в "0" триг~ гера, инверсный выход которого соединен с управляющим входом первого 35 аналогового ключа, выход которого соединен с входом интегратора и информационным входом второго аналогового ключа, управляющий вход которого соединен с шестым входом вычис-40 лителя, а выход - с выходом интегратора и первым входом четвертого блока деления, второй вход которого сое-

динен с выходом логарифмического усилителя.

7. Устройство по п. 1, о т л и чающееся тем, что блок коррекции содержит шесть аналоговых ключей, шесть аналоговых элементов памятн, три дифференциальных усилителя и триггер со счетным входом, причем информационные входы первого и четвертого аналоговых ключей соединены с первым входом блока, информационные входы второго и пятого аналоговых ключей соединены с вторым входом блока, информационные входы третьего и шестого аналоговых ключей соединены с третьим входом блока, выходы первого, второго, третьего, четвертого, пятого и шестого аналоговых ключей соединены с входами соответственно первого, второго, третьего, четвертого, пятого и шестого аналоговых элементов памяти, выходы первого, второго и третьего аналоговых элементов памяти соединены с инвертирующими входами соответственно первого, второго и третьего дифференциальных усилителей, выходы четвертого, пятого и шестого аналоговых элементов памяти соединены с неинвертирующими входами соответственно первого, второго и третьего дифференциальных усилителей, выходы которых соединены соответственно с первым, вторым и третьим выходами блока, четвертый вход которого соединен со счетным входом триггера, прямой выход которого соединен с управляющими входами первого, второго и третьего аналоговых ключей, а инверсный - с управляющими входами четвертого, пятого и шестого аналоговых ключей.

**Øuz**. 2

1

Фиг.3

.

Фиг. 4

φιε.δ

Фие.7

| Редактор А. Огар                            | Составитель А. Пржебел<br>Техред Л.Сердюкова | њский<br>Корректор А. Зимокосов |

|---------------------------------------------|----------------------------------------------|---------------------------------|

| Заказ 1237                                  | Тираж 772                                    | Подписное                       |

| ВНИИПИ Государственного комитета СССР       |                                              |                                 |

| по делам изобретений и открытий             |                                              |                                 |

| 113035, Москва, Ж-35, Раушская наб., д. 4/5 |                                              |                                 |

|                                             |                                              |                                 |

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4