# (19)대한민국특허청(KR) (12) 등록특허공보(B1)

(51) 。Int. Cl.

H01L 27/146 (2006.01)

H01L 31/10 (2006.01)

(45) 공고일자2007년07월23일(11) 등록번호10-0741875(24) 등록일자2007년07월16일

(21) 출원번호10-2004-0070840(22) 출원일자2004년09월06일심사청구일자2004년09월06일

(65) 공개번호10-2006-0022072(43) 공개일자2006년03월09일

(73) 특허권자 동부일렉트로닉스 주식회사 서울 강남구 대치동 891-10

(72) 발명자 황준

충청북도 청주시 상당구 율량동 삼정아파트 201-710

(74) 대리인강용복김용인

(56) 선행기술조사문헌 KR1020030056323 A KR1020040065335 A

KR1020030001795 A KR1020040075695 A

심사관: 김상걸

전체 청구항 수 : 총 10 항

#### (54) СМОЅ 이미지 센서 및 그의 제조 방법

#### (57) 요약

본 발명은 소자 격리막(STI; Shallow Trench Isolation) 계면과 포토다이오드 표면에서의 데미지를 방지하여 수광 특성을 향상시킨 CMOS 이미지 센서 및 그 제조 방법에 관한 것으로, 액티브 영역과 소자 분리 영역이 정의되는 p형 반도체 기판에 적어도 제 1, 제 2 패드막을 형성하는 단계와, 상기 소자 분리 영역의 상기 적어도 제 1, 제 2 패드막을 제거하고 놀출된 상기 반도체 기판을 선택적으로 제거하여 트렌치를 형성하는 단계와, 상기 트렌치 내벽의 상기 반도체 기판에 제 1 P형 불순물 영역을 형성하는 단계와, 상기 트렌치가 채워지도록 상기 기판 전면에 소자 분리용 절연막을 형성하는 단계와, 상기 트렌치 영역에만 남도록 상기 소자 분리용 절연막을 제거하고, 상기 제 2 패드막을 제거하는 단계와, 상기 액티브 영역에 n형 이온주입하여 포토 다이오드 영역을 형성하는 단계를 포함하여 이루어진 것이다.

#### 대표도

도 4d

#### 특허청구의 범위

#### 청구항 1.

삭제

### 청구항 2.

소자 분리 영역과 액티브 영역을 갖는 P-형 반도체 기판;

상기 소자 분리 영역의 상기 반도체 기판에 형성되는 트렌치;

상기 트렌치의 내벽에 형성되는 희생절연막 및 제1 P형 불순물 영역;

상기 트렌치내에 형성되는 소자 분리막;

상기 제 1 P형 불순물 영역에 인접한 상기 액티브 영역에 형성되는 n형 포토다이오드 영역;

상기 포토 다이오드 영역의 표면에 형성되는 제 2 P형 불순물 영역; 그리고

상기 포토 다이오드의 수직선 상에 형성되는 칼라 필터충 및 마이크로 렌즈를 포함하여 구성됨을 특징으로 하는 CMOS 이미지 센서.

### 청구항 3.

제 2 항에 있어서,

상기 소자 분리막은 High Density plasma 산화막으로 형성됨을 특징으로 하는 CMOS 이미지 센서.

#### 청구항 4.

액티브 영역과 소자 분리 영역이 정의되는 p형 반도체 기판에 적어도 제 1, 제 2 패드막을 형성하는 단계;

상기 소자 분리 영역의 상기 적어도 제 1, 제 2 패드막을 제거하고 놀출된 상기 반도체 기판을 선택적으로 제거하여 트렌치를 형성하는 단계;

상기 트렌치 내벽의 상기 반도체 기판에 제 1 P형 불순물 영역을 형성하는 단계;

상기 트렌치 내벽에 희생 절연막을 형성하는 단계와,

상기 희생절연막이 형성된 트렌치가 채워지도록 상기 기판 전면에 소자 분리용 절연막을 형성하는 단계;

상기 트렌치 영역에만 남도록 상기 소자 분리용 절연막을 제거하고, 상기 제 2 패드막을 제거하는 단계;

상기 액티브 영역에 n형 이온주입하여 포토 다이오드 영역을 형성하는 단계를 포함하여 이루어짐을 특징으로 하는 CMOS 이미지 센서의 제조 방법.

#### 청구항 5.

제 4 항에 있어서,

상기 제 1 패드막은 산화막이고, 상기 제 2 패드막은 질화막 또는 질화막과 TEOS 산화막이 적충된 것임을 특징으로 CMOS 이미지 센서의 제조 방법.

### 청구항 6.

삭제

## 청구항 7.

제4 항에 있어서,

상기 희생 절연막은 열산화 공정에 의해 형성함을 특징으로 하는 CMOS 이미지 센서의 제조 방법.

## 청구항 8.

제 4 항에 있어서,

상기 제 1 P형 불순물 영역을 형성하는 방법은, p형 불순물을 틸트 이온 주입 방법을 이용함을 특징으로 하는 CMOS 이미지 센서의 제조 방법.

#### 청구항 9.

제 4 항에 있어서,

상기 소자 분리용 절연막은 High Density plasma 산화막으로 형성함을 특징으로 하는 CMOS 이미지 센서의 제조 방법.

## 청구항 10.

제 4 항에 있어서,

상기 소자 분리용 절연막 및 제 2 패드막은 화학 기계적 연마(CMP) 공정으로 제거함을 특징으로 하는 CMOS 이미지 센서의 제조 방법.

## 청구항 11.

제 4 항에 있어서,

상기 포토 다이오드 영역의 표면에 제 1 P형 불순물 영역을 형성하는 단계를 더 포함함을 특징으로 하는 CMOS 이미지 센서의 제조 방법.

#### 청구항 12.

제 4 항에 있어서,

상기 반도체 기판상에 게이트 절연막 및 게이트 전극을 형성하는 단계와,

소오스/드레인 영역을 형성하는 단계와,

상기 포토다이오드 영역의 상측에 칼라 필터층과 마이크로 렌즈를 형성하는 단계를 더 포함함을 특징으로 하는 CMOS 이미지 센서의 제조 방법.

#### 명세서

## 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 CMOS 이미지 센서 및 그 제조방법에 관한 것으로서, 특히 소자 격리막(STI; Shallow Trench Isolation) 계면과 포토다이오드 표면에서의 데미지를 방지하여 수광 특성을 향상시킨 CMOS 이미지 센서 및 그 제조 방법에 관한 것이다.

일반적으로, 이미지 센서(Image sensor)는 광학적 영상(optical image)을 전기적 신호로 변환시키는 반도체 소자로써, 크게, 전하 결합 소자(charge coupled device: CCD)와 씨모스(CMOS; Complementary Metal Oxide Silicon) 이미지 센서 (Image Sensor)로 구분된다.

상기 전하 결합 소자(charge coupled device: CCD)는 빛의 신호를 전기적 신호로 변환하는 복수개의 포토 다이오드 (Photo diode; PD)가 매트릭스 형태로 배열되고, 상기 매트릭스 형태로 배열된 각 수직 방향의 포토 다이오드 사이에 형성되어 상기 각 포토 다이오드에서 생성된 전하를 수직방향으로 전송하는 복수개의 수직 방향 전하 전송 영역(Vertical charge coupled device; VCCD)과, 상기 각 수직 방향 전하 전송 영역에 의해 전송된 전하를 수평방향으로 전송하는 수평 방향 전하전송영역(Horizontal charge coupled device; HCCD) 및 상기 수평방향으로 전송된 전하를 센싱하여 전기적인 신호를 출력하는 센스 증폭기(Sense Amplifier)를 구비하여 구성된 것이다.

그러나, 이와 같은 CCD는 구동 방식이 복잡하고, 전력 소비가 클 뿐만아니라, 다단계의 포토 공정이 요구되므로 제조 공정이 복잡한 단점을 갖고 있다. 또한, 상기 전하 결합 소자는 제어회로, 신호처리회로, 아날로그/디지털 변환회로(A/D converter) 등을 전하 결합 소자 칩에 집적시키기가 어려워 제품의 소형화가 곤란한 단점을 갖는다.

최근에는 상기 전하 결합 소자의 단점을 극복하기 위한 차세대 이미지 센서로서 씨모스 이미지 센서가 주목을 받고 있다. 상기 씨모스 이미지 센서는 제어회로 및 신호처리회로 등을 주변회로로 사용하는 씨모스 기술을 이용하여 단위 화소의 수 량에 해당하는 모스 트랜지스터들을 반도체 기판에 형성함으로써 상기 모스 트랜지스터들에 의해 각 단위 화소의 출력을 순차적으로 검출하는 스위칭 방식을 채용한 소자이다. 즉, 상기 씨모스 이미지 센서는 단위 화소 내에 포토 다이오드와 모 스 트랜지스터를 형성시킴으로써 스위칭 방식으로 각 단위 화소의 전기적 신호를 순차적으로 검출하여 영상을 구현한다.

상기 씨모스 이미지 센서는 씨모스 제조 기술을 이용하므로 적은 전력 소모, 적은 포토공정 스텝에 따른 단순한 제조공정 등과 같은 장점을 갖는다. 또한, 상기 씨모스 이미지 센서는 제어회로, 신호처리회로, 아날로그/디지털 변환회로 등을 씨모스 이미지 센서 칩에 집적시킬 수가 있으므로 제품의 소형화가 용이하다는 장점을 갖고 있다. 따라서, 상기 씨모스 이미지 센서는 현재 디지털 정지 카메라(digital still camera), 디지털 비디오 카메라 등과 같은 다양한 응용 부분에 널리 사용되고 있다.

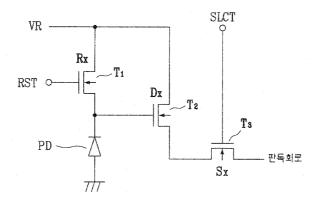

한편, CMOS 이미지 센서는 트랜지스터의 개수에 따라 3T형, 4T형, 5T형 등으로 구분된다. 3T형은 1개의 포토다이오드와 3개의트랜지스터로 구성되며, 4T형은 1개의 포토다이오드와 4개의 트랜지스터로 구성된다. 상기 3T형 CMOS 이미지 센서의 단위화소에 대한 등가회로 및 레이아웃(lay-out)을 살펴보면 다음과 같다.

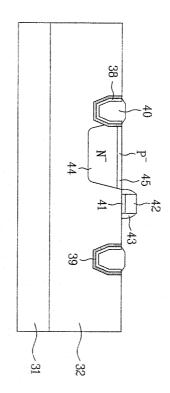

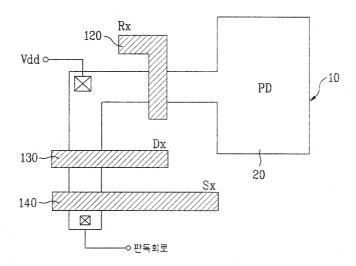

도 1은 일반적인 3T형 CMOS 이미지 센서의 등가 회로도이고, 도 2는 일반적인 3T형 CMOS 이미지 센서의 단위화소를 나타낸 레이아웃도이다.

일반적인 3T형 씨모스 이미지 센서의 단위 화소는, 도 1에 도시된 바와 같이, 1개의 포토다이오드(PD; Photo Diode)와 3개의 nMOS 트랜지스터(T1, T2, T3)로 구성된다. 상기 포토다이오드(PD)의 캐소드는 제 1 nMOS 트랜지스터(T1)의 드레인 및 제 2 nMOS 트랜지스터(T2)의 게이트에 접속되어 있다. 그리고, 상기 제 1, 제 2 nMOS 트랜지스터(T1, T2)의 소오스는 모두 기준 전압(VR)이 공급되는 전원선에 접속되어 있고, 제 1 nMOS 트랜지스터(T1)의 게이트는 리셋신호(RST)

가 공급되는 리셋선에 접속되어 있다. 또한, 제 3 nMOS 트랜지스터(T3)의 소오스는 상기 제 2 nMOS 트랜지스터의 드레인에 접속되고, 상기 제 3 nMOS 트랜지스터(T3)의 드레인은 신호선을 통하여 판독회로(도면에는 도시되지 않음)에 접속되고, 상기 제 3 nMOS 트랜지스터(T3)의 게이트는 선택 신호(SLCT)가 공급되는 열 선택선에 접속되어 있다. 따라서, 상기 제 1 nMOS 트랜지스터(T1)는 리셋 트랜지스터(Rx)로 칭하고, 제 2 nMOS 트랜지스터(T2)는 드라이브 트랜지스터(Dx), 제 3 nMOS 트랜지스터(T3)는 선택 트랜지스터(Sx)로 칭하다.

일반적인 3T형 CMOS 이미지 센서의 단위 화소는, 도 2에 도시한 바와 같이,액티브 영역(10)이 정의되어 액티브 영역(10)중 폭이 넓은 부분에 1개의 포토다이오드(20)가 형성되고, 상기 나머지 부분의 액티브 영역(10)에 각각 오버랩되는 3개의 트랜지스터의 게이트 전극(120, 130, 140)이 형성된다. 즉 상기 게이트 전극(120)에 의해 리셋 트랜지스터(Rx)가 형성되고, 상기 게이트 전극(130)에 의해 드라이브 트랜지스터(Dx)가 형성되며, 상기 게이트 전극(140)에 의해 선택 트랜지스터(Sx)가 형성된다. 여기서, 상기 각 트랜지스터의 액티브 영역(10)에는 각 게이트 전극(120, 130, 140) 하측부를 제외한 부분에 불순물 이온이 주입되어 각 트랜지스터의 소오스/드레인 영역이 형성된다. 따라서, 상기 리셋 트랜지스터(Rx)와 상기 드라이브 트랜지스터(Dx) 사이의 소오스/드레인 영역에는 전원전압(Vdd)이 인가되고, 상기 셀렉트 트랜지스터(Sx) 일측의 소오스/드레인 영역은 판독회로(도면에는 도시되지 않음)에 접속된다.

이와 같은 구성을 갖는 종래의 CMOS 이미지 센서의 제조 방법을 설명하면 다음과 같다.

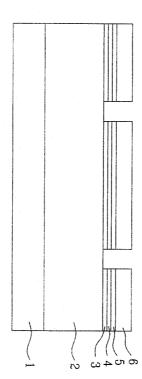

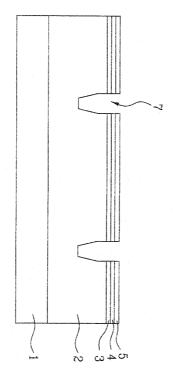

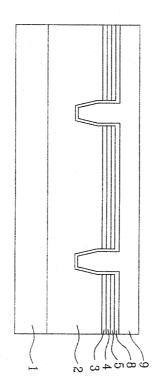

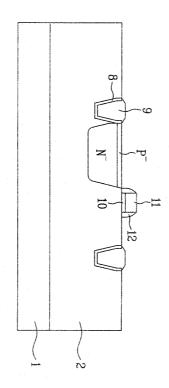

도 3a 내지 3f는 종래 기술에 따른 CMOS 이미지 센서의 공정 단면도로써, 도 2의 I-I' 선상의 단면도이다.

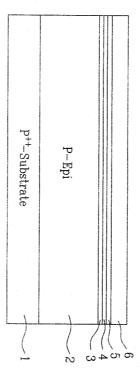

도 3a에 도시한 바와 같이, p형 반도체 기판(1)에 저농도 P형(P-) 에피층(p-type epitaxel layer)(2)을 형성하고, 상기 에 피층(2)위에 패드 산화막(pad oxide)(3), 패드 질화막(pad nitride)(4) 및 TEOS(Tetra Ethyl Ortho Silicate) 산화막(5)을 차례로 형성하고, 상기 TEOS 산화막(5)위에 감광막(6)을 형성한다.

도 3b에 도시한 바와 같이, 액티브 영역과 소자 분리 영역을 정의하는 마스크를 이용하여 노광하고 현상하여 상기 소자 분리 영역의 상기 감광막(6)을 제거한다. 그리고 상기와 같이 패터닝된 감광막(6)을 마스크로 이용하여 상기 소자 분리 영역의 패드 산화막(3), 패드 질화막(4) 및 TEOS 산화막(5)을 선택적으로 제거한다.

도 3c에 도시한 바와 같이, 상기 패터닝된 패드 산화막(3), 패드 질화막(4) 및 TEOS 산화막(5)을 마스크로 이용하여 상기소자 분리 영역의 상기 에피층(2)을 소정 깊이로 식각하여 트렌치(7)을 형성한다. 그리고, 상기 감광막(6)을 모두 제거한다.

도 3d에 도시한 바와 같이, 상기 트렌치(7)가 형성된 기판 전면에 희생 산화막(sacrifice oxide)(8)을 얇게 형성하고, 상기트렌치(7)가 채워지도록 상기 기판에  $O_3$  TEOS막(9)을 형성한다. 이 때 상기 희생 산화막(8)은 상기 트렌치의 내벽에도 형성되며, 상기  $O_3$  TEOS막(9)은 약 1000 이상의 온도에서 진행된다.

도 3e에 도시한 바와 같이, 화학 기계적 연마(CMP; Chemical Mechanical Polishing) 공정으로 상기 트렌치(7) 영역에만 남도록 상기 O<sub>3</sub> TEOS막(9)을 제거한다. 그리고, 상기 패드 산화막(3), 패드 질화막(4) 및 TEOS 산화막(5)을 제거한다.

그리고, 도면에는 도시되지 않았지만, 해당 영역의 상기 에피층(2)에 p형 웰 및 n형 웰을 형성한다.

도 3f에 도시한 바와 같이, 상기 기판 전면에 게이트 절연막 및 도전층을 차례로 형성하고 상기 게이트 절연막 및 도전층을 선택적으로 제거하여 게이트 전극(11) 및 게이트 절연막(10)을 형성한다. 그리고, 전면에 절연막을 증착하고 에치백(etch back)하여 상기 게이트 전극(11) 측면에 측벽 절연막(12)을 형성하고, 포토다이오드 영역에 p형 붉순물 이온 및 n형 불순물 이온을 주입하여 포토다이오드를 형성한다.

그 후, 도면에는 도시되지 않았지만, 상기 p형 웰 및 n형 웰내에 각각 반대 도전형의 불순물을 이온 주입하여 각각 트랜지스터의 소오스/드레인 영역을 형성하고, 상기 포토다이오드 상측에 해당 칼라 필터층과 마이크로 렌즈를 형성한다.

#### 발명이 이루고자 하는 기술적 과제

그러나, 상기와 같은 종래의 CMOS 이미지 센서 및 제조 방법에 있어서는 다음과 같은 문제점이 있었다.

첫째, 상기 소자 분리 영역에 트렌치를 형성할 때 소자 분리 영역 주변의 상기 에피층의 실리콘 격자 구조가 손상되어 포토 다이오드의 누설 전류가 발생하게 된다. 따라서, 포토다이오드의 수광 특성이 저하된다.

둘째, 상기 패드 산화막의 제거 공정 및 상기 희생 산화막 형성 공정 등으로 상기 포토다이오드 영역의 표면이 데미지를 받아 실리콘 댕글링 본드(dangling bond)에 의한 불필요한 인터페이스 트랩(interface trap)이 발생하므로 포토다이오드의 수광 특성이 저하되다.

본 발명은 상기와 같은 문제점을 해결하기 위한 것으로, 소자 분리 영역의 트렌치 내벽의 실리콘 격자 구조가 손상된 부분에 불순물 이온을 주입하여 포토다이오드화 됨을 방지하고 포토다이오드 영역의 표면을 보호하여 저조도 특성 등 수광 특성을 향상시킬 수 있는 CMOS 이미지 센서 및 그 제조 방법을 제공하는데 그 목적이 있다.

#### 발명의 구성

상기와 같은 목적을 달성하기 위한 본 발명에 따른 CMOS 이미지 센서는, 소자 분리 영역과 액티브 영역을 갖는 반도체 기판과, 상기 반도체 기판의 액티브 영역에 p형 불순물 영역이 감싸도록 형성되어 광의 조사에 따라 광 전하를 생성하는 포토 다이오드의 수직선 상에 형성되는 칼라 필터층 및 마이크로 렌즈를 포함하여 구성됨에 그 특징이 있다.

또한, 상기와 같은 목적을 달성하기 위한 본 발명에 따른 CMOS 이미지 센서는, 소자 분리 영역과 액티브 영역을 갖는 P-형 반도체 기판과, 상기 소자 분리 영역의 상기 반도체 기판에 형성되는 트렌치와, 상기 트렌치의 내벽에 형성되는 제 1 P형 불순물 영역과, 상기 트렌치내에 형성되는 소자 분리막과, 상기 제 1 P형 불순물 영역에 인접한 상기 액티브 영역에 형성되는 n형 포토다이오드 영역과, 상기 포토 다이오드 영역의 표면에 형성되는 제 2 P형 불순물 영역과, 상기 포토 다이오드의 수직선 상에 형성되는 칼라 필터층 및 마이크로 렌즈를 포함하여 구성됨에 또 다른 특징이 있다.

여기서, 상기 소자 분리막은 High Density plasma 산화막으로 형성됨에 특징이 있다.

또한, 상기와 같은 목적을 달성하기 위한 본 발명에 따른 CMOS 이미지 센서의 제조 방법은, 액티브 영역과 소자 분리 영역이 정의되는 p형 반도체 기판에 적어도 제 1, 제 2 패드막을 형성하는 단계와, 상기 소자 분리 영역의 상기 적어도 제 1, 제 2 패드막을 제거하고 놀출된 상기 반도체 기판을 선택적으로 제거하여 트렌치를 형성하는 단계와, 상기 트렌치 내벽의 상기 반도체 기판에 제 1 P형 불순물 영역을 형성하는 단계와, 상기 트렌치가 채워지도록 상기 기판 전면에 소자 분리용 절연막을 형성하는 단계와, 상기 트렌치 영역에만 남도록 상기 소자 분리용 절연막을 제거하고, 상기 제 2 패드막을 제거하는 단계와, 상기 액티브 영역에 n형 이온주입하여 포토 다이오드 영역을 형성하는 단계를 포함하여 이루어짐에 그 특징이 있다.

여기서, 상기 제 1 패드막은 산화막이고, 상기 제 2 패드막은 질화막 또는 질화막과 TEOS 산화막이 적충된 것임에 특징이 있다.

상기 트렌치 내벽의 상기 반도체 기판에 제 1 P형 불순물 영역을 형성하기 전에, 상기 트렌치 내벽에 희생 절연막을 형성하는 단계를 더 포함함에 특징이 있다.

상기 희생 절연막은 열산화 공정에 의해 형성함에 특징이 있다.

상기 제 1 P형 불순물 영역은 p형 불순물을 틸트 이온 주입하여 형성함에 특징이 있다.

상기 소자 분리용 절연막은 High Density plasma 산화막으로 형성함에 특징이 있다.

상기 소자 분리용 절연막 및 제 2 패드막은 화학 기계적 연마(CMP) 공정으로 제거함에 특징이 있다.

상기 포토 다이오드 영역의 표면에 제 1 P형 불순물 영역을 형성하는 단계를 더 포함함에 특징이 있다.

상기 반도체 기판상에 게이트 절연막 및 게이트 전극을 형성하는 단계와, 소오스/드레인 영역을 형성하는 단계와, 상기 포 토다이오드 영역의 상측에 칼라 필터층과 마이크로 렌즈를 형성하는 단계를 더 포함함에 특징이 있다. 상기와 같은 특징을 갖는 본 발명에 따른 CMOS 이미지 센서 및 그 제조 방법을 첨부된 도면을 참조하여 보다 상세히 설명하면 다음과 같다.

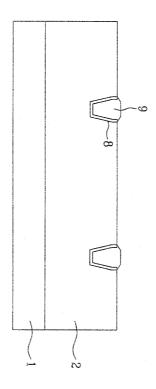

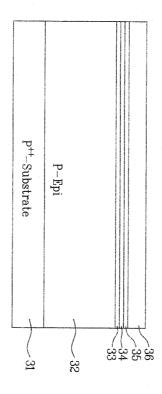

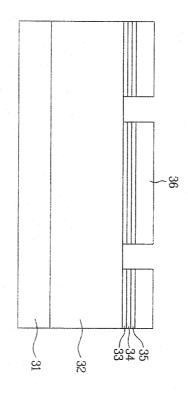

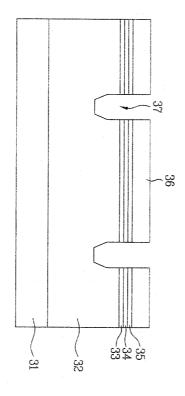

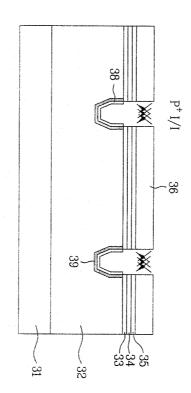

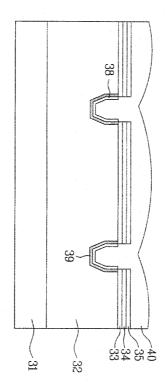

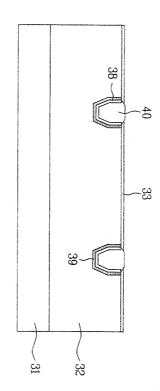

도 4a 내지 4g는 본 발명의 실시예에 따른 CMOS 이미지 센서의 공정 단면도이다.

도 4a에 도시한 바와 같이, p형 반도체 기판(31)에 저농도 P형(P¯) 에피층(p-type epitaxel layer)(32)을 형성하고, 상기에피층(32)위에 패드 산화막(pad oxide)(33), 패드 질화막(pad nitride)(34) 및 TEOS(Tetra Ethyl Ortho Silicate) 산화막(35)을 차례로 형성하고, 상기 TEOS 산화막(35)위에 감광막(36)을 형성한다.

도 4b에 도시한 바와 같이, 액티브 영역과 소자 분리 영역을 정의하는 마스크를 이용한 노광 및 현상 공정으로 상기 소자 분리 영역의 상기 감광막(36)을 제거한다. 그리고 상기와 같이 패터닝된 감광막(36)을 마스크로 이용하여 상기 소자 분리 영역의 패드 산화막(33), 패드 질화막(34) 및 TEOS 산화막(35)을 선택적으로 제거한다.

도 4c에 도시한 바와 같이, 상기 패터닝된 패드 산화막(33), 패드 질화막(34) 및 TEOS 산화막(35)을 마스크로 이용하여 상기 소자 분리 영역의 상기 에피층(32)을 소정 깊이로 식각하여 트렌치(37)를 형성한다.

도 4d에 도시한 바와 같이, 열산화 공정으로 상기 트렌치(37) 내벽에 희생 산화막(38)을 얇게 형성하고, 상기 트렌치(37) 내벽에 고농도 P형(P<sup>+</sup>) 불순물 이온을 주입하여 고농도 P형 불순물 영역(39)을 한다. 이 때, 상기 고농도 P형 불순물 이온 주입은 틸트 이온 주입 방법을 이용한다.

도 4e에 도시한 바와 같이, 상기 감광막(36)을 모두 제거하고, 상기 트렌치가 채워지도록 상기 기판 전면에 HDP(High Density plasma) 산화막(40)을 증착한다.

도 4f에 도시한 바와 같이, 화학 기계적 연마(CMP; Chemical Mechanical Polishing) 공정으로 상기 트렌치(37) 영역에만 남도록 상기 HDP 산화막(40)을 제거한다. 그리고, 상기 패드 질화막(34) 및 TEOS 산화막(35)을 제거한다. 그러나, 상기 패드 산화막(33)은 상기 에피층(32) 표면에 남아 있다. 이것은 후속 공정의 이온 주입 공정에서 버퍼 산화막으로서 이용하기 위합이다.

그리고, 도면에는 도시되지 않았지만, 해당 영역의 상기 에피층(32)에 p형 웰 및 n형 웰을 형성한다.

도 4g에 도시한 바와 같이, 상기 패드 산화막(33)을 제거하고 상기 기판 전면에 게이트 절연막 및 도전층을 차례로 형성하고 상기 게이트 절연막 및 도전층을 선택적으로 제거하여 게이트 전극(42) 및 게이트 절연막(41)을 형성하고, 포토다이오드 영역에 n형 불순물 이온을 주입하여 포토다이오드(44)를 형성한다. 물론 액티브 영역의 소오스/드레인 영역에 LDD를 형성한다.

그리고, 전면에 절연막을 증착하고 에치백(etch back)하여 상기 게이트 전극(42) 측면에 측벽 절연막(43)을 형성하고, 도면에는 도시되지 않았지만, 상기 p형 웰 및 n형 웰내에 각각 반대 도전형의 고농도 불순물을 이온 주입하여 각각 트랜지스터의 소오스/드레인 영역을 형성한다. 또한, 상기 포토다이오드(44) 표면에 p형( $P^0$ ) 불순물 이온주입하여  $P^0$ 형 불순물 영역(45)을 형성한다.

그 후, 통상적인 방법으로 상기 포토다이오드(44) 상측에 해당 칼라 필터층과 마이크로 렌즈를 각각 형성한다.

따라서, 본 발명에 따른 CMOS 이미지 센서의 포토 다이오드의 구조는, 도 4g에 도시한 바와 같이, 소자 분리 영역에 고농도 p+형 불순물 영역이 형성되고, 상기 포토다이오드 표면에  $p^0$ 불순물 영역이 형성되며 하부면은 p-형 에피층이 형성되므로 포토 다이오드가 p형 불순물 영역으로 감싸여지는 구조를 갖는다.

#### 발명의 효과

이상에서 설명한 바와 같은 본 발명에 따른 CMOS 이미지 센서의 제조방법에 있어서는 다음과 같은 효과가 있다.

첫째, 상기 소자 분리 영역에 트렌치를 형성하고 상기 트렌치 내벽에 p형 불순물 이온을 주입하여 상기 트렌치 주변의 p-형 에피층에 p+ 불순물 영역을 형성하므로, 트렌치 형성 시 p-형 에피층의 실리콘 격자 구조가 손상되더라도 상기 포토다이오드의 누설 전류가 발생되지 않는다. 따라서, 포토다이오드의 수광 특성이 향상된다.

둘째, 상기 소자 격리막을 형성하기 위한 CMP 공정 후 상기 패드 산화막이 상기 포토다이오드의 표면에 남아 있으므로 별도의 희생 산화막을 형성할 필요가 없고 P형 웰 및 n형 웰 형성 등의 공정에서 상기 패드 산화막이 상기 포토다이오드의 표면이 손상됨을 방지하므로 포토다이오드의 수광 특성이 향상된다. 특히 저조도 수광 특성이 향상된다.

#### 도면의 간단한 설명

도 1은 일반적인 씨모스 이미지 센서의 1 화소의 등가회로도

도 2는 일반적인 씨모스 이미지 센서되 1 화소의 레이아웃도

도 3a 내지 3f는 종래 기술에 따른 CMOS 이미지 센서의 공정 단면도

도 4a 내지 4g는 본 발명의 실시예에 따른 CMOS 이미지 센서의 공정 단면도

도면의 주요 부분에 대한 설명

31: 반도체 기판 32: P형 에피층

33 : 패드 산화막 34 : 패드 질화막

35: TEOS 산화막 36: 감광막

37 : 트렌치 38 : 희생 산화막

39 : 고농도 P 형 불순물 영역 40 : HDP 산화막

41: 게이트 절연막 42: 게이트 전극

43 : 측벽 절연막 44 : 포토다이오드

45 : p<sup>0</sup>형 불순물 영역

## 도면

## 도면1

도면2

도면3a

도면3b

도면3c

도면3d

## 도면3e

도면3f

도면4a

도면4b

도면4c

도면4d

도면4e

도면4f

# 도면4g