#### (19) 日本国特許庁(JP)

# 再 公 表 特 許(A1)

(11) 国際公開番号

W02011/039835

発行日 平成25年2月21日 (2013.2.21)

#### (43) 国際公開日 平成23年4月7日(2011.4.7)

| (51) Int.Cl. |              |           | F I  |      |   | テーマコード (参考) |

|--------------|--------------|-----------|------|------|---|-------------|

| нозк         | <i>5/2</i> 6 | (2006.01) | нозк | 5/26 | G | 5 J O 3 9   |

| HO3L         | 7/085        | (2006.01) | HO3L | 7/08 | A | 5J106       |

| H03L         | 7/08         | (2006.01) | HO3L | 7/08 | M |             |

#### 審查請求 有 予備審查請求 未請求 (全 24 頁)

特願2011-533975 (P2011-533975) 出願番号 (21) 国際出願番号 PCT/JP2009/066936 平成21年9月29日 (2009.9.29) (22) 国際出願日 (81) 指定国 AP (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), EA (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), EP (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, F1, FR, GB, GR, HR, HU , IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, S K, SM, TR), OA (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE , SN, TD, TG) , AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC , EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, I S. JP. KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE , PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, S Y, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW

(71) 出願人 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74)代理人 100080001

弁理士 筒井 大和

福田 幸二 (72) 発明者

> 東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

(72) 発明者 山下 寛樹

> 東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

Fターム(参考) 5J039 JJ07 JJ13 KK09 KK10 KK11 KK13 KK16 KK27 MM03 MM04

NN01

5J106 BB01 CC21 CC59 DD39 DD47

GG04 HH02 DD48 KK40

## (54) 【発明の名称】データ判定/位相比較回路

## (57)【要約】

クロック生成回路およびそれを備えた信号再生回路に 関し、特に、単相のクロックでデータ判定と位相比較の 両方を行うことが可能なデータ判定 / 位相比較回路、お よびそれを備えた CDR (Clock Data Recovery)回路 を提供する。正しくデータ判定をするのに必要なデータ 確定期間(セットアップ/ホールド時間)の異なる2つ のデータ判定器 G\_GOOD、G\_BADに同一のデー タおよびクロックを入力し、必要なデータ確定期間が短 い方のデータ判定器 G G O D D の出力をデータ判定 / 位相比較回路のデータ出力とし、両データ判定器の出力 が異なる場合にはクロック位相が早すぎることを示す信 号Early、または、クロック位相が遅すぎることを 示す信号Lateを出力する。前後のシンボルとあわせ た合計3シンボルのデータ出力の関係によって、Ear 1yおよびLateのどちらを出力するかを決定論理E L\_LOGICにて選択する。

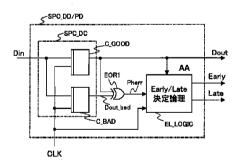

## 図5A

FIG SA: AA Early/Late Decision Logic

#### 【特許請求の範囲】

#### 【請求項1】

データ入力と、単一のクロック信号のみを入力されて、データ判定および位相比較が可能な、データ判定 / 位相比較回路であって、

前記データ入力を、前記クロック信号に同期してデータ判定する第1のデータ判定回路と、

前記データ入力を、前記クロック信号に同期してデータ判定する第2のデータ判定回路と、

前記第1のデータ判定回路の出力と、前記第2のデータ判定回路の出力と、を入力されて、クロック位相が早すぎることを示す位相比較出力Early、あるいは、クロック位相が遅すぎることを示す位相比較結果Lateを出力する位相比較論理回路と、を備え、

前記第2のデータ判定回路は、正しくデータ判定するのに必要なデータ入力の確定期間 (必要セットアップ時間と必要ホールド時間の和)が、前記第1のデータ判定回路が、正 しくデータ判定するのに必要なデータ入力の確定期間(必要セットアップ時間と必要ホー ルド時間の和)よりも長く、

前記第1のデータ判定回路の出力結果、あるいは該出力結果を遅延させたものを、データ判定/位相比較回路全体のデータ判定結果として出力し、

前記位相比較論理回路は、前記第1のデータ判定回路の出力と、前記第2のデータ判定回路の出力と、が異なる場合にのみ、位相比較出力Early、あるいは、Lateを出力する可能性がある論理回路であることを特徴とするデータ判定/位相比較回路。

#### 【請求項2】

請求項1記載のデータ判定/位相比較回路において、

前記位相比較論理回路は、

前記第1のデータ判定回路の出力と、前記第2のデータ判定回路の出力と、が入力される2入力排他的論理和回路と、前記2入力排他的論理和回路の出力を一方の入力とする2つの2入力論理積の出力が、それぞれ、位相比較出力Early、あるいは、Lateとなっていることを特徴とするデータ判定/位相比較回路。

#### 【請求項3】

請求項1記載のデータ判定/位相比較回路において、

前記位相比較論理回路は、

前記第1のデータ判定回路の出力と、前記第2のデータ判定回路の出力と、が異なる場合、前記異なる出力のシンボルを注目シンボルとして、前記第1のデータ判定回路の前記注目シンボルと前後のシンボル分の出力、および、前記第2のデータ判定回路の前記注目シンボルと前後のシンボルとを合わせた3シンボル分の出力、の、合計6シンボルの出力の組み合わせによって、位相比較出力EarlyとLateを定めることを特徴とするデータ判定/位相比較回路。

## 【請求項4】

請求項3記載のデータ判定/位相比較回路において、

前記位相比較論理回路は、

前記第1のデータ判定回路の出力と、前記第2のデータ判定回路の出力と、が異なり、かつ、前記第1のデータ判定回路の現在の出力と、前記第1のデータ判定回路の1シンボル前の出力とが異なる場合に、位相比較出力Earlyを出力し、

前記第1のデータ判定回路の出力と、前記第2のデータ判定回路の出力と、が異なり、かつ、前記第1のデータ判定回路の現在の出力と、前記第1のデータ判定回路の1シンボル後の出力とが異なる場合に、位相比較出力Lateを出力することを特徴とするデータ判定/位相比較回路。

#### 【請求項5】

請求項3記載のデータ判定/位相比較回路において、

前記位相比較論理回路は、

現在のシンボルにおいて前記第1のデータ判定回路の出力と、前記第2のデータ判定回

10

20

30

40

路の出力とが異なり、かつ、1シンボル前および1シンボル後では、前記第1のデータ判定回路の現在の出力と、前記第1のデータ判定回路の1シンボル前の出力とが同一であり、かつ、前記第1のデータ判定回路の現在の出力と、前記第1のデータ判定回路の1シンボル前の出力とが異なる場合に、位相比較出力 Earlyを出力し、

現在のシンボルにおいて前記第1のデータ判定回路の出力と、前記第2のデータ判定回路の出力とが異なり、かつ、1シンボル前および1シンボル後では、前記第1のデータ判定回路の現在の出力と、前記第1のデータ判定回路の1シンボル前の出力とが同一であり、かつ、前記第1のデータ判定回路の現在の出力と、前記第1のデータ判定回路の1シンボル後の出力とが異なる場合に、位相比較出力Lateを出力することを特徴とするデータ判定/位相比較回路。

【請求項6】

請 求 項 1 ~ 5 の い ず れ か 1 項 に 記 載 の デ ー 夕 判 定 / 位 相 比 較 回 路 に お い て 、

前記第1のデータ判定回路が正しくデータ判定するのに必要な必要セットアップ時間と必要ホールド時間の比率、あるいは、前記第2のデータ判定回路が正しくデータ判定するのに必要な必要セットアップ時間と必要ホールド時間の比率、の一方または両方を調整する手段を有していることを特徴とするデータ判定/位相比較回路。

【請求項7】

請 求 項 1 ~ 6 の い ず れ か 1 項 に 記 載 の デ ー 夕 判 定 / 位 相 比 較 回 路 に お い て 、

前記第2のデータ判定回路が、正しくデータ判定するのに必要なデータ入力の確定期間 (正しくデータ判定するのに必要な必要セットアップ時間と必要ホールド時間の和)を調整する手段を有していることを特徴とするデータ判定/位相比較回路。

【請求項8】

請求項7記載のデータ判定/位相比較回路において、

前記第2のデータ判定回路の正しくデータ判定するのに必要なデータ入力の確定期間(正しくデータ判定するのに必要な必要セットアップ時間と必要ホールド時間の和)を調整する手段が、前記第2のデータ判定回路の内部のノードに外部からオフセットを加えること、であることを特徴とするデータ判定/位相比較回路。

【請求項9】

請求項1~5のいずれか1項に記載のデータ判定/位相比較回路において、

前記第1のデータ判定回路と、前記第2のデータ判定回路は、マスター/スレーブ構成の回路であり、かつ、マスター側の回路は、前記第1のデータ判定回路と前記第2のデータ判定回路とで共有しており、スレーブ側の回路のみが異なることを特徴とするデータ判定/位相比較回路。

【請求項10】

請求項9記載のデータ判定/位相比較回路において、

前記第2のデータ判定回路のスレーブ側の回路が、正しくデータ判定するのに必要なデータ入力の確定期間(正しくデータ判定するのに必要な必要セットアップ時間と必要ホールド時間の和)を調整する手段を有していることを特徴とするデータ判定/位相比較回路

【請求項11】

請求項10記載のデータ判定/位相比較回路において、

前記第2のデータ判定回路のスレーブ側の回路の正しくデータ判定するのに必要なデータ入力の確定期間(正しくデータ判定するのに必要な必要セットアップ時間と必要ホールド時間の和)を調整する手段が、前記第2のデータ判定回路のスレーブ側の回路の内部のノードに外部からオフセットを加えること、であることを特徴とするデータ判定/位相比較回路。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、クロック生成回路およびそれを備えた信号再生回路に関し、特に、単相のク

10

20

30

40

ロックでデータ判定と位相比較の両方を行うことが可能なデータ判定 / 位相比較回路、およびそれを備えた C D R (Clock Data Recovery) 回路に関するものである。

## 【背景技術】

#### [0002]

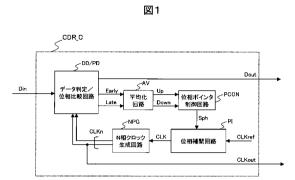

図1は、本発明の前提として検討した信号再生回路を示すものである。図1に示す信号再生回路CDR\_Cは、特許文献1と同様の構成例となっている。信号再生回路CDR\_Cは、データ判定/位相比較回路DD/PD、平均化回路AV、位相ポインタ制御回路PCON、位相補間回路PI、および、N相クロック生成回路NPG、によって構成される

### [0003]

データ判定/位相比較回路DD/PDは、n相クロックCLKnのうちデータ取得用のクロック相に同期して、データ入力Dinを判定し、判定結果をデータ出力Doutに出力する。同時に、データ判定/位相比較回路DD/PDは、n相クロックCLKnの複数のクロック相を利用することで、データ入力Dinとn相クロックCLKnの位相を比較し、n相クロックCLKnの位相がデータ入力Dinよりも早い場合にはLate信号、を出力する。

#### [0004]

平均化回路 A V は、データ判定 / 位相比較回路 D D / P D が出力した位相比較の結果、すなわち E a r 1 y および L a t e 信号を、ある一定期間積算することで、n 相クロック C L K n とデータ入力 D i n の位相の平均的なずれを算出する。その結果、n 相クロック C L K n の位相がデータ入力 D i n の位相よりも平均的に遅い場合には U p 信号、n 相クロック C L K n の位相がデータ入力 D i n の位相よりも平均的に早い場合には D o w n 信号、を出力する。平均化回路 A V による処理は実質的にロウパスフィルタをかけていることと等価であり、平均化回路 A V の代わりにアナログロウパスフィルタを用いる場合もある。

### [0005]

位相ポインタ制御回路PCONは、上記Up信号およびDown信号に基づいて、位相補間回路PIの出力位相を制御する位相制御信号Sphを出力する。平均化回路AVがUp信号を出力した場合には位相補間回路の出力クロックの位相を早めるように、逆に平均化回路AVがDown信号を出力した場合には位相補間回路の出力クロックの位相を遅らせるように制御する。

#### [0006]

位相補間回路 P I は、典型的には、位相制御信号 S p h に基づいて、外部から入力されたリファレンスクロック C L K r e f の位相を変化させることで動作する。しかしながら、位相補間回路 P I の本質的な機能は、位相制御信号 S p h に基づいて出力するクロック C L K の位相を変化させることであり、例えば、リファレンスクロックを用いずに、位相制御信号 S p h に基づいて出力位相を変化させることが可能な源発振器を位相補間回路 P I に内蔵する、という方法も考えられる。

#### [0007]

N相クロック生成回路NPGは、位相補間回路PIが出力した単相のクロックCLKから、データ判定/位相比較回路DD/PDで必要とするn相のクロックを生成する回路である。このとき、n相クロックのうち特定のクロック相を、再生クロックCLKoutとして信号再生回路CDR\_Cの外部に出力する。

#### [0008]

図 1 の信号再生回路 C D R \_ C によれば、 n 相クロック C L K n のうちデータ取得用のクロックが、常にデータ入力 D i n の位相に追随し、正しいデータ判定が可能である。

#### [0009]

図2Aおよび図2Bは、それぞれ本発明の前提として検討したデータ判定/位相比較回路DD/PDの構成例を示すものである。ただし、これらの図は回路全体のうち本質的な

10

20

30

40

部分のみを描いたものであり、各信号間のリタイミング用の回路等は省かれている。

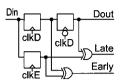

[0010]

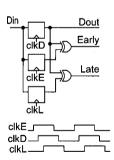

図2Aは非特許文献1で開示されたアレキサンダー方式のデータ判定/位相比較回路DD/PDの構成を示すものである。図2Aに示したデータ判定/位相比較回路DD/PDは、データ入力Dinと、互いに1シンボル周期の半分の時間だけずれた2相のクロックclkDおよびclkEを入力されて、データ出力Dout、および、位相比較信号EarlyとLateを出力する。このとき、2相クロックのうち、clkDに同期してデータ入力Dinを判定した結果をDoutとして出力する。

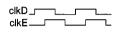

[0011]

図2Bは特許文献1で開示されたアイトラッキング方式のデータ判定/位相比較回路DD/PDの構成を示すものである。図2Bに示したデータ判定/位相比較回路DD/PDは、データ入力Dinと、典型的には互いに1シンボル周期の1/4の時間だけずれた3相のクロックclkD、clkE、およびclkLを入力されて、データ出力Dout、および、位相比較信号EarlyとLateを出力する。このとき、3相クロックのうち、clkDに同期してデータ入力Dinを判定した結果をDoutとして出力する。

【先行技術文献】

【特許文献】

[0012]

【特許文献1】特開2004-180188号公報

【非特許文献】

[ 0 0 1 3 ]

【非特許文献 1】J. D. H. Alexander、"Clock Recovery from Random Binary Data"、Electronics Letters, Vol. 11、1975年10月、p.541-542

【発明の概要】

【発明が解決しようとする課題】

[0014]

図2Aおよび図2Bに示したデータ判定/位相比較回路DD/PDは、データ出力Doutのために必要なクロックclkDに加えて、位相比較信号EarlyおよびLateを出力するためにclkDとは位相が異なるクロックを必要とする。このため、データ判定/位相比較回路DD/PDの動作のために、単相のクロックではなく、2相もしくは3相のクロックCLKnを必要とする。このため、図1に示す信号再生回路CDR\_Cでは、位相補間回路PIが出力した単相のクロックCLKから、N相クロック生成回路NPGによって2相もしくは3相のクロックCLKnを生成している。

[0015]

ところが、一般に、クロック相を増やすことは回路規模および消費電力の増大に直結する。とくに、データ判定 / 位相比較回路 D D / P D は、高速なデータ入力 D i n のデータ判定および位相比較をするために、高い周波数のクロックを必要とする。このため、多相クロックの生成および分配するために必要な、回路の規模および消費電力は大きなものとなる。さらに、近年、伝送速度を向上させるために、データ入力 D i n およびクロックの周波数がさらに高まってきており、多相クロックの生成および分配に用いる回路および消費電力が、信号再生回路全体の回路規模および消費電力のうちかなりの部分を占めるようになった。

[0016]

本発明は、このようなことを鑑みてなされたものであり、その目的の一つは、多相クロックを用いることなく、単相のクロックのみで、データの判定と位相比較の両方が可能なデータ判定 / 位相比較回路を提供することにある。本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

[0017]

本願において開示される発明のうち、代表的な実施の形態の概要を簡単に説明すれば、

10

20

30

40

次のとおりである。

#### [0018]

本実施の形態によるデータ判定 / 位相比較回路は、単一のクロックCLKに同期して動作する2つのデータ判定回路と、その後段に接続されたフリップフロップおよび論理積および排他的論理和からなる論理回路と、を備えた構成となっている。単一のクロックCLKに同期して動作する2つのデータ判定回路は、正しいデータ判定をするのに必要なデータ確定期間(必要セットアップ時間、および必要ホールド時間)が異なっている。

#### [0019]

データ判定 / 位相比較回路のデータ出力 D o u t は、正しいデータ判定をするのに必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が短いほうのデータ判定回路の出力に接続されている。信号再生回路がロック状態にある限り、データ出力 D o u t は、ほぼ正しいデータを出力していると考えられる。

#### [0020]

位相比較信号 Early および Lateの出力は以下のように行う。もし、正しいデータ判定に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が異なる2つのデータ判定回路が同じ判定結果を出力した場合には、Early、Lateともに出力しない。この場合には、必要なデータ確定期間が長いデータ判定回路も正しくデータを判定していることから、データ入力 Dinはクロック CLK に対して十分な確定時間があると考えられる。

## [ 0 0 2 1 ]

一方、もし、2つのデータ判定回路が異なる判定結果を出力した場合には、入力データDinのCLKに対するデータ確定期間が、必要なデータ確定期間が長い方のデータ判定回路が必要とするデータ確定期間よりも短くなって、必要なデータ確定期間が長い方のデータ判定回路が誤判定をした、つまり、データ入力DinのエッジがCLKに近づいている、と考えられる。この場合、そのシンボル(注目シンボル)の1シンボル前のデータおよび1シンボル後のデータを考えることで、クロックの位相が早すぎる(Early)のか、遅すぎるのか(Late)を判断することができる。

#### [0022]

具体的には、必要なデータ確定期間が短いほうのデータ判定結果が、注目シンボルと1つ前のシンボルとが同じ場合にはLateと判断し、注目シンボルと1つ後のシンボルとが同じ場合にはEarlyと判断する。この、クロックの位相が早すぎる(Early)のか、それとも遅すぎる(Late)のかを判断する手順については、実施の形態の説明にて更に詳細に記述する。

### [ 0 0 2 3 ]

このような構成を用いると、データ入力 Dinと単一(単相)のクロック CLKのみを入力されて、データ判定出力 Doutのみならず、位相比較出力 Early および Lateをも出力することが可能となる。このため、前述したような多相クロックを用いる場合に比べて回路規模および消費電力を削減することが可能となる。

## 【発明の効果】

#### [0024]

本願において開示される発明のうち、代表的な実施の形態によって得られる効果を簡単に説明すると、データ判定 / 位相比較回路が単相のクロックのみで動作可能となり、多相クロック信号の生成・分配に必要な回路規模および消費電力を削減できる。

## 【図面の簡単な説明】

#### [ 0 0 2 5 ]

【図1】本発明の前提として検討した信号再生回路を示す図である。

【図2A】本発明の前提として検討した非特許文献1で開示されたデータ判定/位相比較回路を示す図である。

【図2B】本発明の前提として検討した特許文献1で開示されたデータ判定/位相比較回路を示す図である。

10

20

30

40

- 【 図 3 】 本 発 明 の 実 施 の 形 態 1 の 光 通 信 シ ス テ ム の 構 成 例 を 示 す ブ ロ ッ ク 図 で あ る 。

- 【図4】上記実施の形態1の単相クロック位相比較回路を示す図である。

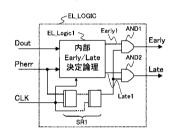

- 【図 5 A 】図 4 における単相クロックデータ判定 / 位相比較回路の詳細な構成を示すブロック図である。

- 【図 5 B 】図 5 A における E a r l y / L a t e 決定論理 E L \_\_ L O G I C の詳細な構成例を示す図である。

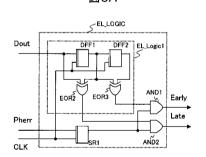

- 【図6A】図5Bにおいて内部Early/Late決定論理EL\_Logic1の部分を更に詳細化したEarly/Late決定論理EL\_LOGICの構成例を示す図である。

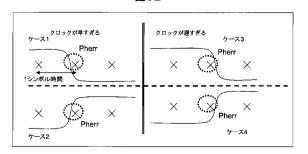

- 【図6B】図6AのEarly/Late決定論理EL\_LOGICの動作原理を示す波形図である。

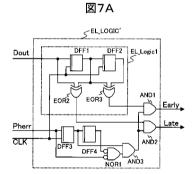

- 【図7A】本発明の実施の形態2の単相クロック位相比較回路に採用するEarly/Late決定論理EL\_LOGIC'の回路図である。

- 【図7B】図7AのEarly/Late決定論理EL\_LOGIC'の原理を説明する 波形図である。

- 【図8A】本発明の実施の形態3の単相クロック位相比較回路に採用する単相クロックデュアルデータ判定器SPC\_DC′(図5AのSPD\_CDの代替)を示す回路図である

- 【 図 8 B 】 図 8 A の 単相 クロックデュアルデータ判定器 S P C \_\_ D C 'の原理を説明する 概念図である。

- 【図9A】図8Aのデータ判定器C BADの一構成例のブロック図である。

- 【図9B】図8Aのデータ判定器C BADの別の構成例のブロック図である。

- 【図10】図9Bのデータ判定器C\_BADの詳細な構成を示す回路図である。

- 【図 1 1 】本発明の実施の形態 4 におけるデータ判定器 C \_\_ B A D '(図 9 B のデータ判定器 C \_\_ B A D の代替)を示す回路図である。

- 【発明を実施するための形態】

- [0026]

以下に記述する各実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

[0027]

さらに、各実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

[ 0 0 2 8 ]

また、実施の形態の各機能プロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOSトランジスタ)等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。なお、実施の形態では、MISFET(Metal Insula tor Semiconductor Field Effect Transistor)の一例としてMOS(Metal Oxide Semiconductor)トランジスタを用いる。図面において、Pチャネル型MOSトランジスタ(PMOSトランジスタ)にはゲートに丸印の記号を付すことで、Nチャネル型MOSトランジスタの基スタ(NMOSトランジスタ)と区別することとする。図面にはMOSトランジスタの基

10

20

30

40

20

30

40

50

板電位の接続は特に明記していないが、MOSトランジスタが正常動作可能な範囲であれば、その接続方法は特に限定しない。

### [0029]

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

#### [0030]

(実施の形態1)

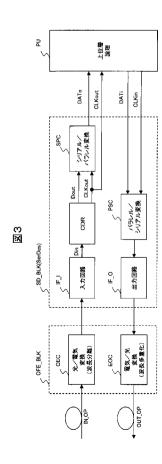

図3は、本発明の実施の形態1による信号再生回路において、それを含めた光通信システムの構成例を示すブロック図である。図3に示す光通信システムは、光・電気変換ブロックOFE\_BLKと、シリアル・パラレル変換ブロック(SerDes:SERializer/DESerializer)SD\_BLKと、上位層論理ブロックPUによって構成される。OFE\_BLKは、例えばフォトダイオード等を介して光入力データ信号IN\_OPを電気信号に変換する光/電気変換回路OECと、半導体レーザ等を介して電気信号を光出力データ信号OUT\_OPに変換する電気/光変換回路EOCを備えている。

## [0031]

SD\_BLKは、入力系回路として、OECからの微小なデータ信号を所定電圧レベルのデータ信号に増幅する入力回路IF\_Iと、その出力となるデータ信号Dinからデータ信号Doutおよびクロック信号CLKoutを再生する信号再生回路CDRと、CLKoutを用いてシリアルデータとなるDoutをパラレルデータ信号DAToに変換するシリアル / パラレル変換回路SPCを備えている。上位層論理ブロックPUは、このCLKoutとDAToを受けて所定の情報処理を行う。また、SD\_BLKは、出力系回路として、PUからのパラレルデータ信号DATiをPUからのクロック信号CLKinを用いてシリアルデータ信号に変換するパラレル / シリアル変換回路PSCと、そのシリアルデータ信号に基づいた所定の電気信号によって電気 / 光変換回路EOCを駆動する出力回路IF Oを備えている。

### [0032]

このような光通信システムでは、数十Gbpsを超える通信が行われるため、信号再生回路CDRにおけるクロック信号の周波数が非常に高くなる。このため、前述したように、図2Aおよび図2Bに示した多相クロックを用いてデータ判定および位相比較を行う方式では、多相クロックの生成・分配に必要な回路規模および消費電力が信号再生回路CDR全体の回路規模および消費電力のうちの大きな部分を占めることになる。そこで、後述するように、単相のクロックで動作可能な本実施の形態によるデータ判定/位相比較回路を用いることで、回路規模および消費電力を削減することが可能となる。

## [ 0 0 3 3 ]

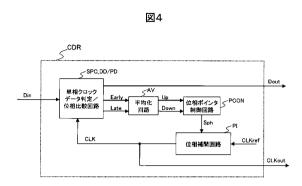

図4は、図3の光通信システムにおいて、その信号再生回路CDRの構成例を示すブロック図である。図4に示す信号再生回路CDRは、単相クロックデータ判定/位相比較回路SPC\_DD/PD、平均化回路AV、位相ポインタ制御回路PCON、および、位相補間回路PI、によって構成される。図4に示した信号再生回路CDRは、図1に示した信号再生回路CDR\_Cと比べて、N相クロック生成回路NPGがなくなっていることが特徴となっている。すなわち、単相クロックデータ判定/位相比較回路SPC\_DD/PDには、データ入力Dinと、単相のクロックCLKが入力される。

### [0034]

単相クロックデータ判定/位相比較回路SPC\_DD/PDは、単相クロックCLKに同期して、データ入力Dinを判定し、判定結果をデータ出力Doutに出力する。同時に、データ入力DinとクロックCLKの位相を比較し、クロックCLKの位相がデータ入力Dinよりも遅い場合にはLate信号、を出力する。

#### [0035]

平均化回路AVは、単層クロックデータ判定/位相比較回路SPC\_DD/PDが出力

20

30

40

50

した位相比較の結果、すなわちEarlyおよびLate信号を、ある一定期間積算することで、クロックCLKとデータ入力Dinの位相の平均的なずれを算出する。その結果、クロックCLKの位相がデータ入力Dinの位相よりも平均的に遅い場合にはUp信号、クロックCLKの位相がデータ入力Dinの位相よりも平均的に早い場合にはDown信号、を出力する。平均化回路AVによる処理は実質的にロウパスフィルタをかけていることと等価であり、平均化回路AVの代わりにアナログロウパスフィルタを用いる構成も可能である。

## [0036]

位相ポインタ制御回路PCONは、上記Up信号およびDown信号に基づいて、位相補間回路PIの出力位相を制御する位相制御信号Sphを出力する。平均化回路AVがUp信号を出力した場合には位相補間回路の出力クロックの位相を早めるように、逆に平均化回路AVがDown信号を出力した場合には位相補間回路の出力クロックの位相を遅らせるように制御する。

## [0037]

位相補間回路PIは、典型的には、位相制御信号Sphに基づいて、外部から入力されたリファレンスクロックCLKrefの位相を変化させることで動作する。これは、リファレンスクロックとして位相が90度ずつずれた4相のクロックを用い、これら4相のクロックに適切な係数をかけて足し合わせる位相補間回路といった公知の手段によって実現することができる。

## [0038]

また、位相補間回路PIの本質的な機能は、位相制御信号Sphに基づいて出力するクロックCLKの位相を変化させることであり、例えば、リファレンスクロックを用いずに、位相制御信号Sphに基づいて出力位相を変化させることが可能な源発振器を位相補間回路PIに内蔵する、という方法も考えられる。この場合、位相制御信号Sphに基づいて出力クロックCLKの位相を直接変える構成や、位相制御信号Sphに基づいて出力クロックCLKの周波数を変化させることで間接的に出力クロックCLKの位相を変化させる構成、といった公知な手段を用いることができる。

#### [0039]

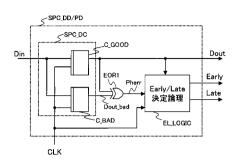

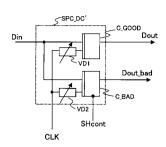

図5Aは、図4における単相クロックデータ判定/位相比較回路SPC\_\_DD/PDの詳細な構成例を示す図である。図5Aに示す単相クロックデータ判定/位相比較回路SPC\_\_DD/PDは、正しいデータ判定に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が短い、すなわち性能が良いクロック同期データ判定器C\_\_GOOと、正しいデータ判定に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が長い、すなわち性能が悪いクロック同期データ判定器C\_\_BADと、2つのクロック同期データ判定器の出力の排他的論理和を出力する排他的論理和回路EOR1と、Early/Late決定論理EL LOGICとで構成される。

## [0040]

20

30

40

50

判定に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が長い、すなわち性能が悪いクロック同期データ判定器 C \_\_ B A D と、をあわせたものを単相クロックデュアルデータ判定器 S P C \_\_ D C と呼ぶことにする。

#### [0041]

また、正しいデータ判定に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が短い、すなわち性能が良いクロック同期データ判定器 C\_\_ G O O D の判定結果 D o u t は、そのまま、単相クロックデータ判定 / 位相比較回路 S P C\_\_ D D / P D のデータ出力 D o u t として出力される。ただし、後述する E a r 1 y / L a t e 決定論理 E L\_\_ L O G I C とのタイミングを合わせる等の目的で、データ判定器 C\_\_ G O O D の出力を、遅延回路、あるいはフリップフロップによるシフトレジスタ等によって、遅延させたものを、単相クロックデータ判定 / 位相比較回路 S P C\_\_ D D / P D のデータ出力 D o u t とする構成も可能である。

#### [0042]

排他的論理和回路EOR1は、データ判定器C\_GOODの出力Doutと、データ判定器C\_BADの出力Dout\_badと、の排他的論理和を計算して、位相エラー信号Pherrとして出力する。

#### [0043]

## [0044]

Early/Late決定論理EL\_LOGICは、性能の良いデータ判定器C\_GOODの出力Doutと、位相エラー信号Pherrとを入力されて、クロックCLKの位相がデータ入力Dinに対して早すぎることを示す信号(Early)と、クロックCLKの位相がデータ入力Dinに対して遅すぎることを示す信号(Late)と、を出力する論理回路である。

#### [0045]

図5BにEarly/Late決定論理EL\_LOGICのより詳細な構成例を示した。図5Bに示したEarly/Late決定論理EL\_LOGICは、性能の良いデータ判定器C\_GOODのデータ出力Doutと、位相エラー信号Pherrと、からEarly1およびLate1を計算する内部Early/Late決定論理EL\_Logic1と、位相エラー信号Pherrを必要なクロックサイクル分だけ遅延させるシフトレジスタSR1と、Early1と位相エラー信号Pherrとの論理積を計算する論理積回路AND1と、Late1と位相エラー信号Pherrとの論理積を計算する論理積回路AND2と、から構成される。

#### [0046]

前述のように、位相エラー信号Pherrは、単相クロックデータ判定/位相比較回路SPC\_DD/PDが位相比較信号EarlyまたはLateを出力するための前提条件となっている。したがって、論理的には、Early/Late決定論理EL\_LOGI

20

30

40

50

Cの、Early出力、Late出力には、位相エラー信号Pherrとの論理積回路が入ることになる。このとき、内部Early/Late決定論理EL\_Logic1における遅延分だけ、位相エラー信号Pherrを遅延させる必要があるため、シフトレジスタSR1の具体的な遅延量は、内部Early/Late決定論理EL\_Logic1で生じる遅延量に合わせて決まっており、内部Early/Late決定論理EL\_Logic1の実装の詳細によって、いろいろな値をとりえる。また、Early1と位相エラー信号Pherrとの論理積を計算する論理積回路AND1と、Late1と位相エラー信号Pherrとの論理積を計算する論理積回路AND2については、論理的にはEARLY/Late決定論理EL\_LOGICの最終段に入る論理積回路という形で表されるが、実際の回路では論理圧縮等の論理の等価論理変換を施した結果、必ずしも、最終段に論理積回路が入らない場合も考えられる。

[0047]

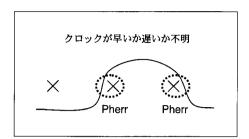

図 6 A は、図 5 B における内部 E a r l y / L a t e 決定論理 E L \_\_ L o g i c 1 の詳 細な構成を含めて、Early/Late決定論理EL\_LOGIC全体の構成例を表したもの である。また、図6Bに図6Aの動作原理を表す波形図を示した。図6Bは、4種類の場 合の波形図を示しており、それぞれの波形は横軸に時間を、縦軸にデータ入力Dinをと って描かれている。図中の×印は、クロック同期データ判定器の判定位置を表しており、 1シンボル時間ごとにおかれている。正しいデータ判定に必要なデータ確定期間(必要セ ットアップ時間と必要ホールド時間の和)が短い、すなわち性能が良いクロック同期デー 夕判 定 器 C \_\_ G O O D と、 正 し N デ ー 夕 判 定 に 必 要 な デ ー 夕 確 定 期 間 ( 必 要 セ ッ ト ア ッ プ 時間と必要ホールド時間の和)が長い、すなわち性能が悪いクロック同期データ判定器C \_\_ BADは、同一のクロックCLKに同期して、同一のデータ入力Dinを判定しており 、図 6 B では、 1 つの x 印が、 C \_\_ G O O D と C \_\_ B A D の両方の判定位置を表している 。 図 6 B にお N て 、 ケ ー ス 1 お よ び ケ ー ス 2 は デ ー 夕 入 力 D i n の 遷 移 が 、 中 央 の 判 定 位 置の直前にあり、クロックCLKの位相が早すぎる場合に相当する。逆に、ケース3およ びケース4はデータ入力Dinの遷移が、中央の判定位置の直後にあり、クロックCLK の位相が早すぎる場合に相当している。ケース1からケース4の全ての場合で、中央の判 定位置において、データ入力Dinの遷移が判定位置に近すぎるため、正しいデータ判定 に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が長い、すな わ 5 性 能 が 悪 い ク ロ ッ ク 同 期 デ ー タ 判 定 器 C \_\_ B A D は 誤 判 定 す る 可 能 性 が あ る。 一 方 で 、 正 し い デ ー 夕 判 定 に 必 要 な デ ー タ 確 定 期 間 ( 必 要 セ ッ ト ア ッ プ 時 間 と 必 要 ホ ー ル ド 時 間 の和)が短い、すなわち性能が良いクロック同期データ判定器C\_GOODは常に正しい 判定をすると考えられる。結果的に、2つのクロック同期データ判定器C\_GOODとC \_\_ B A D の 判 定 結 果 が 異 な る こ と と な り 、 位 相 エ ラ ー 信 号 P h e r r が 出 力 さ れ る 。 図 6 B において、判定位置を示す×印の周りに点線で囲った は、この判定位置で位相エラー 信号Pherrが出力される可能性があることを示している。

[0048]

位相エラー信号 Pherrが出力された場合に、クロック位相が早すぎる場合、つまりケース1もしくはケース2と、クロック位相が遅すぎる場合、つまりケース3もしくだって行うことが可能である。クロック位相が早すずる。クロック位相が早すずる。クロック位相が早ずである。クロック位相が早ずである。クロック位相が早ずである。クロック位相が早ずである。クロック位相が早ずでは、Pherrが出力された中央の判定位置とその1シンボル後(右側)の判定位置とでデータ入力 Dinが同一である。のでデータ入力 Dinが異なる。したがって、位相エラー信号 Pherrが出力された中央の判定位置とその1シンボルをでデータ入力 Dinが異なる。したがって、位相エラー信号 Pherrが出力されたシンボルにおけるデータ入力 Dinが良いクロックにおけるデータ入力 Dinが良いクロックにおけるデータ入力 Dinが良いクロックにおけるデータ入力 Dinが良いクロックにおけるデータ入力 Dinが良いクロックにおけるデータ入力 Dinが良いクロックにおけるデータ入力 Dinが良いクロックにおけるデータ)でで、前後どちらで

データ入力 Dinの遷移が起こっているかを調べることで、クロック位相が早すぎる場合と、クロック位相が遅すぎる場合を識別することが可能である。

## [0049]

図6Aに示した、内部Early/Late決定論理EL\_Logic1はこの考え方に基づいた回路の構成例である。図6Aにおいて、データ出力Dout、すなわち性能が良いクロック同期データ判定器C\_GOODの出力を2つのD型フリップフロップDFF1およびDFF2によって遅延させることで、合わせて3シンボル分のデータ出力Dout間の排他的論理和を計算することで、位相エラー信号Pherrが入力された場合に、クロックCLKの位相がデータ入力Dinに対して早すぎることを示す信号(Early)と、クロックCLKの位相がデータ入力Dinに対して早すぎることを示す信号(Late)と、を出力する。このとき、内部Early/Late決定論理EL\_Logic1内で1シンボル分遅延が発生するため、位相エラー信号Pherr側にも1シンボル遅延させるシフトレジスタ回路SR1を挿入してある。

#### [0050]

以上のとおり、実施の形態 1 による単相クロックデータ判定 / 位相比較回路およびそれを備えた信号再生回路を用いることで、必要なクロック相を従来の 2 相以上から、単相に減らすことが可能となり、回路規模および消費電力を低減することが可能となる。

## [0051]

## (実施の形態2)

実施の形態 2 では、単相クロックデータ判定 / 位相比較回路としては図 5 A に示した実施の形態 1 の構成と変わりがない。ただし、E a r l y / L a t e 決定論理は図 6 A の E L \_ L O G I C に代えて図 7 A の E a r l y / L a t e 決定論理 E L \_ L O G I C 'を用いる。

#### [0052]

前述したように、位相エラー信号 Pherrが出力されたときには、その前後どちらのシンボルでデータ入力 Dinの遷移が起こっているかを調べることで、クロック位相が早すぎる場合とクロック位相が遅すぎる場合を識別することが可能である。しかしながら、図 6 Bで説明した実施の態様 1 の判定方法ではクロック位相が早すぎる、またはクロック位相が遅すぎるという識別を誤る可能性がある。図 7 Bにこの状況を説明する波形図を示した。

## [0053]

図7Bにおいて、中央の判定位置と、その1シンボル後(右側)の判定位置において、 デ ー タ 入 力 D i n の 遷 移 が 判 定 位 置 の 直 前 ま た は 直 後 で 起 こ っ て お り 、 正 し い デ ー タ 判 定 に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が短い、すな わち性能が良いクロック同期データ判定器 C GOODの判定結果と、正しいデータ判定 に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が長い、すな わ ち 性 能 が 悪 い ク ロ ッ ク 同 期 デ ー タ 判 定 器 C \_ B A D の 判 定 結 果 と が 異 な る 、 す な わ ち 位 相エラー信号Pherrが出力される可能性がある。しかしながら、図7Bのように、中 央の判定位置ではデータ入力Dinの遷移が判定位置の前にあり、かつ、その1シンボル 後(右側)の判定位置ではデータ入力Dinの遷移が判定位置の後にある場合、本来であ れば、クロック位相が早すぎるのか、あるいは、クロック位相が遅すぎるのか、を識別す ることは不可能であり、クロックの位相が遅れた結果、図7Bの状態に陥る場合もあり得 る。ところが、この場合、中央の判定位置とその1つ前(左側)の判定位置でのデータ出 力 D o u t が異なる一方で、中央の判定位置とその 1 つ後(右側)の判定位置でのデータ 出力Doutが同一であるため、図6Aに示した構成によるEarly/Late決定論 理 EL\_LOGICでは、クロックCLKの位相がデータ入力Dinに対して早すぎるこ とを示す信号(Early)が出力されることになる。この結果、信号再生回路CDRに よって、クロックCLKの位相が更に遅らされることになるが、これは、本来望ましい動 作ではない。逆に、クロック遅れにもかかわらずLateが出力される場合もある。

10

20

30

40

20

30

40

50

#### [0054]

図7AのEarly/Late決定論理EL\_LOGIC,は、図6AのEARLY/LATE決定論理EL\_LOGIC,は、図6AのEARLY/て、位相エラー信号Pherrは、2つのD型フリップDFF3お記憶されてによって遅延され、合わせて3シンボル分の位相エラー信号Pherrが記憶回路ANDFLate決定論理EL\_LOGIC,ではは「中央の判定位置でのみ位相エラー信号Pherrが出力される。図7Aに示したEarly/Late決定論理EL\_LOGICがではは相当する場合のみ、Early/Late決定論理EL\_LOGICがの結果、一個のように、中央の判定位置のみならず、その前後の判定位置には、ローにの対した場合には、Early信号およびLate信号が誤って出力されることがなくなる。

#### [0055]

以上のとおり、実施の形態 2 の単相クロックデータ判定 / 位相比較回路およびそれを備えた信号再生回路では、位相比較器が誤った位相比較結果を出力することがなくなり、信号再生回路の再生エラーの発生が減少する。

## [0056]

## (実施の形態3)

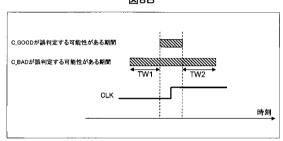

実 施 の 形 態 3 は 、 図 5 A で 説 明 し た 実 施 の 形 態 1 の 単 相 ク ロ ッ ク デ ー タ 判 定 / 位 相 比 較 回路SPC \_\_ DD/PDの各構成要素のうち、単相クロックデュアルデータ判定器SPC \_ D C を図 8 B に示す S P C \_\_ D C 'に置き換えたものである。図 8 B は、図 8 A の単相 クロックデュアルデータ判定器 S P C \_ D C 'の原理的な動作を示す概念図である。図 8 Bは、横軸として時間をとり、クロックCLKと、正しいデータ判定に必要なデータ確定 期間(必要セットアップ時間と必要ホールド時間の和)が短い、すなわち性能が良いクロ ック同期データ判定器 С \_ G О О D が誤判定をする可能性がある期間と、正しいデータ判 定に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が長い、す なわち性能が悪いクロック同期データ判定器 C \_\_ B A D が誤判定をする期間と、を図示し たものである。ここで、性能が良いクロック同期データ判定器 C GOODは正しくデー 夕 判 定 す る 一 方 で 、 性 能 が 悪 い ク ロ ッ ク 同 期 デ ー タ 判 定 器 C \_\_ B A D が 誤 判 定 を す る 可 能 性 が あ る 期 間 は 、 本 発 明 に お け る デ ー 夕 判 定 / 位 相 比 較 回 路 に お い て 、 位 相 比 較 信 号 が 出 る可能性がある期間である。このうち、図 8 B に示したように、クロック立ち上がりに対 して前側の期間をアイトラックウィンドウ期間1あるいはTW1,クロック立ち上がりに 対して後側の期間をアイトラックウィンドウ期間2あるいはTW2、と呼ぶことにする。 デ ー タ 入 カ D i n の 遷 移 が T W 1 の 期 間 中 に 起 こ る と E a r l y 信 号 が 、 デ ー タ 入 力 D i n の遷移がTW2の期間中に起こるとLate信号が出力される可能性がある。

#### [0057]

信号再生回路CDRの性能を高めるには、TW1と、TW2の時間幅が同程度の長さであることが必要である。信号再生回路CDRは、Ear1y信号とLate信号の出現確率を同頻度にするようにクロック信号CLKの位相を制御するフィードバックをかけるため、例えば、TW1の時間幅が、TW2の時間幅に対して長い場合には、クロックCLKの位相が本来最適な位置に対して早すぎる位置で固定されてしまうことになる。

#### [0058]

図8Aに示した単相クロックデュアルデータ判定器SPC\_DCでは、前後のアイトラックウィンドウTW1とTW2の時間幅を同程度にするために、2つのデータ判定器C\_GOODおよびC\_BADに入力されるクロックに、それぞれ可変遅延回路VD1およびVD2が挿入されている。ここで、可変遅延回路VD1の遅延を増加させると、図8BのC\_GOODが誤判定する可能性がある期間が遅くなるため、結果として、前側のアイト

20

30

40

50

ラックウィンドウTW1の時間幅は増加し、後側のアイトラックウィンドウTW2の時間幅は減少することになる。逆に、可変遅延回路VD2の遅延を増加させると、図8BのC \_\_ BADが誤判定する可能性がある期間が遅くなるため、結果として、前側のアイトラックウィンドウTW1の時間幅は減少し、後側のアイトラックウィンドウTW2の時間幅は増加することになる。したがって、2つの可変遅延回路VD1およびVD2の遅延量を適切な値に調整することで、前後のアイトラックウィンドウTW1およびTW2の時間幅を同程度になるように調整することが可能となる。

### [0059]

ここで、2つの可変遅延回路 V D 1 および V D 2 を、2 つのデータ判定器 C \_\_ G O O D および C \_\_ B A D のクロック入力に挿入する代わりに、例えば、 C \_\_ G O O D の前には固定の遅延を挿入し、 C \_\_ B A D の前に挿入されている可変遅延回路 V D 2 のみで T W 1 と T W 2 の時間幅のバランスを調整するような構成も可能である。ここで、 C \_\_ G O O D の前に挿入される固定遅延は、必ずしも、回路図上で陽に表れている必要はなく、データ判定器 C \_\_ G O O D に不可避的に内在している遅延を利用することもできる。また、クロックに可変遅延を挿入する代わりに、それぞれのデータ判定器に入力されるデータ入力に可変遅延を入力する構成も考えられる。この場合、例えば、 C \_\_ G O O D のデータ入力に挿入されている遅延量を増やすと、前側のアイトラックウィンドウ T W 1 の時間幅は減少し、後側のアイトラックウィンドウ T W 2 の時間幅は増加することになる。

## [0060]

ここで、前後のアイトラックウィンドウTW1とTW2の実際の長さを調整する代わりに、信号再生回路CDRのフィードバックループにおいてEarlyとLateの頻度の比を、同一ではないある特定の値になるように調整することで、クロックCLKの位相が最適な位置にくるようする、という構成も可能である。

#### [0061]

信号再生回路CDRの性能を高めるには、TW1とTW2の時間幅のバランスに加えて、TW1およびTW2の時間幅の絶対量にも考慮を払う必要がある。一般に、データ入力Dinに含まれるジッタ量が小さい場合には、TW1とTW2の時間幅を長くすると性能が向上し、データ入力Dinに含まれるジッタ量が大きい場合にはTW1とTW2の時間幅を短くすると性能が向上する。ここで、データ入力Dinに含まれるジッタ量は主に信号を伝送する配線損失に依存しているため、データ入力Dinに含まれるジッタ量は送受信器が使われる状況によって異なり、あらかじめ設計段階で想定することは難しい。したがつて、TW1とTW2の時間幅の絶対量を、使用する状況に合わせて調整可能とすることが望ましい。

## [0062]

図8 Bより、TW1とTW2の時間幅の絶対量の調整は、C\_BADが誤判定をする可能性がある期間を調整可能とすることで、実現可能なことがわかる。図8 Aに示した単相クロックデュアルデータ判定器SPC\_DC」では、正しいデータ判定に必要なデータ確定期間(必要セットアップ時間と必要ホールド時間の和)が長い、すなわち性能が悪いクロック同期データ判定器C\_BADの、必要なデータ確定期間(必要セットアップ時間、および必要ホールド時間)を外部からの制御信号SHcontによって制御可能としている。

#### [0063]

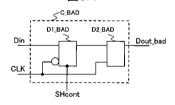

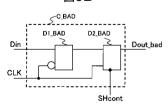

図9Aは、図8Aのデータ判定器 C \_\_ BADの一構成例を示す。また、図9Bはデータ判定器 C \_\_ BADの別の構成例を表す図である。図9Aのデータ判定器、および図9Bのデータ判定器の双方とも、それぞれ逆相のクロック C L K に同期して動作する2つのD型ラッチ回路(レベルトリガラッチ回路)D1\_BADおよびD2\_BADを含み、マスター/スレーブ構成のD型フリップフロップ回路を構成している。

#### [0064]

図 9 A に示したデータ判定器 C \_\_ B A D では、マスター側の D 型ラッチ回路(レベルトリガラッチ回路) D 1 \_\_ B A D に、制御信号 S H c o n t が入力されており、 D 1 \_\_ B A

Dが正しくデータ保持動作をするのに必要なデータ確定期間を、制御信号SHcontによって調整可能としている。この結果、制御信号SHcontによって、データ判定器C \_ BAD全体の、正しいデータ判定に必要なデータ確定期間(必要セットアップ時間、および必要ホールド時間)を可変とし、アイトラックウィンドウTW1とTW2の時間幅の絶対量を調整することができる。

### [0065]

図9Bに示したデータ判定器 C \_\_ BADでは、スレーブ側のD型ラッチ回路(レベルトリガラッチ回路)D2\_BADに、制御信号SHcontが入力されており、D2\_BADが正しくデータ保持動作をするのに必要なデータ確定期間を、制御信号SHcontによって調整可能としている。この結果、図9Aと同様に、制御信号SHcontによって、データ判定器 C \_\_ BAD全体の、正しいデータ判定に必要なデータ確定期間(必要セットアップ時間、および必要ホールド時間)を可変とし、アイトラックウィンドウTW1とTW2の時間幅の絶対量を調整することができる。

#### [0066]

また、マスター側のD型ラッチ回路(レベルトリガラッチ回路)D1\_BAD、あるいは、スレーブ側のD型ラッチ回路(レベルトリガラッチ回路)D2\_BADのみに制御信号SHcontを入力するのではなく、マスター側およびスレーブ側の両方のD型ラッチ回路(レベルトリガラッチ回路)に制御信号SHcontを入力し、2つのD型ラッチ回路(レベルトリガラッチ回路)が正しくデータ保持動作をするのに必要なデータ確定期間を、同時に調整する構成も可能である。

#### [0067]

## [0068]

図10において、CMOSインバータに挿入する可変抵抗は、必ずしもNMOS側とPMOS側の両方に入れる必要はなく、NMOS側のみ、あるいはPMOS側のみに挿入する構成も可能である。この場合、動作としては、後述する実施の形態4におけるデータ判定器C\_BADと同様に、データ判定器C\_BADに強制的にオフセットを導入したことに相当する。

## [0069]

以上、本実施の形態3による単相クロックデータ判定/位相比較回路およびそれを備えた信号再生回路を用いることで、位相比較回路の前後のアイトラックウィンドウTW1およびTW2のバランスおよび絶対時間を調整することが可能となり、信号再生回路を伝送路の状態に合わせて最適な動作とすることが可能となる。

## [0070]

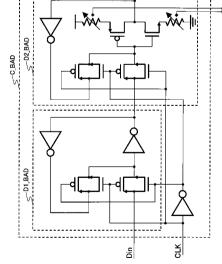

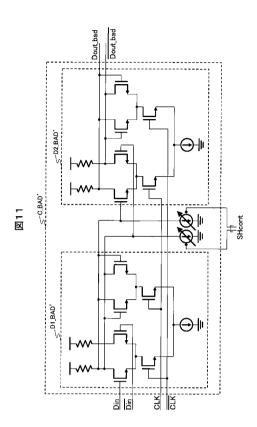

#### (実施の形態4)

実施の形態 4 では、図 8 A に示した単相クロックデュアルデータ判定器の「性能が悪い」方のデータ判定器 C \_\_ B A D として、図 1 1 に示すものを用いる。図 1 1 のデータ判定器 C \_\_ B A D 'は、 2 つの完全差動構成のカレントモードロジック回路( C M L 回路)に

10

20

30

40

よるD型ラッチ回路(レベルトリガラッチ回路)D1\_BAD,およびD2\_BAD,と、これらD型ラッチ回路(レベルトリガラッチ回路)D1\_BAD,およびD2\_BAD,の間に配置されている2つの可変電流源と、から構成されている。この2つの可変電流源は、カレントモードロジック回路(CML回路)のオフセット調整用に一般的に使われる回路と同様のものである。この2つの可変電流源を制御信号SHcontによって制御することで、スレーブ側のD型ラッチ回路(レベルトリガラッチ回路)D2\_BAD,に強制的にオフセットを導入することができる。オフセットが導入されることで、等価的に、データ判定器C\_BADが正しくデータ判定をするのに必要なデータ確定期間を長くすることが可能である。

### [0071]

たとえば、オフセットを導入することで、スレーブ側のD型ラッチ回路(レベルトリガラッチ回路)D2\_BAD'は、"1"に比べて"0"を出力しやすい状態になったとする。このとき、データ入力Dinが"0"から"1"に遷移する場合を考えると、オフセットを導入したことによりD2\_BAD'は"0"を出力しやすくなっているため、D2\_BAD'は"0"を出力しやすくなっているため、D2」BAD'の出力Dout\_badが、"0"から"1"に遷移するためには、オフセットがない状態に比べて長時間データ入力が確定している必要がある。一方で、データ入りの確定期間は短くなる。しかしながら、データ判定器C\_BAD全体としてみたときの必要なデータ確定期間は、最も必要なデータ確定期間が長くなるようなデータパタンによって規定されているため、オフセットを導入したことで、データ判定器C\_BAD′が正しくデータ判定をするのに必要なデータ確定期間は長くなる。

#### [0072]

以上より、導入するオフセットの量を、制御信号SHcontによって調整することで、データ判定器C\_BAD'の必要なデータ確定期間(必要セットアップ時間、および必要ホールド時間)を可変とし、アイトラックウィンドウTW1とTW2の時間幅の絶対量を調整することが可能となる。

## [ 0 0 7 3 ]

ここで、図11で示した可変電流源による方法以外にも、差動信号線の p および n に、それぞれ可変容量を付加する、といった公知の方法によってデータ判定器 C \_ B A D にオフセットを導入することも可能である。

#### [0074]

オフセット導入による必要データ確定期間の長時間化は、前後のアイトラックウィンドウTW1およびTW2に同じように利くため、オフセット導入に伴って、実施の形態3に関しての記述で前述した、前後のアイトラックウィンドウTW1とTW2の時間幅のアンバランスが生じる問題が起こらない、という利点がある。

## [0075]

以上、本実施の形態 4 による単相クロックデータ判定 / 位相比較回路およびそれを備えた信号再生回路を用いることで、位相比較器の前後のアイトラックウィンドウTW 1 およびTW 2 の絶対時間をそのバランスを保ちながら調整することが可能となり、信号再生回路を伝送路の状態に合わせて最適な動作とすることが可能となる。

## [0076]

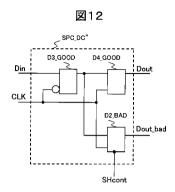

#### (実施の形態5)

実施の形態 5 は、図 5 Aに示した実施の形態 1 の単相クロックデータ判定 / 位相比較回路 S P C \_\_ D D / P D の各構成要素のうち、単相クロックデュアルデータ判定器 S P C \_\_ D C を図 1 2 に示す S P C \_\_ D C "に置き換えたものである。図 1 2 の単相クロックデュアルデータ判定器 S P C \_\_ D C "は、 3 つの D 型ラッチ回路(レベルトリガラッチ回路) D 3 \_\_ G O O D、 D 4 \_\_ G O O D、および、 D 2 \_\_ B A D から構成される。本回路は、図 5 A に示した単相クロックデュアルデータ判定器 S P C \_\_ D C における性能の良いデータ判定器 C \_\_ G O O D、および、性能が悪いデータ判定器 C \_\_ B A D で、マスター側の D 型ラッチ回路(レベルトリガラッチ回路)を共有しており、スレーブ側の D 型ラッチ回路(

10

20

30

40

レベルトリガラッチ回路)のみを別々にしたものと言える。 D型ラッチ回路(レベルトリガラッチ回路) D 2 \_\_ B A D が正しくデータ保持するのに必要なデータ確定期間を制御信号 S H c o n t で調整することで、性能の悪いデータ判定器 C \_\_ B A D が正しくデータ判定するのに必要なデータ確定期間、すなわちアイトラックウィンドウTW 1 およびTW 2 の時間幅の絶対量を調整することが可能である。この調整には、実施の形態 3 の説明で述べた方法、もしくは実施の形態 4 の説明で述べた方法を適用する。

[0077]

本実施の形態 5 では、マスター側の D 型ラッチ回路 (レベルトリガラッチ回路) D 3 . G O O D は、性能の良いデータ判定器 C \_\_ G O O D 、および、性能が悪いデータ判定器 C \_ B A D とで共有されている。このため、もし、性能が悪いデータ判定器 C \_\_ B A D のス レーブ側の D 型ラッチ回路 (レベルトリガラッチ回路) D 2 \_ B A D を、性能が良いデー タ判定器 C G O O D のスレーブ側の D 型ラッチ回路 (レベルトリガラッチ回路) D 4 GOODと全く同一のものであれば、2つの判定器は全く同一の結果を出力することにな る。この状態から、制御信号SHcontによって、性能が悪いデータ判定器C\_BAD のスレーブ側のD型ラッチ回路(レベルトリガラッチ回路)D2 BADが正しくデータ 保持するのに必要なデータ確定期間を長くしていくことで、アイトラックウィンドウTW 1およびTW2の時間幅を望ましい量に調整することができる。このときに、実施の形態 4 で説明したようなオフセット導入によって、性能が悪いデータ判定器 C \_\_ B A D のスレ ーブ側の D 型ラッチ回路(レベルトリガラッチ回路) D 2 \_ B A D が正しくデータ保持す るのに必要なデータ確定期間を長くすると、オフセット導入に伴って、実施の形態3に関 して記述した、前後のアイトラックウィンドウTW1とTW2の時間幅のアンバランスが 生じる問題が起こらない。したがって、前後のアイトラックウィンドウTW1とTW2の 時間幅のバランスを調整する回路が不要となり、回路規模および消費電力を削減すること が可能となる。

[0078]

以上、実施の形態 5 による単相クロックデータ判定 / 位相比較回路およびそれを備えた信号再生回路を用いることで、マスター側の D 型ラッチ回路(レベルトリガラッチ回路)を 2 つのデータ判定器で共有することにより回路規模および消費電力を削減することが可能となるのみならず、位相比較器の前後のアイトラックウィンドウTW 1 およびTW 2 の絶対時間をそのバランスを保ちながら調整することが可能となり、信号再生回路を伝送路の状態に合わせて最適な動作とすることが可能となる。

[0079]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は記述された実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

【産業上の利用可能性】

[0800]

本発明の種々の実施の形態による光通信装置は、特に、数十Gbpsを超える通信速度を備えた光通信システムにおいて、その受信部の回路に適用して有効なものである。

【符号の説明】

[ 0 0 8 1 ]

CDR: 信号再生回路

S P C \_ D D / P D : 単相クロックデータ判定/位相比較回路

SPC\_DC、SPC\_DC'、SPC\_DC": 単相クロックデュアルデータ判定器

C\_GOOD、C\_BAD: 単相クロックデータ判定器

EL\_LOGIC、EL\_LOGIC': Early/Late決定論理

DFF1、DFF2、DFF3, DFF4: D型フロップフロップ

SR1: シフトレジスタ

D 1 \_ B A D 、 D 2 \_ B A D 、 D 3 \_ G O O D 、 D 4 \_ G O O D : D型ラッチ回路

20

10

30

# 【図1】

# 【図2A】

# 図2A

# 【図2B】

図2B

## 【図3】

## 【図4】

## 【図5A】

図5A

## 【図5B】

図5B

## 【図6A】

【図7A】

# 図6A

## 【図 6 B】

図6B

## 【図7B】

図7B

## 【図8A】

図8A

## 【図8B】

図8B

## 【図9A】

図9A

## 【図9B】

図9B

## 【図10】

図10

【図11】

【図12】

#### 【国際調査報告】

### INTERNATIONAL SEARCH REPORT International application No. PCT/JP2009/066936 A. CLASSIFICATION OF SUBJECT MATTER H03K5/26(2006.01)i, H03L7/06(2006.01)i, H03L7/085(2006.01)i According to International Patent Classification (IPC) or to both national classification and IPC B. FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) H03K5/26, H03L7/06, H03L7/085 Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Jitsuyo Shinan Koho 1922-1996 Jitsuyo Shinan Toroku Koho 1996-2009 1971-2009 Toroku Jitsuyo Shinan Koho Kokai Jitsuyo Shinan Koho 1994-2009 Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) C. DOCUMENTS CONSIDERED TO BE RELEVANT Relevant to claim No. Category\* Citation of document, with indication, where appropriate, of the relevant passages 1-11 JP 60-256227 A (Enu Be Firippusu Α Furuiranbenfuaburiken), 17 December 1985 (17.12.1985), entire text; fig. 3 & US 04689577 A JP 11-112335 A (NEC Corp.), 1 - 11Α 23 April 1999 (23.04.1999), entire text; fig. 4 & US 06314151 B1 Α JP 11-355133 A (NEC Corp.), 1-11 24 December 1999 (24.12.1999), entire text; fig. 3 & US 06421404 B1 Further documents are listed in the continuation of Box C. See patent family annex. later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention Special categories of cited documents: document defining the general state of the art which is not considered to be of particular relevance document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone "E" earlier application or patent but published on or after the international filing "X" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination document referring to an oral disclosure, use, exhibition or other means being obvious to a person skilled in the art document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Date of mailing of the international search report 27 October, 2009 (27.10.09) Date of the actual completion of the international search 16 October, 2009 (16.10.09) Name and mailing address of the ISA/ Authorized officer Japanese Patent Office Telephone No.

Facsimile No.

Form PCT/ISA/210 (second sheet) (April 2007)

#### 国際調査報告

国際出願番号 PCT/JP2009/066936

発明の属する分野の分類(国際特許分類(IPC))

Int.Cl. H03K5/26(2006.01)i, H03L7/06(2006.01)i, H03L7/085(2006.01)i

B. 調査を行った分野

調査を行った最小限資料(国際特許分類(IPC))

Int.Cl. H03K5/26, H03L7/06, H03L7/085

最小限資料以外の資料で調査を行った分野に含まれるもの

日本国実用新案公報 1922-1996年 日本国公開実用新案公報 1971-2009年 日本国実用新案登録公報 1996-2009年 1994-2009年 日本国登録実用新塞公報

国際調査で使用した電子データベース(データベースの名称、調査に使用した用語)

#### 関連すると認められる文献

| 0. 対定すると前のうれる人間         |                                                                                     |                |  |  |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------|----------------|--|--|--|--|--|

| 引用文献の<br>カテゴリー <b>*</b> | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                   | 関連する<br>請求項の番号 |  |  |  |  |  |

| A                       | JP 60-256227 A (エヌ・ベー・フィリップス・フルーイランベンフアプリケン) 1985.12.17、全文、FIG.3<br>& US 04689577 A | 1-11           |  |  |  |  |  |

| A                       | JP 11-112335 A (日本電気株式会社)<br>1999.04.23、全文、図4<br>& US 06314151 B1                   | 1-11           |  |  |  |  |  |

| A                       | JP 11-355133 A (日本電気株式会社)<br>1999. 12. 24、全文、図3<br>& US 06421404 B1                 | 1 – 1 1        |  |  |  |  |  |

□ C欄の続きにも文献が列挙されている。

『 パテントファミリーに関する別紙を参照。

- \* 引用文献のカテゴリー

- 「A」特に関連のある文献ではなく、一般的技術水準を示す 「T」国際出願日又は優先日後に公表された文献であって 40

- 「E」国際出願目前の出願または特許であるが、国際出願目 以後に公表されたもの

- 「L」優先権主張に疑義を提起する文献又は他の文献の発行 日若しくは他の特別な理由を確立するために引用す る文献(理由を付す)

- 「O」口頭による開示、使用、展示等に言及する文献

- 「P」国際出願目前で、かつ優先権の主張の基礎となる出願

- の日の後に公表された文献

- 出願と矛盾するものではなく、発明の原理又は理論 の理解のために引用するもの

- 「X」特に関連のある文献であって、当該文献のみで発明 の新規性又は進歩性がないと考えられるもの

- 「Y」特に関連のある文献であって、当該文献と他の1以 上の文献との、当業者にとって自明である組合せに よって進歩性がないと考えられるもの

- 「&」同一パテントファミリー文献

国際調査を完了した日 国際調査報告の発送日 16. 10. 2009 27. 10. 2009 5 X 3572 国際調査機関の名称及びあて先 特許庁審査官(権限のある職員) 日本国特許庁(ISA/JP) 石田 勝 郵便番号100-8915 東京都千代田区霞が関三丁目4番3号 電話番号 03-3581-1101 内線 3596

様式PCT/ISA/210 (第2ページ) (2007年4月)

(注)この公表は、国際事務局(WIPO)により国際公開された公報を基に作成したものである。なおこの公表に係る日本語特許出願(日本語実用新案登録出願)の国際公開の効果は、特許法第184条の10第1項(実用新案法第48条の13第2項)により生ずるものであり、本掲載とは関係ありません。