### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5145691号 (P5145691)

(45) 発行日 平成25年2月20日(2013.2.20)

(24) 登録日 平成24年12月7日(2012.12.7)

| 11012        | E1/UEE  | (2000.01)          | 11011 2 | •            | 2 (全 19 頁) | 最終頁に続く |

|--------------|---------|--------------------|---------|--------------|------------|--------|

| HO1L         | 21/922  | (2006, 01)         | HO1L 27 | 7/08 331A    |            |        |

| HO1L         | 27/08   | (2006.01)          | HO1L 27 | 7/08 331E    |            |        |

| HO1L         | 27/088  | (2006.01)          | HO1L 27 | 7/08 1 O 2 A |            |        |

| HO1L         | 21/8234 | <b>(2006</b> . 01) | HO1L 21 | L/76 L       |            |        |

| HO1L         | 21/76   | (2006.01)          | HO1L 21 | L/76 S       |            |        |

| (51) Int.Cl. |         |                    | FΙ      |              |            |        |

特願2006-295740 (P2006-295740) (21) 出願番号 (22) 出願日 平成18年10月31日 (2006.10.31) (65) 公開番号 特開2007-294844 (P2007-294844A) (43) 公開日 平成19年11月8日 (2007.11.8) 平成20年10月1日(2008.10.1) 審査請求日 (31) 優先権主張番号 特願2006-46447 (P2006-46447) 平成18年2月23日 (2006.2.23) (32) 優先日 (33) 優先権主張国 日本国(JP) (31) 優先権主張番号 特願2006-87643 (P2006-87643)

(32) 優先日 平成18年3月28日 (2006.3.28) (33) 優先権主張国 日本国 (JP) ||(73)特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

||(74)代理人 100066980

弁理士 森 哲也

||(74)代理人 100075579

弁理士 内藤 嘉昭

(74)代理人 100103850

弁理士 田中 秀▲てつ▼

||(72)発明者 加藤 樹理

長野県諏訪市大和3丁目3番5号 セイコ

ーエプソン株式会社内

審査官 松本 陶子

最終頁に続く

# (54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

## 【請求項1】

絶縁層上に第1半導体層が積層されてなる第1SOI領域と、

前記第1半導体層上からみて前記第1SOI領域と異なる領域に第2絶縁層と第2半導体層とが積層されてなる第2SOI領域とを同一の支持基板に備え、

前記第1SOI領域における前記第1半導体層の表面と、前記第2SOI領域における前記第2半導体層の表面とが同一平面上にあり、

前記第1SOI領域に形成された回路素子と、前記第2SOI領域に形成された回路素子との間の前記第1半導体層に電位固定用の不純物拡散層を備える、ことを特徴とする半導体装置。

【請求項2】

前記支持基板は半導体基板であり、前記半導体基板は、500 cmを超える抵抗を有することを特徴とする請求項1に記載の半導体装置。

【発明の詳細な説明】

### 【技術分野】

# [0001]

本発明は半導体装置に関し、特に、バルク構造とSOI(Silicon On Insulator)構造とが同一基板上に混載された半導体装置に適用して好適なものである。

【背景技術】

### [0002]

SOI基板上に形成された電界効果型トランジスタは、素子分離の容易性、ラッチアップフリー、ソース / ドレイン接合容量が小さいなどの点から、その有用性が注目されている。特に、完全空乏型SOIトランジスタは、低消費電力かつ高速動作が可能で、低電圧駆動が容易なため、SOIトランジスタを完全空乏モードで動作させるための研究が盛んに行われている。ここで、非特許文献1には、バルク基板上にSOI層を形成することで、SOIトランジスタを低コストで形成できる方法が開示されている。この非特許文献1に開示された方法では、Si基板上にSi / SiGe層を成膜し、SiとSiGeとのエッチングレートの違いを利用してSiGe層のみを選択的に除去することにより、Si基板とSi層との間に空洞部を形成する。そして、空洞部内に露出されたSiの熱酸化を行うことにより、Si基板とSi層との間にSiО₂層を埋め込み、Si基板とSi層との間にBOX層を形成する。

【非特許文献1】T.Sakai et al."Separation by BondingSi Islands(SBSI) for LSI Application", Second International SiGe Technology and Device Meeting, Meeting Abstract, pp. 230-231, May(2004)

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0003]

しかしながら、バルク構造とSOI構造とを同一基板上に混載した場合、回路ブロックの配置位置によっては回路ブロック間で基板ノイズによる干渉が発生し、半導体装置の信頼性の低下を招くという問題があった。一方、回路ブロック間でのノイズによる干渉を低下させるために、隣接する回路ブロック間の距離を大きく取ると、チップサイズの増大を招き、実装面積の増大やコストアップの要因となるという問題があった。

そこで、本発明の目的は、回路ブロック間でのノイズによる干渉を抑制しつつ、バルク構造とSOI構造とを同一基板上に混載することが可能な半導体装置を提供することである。

【課題を解決するための手段】

# [0004]

〔発明1〕 上述した課題を解決するために、発明1の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成された第1回路ブロックと、前記第1回路ブロックを介して互いに隔てられるようにして前記半導体基板に形成された第2および第3回路ブロックとを備えることを特徴とするものである。

これにより、バルク構造を持つ複数の回路ブロックを、クロストークノイズ耐性に強い SOI構造を介して互いに隔てられるようにして同一基板上に混載することができる。このため、回路ブロック間でのクロストークノイズを抑制しつつ、隣接する回路ブロック間の距離を小さくすることが可能となり、チップサイズの増大を抑制しつつ、様々の機能を 1 チップに搭載することが可能となるとともに、半導体装置の特性を向上させつつ、半導体装置の信頼性を向上させることができる。

# [0005]

〔発明2〕 発明2の半導体装置は、発明1の半導体装置において、前記第1回路ブロックは、前記第2回路ブロックと前記第3回路ブロックとの間に配置されていることを特徴とするものである。

これにより、バルク構造を持つ複数の回路ブロックを、SOI構造を介して互いに隔てられるようにして同一基板上に混載することができ、チップサイズの増大を抑制しつつ、回路ブロック間でのクロストークノイズを抑制することが可能となる。また、第1回路ブロックの周囲を半導体基板で囲むことが可能となり、第1回路ブロックからの熱放散性を向上させることを可能として、第1回路ブロックの温度特性を向上させることができる。

# [0006]

10

20

30

〔発明3〕 発明3の半導体装置は、発明1または発明2の半導体装置において、前記第2回路ブロックまたは前記第3回路ブロックは前記第1回路ブロックの少なくとも一辺に接するように配置されていることを特徴とするものである。

これにより、バルク構造とSOI構造とを同一基板上に混載した場合においても、バルク構造を持つ複数の回路ブロックがSOI構造を介して互いに隔てられるように配置することが可能となり、チップサイズの増大を抑制しつつ、回路ブロック間でのクロストークノイズを抑制することが可能となる。

〔発明4〕 発明4の半導体装置は、発明1から発明3の何れか一の半導体装置において、前記半導体基板は、500 cmを超える抵抗を有することを特徴とするものである。

[0007]

〔発明5〕 発明5の半導体装置は、発明1から発明4の何れか一の半導体装置において、前記第1回路ブロックはデジタル回路、前記第2回路ブロックおよび前記第3回路ブロックはアナログ回路であることを特徴とするものである。

これにより、デジタル回路とアナログ回路とを同一基板上に混載しつつ、デジタル回路をSOI構造、アナログ回路をバルク構造にて構成することが可能となるとともに、ラッチアップ耐性を強化しつつ、デジタル回路から外部に放出されるノイズをSOI構造にて遮断することが可能となる。このため、チップサイズの増大を抑制しつつ、デジタル回路の低電圧駆動化、高速化および低消費電力化を図ることが可能となるとともに、アナログ回路の高耐圧化および高信頼性化を図ることが可能となる。

[00008]

〔発明 6 〕 発明 6 の半導体装置は、発明 1 から発明 4 の何れか一の半導体装置において、前記第 1 回路ブロックは低電圧駆動回路、前記第 2 回路ブロックおよび前記第 3 回路ブロックは高電圧駆動回路であることを特徴とするものである。

これにより、低電圧駆動回路と高電圧駆動回路とを同一基板上に混載しつつ、低電圧駆動回路をSOI構造、高電圧駆動回路をバルク構造にて構成することが可能となるとともに、ラッチアップ耐性を強化しつつ、低電圧駆動回路から外部に放出されるノイズをSOI構造にて遮断することが可能となる。このため、チップサイズの増大を抑制しつつ、低電圧駆動回路の高速化および低消費電力化を図ることが可能となるとともに、高電圧駆動回路の高耐圧化および高信頼性化を図ることが可能となる。

[0009]

〔発明7〕 発明7の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成されたMCUコアと、前記半導体基板に形成され、前記MCUコアの周囲に配置されたDRAM、不揮発性メモリ、電源回路、高電圧駆動ドライバ、RF回路または発振回路の中から選択される少なくとも2以上の回路ブロックとを備えることを特徴とするものである。

これにより、システムLSIを1チップにて構成した場合においても、バルク構造を持つ複数の回路ブロックを、SOI構造を介して互いに隔てられるようにして同一基板上に混載することが可能となる。このため、回路ブロック間でのクロストークノイズを抑制しつつ、回路ブロック間の距離を小さくすることが可能となり、チップサイズの増大を抑制しつつ、システムLSIを実現することが可能となるとともに、システムLSIの特性を向上させつつ、システムLSIの信頼性を向上させることができる。

[0010]

[発明8] 発明8の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成されたMCUコアと、前記半導体基板に形成され、前記MCUコアの周囲に配置されたセンサインターフェース回路、RF回路または発振回路の中から選択される少なくとも2以上の回路ブロックとを備え、前記回路ブロックには前記回路ブロックの外周の少なくとも一辺に配置されるとともに、他の回路ブロックに接するように配置されたSOI構造が設けられていること特徴とするものである。

これにより、システムLSIを1チップにて構成した場合においても、回路ブロック間でのクロストークノイズを抑制しつつ、隣接する回路ブロック間の距離を小さくすること

10

20

30

40

20

30

40

50

が可能となる。このため、チップサイズの増大を抑制しつつ、システムLSIを実現することが可能となるとともに、システムLSIの特性を向上させつつ、システムLSIの信頼性を向上させることができる。

### [0011]

〔発明9〕 発明9の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成されたSRAMと、前記半導体基板に形成され、前記SRAMの周囲に配置された電源回路、ドライバまたはD/Aコンバータの中から選択される少なくとも2以上の回路ブロックとを備えることを特徴とするものである。

これにより、SRAMを持つドライバLSIを1チップにて構成した場合においても、回路ブロック間でのクロストークノイズを抑制しつつ、回路ブロック間の距離を小さくすることが可能となる。このため、チップサイズの増大を抑制しつつ、ドライバLSIを実現することが可能となるとともに、ドライバLSIの特性を向上させつつ、ドライバLSIの信頼性を向上させることができる。

### [0012]

[発明10] 発明10の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成された、RTC回路及び待機(スタンド・バイ)時に動作する回路を備えることを特徴とするものである。

### [0013]

〔発明11〕 上記目的を達成するために、発明11の半導体装置は、絶縁層上に半導体層が積層されてなるSOI領域と、下地が基板のみからなるバルク領域とを同一の半導体基板に備え、前記SOI領域に形成された回路素子と、前記バルク領域に形成された回路素子との間の前記半導体基板に電位固定用の第1不純物拡散層を備える、ことを特徴とするものである。

このような構成であれば、SOI領域に形成された回路素子と、バルク領域に形成された回路素子との間で生じる電気力線を第1不純物拡散層で遮断することができ、両領域間でのクロストークノイズを抑制することができる。これにより、半導体装置の誤作動を防止することができる。

### [0014]

[発明12] 発明12の半導体装置は、発明11の半導体装置において、前記SOI領域には、第1SOI領域と、当該第1SOI領域よりも前記半導体層の厚さが大きい第2SOI領域とが含まれ、前記第1SOI領域に形成された回路素子と、前記第2SOI領域に形成された回路素子との間の前記半導体層に電位固定用の第2不純物拡散層を備える、ことを特徴とするものである。ここで、第1SOI領域には例えば部分空乏型のトランジスタが形成され、第2SOI領域には例えば完全空乏型のトランジスタが形成される。

このような構成であれば、第1SOI領域に形成された回路素子と、第2SOI領域に 形成された回路素子との間で生じる電気力線を第2不純物拡散層で遮断することができる ので、SOI領域内でのクロストークノイズを抑制することができる。

### [0015]

[発明13~15] 発明13の半導体装置は、発明11又は発明12の半導体装置において、前記SOI領域の前記絶縁層下の前記半導体基板に電位固定用の第3不純物拡散層を備える、ことを特徴とするものである。

発明14の半導体装置は、発明13の半導体装置において、前記第1不純物拡散層と前記第3不純物拡散層は共に第1導電型であり、前記第1不純物拡散層は前記第3不純物拡散層よりも前記第1導電型の不純物濃度が高いことを特徴とするものである。

#### [0016]

発明15の半導体装置は、発明13の半導体装置において、前記第2不純物拡散層と前記第3不純物拡散層は共に第1導電型であり、前記第2不純物拡散層は前記第3不純物拡散層よりも前記第1導電型の不純物濃度が高いことを特徴とするものである。

発明13~15の半導体装置によれば、バルク領域からSOI領域の絶縁層下側に回り込んでくる電気力線を遮断したり、SOI領域で発生するノイズの基板側への伝達を防い

だりすることが容易である。

### [0017]

[発明16] 発明16の半導体装置は、発明11の半導体装置において、前記半導体基板は、500 cmを超える抵抗を有することを特徴とするものである。このような構成であれば、SOI領域の絶縁層下の基板抵抗を大きくすることができるので、半導体装置のクロストークノイズ耐性をよりいっそう向上させることが可能である。

#### [ 0 0 1 8 ]

[発明17] 発明17の半導体装置は、絶縁層上に第1半導体層が積層されてなる第1SOI領域と、前記第1半導体層上に第2絶縁層と第2半導体層とが積層されてなる第2SOI領域とを同一の支持基板に備え、前記第1SOI領域に形成された回路素子と、前記第2SOI領域に形成された回路素子との間の前記第1半導体層に電位固定用の不純物拡散層を備える、ことを特徴とするものである。

このような構成であれば、第1SOI領域に形成された回路素子と、第2SOI領域に 形成された回路素子との間で生じる電気力線を不純物拡散層で遮断することができ、両領 域間でのクロストークノイズを抑制することができる。これにより、半導体装置の誤作動 を防止することができる。

### [0019]

〔発明18〕 発明18の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成された第1回路ブロックと、前記所定領域の周囲の前記半導体基板に形成された第2回路ブロックと、前記第1回路ブロックと前記第2回路ブロックとの間の前記半導体基板に形成された電位固定用の不純物拡散層と、を備えることを特徴とするものである。

このような構成であれば、SOI構造を持つ第1回路ブロックと、バルク構造を持つ第 2回路ブロックとの間で生じる電気力線を不純物拡散層で遮断することができ、第1、第 2回路ブロック間でのクロストークノイズを抑制することができるので、半導体装置の誤 作動を防止することができる。

# [0020]

[発明19] 発明19の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成されたMCUコアと、前記半導体基板に形成され、前記MCUコアの周囲に配置されたメモリ回路、電源回路、発振回路、A/Dコンバータを少なくとも1つ以上含む周辺回路ブロックと、前記MCUコアと前記周辺回路ブロックとの間の前記半導体基板に形成された電位固定用の不純物拡散層と、を備えることを特徴とするものである。

このような構成であれば、システムLSIを1チップにて構成した場合においても、SOI構造を持つMCUコアと、バルク構造を持つ周辺回路ブロックとの間で生じる電気力線を不純物拡散層で遮断することができ、双方の間でクロストークノイズを抑制することができる。これにより、システムLSIの誤作動を防止することができ、その動作信頼性を向上させることができる。

# [0021]

【発明20〕 発明20の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成されたMCUコアと、前記半導体基板に形成され、前記MCUコアの周囲に配置されたセンサインターフェース回路、RF回路、液晶コントローラ、又は電源回路を少なくとも1つ以上含む第1周辺回路ブロックと、前記半導体基板に形成された第2周辺回路ブロックと、前記第1周辺回路ブロックの外周の少なくとも一辺に配置されるとともに、前記第2周辺回路ブロックと隣りあうように配置されたSOI構造体と、前記MCUコアと前記第1周辺回路ブロックとの間の前記半導体基板に形成された電位固定用の不純物拡散層と、を備えることを特徴とするものである。

#### [0022]

このような構成であれば、システムLSIを1チップにて構成した場合においても、SOI構造を持つMCUコアと、バルク構造を持つ第1周辺回路ブロックとの間で生じる電

10

20

30

40

気力線を不純物拡散層で遮断することができ、双方の間でクロストークノイズを抑制することができる。また、第1周辺回路ブロックと第2周辺回路ブロックとの間でのクロストークノイズもSOI構造の介在によって抑制することができる。これにより、システムLSIの誤作動を防止することができ、その動作信頼性を向上させることができる。

ここで、RTC回路及び待機時に電圧が印加されている回路部分を完全空乏SOI構造にすれば、待機時の消費電力を大幅に削減できる。また、動作時には、強いクロストークノイズ耐性を有するため、RTC回路や待機時動作回路を低電圧で駆動しながら、バルク構造を持つ回路を高電圧で駆動できる。

### [0023]

[発明21] 発明21の半導体装置は、半導体基板上の一部の領域に絶縁層を介して配置された半導体層と、前記半導体層上に形成されたSRAMと、前記半導体基板に形成され、前記SRAMの周囲に配置された電源回路、ドライバ、I/O回路、又はD/Aコンバータを少なくとも1つ以上含む周辺回路ブロックと、前記SRAMと前記周辺回路ブロックとの間の前記半導体基板に形成された電位固定用の不純物拡散層と、を備えることを特徴とするものである。

#### [0024]

このような構成であれば、SRAMを持つドライバLSIを1チップにて構成した場合においても、SOI構造を持つSRAMと、バルク構造を持つ周辺回路ブロックとの間で生じる電気力線を不純物拡散層で遮断することができ、双方の間でクロストークノイズを抑制することができる。これにより、ドライバLSIの誤作動を防止することができ、その動作信頼性を向上させることができる。

【発明を実施するための最良の形態】

### [0025]

以下、本発明の実施形態に係る半導体装置の製造方法について図面を参照しながら説明 する。

### (1)第1実施形態

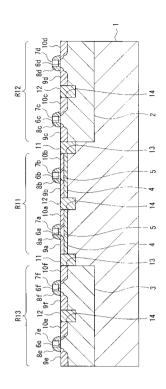

図1は、本発明の第1実施形態に係る半導体装置の構成例を示す断面図である。

図1において、半導体基板1には、SOI形成領域R11およびバルク領域R12、R13が設けられ、バルク領域R12、R13には、ウェル2、3がそれぞれ形成されている。なお、バルク領域R12、R13は、SOI形成領域R11を介して互いに隔てられるようにして半導体基板1に配置することができ、例えば、SOI形成領域R11は、バルク領域R12とバルク領域R13との間に形成することができる。半導体基板1に500mを超える高抵抗基板を用いた場合には、SOI形成領域の絶縁膜4の下の基板抵抗を大きくすることができる。

# [0026]

そして、SOI形成領域R11、バルク領域R12、R13には、SOI形成領域R11およびバルク領域R12内の素子をそれぞれ素子分離する溝14が形成されている。また、SOI形成領域R11とバルク領域R12、R13との境界には、SOI形成領域R11とバルク領域R12、R13とを素子分離する溝13が形成されている。そして、溝13、14内には、埋め込み絶縁体11、12がそれぞれ埋め込まれている。なお、溝13、14内にそれぞれ埋め込まれた埋め込み絶縁体11、12としては、例えば、シリコン酸化膜またはシリコン窒化膜などを用いることができる。

## [0027]

そして、SOI形成領域R11において、半導体基板1上には埋め込み絶縁層4が形成され、埋め込み絶縁層4上には、溝13及び溝14にて素子分離された半導体層5が積層されている。そして、半導体層5上には、ゲート絶縁膜6a、6bをそれぞれ介してゲート電極7a、7bが形成され、ゲート電極7a、7bの側壁にはサイドウォール8a、8bがそれぞれ形成されている。そして、半導体層5には、ゲート電極7aを挟み込むように配置されたソース層9aおよびドレイン層10aが形成されるとともに、ゲート電極7bを挟み込むように配置されたソース層9bおよびドレイン層10bが形成されている。

10

20

30

40

20

30

40

50

#### [0028]

一方、バルク領域 R 1 2 において、ウェル 2 上には、ゲート絶縁膜 6 c、 6 dをそれぞれ介してゲート電極 7 c、 7 d が形成され、ゲート電極 7 c、 7 d の側壁にはサイドウォール 8 c、 8 d がそれぞれ形成されている。そして、ウェル 2 には、ゲート電極 7 c を挟み込むように配置されたソース層 9 c およびドレイン層 1 0 c が形成されるとともに、ゲート電極 7 d を挟み込むように配置されたソース層 9 d およびドレイン層 1 0 d が形成されている。

### [0029]

また、バルク領域 R 1 3 において、ウェル 3 上には、ゲート絶縁膜 6 e 、 6 f をそれぞれ介してゲート電極 7 e 、 7 f が形成され、ゲート電極 7 e 、 7 f の側壁にはサイドウォール 8 e 、 8 f がそれぞれ形成されている。そして、ウェル 3 には、ゲート電極 7 e を挟み込むように配置されたソース層 9 e およびドレイン層 1 0 e が形成されるとともに、ゲート電極 7 f を挟み込むように配置されたソース層 9 f およびドレイン層 1 0 f が形成されている。

### [0030]

なお、半導体基板 1 および半導体層 5 の材質としては、例えば、S i、G e、S i G e 、S i G e G e G i G e G i G e G i G e G i G e G i G e G i G e i G i G e i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i G i

#### [0031]

これにより、バルク領域 R 1 2 、 R 1 3 に形成された複数の回路ブロックを、クロストークノイズ耐性に強いSOI形成領域 R 1 1を介して互いに隔てられるようにして同一半導体基板 1 上に混載することができる。このため、同一半導体基板 1 上に形成された回路ブロック間でのクロストークノイズを抑制しつつ、隣接する回路ブロック間の距離を小さくすることが可能となり、チップサイズの増大を抑制しつつ、様々の機能を 1 チップに搭載することが可能となるとともに、半導体装置の特性を向上させつつ、半導体装置の信頼性を向上させることができる。ここで、半導体基板 1 に高抵抗基板を用いれば、基板クロストークノイズ耐性が、更に向上する。また、SOI形成領域 R 1 1 からの熱放散性を向上させることを可能として、SOI形成領域 R 1 1 からの熱放散性を向上させることができる。

# [0032]

なお、上述した実施形態では、STI(Shallow Trench Isolation)構造にてSOI形成領域R11およびバルク領域R12、R13を素子分離する方法について説明したが、SOI形成領域R11およびバルク領域R12、R13をLOCOS(Local Oxdation Of Silicon)構造にて素子分離するようにしてもよい。

### [0033]

また、SOI形成領域R11には低電圧・低電流駆動デバイスを形成し、バルク領域R12、R13には高耐圧・高電圧駆動デバイスを形成することができる。これにより、低電圧駆動回路と高電圧駆動回路とを同一半導体基板1基板上に混載しつつ、低電圧駆動回路をSOI構造、高電圧駆動回路をバルク構造にて構成することが可能となるとともに、ラッチアップ耐性を強化しつつ、低電圧駆動回路から外部に放出されるノイズをSOI構造にて遮断することが可能となる。このため、チップサイズの増大を抑制しつつ、低電圧駆動回路の高速化および低消費電力化を図ることが可能となるとともに、高電圧駆動回路の高耐圧化および高信頼性化を図ることが可能となる。あるいは、SOI形成領域R11

にはロジック回路やSRAMを形成し、バルク領域R12、R13には静電保護回路やアナログ回路やバイポーラトランジスタを形成するようにしてもよい。

### [0034]

### (2)第2実施形態

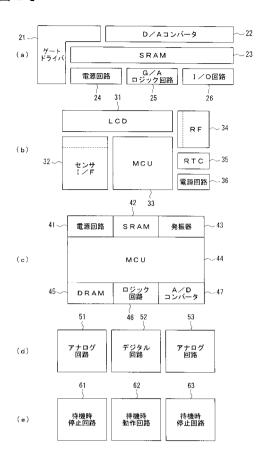

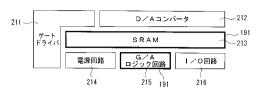

図2は、本発明の第2実施形態に係る半導体装置の構成例を示す平面図である。

図2(a)において、半導体チップには複数の回路ブロックが搭載され、回路ブロックとしてゲートドライバ21、D/Aコンバータ22、SRAM23、電源回路24、ゲートアレイロジック回路25およびI/O回路26が形成されている。ここで、ゲートドライバ21、D/Aコンバータ22、電源回路24およびI/O回路26はバルク領域に配置し、SRAM23およびゲートアレイロジック回路25はSOI形成領域に配置することができる。また、バルク領域に形成された回路ブロックは、SOI形成領域に形成された回路ブロックの少なくとも一辺に接するように配置することができる。また、SOI形成領域に形成された回路ブロックの間に配置することができる。

### [0035]

これにより、SRAM23を持つドライバLSIを1チップにて構成した場合においても、回路ブロック間でのクロストークノイズを抑制しつつ、隣接する回路ブロック間の距離を小さくすることが可能となる。このため、チップサイズの増大を抑制しつつ、ドライバLSIを実現することが可能となるとともに、ドライバLSIの特性を向上させつつ、ドライバLSIの信頼性を向上させることができる。

### [0036]

また、図2(b)において、半導体チップには複数の回路ブロックが搭載され、回路ブロックとして液晶コントローラ31、センサインターフェース回路32、MCU(マイクロコントローラユニット)33、RF(Radio Freqency)回路34、RTC(リアルタイムクロック)回路35、電源回路36が形成されている。ここで、液晶コントローラ31および電源回路36はバルク領域に配置し、MCU33およびRTC回路35はSOI形成領域に配置することができる。また、センサインターフェース回路32およびRF回路34はバルク領域に配置されるとともに、センサインターフェース回路32およびRF回路34の外周の少なくとも一辺にそれぞれ配置されるとともに、他の回路ブロックに接するように配置されたSOI構造がそれぞれ設けられている。

### [0037]

これにより、システムLSIを1チップにて構成した場合においても、回路プロック間でのクロストークノイズを抑制しつつ、回路プロック間の距離を小さくすることが可能となる。このため、チップサイズの増大を抑制しつつ、システムLSIを実現することが可能となるとともに、システムLSIの特性を向上させつつ、システムLSIの信頼性を向上させることができる。ここで、RTC回路及び待機(スタンド・バイ)時に電圧が印加されている回路部分を完全空乏SOI構造にすれば、待機時の消費電力を大幅に削減できる。待機時に電圧が印加されない回路領域をバルク領域に形成しても、待機時の消費電力増加は無い。

### [0038]

また、図2(c)において、半導体チップには複数の回路ブロックが搭載され、回路ブロックとして電源回路41、SRAM42、発振器43、MCU44、DRAM45、ロジック回路46およびA/Dコンバータ47が形成されている。ここで、電源回路41、発振器43、DRAM45およびA/Dコンバータ47はバルク領域に配置し、SRAM42、MCU44およびロジック回路46はSOI形成領域に配置することができる。また、バルク領域に形成された回路ブロックは、SOI形成領域に形成された回路ブロックの少なくとも一辺に接するように配置することができる。また、SOI形成領域に形成された回路ブロックは、バルク領域に形成された回路ブロックの間に配置することができる

40

30

10

20

50

[0039]

20

30

40

50

これにより、システムLSIを1チップにて構成した場合においても、バルク構造を持つ複数の回路プロックを、SOI構造を介して互いに隔てられるようにして同一基板上に混載することが可能となる。このため、回路プロック間でのクロストークノイズを抑制しつつ、回路プロック間の距離を小さくすることが可能となり、チップサイズの増大を抑制しつつ、システムLSIを実現することが可能となるとともに、システムLSIの特性を向上させつつ、システムLSIの信頼性を向上させることができる。

#### [0040]

また、図2(d)において、半導体チップには複数の回路ブロックが搭載され、回路ブロックとしてアナログ回路51、53およびデジタル回路52が形成されている。ここで、アナログ回路51、53はバルク領域に配置し、デジタル回路52はSOI形成領域に配置することができる。また、バルク領域に形成された回路ブロックは、SOI形成領域に形成された回路ブロックの少なくとも一辺に接するように配置することができる。また、SOI形成領域に形成された回路ブロックの間に配置することができる。

### [0041]

これにより、デジタル回路52とアナログ回路51、53とを同一基板上に混載しつつ、デジタル回路52をSOI構造、アナログ回路51、53をバルク構造にて構成することが可能となるとともに、ラッチアップ耐性を強化しつつ、デジタル回路62から外部に放出されるノイズをSOI構造にて遮断することが可能となる。また、アナログ回路51と53との距離が離れており、間にSOI構造が割ってはいるため、アナログ回路ブロック間(51と53間)の基板クロストークノイズ耐性も向上する。このため、チップサイズの増大を抑制しつつ、デジタル回路52の低電圧駆動化、高速化および低消費電力化を図ることが可能となるとともに、アナログ回路51、53の高耐圧化および高信頼性化を図ることが可能となる。

#### [0042]

また、図2(e)において、半導体チップには複数の回路ブロックが搭載され、回路ブロックとして待機時に動作が必要な回路62、及び、待機時に電圧の印加が無い停止回路61、63が形成されている。ここで、待機時動作回路62は、SOI形成領域に配置し、完全空乏SOIデバイスを活用できる。このため、待機時動作回路の電圧を低く設定でき、かつ、待機時リーク電流を抑制できる。それゆえ、待機時のLSI全体の消費電力を大幅に低減できる。また、待機時停止回路61、63は、バルク領域、SOI領域のいずれの領域に形成しても良い。このとき、バルク領域に形成された回路ブロックは、SOI領域に形成された回路ブロックの少なくとも一辺に接するように配置できる。これにより、待機時の消費電力を大幅に削減しつつ、基板クロストークノイズ耐性に優れた半導体装置を提供できる。

## [0043]

# (3)第3実施形態

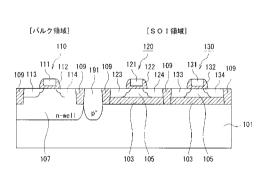

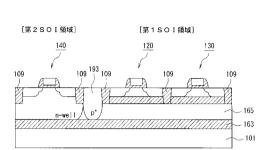

図3は、本発明の第3実施形態に係る半導体装置の構成例を示す断面図である。

図3に示すように、この半導体装置では、半導体基板101内にバルク領域とSOI領域とが設けられている。ここで、バルク領域とは、下地が半導体基板101のみからなる領域のことである。また、SOI領域とは、半導体基板101に絶縁層103を介して半導体層105が形成されている領域のことである。半導体基板101は例えばp型のシリコン(Si)基板であり、絶縁層103は例えばシリコン酸化膜(SiO2)である。また、半導体層105は例えばSiである。このように、バルク領域とSOI領域とを同一基板に有する半導体基板(装置)は、例えばSBSI法によって形成される。

# [0044]

図3に示すように、バルク領域の半導体基板101には例えばn型のウェル107が形成されている。このウェル107の周囲には素子分離膜109が形成されており、素子分離膜109で囲まれた領域にはMIS型のトランジスタ110が形成されている。即ち、ウェル107上にはゲート絶縁膜を介してゲート電極111が形成されており、その両側

の側壁にはサイドウォール 1 1 2 が形成されている。また、ゲート電極 1 1 1 の両側のウェル 1 0 7 にはソース 1 1 3 とドレイン 1 1 4 とが形成されている。

### [0045]

一方、SOI領域の半導体基板101上には、絶縁層103が形成されておりその上に半導体層105が形成されている。SOI領域にも素子分離膜109が形成されており、素子分離膜109で囲まれた領域にMIS型のトランジスタ120、130が形成されている。即ち、SOI領域の一方には、ゲート絶縁膜を介してゲート電極121が形成されており、その両側の側壁にはサイドウォール22が形成されている。また、ゲート電極121の両側の半導体層105にはソース123とドレイン124とが形成されている。同様に、SOI領域の他方には、ゲート絶縁膜を介してゲート電極131が形成されており、その両側の側壁にはサイドウォール32が形成されている。また、ゲート電極131の両側の半導体層105にはソース1133とドレイン134とが形成されている。

#### [0046]

なお、素子分離膜 1 0 9 は例えば S i O  $_2$  であり、 S T I ( shallow trenchisolation) 法又は L O C O S ( local oxidation of silicon) 法によって形成されたものである。また、図示しないゲート絶縁膜は例えば S i O  $_2$ 、シリコン酸化窒化膜 ( S i O N )、シリコン窒化膜 ( S i N )、又はこれらの組合せ等である。ゲート電極 1 1 1、2 1、3 1 は例えばリン又はボロン等の導電型不純物を含む多結晶シリコン等である。サイドウォール 1 1 2、1 2 2、1 3 2 は例えば S i O  $_2$  である。

以下では説明の便宜上から、バルク領域に形成されたMIS型のトランジスタをバルクトランジスタと呼ぶ。また、SOI領域に形成されたMIS型のトランジスタをSOIトランジスタと呼ぶ。

#### [0047]

ところで、この半導体装置では、バルクトランジスタ110とSOIトランジスタ120との間の半導体基板101に電位固定用の不純物拡散層191が形成されている。この不純物拡散層191の導電型は例えばp型であり、半導体装置を動作させる際には不純物拡散層191に逆バイアス(即ち、負の電位)を印加してその電位を固定する。このような構成であれば、バルクトランジスタ110とSOIトランジスタ120との間で生じる電気力線を不純物拡散層191で遮断することができ、両トランジスタ110、120間でのクロストークノイズを抑制することができる。

# [0048]

例えば、SOIトランジスタ120が低電圧駆動のデジタル回路を構成する回路素子であり、バルクトランジスタ110が高電圧駆動回路(あるいはアナログ回路)を構成する回路素子である場合、不純物拡散層191に逆バイアスを印加してその電位を固定することによって、バルクトランジスタ110からの高電圧ノイズ電気力線(即ち、ソース又はドレインに高電圧を印加することによって生じるノイズ)を不純物拡散層191で終端することができる。また、逆バイアス印加によって不純物拡散層191から半導体基板101側へ空乏層が拡がるので、空乏層によってバルクトランジスタ110からの高電界が遮断される。従って、ゲート電極121直下の半導体層105のうちの絶縁層103近傍部位の反転を防ぐことができる。

### [0049]

また、デジタル回路の急峻な信号スイッチングは多くのノイズを発生するが、SOIトランジスタ120、130は絶縁層103によって半導体基板101から分離されているため、当該ノイズの半導体基板101側への伝達を抑制することができる。さらに、バルクトランジスタ110とSOIトランジスタとの間には素子分離膜109が設けられており、DC電流パスがない。

このため、バルクトランジスタ110とSOIトランジスタ120、130との間での クロストークノイズを抑制することができ、低電圧駆動のデジタル回路と高電圧駆動回路 (あるいはアナログ回路)のそれぞれの誤作動を防止することができる。これにより、半 10

20

30

40

導体装置の動作信頼性を高めることができる。

### [0050]

なお、半導体基板101には500 cmを超える高抵抗基板を用いることが好ましい。このような構成であれば、SOI領域の絶縁層103下の基板抵抗を大きくすることができるので、半導体装置のクロストークノイズ耐性をよりいっそう向上させることが可能である。

この第3実施形態では、不純物拡散層191が本発明11~16の「第1不純物拡散層」に対応し、バルクトランジスタ110が本発明11~16の「バルク領域に形成された回路素子」に対応し、SOIトランジスタ120、130が本発明11、13~16の「SOI領域に形成された回路素子」に対応している。

[0051]

### (4)第4実施形態

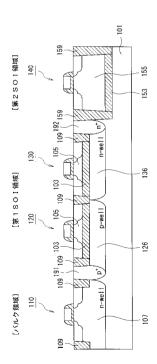

図4は、本発明の第4実施形態に係る半導体装置の構成例を示す断面図である。図4において、図3と同一の構成を有する部分には同一の符号を付し、その詳細な説明は省略する。

図4に示すように、この半導体装置では、半導体基板101内にバルク領域と第1、第2SOI領域とが設けられている。バルク領域の半導体基板101にはn型のウェル107が形成されている。このウェル107の周囲には素子分離膜109が形成されており、素子分離膜109で囲まれた領域にバルクトランジスタ110が形成されている。

# [0052]

また、第1SOI領域の半導体基板101上には絶縁層103が形成されておりその上に半導体層105が形成されている。この第1SOI領域にも素子分離膜109が形成されており、素子分離膜109で囲まれた領域に例えば完全空乏型(fully depleted)のSOIトランジスタ120、30が形成されている。

ここで、完全空乏型のSOIトランジスタは、半導体層の厚さが例えば50[nm]以下と小さく、ソース / ドレインに挟まれたボディが全て空乏化されている。完全空乏型では、急峻なサブスレショルド特性が得られ、オフリーク電流を抑制しつつ閥値電圧を低くできるので、低電圧で高速動作が可能である。このような特性から、完全空乏型のトランジスタは低電圧駆動のロジック回路の回路素子として使用されることが多い。

# [0053]

特に、待機時に動作するRTC回路や待機時に電圧が印加される回路を第1SOI領域に形成することにより、待機時の消費電力を大きく削減できる。

また、第2SOI領域には絶縁層153が形成されておりその上に半導体層155が形成されている。この第2SOI領域には素子分離膜109よりも基板方向に深く形成された素子分離膜159が形成されており、素子分離膜159で囲まれた領域に例えば部分空乏型(partially depleted)のSOIトランジスタ140が形成されている。

### [0054]

ここで、部分空乏型のSOIトランジスタは、半導体層の厚さが例えば100[nm]以上と大きく、ボディの底部が空乏化されていない。部分空乏型のSOIトランジスタはサブスレショルド特性がバルクトランジスタと同程度となり、低消費電力の観点では完全空乏型ほどの効果は望めない。その一方で、部分空乏型は、完全空乏型と比べて、耐圧特性に優れる。このような特性から、部分空乏型のトランジスタは高電圧駆動回路の回路素子として使用されることが多い。

第2 S O I 領域の絶縁層 1 5 3 は例えば S i O $_2$ であり、半導体層 1 5 5 は例えば S i である。さらに、第2 S O I 領域を囲む素子分離膜 1 5 9 は例えば S i O $_2$ であり、 S T I 法又は L O C O S 法によって形成されたものである。

### [0055]

ところで、この半導体装置では、バルクトランジスタ110と完全空乏型のSOIトランジスタ120との間に例えばp型の不純物拡散層191が形成されている。また、完全

10

20

30

40

20

30

40

50

空乏型のSOIトランジスタ130と部分空乏型のSOIトランジスタ140との間には例えばn型の不純物拡散層192が形成されている。さらに、SOIトランジスタ120直下の絶縁層103下の半導体基板101にはp型のウェル126が形成されており、SOIトランジスタ130直下の絶縁層下の半導体基板101にはn型のウェル136が形成されている。

# [0056]

図4に示すように、半導体基板101の内部で不純物拡散層191とウェル126とが接合しており、不純物拡散層191のほうがウェル126よりもp型の不純物濃度は高くなっている。また、半導体基板101の内部で不純物拡散層192とウェル136とが接合しており、不純物拡散層192のほうがウェル136よりもn型の不純物濃度は高くなっている。そして、この半導体装置を動作させる際には、不純物拡散層191に逆バイアス(即ち、負の電位)を印加して不純物拡散層191とウェル126との電位を固定すると共に、不純物拡散層192に逆バイアス(即ち、正の電位)を印加して不純物拡散層192とウェル136の電位を固定する。

このような構成であれば、バルクトランジスタ110とSOIトランジスタ120との間で生じる電気力線を不純物拡散層191で遮断することができる。また、SOIトランジスタ130とSOIトランジスタ140との間で生じる電気力線を不純物拡散層192で遮断することができる。

### [0057]

さらに、この半導体装置では、SOIトランジスタ120直下の絶縁層103下の半導体基板101にウェル126を備えているので、バルク領域からSOIトランジスタ120の下側へ回り込んでくる電気力線を遮断したり、SOIトランジスタ120で発生するノイズの半導体基板101側への伝達を防いだりすることが容易である。同様に、この半導体装置は、SOIトランジスタ130直下の絶縁層103下の半導体基板101にウェル136を備えているので、第2SOI領域からSOIトランジスタ130の下側へ回り込んでくる電気力線を遮断したり、SOIトランジスタ130で発生するノイズの半導体基板101側への伝達を防いだりすることが容易である。

### [0058]

この第4実施形態では、不純物拡散層191が本発明11~15の「第1不純物拡散層」に対応し、バルクトランジスタ110が本発明11~15の「バルク領域に形成された回路素子」に対応している。また、SOIトランジスタ120、130が本発明11~15の「(第1)SOI領域に形成された回路素子」に対応し、SOIトランジスタ140が本発明12~15の「第2SOI領域に形成された回路素子」に対応している。さらに、不純物拡散層192が本発明12~15の「第2不純物拡散層」に対応している。

# [0059]

## (5)第5実施形態

図5は、本発明の第5実施形態に係る半導体装置の構成例を示す断面図である。図5において、図3又は図4と同一の構成を有する部分には同一の符号を付し、その詳細な説明は省略する。

図5に示すように、この半導体装置では、半導体基板101内に第1、第2SOI領域が設けられており、半導体基板101上には部分的に第1絶縁層163と第1半導体層165とが積層されている。第2SOI領域では第1半導体層165に部分空乏型のSOIトランジスタ140が形成されている。また、第1SOI領域では、第1半導体層165上にさらに第2絶縁層103と第2半導体層105とが積層されており、この第2半導体層105に完全空乏型のSOIトランジスタ120、130が形成されている。

# [0060]

そして、この半導体装置では、第1SOI領域のSOIトランジスタ120と、第2SOI領域のSOIトランジスタ140との間に電位固定用の不純物拡散層193が形成されている。この不純物拡散層193の導電型は例えばp型である。半導体装置を動作させる際には不純物拡散層193に逆バイアス(即ち、負の電位)を印加してその電位を固定

20

30

40

50

する。このような構成であれば、完全空乏型のSOIトランジスタ120と、部分空乏型のSOIトランジスタ140との間で生じる電気力線を不純物拡散層193で遮断することができるので、両トランジスタ120、40間でのクロストークノイズを抑制することができる。

この第5実施形態では、半導体基板101が本発明17の「支持基板」に対応し、SOIトランジスタ120、130が本発明17の「第1SOI領域に形成された回路素子」に対応し、SOIトランジスタ140が本発明17の「第2SOI領域に形成された回路素子」に対応している。

### [0061]

以上、第3~第5実施形態では、回路ブロック内のSOI構造の周辺に電位固定用の不純物拡散層191、192、193やウェル126、136を形成する。これら不純物拡散層やウェルの電位を固定することにより、周辺回路ブロックからの高電圧ノイズ電気力線を終端し、ボックス(即ち、絶縁層)上のSOI層(即ち、半導体層)裏面の反転を防ぐ。また、デジタル回路の急峻な信号スイッチングは半導体基板101に多くのノイズを発生させるが、本発明では、これらのノイズをボックスや素子分離膜が阻止する。

#### [0062]

さらに、本発明では半導体基板101には500 ・cmより高い抵抗の基板を用いることが好ましい。高抵抗基板上のSOI構造は、クロストークノイズ耐性をさらに強化する。これにより、クロストークノイズ耐性に優れ、異なる電圧駆動の回路ブロック、或いは、デジタルとアナログとを混載した回路ブロックが安定した動作を行い、高精度、高速動作・低消費電力、しかも安価な半導体装置を提供することができる。

### [0063]

## (6)第6実施形態

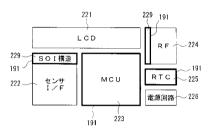

図6は、本発明の第6実施形態に係る半導体装置の構成例を示す平面図である。図6において、図3と同一の構成を有する部分には同一の符号を付し、その詳細な説明は省略する。

図6において、半導体基板(半導体チップ)には複数の回路ブロックが搭載され、回路ブロックとしてゲートドライバ211、D/Aコンバータ212、SRAM213、電源回路214、ゲートアレイロジック回路215及びI/O回路216が形成されている。ここで、ゲートドライバ211、D/Aコンバータ212、電源回路214及びI/O回路216はバルク領域に配置されており、SRAM213及びゲートアレイロジック回路215はSOI領域に配置されている。また、バルク領域に形成された(即ち、バルク構造を持つ)回路ブロックは、SOI領域に形成された(即ち、SOI構造を持つ)回路ブロックの少なくとも一辺に隣りあうように配置されている。また、SOI構造を持つ回路ブロックの間に配置されている。

### [0064]

これにより、SRAM213を持つドライバLSIを1チップにて構成した場合においても、回路ブロック間でのクロストークノイズを抑制しつつ、隣接する回路ブロック間の 距離を小さくすることが可能となる。

また、この半導体装置では、SOI構造を持つSRAM213の周囲の半導体基板には電位固定用の不純物拡散層191が形成されており、この不純物拡散層191によってSRAM213は平面視で囲まれている。同様に、SOI構造を持つゲートアレイロジック回路215の周囲の半導体基板には電位固定用の不純物拡散層191が形成されており、この不純物拡散層191によってゲートアレイロジック回路215は平面視で囲まれている。そして、ドライバLSIを動作させる際には、不純物拡散層191に逆バイアスを印加してその電位を固定する。

### [0065]

このような構成であれば、SOI構造を持つSRAM213やゲートアレイロジック回路215と、バルク構造を持つ回路ブロックとの間で生じる電気力線を不純物拡散層19 1で遮断することができ、双方の間でクロストークノイズを抑制することができる。これ

20

30

40

50

により、ドライバLSIの誤作動を防止することができ、その動作信頼性を向上させることができる。

第6実施形態では、SRAM213やゲートアレイロジック回路215が本発明18の「第1回路ブロック」に対応している。また、ゲートドライバ211、D/Aコンバータ 212、電源回路214及びI/O回路216が本発明18の「第2回路ブロック」及び 、本発明21の「周辺回路ブロック」に対応している。

#### [0066]

# (7)第7実施形態

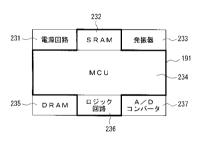

図7は、本発明の第7実施形態に係る半導体装置の構成例を示す平面図である。図7において、図3と同一の構成を有する部分には同一の符号を付し、その詳細な説明は省略する。

図7において、半導体基板(半導体チップ)には複数の回路ブロックが搭載され、回路ブロックとしてLCD(液晶コントローラ)221、センサインターフェース回路222、MCU(マイクロコントローラユニット)223、RF(Radio Freqency)回路224、RTC(リアルタイムクロック)回路225、電源回路226が形成されている。ここで、LCD221、センサインターフェース回路222、RF回路224及び電源回路226はバルク領域に配置され、MCU223及びRTC回路225はSOI領域に配置されている。

### [0067]

さらに、センサインターフェース回路 2 2 2 及び R F 回路 2 2 4 の外周の少なくとも一辺を含む領域には、他の回路プロックと隣りあうように S O I 構造体 2 2 9 がそれぞれ設けられている。ここで、 S O I 構造体とは、半導体基板上に絶縁層と半導体層とが積層されてなる構造体のことである。これにより、システム L S I を 1 チップにて構成した場合においても、回路ブロック間でのクロストークノイズを抑制しつつ、回路ブロック間の距離を小さくすることが可能となる。

### [0068]

また、この半導体装置では、SOI領域に配置された(即ち、SOI構造を持つ)MCU223や、RTC回路225の周囲の半導体基板にはそれぞれ電位固定用の不純物拡散層191が形成されており、この不純物拡散層191によってMCU223やRTC回路225は平面視で個々に囲まれている。さらに、SOI構造体229の周囲の半導体基板にも当該SOI構造を個々に囲むように電位固定用の不純物拡散層191が形成されている。

# [0069]

このような構成であれば、SOI構造を持つMCU223やRTC回路225と、バルク構造を持つ回路ブロックとの間で生じる電気力線を不純物拡散層191で遮断することができ、双方の間でクロストークノイズを抑制することができる。これにより、システムLSIの誤作動を防止することができ、その動作信頼性を向上させることができる。

また、RTC回路など待機時に電圧が印加される回路群をSOI領域に設け、完全空乏SOIトランジスタを適用することにより、待機時の消費電力を大きく削減できる。

### [0070]

第7実施形態では、MCU223及びRTC回路225が本発明18の「第1回路ブロック」に対応している。また、LCD221、センサインターフェース回路222、MCU223、RF回路224、RTC回路225、電源回路226が本発明18の「第2回路ブロック」に対応している。さらに、MCU223が本発明20の「MCUコア」に対応している。また、センサインターフェース回路222及びRF回路224が本発明20の「第1周辺回路ブロック」に対応し、LCD221が本発明20の「第2周辺回路ブロック」に対応している。

# [0071]

### (8)第8実施形態

図8は、本発明の第8実施形態に係る半導体装置の構成例を示す平面図である。図7に

おいて、図3と同一の構成を有する部分には同一の符号を付し、その詳細な説明は省略する。

図8において、半導体基板(半導体チップ)には複数の回路ブロックが搭載され、回路ブロックとして電源回路231、SRAM232、発振器233、MCU234、DRAM235、ロジック回路236及び237が形成されている。ここで、電源回路231、発振器233、DRAM235及び237はバルク領域に配置され、SRAM232、MCU234及びロジック回路236はSOI領域に配置されている。また、バルク領域に形成された(即ち、バルク構造を持つ)回路ブロックは、SOI領域に形成された(即ち、SOI構造を持つ)回路ブロックの少なくとも一辺と隣りあうように配置されている。さらに、SOI構造を持つ回路ブロックの少なくとも一辺と隣りあうように配置されている。

[0072]

これにより、システムLSIを1チップにて構成した場合においても、バルク構造を持つ複数の回路ブロックを、SOI構造を介して互いに隔てられるようにして同一基板上に混載することが可能となる。このため、回路ブロック間でのクロストークノイズを抑制しつつ、回路ブロック間の距離を小さくすることが可能となる。

また、この半導体装置では、SOI構造を持つ回路ブロックの周囲の半導体基板に電位固定用の不純物拡散層191が形成されており、この不純物拡散層191によってSRAM232、MCU234及びロジック回路236は平面視で一まとめに囲まれている。

[0073]

このような構成であれば、SOI構造を持つ回路ブロックとバルク構造を持つ回路ブロックとの間で生じる電気力線を不純物拡散層191で遮断することができ、双方の間でクロストークノイズを抑制することができる。これにより、システムLSIの誤作動を防止することができ、その動作信頼性を向上させることができる。

第8実施形態では、SRAM232、MCU234及びロジック回路236が本発明18の「第1回路ブロック」に対応している。また、電源回路231、発振器233、DRAM235及び237が本発明18の「第2回路ブロック」及び、本発明19の「周辺回路ブロック」に対応している。さらに、MCU234が本発明19の「MCUコア」に対応し、DRAMが本発明19の「メモリ回路」に対応し、発信器が本発明19の「発振回路」に対応している。

[0074]

以上、第6~第8実施形態では、(薄い)SOI構造を持つ低電圧駆動MCUやSRAMと、バルク構造(或いは、厚いSOI構造)を持つ高電圧駆動回路(或いはアナログ回路)の各ブロック間に、電位固定用の不純物拡散層191を配置している。ボックス103と素子分離膜109とによって、低電圧駆動のデジタル回路ブロックは、高電圧で駆動するドライバ回路ブロック、DRAM、Flashメモリ回路ブロック等と電気的に遮断される。

[0075]

このため、デジタル回路が発するクロストークノイズが半導体基板101に侵入せず、アナログ回路の特性劣化が生じない。特に、高抵抗Si基板を用いると、クロストークノイズ耐性が向上する。一方、逆バイアス印加によって不純物拡散層191から半導体基板101側へ拡がる空乏層によって、電界も遮断される。このため、高電圧駆動回路ブロックから低電圧駆動回路ブロックへの電界ノイズが抑制され、高精度かつ高信頼性な低電圧・低パワーデジタル回路動作が可能となる。以上、本発明によれば、高精度・低電圧駆動回路ブロックと、高電圧駆動回路ブロックとを混載し、耐クロストークノイズに優れた高信頼性システムLSI半導体装置を提供することができる。

【図面の簡単な説明】

[0076]

【図1】第1実施形態に係る半導体装置の構成例を示す断面図。

【図2】第2実施形態に係る半導体装置の構成例を示す平面図。

10

20

30

40

20

- 【図3】第3実施形態に係る半導体装置の構成例を示す断面図。

- 【図4】第4実施形態に係る半導体装置の構成例を示す断面図。

- 【図5】第5実施形態に係る半導体装置の構成例を示す断面図。

- 【図6】第6実施形態に係る半導体装置の構成例を示す平面図。

- 【図7】第7実施形態に係る半導体装置の構成例を示す平面図。

- 【図8】第8実施形態に係る半導体装置の構成例を示す平面図。

#### 【符号の説明】

# [0077]

R 1 1 S O I 形成領域、 R 1 2 、 R 1 3 バルク領域、 1 半導体基板、 2 、 3 ウ ェル、4 埋め込み絶縁層、5 半導体層、6 a ~ 6 f ゲート絶縁膜、7 a ~ 7 f ゲ ート電極、8a~8f サイドウォールスペーサ、9a~9f ソース層、10a~10 f ドレイン層、1.1、1.2 埋め込み絶縁体、1.3、1.4 素子分離用溝、2.1 ゲー トドライバ、22 D/Aコンバータ、23、42 SRAM、24 電源回路、25 ゲートアレイロジック回路、26 I/O回路、31 液晶コントローラ、32 センサ インターフェース回路、33、44 MCU、34 RF回路、35 RTC回路、36 、4.1 電源回路、4.3 発振器、4.5 DRAM、4.6 ロジック回路、4.7 A/D コンバータ、51、53 アナログ回路、52 デジタル回路、61、63 待機時停止 回路、62 待機時動作回路、

101 半導体基板、103、153 絶縁層(ボックス)、105、155 半導体 層(SOI層)、107 ウェル、109、159 素子分離膜、110 バルクトラン ジスタ、111、121、131 ゲート電極、113、123、133 ソース、11 4、124、134 ドレイン、120、130 (完全空乏型) SOIトランジスタ、 1 2 6 、 1 3 6 (電位固定用の)ウェル、1 4 0 (部分空乏型) S O I トランジスタ 、191~193 (電位固定用の)不純物拡散層、211 ゲートドライバ、212 D / A コンバータ、 2 1 3 、 2 3 2 S R A M 、 2 1 4 、 2 2 6 、 2 3 1 電源回路、 2 1 5 ゲートアレイロジック回路、2 1 6 I/O回路、2 2 1 LCD、2 2 2 セン サインターフェース回路、 2 2 3 、 2 3 4 M C U 、 2 2 4 R F 回路、 2 2 5 R T C 回路、233 発信器、235 DRAM、236 ロジック回路、237 A/Dコン バータ

【図1】

【図2】

【図3】

【図4】

# 【図5】

# 【図6】

# 【図7】

# 【図8】

# フロントページの続き

(51) Int.CI. F I

H 0 1 L 27/04 (2006.01) H 0 1 L 27/04 A H 0 1 L 27/04 H

(56)参考文献 特開2006-012995(JP,A)

国際公開第2006/001915(WO,A2)

特開2004-207694(JP,A)

特開平09-223802(JP,A)

特開平09-162417(JP,A)

特開2001-345428(JP,A)

特開2004-153175(JP,A)

特開2003-258212(JP,A)

特開2003-100900(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/76

H01L 21/762

H01L 21/822

H01L 21/8234

H01L 27/04

H01L 27/08

H01L 27/088