# (19) 대한민국특허청(KR) (12) 등록특허공보(B1)

| (51) Int. CI. <sup>6</sup><br>G11C 11/40 |                                                | (45) 공고일자<br>(11) 등록번호<br>(24) 등록일자 | 1999년07월15일<br>10-0207971<br>1999년04월14일 |

|------------------------------------------|------------------------------------------------|-------------------------------------|------------------------------------------|

| (21) 출원번호<br>(22) 출원일자                   | 10-1995-0003656<br>1995년02월24일                 | (65) 공개번호<br>(43) 공개일자              | 특 1995-0025780<br>1995년09월 18일           |

| (30) 우선권주장                               | 94-027103 1994년02월25일 일                        | 일본(JP)                              |                                          |

| (73) 특허권자                                | 가부시끼가이샤 도시바 니/                                 |                                     |                                          |

| (72) 발명자                                 | 일본국 가나가와껭 가와사끼시<br>스기우라 요시히사                   | 사이와이꾸 호리가오                          | ·쪼 72반지                                  |

|                                          | 일본국 가나가와현 가와사키시<br>가이샤 도시바 연구개발센터내<br>이와타 요시히사 |                                     | I도시바정 1번지 가부시키                           |

|                                          | 일본국 가나가와현 가와사키시<br>가이샤 도시바 연구개발센터내<br>이마미야 겐이치 |                                     | I도시바정 1번지 가부시키                           |

| (74) 대리인                                 | 일본국 가나가와현 가와사키시<br>가이샤 도시바 연구개발센터내<br>김윤배, 이세진 |                                     | I도시바정 1번지 가부시키                           |

| <i>11171 • 710</i> <b>7</b>              |                                                |                                     |                                          |

#### 심사관 : 김용주

## (54) 전위 전송회로 및 이를 이용한 반도체 장치

## 요약

본 발명은, 테스트시에 고전위가 인가되는 테스트 제어패드(31)와, 테스트시에 신호레벨이 전원전위 보다도 높은 테스트전위가 인가되는 테스트 신호패드(32), 테스트 제어패드(31)에 접속되고, 해당 테스트 제어패드에 인가된 고전위를 검출하여 테스트 제어신호(TEST)를 발생하는 고전위 검출회로(1), 전원이 테스트 제어패드(31)에서 공급되고, 테스트 제어신호의 진폭레벨을 시프트시켜 고레벨이 고전위인 구동신호를 출력하는 레벨시프트회로(2), 드레인이 테스트 신호패드(32)에 접속되어 게이트가 구동신호에 의해 구동되는 MOS트랜지스터(Q3)로 이루어지고, MOS트랜지스터의 소스에서 테스트전위를 내부로 전송하는 것을 특징으로 하는 테스트전위 전송회로.

본 발명을 이용하면, 승압회로를 필요로 하지 않는 낮은 점유면적의 테스트 전위전송회로를 제공할 수 있다.

## 대표도

## 명세서

[발명의 명칭]

전위 전송회로 및 이를 이용한 반도체장치

[도면의 간단한 설명]

제1도는 본 발명의 실시예에 따른 테스트전위 전송회로를 도시한 회로도.

제2도는 본 발명의 실시예에 의한 반도체장치의 회로구성을 도시한 회로구성도.

제3도는 본 발명의 실시예중 승압회로의 회로구성을 도시한 회로도.

제4도는 본 발명의 실시예중 행디코더 및 메모리셀의 회로구성을 도시한 회로도이다.

\* 도면의 주요부분에 대한 부호의 설명

1 : 고전위 검출회로 11 : 인버터

12 : 인버터 2 : 레벨시프트회로 21 : 인버터 31 : 테스트 제어패드

32 : 테스트 신호패드 Q : 트랜지스터

[발명의 상세한 설명]

[산업상의 이용분야]

본 발명은 테스트신호 전송회로에 관한 것으로, 특히 테스트시에 워드선에 인가하는 테스트신호를 전송하는 테스트신호 전송회로를 갖춘 반도체 기억장치에 관한 것이다.

[종래의 기술 및 그 문제점]

저전원전압에서 동작하는 불휘발성 반도체 메모리는, 독출시에 충분한 셀전위를 얻기 위해 워드선에 칩 내에서 승압한 승압전위를 인가하고 있었다.

이 경우, 승압전위는 리미터회로에 의해 결정되는 전위로 고정되고, 외부로부터 제어하는 것은 불가능하다. 그러나, 디바이스 평가에 있어서는, 워드선에 더 높은 전위를 인가할 필요가 있다. 이 때문에, 칩 내부에서 전원전압을 승압하고, 이 전압을 워드선에 공급할 뿐만 아니라, 이와는 별도로 칩 외부로부터임의의 레벨 테스트신호를 공급할 필요가 있다.

외부에서 임의의 레벨 테스트신호를 공급하기 위해서는 테스트전위 전송회로가 필요해진다. 이것은 통상, 테스트전위가 인가되는 테스트 신호패드에 스위칭용 MOS트랜지스터의 드레인을 접속하여 이루어지고, 이 MOS트랜지스터의 게이트는 내부승압한 전위가 공급된다. 내부승압한 전위를 공급하는 이유는 MOS트랜지스 터의 임계치분의 레벨시프트를 방지하기 위해서이고, 게다가 전원 전위 보다도 고전위의 테스트신호를 전 송하기 위해서이다. 이 때문에, 테스트 신호 공급용으로 새로운 내부승압회로를 설치할 필요가 있다.

상술한 바와 같이, 종래의 테스트전위 전송회로는 테스트신호 공급용으로 새로운 내부승압회로가 필요하게 되고, 이 승압회로는 용량소자를 많이 이용해 비교적 큰 면적을 점유하기 때문에 칩 면적의 증대를 일으켰다.

[발명의 목적]

본 발명은 상기한 점을 감안하여 이루어진 것으로, 상기한 결점을 제거하고, 승압회로를 필요로 하지 않는 전위 전송회로를 제공함에 그 목적이 있다.

[발명의 구성]

상기 목적을 달성하기 위한 본 발명은, 제1패드와, 제2패드, 상기 제1패드에 연결되고, 상기 제1패드에 검출된 고전압신호에 따라 제어신호를 발생하는 전압검출회로, 이 전압검출회로에 연결되고, 상기 제어신호에 따라 구동신호를 발생하는 레벨시프트회로, 상기 레벨시프트회로에 의해 발생된 구동신호에 의해 MOS트랜지스터의 게이트가 구동되도록 상기 레벨시프트회로에 연결된 게이트와 상기 제2패드에 연결된 드레인으로 이루어진 MOS트랜지스터 및, 상기 제어신호에 의해 제어된 내부회로를 구비하여 구성되고, 상기레벨시프트회로의 전원단자는 패드에 접속되고, 상기 내부회로는 승압전위로 외부적에서 공급된 전원전위까지 높이기 위한 전압 승압회로이며, 상기 전압 승압회로에 의해 발생된 전압신호와 충돌을 방지하기 위해 상기 전압 증압회로의 동작이 상기 제어신호에 의해 제어되는 것을 특징으로 하는 반도체장치를 제공한다.

또한, 제어노드와, 신호노드, 상기 제어노드에 접속되고, 상기 제어노드에 고전압신호가 존재하는지를 나타내는 디지털 제어신호값을 발생하는 전압검출회로, 상기 고전압신호가 상기 제어노드에 존재하는 것을 상기 디지털 제어신호가 나타낼 경우, 상기 제어신호의 논리레벨을 시프팅함으로써 구동신호를 발생하기 위한 레벨시프트회로 및, 상기 신호노드에 연결된 드레인단자와 상기 레벨시프트회로에 연결된 게이트단자를 갖춘 MOS트랜지스터를 구비하여 구성되고, 상기 MOS트랜지스터의 게이트단자는 상기 레벨시프트회로에 의해 부생된 구동신호에 의해 구동되고, 상기 고전압신호가 상기 제어노드에 존재할 경우, 상기 레벨시프트회로에 의해 발생된 구동신호가 사실상 상기 제어노드와 동일한 레벨이도록 상기 레벨시프트회로의 전력단자가 상기 제어노드에 접속되고, 상기 디지털 제어신호는 기준전위 또는 전원전위이고, 상기 고전압신호가 상기 제어노드에 접속되고, 상기 디지털 제어신호는 기준전위 또는 전원전위이고, 상기 고전압신호가 상기 제어노드에 존재할 경우, 구동신호의 레벨( $V_{drv}$ )이 상기 전원전위 보다도 크도록 상기 고전압신호가 상기 제어노드에 존재할 경우, 구동신호의 레벨( $V_{drv}$ )에서 N채널 MOS트랜지스터의 임계전압( $V_{th}$ )을 뺀 것 보다도 작아( $V_{s}$   $\langle V_{drv} - V_{th}$ )지는 동안에는 사실상 전압강하 없이 상기 MOS트랜지스터의 소스단자에 상기 신호노드에 존재하는 신호가 전송되는 N채널 MOS트랜지스터인 것을 특징으로 하는 전위전송회로를 제공한다.

### [작용]

상기와 같이 구성된 본 발명은, 테스트모드의 제어에 이용하는 테스트 제어신호를 칩 외부로부터 입력하

는 고전압을 검출함으로써 생성한다. 이와 동시에, 이 고전압을 레벨시프트회로의 전원으로서 이용한다. 이와 같이, 외부로부터 인가하는 고전압을 신호 및 전원의 양자로서 이용하기 때문에 종래와 같은 승압회 로는 필요 없게 된다. 이 결과, 칩 면적이 대폭 줄어든다.

레벨시프트회로의 출력인 구동신호는 고레벨이 외부로부터 테스트 제어패드에서 입력한 고전위이기 때문에 이 패드에 인가하는 전위가 충분히 높다면, MOS트랜지스터의 임계치가 떨어짐(MOS트랜지스터의 임계치에 상당하는 분만큼, 게이트・소스 사이에 생기는 전압강하) 없이 테스트전위를 내부회로로 전송하는 것이 가능해진다.

또한, 본 발명에서 제공하는 제2수단을 이용하면, 테스트전위가 디코더회로를 매개로 워드선에 인가된다. 이 결과, 워드선의 전위를 임의로 제어시키는 것이 가능해진다.

또한, 본 발명에서 제공하는 제3수단을 이용하면, 테스트 제어신호는 고전위에서는 없기 때문에 테스트시에 내부회로의 제어신호로서 이용할 수 있다.

#### [실시예]

이하, 예시도면을 참조하여 본 발명에 따른 실시예를 상세히 설명한다.

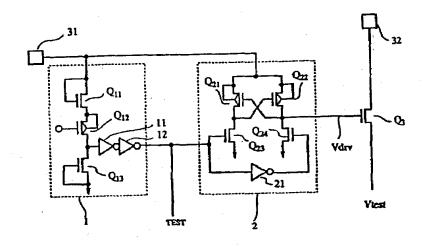

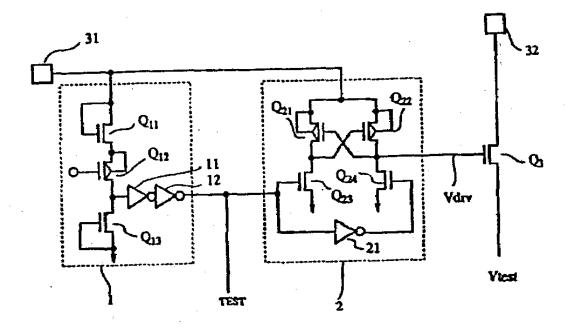

제1도는 본 발명의 테스트전위 전송회로를 상세히 도시한 회로구성도이다.

즉, 테스트시에 고전위가 인가되는 테스트 제어패드(31)와, 테스트시에 신호레벨이 전원전위 보다도 높은 테스트전위가 인가되는 테스트 신호패드(32), 테스트 제어패드(31)에 접속되고, 테스트 제어패드(31)에 인가된 고전위를 검출해 테스트 제어신호(TEST)를 발생하는 고전위 검출회로(1), 전원이 테스트 제어패드(31)에서 공급되고, 테스트 제어신호(TEST)의 진폭레벨을 시프트시킨 구동신호(Vdrv)를 출력하는 레벨시 프트회로 및, 드레인이 테스트 신호패드(32)에 접속되어 게이트가 구동신호(Vdrv)에 의해 구동되는 MOS트 랜지스터로 이루어진다.

고전압 검출회로(1)는 N채널 트랜지스터(Q11)와, P채널 트랜지스터(Q12) 및, N채널 트랜지스터(Q13)를 테스트 제어패드(31)와 전지전위 사이에 직렬 접속하여 이루어지고, P채널 트랜지스터(Q12) 및 N채널 트랜지스터(Q13)의 접속점에 인버터 11 및 인버터 12가 접속되어 있다. 트랜지스터(Q11,Q12,Q13)는 테스트 제어패드(31)에 인가되는 전압의 강압 및 분압을 행하고, 인버터(11,12)는 파형정형을 행하는(내부전원의 진폭레벨로 정형한다) 테스트 제어신호(TEST)를 출력한다. 테스트 제어패드(31)에 인가되는 고전압은 「신호」로서 이용되고 있다.

레벨시프트회로(2)는 P채널 트랜지스터(Q21,Q22)와, N채널 트랜지스터(Q23,Q24), 더욱이 트랜지스터(Q23,Q24)를 상보적으로 구동하기 위해 인버터(21)로 이루어진다. 트랜지스터(Q21,Q22)의 소스는 공히 테스트 제어패드(31)에 접속되어 있고, 레벨시프트회로(2)의 전원전압은 테스트 제어패드에서 공급되며, 테스트 제어신호(TEST)의 진폭레벨을 시프트시킨 구동신호(Vdrv)는 테스트 제어패드(31)에 인가되는 고전압의 레벨까지 레벨시프트된다. 테스트 제어패드(31)에 인가되는 고전압은 「전원」으로서 이용되고 있다.

트랜지스터(Q3)의 게이트에는 구동신호(Vdrv)가 공급되고, 테스트 신호패드(32)에 인가한 테스트전위가 내부로 Vtest로서 도입된다.

이와 같이 구성함으로써, 테스트모드의 제어에 이용하는 테스트 제어신호를 칩 외부로부터 입력하는 고전 압을 검출하는 것에 의해 생성한다. 이와 동시에, 이 고전압을 레벨시프트회로의 전원으로서 이용한다. 결국, 외부로부터 인가하는 고전압을 신호 및 전원의 양자로서 이용하기 때문에 종래와 같은 승압회로는 필요 없게 된다. 이 결과, 칩 면적이 대폭 줄어든다.

또한, 레벨시프트회로의 출력인 구동신호는 고레벨이 외부로부터 테스트 제어패드에서 입력한 고전위이기때문에, 이 패드에 인가하는 전위가 충분히 높다면, MOS트랜지스터의 임계치 떨어짐(MOS트랜지스터의 임계치에 상당하는 분만큼, 게이트·소스 사이에 생기는 전압강하) 없이 테스트전위를 내부회로로 전송하는 것이 가능해진다. 전원전압을 3.3V로 했을 때 테스트 제어패드에는 예컨대 10V의 고전압이 공급되고, 테스트 신호패드에는 예컨대 4V에서 7V의 일정 범위의 전압이 공급된다.

이어서, 본 발명을 적용한 반도체 기억장치의 예를 제2도~제4도를 이용해 설명한다.

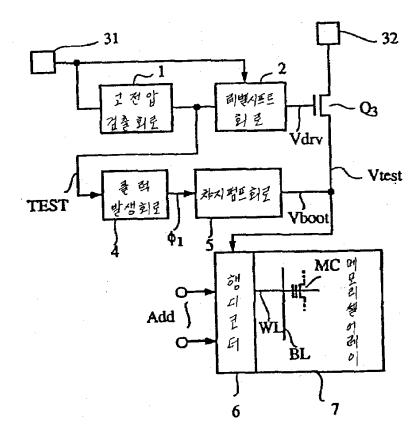

제2도는 반도체 기억장치의 전체 회로구성을 도시한 회로도이다. 즉, 테스트 제어패드(31)와, 테스트 신호패드(32), 고전압 검출회로(1), 레벨시프트회로(2)와, MOS트랜지스터(Q3), 클럭신호( $\phi$ 1)를 발생시키는 클럭 발생회로(4), 클럭신호( $\phi$ 1)에 의해 구동되어 통상 독출동작시에 워드선에 공급하는 고전위를 발생시키는 챠지펌프회로(5), 외부로부터 입력된 테스트전위 혹은 챠지펌프회로(5)에 의해 발생시킨 승압전위를 어드레스신호에 기초하여 워드선에 분배 공급하는 행디코더(6) 및, 워드선(WL), 비트선(BL) 및 메모리셀(MC) 등을 포함하는 메모리셀어레이(7)로 이루어진다.

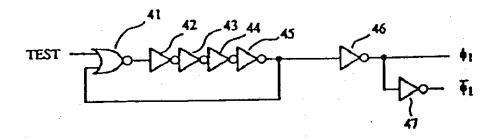

클럭발생회로(4)는 테스트 제어신호(TEST)에 의해 제어되고, 테스트 제어신호(TEST)가 H일 때는 클럭( $\phi$ 1)의 발생을 정지한다. 구체적인 회로구성을 제3도(a)에 도시한다. 즉, NOR게이트(41)와, 짝수단의 인버터(42…45)로 이루어진 링오실레이터, 파형정형용의 인버터(46) 및 반전출력용의 인버터(47)로 이루어진다. 그 외에, 독출할 때에만 승압동작을 행하기 위해 각종 제어회로가 실제로는 구비되어 있지만, 여기서는 설명을 생략한다.

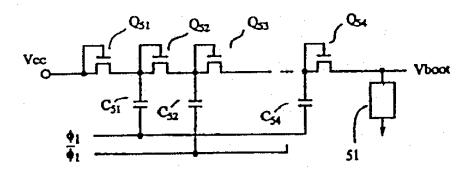

차지펌프회로(5)는 클럭신호( $\phi$ 1)에 의해 구동되어 통상 독출동작시에 워드선에 공급하는 승압전위 (Vboot)를 발생시킨다. 구체적인 회로구성을 제3도(b)에 도시한다. 즉, 게이트·드레인이 공통 접속된 N 채널 트랜지스터(Q51,Q52···Q54)와, 각 트랜지스터의 접속노드에 접속된 캐패시터(C51,C52···C54) 및, 출력 단자에 접속된 리미터회로(D1)로 이루어진다. 각 캐패시터의 대향전극은 하나 걸러 클럭신호( $\phi$ 1,/ $\phi$ 1)에 의해 클럭 구동된다.

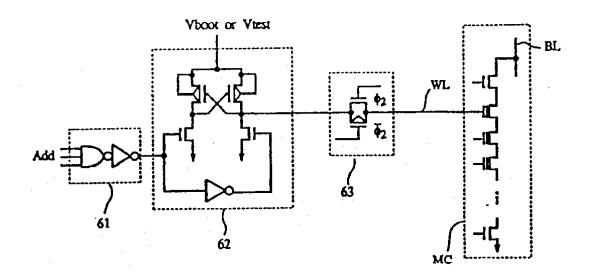

행디코더(6)는 챠지펌프회로(5)에 의해 발생시킨 승압전위를 어드레스신호(Add)에 기초하여 워드선(WL)에 분배 공급한다. 구체적인 회로구성을 제4도에 도시한다. 즉 어드레스신호(Add)에 기초하여 선택신호를 발생하는 어드레스 디코더(61)와, 이 선택신호를 레벨시프트하는 레벨시프트회로(62) 및, 필요에 따라 삽입

되는 선택회로(63)로 이루어진다. 레벨시프트회로(62)의 출력은 선택회로(63)를 매개로 메모리셀(MC)의 접속된 워드선(WL)에 공급된다. 레벨시프트회로(62)는 상술한 레벨시프트회로(2)와 거의 동일한 구성이기때문에 설명을 생략한다. 선택회로는 또 다른 어드레스신호에 의해 생성된 제어신호(ψ2)에 의해 온ㆍ온 프동작하고, 선택시에는 레벨시프트회로(62)의 출력을 워드선에 공급한다. 메모리셀은 불휘발성의 NAND형메모리셀이다. 특히, NAND형 메모리셀을 이용한 경우, 독출시의 셀전류가 NOR형과 비교해 감소하기 쉽다. 따라서, 독출시에 워드선을 승압할 필요성은 보다 크고, 이와 함께 외부에서 고전위의 테스트신호를 워드선에 공급할 필요성도 크다. 그러므로, NAND형메모리셀을 이용한 경우에는 특히 장점이 크다.

이어서, 제2도~제4도에 도시한 반도체 기억장치의 동작설명을 행한다. 통상의 독출동작시에는 테스트 제어패드(31)는 전원전위레벨의 신호입력단자로서 이용한다. 예컨대, /WP(라이트 프로텍트 제어신호)로서이용한다. 이 때, 테스트 제어패드(31)에는 고전위는 인가되지 않기 때문에 고전위 검출회로(1)의 출력인 TEST는 L이고, 레벨시프트회로(2)의 출력(Vdrv)도 L이다. 이 결과, 트랜지스터(Q3)는 오프하고, 테스트 신호패드와 내부회로는 분리된다. 또한, TEST가 L이기 때문에, 클럭발생회로(4)는 클럭신호(ψ1)를 출력하고, 챠지펌프회로(5)는 이 클럭신호(ψ1)에 의해 구동되며, 승압전위(Vboot)를 출력한다(도시되어 있지는 않지만, 독출 동작시만). 이 승압전위(Vboot)는 행디코더(6)에 공급되고, 행디코더(6)내에서는 레벨시프트회로(62)의 전원으로 된다.

이 결과, 워드선(WL)은 승압전위(Vboot)에 의해 구동되고, 통상의 독출이 행해진다.

테스트시에는, 테스트 제어패드(31)에는 예컨대 10V의 고전위가 인가된다.

고전위 검출회로(1)의 출력인 TEST는 H이고, 클럭발생회로(4)는 클럭의 발생을 정지한다. 이 결과, 챠지 펌프회로(5)는 승압동작을 정지한다. 또한, 도시하지 않지만, 리미터회로(51)는 출력단자에서 분리된다. 더욱이, 레벨시프트회로(2)의 출력(Vdrv)은 고전위, 예컨대 10V로 되기 때문에, MOS트랜지스터(Q3)는 온하고, 테스트 신호패드의 테스트전위(Vtest)가 트랜지스터(Q3)를 매개로 행디코더(6)에 공급된다. 이 테스트전위(Vtest)는 행디코더(6)내에서는 레벨시프트회로(62)의 전원으로 되고, 워드선(WL)은 승압전위(Vtest)에 의해 구동되며, 독출테스트가 행해진다. 더욱이, 테스트 신호패드에는 예컨대 4V에서 7V의 일정 범위의 전압이 공급된다.

이와 같이, 테스트 제어패드(31)를 전원전위레벨의 신호 입력단자와 공용할 수 있어 패드수를, 더 나아가 서 외부리드수를 삭감할 수 있다.

또한, 상술한 바와 같이, 테스트모드의 제어에 이용하는 테스트 제어신호를 칩 외부로부터 입력하는 고전 압을 검출함으로써 생성하고, 이와 마찬가지로, 이 고전압을 레벨시프트회로의 전원으로서 이용한다. 이 와 같이, 외부로부터 인가하는 고전압을 신호 및 전원의 양자로서 이용하기 때문에, 종래와 같은 승압회 로는 필요 없게 된다. 이 결과, 칩 면적이 대폭 줄어든다.

또한, 레벨시프트회로의 출력인 구동신호는 고레벨이 외부로부터 테스트 제어패드에서 입력한 고전위이기 때문에, 이 패드에 인가하는 전위가 충분히 높다면, MOS트랜지스터의 임계치의 떨어짐(MOS트랜지스터의임계치에 상당하는 분만큼, 게이트·소스 사이에 생기는 전압강하)없이 테스트전위를 내부회로로 전송하는 것이 가능해진다. 더욱이, 본 발명에서는 테스트 신호패드를 제어신호로서 이용하고 있는 것은 아니기때문에, 테스트 신호패드에는 어느 일정한 범위(range)의 전위를 공급하는 것이 가능해진다.

또한, 테스트전위가 디코더회로를 매개로 워드선에 인가되기 때문에, 워드선의 전위를 임의로 제어시키는 것이 가능해진다.

또한, 테스트 제어신호는 테스트 제어패드에 인가하는 전위와는 달리, 고전압에서는 없기 때문에, 테스트 시에 내부회로의 제어신호로서 이용할 수 있다. 본 실시예에서는 일례로서 승압회로중의 클럭발생회로의 제어에 이용했다.

한편, 본원 청구범위의 각 구성요건에 병기한 도면참조부호는 본원 발명의 이해를 용이하게 하기 위한 것으로, 본원 발명의 기술적 범위를 도면에 도시한 실시예로 한정할 의도로 병기한 것은 아니다.

## [발명의 효과]

이상 설명한 바와 같이 본 발명에 의하면, 승압회로를 필요로 하지 않는 테스트전위 전송회로를 제공할 수 있다.

#### (57) 청구의 범위

## 청구항 1

제1패드와, 제2패드, 상기 제1패드에 연결되고, 상기 제1패드에 검출된 고전압신호에 따라 제어신호를 발생하는 전압검출회로, 이 전압검출회로에 연결되고, 상기 제어신호에 따라 구동신호를 발생하는 레벨시프트회로, 상기 레벨시프트회로에 의해 발생된 구동신호에 의해 MOS트랜지스터의 게이트가 구동되도록 상기 레벨시프트회로에 연결된 게이트와 상기 제2패드에 연결된 드레인으로 이루어진 MOS트랜지스터 및, 상기 제어신호에 의해 제어된 내부회로를 구비하여 구성되고, 상기 레벨시프트회로의 전원단자는 패드에 접속되고, 상기 내부회로는 승압전위로 외부적에서 공급된 전원전위까지 높이기 위한 전압 승압회로이며, 상기 전압 승압회로에 의해 발생된 전압신호와 충돌을 방지하기 위해 상기 전압 증압회로의 동작이 상기 제어신호에 의해 제어되는 것을 특징으로 하는 반도체장치.

#### 청구항 2

제1패드와, 제2패드, 상기 제1패드에 연결되고, 상기 제1패드에 인가된 고전압신호에 따라 제어신호를 발생하는 전압검출회로, 이 전압검출회로에 연결되고, 상기 제어신호에 따라 구동신호를 발생하는 레벨시프트회로, 상기 레벨시프트회로에 의해 발생된 구동신호에 의해 MOS트랜지스터의 게이트가 구동되도록 상기레벨시프트회로에 연결된 게이트와 상기 제2패드에 연결된 드레인 및 소스로 이루어진 MOS트랜지스터, 다

수의 메모리셀에 접속된 다수의 워드선을 갖춘 메모리셀어레이 및, 승압전위로 외부적에서 공급된 전원전위까지 높이기 위한 전압 승압 회로를 구비하여 구성되고, 상기 레벨시프트회로의 전원단자는 상기 제1패드에 접속되고, 상기 MOS트랜지스터의 소스는 상기 다수의 워드선에 연결되고, 상기 전압 승압회로의 동작은 상기 제어신호에 의해 제어되며, 상기 승압전위는 상기 워드선중에 인가되는 것을 특징으로 하는 반도체장치.

#### 청구항 3

제2항에 있어서, 상기 제어신호는 감소된 전력소비를 갖는 동작모드로 상기 전압 승압회로를 스위치하는 것을 특징으로 하는 반도체장치.

#### 청구항 4

제어노드와, 신호노드, 상기 제어노드에 접속되고, 상기 제어노드에 고전압신호가 존재하는지를 나타내는 디지털 제어신호값을 발생하는 전압검출회로, 상기 고전압신호가 상기 제어노드에 존재하는 것을 상기 디지털 제어신호가 나타낼 경우, 상기 제어신호의 논리레벨을 시프팅함으로써 구동신호를 발생하기 위한 레벨시프트회로 및, 상기 신호노드에 연결된 드레인단자와 상기 레벨시프트회로에 연결된 게이트단자를 갖춘 MOS트랜지스터를 구비하여 구성되고, 상기 MOS트랜지스터의 게이트단자는 상기 레벨시프트회로에 의해 발생된 구동신호가 사실상 상기 제어노드와 동일한 레벨이도록 상기 레벨시프트회로에 의해 발생된 구동신호가 사실상 상기 제어노드와 동일한 레벨이도록 상기 레벨시프트회로의 전력단자가 상기 제어노드에 접속되고, 상기 디지털 제어신호는 기준전위 또는 전원전위이고, 상기 고전압신호가 상기 제어노드에 존재할 경우, 구동신호의 레벨(V<sub>drv</sub>)이 상기 전원전위 보다도 크도록 상기 고전압신호의 레벨이 상기 전원전위 보다도 크도록 상기 고전압신호의 레벨이 상기 전원전위 보다도 크며, 상기 MOS트랜지스터는 상기 고전압신호가 상기 제어노드에 존재할 경우, 상기 신호노드에 신호레벨(V<sub>s</sub>)이 상기 구동신호의 레벨(V<sub>drv</sub>)에서 N채널 MOS트랜지스터의 임계전압(V<sub>th</sub>)을 뺀 것 보다도 작아(V<sub>s</sub> 〈V drv-V<sub>th</sub>)지는 동안에는 사실상 전압강하 없이 상기 MOS트랜지스터의 소스단자에 상기 신호노드에 존재하는 신호가 전송되는 N채널 MOS트랜지스터인 것을 특징으로 하는 전위 전송히로

#### 청구항 5

제어노드와, 신호노드, 상기 제어노드에 접속되고, 상기 제어노드에 고전압신호가 존재하는지를 나타내는 디지털 제어신호값을 발생하는 전압검출회로, 상기 고전압신호가 상기 제어노드에 존재하는 것을 상기 디지털 제어신호가 나타낼 경우, 상기 제어신호의 논리레벨을 시프팅함으로써 구동신호를 발생하기 위한 레벨시프트회로 및, 상기 신호노드에 연결된 드레인단자와 상기 레벨시프트회로에 연결된 게이트단자를 갖춘 MOS트랜지스터를 구비하여 구성되고, 상기 MOS트랜지스터의 게이트단자는 상기 레벨시프트회로에 의해 발생된 구동신호에 의해 구동되고, 상기 고전압신호가 상기 제어노드에 존재할 경우, 상기 레벨시프트회로에 의해 발생된 구동신호가 사실상 상기 제어노드와 동일한 레벨이도록 상기 레벨시프트회로의 전력단자가 상기 제어노드에 접속되고, 상기 디지털 제어신호는 기준전위 또는 전원전위이고, 상기 고전압신호가 상기 제어노드에 존재할 경우, 구동신호의 레벨(V<sub>drv</sub>)이 상기 전원전위 보다보 크도록 상기 고전압신호가 상기 제어노드에 존재할 경우, 수기 신호노드에 인가된 신호가 사실상 전압강하 없이 상기 MOS트랜지스터의 소스단자로 전송되도록 상기 고전압신호의 레벨(V<sub>h</sub>)을 상기 신호노드에 인가된 신호의 최대레벨(V<sub>S-max</sub>)에 상기 N채널 MOS트랜지스터의 임계전압(V<sub>th</sub>)을 더한 것보다도 크게 (V<sub>h</sub>) V<sub>S-max</sub>+V th)하는 것을 특징으로 하는 전위 전송회로.

### 청구항 6

제어노드와, 신호노드, 상기 제어노드에 접속되고, 상기 제어노드에 검출된 고전압신호에 따라 제어신호를 발생하는 전압검출회로, 상기 전압검출회로에 연결되고, 상기 제어신호의 논리레벨을 시프팅함으로써 발생되고 상기 제어신호에 따른 구동신호를 발생하며, 고전압신호가 상기 제어노드에 검출될 경우, 레벨시프트회로에 의해 발생된 구동신호의 레벨이 사실상 상기 고전압신호의 레벨과 동일하도록 상기 제어노드에 의해 파워(power)되는 레벨시프트회로, 상기 MOS트랜지스터의 게이트가 상기 레벨시프트회로에 의해 발생된 구동신호에 의해 구동되도록 상기 레벨시프트회로에 연결된 게이트와 신호노드에 연결된 드레인을 갖춘 MOS트랜지스터를 구비하여 구성되고, 상기 MOS트랜지스터는 N채널 MOS트랜지스터이며, 상기 고전압신호가 제어노드에 존재할 경우, 상기 신호노드에 신호레벨( $V_s$ )이 상기 구동신호의 레벨( $V_{drv}$ )에서 상기 N 채널 MOS트랜지스터의 임계전압을 뺀 것 보다도 작아( $V_s$   $\langle V_{drv} - V_{th} \rangle$ 지는 동안에는 사실상 전압강하 없이 상기 MOS트랜지스터의 소스단자에 상기 신호노드에 존재하는 신호가 전송되는 것을 특징으로 하는 전위 전송회로.

## 청구항 7

제6항에 있어서, 상기 제어노드 및 신호노드는 칩상에 1/0 패드인 것을 특징으로 하는 전위 전송회로.

#### 청구항 8

제6항에 있어서, 다수의 메모리셀에 연결된 다수의 워드선을 갖춘 메모리셀어레이를 더 구비하여 구성되고, 상기 MOS트랜지스터를 더 구비하여 구성되고, 상기 MOS트랜지스터의 소스는 상기 다수의 워드선에 연결된 것을 특징으로 하는 전위 전송회로.

#### 청구항 9

제8항에 있어서, 상기 메모리셀은 NAND형 메모리셀인 것을 특징으로 하는 전위 전송회로.

## 청구항 10

제8항에 있어서, 상기 MOS트랜지스터의 소스에서 상기 워드선으로 전위를 분배하기 위한 행디코더를 더구비하여 구성된 것을 특징으로 하는 전위 전송회로.

#### 청구항 11

제6항에 있어서, 상기 전압검출회로는 하나의 전압분할기와 적어도 하나의 인버터를 갖춘 것을 특징으로 하는 전위 전송회로.

#### 청구항 12

제6항에 있어서, 상기 전압검출회로는 하나의 전압분할기와 적어도 2개의 인버터로 이루어진 것을 특징으로 하는 전위 전송회로.

#### 청구항 13

제어노드와, 신호노드, 상기 제어노드에 접속되고, 상기 제어노드에 검출된 고전압신호에 따라 상기 제어 신호를 발생하는 전압검출회로, 상기 전압검출회로에 연결되고, 상기 제어신호의 논리레벨을 시프팅함으로써 발생되고 상기 제어신호에 따른 구동신호를 발생하며, 상기 고전압 신호가 상기 제어노드에 검출될경우, 레벨시프트회로에 의해 발생된 상기 구동신호의 레벨이 사실상 상기 고전압신호의 레벨과 동일하도록 상기 제어노드에 의해 파워(power)되는 레벨시프트회로, 상기 MOS트랜지스터의 게이트가 상기 레벨시프트회로에 의해 발생된 구동신호에 의해 구동되도록 상기 레벨시프트회로에 연결된 게이트와 신호노드에연결된 드레인을 갖춘 MOS트랜지스터를 구비하여 구성되고, 상기 MOS트랜지스터는 N채널 MOS트랜지스터이며, 상기 고전압신호가 상기 제어노드에 존재할 경우, 상기 신호노드에 인가된 신호가 사실상 전압강하없이 상기 MOS트랜지스터의 소스단자로 전송되도록 상기 고전압신호의 레벨(V<sub>s-max</sub>)에 상기 N채널 MOS트랜지스터의 임계전압(V<sub>th</sub>)을 더한 것보다도 크게 (V<sub>h</sub>〉V<sub>s-max</sub>+V<sub>th</sub>)하는 것을 특징으로 하는 전위 전송회로.

## 청구항 14

제13항에 있어서, 상기 제어노드 및 신호노드는 칩상에 I/O 패드인 것을 특징으로 하는 전위 전송회로.

#### 청구항 15

제13항에 있어서, 다수의 메모리셀에 연결된 다수의 워드선을 갖춘 메모리셀어레이를 더 구비하여 구성되고, 상기 MOS트랜지스터의 소스는 상기 다수의 워드선에 연결된 것을 특징으로 하는 전위 전송회로.

#### 청구항 16

제15항에 있어서, 상기 메모리셀은 NAND형 메모리셀인 것을 특징으로 하는 전위 전송회로.

#### 청구항 17

제15항에 있어서, 상기 MOS트랜지스터의 소스에서 상기 워드선으로 전위를 분배하기 위한 행디코더를 더구비하여 구성된 것을 특징으로 하는 전위 전송회로.

#### 청구항 18

제13항에 있어서, 상기 전압검출회로는 하나의 전압분할기와 적어도 하나의 인버터를 갖춘 것을 특징으로 하는 전위 전송회로.

## 청구항 19

제13항에 있어서, 상기 전압검출회로는 하나의 전압분할기와 적어도 2개의 인버터로 이루어진 것을 특징으로 하는 전위 전송회로.

## 도면

도면1

## 도면2

## 도*면3a*

## 도면3b

# 도면4