# (19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第6392133号 (P6392133)

最終頁に続く

(45) 発行日 平成30年9月19日(2018.9.19)

(24) 登録日 平成30年8月31日 (2018.8.31)

| (51) Int.Cl. |                       | F 1             |           |                         |

|--------------|-----------------------|-----------------|-----------|-------------------------|

| HO1L 29/78   | (2006.01)             | HO1L            | 29/78     | 657D                    |

| HO1L 29/739  | (2006.01)             | HO1L            | 29/78     | 655B                    |

| HO1L 29/861  | (2006.01)             | HO1L            | 29/78     | 653C                    |

| HO1L 29/868  | (2006.01)             | HO1L            | 29/78     | 652S                    |

| HO1L 21/823  | 4 (2006.01)           | HO1L            | 29/78     | 655D                    |

|              |                       |                 |           | 請求項の数 3 (全 10 頁) 最終頁に続く |

| (21) 出願番号    | <b>特願2015-14168</b> ( | P2015-14168)    | (73) 特許権者 | f 000003078             |

| (22) 出願日     | 平成27年1月28日            | (2015. 1. 28)   |           | 株式会社東芝                  |

| (65) 公開番号    | 特開2016-139719         | (P2016-139719A) |           | 東京都港区芝浦一丁目1番1号          |

| (43) 公開日     | 平成28年8月4日(            | 2016.8.4)       | (73) 特許権者 | \$ 317011920            |

| 審查請求日        | 平成29年3月7日(            | 2017.3.7)       |           | 東芝デバイス&ストレージ株式会社        |

|              |                       |                 |           | 東京都港区芝浦一丁目1番1号          |

|              |                       |                 | (74) 代理人  | 100108062               |

|              |                       |                 |           | 弁理士 日向寺 雅彦              |

|              |                       |                 | (72) 発明者  | 下條 亮平                   |

|              |                       |                 |           | 東京都港区芝浦一丁目1番1号 株式会社     |

|              |                       |                 |           | 東芝内                     |

|              |                       |                 |           |                         |

|              |                       |                 | 審査官       | 早川 朋一                   |

-(54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

# 【請求項1】

第1電極と、

前記第1電極上の第1領域に設けられ、前記第1電極と電気的に接続された第1導電形の第1半導体層と、

前記第1電極上の第2領域に設けられ、前記第1電極と電気的に接続された第2導電形の第2半導体層と、

前記第1半導体層上及び前記第2半導体層上に設けられ、前記第2半導体層よりも低い 第2導電形のキャリア濃度を有する第2導電形の第3半導体層と、

前記第3半導体層上に設けられ、前記第3半導体層よりも低い第2導電形のキャリア濃度を有する第2導電形の第4半導体層と、

前記第4半導体層上に設けられ、第1導電形の第5半導体層と、

前記第1領域において、前記第5半導体層上に設けられた第2導電形の第6半導体層と

前記第4半導体層、前記第5半導体層及び第6半導体層に第1絶縁膜を介して対面し、 前記第1領域に設けられた第2電極と、

前記第4半導体層及び前記第5半導体層に第2絶縁膜を介して対面し、前記第2領域に 設けられた第3電極と、

前記第5半導体層、前記第6半導体層及び前記第3電極に接続された第4電極と、 を備え、 10

前記第3半導体層と前記第3電極との間の距離、及び前記第2領域における前記第3半 導体層と前記第5半導体層との距離のうち、少なくとも一方は、前記<u>第</u>3半導体層と前記 第2電極との距離よりも短く、

前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第1領域に位置する部分の上面よりも上方に位置し、

前記第3半導体層における前記第2領域に位置する部分の不純物濃度は、前記第3半導体層における前記第1領域に位置する部分の不純物濃度よりも高い半導体装置。

# 【請求項2】

前記第3電極の下端は、前記第2電極の下端よりも下方に位置する請求項1記載の半導体装置。

【請求項3】

前記第5半導体層における前記第2領域に位置する部分の下面は、前記第3電極の下端よりも下方に位置し、前記第5半導体層における前記第1領域に位置する部分の下面より も下方に位置している請求項1記載の半導体装置。

【発明の詳細な説明】

【技術分野】

[0001]

本発明の実施形態は、半導体装置に関する。

【背景技術】

[0002]

近年、高耐圧で大電流を流すことができる電力用半導体装置として、IGBT(insula ted gate bipolar transistor: 絶縁ゲートバイポーラトランジスタ)が広く用いられている。また、1つのチップにIGBTとダイオードを混載した逆導通型IGBTも実用化されている。一般に、電力用半導体装置においては、導通損失及びスイッチング損失等の損失を低減しようとすると、アバランシェ耐量等が低下する。

【先行技術文献】

【特許文献】

[0003]

【特許文献1】特開2008-47565号公報

【発明の概要】

【発明が解決しようとする課題】

[0004]

実施形態の目的は、耐量の増加を可能とする半導体装置を提供することである。

【課題を解決するための手段】

[0005]

実施形態に係る半導体装置は、第1電極と、前記第1電極上の第1領域に設けられ、前記第1電極と電気的に接続された第1導電形の第1半導体層と、前記第1電極上の第2領域に設けられ、前記第1電極と電気的に接続された第2導電形の第2半導体層と、前記第2半導体層と、前記第2半導体層と、前記第2半導体層と、前記第3半導体層上に設けられ、前記第3半導体層上に設けられ、前記第3半導体層上に設けられ、第1導電形の第5半導体層と、前記第1半導体層と、前記第1半導体層と、前記第1半導体層と、前記第1半導体層と、前記第1半導体層と、前記第1半導体層と、前記第1半導体層に第1絶縁膜を介して対配第1領域に設けられた第2電極と、前記第5半導体層に第2絶縁膜を介して対面し、前記第1半導体層し、前記第1半導体層と、前記第5半導体層と、前記第1半導体層と、前記第3半導体層との距離のの距離、及び前記第2領域における前記第3半導体層との距離よりも短い。前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における前記第2領域に位置する部分の上面は、前記第3半導体層における記載なりませば、前記第3半導体層における記載なりませば、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、前記第3半導体層と、11・第3半導体層と、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・第3半導体層を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を、11・1を

10

20

30

40

10

20

30

40

50

領域に位置する部分の上面よりも上方に位置する。前記第3半導体層における前記第2領域に位置する部分の不純物濃度は、前記第3半導体層における前記第1領域に位置する部分の不純物濃度よりも高い。

# 【図面の簡単な説明】

### [0006]

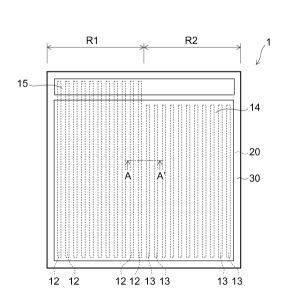

- 【図1】第1の実施形態に係る半導体装置を例示する平面図である。

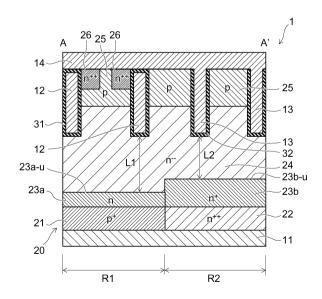

- 【図2】第1の実施形態に係る半導体装置を示す断面図である。

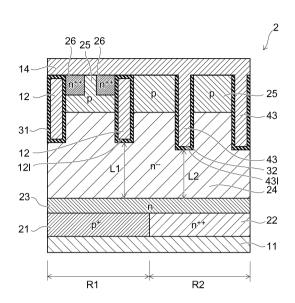

- 【図3】第2の実施形態に係る半導体装置を示す断面図である。

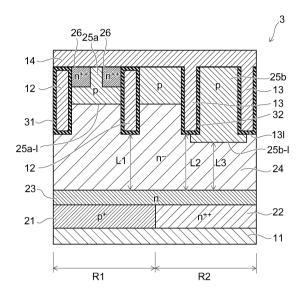

- 【図4】第3の実施形態に係る半導体装置を示す断面図である。

- 【図5】第4の実施形態に係る半導体装置を示す断面図である。

- 【図6】第5の実施形態に係る半導体装置を示す断面図である。

- 【発明を実施するための形態】

### [0007]

(第1の実施形態)

以下、図面を参照しつつ、本発明の実施形態について説明する。

先ず、第1の実施形態について説明する。

- 図1は、本実施形態に係る半導体装置を示す平面図である。

- 図2は、本実施形態に係る半導体装置を示す断面図である。

- 図2に示す断面は、図1に示すA-A'線による断面である。

### [00008]

図1及び図2に示すように、本実施形態に係る半導体装置1は、1つのチップ内にIGBT及びダイオードが混載された逆導通型IGBTである。半導体装置1においては、IGBT領域R1及びダイオード領域R2が設定されている。上方から見て、IGBT領域R1及びダイオード領域R2は、例えば、それぞれ矩形の領域である。

#### [0009]

半導体装置 1 においては、例えば金属からなる平板状のコレクタ電極 1 1 が設けられている。コレクタ電極 1 1 は、半導体装置 1 の下面全体に設けられている。コレクタ電極 1 1 上には、 p <sup>†</sup> 形コレクタ層 2 1 及び n <sup>†</sup> <sup>†</sup> 形カソード層 2 2 が並列に設けられている。 p <sup>†</sup> 形コレクタ層 2 1 は I G B T 領域 R 1 に配置されており、 n <sup>†</sup> <sup>†</sup> 形カソード層 2 2 は ダイオード領域 R 2 に配置されている。 p <sup>†</sup> 形コレクタ層 2 1 及び n <sup>†</sup> <sup>†</sup> 形カソード層 2 2 の厚さは相互に略等しく、端面同士が接している。

# [0010]

本明細書において、例えば「p  $^+$  形コレクタ層  $^2$  1」との表記は、その層の導電形がp形であることを示す。  $^n$  形についても同様である。また、上付きの「 $^+$  」及び「 $^-$  」の文字は、実効的な不純物濃度を相対的に表している。すなわち、導電形が $^n$  形の層に関しては、実効的な不純物濃度が高い順に、「 $^n$   $^+$  形」、「 $^n$   $^+$  形」、「 $^n$   $^+$  形」、「 $^n$   $^+$  形」と表記する。更に、「実効的な不純物濃度」とは、半導体材料の導電に寄与する不純物の濃度をいい、ある部分がドナーとなる不純物及びアクセプタとなる不純物の双方を含む場合は、それらの相殺分を除いた濃度をいう。「実効的な不純物濃度」は、「キャリア濃度」と等しい。更にまた、本明細書においては、説明の便宜上、コレクタ電極  $^n$  1 から  $^n$  形コレクタ層  $^n$  1 及び  $^n$   $^+$  形カソード層  $^n$  2 2 に向かう方向を「上」といい、その反対方向を「下」という。但し、これらの方向は重力の方向とは無関係である。

# [0011]

$p^+$  形コレクタ層 2 1 上には、n 形 バッファ層 2 3 a が設けられている。また、 $n^+$  形 カソード層 2 2 上には、 $n^+$  形 バッファ層 2 3 b が設けられている。n 形 バッファ層 2 3 b が設けられている。n 形 バッファ層 2 3 b は n 形 バッファ層 2 3 b は n 形 バッファ層 2 3 b は n 形 バッファ層 2 3 a よりも厚い。すなわち、 $n^+$  形 バッファ層 2 3 b の上下方向の長さよりも長い。従って、 $n^+$  形 バッファ層 2 3 b の上面 2 3 b - u は n 形 バッファ層 2 3 a の上面 2 3 a - u よりも上方に位置してい

る。なお、上述の表記法に従い、 $n^+$ 形バッファ層 2 3 bの実効的な不純物濃度は $n^{++}$ 形カソード層 2 2 の実効的な不純物濃度よりも低く、n 形バッファ層 2 3 a の実効的な不純物濃度よりも高い。

# [0012]

n 形 バッファ層 2 3 a 上及 び n  $^+$  形 バッファ層 2 3 b 上には、 n  $^-$  形 ベース層 2 4 が 設けられている。すなわち、 n  $^-$  形 ベース層 2 4 は、 1 G B T 領域 R 1 及 び ダイオード 領域 R 2 の 双方にわたって連続的に配置されている。但 し、 n  $^-$  形 ベース層 2 4 に 配置された 部分の厚さ、すなわち上下方向の長さは、 n  $^-$  形 ベース層 2 4 に おける 1 G B T 領域 R 1 に 配置された 部分の厚さよりも薄い。

# [0013]

$n^{-1}$  形ベース層 2 4 上には、p 形ベース層 2 5 が設けられている。p 形ベース層 2 5 も、I G B T 領域 R 1 及びダイオード領域 R 2 の双方にわたって配置されている。I G B T 領域 R 1 において、p 形ベース層 2 5 上の一部には、複数の  $n^{-1}$  形エミッタ層 2 6 が相互に離隔して設けられている。

# [0014]

p \* 形コレクタ層 2 1 、 n \* \* \* 形カソード層 2 2 、 n 形パッファ層 2 3 a 、 n \* 形パッファ層 2 3 b 、 n \* \* 形ベース層 2 4 、 p 形ベース層 2 5 及び n \* \* 形エミッタ層 2 6 により、半導体部分 2 0 が構成されている。半導体部分 2 0 は、ドナーとなる不純物及びアクセプタとなる不純物が局所的に導入されたシリコンからなり、例えば、 1 つの単結晶からなる。

#### [0015]

IGBT領域R1において、半導体部分20の上部内には、一方向に延びる複数本のトレンチゲート電極12が設けられている。トレンチゲート電極12は、n \* \* 形工ミッタ層26及びp形ベース層25を上下方向に貫通し、その下端部はn \* 形ベース層24の上部内に位置している。トレンチゲート電極12は、ポリシリコン又は金属により形成されている。また、トレンチゲート電極12は、ポリシリコン又は金属により形成されている。また、トレンチゲート電極12は、のえばシリコン酸化物又はシリコン窒化物からなるゲート絶縁膜31が設けられている。これにより、トレンチゲート電極12は、半導体部分20からゲート絶縁膜31によって絶縁されている。ゲート絶縁膜31はトレンチゲート電極12の上面も覆っている。

# [0016]

一方、ダイオード領域R2において、半導体部分20の上部内には、複数本のトレンチエミッタ電極13が設けられている。トレンチエミッタ電極13はトレンチゲート電極12と同じ方向に延びている。トレンチエミッタ電極13は、p形ベース層25を上下方向に貫通し、その下端部はn 形ベース層24の上部内に位置している。トレンチエミッタ電極13は、例えばポリシリコン又は金属により形成されている。また、トレンチエミッタ電極13と、n 形ベース層24及びp形ベース層25との間には、例えばシリコン酸化物又はシリコン窒化物からなるゲート絶縁膜32が設けられている。

# [0017]

#### [0018]

図 1 に示すように、半導体部分 2 0 及びトレンチゲート電極 1 2 の上方であって、 I G B T 領域 R 1 の一端部には、ゲート電極 1 5 が設けられている。トレンチゲート電極 1 2

10

20

30

40

10

20

30

40

50

は、その長手方向の一端部において、ゲート電極15と接続されている。ゲート電極15の端面は、エミッタ電極14の端面と隙間を介して対向している。上方から見て、エミッタ電極14の面積はゲート電極15の面積よりも大きい。半導体部分20上であって、エミッタ電極14及びゲート電極15が配置されていない領域には、パッシベーション膜30が設けられている。

# [0019]

そして、本実施形態に係る半導体装置 1 においては、  $n^+$  形バッファ層 2 3 b の上面 2 3  $b^-$  u が n 形バッファ層 2 3 a の上面 2 3  $a^-$  u よりも上方に位置しているため、ダイオード領域 R 2 における  $n^+$  形バッファ層 2 3 b とトレンチエミッタ電極 1 3 との距離 L 2 は、 I G B T 領域 R 1 における n 形バッファ層 2 3 a とトレンチゲート電極 1 2 との距離 L 1 よりも短い。

#### [0020]

次に、本実施形態の作用効果について説明する。

本実施形態に係る半導体装置1においては、IGBT領域R1において、コレクタ電極11、p<sup>+</sup> 形コレクタ層21、n形バッファ層23a、n<sup>・・</sup> 形ベース層24、p形ベース層25、n<sup>・・</sup> 形エミッタ層26、エミッタ電極14、トレンチゲート電極12及びゲート絶縁膜31により、pnpn構造を持つIGBTが形成されている。そして、ゲート電極15を介してトレンチゲート電極12の電位を制御することにより、コレクタ電極11からエミッタ電極14に流れる電流の大きさを制御することができる。IGBT領域R1において、非導通時において耐圧を担保する低濃度部分は、n・・形ベース層24におけるn形バッファ層23aとトレンチゲート電極12との距離L1である。

### [0021]

また、ダイオード領域 R 2 においては、 n <sup>+ +</sup> 形カソード層 2 2 、 n <sup>+</sup> 形バッファ層 2 3 b 及び n <sup>- -</sup> 形ベース層 2 4 が n 形部分となり、 p 形ベース層 2 5 が p 形部分となって、 p n ダイオードが形成される。この p n ダイオードは、コレクタ電極 1 1 からエミッタ電極 1 4 に流れる電流は遮断し、エミッタ電極 1 4 からコレクタ電極 1 1 に流れる電流は 導通させる。すなわち、コレクタ電極 1 1 はカソード電極として機能し、エミッタ電極 1 4 及びトレンチエミッタ電極 1 3 はアノード電極として機能する。そして、ダイオード領域 R 2 において、逆バイアス電圧が印加されたときに耐圧を担保する低濃度部分は、 n <sup>-</sup> 形ベース層 2 4 における n <sup>+</sup> 形バッファ層 2 3 b とトレンチエミッタ電極 1 3 との間の部分であり、その厚さは、 n <sup>+</sup> 形バッファ層 2 3 b とトレンチエミッタ電極 1 3 との距離 L 2 である。

# [0022]

そして、本実施形態においては、ダイオード領域R2において耐圧を担保する距離L2が、IGBT領域R1において耐圧を担保する距離L1よりも短いため、ダイオード領域R2の耐圧はIGBT領域R1の耐圧よりも低い。このため、コレクタ電極11を正極としエミッタ電極14を負極とする過大電圧が印加された場合に、IGBT領域R1よりも先にダイオード領域R2においてアバランシェ降伏が発生する。アバランシェ降伏が発生するとアバランシェ電流が流れ、電圧が緩和されるため、IGBT領域R1におけるアバランシェ降伏を回避することができる。このため、半導体装置1は、アバランシェ耐量の増加を可能とする。

# [0023]

。このように、本実施形態によれば、信頼性が高い半導体装置を実現することができる。

# [0024]

(第2の実施形態)

次に、第2の実施形態について説明する。

図3は、本実施形態に係る半導体装置を示す断面図である。

図3が示す断面は、図1に示すA-A'線による断面に相当する。

#### [0025]

図 3 に示すように、本実施形態に係る半導体装置 2 は、前述の第 1 の実施形態に係る半導体装置 1 (図 2 参照)と比較して、n 形パッファ層 2 3 a 及び n <sup>†</sup> 形パッファ層 2 3 b の代わりに、I G B T 領域 R 1 及びダイオード領域 R 2 の双方にわたって、単一のn 形パッファ層 2 3 が設けられている。

[0026]

また、上下方向において、トレンチエミッタ電極 4 3 がトレンチゲート電極 1 2 よりも長く、従って、トレンチエミッタ電極 4 3 の下端 4 3 1 がトレンチゲート電極 1 2 の下端 1 2 1 よりも下方に位置している。このため、 n 形バッファ層 2 3 とトレンチエミッタ電極 4 3 との距離 L 2 は、 n 形バッファ層 2 3 とトレンチゲート電極 1 2 との距離 L 1 より も短い。

#### [0027]

本実施形態においても、ダイオード領域 R 2 において耐圧を担保する距離 L 2 が、 I G B T 領域 R 1 において耐圧を担保する距離 L 1 よりも短いため、ダイオード領域 R 2 の耐圧は I G B T 領域 R 1 の耐圧よりも低い。

本実施形態における上記以外の構成及び作用効果は、前述の第 1 の実施形態と同様である。

# [0028]

(第3の実施形態)

次に、第3の実施形態について説明する。

図4は、本実施形態に係る半導体装置を示す断面図である。

図4が示す断面は、図1に示すA-A′線による断面に相当する。

# [0029]

図4に示すように、本実施形態に係る半導体装置3においては、前述の第2の実施形態と同様に、n形バッファ層23a及びn<sup>+</sup>形バッファ層23bの代わりに、単一のn形バッファ層23が設けられている。また、本実施形態においては、p形ベース層25の厚さが、IGBT領域R1に配置された部分25aとダイオード領域R2に配置された部分25bとで異なっており、部分25bは部分25aよりも厚い。このため、部分25bの下面25b-1は、部分25aの下面25a-1よりも下方に位置しており、トレンチエミッタ電極13の下端131よりも下方に位置している。

# [0030]

従って、ダイオード領域R2において、n形バッファ層23とp形ベース層25の部分25bとの距離L3は、n形バッファ層23とトレンチエミッタ電極13との距離L2よりも短くなる。このため、半導体装置2のダイオード領域R2において、逆バイアス電圧が印加されたときの耐圧は、距離L2よりも距離L3により強く依存する。そして、距離L3は、IGBT領域R1において耐圧を担保する距離L1よりも短い

#### [0031]

本実施形態においては、ダイオード領域R2において耐圧を担保する距離L3が、IGBT領域において耐圧を担保する距離L1よりも短いため、ダイオード領域R2の耐圧はIGBT領域R1の耐圧よりも低い。これにより、IGBT領域R1よりも先にダイオード領域R2においてアバランシェ降伏が発生し、IGBT領域R1におけるアバランシェ降伏を防止することができる。このため、本実施形態に係る半導体装置3は、アバランシェ耐量が高い。

本実施形態における上記以外の構成及び作用効果は、前述の第1の実施形態と同様であ

10

20

30

40

る。

# [0032]

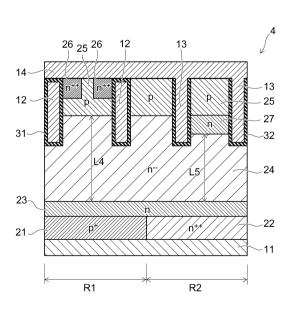

(第4の実施形態)

次に、第4の実施形態について説明する。

図5は、本実施形態に係る半導体装置を示す断面図である。

図 5 が示す断面は、図 1 に示す A - A '線による断面に相当する。

#### [0033]

図 5 に示すように、本実施形態に係る半導体装置 4 においては、前述の第 2 の実施形態と同様に、 I G B T 領域 R 1 及びダイオード領域 R 2 にわたって、単一の n 形パッファ層 2 3 が設けられている。また、ダイオード領域 R 2 において、 n 形パース層 2 4 と p 形パース層 2 5 との間に n 形パリア層 2 7 が設けられている。 n 形パリア層 2 7 における実効的な不純物濃度は、 n 形パース層 2 4 における実効的な不純物濃度よりも高い。

#### [0034]

本実施形態によれば、ダイオード領域R2にn形バリア層27が設けられているため、ダイオード領域R2におけるn 形ベース層24の厚さは、n形バッファ層23とn形バリア層27との距離L5となる。n 形ベース層24は耐圧を担保する低濃度部分として機能するため、n 形ベース層24の厚さ、すなわち、距離L5が短いほど、ダイオード領域R2の耐圧は低くなる。一方、IGBT領域R1におけるn 形ベース層24の厚さは、n形バッファ層23とp形ベース層25との距離L4であり、距離L4が短いほど、IGBT領域R1の耐圧は低くなる。そして、本実施形態においては、距離L5は距離L4よりも短いため、ダイオード領域R2の耐圧はIGBT領域R1の耐圧よりも低い

本実施形態における上記以外の構成及び作用効果は、前述の第1の実施形態と同様である。

# [0035]

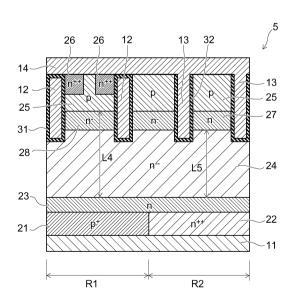

(第5の実施形態)

次に、第5の実施形態について説明する。

図6は、本実施形態に係る半導体装置を示す断面図である。

図6が示す断面は、図1に示すA-A'線による断面に相当する。

# [0036]

図6に示すように、本実施形態に係る半導体装置5においては、前述の第4の実施形態に係る半導体装置4(図5参照)と比較して、IGBT領域R1において、n 形ベース層24とp形ベース層25との間にn 形バリア層28が設けられている。n 形バリア層28の実効的な不純物濃度は、n形バリア層27の実効的な不純物濃度よりも低い。【0037】

本実施形態に係る半導体装置5においては、n 形バリア層28はn 形ベース層24と共に、IGBT領域R1において耐圧を担保する低濃度部分として機能する。このため、前述の第4の実施形態と同様に、ダイオード領域R2において耐圧を担保する距離L5は、IGBT領域R1において耐圧を担保する距離L4よりも短い。このため、IGBT領域R1よりも先にダイオード領域R2においてアバランシェ降伏が発生する。

本実施形態における上記以外の構成及び作用効果は、前述の第4の実施形態と同様である。

# [0038]

以上説明した実施形態によれば、アバランシェ耐量の増加を可能とする半導体装置を実現することができる。

# [0039]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の

10

20

30

40

範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明及びその等価物の範囲 に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

### 【符号の説明】

# [0040]

【図1】

1、2、3、4、5:半導体装置、11:コレクタ電極、12:トレンチゲート電極、121:下端、13:トレンチエミッタ電極、131:下端、14:エミッタ電極、15:ゲート電極、20:半導体部分、21:p<sup>+</sup>形コレクタ層、22:n<sup>+</sup><sup>+</sup>形カソード層、23a:n形バッファ層、23b:n<sup>+</sup>形バッファ層、24:n<sup>-</sup>形ベース層、25:p形ベース層、25a:部分、25a-1:下面、25b:部分、25b-1:下面、26:n<sup>+</sup>\*形エミッタ層、27:n形バリア層、28:n<sup>-</sup>形バリア層、30:パッシベーション膜、31:ゲート絶縁膜、32:ゲート絶縁膜、43:トレンチエミッタ電極、431:下端、L1~L5:距離、R1:IGBT領域、R2:ダイオード領域

【図2】

【図3】 【図4】

【図5】 【図6】

# フロントページの続き

(51) Int.CI. F I

H 0 1 L 27/06 (2006.01) H 0 1 L 29/78 6 5 2 J H 0 1 L 29/91 C H 0 1 L 27/06 1 0 2 A

(56)参考文献 特開2011-243694(JP,A)

特開2010-114248(JP,A) 特開2016-131224(JP,A) 特開2015-032689(JP,A) 特開2007-012972(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 1 L 2 9 / 7 8 H 0 1 L 2 1 / 3 3 6 H 0 1 L 2 9 / 7 3 9 H 0 1 L 2 1 / 3 3 1 H 0 1 L 2 9 / 8 6 1 - 2 9 / 8 8 5 H 0 1 L 2 1 / 3 2 9 H 0 1 L 2 7 / 0 6 - 2 7 / 0 7