(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4840382号 (P4840382)

(45) 発行日 平成23年12月21日(2011.12.21)

(24) 登録日 平成23年10月14日(2011.10.14)

(51) Int. CL.

(21) 出願番号

(22) 出願日

F I

HO5B 41/24 (2006.01)

HO5B 41/24

$\mathbf{Z}$

請求項の数 20 (全 43 頁)

(62) 分割の表示 特願2001-401532 (P2001-401532) の分割 原出願日 平成13年12月28日 (2001.12.28) 特開2008-166298 (P2008-166298A) 平成20年7月17日 (2008.7.17) 審査請求日 平成20年3月17日 (2008.3.17)

特願2008-59669 (P2008-59669)

平成20年3月10日 (2008.3.10)

||(73)特許権者 000005832

パナソニック電工株式会社

大阪府門真市大字門真1048番地

(74)代理人 100087767

弁理士 西川 惠清

||(72)発明者 光安 啓

大阪府門真市大字門真1048番地 松下

電工株式会社内

|(72)発明者 佐藤 勝己

大阪府門真市大字門真1048番地 松下

電工株式会社内

(72)発明者 濱本 勝信

大阪府門真市大字門真1048番地 松下

電工株式会社内

最終頁に続く

(54) 【発明の名称】放電灯点灯装置

### (57)【特許請求の範囲】

## 【請求項1】

少なくとも1つの平滑コンデンサ及びスイッチング素子を有し前記スイッチング素子をオン・オフすることで所定の直流電圧を出力する昇圧チョッパ回路からなる直流電源回路と、前記直流電源回路の出力端に接続されたスイッチング素子2つの直列回路を少なくとも1つ有し前記2つのスイッチング素子が交互にオン・オフすることによって前記直流電源回路が出力する直流電圧を高周波電圧に変換するインバータ回路と、少なくとも1つの放電灯と少なくとも1つの共振インダクタ及び共振コンデンサとを有し前記インバータ回路から高周波電圧を供給されて前記放電灯が点灯する負荷回路と、直流電源回路のスイッチング素子のオン・オフ時間の制御信号を出力する第1の制御手段と、第1の制御手段から出力される制御信号によって直流電源回路のスイッチング素子の駆動信号を出力するドライブ回路と、インバータ回路の各スイッチング素子を制御する制御用集積回路とを備え

10

前記制御用集積回路は、前記インバータ回路のスイッチング素子のオン・オフ時間の制御信号を出力する第2の制御手段と、前記第2の制御手段から出力される制御信号によって前記インバータ回路の各スイッチング素子の駆動信号を出力するドライブ回路と、前記第1の制御手段、及びドライブ回路を起動するための制御電源を供給する起動回路と、前記第1の制御手段、第2の制御手段、及びドライブ回路が起動した後の前記放電灯のフィラメントの先行予熱期間及び始動電圧印加期間を設定し前記各期間に対応した信号を出力する第1のタイマ手段と、前記第1のタイマ手段の出力に応じて前記イ

ンバータ回路のスイッチング素子のオン・オフ時間を切替える動作切替手段と、前記直流電源回路の出力電圧を検出した信号を前記第1の制御手段に出力する電源出力検出回路と、前記電源出力検出回路の出力信号と所定のしきい値とを比較して、前記電源出力検出回路の出力信号がしきい値より低い場合に、前記インバータ回路の出力を低下させるよう制御する第2の出力抑制手段とを備え、

前記第2の出力抑制手段は、前記第1のタイマ手段で設定される始動電圧印加期間の開始から終了までの間の所定の時間までは動作を停止することを特徴とする放電灯点灯装置

### 【請求項2】

前記制御用集積回路は、外部から入力される信号を、前記放電灯の点灯状態を制御するための放電灯制御信号に変換する信号変換手段と、前記放電灯制御信号に基づいて前記放電灯の出力を調光制御する出力補正手段とを備えることを特徴とする請求項1記載の放電灯点灯装置。

## 【請求項3】

前記インバータ回路と負荷回路とのうち少なくともいずれか一方に前記放電灯の点灯動作状態を検出する動作検出回路を備え、前記出力補正手段は前記動作検出回路からの信号と前記放電灯制御信号との比較演算を行う演算手段を備えて、比較演算結果を前記第2の制御手段に出力し、前記第2の制御手段は前記比較演算結果に基づいて前記インバータ回路のスイッチング素子のオン・オフ時間の制御信号を出力することを特徴とする請求項2記載の放電灯点灯装置。

#### 【請求項4】

前記第1の制御手段、第2の制御手段、及びドライブ回路が起動し、前記ドライブ回路が前記直流電源回路、インバータ回路の各スイッチング素子の駆動信号の出力を開始した時点では、前記出力補正手段は前記放電灯の出力を調光制御する動作を停止していることを特徴とする請求項2または3記載の放電灯点灯装置。

### 【請求項5】

前記出力補正手段は、前記第1のタイマ手段で設定される先行予熱期間が終了してから 始動電圧印加期間が終了するまでの間の所定の時間までは、前記放電灯の出力を調光制御 する動作を停止していることを特徴とする請求項4記載の放電灯点灯装置。

## 【請求項6】

前記出力補正手段は、前記第1のタイマ手段で設定される始動電圧印加期間の終了時点で前記放電灯の出力を調光制御する動作を開始することを特徴とする請求項4または5記載の放電灯点灯装置。

### 【請求項7】

前記放電灯の異常状態を検出して異常検出信号を出力する異常検出回路を備え、前記制御用集積回路は、前記異常検出信号に基づいて異常状態であるか否かを判別する異常判別手段と、異常状態が所定の期間継続したか否かを判別する第2のタイマ手段と、前記異常判別手段が異常状態であると判別し、第2のタイマ手段が異常状態は所定の期間継続したと判別した場合、前記インバータ回路と直流電源回路とのうち少なくともいずれか一方の出力を低下、もしくは停止させるよう制御する第1の出力抑制手段とを備えることを特徴とする請求項1乃至6いずれか記載の放電灯点灯装置。

#### 【請求項8】

前記制御用集積回路は、前記第1の出力抑制手段が動作を開始した後、前記インバータ 回路と直流電源回路とのうち少なくともいずれか一方の出力を低下、もしくは停止するよ う制御する出力抑制期間を設定する第3のタイマ手段を備え、前記出力抑制期間が経過し た後は、前記第1のタイマ手段は初期状態にリセットされて再動作することを特徴とする 請求項7記載の放電灯点灯装置。

### 【請求項9】

前記第1のタイマ手段、及び第2のタイマ手段で設定される時間は負の温度特性を有し、前記第3のタイマ手段で設定される時間は正の温度特性を有することを特徴とする請求

10

20

30

40

項8記載の放電灯点灯装置。

### 【請求項10】

前記第1の制御手段は、前記電源出力検出回路の出力信号に基づいて前記直流電源回路のスイッチング素子のオン・オフ時間を制御し、前記異常検出回路は、前記インバータ回路もしくは負荷回路に流れる共振電流波形を検出し、前記異常判別手段は、前記異常検出回路が検出した共振電流波形の位相によって前記放電灯が異常状態であるか否かを判別し、且つ前記直流電源回路の起動時に、前記電源出力検出回路が検出した出力電圧が所定の電圧より低い場合は、前記異常判別手段と第1の出力抑制手段とのうち少なくともいずれか一方の動作を停止させることを特徴とする請求項7乃至9いずれか記載の放電灯点灯装置。

【請求項11】

前記異常判別手段と第2のタイマ手段と第1の出力抑制手段とのうち少なくともいずれか一つは、前記第1のタイマ手段で設定される先行予熱期間が終了するまでの所定の時間までは、動作を停止していることを特徴とする請求項7乃至10いずれか記載の放電灯点灯装置。

#### 【請求項12】

前記異常判別手段と第2のタイマ手段と第1の出力<u>抑制</u>手段とのうち少なくともいずれか一つは、前記第1のタイマ手段で設定される先行予熱期間が終了してから始動電圧印加期間が終了するまでの間の所定の時間までは、動作を停止していることを特徴とする請求項7乃至10いずれか記載の放電灯点灯装置。

【請求項13】

前記直流電源回路の入力電圧を検出する電源入力検出回路を備え、前記制御用集積回路 は、前記電源入力検出回路の出力信号としきい値とを比較して、前記電源入力検出回路の 出力信号がしきい値より高い場合に、前記制御用集積回路の前記第1のタイマ手段、第1 の制御手段、及び第2の制御手段の動作を開始させる比較手段を備えることを特徴とする 請求項1乃至12いずれか記載の放電灯点灯装置。

### 【請求項14】

前記直流電源回路の入力電圧を検出する電源入力検出回路を備え、前記制御用集積回路は、前記電源入力検出回路の出力信号と第1のしきい値とを比較して、前記電源入力検出回路の出力信号が第1のしきい値より高い場合に、前記制御用集積回路の前記第1のタイマ手段、第1の制御手段、及び第2の制御手段の動作を開始させ、前記電源入力検出回路の出力信号と第1のしきい値より低い第2のしきい値とを比較して、前記電源入力検出回路の出力信号が第2のしきい値より低い場合に低電圧状態であると判別する比較手段と、低電圧状態が所定の期間継続したか否かを判別する第4のタイマ手段とを備え、前記比較手段が低電圧状態であると判別し、第4のタイマ手段が低電圧状態は所定の期間継続したと判別した場合、前記インバータ回路と直流電源回路との動作は停止することを特徴とする請求項1乃至12いずれか記載の放電灯点灯装置。

## 【請求項15】

前記直流電源回路の出力電圧を検出した信号を前記第1の制御手段に出力する電源出力 検出回路を備え、前記第1の制御手段は、前記電源出力検出回路の出力信号と前記電源入 力検出回路の出力信号とに基づいて前記直流電源回路のスイッチング素子のオン・オフ時 間を制御することを特徴とする請求項13または14記載の放電灯点灯装置。

【請求項16】

前記第1の出力抑制手段、及び第2の出力抑制手段が動作を停止して、前記第1の制御手段、及び第2の制御手段が再起動する場合に、前記制御用集積回路は、前記第2の制御手段を前記第1の制御手段より先に再起動させるために前記第1の制御手段を再起動する信号を遅延させる遅延手段を備えることを特徴とする請求項10乃至15いずれか記載の放電灯点灯装置。

### 【請求項17】

前記制御用集積回路は、クロック信号を生成する発振器を備え、前記第1乃至4のタイ

10

20

30

40

マ手段のうち少なくとも第1,第4のタイマ手段は、タイマ手段毎に設定された回数の前記クロック信号をカウントするカウンタ手段を備えることを特徴とする請求項<u>14乃至1</u>6いずれか記載の放電灯点灯装置。

## 【請求項18】

前記制御用集積回路は、<u>前記直流電源回路の出力電圧が負の温度特性を有するように</u>制御し、前記インバータ回路の出力電圧の周波数が正の温度特性を有するように制御することを特徴とする請求項1乃至17いずれか記載の放電灯点灯装置。

## 【請求項19】

前記直流電源回路、インバータ回路、及び制御用集積回路が実装されるプリント基板を備え、前記直流電源回路のスイッチング素子は、前記制御用集積回路の第1の制御手段からの制御信号を入力されたドライバ回路が出力する駆動信号の出力端子の近傍に配置され、前記インバータ回路のスイッチング素子は、前記制御用集積回路の第2の制御手段からの制御信号を入力されたドライバ回路が出力する駆動信号の出力端子の近傍に配置されて、前記直流電源回路とインバータ回路との各スイッチング素子は互いに並んで配置されることを特徴とする請求項1乃至18いずれか記載の放電灯点灯装置。

### 【請求項20】

前記直流電源回路、インバータ回路、及び制御用集積回路が実装されるプリント基板を備え、前記制御用集積回路のパッケージの形状は直方体であり、パッケージの長手方向に沿った両側面に前記プリント基板の信号配線と接続するリードを設けており、前記プリント基板の面形状は長方形であり、長手方向の一端に電源入力端子を配置し、他端に出力端子を配置し、長手方向の一端側から他端側に直流電源回路、制御用集積回路、インバータ回路、負荷回路の順に配置し、前記直流電源回路のスイッチング素子は、前記制御用集積回路の第1の制御手段からの制御信号を入力されたドライバ回路からの駆動信号を出力するリードの近傍に配置され、前記インバータ回路のスイッチング素子は、前記制御用集積回路の第2の制御手段からの制御信号を入力されたドライバ回路からの駆動信号を出力するリードの近傍に配置されることを特徴とする請求項1乃至18いずれか記載の放電灯点灯装置。

## 【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、放電ランプを高周波電力で点灯させる放電灯点灯装置に関するものである。

### 【背景技術】

## [0002]

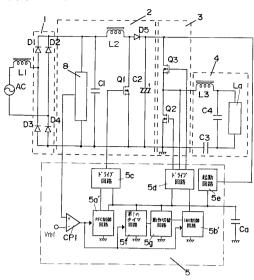

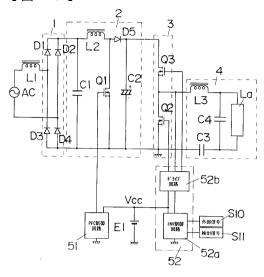

図40に示す従来の放電灯点灯装置は、商用電源よりなる交流電源ACと、交流電源ACの一端に直列接続された雑音防止用のフィルタチョークL1と、ダイオードD1~D4をブリッジ接続して交流電源ACの出力を全波整流する整流器1と、整流器1の全波整流出力を所望の直流電圧に変換する直流電源回路2と、直流電源回路2が出力する直流電圧を高周波電圧に変換するインバータ回路3と、少なくとも1つの放電灯を有し、インバータ回路3から高周波電圧を供給されて放電灯が点灯する負荷回路4と、チョッパ制御用集積回路51と、インバータ制御用集積回路52と、制御電源E1とから構成される。

#### [0003]

直流電源回路2は、整流器1の高圧出力側に直列接続したインダクタL2,ダイオードL5の直列回路と、整流器1の出力端間に接続したコンデンサC1と、インダクタL2を介してコンデンサC1に並列接続したスイッチング素子Q1と、ダイオードD5を介してスイッチング素子Q1に並列接続した平滑コンデンサC2とからなり、スイッチング素子Q1をオン・オフすることによって全波整流した電圧をチョッピングして所望の直流電圧を得る昇圧チョッパ回路を構成している。

## [0004]

インバータ回路 3 は、MOSFETよりなるスイッチング素子Q2,Q3の直列回路を 平滑コンデンサC2の両端間に接続したハーフブリッジ型のインバータ回路であり、スイ 10

20

30

10

20

30

40

50

ッチング素子Q2,Q3が交互にオン・オフすることによって、直流電源回路2が出力する直流電圧を高周波電圧に変換している。

#### [00005]

負荷回路4は、ローサイド側のスイッチング素子Q2のドレイン・ソース間に接続した 共振用インダクタL3、共振用コンデンサC4、直流カット用コンデンサC3の直列回路 と、共振用コンデンサC4に並列接続した放電灯Laとからなり、インバータ回路3から 高周波電圧を供給されて放電灯Laが点灯する。

## [0006]

チョッパ制御用集積回路 5 1 は、PFC制御回路からなり、スイッチング素子Q1のオン・オフを制御することで、入力電圧の変動や負荷の軽重に関わらず、昇圧チョッパ回路の出力電圧を一定に制御することができるとともに、整流器1の入力電流波形を入力電圧波形と相似な正弦波に改善することができて、例えばモトローラ社製のMC33262等の汎用力率改善用集積回路を使用している。

## [0007]

インバータ制御用集積回路52は、いわゆるHVIC(High Voltage IC)よりなり、INV制御回路52aとドライブ回路52bとから構成されている。INV制御回路52aは、インバータ回路3のスイッチング素子Q2,Q3のオン・オフ時間の制御信号を出力し、ドライブ回路52bは、INV制御回路52aから出力される制御信号によって駆動信号を出力して、インバータ回路3のスイッチング素子Q2,Q3を直接駆動している。スイッチング素子Q2,Q3が交互にオン・オフ駆動されて、平滑コンデンサC2から放電灯Laに電力を供給する状態と、直流カット用コンデンサC3を電源として放電灯Laに電力を供給する状態とを交互に繰り返すことによって、放電灯Laに高周波電圧を印加して、高周波の交番電流を流すようになっている。

#### [0008]

また、インバータ制御用集積回路 5 2 には放電灯 L a の寿命末期時に検出信号 S 1 1 を入力されてインバータ回路 3 の発振を停止させる異常検出機能や、外部信号 S 1 0 によって放電灯の出力を変化させる調光機能などが設けられ、これらの回路を含めてワンチップで構成されている。

## [0009]

なお、チョッパ制御用集積回路 5 1、インバータ制御用集積回路 5 2 の電源としては、 直流電圧源 E 1 から生成した電圧 V c c が供給されている。

## [0010]

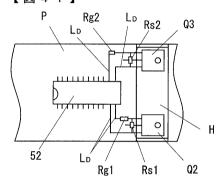

上記集積回路を用いた放電灯点灯装置の一例として、特開平11-238590号公報で示される放電灯点灯装置が提案されており、図41にプリント基板30におけるインバータ制御用集積回路52とスイッチング素子Q1,Q2との位置関係を説明するための概略説明図を示す。

## [0011]

インバータ回路3は、直流電源2の両端間に接続されるスイッチング素子Q2,Q3の直列回路を備えており、スイッチング素子Q2,Q3はプリント基板Pの短手方向に沿って離間して直線状に配設して、両スイッチング素子Q1,Q2で一つの放熱板Hを共用している。スイッチング素子Q2,Q3のオン・オフを制御するインバータ制御用集積回路52のパッケージ本体はプリント基板Pに長手方向が一致し且つ長手方向に沿って両スイッチング素子Q2,Q3が位置するように配設している。インバータ制御用集積回路52のパッケージ本体の一方の長辺部にスイッチング素子Q2を駆動信号配線LD,ゲート抵抗Rg1を介して接続するためのリードが配置され、他方の長辺部にスイッチング素子Q3を駆動信号配線LD,ゲート抵抗Rg2を介して接続するためのリードを配置しており、また、スイッチング素子Q1,Q2の各ゲート・ソース間には抵抗Rs1,Rs2が接続されている。

### [0012]

このようにインバータ制御用集積回路52とスイッチング素子Q2,Q3とを配置する

ことにより、駆動信号配線LDをできるだけ短くして配線のインダクタンスを小さくするとともに、両スイッチング素子Q2,Q3で駆動信号配線LDの長さが略同じになるように決められているので、耐ノイズ性に優れた小型の放電灯点灯装置を実現することができる。

## [0013]

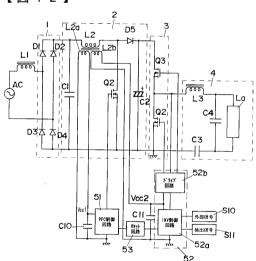

次に、図42に別の従来例の回路構成を示す。この放電灯点灯装置は、特許第3106 592号にて提案されているものであり、回路構成は図40に示す従来例と略同様であり 、同様の構成には同一の符号を付して説明は省略する。

#### [0014]

この実施例では、直流電源回路2のインダクタL2に磁気結合した巻線L2a,L2bを備えて、チョッパ制御用集積回路51、インバータ制御用集積回路52の各電源電圧Vcc1,Vcc2を各々巻線L2a、L2bからコンデンサC10,C11を介して供給するようにしている。

## [0015]

また、放電灯 L a の寿命末期時等には、インバータ制御用集積回路 5 2 自身をリセット信号で初期化してインバータ回路 3 の発振動作を停止させるとともに、このリセット信号をリセット回路 5 3 を介してチョッパ制御用集積回路 5 1 に入力して、直流電源回路 2 のチョッパ動作も停止させる。よって、発振停止時の電力の無駄を低減することができ、かつ、安全性も向上させることができる。

【特許文献1】特開平11-238590号公報

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0016]

しかし、これら従来の放電灯点灯装置では、直流電源回路 2 とインバータ回路 3 との制御に別個の集積回路を設ける必要があり、これらの部品を実装するプリント基板のパターン配線に制約を受ける。また、図 4 2 に示す従来例のように、放電灯 L a の寿命末期時にインバータ回路 3 を停止させる際に直流電源回路 2 も停止させる場合、この動作を制御する部品がさらに必要になるため放電灯点灯装置の小型化がさらに困難となる。その結果、これらの制御回路が外来ノイズの影響を受けやすくなり、誤動作が発生するという問題がある。

### [0017]

本発明は、上記事由に鑑みてなされたものであり、その目的は、部品点数が少なく、小型の放電灯点灯装置を提供することにある。

## 【課題を解決するための手段】

## [0018]

請求項1の発明は、少なくとも1つの平滑コンデンサ及びスイッチング素子を有し前記スイッチング素子をオン・オフすることで所定の直流電圧を出力する昇圧チョッパ22ことで所定の直流電圧を出力する昇圧チョッパ22この直流電源回路を少なくとも1つ有し前記2つのスイッチング素子が交互にオン・オフタロ路を少なくとも1つ有し前記2つのスイッチング素子が交互にオン・オフタロ路が出力する直流電圧を換するインバータロ路が出力する直流で変換するインデンサととも1つの対象ででは、少なくとも1つの放電圧を供給されて前記放電灯が点灯する第1の出海でのおいた。第1の制御手段から出力される制御信号を出力する第1の制御手段と、前記インバータ回路のスイッチング素子の制御のスイッチング素子の制御の表スイッチング素子の制御のまたが前記制御用集積回路とを備え、前記制御用集積回路と、前記インバータ回路の入イッチンが素子の制御のされる制御信号によって前記インバータ回路の各スイッチング素子の駆動信号を出力するドライブ回路と、前記引力である制御手段と、前記第1の制御手段、第2の制御手段、及びドライブの制御電源を供給する起動回路と、前記第1の制御手段、第2の制御手段、及びドライブの制御電源を供給する起動回路と、前記第1の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第2の制御手段、第3の制御手段、第3の制御手段、第3の発表を対している。

10

20

30

40

回路が起動した後の前記放電灯のフィラメントの先行予熱期間及び始動電圧印加期間を設定し前記各期間に対応した信号を出力する第1のタイマ手段と、前記第1のタイマ手段の出力に応じて前記インバータ回路のスイッチング素子のオン・オフ時間を切替える動作切替手段と、前記直流電源回路の出力電圧を検出した信号を前記第1の制御手段に出力する電源出力検出回路と、前記電源出力検出回路の出力信号と所定のしきい値とを比較して、前記電源出力検出回路の出力信号がしきい値より低い場合に、前記インバータ回路の出力を低下させるよう制御する第2の出力抑制手段とを備え、前記第2の出力抑制手段は、前記第1のタイマ手段で設定される始動電圧印加期間の開始から終了までの間の所定の時間までは動作を停止することを特徴とする。

### [0019]

請求項2の発明は、請求項1において、前記制御用集積回路は、外部から入力される信号を、前記放電灯の点灯状態を制御するための放電灯制御信号に変換する信号変換手段と、前記放電灯制御信号に基づいて前記放電灯の出力を調光制御する出力補正手段とを備えることを特徴とする。

#### [0020]

請求項3の発明は、請求項2において、前記インバータ回路と負荷回路とのうち少なくともいずれか一方に前記放電灯の点灯動作状態を検出する動作検出回路を備え、前記出力補正手段は前記動作検出回路からの信号と前記放電灯制御信号との比較演算を行う演算手段を備えて、比較演算結果を前記第2の制御手段に出力し、前記第2の制御手段は前記比較演算結果に基づいて前記インバータ回路のスイッチング素子のオン・オフ時間の制御信号を出力することを特徴とする。

#### [0021]

請求項4の発明は、請求項2または3において、前記第1の制御手段、第2の制御手段、及びドライブ回路が起動し、前記ドライブ回路が前記直流電源回路、インバータ回路の各スイッチング素子の駆動信号の出力を開始した時点では、前記出力補正手段は前記放電灯の出力を調光制御する動作を停止していることを特徴とする。

#### [0022]

請求項5の発明は、請求項4において、前記出力補正手段は、前記第1のタイマ手段で設定される先行予熱期間が終了してから始動電圧印加期間が終了するまでの間の所定の時間までは、前記放電灯の出力を調光制御する動作を停止していることを特徴とする。

## [0023]

請求項6の発明は、請求項4または5において、前記出力補正手段は、前記第1のタイマ手段で設定される始動電圧印加期間の終了時点で前記放電灯の出力を調光制御する動作を開始することを特徴とする。

## [0024]

請求項7の発明は、請求項1乃至6いずれかにおいて、前記放電灯の異常状態を検出して異常検出信号を出力する異常検出回路を備え、前記制御用集積回路は、前記異常検出信号に基づいて異常状態であるか否かを判別する異常判別手段と、異常状態が所定の期間継続したか否かを判別する第2のタイマ手段と、前記異常判別手段が異常状態であると判別し、第2のタイマ手段が異常状態は所定の期間継続したと判別した場合、前記インバータ回路と直流電源回路とのうち少なくともいずれか一方の出力を低下、もしくは停止させるよう制御する第1の出力抑制手段とを備えることを特徴とする。

#### [0025]

請求項8の発明は、請求項7において、前記制御用集積回路は、前記第1の出力抑制手段が動作を開始した後、前記インバータ回路と直流電源回路とのうち少なくともいずれか一方の出力を低下、もしくは停止するよう制御する出力抑制期間を設定する第3のタイマ手段を備え、前記出力抑制期間が経過した後は、前記第1のタイマ手段は初期状態にリセットされて再動作することを特徴とする。

### [0026]

請求項9の発明は、請求項8において、前記第1のタイマ手段、及び第2のタイマ手段

10

20

30

40

で設定される時間は負の温度特性を有し、前記第3のタイマ手段で設定される時間は正の温度特性を有することを特徴とする。

### [0027]

請求項10の発明は、請求項7乃至9いずれかにおいて<u>、前</u>記第1の制御手段は、前記電源出力検出回路の出力信号に基づいて前記直流電源回路のスイッチング素子のオン・オフ時間を制御し、前記異常検出回路は、前記インバータ回路もしくは負荷回路に流れる共振電流波形を検出し、前記異常判別手段は、前記異常検出回路が検出した共振電流波形の位相によって前記放電灯が異常状態であるか否かを判別し、且つ前記直流電源回路の起動時に、前記電源出力検出回路が検出した出力電圧が所定の電圧より低い場合は、前記異常判別手段と第1の出力抑制手段とのうち少なくともいずれか一方の動作を停止させることを特徴とする。

[0028]

請求項11の発明は、請求項7乃至10いずれかにおいて、前記異常判別手段と第2のタイマ手段と第1の出力<u>抑制</u>手段とのうち少なくともいずれか一つは、前記第1のタイマ手段で設定される先行予熱期間が終了するまでの所定の時間までは、動作を停止していることを特徴とする。

### [0029]

請求項12の発明は、請求項7乃至10いずれかにおいて、前記異常判別手段と第2のタイマ手段と第1の出力抑制手段とのうち少なくともいずれか一つは、前記第1のタイマ手段で設定される先行予熱期間が終了してから始動電圧印加期間が終了するまでの間の所定の時間までは、動作を停止していることを特徴とする。

[0030]

請求項13の発明は、請求項1乃至12いずれかにおいて、前記直流電源回路の入力電圧を検出する電源入力検出回路を備え、前記制御用集積回路は、前記電源入力検出回路の出力信号としきい値とを比較して、前記電源入力検出回路の出力信号がしきい値より高い場合に、前記制御用集積回路の前記第1のタイマ手段、第1の制御手段、及び第2の制御手段の動作を開始させる比較手段を備えることを特徴とする。

[0031]

請求項14の発明は、請求項1乃至12いずれかにおいて、前記直流電源回路の入力電圧を検出する電源入力検出回路を備え、前記制御用集積回路は、前記電源入力検出回路の出力信号が第1のしきい値とを比較して、前記電源入力検出回路の出力信号が第1のしきい値より高い場合に、前記制御用集積回路の前記第1のタイマ手段、第1の制御手段、及び第2の制御手段の動作を開始させ、前記電源入力検出回路の出力信号と第1のしきい値より低い第2のしきい値とを比較して、前記電源入力検出回路の出力信号が第2のしきい値より低い場合に低電圧状態であると判別する比較手段と、低電圧状態が所定の期間継続したか否かを判別する第4のタイマ手段とを備え、前記比較手段が低電圧状態であると判別し、第4のタイマ手段が低電圧状態は所定の期間継続したと判別した場合、前記インバータ回路と直流電源回路との動作は停止することを特徴とする。

[0032]

請求項15の発明は、請求項13または14において、前記直流電源回路の出力電圧を検出した信号を前記第1の制御手段に出力する電源出力検出回路を備え、前記第1の制御手段は、前記電源出力検出回路の出力信号と前記電源入力検出回路の出力信号とに基づいて前記直流電源回路のスイッチング素子のオン・オフ時間を制御することを特徴とする。

[0034]

請求項1<u>6</u>の発明は、請求項<u>10乃至15いずれか</u>において、前記第1の出力抑制手段、及び第2の出力抑制手段が動作を停止して、前記第1の制御手段、及び第2の制御手段が再起動する場合に、前記制御用集積回路は、前記第2の制御手段を前記第1の制御手段より先に再起動させるために前記第1の制御手段を再起動する信号を遅延させる遅延手段を備えることを特徴とする。

[0035]

10

20

30

40

請求項1<u>7</u>の発明は、請求項14乃至1<u>6</u>いずれかにおいて、前記制御用集積回路は、クロック信号を生成する発振器を備え、前記第1乃至4のタイマ手段のうち少なくとも第1,第4のタイマ手段は、タイマ手段毎に設定された回数の前記クロック信号をカウントするカウンタ手段を備えることを特徴とする。

## [0036]

請求項1<u>8</u>の発明は、請求項1乃至1<u>7</u>いずれかにおいて、前記制御用集積回路は、前記直流電源回路の出力電圧が負の温度特性を有するように制御し、前記インバータ回路の出力電圧の周波数が正の温度特性を有するように制御することを特徴とする。

### [0037]

請求項<u>19</u>の発明は、請求項1乃至1<u>8</u>いずれかにおいて、前記直流電源回路、インバータ回路、及び制御用集積回路が実装されるプリント基板を備え、前記直流電源回路のスイッチング素子は、前記制御用集積回路の第1の制御手段からの制御信号を入力されたドライバ回路が出力する駆動信号の出力端子の近傍に配置され、前記インバータ回路のスイッチング素子は、前記制御用集積回路の第2の制御手段からの制御信号を入力されたドライバ回路が出力する駆動信号の出力端子の近傍に配置されて、前記直流電源回路とインバータ回路との各スイッチング素子は互いに並んで配置されることを特徴とする。

#### [0038]

請求項2<u>0</u>の発明は、請求項1乃至1<u>8</u>いずれかにおいて、前記直流電源回路、インバータ回路、及び制御用集積回路が実装されるプリント基板を備え、前記制御用集積回路のパッケージの形状は直方体であり、パッケージの長手方向に沿った両側面に前記プリント基板の信号配線と接続するリードを設けており、前記プリント基板の面形状は長方形であり、長手方向の一端に電源入力端子を配置し、他端に出力端子を配置し、長手方向の一端側に直流電源回路、制御用集積回路、インバータ回路、負荷回路の順に配置し、前記直流電源回路のスイッチング素子は、前記制御用集積回路の第1の制御手段からの制御信号を入力されたドライバ回路からの駆動信号を出力するリードの近傍に配置され、前記インバータ回路のスイッチング素子は、前記制御用集積回路の第2の制御手段からの制御信号を入力されたドライバ回路からの駆動信号を出力するリードの近傍に配置されることを特徴とする。

## 【発明の効果】

## [0039]

本発明は、部品点数が少なく、小型の放電灯点灯装置を提供することができるという効果がある。また、直流電源回路の出力が直流電源回路の出力電力の供給限界を超える等の原因で直流電源回路の出力電圧が所定の電圧より低下した場合には、インバータ回路のスイッチング素子には共振電流の進相波形によるストレスが印加されるが、この場合にはインバータ回路の出力を低下させることで、ストレスを低減させることができるという効果がある。さらに、起動直後のリプル電圧による誤動作の発生を防ぐことができるという効果もある。

### [0040]

請求項2の発明によれば、さらに外部からの信号によって調光制御を行うことができるという効果がある。

## [0041]

請求項3の発明によれば、さらに放電灯の点灯動作状態に応じて出力制御を行うことができるという効果がある。

## [0042]

請求項4の発明によれば、さらに回路素子に過大なストレスが印加されることがないという効果がある。

#### [0043]

請求項5の発明によれば、さらに回路素子に過大なストレスが印加されることなく、放電灯のフィラメントに所定の予熱電流を所定の時間、確実に供給することができるという効果がある。

10

20

30

40

#### [0044]

請求項6の発明によれば、さらに回路素子に過大なストレスが印加されることなく、予熱時、始動時に放電灯のフィラメントに所定の電流、電圧を所定の時間、確実に供給することができるという効果がある。

## [0045]

請求項7の発明によれば、さらに放電灯の異常時には出力を低減させて回路素子に過大なストレスが印加されることを防ぐことができるという効果がある。

## [0046]

請求項8の発明によれば、さらに再起動時には、先行予熱期間と始動電圧印加期間とを経て起動し、各素子にストレスが印加されることを防ぐことができるという効果がある。

## [0047]

請求項9の発明によれば、さらに周囲の環境変化をはじめ、起動初期から安定点灯状態に移行したときや、放電灯の異常となったとき等、周囲温度が変化した場合、周囲温度の変化に応じた出力制御の変化をもたらし、直流電源回路及びインバータ回路の出力制御動作性能を向上させて、安定した最適動作を維持することができるという効果がある。

#### [0048]

請求項10の発明によれば、さらに直流電源回路の出力電圧に応じた直流回路の出力制御を行うことができ、また負荷異常による共振電流の進相動作による回路素子へのストレスの印加を防ぐことができるという効果がある。さらに、起動初期において、直流電源回路の出力電圧の立ち上がり時の過渡動作時に放電灯が正常であるにも関わらず、負荷回路のLC共振回路に出力するインバータ回路の入力電圧が低いために発生する進相動作は検出しないので、誤検出を防止することができるという効果もある。

#### [0049]

請求項11の発明によれば、さらに請求項10の電源出力検出回路を備えていなくても、負荷異常による共振電流の進相動作による回路素子へのストレスの印加を防ぐことができ、且つ、起動初期において、直流電源回路の出力電圧の立ち上がり時の過渡動作時に放電灯が正常であるにも関わらず、負荷回路のLC共振回路に出力するインバータ回路の入力電圧が低いために発生する進相動作は検出しないので、誤検出を防止することができるという効果がある。

## [0050]

請求項12の発明によれば、さらに請求項11と同様の効果を得ることができる。

## [0051]

請求項13の発明によれば、さらに直流電源回路の入力電圧がかなり低い場合に、直流電源回路及びインバータ回路を動作させることによって生じる各々のスイッチング素子への過大なストレスを低減することができ、さらに、交流電源が復帰した場合は先行予熱期間から起動させれば、放電灯の寿命を損なうことがないという効果がある。

## [0052]

請求項14の発明によれば、さらに請求項13と同様の効果を得ることができ、さらに、直流電源回路に入力される電圧が低下した場合、ヒステリシス特性により、電圧の低下が所定の期間継続した後に出力が停止するため、外来ノイズ、比較手段の出力のチャタリング等で誤動作して停止する恐れがなくなるという効果がある。また、交流電源が一般の商用交流電源であれば、その瞬時電圧降下は比較的短時間で大きい電圧降下が頻繁に発生しやすい傾向にあるが、電圧降下から出力停止するまでに時間遅れがあるために、出力が頻繁に停止して放電灯が消灯することによる不快感を使用者に与えることがないという効果もある。

## [0053]

請求項15の発明によれば、さらに直流電源回路の出力電圧を所望のレベルで安定制御し、交流電源から入力される入力電流の波形歪みを大幅に低減することができるという効果がある。

## [0055]

50

10

20

30

10

20

30

40

50

請求項1<u>6</u>の発明によれば、さらに再起動するために動作停止状態の解除信号が出力された場合でも、解除信号に遅延を持たせることによって、部品、素子へのストレスを抑えた状態で負荷状態を判別することができるという効果がある。

### [0056]

請求項1<u>7</u>の発明によれば、さらに同一のクロック信号を用いて出力制御を行うことによって、直流電源回路とインバータ回路との間の伝達の遅れや、干渉を最小限に抑えることができるという効果がある。

## [0057]

請求項1<u>8</u>の発明によれば、さらに放電灯の周囲温度が高い状態では、ランプ電流の過剰な増加を抑制し、逆に放電灯の周囲温度が低い状態では、ランプ電流を増加させることによって、放電灯を安定して点灯させることができるという効果がある。

#### [0058]

請求項<u>19</u>の発明によれば、さらにプリント基板上の配線を行うことが比較的容易になり、信号線の交差によって引き起こされるノイズによる誤動作を防止することができ、さらにスイッチング素子の駆動信号の配線が最短となって駆動信号のパターン面積を減少させて、輻射雑音を低減することができるという効果がある。

#### [0059]

請求項20の発明によれば、さらに請求項19と同様の効果を得ることができる。

【発明を実施するための最良の形態】

### [0060]

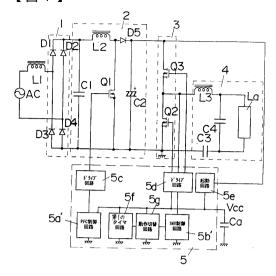

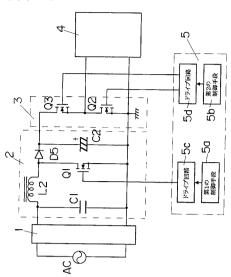

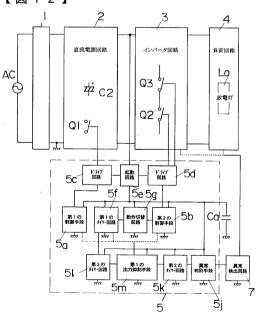

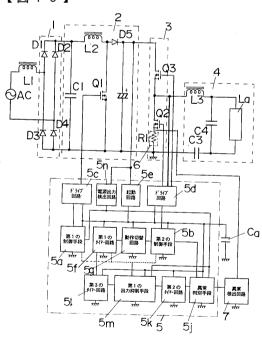

本発明の基本回路構成を図2~5に示し、各回路構成は図40に示す従来例と略同様の 構成を有しており、同様の構成には同一の符号を付して説明は省略する。

### [0061]

図2の放電灯点灯装置は、直流電源回路2とインバータ回路3とのスイッチング素子Q1,Q2,Q3をオン・オフ制御する1つの集積回路を構成する制御用集積回路5を備えており、制御用集積回路5は、直流電源回路2のスイッチング素子Q1のオン・オフ時間の制御信号を出力する第1の制御手段5aから出力される制御信号によってスイッチング素子Q1の駆動信号を出力するドライブ回路5cと、インバータ回路3のスイッチング素子Q2,Q3のオン・オフ時間の制御信号を出力する第2の制御手段5bと、第2の制御手段5bから出力される制御信号によってスイッチング素子Q2,Q3の駆動信号を出力するドライブ回路5dとから構成されることを特徴とする。この基本構成では、直流電源回路2を昇圧チョッパ回路で構成し、インバータ回路3をハーフブリッジ型のインバータ回路で構成しており、その動作は従来例の動作と同様である。

## [0062]

なお、直流電源回路 2 は、整流された電圧を所定の直流電圧に変換でき、そのスイッチング素子を制御用集積回路 5 で制御する構成であればどのような構成であってもよく、例えば、降圧チョッパ回路や昇降圧チョッパ回路であってもよい。

### [0063]

また、インバータ回路 3 は、スイッチング素子 2 つの直列回路を少なくとも 1 つ有し、この 2 つのスイッチング素子が交互にオン・オフすることによって、直流電源回路 2 が出力する直流電圧を高周波電圧に変換でき、これらのスイッチング素子を制御用集積回路 5 で制御する構成であればどのような構成であってもよく、例えば、フルブリッジ型のインバータ回路や複数のインバータ回路を備える構成であってもよい。

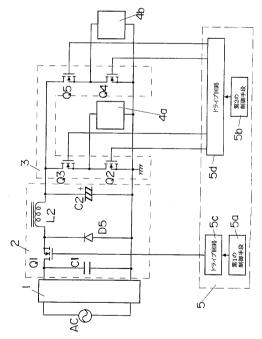

## [0064]

図3の放電灯点灯装置は、直流電源回路2を降圧チョッパ回路で構成したもので、整流器1の高圧出力側に直列接続したスイッチング素子Q1,インダクタL2の直列回路と、整流器1の出力端間に接続したコンデンサC1と、スイッチング素子Q1を介してコンデンサC1に並列接続したダイオードD5と、インダクタL2を介してダイオードD5に並列接続した平滑コンデンサC2とからなっており、整流電圧を降圧して所望の直流電圧に変換している。また、インバータ回路3は、平滑コンデンサC2の両端間に接続したスイ

ッチング素子Q2,Q3の直列回路、及びスイッチング素子Q4,Q5の直列回路からなる2つのハーフブリッジ型のインバータ回路であり、スイッチング素子Q2,Q3を交互にオン・オフし、スイッチング素子Q4,Q5を交互にオン・オフすることによって、負荷回路4a,4bに高周波電圧を各々供給している。

## [0065]

図4の放電灯点灯装置は、インバータ回路3を平滑コンデンサC2の両端間に接続したスイッチング素子Q2,Q3の直列回路、及びスイッチング素子Q4,Q5の直列回路からなるフルブリッジ型のインバータ回路で構成したものであり、制御用集積回路5によって、スイッチング素子Q3,Q4とスイッチング素子Q2,Q5とが交互にオン・オフ制御されて、スイッチング素子Q2,Q3の接続中点とスイッチング素子Q4,Q5の接続中点との間に接続されている負荷回路4に高周波電圧を供給している。

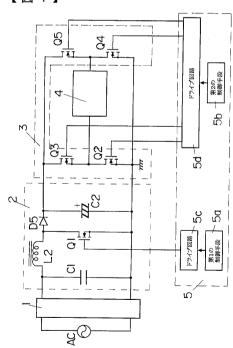

[0066]

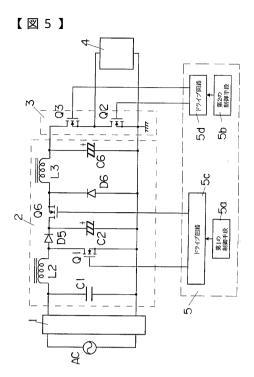

図5の放電灯点灯装置は、直流電回路2を昇降圧チョッパ回路で構成したもので、整流器1の高圧出力側に直列接続したインダクタL2,ダイオードD5,スイッチング素子Q6,インダクタL3の直列回路と、整流器1の出力端間に接続したコンデンサC1と、インダクタL2を介してコンデンサC1に並列接続したスイッチング素子Q1と、ダイオードD5を介してスイッチング素子Q1に並列接続した平滑コンデンサC2と、スイッチング素子Q6を介して平滑コンデンサC2に並列接続したダイオードD6と、インダクタL3を介してダイオードD6に並列接続した平滑コンデンサC6とからなっており、スイッチング素子Q1,Q6は制御用集積回路5によって制御されて、整流電圧を昇降圧して所望の直流電圧に変換している。

[0067]

以下、本発明の実施の形態を図面に基づいて説明する。

[0068]

(実施形態1)

図1に示す本実施形態の放電灯点灯装置の回路構成は、図40に示す従来例と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

[0069]

[0070]

次に本実施形態の動作について説明する。まず電源投入時には、起動回路5eが動作し、コンデンサCaの両端電圧を制御電圧Vccにまで立ち上げる。制御電圧Vccが立ち上がると、制御用集積回路5の各回路が動作を開始する。

[0071]

そして、PFC制御回路5 a '、INV制御回路5 b 'が動作し、ドライブ回路5 c , 5 d から駆動信号が出力されて直流電源回路2、インバータ回路3の各スイッチング素子Q1~Q3が発振を開始すると、第1のタイマ回路5 f は発振を開始してからの動作時間をカウントする。第1のタイマ回路5 f は、放電灯Laのフィラメントの先行予熱期間及

10

20

30

40

び始動電圧印加期間を設定されており、カウントした動作時間が先行予熱期間を終了するまでは、動作切替回路 5 g に予熱信号を出力し、動作切替回路 5 g は I N V 制御回路 5 b に予熱時のオン・オフ時間の制御信号を出力させて、ドライブ回路 5 d がその制御信号に応じたオン・オフ時間でスイッチング素子 Q 2 , Q 3 を駆動する駆動信号を出力することで、放電灯 L a のフィラメントに予熱電流が供給されて、フィラメントが予熱される。

### [0072]

先行予熱期間(予熱モード)が終了して、次に始動電圧印加期間が始まると、第1のタイマ回路5fは、カウントした動作時間が始動電圧印加期間を終了するまでは、動作切替回路5gに始動信号を出力し、動作切替回路5gはINV制御回路5b<sup>'</sup> に始動時のオン・オフ時間の制御信号を出力させて、ドライブ回路5dが制御信号に応じたオン・オフ時間でスイッチング素子Q2,Q3を駆動する駆動信号を出力することで、放電灯Laのフィラメント間に点灯するのに充分な始動電圧が印加されて、放電灯Laが点灯する。

#### [0073]

始動電圧印加期間(始動モード)が終了すると、第1のタイマ回路 5 f は、動作切替回路 5 g に点灯信号を出力し、動作切替回路 5 g は I N V 制御回路 5 b 'に点灯時のオン・オフ時間の制御信号を出力させて、ドライブ回路 5 d が制御信号に応じたオン・オフ時間でスイッチング素子 Q 2 , Q 3 を駆動する駆動信号を出力することで、放電灯 L a は所定の出力で点灯する。

## [0074]

この間、PFC制御回路5 a 'は直流電源回路2 の出力電圧を所定の電圧に制御しているので入力電圧が変動しても放電灯 L a の出力が変化することなく、且つ入力電流の高調波歪みを改善している。

## [0075]

このような本実施形態では、各制御回路を、1つの制御用集積回路5で構成しているため、部品点数を少なくでき、各回路を実装するプリント基板のパターン配線が容易になり、したがって小型の放電灯点灯装置を提供することができる。

### [0076]

なお、本実施形態では、直流電源回路 2 を昇圧チョッパ回路で構成しているが、図 3 や図 5 のように降圧チョッパ回路や昇降圧チョッパ回路で構成してもよく、また、インバータ回路 3 を図 4 のようにフルブリッジ型のインバータ回路としてもよい。

### [0077]

## (実施形態2)

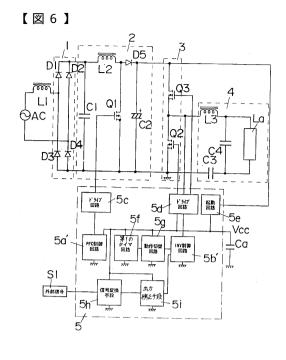

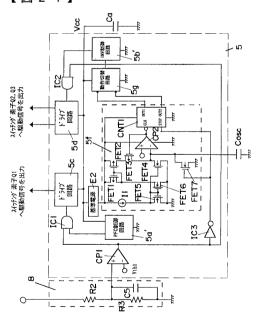

図6に示す本実施形態の放電灯点灯装置の回路構成は、図1に示す実施形態1と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

## [0078]

本実施形態の制御用集積回路5は、実施形態1の制御用集積回路5に信号変換手段5hと出力補正手段5iとを備えたもので、信号変換手段5hは、制御用集積回路5に入力される外部信号S1を放電灯Laの点灯状態を制御するための放電灯制御信号に変換し、出力補正手段5iは、放電灯制御信号に基づいて放電灯Laの出力を調光制御する調光信号をINV制御回路5b'は、出力補正手段5iからの調光信号に基づいて、例えばスイッチング素子Q1,Q2の発振周波数を変化させることによって外部信号S1に応じた放電灯Laの明るさに調光制御することができる。

## [0079]

## (実施形態3)

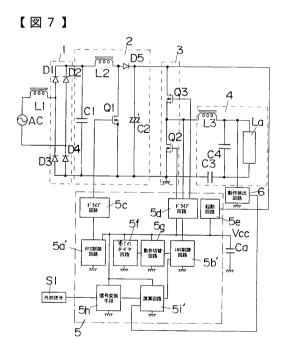

図 7 に示す本実施形態の放電灯点灯装置の回路構成は、図 6 に示す実施形態 2 と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

#### [0800]

本実施形態は、実施形態2の放電灯点灯装置に、放電灯Laの点灯状態(ここでは放電灯Laの出力)を検出する動作検出回路6を備え、制御用集積回路5の出力補正手段として動作検出回路6からの信号と信号変換手段5hからの放電灯制御信号との比較演算を行

10

20

30

40

う演算回路 5 i 'を設けたものである。

## [0081]

演算回路5i,は、この比較演算の結果に基づいてインバータ回路3のスイッチング素子Q2,Q3のオン・オフ時間を変化させるもので、例えば放電灯Laの出力が下がり、動作検出回路6が出力する信号が信号変換手段5hからの放電灯制御信号よりも小さくなれば、放電灯Laの出力が大きくなるようにスイッチング素子Q2,Q3のオン・オフ時間を制御して放電灯Laの出力を調光制御し、逆に放電灯Laの出力が上がり、動作検出回路6が出力する信号が信号変換手段5hからの放電灯制御信号よりも大きくなれば、放電灯Laの出力が小さくなるように、スイッチング素子Q2,Q3のオン・オフ時間を制御して放電灯Laの出力を調光制御する調光信号をINV制御回路5b,に出力する。このように、動作検出回路6によって放電灯Laの出力を検出するフィードバック制御により調光制御を行うことができ、外部信号S1に対して放電灯Laの出力を一定に保つことができる。

## [0082]

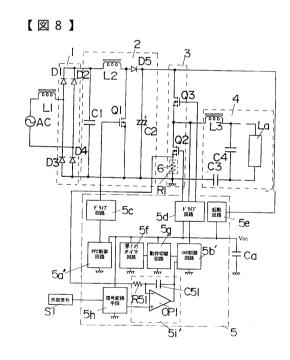

次に、本実施形態の別の回路構成を図8に示す。図7では、動作検出回路6は放電灯Laの出力を動作状態として検出しているが、図8に示すようにスイッチング素子Q2のソース端子に直列に抵抗R1を設けて、インバータ回路3の出力電流、すなわち抵抗R1の両端電圧を放電灯Laの動作状態として検出してもよい。

#### [0083]

演算回路5i,は、オペアンプOP1と、オペアンプOP1の反転入力端子・出力端子間に接続したコンデンサC51と、オペアンプOP1の反転入力端子に一端を接続した抵抗R51とからなる積分回路で構成され、抵抗R51の他端は、スイッチング素子Q2と抵抗R1との接続中点に接続され、オペアンプOP1の非反転入力端子は信号変換手段5hが出力する放電灯制御信号が入力されている。そして、オペアンプOP1は、インバータ回路3の出力電流の検出信号(抵抗R1の両端電圧)と放電灯制御信号とを比較し、外部信号S1に対してインバータ回路3の出力電流が一定となるような調光信号をINV制御回路5b′に出力して、インバータ回路3のスイッチング素子Q2,Q3のオン・オフ時間を制御することで、外部信号S1に応じた放電灯Laの明るさに調光制御している。

## [0084]

このような図8に示す構成であれば、動作検出回路6、及び出力補正手段たる演算回路5i′を簡単な構成で実現できる。なお、演算回路5i′の積分要素である抵抗R51及びコンデンサC51を制御用集積回路5の外部に構成し、抵抗R51の抵抗値及びコンデンサC51の静電容量値を変更できるようにしても、上記同様の効果を得ることができる。

## [0085]

## (実施形態4)

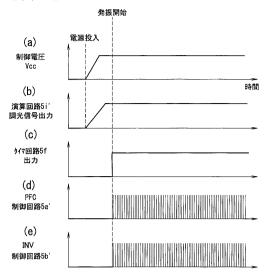

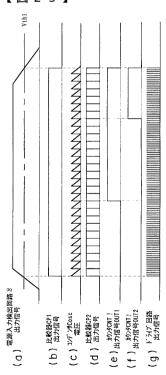

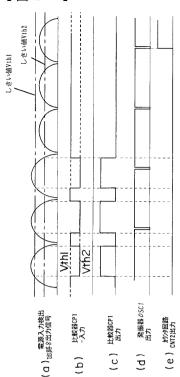

図9(a)~(e)は実施形態3の図7、図8に示す放電灯点灯装置の各部波形のタイムチャートであり、図9(a)は制御電圧Vcc、図9(b)は演算回路5i'の調光信号出力、図9(c)は第1のタイマ回路5fの出力、図9(d)はPFC制御回路5a'の出力、図9(e)はINV制御回路5b'の出力を各々示す。

## [0086]

このタイムチャートは電源投入時の第1のタイマ回路5fと出力補正手段たる演算回路5i,との各出力の関係を示したものであり、従来、電源投入後のインバータ回路3が発振を開始する前の状態では、動作検出回路6の出力がほぼ0であるため、この0出力に基づいて演算回路5i,にてフィードバック制御を行うと発振開始直後のインバータ回路3の出力が所定の出力よりも過大な出力となり、インバータ回路3のスイッチング素子Q1,Q2に過大なストレスが印加される恐れがあった。あるいは、演算回路5i,が積分要素のような時間遅れ要素を有する場合には、演算回路5i,の動作開始直後の出力電圧が安定せず、インバータ回路3が所定の出力を行わないため、放電灯Laに供給される電力に過不足が生じるという問題があった。

10

20

30

40

10

20

30

40

50

#### [0087]

[0088]

そこで、本実施形態においては、演算回路5i′による調光動作を禁止してからインバータ回路3の発振を開始させるようにしたことを特徴としている。例えば、演算回路5i′が出力する調光信号がHighレベルに固定された状態では演算回路5i′による調光動作が禁止される場合、図9に示すように、演算回路5i′が出力する調光信号がHighレベルに立ち上がってからPFC制御回路5a′、INV制御回路5b′、及びドライブ回路5c,5dが動作を開始するとともに、第1のタイマ回路5fの動作も開始する。

このような本実施形態では、インバータ回路3の発振開始時の演算回路5 i '(出力補正手段)の調光動作が禁止されているため、インバータ回路3等に過大なストレスが印加されることなく、さらに所定の電力が出力された状態で第1のタイマ回路5 f が動作するため、放電灯Laのフィラメントに所定の予熱電流を所定の時間、確実に供給することができる。また、これらの各制御回路が1つの集積回路で構成されているため、各制御回路間の時間遅れが殆どなく、且つ少ない部品点数で構成することができる。

## [0089]

(実施形態5)

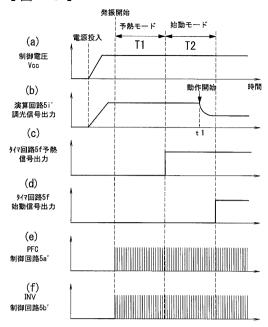

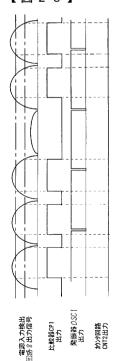

図10(a)~(f)は実施形態3の図7、図8に示す放電灯点灯装置の各部波形のタイムチャートを示したもので、図10(a)は制御電圧Vcc、図10(b)は演算回路5i'の調光信号出力、図10(c)は第1のタイマ回路5fの予熱信号出力、図10(d)は第1のタイマ回路5fの始動信号出力、図10(e)はPFC制御回路5a'の出力、図10(f)はINV制御回路5b'の出力を各々示す。

[0090]

このタイムチャートは、第1のタイマ回路5fの先行予熱期間(予熱モード)、及び始動電圧印加期間(始動モード)の切替えのタイミングと、出力補正手段たる演算回路5i,の出力との関係を示したものであり、従来、先行予熱期間T1内で演算回路5i,が調光動作可能な時に外部信号S1が変化した場合、インバータ回路3の出力も変化することになり、放電灯Laのフィラメントに供給される予熱電流に過不足が生じ、放電灯Laが点灯しなかったり、あるいは予熱電流・電圧の過多によって放電灯Laの寿命が悪化する恐れがあった。

[0091]

そこで、本実施形態においては、第1のタイマ回路5fで設定される先行予熱期間T1が終了してから始動電圧印加期間T2が終了するまでの間の時間t1までは、出力補正手段たる演算回路5i'の調光動作を禁止していることを特徴としており、そのため、上記予熱電流の過不足が発生する恐れはなく、放電灯Laに安定した予熱電流を供給することができる。また、これらの各制御回路が1つの集積回路で構成されているため、各制御回路間の時間遅れが殆どなく、且つ少ない部品点数で構成することができる。

## [0092]

(実施形態6)

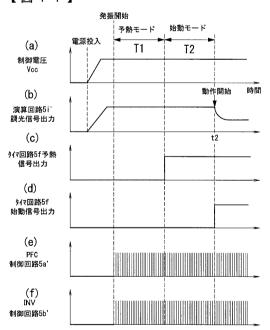

図11(a)~(f)は実施形態3の図7、図8に示す放電灯点灯装置の各部波形のタイムチャートを示したもので、図11(a)は制御電圧Vcc、図11(b)は演算回路5i'の調光信号出力、図11(c)は第1のタイマ回路5fの予熱信号出力、図11(d)は第1のタイマ回路5fの始動信号出力、図11(e)はPFC制御回路5a'の出力、図11(f)はINV制御回路5b'の出力を各々示す。

[0093]

このタイムチャートは、第1のタイマ回路5fの先行予熱期間(予熱モード)、及び始動電圧印加期間(始動モード)の切替えのタイミングと、出力補正手段たる演算回路5i,の出力との関係を示したものであり、従来、先行予熱期間T1及び始動電圧印加期間T2内において、演算回路5i,が調光動作可能な時に外部信号S1が変化した場合、インバータ回路3の出力も変化することになり、放電灯Laのフィラメントに供給される予熱電流だけでなく始動電圧にも過不足が生じ、放電灯Laが点灯しなかったり、あるいは放

10

20

30

40

50

電灯 Laの寿命が悪化する恐れがあった。あるいは、放電開始前後での放電灯 Laのランプインピーダンスが大きく異なるため、インバータ回路 3 や放電灯 Laの動作状態に大きな変化が生じ、それを補正するために演算回路 5 i 'の出力が不安定になることも考えられる。

## [0094]

そこで、本実施形態においては、出力補正手段たる演算回路5i,の調光動作の禁止を解除するタイミングを、始動電圧印加期間T2の終了時点t2、すなわち点灯に切り替わるモード切替えのタイミングとほぼ同期させていることを特徴としている。例えば、演算回路5i,が出力する調光信号がHighレベルに固定された状態では演算回路5i,による調光動作が禁止される場合、点灯時に動作検出回路6によって放電灯Laの出力を検出するフィードバック制御を有効に行うには、演算回路5i,が出力する調光信号をHighレベルよりもやや低いレベルとする必要がある。これは、点灯時に演算回路5i,が出力する調光信号がHighレベルである場合、演算回路5i,による調光動作が禁止されるため、動作検出回路6によるフィードバック制御が行われず、インバータ回路3の出力が大きくなり過ぎてスイッチング素子Q2,Q3に過大なストレスが印加される恐れがあるためである。

### [0095]

したがって、第1のタイマ回路 5 f のカウントした動作時間が始動電圧印加期間 T 2 を終了するまで、演算回路 5 i 'による調光動作を禁止している場合には、始動電圧印加期間 T 2 から点灯への切替と同時に演算回路 5 i 'による調光動作を開始させることが望ましい。

#### [0096]

このような本実施形態では、演算回路 5 i 'による調光動作開始のタイミングと、第 1 のタイマ回路 5 f の始動電圧印加期間 T 2 から点灯への切替のタイミングがほぼ同期しているため、インバータ回路 3 に過大なストレスが印加されることなく、さらに予熱・始動時にインバータ回路 3 の出力が不安定になり、放電灯 L a の不点灯や短寿命が発生することもない。また、これらの各制御回路が 1 つの集積回路で構成されているため、各制御回路間の時間遅れが殆どなく、且つ少ない部品点数で構成することができる。

## [0097]

## (実施形態7)

図12に示す本実施形態の放電灯点灯装置の回路構成は、実施形態1乃至6と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

## [0098]

本実施形態は、放電灯 Laの異常状態を検出して異常検出信号を出力する異常検出回路 7を備えている。また、整流器 1、直流電源回路 2、インバータ回路 3、負荷回路 4 は回路プロックで示し、各ブロックの主な構成要素のみを図示しておく。

## [0099]

制御用集積回路5は、直流電源回路2のスイッチング素子Q1のオン・オフ時間の制御信号を出力する第1の制御手段5aと、第1の制御手段5aから出力される制御信号によってスイッチング素子Q1の駆動信号を出力するドライブ回路5cと、インバータ回路3のスイッチング素子Q2,Q3のオン・オフ時間の制御信号を出力する第2の制御手段5bから出力される制御信号によってスイッチング素子Q2,Q3の駆動信号を出力するドライブ回路5dと、電源投入後のインバータ回路3のスイッチング素子Q2,Q3が発振を開始してから(第1の制御手段5a,第2の制御手段5b,ドライブ回路5c,5dが起動してから)の時間をカウントして、放電灯Laのフィラメンクライブ回路5c,5dが起動してから)の時間をカウントして、放電灯Laのフィラメントの先行予熱期間及び始動電圧印加期間を設定する第1のタイマ回路5f(第1のタイマ手段)と、第1のタイマ回路5fの出力に応じてインバータ回路3のスイッチング素子Q2,Q3のオン・オフ時間を切替える動作切替回路5gと、放電灯Laに異常が生じた際に、異常検出回路7からの異常検出信号を受けて異常状態を判別する異常判別手段5jと、異常判別手段5jで判別した異常状態が所定の時間継続していることを判別する第2の

タイマ回路 5 k (第2のタイマ手段)と、第2のタイマ回路 5 k で異常状態の継続を認識した場合、第1の制御手段 5 a と第2の制御手段 5 b とに出力抑制信号を出力して、直流電源回路 2 とインバータ回路 3 との出力を低下、もしくは停止させるよう制御する第1の出力抑制手段 5 m と、第1の出力抑制手段 5 m が出力抑制動作を行う時間を設定し、設定した所定の時間経過後は第1のタイマ回路 5 f を初期状態にリセットする第3のタイマ回路 5 l (第3のタイマ手段)と、電源投入時(起動時)、制御用集積回路 5 内の各回路に制御電源を供給するために直流電源回路 2 の出力から生成した制御電源を供給する起動回路 5 e とからなり、同一のウエハ上に構成されている。なお、第1の出力抑制手段 5 m は、第2のタイマ回路 5 k で異常状態の継続を認識した場合、第1の制御手段 5 a と第2の制御手段 5 b とのうち少なくともいずれか一方に出力抑制信号を出力してもよい。

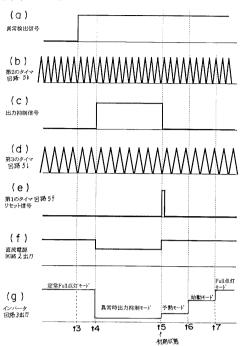

[0100]

次に本実施形態の動作について図13(a)~(g)のタイムチャートを用いて説明する。負荷である放電灯Laが定常Fu11点灯モード時に異常が発生し、異常検出回路7が出力する異常検出信号がLowレベルからHighレベルに反転すると(時間t3)、異常判別手段5jは異常信号を出力し、異常信号を受けた第2のタイマ回路5kは異常状態発生からの継続時間のカウントを開始し、所定時間(本実施形態では第2のタイマ回路5kが発振させている三角波3回分)の異常継続を認識すると第1の出力抑制手段5mが出力する出力抑制信号がLowレベルからHighレベルに反転する(時間t4)。

[0101]

すると、このHighレベルの出力抑制信号を受けた第1,第2の制御手段5a,5bがドライブ回路5c,5dを介してスイッチング素子Q1~Q3のオン・オフを制御して各出力を抑制し、直流電源2、インバータ回路3の各出力は低下して、異常時出力抑制モードになる。

[0102]

また、出力抑制信号がLowレベルからHighレベルに反転すると同時に、第3のタイマ回路51が出力抑制状態の維持時間のカウントを開始する。そして、第3のタイマ回路51が所定時間(本実施形態では第3のタイマ回路51が発振させている三角波7回分)の維持時間を認識すると、第3のタイマ回路51から第1のタイマ回路5fにリセット信号が出力され(時間t5)、第1のタイマ回路5fのカウント動作がリセットされることにより放電灯点灯装置の動作モードが初期状態に戻り、第1のタイマ回路5fに設定された放電灯Laのフィラメントの先行予熱期間、始動電圧印加期間に従って、予熱モードが開始し、さらに始動モードが開始して(時間t6)、再びFu11点灯モード(時間t7)になる。

[0103]

このような本実施形態では、直流電源回路 2、インバータ回路 3 の出力制御を行う各回路が同一ウエハ上に構成され、かつ同一のタイマ回路を用いて出力制御を行うことによって、直流電源回路 2 とインバータ回路 3 との間の伝達の遅れや、干渉を最小限に抑えることができ、検出過渡動作時の誤動作を防止することができるという効果が得られる。

[0104]

(実施形態8)

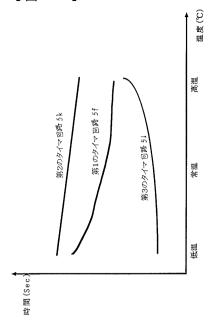

本実施形態の回路構成は、図12に示す実施形態7と同様であり、実施形態7で示した第1~第3のタイマ回路5f,5k,5lについて、各々の周囲温度変動特性を図14に示す。第1,第2のタイマ回路5f,5kは周囲温度が上昇するとタイマ時間が減少する負特性であり、第3のタイマ回路5lは周囲温度が上昇するとタイマ時間も増加する正特性を持っており、各タイマ回路の機能と、周囲温度の高低に対するタイマ時間の変動について図15に示す。

[0105]

まず、第1のタイマ回路 5 f は、放電灯 L a のフィラメントの先行予熱期間(予熱モード)及び始動電圧印加期間(始動モード)を設定する役割を持っている。そして、放電灯 L a は周囲温度が下がると起動初期放電を開始しにくい状態となる。そこで、第1のタイ

10

20

30

40

マ回路 5 f に負特性を持たせることにより常温時より低温時の先行予熱時間及び始動電圧 印加時間が長くなり、低温時にも確実に放電灯 L a を始動させることができる。

### [0106]

次に第2のタイマ回路5 k は、異常状態が所定時間継続していることを判別する役割を持っており、異常が発生してから異常時出力抑制モードに移行する間での時間を設定している。放電灯 L a に異常が発生した場合、インバータ回路3を構成する電子部品に正常動作時より大きなストレスが印加され、電子部品の温度が上昇する。そこで、第2のタイマ回路5 k に負特性を持たせることにより、電子部品の温度上昇による周囲温度の上昇に対し、第2のタイマ回路5 k がカウントする時間が短くなり、異常の発生から異常時出力抑制モードに移行するまでの時間が短くなり、電子部品に印加されるストレスを減らす方向に働く。

### [0107]

そして、第3のタイマ回路51は、異常時出力抑制モードから、第1のタイマ回路5fを初期状態にリセットして、直流電源回路2及びインバータ回路3を初期状態から再始動させるまでの時間を設定する役割を持っており、異常時出力抑制モードの維持期間を設定している。また、前記同様に、放電灯Laに異常が発生した場合、電子部品にストレスが印かが、電子部品の温度が上昇するので、異常時出力抑制モードの維持期間は、このような異常状態となったときに上昇した電子部品の温度を低下させるために設けられている。そこで、第3のタイマ回路51に正特性を持たせることにより、ストレスの印加により電子部品の温度が上昇したときに、異常時出力抑制モードの維持期間が長くなり、電子部品の温度が低下するための充分な時間を確保することができる。したがって、ストレスが大きく、電子部品の温度上昇が大きくなればなるほど、異常時出力抑制モードの維持期間が長くなり、印加されるストレスの大小により異常時出力抑制モードの時間が変化する。

このような本実施形態では、周囲の環境変化をはじめ、起動初期から安定点灯状態に移行したときや、放電灯Laの異常となったとき等、周囲温度が変化した場合、周囲温度の変化に応じた出力制御の変化をもたらし、直流電源回路2及びインバータ回路3の出力制御動作性能を向上させて、安定した最適動作を維持することができ、前記所定の周囲温度変化特性を持たせた各タイマ回路を集積回路として同一ウエハ上に構成することにより、相互間の特性ばらつきを最小限に抑えることができて、各タイマ回路間の相対的な特性のバラツキも殆どなく、安定した最適動作を実現することできる。

## [0109]

[0108]

#### (実施形態9)

図16に示す本実施形態の放電灯点灯装置の回路構成は、実施形態1乃至6と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

#### [0110]

本実施形態は、インバータ回路3のスイッチング素子Q2のソース端子に直列に接続した抵抗R1からなり、インバータ回路3の出力電流、すなわち抵抗R1の両端電圧を放電灯Laの動作状態として検出する動作検出回路6と、この電圧波形から放電灯Laの異常状態を検出して異常検出信号を出力する異常検出回路7とを備えている。

## [0111]

制御用集積回路 5 は、図 1 2 に示す実施形態 7 と略同様であり、直流電源回路 2 の出力電圧レベルをモニタし出力する電源出力検出回路 5 n を備えている点が異なる。

## [0112]

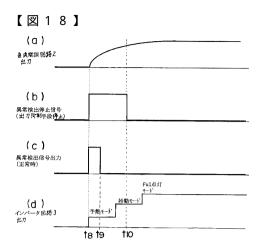

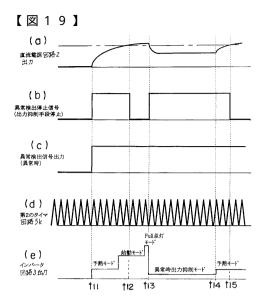

次に本実施形態の動作について図17(a)~(d)の波形、図18(a)~(d)、図19(a)~(e)の各タイムチャートを用いて説明する。図17(a)に示すインバータ回路3のスイッチング素子Q2の駆動信号に対し、放電灯Laの正常時のターンオフ時には図17(b)に示すような正の動作電流がスイッチング素子Q2に流れる。放電灯Laの異常時には共振用のインダクタL3、コンデンサC4により構成されるLC共振回路の共振電流が駆動信号に対して進み位相(進相)になり、ターンオフ時には図17(c

10

20

30

40

)に示すような負の動作電流がスイッチング素子Q2に流れる。

#### [0113]

この異常動作モードを検出するために本実施形態では、スイッチング素子Q2の動作電流を抵抗R1の両端電圧として異常検出回路7が検出し、スイッチング素子Q2の駆動信号の立下がり時における動作電流の極性によって異常状態を判別する異常判別手段5jを用いている。つまり、スイッチング素子Q2の駆動信号の立下がり時を位相検出点として、位相検出点での動作電流が正であれば正常、負であれば異常といった判断を異常判別手段5jが行い、実施形態7同様に、第2のタイマ回路5kを介して第1の出力抑制手段5mへと異常信号を伝達して異常時出力抑制モードに切り替えて保護制御を行う。

## [0114]

しかし、起動初期において、図18(a)に示す直流電源回路2の出力電圧の立ち上がり時の過渡動作時(時間t8~t9)に、放電灯Laが正常であるにも関わらず、負荷回路4にLC共振回路を有するインバータ回路3の入力電圧が低いために進相動作が発生するため、図18(c)に示すように異常検出回路7が異常検出信号を出力する場合がある。そこで図18(b)に示すように、電源出力検出回路5nは、検出した直流電源回路2の出力電圧レベルが所定の電圧レベルを超える時間t10までは出力抑制動作を停止させる異常検出停止信号を第1の出力抑制手段5mに出力している。したがって、図18(d)に示すようにインバータ回路3の出力は、異常時出力抑制モードに切替わることなく、予熱モード、始動モード、Fu11点灯モードの各動作を行うことができる。

## [0115]

次に、放電灯Laの異常時には、LC共振回路の共振電流の進相状態が継続し、図19 (c)に示すように異常検出回路 7 が出力する異常検出信号も継続するので、図 1 9 (b )に示す異常検出停止信号が終了する時間t12を過ぎても、異常検出信号がHighレ ベルを維持するため、異常判別手段5 jによって異常であると認識されて、第2のタイマ 回路5kが異常の継続時間のカウントを開始する。そして、所定時間(本実施形態では第 2のタイマ回路5kが発振させている三角波3回分)の異常継続を認識すると(時間t1 2 ~ t 1 3 ) 、 第 1 の出力抑制手段 5 m が働き、インバータ回路 3 の出力を低減して異常 時出力抑制モードに切替えると同時に、直流電源回路2の出力も低減させている。このと き、異常検出停止信号は再び出力を開始する。次に第3のタイマ回路51が所定の異常時 出力抑制モードの維持時間(時間t13~t14)を認識すると、第3のタイマ回路51 から第1のタイマ回路5fにリセット信号が出力され、第1のタイマ回路5fのカウント 動作がリセットされることにより放電灯点灯装置の動作モードが初期状態に戻り(時間t 14)、第1のタイマ回路5fに設定された放電灯Laのフィラメントの先行予熱期間に 従って、予熱モードが開始して、放電灯Laが再始動する。そして、再び直流電源回路2 の出力電圧レベルが所定の電圧レベルを超えると異常検出停止信号が終了する(時間t1 5)。

## [0116]

このような本実施形態では、直流電源回路 2、インバータ回路 3 の出力制御を行う各回路が同一ウエハ上に構成され、かつ同一のタイマ回路、及び異常保護用制御回路を用いて出力制御を行うことによって、直流電源回路 2 とインバータ回路 3 との間の伝達の遅れなく確実に異常保護制御を行うことができ、また異常時の検出過渡動作時においても相互間の干渉による検出の誤動作を防止することができるという効果が得られる。

## [0117]

## (実施形態10)

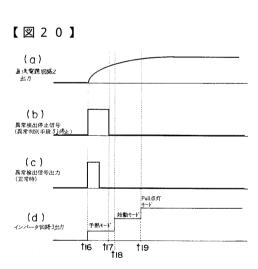

本実施形態は、図20(a)~(d)のタイムチャートに示すように、異常検出停止信号を、起動時間 t 16 から第1のタイマ回路5fで設定される先行予熱期間が終了する時間 t 18までの期間内の時間 t 17 に終了させて、異常検出動作の停止を異常判別手段5jの動作を停止させることで行っていることが特徴である。

#### [0118]

次に本実施形態の動作について説明する。実施形態 9 で説明した起動初期の進相動作発

10

20

30

40

生に対して、起動時から先行予熱期間が終了する期間(時間t16~t18)内の所定の期間(時間t16~t17)の間に、図20(b)に示すように、電源出力検出回路5nは、異常判別動作を停止させる異常検出停止信号を異常判別手段5jに出力している。したがって、図20(c)に示す起動初期の進相動作による異常検出信号が異常判別手段5jに入力されても異常であるとは判別せず、第2のタイマ回路5k、第1の出力抑制手段5mへの信号の伝達はなく、図20(d)に示すようにインバータ回路3の出力は予熱モードから始動モード、Fu11点灯モードへと、正常時のシーケンス通りの出力制御が進む。放電灯Laの異常時には、異常判別動作の停止期間(時間t16~t17)が終了後、実施形態9と同様に異常状態の継続を確認した後、異常時出力抑制モードに移行する。このような本実施形態においては、実施形態9で必要であった電源出力検出回路5nを用いることなく、直流電源回路2とインバータ回路3との間の伝達の遅れなく確実に異常保護制御を行うことができ、また異常時の検出過渡動作時においても相互間の干渉による検出の誤動作を防止することができるという同様の効果を得ることができる。

[0119]

なお、異常検出動作の停止を第2のタイマ回路5k、または第1の出力抑制手段5mの動作を停止させることで行ってもよい。

[0120]

(実施形態11)

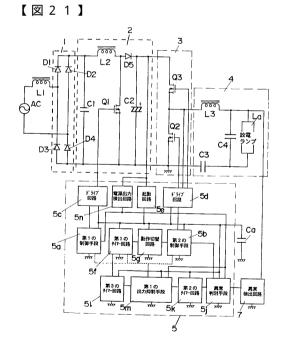

図21に示す本実施形態の放電灯点灯装置の回路構成は、図16に示す実施形態9と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

[0121]

本実施形態は、放電灯Laのランプ電圧を異常検出回路7に入力して、異常検出回路7はランプ電圧に応じて放電灯Laの異常状態を検出して、異常検出信号を出力するものである。

[0122]

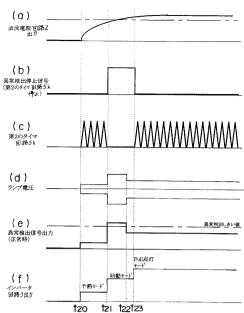

本実施形態の動作について図22(a)~(f)のタイムチャートを用いて説明する。放電灯Laの正常時における起動初期において、放電灯Laの放電を開始させるため、放電灯Laに始動電圧を印加する始動電圧印加期間(始動モード:時間t21~t23)では、図22(d)に示すように、一時的にランプ電圧が異常時と同等以上のレベルにまで上昇する領域(時間t21~t22)がある。そのため放電灯Laが正常であっても、図22(e)に示すように、その領域(時間t21~t22)ではランプ電圧が異常判別しきい値を超えて、異常判別手段5jが一時的に異常であると認識してしまう。

[0123]

そこで、本実施形態では図22(b)に示すように、異常検出停止信号が、始動電圧印加期間(始動モード:時間 t 21~ t 23)に、第2のタイマ回路5kに出力されて、図22(c)に示すように異常検出動作の停止を第2のタイマ回路5kの動作を停止させることで行っている。そのため、始動モード時に異常判別手段5jからの異常信号が第2のタイマ回路5kに伝達されても、第2のタイマ回路5kは異常の継続時間をカウントすることなく、次段の第1の出力抑制手段5mには出力の抑制を指示する信号は伝達されない。したがって、図22(f)に示すようにインバータ回路3の出力は予熱モードから始動モード、Full点灯モードへと、正常時のシーケンス通りの出力制御が進む。

[0124]

このような本実施形態においては、直流電源回路2、インバータ回路3の出力制御を行う各回路が同一ウエハ上に構成され、かつ同一のタイマ回路、異常保護回路を用いて出力制御を行うことによって、直流電源回路2とインバータ回路3との間の伝達の遅れや、干渉を最小限に抑えることができ、また異常時のストレスを最小限に抑えることができて、検出過渡動作時の誤動作を防止することができるという効果が得られる。

[0125]

なお、異常検出動作の停止を異常判別手段 5 j、または第 1 の出力抑制手段 5 mの動作を停止させることで行ってもよい。

10

20

30

40

### [0126]

(実施形態12)

図23に示す本実施形態の放電灯点灯装置の回路構成は、図1に示す実施形態1と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

## [0127]

本実施形態は、直流電源回路2の入力電圧を検出する電源入力検出回路8を直流電源回路2の入力端に並列に接続し、電源入力検出回路8が出力する直流電源検出回路2の検出値としきい値Vth1とを比較して、検出値がしきい値Vth1より低いとき、PFC制御回路5a',INV制御回路5b',第1のタイマ回路5fの各動作を停止させる比較器CP1を制御用集積回路5に備えている。

### [0128]

図24に制御用集積回路5及び電源入力検出回路8の詳細な構成を示し、電源入力検出 回路8は、直流電源回路2の入力端に並列に接続した抵抗R2,R3の直列回路と、抵抗 R3に並列に接続したコンデンサC5とから構成されて、抵抗R3とコンデンサC5との 並列回路の両端電圧を検出値として出力している。

#### [0129]

制御用集積回路5は、比較器CP1の出力とPFC制御回路5a, との出力のAND演算を行い、出力をドライブ回路5cに接続したAND素子IC1と、比較器CP1の出力とINV制御回路と5b, との出力のAND演算を行い、出力をドライブ回路5dに接続したAND素子IC2と、比較器CP1の出力を反転させるINV素子IC3と、起動回路5e(図24では図示無し)を介して供給される制御用電源Vccから基準電源を生成する基準電源E2とを備えている。

#### [0130]

第1のタイマ回路5fは、基準電源E2に接続した定電流源I1と、定電流源I1にドレイン端子を接続したFET5と、基準電源に各ソース端子を接続し、互いのゲート端子に接続したFET1のドレイン端子に接続したFET1のドレイン端子に接続したFET3のゲート端子に接続したFET3のドレイン端子に接続したFET3のドレイン端子に接続し、ゲート端子に接続したFET3のドレイン端子に接続し、ゲート端子をFET3のドレイン端子をFET3のドレイン端子に接続し、がートイン端子をFET3のゲート端子に接続し、出力をFET3のゲートは当日に接続し、北反転入力端子をしきい値に接続し、出力をFET3のゲート端子に接続した比較器CP2と、CLK端子に比較器CP2の出力を接続し、STOP端子に接続した比較器CP2と、ドレイン端子をFET4のドレイン端子に接続したカウンタ回路CNT1と、ドレイン端子をFET4のドレイン端子に接続したアロコート端子とを接続し、FET1及びFET5は、各ドレイン端子とが一ト端子とを接続し、FET1を構成し、FET1及びFET5は、各ドレイン端子とが一ト端子とを接続し、FET4~7は各ソース端子をGNDレベルに接続している。また、制御用集積回路5の外部には較器CP2の反転入力端子に接続した発振用コンデンサCoscを備えている。

# [0131]

次に本実施形態の動作について図25(a)~(g)のタイムチャートを用いて説明する。まず、電源入力検出回路8は直流電源回路2に入力される脈流電圧を抵抗分圧し、平滑している。

#### [0132]

そして、交流電源ACを投入した際、起動用集積回路5が備える起動回路5e(図24では図示無し)を介して制御電源Vccが供給され、電源入力検出回路8の出力信号も立ち上がり(図25(a))、その電圧がしきい値Vth1より低い場合、比較器CP1の出力がLowレベルになり(図25(b))、AND素子IC1,IC2の各出力もLowレベルになって、PFC制御回路5a'、INV制御回路5b'が出力する各制御信号はドライブ回路5c,5dに入力されず、直流電源回路2及びインバータ回路3のスイッチング素子Q1~Q3はオフ状態を維持する。

## [ 0 1 3 3 ]

50

20

10

30

電源入力検出回路8の出力信号がしきい値Vth1を超えると、比較器CP1の出力が Highレベルになり(図25(b))、AND素子IC1,IC2の各出力はPFC制 御回路5a'、INV制御回路5b'が出力する各制御信号がそのまま出力され、PFC 制御回路5a'、INV制御回路5b'が出力する各制御信号はドライブ回路5c,5d に入力されて、直流電源回路2及びインバータ回路3のスイッチング素子Q1~Q3は駆 動状態となる(図25(g))。

#### [0134]

ここで、第1のタイマ回路5fでは、発振用コンデンサCoscへの充放電電流を、カレントミラー回路、及び比較器CP2によって制御することによって、発振用コンデンサCoscの両端電圧を三角波に生成し(図25(c))、この三角波としきい値とを比較した比較器CP2の出力(図25(d))をクロック信号としてカウンタ回路CNT1のCLK端子に入力している。

#### [0135]

また、ここでは図示していないが、比較器 C P 2 の非反転入力端子には、発振用コンデンサ C o s c の両端電圧の三角波の上限値、下限値を決定するしきい値を入力しており、比較器 C P 2 の出力に応じて 2 つのしきい値を切替える構成であればどのような構成であってもよい。

## [0136]

カウンタ回路CNT1は、STOP端子を備えており、このSTOP端子の入力がHighレベルのとき、すなわち電源入力検出回路8の出力信号がしきい値Vth1より低いときは、カウント動作を停止してOUT1,OUT2端子の出力をLowレベルにリセットしている。そして、STOP端子の入力がLowレベルに切り替わったとき、すなわち電源入力検出回路8の出力信号がしきい値Vth1を超えたときから、カウント動作を開始する。

## [0137]

カウンタ回路CNT1は、放電灯Laのフィラメントの先行予熱期間及び始動電圧印加期間を設定されており、先行予熱期間終了時点でOUT1端子をHighレベルに立ち上げ(図25(e))、始動電圧印加期間終了時点でOUT2端子をHighレベルに立ち上げている(図25(f))。

## [0138]

そして、動作切替回路 5 g は、カウンタ回路 C N T 1 の O U T 1 , O U T 2 端子の各出力信号に応じて先行予熱期間、始動電圧印加期間、点灯期間を切り替えて、 I N V 発振回路 5 b 'から出力される制御信号の周波数を変化させている。

### [0139]

ここで、交流電源ACが瞬時停電になった場合、または瞬時にレベル低下した場合は、電源入力検出回路8の検出信号も低下し、比較器CP1のしきい値Vth1よりも低くなると直流電源回路2、及びインバータ回路3のスイッチング素子Q1~Q3はオフ状態を維持し、カウンタ回路CNT1はカウント動作を停止して初期状態(OUT1,OUT2端子の各出力がLowレベル)にリセットされる。

### [0140]

このような本実施形態においては、直流電源回路2の入力電圧がかなり低い場合に、直流電源回路2、及びインバータ回路3を動作させることによって生じる各々のスイッチング素子Q1~Q3への過大なストレスを低減することができる。

## [0141]

また、直流電源回路2の入力電圧が大幅に低下することによる出力電圧低下によって、 放電灯Laが立ち消え状態になり、実施形態11で説明した異常検出回路7が動作して、 インバータ回路3が比較的長く停止状態を維持するという誤動作も発生しない。

#### [0142]

さらに、交流電源ACが復帰した場合は、先行予熱からの起動になるため、放電灯Laの寿命を損なうことがない。

10

20

30

40

### [0143]

#### (実施形態13)

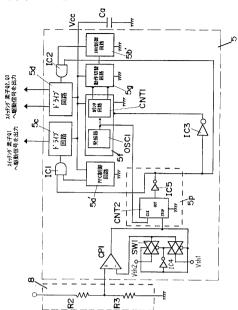

本実施形態の放電灯点灯装置の回路構成は、図23,図24に示す実施形態12と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

## [0144]

図26に本実施形態の制御用集積回路5及び電源入力検出回路8の詳細な構成を示し、電源入力検出回路8は抵抗R2,R3の直列回路のみで構成されており、したがって電源入力検出回路8の出力信号は交流電源ACを全波整流した脈流電圧波形になる(図27(a))。

## [0145]

制御用集積回路5は、電源入力検出回路8が出力する直流電源検出回路2の検出値としきい値とを比較する比較器CP1の出力がLowレベルならば比較器CP1の反転入力端子に入力するしきい値をVth1に切り替え、比較器CP1の出力がHighレベルならばしきい値をVth2(Vth1>Vth2)に切り替える(図27(b),(c))スイッチ素子SW1と、比較器CP1の出力を反転してスイッチ素子SW1に入力するINV素子IC4と、比較器CP1の出力がHighレベルからLowレベルへ切り替わった後、所定の時間遅延させてHighレベルの信号を出力する第4のタイマ回路5p(第4のタイマ手段)と、第4のタイマ回路5pの出力とPFC制御回路5a'との出力のAND演算を行い、出力をドライブ回路5cに接続したAND素子IC1と、第4のタイマ回路5pの出力とINV制御回路と5b'との出力のAND演算を行い、出力をドライブ回路5dに接続したAND素子IC2と、第4のタイマ回路5pの出力を反転させるINV素子IC3と、INV素子IC3の出力を入力される第1のタイマ回路5fとを備えている。

#### [0146]

比較器 CP1は、出力に応じてしきい値が Vth1とVth2とに交互に切り替わるのでヒステリシス特性を持っている。

### [0147]

第1のタイマ回路5fは、クロック信号を出力する発振器OSC1と、発振器OSC1のクロック信号及びINV素子IC3の出力を接続したカウンタ回路CNT1とを備え、INV素子IC3の出力がHighレベルのとき、カウント動作を停止して出力端子の出力をLowレベルにリセットしている。そして、INV素子IC3の出力がLowレベルに切り替わってから、クロック信号のカウント動作を開始する。

#### [0148]

カウンタ回路 C N T 1 は、実施形態 1 2 と同様の動作を行い、放電灯 L a のフィラメントの先行予熱期間及び始動電圧印加期間を設定されており、 I N V 素子 I C 3 の出力が L o w レベルに切り替わってからクロック信号をカウントして、先行予熱期間終了時点で一方の出力端子を H i g h レベルに立ち上げ、始動電圧印加期間終了時点で他方の出力端子を H i g h レベルに立ち上げている。

## [0149]

第4のタイマ回路5pは、CLK端子にカウンタ回路CNT1の発振器OSC1のクロック信号(図27(d))を接続し、STOP端子に比較器CP1の出力を接続したカウンタ回路CNT2の出力端子OUTの出力を反転させるINV素子IC5とを備えている。

## [0150]

カウンタ回路 C N T 2 は、 S T O P 端子の入力が H i g h レベルのとき、すなわち電源入力検出回路 8 の出力信号がしきい値 V t h 1 を超えたときは、クロック信号のカウント動作を停止して出力端子 O U T の出力を L o w レベルにリセットしており、 I N V 素子 I C 5 の出力は H i g h レベルとなる。したがって、 I N V 素子 I C 3 の出力は L o w レベルになって、カウンタ回路 C N T 1 は先行予熱期間及び始動電圧印加期間に応じた信号を出力し、 A N D 素子 I C 1 , I C 2 の各出力は P F C 制御回路 5 a '、 I N V 制御回路 5

10

20

30

40

b が出力する各制御信号がそのまま出力され、 P F C 制御回路 5 a 、 I N V 制御回路 5 b が出力する各制御信号はドライブ回路 5 c , 5 d に入力されて、直流電源回路 2 及びインバータ回路 3 のスイッチング素子 Q 1 ~ Q 3 は駆動状態となる。

#### [0151]

次に、カウンタ回路CNT2のSTOP端子の入力がLowレベルのとき、すなわち電源入力検出回路8の出力信号がしきい値Vth1より低くなったときは、カウンタ回路CNT2はクロック信号のカウント動作を開始し、クロック信号の立下りを2回カウントして出力端子OUTの出力をHighレベルに立ち上げている(図27(e))。したがって、INV素子IC3の出力もHighレベルになって、カウント回路CNT1は、カウント動作を停止して出力端子の出力をLowレベルにリセットし、AND素子IC1,IC2の各出力もLowレベルになって、直流電源回路2及びインバータ回路3のスイッチング素子Q1~Q3はオフ状態を維持する。

#### [0152]

このような本実施形態においては、実施形態12と同様の効果を得ることができ、さらに、直流電源回路2に入力される電圧が低下した場合、電源入力検出回路8からの出力信号と比較されるしきい値にヒステリシスを持っており、電圧の低下が所定の期間継続した後に出力が停止するため、外来ノイズ、比較器CP1の出力のチャタリング等で誤動作して停止する恐れがなくなる。

#### [0153]

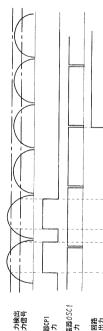

また、交流電源ACが一般の商用交流電源であれば、その瞬時電圧降下は比較的短時間で大きい電圧降下が頻繁に発生しやすい傾向にある。本実施形態においては、電圧降下から出力停止するまでに時間遅れがあるために、交流電源ACの比較的短期間の電圧降下の場合は、図28(a)~(d)に示すように直流電源回路2及びインバータ回路3の各動作を継続し、比較的長時間の電圧降下の場合は、図29(a)~(d)に示すように直流電源回路2及びインバータ回路3の各動作を停止するため、出力が頻繁に停止して放電灯Laが消灯することによる不快感を使用者に与えることがない。

## [0154]

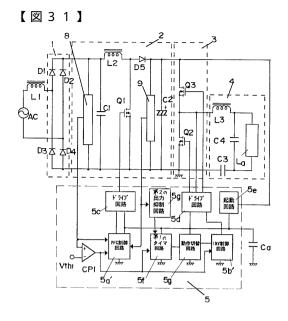

## (実施形態14)

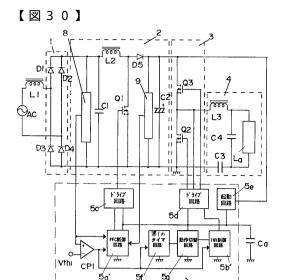

図30に示す本実施形態の放電灯点灯装置の回路構成は、図23に示す実施形態12と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

### [0155]

本実施形態は、実施形態12と同様に、直流電源検出回路2の入力電圧を検出する電源入力検出回路8を直流電源回路2の入力端に並列に接続し、電源入力検出回路8の出力信号を比較器CP1に入力して、その比較結果をPFC制御回路5a'に入力することによって交流電源ACの瞬時電圧降下、及び停電等を検出して、直流電源回路2、及びインバータ回路3のスイッチング素子Q1~Q3のオン・オフ動作を停止している。

## [0156]

さらに本実施形態においては、直流電源回路2の出力端に並列に接続された電源出力検出回路9からの出力信号もPFC制御回路5 a 'に入力し、電源入力検出回路8が出力する脈流信号をPFC制御回路5 a 'に直接入力している。

## [0157]

直流電源回路 2 は昇圧チョッパ回路で構成されているが、一般的に行われている昇圧チョッパ回路の制御としては、制御部に主に誤差アンプ、マルチプライヤを備えており、昇圧チョッパ回路の出力電圧に比例した信号を誤差アンプに入力している。そして、誤差アンプの出力信号と昇圧チョッパ回路に入力される脈流電圧に比例した信号とはマルチプライヤへ入力され、マルチプライヤの出力信号とスイッチング素子Q1を流れる電流とを比較して、スイッチング素子Q1のオン時間を決定している。

#### [0158]

本実施形態のPFC制御回路5a'も上記と同様の動作を行っており、交流電源ACの 正弦波波形に追従してスイッチング素子Q1のオン時間を制御し、直流電源回路2の出力 10

20

30

40

電圧を所望のレベルで安定制御し、交流電源ACから入力される入力電流の波形歪みを大幅に低減することができる。

#### [0159]

さらに、交流電源ACの瞬時電圧降下を検出する電源入力検出回路8が出力する脈流信号と、PFC制御回路5a'に入力される脈流信号とを同一信号としているため、制御回路の集積化により部品点数の削減、放電灯点灯装置の小型化がより容易にできる。

#### [ 0 1 6 0 ]

## (実施形態15)

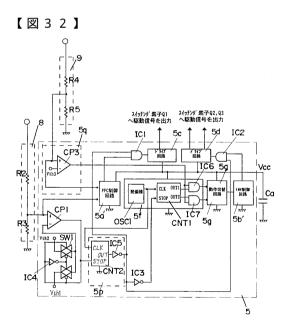

図31に示す本実施形態の放電灯点灯装置の回路構成は、図30に示す実施形態14と 略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

### [0161]

本実施形態では、制御用集積回路 5 に第 2 の出力抑制回路 5 q (第 2 の出力抑制手段)を備え、電源出力検出回路 9 の出力信号が P F C 制御回路 5 a 'だけでなく第 2 の出力抑制回路 5 q にも入力されており、第 2 の出力抑制回路 5 q の出力は第 1 のタイマ回路 5 f に入力されている。

#### [0162]

図32に本実施形態の制御用集積回路5、電源入力検出回路8、及び電源出力検出回路9の詳細な構成を示し、第2の出力抑制回路5qの動作を説明する。なお、この構成は図26に示す実施形態13と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

#### [0163]

電源出力検出回路9は抵抗R4,R5の直列回路で構成され、抵抗R5の両端電圧を出力信号としている。

#### [0164]

第2の出力抑制回路5qは、反転入力端子にしきい値Vth3を入力し、非反転入力端子に電源出力検出回路9の出力信号を入力した比較器CP3からなり、第1のタイマ回路5fは、AND素子IC6,IC7は一方の入力にカウンタ回路CNT1のOUT1,OUT2端子に各々接続して、他方の入力には比較器CP3の出力を各々接続している。

## [0165]

この第2の出力抑制回路5 q は、実施形態12と同様に、カウンタ回路CNT1のOUT1,OUT2端子は、起動後の放電灯Laの先行予熱期間において、OUT1: "Lowレベル"、OUT2: "Lowレベル"の信号を出力し、放電灯Laに始動電圧を印加する始動期間においては、OUT1: "Highレベル"、OUT2: "Lowレベル"の信号を出力し、始動期間の終了後には、OUT1: "Highレベル"、OUT2: "Highレベル"の信号を出力し、動作切替回路5 g は、これらの信号に対応した動作切替えの信号をINV制御回路5 b'に出力することによって、スイッチング素子Q2,Q3の発振周波数を可変としている。

## [0166]

ここで、直流電源回路3の出力電圧が所定の電圧より高い場合、すなわち比較器CP3の出力がHighレベルの場合は、AND素子IC6,IC7の各出力は、カウンタ回路CNT1のOUT1,OUT2端子の出力となり、先行予熱期間、始動電圧を印加する始動期間、始動終了後の信号が正常に動作切替回路5gに伝達される。

## [0167]

直流電源回路3の出力電圧が所定の電圧より低い場合、すなわち比較器CP3の出力がLowレベルの場合は、AND素子IC6,IC7の各出力はLowレベルとなる。すなわち、先行予熱期間中の信号と同一の信号になり、スイッチング素子Q2,Q3の発振周波数も先行予熱期間中の設定と同じ発振周波数に制御される。

#### [0168]

一般的にインバータ回路3の発振周波数は、先行予熱期間の発振周波数>始動期間の発

10

20

30

50

振周波数 > 点灯時の発振周波数という関係に設定されているため、先行予熱期間中の設定と同じ発振周波数に制御されるということは、より高い発振周波数に制御されているということになる。つまり、直流電源回路 3 の出力電圧が所定の電圧より低下した場合には、インバータ回路 3 の発振周波数を高くなる方向に変化させて、インバータ回路 3 から放電灯 Laに供給する出力を低減させている。

### [0169]

ここで、放電灯 Laが寿命末期に近い状態であり、さらに実施形態 7~11の異常検出回路 7によって異常状態であると判断される直前の状態が継続した場合には、インバータ回路 3、負荷回路 4を流れる共振電流が著しく増大して、各々の部品の消費電力も増大し、直流電源回路 2においても過大な電力を供給しなければならないため、直流電源回路 2、インバータ回路 3、負荷回路 4に過大なストレスが印加されやすくなる。

### [0170]

さらに、直流電源回路 2 の出力電力の供給限界を超えると、直流電源回路 2 の出力電圧は、安定制御されずに低下しやすくなり、放電灯 L a のインピーダンスがさらに上昇を続けるため、インバータ回路 3 のスイッチング素子 Q 2 , Q 3 には共振電流の進相波形によるストレスが印加され、さらに過剰なストレスが印加されることになる。

### [0171]

しかし、本実施形態においては、直流電源回路2の出力電圧の低下を検出した場合には、インバータ回路3の発振周波数を高くして放電灯Laへの出力供給を低減させるため、前記共振電流の進相波形によるストレスが印加されず、さらに直流電源回路2、インバータ回路3での消費電力も低減することができる。

#### [0172]

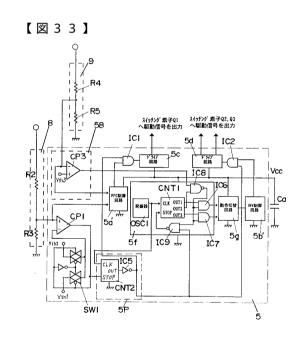

### (実施形態16)

本実施形態の放電灯点灯装置の回路構成は、図31,図32に示す実施形態15と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

### [0173]

図33に本実施形態の制御用集積回路5、電源入力検出回路8、及び電源出力検出回路9の詳細な構成を示し、制御用集積回路5の第1のタイマ回路5 f は、カウンタ回路CNT1の出力としてOUT1~OUT3端子を備えており、さらに、第2の出力抑制回路5 q の比較器CP3の出力とカウンタ回路CNT1のOUT2端子の出力とのNAND演算を行うNAND素子IC8の出力とINV素子IC5の出力とのNAND素子IC8の出力とIOP端子に入力するNAND素子IC9とを備えて、AND素子IC6はNAND素子IC8の出力とカウンタ回路CNT1のOUT1端子の出力とのAND演算を行い、AND素子IC7はNAND素子IC8の出力とカウンタ回路CNT1のOUT3端子の出力とのAND演算を行って、各々の演算結果を動作切替回路5gに出力しており、さらに電源出力検出回路9の出力信号を比較器CP3の反転入力端子に接続し、しきい値Vth3を非反転入力端子に接続しており、第2の出力抑制回路5 q からの出力信号の処理、及び第1のタイマ回路

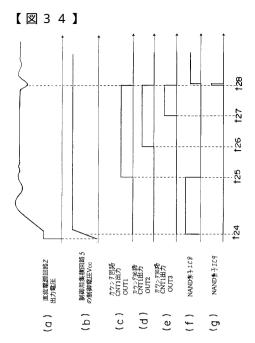

## [0174]

次に第2の出力抑制回路5 q、カウンタ回路CNT1の動作について図34(a)~(g)のタイムチャートを用いて説明する。交流電源AC投入後、時間t24で直流電源回路2の出力電圧は立ち上がる(図34(a))と同時に、制御用集積回路5の制御電圧Vccも立ち上がり(図34(b))、所定のレベルに達すると制御用集積回路5内の各部動作を開始する。

## [0175]

起動初期においては、カウンタ回路 C N T 1 の O U T 1 ~ O U T 3 端子の各出力(図 3 4 ( c ) ~ ( e ) ) は全て L o w レベルとなっており、ここで、O U T 2 端子の出力は N A N D 素子 I C 8 の一方の入力に接続しているため、N A N D 素子 I C 8 は他方の入力(比較器 C P 3 の出力)に関わらず、出力は H i g h レベルとなる。このとき、A N D 素子

10

20

30

40

IC6,IC7の各出力はLowレベルとなっており、動作切替回路5gによってスイッチング素子Q2,Q3の発振周波数は先行予熱期間中の発振周波数に制御される。

### [0176]

そして、時間 t 2 5 でカウンタ回路 C N T 1 の O U T 1 端子が H i g h レベルになると、 A N D 素子 I C 6 の出力も H i g h レベルになって、動作切替回路 5 g は先行予熱期間を終了して始動期間へと移行して、スイッチング素子 Q 2 , Q 3 の発振周波数は始動期間中の発振周波数に制御される。

## [0177]

次に時間 t 2 6 でカウンタ回路 C N T 1 の O U T 2 端子が H i g h レベルになり、このとき比較器 C P 3 の出力が L o w レベルであるなら、すなわち直流電源回路 2 の出力電圧が所定の電圧以上であるならば、N A N D 素子 I C 8 の出力は H i g h レベルのままであり、スイッチング素子 Q 2 , Q 3 の発振周波数は始動期間中の発振周波数を維持している

## [0178]

さらに時間t27でカウンタ回路CNT1のOUT2端子がHighレベルになると、 AND素子IC7の出力もHighレベルになって、動作切替回路5gは始動期間を終了 して、スイッチング素子Q2,Q3の発振周波数は点灯中の発振周波数に制御される。

## [0179]

時間 t 2 8 で何らかの理由で直流電源回路 2 の出力電圧が低下した場合、比較器 C P 3 の出力は H i g h レベルになるために、N A N D 素子 I C 8 の出力は L o w レベルになる。したがって A N D 素子 I C 6 , I C 7 の各出力も L o w レベルになり、動作切替回路 5 g に入力される信号は先行予熱期間中と同じ信号となり、スイッチング素子 Q 2 , Q 3 の発振周波数 は先行予熱期間中の発振周波数に制御される。

## [0180]

一方で、NAND素子IC8の出力はNAND素子IC9の一方の入力に入力されているため、直流電源回路2の出力電圧が低下してNAND素子IC8の出力がLowレベルになると、NAND素子IC9は他方の入力に関わらず出力はHighレベルになり、カウンタ回路CNT1のSTOP端子にHighレベルの信号が入力される。

## [0181]

カウンタ回路CNT1のSTOP端子にHighレベルの信号が入力されると、OUT 1~OUT3端子の各出力はLowレベルにリセットされ、NAND素子IC9の出力が Highレベルの間はカウント動作を停止する。

#### [0182]

そして、OUT2端子の出力がLowレベルになることによって、NAND素子IC8の出力はHighレベルになり、NAND素子IC9の出力がLowレベルになるために、カウンタ回路CNT1は再びカウント動作を開始する。ここで、NAND素子IC9の他方の入力は、実施形態13で説明した、交流電源ACの低下を検出して信号を出力する第4のタイマ回路5pの出力を接続しており、交流電源ACが所定の電圧レベルであれば、第4のタイマ回路5pの出力はHighレベルであるために上記動作には影響を与えない。

## [0183]

また、第4のタイマ回路5 pの出力がLowレベルになった場合においても、NAND素子IC9からHighレベルの信号が出力されて、カウント回路CNT1のカウント動作を停止する。

#### [0184]

前記動作を行う本実施形態では、直流電源回路2の出力電圧が低下したときに、電源出力検出回路9の出力信号によってインバータ回路3の発振周波数を高い方向(先行予熱期間の発振周波数>始動期間の発振周波数>点灯時の発振周波数)に制御するのは、カウンタ回路CNT1のOUT2端子がHighレベルの信号を出力する時間t26以降であり、時間t24~t26までの間は電源出力検出回路9の出力信号によるインバータ回路3

10

20

30

40

の発振周波数の可変制御を禁止している。

## [0185]

交流電源ACを投入直後、直流電源回路2である昇圧チョッパ回路の起動直後の出力電圧は、図34(a)に示すように安定するまでに時間がかかり、リプルが大きい場合もある。また、昇圧チョッパ回路をソフトスタートさせる場合、昇圧チョッパ回路の出力電圧が所定のレベルに安定するまでに比較的長時間を要し、さらに、交流電源ACの変動、使用部品の定数の公差、温度特性等によって出力電圧が安定するまでのリプルが増大することもあるため、実施形態15の構成ではこのリプル電圧による誤動作の恐れがある。

### [0186]

本実施形態では、この起動時のリプル電圧による誤動作を回避するために、時間 t 2 4 ~ t 2 6 まで、電源出力検出回路 9 の出力信号によるインバータ回路 3 の発振周波数の可変制御を禁止しているため、リプル電圧による誤動作を生じることはない。

#### [0187]

なお、本実施形態では、時間 t 2 6 は、 t 2 5 t 2 6 t 2 7 を満たす時間であればどのような時間設定であってもよい。ただし、先行予熱期間から始動電圧印加期間に移行した直後、放電灯 L a に高電圧の始動電圧が印加されて点灯するが、共振用インダクタ L 3、共振用コンデンサ C 4 の設定によってはこの始動期間中でのインバータ回路 3 の発振周波数においても定格時に比較的近いランプ電力を消費する場合があり、このときに昇圧チョッパ回路の出力電圧が低下する場合もあり、時間 t 2 6 は時間 t 2 7 に近いほうが望ましい。

#### [0188]

さらに本実施形態では、カウンタ回路 CNT1の出力信号をもとに第2の出力抑制回路5 qの出力信号を後段に伝達しないようにして、電源出力検出回路9の出力信号によるインバータ回路3の発振周波数の可変制御を禁止しているが、この禁止期間中に、第2の出力抑制回路5 qに設定されているしきい値 Vth3の値を切り替えたり、または第2の出力抑制回路5 qの出力が確実にLowレベルになるようなロジック回路を構成する等、前記と同様の動作が達成できるならどのような手段を用いてもよい。

## [0189]

## (実施形態17)

本実施形態の放電灯点灯装置の回路構成は、図1に示す実施形態1と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。

## [0190]

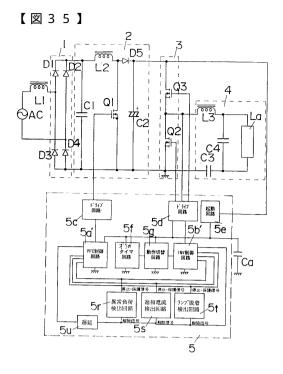

本実施形態の制御用集積回路 5 は、異常負荷検出回路 5 r と、進相電流検出回路 5 s と、ランプ脱着検出回路 5 t と、遅延回路 5 u とを備えたものである。

# [0191]

異常負荷検出回路 5 r は、負荷である放電灯 L a の状態を検出するものであり、放電灯 L a の異常状態を検出したときは、 P F C 制御回路 5 a '及び I N V 制御回路 5 b 'に停止・保護信号を出力して、直流電源回路 2 及びインバータ回路 3 の動作を停止または保護状態にする。

### [0192]

進相電流検出回路5gは、スイッチング素子Q2,Q3の電流を検出するものであり、 共振用インダクタL3、共振用コンデンサC4によって形成される共振回路の共振周波数よりも低い周波数で点灯動作させる場合に、放電灯Laの放電状態が不安定な状態(例えばランプインピーダンスが急激に上昇する立消え状態)においては、スイッチング素子Q2,Q3に進相電流が流れるため、その進相状態を検出した場合に、PFC制御回路5a′及びINV制御回路5b′に停止・保護信号を出力して、直流電源回路2及びインバータ回路3の動作を停止または保護状態にする。

### [0193]

ランプ脱着検出回路 5 t は、放電灯 L a の着脱を検出するものであり、放電灯 L a が正常に装着されていないことを検出したときは、PFC制御回路 5 a '及び I N V 制御回路

10

20

30

40

5 b ' に停止・保護信号を出力して、直流電源回路 2 及びインバータ回路 3 の動作を停止または保護状態にする。

#### [0194]

遅延回路 5 u は、異常負荷検出回路 5 r、進相電流検出回路 5 s、ランプ脱着検出回路 5 t から発振停止あるいは保護動作の解除信号を出力した際に、 P F C 制御回路 5 a 'での解除動作の開始を遅延させるものである。

#### [0195]

すなわち、各検出回路からの解除信号によって、回路の保護状態(回路停止または出力抑制)から通常動作に復帰させる場合には、PFC制御回路への解除信号に遅延回路5 uで遅延時間を持たせることによって、直流電源回路2 からインバータ回路3 へ供給する電圧が低い状態で復帰直後の負荷状態を検出することができる。

#### [0196]

したがって、例えば検出誤動作によって解除信号が出力された場合でも、解除信号に遅延を持たせることによって、部品、素子へのストレスを抑えた状態で負荷状態を判別することができる。

#### [0197]

そして、本実施形態においても、PFC制御回路5 a '、INV制御回路5 b '、異常負荷検出回路5 r、進相電流検出回路5 s、ランプ脱着検出回路5 t を含む各制御回路、各検出回路を同一の集積回路(制御用集積回路5)に備えており、外部にて別々にロジック回路を構成するものと比較して、過渡的に発生するストレスモードによるノイズの影響を受けにくくなるため、安定した動作を行うことができ、検出・保護動作を素早く行うことができ、ストレスが印加される期間を最小限に抑えることができる。

### [0198]

なお、本実施形態には記載していないが、異常負荷検出、進相電流検出、ランプ脱着検出の動作を行う外部回路については、その種類を問わない。また、回路の保護状態についても、発振停止、間欠発振、出力抑制等の部品、素子へのストレスを緩和できる手段であれば、その方法は問わない。

#### [0199]

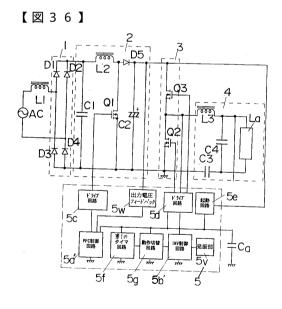

## (実施形態18)

本実施形態の放電灯点灯装置の回路構成は、図1に示す実施形態1と略同様の構成を有しており、同様の構成には同一の符号を付して説明は省略する。本実施形態の制御用集積回路5は、直流電源回路2の出力電圧を検出してPFC制御回路5 a 'にフィードバックする出力電圧フィードバック回路5 wと、INV制御回路5 b 'に接続し、ドライブ回路5 d に出力する制御信号の周波数を設定することでインバータ回路3の発振周波数を設定する発振部5 v とを備えている。

#### [0200]

放電灯Laを含む共振回路の共振動作によって点灯を行う放電灯点灯装置は、周囲温度によるランプインピーダンスの変化による大きな影響を受ける。放電灯Laの周囲温度が高い場合、ランプインピーダンスの低下によって、ランプ電流が増加し、逆に周囲温度が低い場合にはランプ電流が減少する。特に、放電灯Laへの出力電力を一定に保とうとする補正機能を設けた回路は前記現象が顕著に現れる。

#### [0201]

そこで、本実施形態においては、制御用集積回路 5 の周囲温度をパラメータとして、インバータ回路 3 の出力を高温時には減少させ、低温時には増加させる温度依存性を制御用集積回路 5 の特性に持たせたことを特徴とする。

## [0202]

具体的には、制御用集積回路 5 の周囲温度に対して、インバータ回路 3 の発振周波数に正の温度特性、すなわち発振部 5 v が出力する発振周波数に正の温度特性を持たせ、出力電圧フィードバック回路 5 w がフィードバックする信号に負の温度特性、すなわち直流電源回路 2 の出力電圧に負の温度特性を持たせた。

10

20

30

40

### [0203]

したがって、放電灯 L a の周囲温度が高い状態、すなわち制御用集積回路 5 の周囲温度が高い状態では、ランプ電流の過剰な増加を抑制し、逆に放電灯 L a の周囲温度が低い状態 では、ランプ電流を増加させることによって、放電灯 L a を安定して点灯させることができる。

#### [0204]

この方式においては、特に制御用集積回路 5 の内部に複数の出力制御要因(本実施形態では直流電源回路制御とインバータ回路制御)を備えたものは、同一チップ内で回路を構成するために素子間のバラツキを抑制することができ、同じ周囲温度に対して制御を行うことができて、精度のよい出力制御を行うことができる。

## [0205]

また、本実施形態では、直流電源回路制御とインバータ回路制御の両方について温度依存性を持たせたが、必要に応じていずれか1つでもよいし、他に出力を変化させる要因があれば、それでもよい。たとえば、出力電力を一定に保つ補正機能を持つ放電灯点灯装置に対しては、補正のためのフィードバック信号、あるいは基準となる電圧に温度依存性を持たせることによっても本実施形態と同様の効果を得ることができる。

### [0206]

したがって、同一の集積回路に精度よく温度特性を持たせることによって、放電灯Laを安定に点灯させ、部品、素子にかかるストレスを低減して、過剰な温度上昇を抑制することができる。

#### [0207]

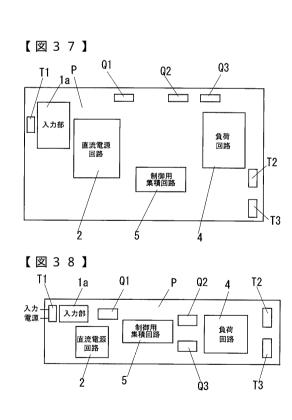

### (実施形態19)

図37は、実施形態1~18の放電灯点灯装置をプリント基板P上に配置した構成を示す。プリント基板Pは、部品の実装面を長方形に形成し、実装面の長手方向の一端に交流電源ACを接続する入力端子T1を配置し、その一端側から他端側に入力部1a(整流器1を含む)、直流電源回路2、制御用集積回路5、放電灯Laを除く負荷回路4を順に配置して、実装面の長手方向の他端には放電灯Laを接続するための出力端子T2,T3を配置している。

## [0208]

制御用集積回路5は、直方体のパッケージを備えて、パッケージの長手方向に沿った両側面にリード(図示なし)を設けており、パッケージの長辺方向をプリント基板Pの長辺方向と同一方向として配置されている。そして、そのリードのうち直流電源回路2のスイッチング素子Q1の駆動信号を出力するリードは、入力端子T1側である一端側に設けられ、インバータ回路2のスイッチング素子Q2,Q3を駆動するリードは入力端子T2,T3側である他端側に設けられている。

#### [0209]

そして、直流電源回路2のスイッチング素子Q1は制御用集積回路5より入力端子T1側に配置し、インバータ回路3のスイッチング素子Q2,Q3は制御用集積回路5より出力端子T2,T3側に配置し、且つスイッチング素子Q1~Q3は、プリント基板Pの一方の側面側に互いに並んで配置されている。

したがって、スイッチング素子Q1の駆動信号の配線が、負荷回路4からの信号線と交差 しないようにプリント基板P上の配線を行うことが比較的容易になり、信号線の交差によ って引き起こされるノイズによる誤動作を防止することができる。

## [0210]

また、直流電源回路 2 のスイッチング素子 Q 1 の駆動信号と、インバータ回路 3 のスイッチング素子 Q 2 , Q 3 の駆動信号との各配線が、互いに交差することなく配線可能となる。

## [0211]

また、スイッチング素子Q1を制御用集積回路5のスイッチング素子Q1の駆動信号を 出力するリードの近傍に配置し、スイッチング素子Q2,3を制御用集積回路5のスイッ 10

20

30

40

チング素子Q2,Q3の駆動信号を出力するリードの近傍に配置することによって、各駆動信号の配線が最短となって駆動信号のパターン面積を減少させて、輻射雑音を低減することができる。

### [0212]

さらには、温度上昇が高い部品である入力部1 a、スイッチング素子Q1~Q3、負荷回路4を避ける位置に、実施形態8または実施形態18で説明した温度依存性を持った制御用集積回路5を配置することによって部品実装上、最も正確に周囲温度を制御用集積回路5に反映することができる。

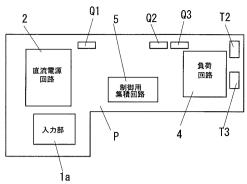

### [0213]

2つめの配置例としては、図38に示すように、部品の実装面を長方形に形成したプリント基板Pの実装面の長手方向の一端に交流電源ACを接続する入力端子T1を配置し、その一端側から他端側に入力部1a(整流器1を含む)、直流電源回路2、スイッチング素子Q1、制御用集積回路5、スイッチング素子Q2,Q3、放電灯Laを除く負荷回路4を順に配置して、実装面の長手方向の他端には放電灯Laを接続するための出力端子T2,T3を配置しても、前記同様の効果を得ることができる。

#### [0214]

さらには、プリント基板 P の実装面の形状は長方形に限らず、図 3 9 に示すように、略 L 字形の実装面を有するプリント基板 P を用いてもよく、この場合は長辺方向の一端に、直流電源回路 2 と入力部 1 a とを短辺方向に並んで配置し、他端側に向かって、スイッチング素子 Q 1、制御用集積回路 5、スイッチング素子 Q 2 、Q 3、負荷部 4、出力端子 T 2 、T 3 を配置しても、前記同様の効果を得ることができる。

#### 【 0 2 1 5 】

要するに、プリント基板 P 上に、制御用集積回路 5 を基準として、入力側に直流電源回路 2 の部品を配置し、出力側にインバータ回路 3 、負荷回路 4 の部品を配置する構成であればよい。

【図面の簡単な説明】

### [0216]

- 【図1】本発明の実施形態1の回路構成を示す図である。

- 【図2】本発明の第1の基本構成を示す図である。

- 【図3】本発明の第2の基本構成を示す図である。

- 【図4】本発明の第3の基本構成を示す図である。

- 【図5】本発明の第4の基本構成を示す図である。

- 【図6】本発明の実施形態2の回路構成を示す図である。

- 【図7】本発明の実施形態3の第1の回路構成を示す図である。

- 【図8】本発明の実施形態3の第2の回路構成を示す図である。

- 【図9】(a)~(e)本発明の実施形態4の動作のタイムチャートを示す図である。

- 【図10】(a)~(f)本発明の実施形態5の動作のタイムチャートを示す図である。

- 【図11】(a)~(f)本発明の実施形態6の動作のタイムチャートを示す図である。

- 【図12】本発明の実施形態7の回路構成を示す図である。

- 【図13】(a)~(g)本発明の実施形態7の動作のタイムチャートを示す図である。

- 【図14】本発明の実施形態8の周囲温度変動特性を示す図である。

- 【図15】本発明の実施形態8の機能・特性を示す図である。

- 【図16】本発明の実施形態9の回路構成を示す図である。

- 【図17】(a)~(d)本発明の実施形態9の動作波形を示す図である。

- 【図18】(a)~(d)本発明の実施形態9の正常時の動作のタイムチャートを示す図である。

- 【図19】(a)~(e)本発明の実施形態9の異常時の動作のタイムチャートを示す図 である。

- 【図20】(a)~(d)本発明の実施形態10の動作のタイムチャートを示す図である

10

20

30

50

- 【図21】本発明の実施形態11の回路構成を示す図である。

- 【図22】(a)~(f)本発明の実施形態11の動作のタイムチャートを示す図である

0

- 【図23】本発明の実施形態12の回路構成を示す図である。

- 【図24】本発明の実施形態12の部分回路構成を示す図である。

- 【図25】(a)~(g)本発明の実施形態12の動作のタイムチャートを示す図である

- 【図26】本発明の実施形態13の回路構成を示す図である。

- 【図27】(a)~(e)本発明の実施形態13の動作の第1のタイムチャートを示す図である。

10

- 【図28】(a)~(d)本発明の実施形態13の動作の第2のタイムチャートを示す図である。

- 【図 2 9 】 (a) ~ (d) 本発明の実施形態 1 3 の動作の第 3 のタイムチャートを示す図である。

- 【図30】本発明の実施形態14の回路構成を示す図である。

- 【図31】本発明の実施形態15の回路構成を示す図である。

- 【図32】本発明の実施形態15の部分回路構成を示す図である。

- 【図33】本発明の実施形態16の部分回路構成を示す図である。

- 【図34】(a)~(g)本発明の実施形態16の動作のタイムチャートを示す図である

20

- 【図35】本発明の実施形態17の回路構成を示す図である。

- 【図36】本発明の実施形態18の回路構成を示す図である。

- 【図37】本発明の実施形態19の第1の部品配置を示す図である。

- 【図38】本発明の実施形態19の第2の部品配置を示す図である。

- 【図39】本発明の実施形態19の第3の部品配置を示す図である。

- 【図40】従来例の第1の回路構成を示す図である。

- 【図41】従来例の部品配置を示す図である。

- 【図42】従来例の第2の回路構成を示す図である。

#### 【符号の説明】

[0217]

- 3 インバータ回路

- 5 制御用集積回路

- 5 b ' INV制御回路(第2の制御手段)

- 5 d ドライブ回路

- 5 e 起動回路

- 5 f 第 1 の タイマ 回路 ( 第 1 の タイマ 手段 )

- 5 g 動作切替回路(動作切替手段)

- Q2,Q3 スイッチング素子

- La 放電灯

- インバータ回路 制御用集積回路 ・ INV制御回路(第2の制御手段) ドライブ回路

- 5 d トフィノ回路 5 e 起動回路 5 f 第1のタイマ回路(第1のタイマ手段) 5 g 動作切替回路(動作切替手段) Q 2, Q 3 スイッチング素子 L a 放電灯

【図2】

【図3】

【図4】

【図9】

【図10】

【図11】

【図12】

## 【図13】

## 【図14】

## 【図15】

| タイマ回路 | 機能                     | 低温 | 高温 |

|-------|------------------------|----|----|

| タイマ1  | 先行予熱期間、始動電圧印<br>加期間の設定 | 長  | 短  |

| タイマ2  | 異常状態継続時間の測定            | 長  | 短  |

| タイマ3  | 異常検出時の出力制御期<br>間の設定    | 短  | 長  |

## 【図16】

## 【図17】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

(p)

(p) (c)

【図29】

| 電源入力検出    | 比較器CP1 | 発振器のSC/ | がか回路   |

|-----------|--------|---------|--------|

| 回路 8 出力信号 | 出力     | 出力      | CNT2出力 |

| (D)       | (p)    | (c)     | (p)    |

【図39】

## 【図40】

【図41】

# 【図42】

### フロントページの続き

(72)発明者 山中 正弘

大阪府門真市大字門真1048番地 松下電工株式会社内

(72)発明者 黒木 芳文

大阪府門真市大字門真1048番地 松下電工株式会社内

## 審査官 宮崎 光治

(56)参考文献 特開平11-008083(JP,A)

特開2001-135494(JP,A)

特開2000-030887(JP,A)

特開平11-135289(JP,A)

特開2001-052886(JP,A)

特開2001-345191(JP,A)

特開平09-237690(JP,A)

特開2000-215996(JP,A)

特開昭62-163290(JP,A)

特開2001-023780(JP,A)

特開2001-035679(JP,A)

特開昭55-137698(JP,A)

特開平02-288195(JP,A)

特開平03-285296(JP,A)

特開平06-076966(JP,A)

特開平05-082280(JP,A)

(58)調査した分野(Int.CI., DB名)

H05B 41/24-43/02