# (10) **DE 10 2008 051 542 A1** 2009.05.14

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2008 051 542.6

(22) Anmeldetag: 14.10.2008 (43) Offenlegungstag: 14.05.2009 (51) Int Cl.8: **H01L 23/29** (2006.01)

H01L 21/56 (2006.01)

(30) Unionspriorität:

11/933,459 01.11.2007

US

Patentanwälte Lambsdorff & Lange, 81673

München

(71) Anmelder:

Infineon Technologies AG, 85579 Neubiberg, DE

(72) Erfinder:

(74) Vertreter:

Mahler, Joachim, 93051 Regensburg, DE; Behrens, Thomas, 93173 Wenzenbach, DE; Galesic, Ivan, 93053 Regensburg, DE

Prüfungsantrag gemäß § 44 PatG ist gestellt.

#### Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

## (54) Bezeichnung: Integriertes Schaltungsbauelement und Verfahren

(57) Zusammenfassung: Ein integriertes Schaltungsbauelement enthält einen Halbleiterchip mit einer Metallisierungsschicht auf dem Chip. Eine aus der Gasphase abgeschiedene Isolationsschicht ist auf der Metallisierungsschicht angeordnet.

### **Beschreibung**

#### Allgemeiner Stand der Technik

[0001] Halbleiter-Bauelemente wie etwa integrierte Schaltungs-Packages (IC) enthalten in der Regel ein oder mehrere auf einem Systemträger oder Träger angeordnete Halbleiter-Bauelemente. Das Halbleiter-Bauelement wird in der Regel durch ein klebendes Material oder durch Löten an dem Systemträger angebracht, und Bonddrähte werden an Bond-Pads auf den Halbleiter-Bauelementen und an Anschlussdrahtfingern auf dem Träger angebracht, um elektrische Zwischenverbindungen zwischen den verschiedenen Halbleiter-Bauelementen und/oder zwischen einem Halbleiter-Bauelement und dem Träger bereitzustellen. Das Bauelement wird dann in einem Kunststoffgehäuse gekapselt, um beispielsweise einen Schutz bereitzustellen und ein Gehäuse zu bilden, von dem aus sich die Anschlussdrähte erstrecken.

[0002] Solche Halbleiter-Packages enthalten in der Regel einen Halbleiterchip mit einer über dem Chip ausgebildeten Metallisierungsschicht, um unter anderem Leiterbahnen und die leitenden Kontaktflecken für die Drahtbindungen bereitzustellen. Die Metallisierungsschicht besteht oftmals aus mehreren Schichten wie beispielsweise Kupfer-, Nickel-Phosphor-, Palladium- und/oder Goldschichten. Das direkte Aufbringen des Kunststoffkapselungsmaterials über der Metallisierungsschicht kann zu elektrischen Kurzschlüssen zwischen verschiedenen elektrischen Potentialen der Metallisierungsschicht, Korrosion durch und unter der Metallisierung, unzureichender Verkapselungsmasse und adhäsivem Binden (was zu einer Delamination des Kapselungsmaterials führt) usw. führen.

[0003] Lösungsversuche für solche Probleme waren größtenteils unzufriedenstellend. Beispielsweise wird manchmal eine Polyimid-Beschichtung auf der Chipfront-Metallisierungsschicht aufgebracht, doch auch dies ist mit Nachteilen verbunden. Beispielsweise kann der hohe Feuchtigkeitsgehalt der Polyimide tatsächlich die Korrosion und Kontamination der Metallisierung fördern, und die hinzugefügte Schicht aus Polyimid liefert möglicherweise nicht die gewünschte Wärmeleitfähigkeit. Zudem sind die Polyimid-Materialien im Allgemeinen teuer.

**[0004]** Aus diesen und anderen Gründen besteht ein Bedarf an der vorliegenden Erfindung.

### Kurze Darstellung der Erfindung

[0005] Gemäß Aspekten der vorliegenden Offenbarung enthält ein integriertes Schaltungsbauelement einen Halbleiterchip mit einer Metallisierungsschicht auf dem Chip. Eine aus der Gasphase abgeschiedene Isolationsschicht wird auf der Metallisierungs-

schicht abgeschieden. Bei Ausführungsbeispielen enthält diese ein anorganisches Material.

## Kurze Beschreibung der Zeichnungen

**[0006]** Ausführungsformen der Erfindung werden bei Bezugnahme auf die folgenden Zeichnungen besser verständlich. Die Elemente der Zeichnungen sind relativ zueinander nicht notwendigerweise maßstabsgetreu. Gleiche Bezugszahlen bezeichnen entsprechende ähnliche Teile.

**[0007]** Fig. 1 ist ein Blockdiagramm, das ein Konzept einer Seitenansicht eines integrierten Schaltungsbauelements darstellt.

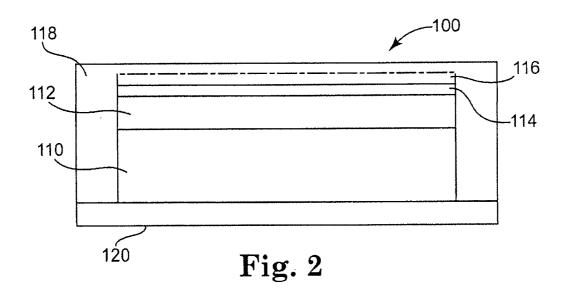

**[0008]** Fig. 2 ist ein Blockdiagramm, das das Konzept weiterer Aspekte eines integrierten Schaltungsbauelements darstellt.

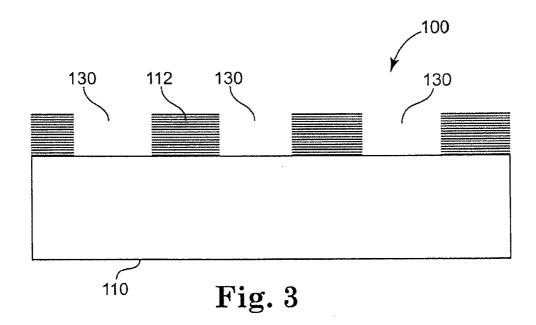

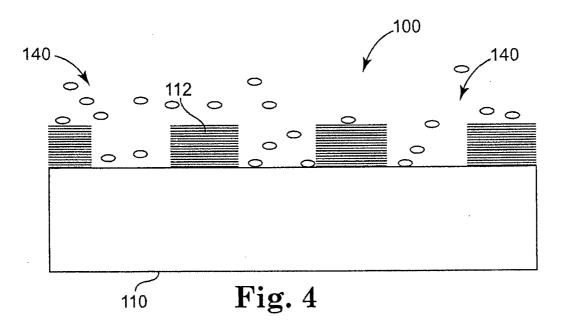

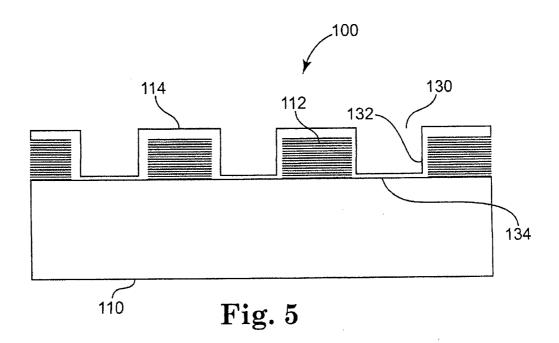

**[0009]** Fig. 3–Fig. 5 sind Blockdiagramme, die verschiedene Abschnitte, eines integrierten Schaltungsbauelements darstellen.

#### Ausführliche Beschreibung

[0010] In der folgenden ausführlichen Beschreibung wird auf die beiliegenden Zeichnungen Bezug genommen, die einen Teil hiervon bilden und in denen als Veranschaulichung spezifische Ausführungsformen gezeigt sind, in denen die Erfindung ausgeübt werden kann. In dieser Hinsicht wird Richtungsterminologie wie etwa "Oberseite", "Unterseite", "Vorderseite", "Rückseite", "vorderer", "hinterer" usw. unter Bezugnahme auf die Orientierung der beschriebenen Figur(en) verwendet. Da Komponenten von Ausführungsformen der vorliegenden Erfindung in mehreren verschiedenen Orientierungen positioniert sein können, wird die Richtungsterminologie zu Zwecken der Darstellung verwendet und ist in keinerlei Weise einschränkend. Es versteht sich, dass andere Ausführungsformen genutzt und strukturelle oder logische Änderungen vorgenommen werden können, ohne von dem Schutzbereich der vorliegenden Erfindung abzuweichen. Die folgende ausführliche Beschreibung ist deshalb nicht in einem einschränkendem Sinne zu verstehen, und der Schutzbereich der vorliegenden Erfindung wird durch die beigefügten Ansprüche definiert.

[0011] Fig. 1 ist eine schematische Seitenansicht, die ein Konzept eines integrierten Schaltungsbauelements gemäß Ausführungsformen der vorliegenden Erfindung veranschaulicht. Das beispielhafte integrierte Schaltungsbauelement 100 enthält ein Halbleiter-Bauelement oder einen Chip 110, auf dem eine Metallisierungsschicht 112 abgeschieden ist. Eine Isolationsschicht 114 ist über der Metallisierungsschicht abgeschieden, die unter anderem die Metallisierung 112 schützt. Fig. 2 zeigt weitere Aspekte ei-

nes derartigen beispielhaften integrierten Schaltungsbauelements **100**, wobei eine zusätzliche Schicht **116** gezeigt ist, die über der Isolationsschicht gemäß bestimmten Ausführungsformen vorgesehen ist. Der Chip **110** ist mit einem Chipträger oder Systemträger **120** verbunden gezeigt, und ein Formmaterial **118** kapselt das Bauelement **100**.

[0012] Die Metallisierungsschicht 112 kann beispielsweise mehrere Schichten enthalten. Beispielsweise enthält die Metallisierungsschicht 112 bei einigen Ausführungsformen Schichten aus Kupfer, Nickel-Phosphor, Palladium und Gold, wodurch eine Metallisierungsschicht mit einer Dicke von mehr als 10 nm entsteht. Wie oben angemerkt, besteht ein Zweck der Isolationsschicht 114 in dem Schutz der Metallisierungsschicht 112. Wenn jedoch das zum Ausbilden der Isolationsschicht 114 abgeschiedene Material einen hohen Feuchtigkeitsgehalt aufweist, kann dies zur Korrosion der Metallisierungsschicht 112 führen und Kurzschlüsse zwischen Bereichen der Metallisierungsschicht mit verschiedenen elektrischen Potentialen herbeiführen. Somit wird die Isolationsschicht 114 aus einem Material hergestellt, das in der Gasphase auf der Metallisierungsschicht 112 abgeschieden werden kann, anstatt das Material in der flüssigen Phase aufzubringen, wie bei einigen bekannten Prozessen. Die resultierende Isolationsschicht 114 besitzt eine Dicke im Bereich von etwa 10 nm-20 µm, als Beispiel. Es werden Ausführungsformen in Betracht gezogen, bei denen die Dicke etwa 1 µm beträgt, und die eine robuste Schicht zum Schutz der Metallisierungsschicht 114 und einer Oberfläche liefern, die die Haftung des Formmaterials 118 fördert, oder für zusätzliche Halbleiter, die auf dem Bauelement 100 montiert sind, wie bei einer Chip-auf-Chip-Anordnung.

[0013] Die Fig. 3–Fig. 5 zeigen verschiedene Aspekte des Bauelements 100. Wie in Fig. 3 gezeigt, besitzt der Halbleiterchip 110 die darauf ausgebildete Metallisierungsschicht 112. Die Metallisierungsschicht 112 liefert unter anderem Verbindungspunkte für Drahtverbindungen oder andere Leiter. Bei der dargestellten Ausführungsform besitzt die Metallisierungsschicht 112 Gräben 130, die über dem Chip 110 ausgebildet sind.

[0014] Die Isolationsschicht 114 besteht beispielsweise aus einem in der Gasphase auf der Metallisierungsschicht 112 abgeschiedenen anorganischen oder keramischen Material. Fig. 4 veranschaulicht das Konzept der Abscheidung von anorganischen Vorläufern 140 aus der Gasphase unter Verwendung eines geeigneten Gasphasenabscheidungsprozesses wie etwa dem Prozess der chemischen Abscheidung aus der Dampfphase (CVD) oder dem Prozess der plasmaunterstützten chemischen Abscheidung aus der Dampfphase (PE-CVD), was zu dem gewünschten anorganischen Material für die Isolations-

schicht **114** führt. Zu geeigneten anorganischen Vorläufern zählen beispielsweise Silan oder Titanat.

[0015] Fig. 5 zeigt die aus der Gasphase abgeschiedene Isolationsschicht 114 auf der Metallisierungsschicht 112, einschließlich Seitenwänden 132 und des unteren Bodens 134 der Gräben 130. Wie oben angemerkt, besteht die Isolationsschicht 114 bei Ausführungsbeispielen aus einem anorganischen Material, einschließlich Silika, Silikanitrid, CVD-Diamant, Titandioxid oder Zirkoniumoxid, als Beispiel. Bei weiteren Ausführungsformen enthält die aus der Gasphase abgeschiedene Schicht ein Keramikmaterial wie etwa diamantartigen Kohlenstoff (DLC - diamond-like carbon). Der Ausdruck diamantartiger Kohlenstoff (DLC) bezieht sich im Allgemeinen auf eine beliebige der sieben Formen von amorphem Kohlenstoffmaterial mit einer sp<sup>3</sup>-Gitterstruktur oder einer modifizierten sp³-Gitterstruktur, einschließlich eines sp<sup>2</sup>-Gitterabschnitts aus Kohlenstoffbindungen, der einige der physikalischen Eigenschaften von Naturdiamant zeigt. Das zu der aus der Gasphase abgeschiedenen Isolationsschicht führende Material besitzt einen niedrigen Feuchtigkeitsgehalt, wodurch zumindest die Wahrscheinlichkeit von Kurzschlüssen oder Korrosion auf der Metallisierungsschicht 112 reduziert wird.

[0016] Bei noch weiteren Ausführungsformen enthält die Isolationsschicht 114 amorphen Kohlenstoff mit weiter eingearbeiteten Elementen wie etwa Silizium, Wasserstoff und/oder Sauerstoff. Die zugesetzten Elemente können in einem solchen Verhältnis zugesetzt werden, dass der gleiche oder ein ähnlicher Wärmeausdehnungskoeffizient (CTE – Coefficient of Thermal Expansion) wie der Chip 110 erreicht wird, was Wärmespannung wesentlich reduziert. Zudem besitzt eine derartige amorphe anorganische Isolationsschicht oder eine Schicht vom Keramik-Kohlenstoff-Typ eine Temperaturstabilität bis zu 450–500°C.

[0017] Bei anderen Ausführungsformen besteht die Isolationsschicht 114 aus einem organischen polymeren Material wie etwa plasmaerzeugten Polymeren wie Parylen oder Teflon. Solche Materialien verhindern oder reduzieren die Wahrscheinlichkeit einer Kontamination der Metallisierungsschicht 114 und liefern auch eine elektrische Isolation. Sie nehmen sehr wenig Feuchtigkeit auf und sind vergleichsweise elastisch, wodurch thermomechanische Belastungen abgepuffert werden.

[0018] Zum Verbessern der Haftung der Formmasse 118 oder anderer Kleber auf solchen Polymerschichten kann ein Sperrplasmabehandlungsprozess, insbesondere mit Sauerstoff, verwendet werden. Bei anderen Implementierungen wird eine dünne (beispielsweise 1–10 nm) Haftvermittlerschicht (wie etwa die in Fig. 2 gezeigte Schicht 116) unter Verwendung eines Materials wie etwa einem Silan

aus der Gasphase auf der Isolationsschicht **114** abgeschieden.

[0019] Eine Maskenschicht kann verwendet werden, um die Isolationsschicht 114 zu strukturieren, oder die Isolationsschicht 114 kann unter Verwendung eines geeigneten Fotolithographieprozesses strukturiert werden. Bei weiteren Ausführungsformen kann zum Strukturieren der Isolationsschicht ein Laser-Ablationsprozess verwendet werden.

[0020] Wenngleich hierin spezifische Ausführungsformen dargestellt und beschrieben worden sind, versteht sich für den Durchschnittsfachmann, dass die gezeigten und beschriebenen spezifischen Ausführungsformen durch eine Vielzahl alternativer und/oder äquivalenter Implementierungen ersetzt werden können, ohne von dem Schutzbereich der vorliegenden Erfindung abzuweichen. Diese Anmeldung soll alle Adaptationen oder Variationen der hierin erörterten spezifischen Ausführungsformen abdecken. Deshalb soll die vorliegende Erfindung nur durch die Ansprüche und die Äquivalente davon beschränkt werden.

#### Patentansprüche

Integriertes Schaltungsbauelement, umfassend:

einen Halbleiterchip;

eine Metallisierungsschicht auf dem Chip und eine auf der Metallisierungsschicht angeordnete, aus der Gasphase abgeschiedene Isolationsschicht.

- 2. Integriertes Schaltungsbauelement nach Anspruch 1, wobei die aus der Gasphase abgeschiedene Isolationsschicht dünner ist als 20 µm.

- 3. Integriertes Schaltungsbauelement nach Anspruch 1, wobei die Metallisierungsschicht eine Dicke von mehr als 10 nm aufweist.

- 4. Integriertes Schaltungsbauelement nach Anspruch 1, wobei die Metallisierungsschicht mindestens eines von Kupfer, Gold und Palladium enthält.

- 5. Integriertes Schaltungsbauelement nach Anspruch 1, wobei die Metallisierungsschicht mehrere Schichten enthält.

- 6. Integriertes Schaltungsbauelement nach Anspruch 1, weiterhin umfassend ein über der aus der Gasphase abgeschiedenen Isolationsschicht abgeschiedenes Kapselungsmaterial.

- 7. Integriertes Schaltungsbauelement nach Anspruch 1, wobei die aus der Gasphase abgeschiedene Schicht ein anorganisches Material enthält.

- 8. Integriertes Schaltungsbauelement nach An-

spruch 1, wobei die aus der Gasphase abgeschiedene Schicht ein Keramikmaterial enthält.

- 9. Integriertes Schaltungsbauelement nach Anspruch 1, wobei die aus der Gasphase abgeschiedene Schicht mindestens eines von Silika, Silikanitrid, CVD-Diamant, Titandioxid, Zirkoniumoxid, diamantartigem Kohlenstoff (DLC), amorphem Kohlenstoff, Parylen und/oder Teflon enthält.

- 10. Integriertes Schaltungsbauelement nach Anspruch 1, wobei die aus der Gasphase abgeschiedene Schicht ein organisches polymeres Material enthält, und weiterhin umfassend eine Haftvermittlerschicht über der Isolationsschicht.

- 11. Integriertes Schaltungsbauelement nach Anspruch 1, wobei die Metallisierungsschicht einen Graben mit Seitenwänden und einem Boden enthält und wobei die aus der Gasphase abgeschiedene Isolationsschicht die Seitenwände und den Boden des Grabens bedeckt.

- 12. Verfahren zum Herstellen eines integrierten Schaltungsbauelements, umfassend:

Bereitstellen eines Halbleiterchips;

Aufbringen einer Metallisierungsschicht auf dem Halbleiterchip;

Aufbringen einer Isolationsschicht über der Metallisierungsschicht durch eine Gasphasenabscheidung.

- 13. Verfahren nach Anspruch 12, wobei das Aufbringen der Isolationsschicht das Abscheiden eines anorganischen Vorläufers beinhaltet.

- 14. Verfahren nach Anspruch 12, weiterhin umfassend das Strukturieren der Isolationsschicht.

- 15. Verfahren nach Anspruch 14, wobei das Strukturieren der Isolationsschicht das Abscheiden einer Maskenschicht beinhaltet.

- 16. Verfahren nach Anspruch 14, wobei das Strukturieren der Isolationsschicht einen fotolithographischen Prozess beinhaltet.

- 17. Verfahren nach Anspruch 14, wobei das Strukturieren der Isolationsschicht Laser-Ablation beinhaltet.

- 18. Verfahren nach Anspruch 12, weiterhin umfassend das Kapseln des integrierten Schaltungsbauelements.

- 19. Verfahren nach Anspruch 12, wobei die Gasphasenabscheidung einen Prozess der chemischen Abscheidung aus der Dampfphase (CVD) beinhaltet.

- 20. Verfahren nach Anspruch 12, wobei die Gasphasenabscheidung einen Prozess der plasmaunter-

## DE 10 2008 051 542 A1 2009.05.14

stützten chemischen Abscheidung aus der Dampfphase (PE-CVD) beinhaltet.

- 21. Verfahren nach Anspruch 12, weiterhin umfassend das Aufbringen einer Haftvermittlerschicht über der Isolationsschicht.

- 22. Verfahren nach Anspruch 21, wobei das Aufbringen der Haftvermittlerschicht eine Gasphasenabscheidung von Silan enthält.

- 23. Integriertes Schaltungsbauelement, umfassend:

einen Halbleiterchip;

eine Metallisierungsschicht auf dem Chip; und

auf der Metallisierungsschicht angeordnete Mittel

zum Isolieren der Metallisierungsschicht.

Es folgen 3 Blatt Zeichnungen

# DE 10 2008 051 542 A1 2009.05.14

# Anhängende Zeichnungen

Fig. 1