# (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4709442号 (P4709442)

(45) 発行日 平成23年6月22日(2011.6.22)

(24) 登録日 平成23年3月25日(2011.3.25)

| (51) Int.Cl. | F I                           |                         |

|--------------|-------------------------------|-------------------------|

| GO2F 1/136   | <b>8 (2006.01)</b> GO2F       | 1/1368                  |

| GO9F 9/00    | <b>(2006.01)</b> GO9F         | 9/00 338                |

| GO9F 9/30    | <b>(2006.01)</b> GO9F         | 9/00 3 4 2 Z            |

| GO9F 9/35    | <b>(2006.01)</b> G09F         | 9/30 3 3 8              |

| HO1L 29/786  | <b>(2006.01)</b> GO9F         | 9/35                    |

|              |                               | 請求項の数 3 (全 11 頁) 最終頁に続く |

| (21) 出願番号    | 特願2001-257127 (P2001-257127)  | (73) 特許権者 502356528     |

| (22) 出願日     | 平成13年8月28日 (2001.8.28)        | 株式会社 日立ディスプレイズ          |

| (65) 公開番号    | 特開2003-69030 (P2003-69030A)   | 千葉県茂原市早野3300番地          |

| (43) 公開日     | 平成15年3月7日(2003.3.7)           | (73) 特許権者 506087819     |

| 審査請求日        | 平成17年2月16日 (2005.2.16)        | パナソニック液晶ディスプレイ株式会社      |

| 審判番号         | 不服2008-14620 (P2008-14620/J1) | 兵庫県姫路市飾磨区妻鹿日田町1-6       |

| 審判請求日        | 平成20年6月11日 (2008.6.11)        | (74)代理人 110000154       |

|              |                               | 特許業務法人はるか国際特許事務所        |

|              |                               | (72) 発明者 堀越 和彦          |

|              |                               | 神奈川県横浜市戸塚区吉田町292番地      |

|              |                               | 株式会社日立製作所生産技術研究所内       |

|              |                               | (72)発明者 尾形 潔            |

|              |                               | 神奈川県横浜市戸塚区吉田町292番地      |

|              |                               | 株式会社日立製作所生産技術研究所内       |

|              |                               | 最終頁に続く                  |

(54) 【発明の名称】薄膜トランジスタの製造方法

### (57)【特許請求の範囲】

# 【請求項1】

薄膜トランジスタの製造方法であって、

- (1)無アニールガラス基板の上方に非晶質シリコン層を形成する工程と、

- (2)前記非晶質シリコン層にイオン注入装置を用いて3b族の元素または5b族の元素 を注入する工程と、

- (3)<u>前記3b族の元素または前記5b族の元素が注入された</u>前記非晶質シリコン層にレーザ光を照射して、これを多結晶シリコン層に変える工程と、

- (4) <u>前記無アニールガラス基板の上方に形成され前記3 b 族の元素または前記5 b 族の元素が注入された</u>前記多結晶シリコン層の表面を<u>少なくともオゾンを含有する雰囲気中に</u> <u>て 5 0 0 以下の温度で酸化させることにより</u>、第 1 の絶縁層を 4 ~ 2 0 n m の厚さで形成する工程と、

- (5)前記第1の絶縁層の上に第2の絶縁層を形成する工程と、

- (6)前記第2の絶縁層の上にゲート領域を形成する工程と、

- (7)前記ゲート領域をマスクとして、イオン注入法によりソース領域及びドレイン領域に3b族の元素または5b族の元素を注入する工程と、

- (8)前記ゲート領域を覆うようにして層間絶縁層を形成した後、前記ソース領域、前記 ドレイン領域、及び前記ゲート領域のいずれかに電気的に接続される電極を夫々形成する 工程とを備えたことを特徴とする薄膜トランジスタの製造方法。

#### 【請求項2】

薄膜トランジスタの製造方法であって、

- (1)無アニールガラス基板の上方に非晶質シリコン層を形成する工程と、

- (2)前記非晶質シリコン層にレーザ光を照射して、これを多結晶シリコン層に変える工程と、

- (3)前記多結晶シリコン層にイオン注入装置を用いて3b族の元素または5b族の元素を注入する工程と、

- (4)前記無アニールガラス基板の上方に形成され前記3 bの元素または前記5 b族の元素が注入された前記多結晶シリコン層の表面を少なくともオゾンを含有する雰囲気中にて5 0 0 以下の温度で酸化させることにより、第1の絶縁層を4~20 nmの厚さで形成する工程と、

- (5)前記第1の絶縁層の上に第2の絶縁層を形成する工程と、

- (6)前記第2の絶縁層の上にゲート領域を形成する工程と、

- (7)前記ゲート領域をマスクとして、イオン注入法によりソース領域及びドレイン領域 に3b族の元素または5b族の元素を注入する工程と、

- (8)前記ゲート領域を覆うようにして層間絶縁層を形成した後、前記ソース領域、前記 ドレイン領域、及び前記ゲート領域のいずれかに電気的に接続される電極を夫々形成する 工程とを備えたことを特徴とする薄膜トランジスタの製造方法。

#### 【請求項3】

前記3b族の元素がボロン(B),前記5b族の元素がリン(P)であることを特徴とする請求項1又は請求項2に記載の薄膜トランジスタの製造方法。

【発明の詳細な説明】

[00001]

【発明の属する技術分野】

本発明は液晶表示装置に用いられる薄膜トランジスタ及びその製造方法に関する。

[0002]

【従来の技術】

近年、ノートパソコンや携帯機器等の表示装置として用いられる液晶ディスプレイにおいて、その駆動方式は単純マトリクス方式からアクティブマトリクス方式へと進み、特に、ガラス基板上に多くの薄膜トランジスタ(以下、TFT:Thin Film Transistor)を形成したTFTアクティブマトリクス駆動方式が主流になりつつある。TFT駆動方式の中で、多結晶シリコン層を用いたTFTは非晶質シリコン層の場合と比較して電子移動度が大きいため、表示用画素部のトランジスタとしてばかりでなく、駆動用トランジスタとしてガラス基板上に作り込むことが可能である。

[0003]

従来、多結晶シリコンの形成には1000 程度の高温を必要とするため,基板には高価な石英ガラス基板の使用が必須であった。最近では約600 のプロセス温度で多結晶シリコンを形成できる技術開発が進み、石英基板以外のガラス素材が使用可能となった。この方法では,ガラス基板上に形成されたアモルファスシリコン膜へのレーザ照射等により,基板温度を上昇させることなく、アモルファスシリコン膜のみを加熱し結晶化させることができる。

[0004]

一方、単結晶シリコン基板を用いた集積回路素子においてはシリコンの熱酸化膜(膜厚、数 n m ~ 数 1 0 n m)がゲート絶縁膜として使用されている。しかしながら、このシリコンの熱酸化膜の形成には約 1 0 0 0 の熱処理が必要であって、このプロセスを上記した6 0 0 以下のプロセス温度を必要条件とする多結晶ポリシリコンTFTの製造プロセスには利用できない。

[00005]

TFTの製造プロセスでは、通常、TEOS(Tetraethoxysilane)を原料として、プラズマCVD法等により形成されたSiO $_2$ 膜(膜厚:約100nm)をゲート絶縁膜としている。しかしながら、このプラズマCVD法によるSiO $_2$ 膜は界面

10

20

30

40

準位密度が大きい。従ってその膜をゲート絶縁膜として用いた場合には、しきい値電圧の変動等に見られるようなTFT特性の著しい性能低下をもたらすことになる。更にまた、TFTの耐圧が経時的に激しく劣化をもたらし、その結果としてTFTの絶縁破壊を起こすこともある。従って、TFT用ゲート絶縁膜とシリコン層との界面には、シリコンの熱酸化によって形成させた熱酸化膜に匹敵する界面準位密度の小さな酸化膜の形成が望まれる。

上記した課題に対して、例えば特開平8-195494号公報によれば,通常の高耐熱ガラス基板を用い,600 以下のプロセス温度で多結晶シリコンTFTの製造方法が開示されている。

# [0006]

【発明が解決しようとする課題】

上記した特開平8-195494号公報によれば、多結晶シリコン層の形成は約600 の温度で行われるため、使用可能なガラス基板として事前に熱処理を施した、所謂アニールガラス基板に限定される。従って、アニールガラス基板の代わりに無アニールガラス基板を使用した場合には、約600 という温度条件がガラス基板の収縮を引き起こし、このことがガラス基板の反りや歪を発生させ、最悪の場合にはガラス基板自身の割れや膜剥離等の不都合を齎すことになる。

### [00007]

一般に,ガラスの歪点が高いほど熱的安定性は高くなるが,ガラス基板製造工程において溶融,成形,加工が困難となり,製造コストが高くなる。したがって,コストを抑えるためには歪点が低く,安価なガラスの使用を可能にする製造方法が必須である。

#### [0008]

通常,薄膜トランジスタの基板として用いられる無アルカリガラス基板の歪点は約600であり,歪点よりやや低い温度以上の熱履歴により,ガラスのコンパクション(熱収縮)は急激に大きくなる。例えば,無アニールのコーニング社製のコーニング7059F(歪点593 )は,600 ,1時間,冷却速度1 /分の熱履歴により約800ppmのコンパクションがある。また歪点の高いコーニング1735F(歪点665 )の場合,上記と同様の熱履歴が加わると173ppmのコンパクションを示す。そして、予め660 /1hrのアニール処理を行うことにより,同様の熱履歴によるコンパクションを約10ppmまで低下させることが可能とされている。

### [0009]

多結晶TFTパネル用の基板には,通常20ppm以下の熱収縮率が要求されるため,これまではアニールガラス基板の使用が必須とされてきた。従って、プロセス温度の上限を単純に無アニールガラス基板の収縮が無視できる程度の温度、例えば450~500 に下げた場合、以下に述べる問題が発生する。

#### [0010]

即ち、多結晶シリコン層の上に形成されるゲート絶縁層として、一般的にはTEOSを原料ガスとしてプラズマCVD(Chemical Vapor Deposition) 法等を用いてSiO $_2$  膜を約100nmの厚さで形成する。しかしながら、多結晶シリコン層とTEOSからなる絶縁層との界面においては界面準位密度が大きいため、TFTとしてのしきい値電圧が変動し易く、またゲート絶縁層としての絶縁耐圧特性が経時的に著しく劣化する等、TFTの信頼性において大きな問題が存在する。

従って、無アニールガラス基板の使用を前提とした場合、プロセス温度の上限を450~500 程度とし、かつ多結晶シリコン層とゲート絶縁層との界面準位密度を熱酸化法によるシリコン酸化層に準ずる程度に低減する工夫が重要である。

# [0011]

上記した課題に対して本発明は,無アニールガラス基板を使用してもコンパクションが問題にならないプロセス温度で高信頼度を有する多結晶シリコン薄膜トランジスタを形成することを目的とする。

# [0012]

10

20

30

尚、本発明において,ガラス基板を600 ,1時間の熱処理後,1 /分で冷却した場合、そのコンパクションが30ppm以上であるガラス基板を無アニールガラス基板と定義した。

### [0013]

### 【課題を解決するための手段】

上記した目的を達成するために、本発明では無アニールガラス基板の上方にチャネル領域とソース領域とドレイン領域とを形成するためのポリシリコン結晶層と、第1の絶縁層と第2の絶縁層とを形成する。そして、チャネル領域に対応する位置であって第2の絶縁層の上にゲート領域を、またゲート領域、ソース領域、ドレイン領域の各領域と電気的な接続を行なうためのゲート電極、ソース電極、ドレイン電極とを形成した。

### [0014]

この時、第1の絶縁層が3b族の元素(例えばボロン(B))または5b族の元素(例えばリン(P))がドープされているチャネル領域の多結晶シリコン表面を500以下の温度で酸化させてなるシリコン酸化層であって、少なくともチャネル領域の表面を覆うようにして形成されており、かつその膜厚が4nm以上20nm以下であるようにした。

#### [0015]

また本発明は、少なくともオゾンを含有する雰囲気の中で多結晶シリコン層の表面を酸化 させることにより、第1の絶縁層であるシリコン酸化層を形成するようにした。

そして本発明は、上記した第1の絶縁層の上方に配設された第2の絶縁層が少なくとも化 学堆積法、物理堆積法、またはスピン塗布法を用いて形成した。

#### [0016]

上記したように、オゾン雰囲気中で,3 b 族の元素または5 b 族の元素をドープした多結晶シリコン層の表面を酸化させることによって,従来よりも厚いシリコン酸化層を高速に形成することができる。また多結晶シリコン表面を酸化することにより,多結晶シリコン層とシリコン酸化層との界面を良好な状態に保つことが出来る。しかも、従来より低いプロセス温度でシリコン酸化膜の形成を行なうことが可能であるので、比較的安価な無アニールガラスを基板として使用することが出来る。

換言すれば、上記した方法によって作製された薄膜トランジスタは、シリコン多結晶からなるチャネル領域の表面とその上に形成されたゲート絶縁層との界面が良好であるため、そこでの界面準位密度に密接に関係する薄膜トランジスタの特性、例えばしきい値電圧の変動を低減することが可能になるため、その結果として優れたTFT特性を発揮することが出来る。そして、基板として無アニールガラス基板の使用が可能であるため、石英ガラス等に比較して大きな面積に、しかも安価にTFTを作製することが可能となる。

# [0017]

なお本発明のTFTと類似の構造を持つ公知例として,特開2000-164885号公報にはガラス基板等からのNaイオンの拡散防止を目的に,リンもしくはボロンを含むゲート絶縁層をスパッタリングにより形成した絶縁ゲート型半導体装置,およびその製造方法が開示されている。しかしながら、上記した公報に記載された構成では,ゲート絶縁膜の形成方法として堆積法(スパッタリング)を用いているためにゲート絶縁層/半導体の界面からホットキャリアが注入されやすく経時劣化を引き起こす。

# [0018]

また,特開平10-261801号公報にはガラス基板等からのNaイオンの拡散防止を目的に,ゲート絶縁膜がリンもしくはボロンを含有する酸化シリコン膜からなる薄膜トランジスタ装置が開示されている。しかしながら、上記した公報に記載のゲート絶縁膜は堆積法(CVD)を用いて形成されるため、前述の特開2000-164885号公報の場合と同様にゲート絶縁層/半導体界面のホットキャリアによる劣化が問題となる。

#### [0019]

本発明では,シリコン多結晶からなるチャネル領域の上に形成する絶縁膜を上記した堆積法とは異なる方法、即ち、ポリシリコン膜の表面を酸化することにより $SiO_2$ を形成するため, $SiO_2$ /p-Si界面に不純物等による準位が少なく、かつ経時劣化の小さい

10

20

30

40

薄膜トランジスタを形成することができる。

# [0020]

#### 【発明の実施の形態】

以下、本発明の実施例を、図面を用いて詳細に説明する。

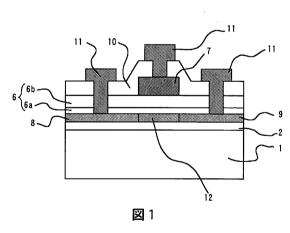

図 1 は第 1 の実施例である薄膜トランジスタの要部断面を表わす構造図である。無アニールガラス基板 1 上に形成された拡散防止層 2 上に、多結晶シリコン層からなるソース領域 8 、ドレイン領域 9 、チャネル領域 1 2 が形成されている。そして、チャネル領域 1 2 上には、3 b 族元素または 5 b 族元素、具体的には例えば 3 b 族元素であるボロン(B)または 5 b 族元素であるリン(P)がドープされた多結晶シリコン層を酸化して形成された S i O  $_2$  層 6 a が形成され、更に堆積法により形成された絶縁層 6 b とからなるゲート絶縁層 6 が配されている。

#### [0021]

ゲート絶縁層6の上部にはチャネル領域12に対応する位置にゲート領域7が形成され、このゲート領域7の表面の一部を覆うようにして層間絶縁層10が形成されている。そして、この層間絶縁層10に設けられた開口部を介してソース領域8、ドレイン領域9及びゲート領域7が各々の電極11によって電気的に接続されている。

#### [0022]

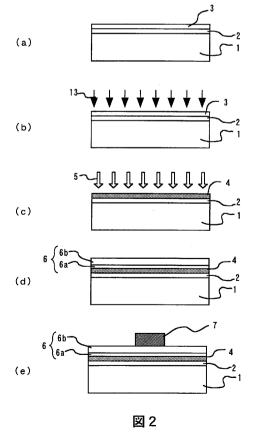

次に、上記の図1に示した構造の製造方法を、図2に示したプロセスフローを用いて説明する。

先ず、無アニールガラス基板 1 上に、通常のプラズマ C V D ( C h e m i c a l V a p o u r D e p o s i t i o n ) 法を用いて S i N 膜または S i O  $_2$  膜からなる拡散防止層 2 ( 膜厚 5 0 ~ 2 0 0 n m ) を形成する。その目的は無アニールガラス基板に含まれる不純物、例えばナトリウムイオンが後述する基板上に形成した薄膜トランジスタに拡散して悪影響を及ぼすことを防止するためである。その後、続けてモノシランまたはジシランを原料とし処理温度 3 0 0 ~ 5 0 0 の条件でプラズマ C V D 法を用いてアモルファスシリコン膜 3 ( 膜厚 5 0 n m ) を形成する ( 図 2 ( a ) )。

#### [0023]

次に、アモルファスシリコン膜3の表面に3b族元素であるボロン(B)イオン13を加速電圧:0.5~100keV、ドーズ量:1E10~1E16/cm²の条件でイオン打ち込みを行う(図2(b))。このイオン打ち込みにより,少なくとも後にチャネルとなるゲート直下の多結晶シリコン層にボロンが打ち込まれる。また,拡散防止層2にもボロン(B)が一部打ち込まれることにより,ガラス基板からナトリウムイオン等が素子中に拡散するのを防止する効果を高めることができる。ボロンを打ち込む際の加速電圧およびドーズ量はTFT特性を低下させずに酸化促進効果を得られる範囲を選択すればよい。このとき、打ち込まれたボロンはアモルファスシリコン膜3の表面から深さ方向に濃度分布を形成する。従って、ボロンのピーク濃度は1E18~1E21/cm³程度が好ましい。この理由は、後の工程でシリコン表面を酸化する際,酸化速度の増速効果を得るのに適当な値だからである。

### [0024]

その後、アモルファスシリコン膜3の表面にエキシマレーザ光5を照射し、アモルファスシリコン膜3の一部または全部を結晶化させて多結晶シリコン層4を形成する(図2(c))。エキシマレーザ光5の照射条件は,例えば300~600mJ/cm²で,パルス光による10~20回の照射を行っている。このとき、エキシマレーザ光5はアモルファスシリコン膜3に吸収され、そして加熱及び結晶化が行なわれるので、このエキシマレーザ光5の照射によって無アニールガラス基板1全体が500 以上に加熱されることはない。図2(c)では便宜上、ガラス基板1の全面にレーザ光が照射されているかのごとく図示しているが、実際には短冊状に集光させたエキシマレーザ光5を走査させるようにして照射されている。

# [0025]

40

30

10

20

# [0026]

そして、ゲート絶縁層6上に通常良く知られた方法を用いてゲート領域7を形成し、所望の形状に加工する(図2(e))。ゲート領域の材料としては、不純物ドープシリコン膜、金属、金属化合物(TiN、TiW等)等の導電性の材料を用いる。

[0027]

次に、加工されたゲート領域 7 をマスクとして、多結晶シリコン層 4 に 5 b 族元素であるリン(P)イオンの打ち込みを行い、ソース領域 8 、ドレイン領域 9 を形成した。多結晶シリコン層 4 にリンイオンを打ち込むときの条件は,加速電圧  $1 \sim 100$  keV,ドーズ量:  $1 \in 10 \sim 1 \in 16$  / cm² である。その後、打ち込んだリンイオンを活性化させるため、多結晶シリコン層 4 の R T A (Rapid Thermal Annealing)処理を行った。このときの条件は  $1 \sim 50$  kW / cm² ,  $1 \sim 5$  s である。尚、この R T A 処理においても多結晶シリコン層 4 のみが加熱されるため、下地の無アニールガラス基板全体の温度が少なくとも 550 以上に上昇することはない。

[0028]

次に、図 2 ( e )に示すゲート領域 7 の表面を覆うようにしてゲート絶縁膜 6 の上に、 T E O S を原料とし処理温度 3 0 0 ~ 5 0 0 でプラズマ C V D 法により形成した S i O  $_2$  からなる層間絶縁層 1 0 を通常の方法を用いて形成した。そして、この層間絶縁層 1 0 の所定の位置にゲート領域 7 、ソース領域 8 、ドレイン領域 9 と電気的接続を行うための開口部を形成し、この開口部を介してゲート領域 7 、ソース領域 8 、ドレイン領域 9 と接続した各電極 1 1 を形成し、図 1 に示した薄膜トランジスタが完成する。

[0029]

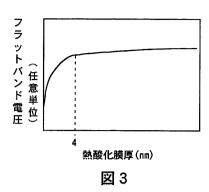

ところで、図2(d)に示した第1の絶縁膜の膜厚について説明する。図3は熱酸化膜/TEOSの2層ゲート絶縁膜構造であるMOSトランジスタにおける熱酸化膜(第1の絶縁膜)の膜厚とフラットバンド電圧との関係を示したものである。この図から明らかなように,熱酸化膜厚が4nm未満の場合にはMOSトランジスタにおけるフラットバンド電圧が低下してしまう。この現象は、熱酸化膜と下地膜であるシリコン層との界面における界面準位密度が大きく、この界面準位に電子が捕獲されることによって所望のトランジスタ特性を発揮させることが不可能になるためである。一方、熱酸化膜厚が4nm以上であればフラットバンド電圧はほぼ一定値を示し、所望のトランジスタ特性を確保することが可能になる。

[0030]

尚、熱酸化膜厚の上限は敢えて規定する必要はないが、ゲート絶縁膜を熱酸化膜 / TEOSなる 2 層構造とする場合には必要以上に厚くする必要はない。即ち、薄膜トランジスタの生産性を考慮すれば、熱酸化という方法は酸化膜の形成速度が小さい方法であることを考えて、その膜厚の上限として例えば 2 0 n m 程度が適当である。

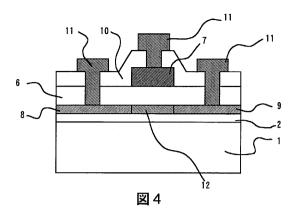

[0031]

次に、第2の実施例について図4を用いて説明する。ボロン(B)イオンを打ち込んだアモルファスシリコン膜3をエキシマレーザ光5により結晶化する工程までは先の第1の実施例と同様である(図2(c))。

次に、ボロン(B)がドープされた多結晶シリコン層4の表面を酸化させて,4nm以上のシリコン酸化層を形成する。そして、このシリコン酸化層をゲート絶縁層6として機能させる。その後、ゲート領域7を形成する工程以降の工程は先に示した実施例1の場合と同様である。上記した工程を経て、図4に示すゲート絶縁層6が1層の構造である薄膜ト

10

20

30

40

ランジスタが完成する。

# [0032]

第2の実施例において、ゲート絶縁層6を1層の構造とし,その膜厚を例えば20nm程度にすることによって、第1の実施例に比較して低電圧で薄膜トランジスタを安定に動作させることが可能になる。

# [0033]

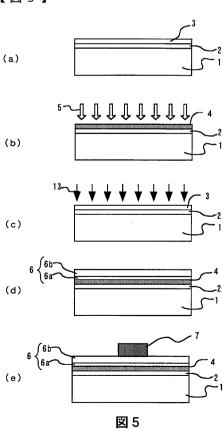

次に、第3の実施例について図5を用いて説明する。

図 5 は薄膜トランジスタの形成プロセスフローである。ガラス基板 1 の上にアモルファスシリコン膜 3 を形成する工程までは先に示した第 1 の実施例の場合と同様である(図 5 (a))。

# [0034]

次に、アモルファスシリコン膜3にエキシマレーザ光5を照射して結晶化処理を行い,多結晶シリコン膜4を形成する(図5(b))。その後、多結晶シリコン膜4に加速電圧:0.5~100keV、ドーズ量:1E10~1E16/cm²の条件で3b族元素であるボロン(B)イオン13を打ち込む(図5(c))。このイオン打ち込みにより,少なくとも後にチャネルとなるゲート直下の多結晶シリコン層にボロンが打ち込まれる。また,拡散防止層2にもボロン(B)が一部打ち込まれることにより,ガラス基板からナトリウムイオン等が素子中に拡散するのを防止する効果を高めることができる。

### [0035]

次に、ボロン(B)イオンの打ち込まれた多結晶シリコン膜4の上に第1の絶縁層6a及び第2の絶縁層6bを形成する(図5(d))。このとき、先の第1の実施例では,アモルファスシリコンにボロン(B)イオン打ち込みを行った後にエキシマレーザ光5により結晶化を行ったが,本実施例に示すようにエキシマレーザ光5による結晶化の工程とボロン(B)イオン打ち込みの工程とを行なう順番を逆にしても、多結晶シリコン膜4上に形成される酸化膜(第1の絶縁層6a)の形成速度が低下することはない。

### [0036]

次に、ゲート絶縁膜 6 上にチャネル領域12に対応させた位置にゲート領域7を形成し(図5(e))、層間絶縁膜10及び電極11を形成して図1に示した場合と同様の薄膜トランジスタが完成する。

# [0037]

上記した実施例では,第2の絶縁層シリコン酸化膜の形成方法は第1の実施例同様にCVD法を用いたが、スパッタ等の物理堆積法、スピン塗布法等を用いて形成しても同様の効果が得られる。

# [0038]

ところで、上記した第1の実施例あるいは第3の実施例では、NチャネルMOS型の薄膜トランジスタを構成するが、ソース領域8、ドレイン領域9に打ち込むイオンの種類を適宜選択することによりPチャネルMOS型薄膜トランジスタを形成することも可能である。また、これらのイオン打ち込みを使い分けることにより,同一基板上にNチャネルMOS型とPチャネルMOS型とを作り込んだC-MOS型薄膜トランジスタを形成することも可能である。

# [0039]

次に、多結晶シリコン層4の表面を酸化して得られるシリコン酸化層6aの形成方法について、以下に詳しく説明する。

無アニールガラス基板 1 の上に多結晶シリコン層 4 が形成されたサンプルを第 1 の処理室に搬入し、無アニールガラス基板 1 に対して熱的な悪影響を及ぼさない程度の温度、例えば約 4 5 0 で加熱する。一方、第 1 の処理室とは隔離されて隣接する第 2 の処理室に、 1 0 0 g / N m  $^3$  のオゾン(約 1 S L M / c m  $^2$  : オゾンの全流量を有効処理面積で除した値)を導入し、第 2 の処理室内を約 7 0 0 T o r r に制御する。オゾンは純酸素ガス( 1 0 S L M )と微量の N  $_2$  ガス( 5 5 S C C M )との混合ガスを原料とし、良く知られた無声放電型オゾナイザを用いて 1 0 0 g / N m  $^3$  (オゾン濃度約 5 % ) のオゾンを生成し

10

20

30

40

た。

# [0040]

上記のオゾン雰囲気にある第 2 の処理室に、第 1 の処理室から 4 5 0 に加熱されたサンプルを搬入する。このような処理を行なうことによって多結晶シリコン層 4 の表面が酸化される。第 2 の処理室における処理時間を例えば 1 0 分とすれば、多結晶シリコン層 4 の表面に約 4 n m の膜厚を有する第 1 の絶縁層 6 a、即ち S i O  $_2$  層が形成される。ここで多結晶シリコン層 4 にはボロン(B)イオンが注入されているため、ボロン(B)イオンが注入されていない場合(従来方法)に比較して酸化速度が大きく、結果的には膜厚の厚い S i O  $_2$  層を形成することができる。

# [0041]

次に、シリコン層の酸化メカニズムについて簡単に説明する。

シリコンの表面が酸化種の雰囲気に晒されたとき、先ずこの酸化種がシリコンの表面に吸着し、酸化反応が開始される。また、シリコンの表面にシリコン酸化膜を有する場合には、シリコン酸化膜の表面に吸着した酸化種がシリコン酸化膜中を拡散する。そして、酸化種の拡散が進行してシリコン酸化膜/シリコンの界面に到達すると、そこでシリコンと酸化種との反応が起こり、シリコン酸化膜が成長する。

### [0042]

従来、シリコンの酸化は,800 以上の高温プロセスを必要としていたが,オゾンガスを用いることにより酸化膜形成温度の低温化が可能となる。さらに多結晶シリコンにボロン(B)やリン(P)等の不純物がドープされていると,これらの不純物がドープされていない場合よりも酸化膜形成速度が大きくなる。

#### [0043]

この理由は次のようなメカニズムによる。

多結晶シリコン層にリン( P )がドープされている場合の酸化メカニズムは、単結晶シリコンで広く用いられているリニア・パラボリック近似でモデル化できる。

即ち、酸化膜厚 d と時間 t の間には、 d  $^2$  + A ・ d = B / ( t + ) なる関係式が成り立つ。ここで、 、 A 、 B は定数である。

# [0044]

リンをドープしたシリコンの酸化ではリンがシリコン側に偏析し、シリコン領域に酸化種とSiの反応サイトとなる空孔濃度を高めるため酸化速度が増大する。言い換えれば、シリコン側へのリンの偏析によりSi/SiO₂界面での反応速度が大きくなり、線形定数 B/Aが最も顕著に影響を受けて大きくなる。さらに多結晶シリコンではリンは粒界に偏析するため、粒界を介してより酸化膜形成速度は大きくなる。

### [0045]

一方、多結晶シリコン中にボロン(B)イオンをドープした場合には,ボロンはSiO<sub>2</sub>側に偏析し,SiO<sub>2</sub>の結合構造を弱める。従って、弱められた構造を有する酸化膜中では酸化種の拡散が促進されて、その結果として酸化速度が増大する。即ち、ボロンイオンをドープしたシリコン層では前述の関係式における定数Bの値が増大することになる。

# [0046]

多結晶シリコン層 4 の表面を酸化して形成した第 1 の絶縁層 6 a(SiO  $_2$  層)上に形成した第 2 の絶縁層 6 b は、例えば C V D 法、 P V D 法、またはスピン塗布法により形成する。 C V D 法の場合、 T E O S を原料ガスとして熱分解反応を利用する方法、またモノシランやジシランを原料ガスとして熱分解を利用する方法等がある。また、 P V D 法の場合、 スパッタ法、蒸着法等がある。例えば S i O  $_2$  ターゲットを用い、 A r / O  $_2$  混合ガス中で R F スパッタを行うことによって、緻密な S i O  $_2$  膜が得られる。また、スピン塗布法では、 S O G (S p i n O n G l a s s ) 法等がある。

以上述べた方法によって、ゲート絶縁層6が完成する。

#### [0047]

以上に述べたプロセスを用いて、無アニールガラス基板上に500 以下なる低温で形成されたTFTは、多結晶シリコン層なるチャネル領域の上に約4nm以上のゲート絶縁膜

10

20

30

40

10

20

を有し、その絶縁膜として多結晶シリコン層を酸化させて形成させた $SiO_2$ 層を用いることによって、その界面準位密度を下げることが出来る。そして、その結果としてTFTの重要な特性のひとつであるしきい電圧Vthの経時的変動を小さく抑えることが可能であることを確認した。

# [0048]

# 【発明の効果】

以上で説明したように、オゾン酸化を利用した多結晶シリコン膜の表面処理を用いることにより、安価な無アニールガラス基板上に液晶表示用の薄膜トランジスタを形成することが出来る。

# 【図面の簡単な説明】

【図1】第1の実施例である薄膜トランジスタを説明するための概略断面図である。

【図2】第1の実施例である薄膜トランジスタの製造方法を説明するための工程図である

【図3】熱酸化膜厚とフラットバンド電圧との関係を表す説明図である。

【図4】第2の実施例である薄膜トランジスタを説明するための概略断面図である。

【図5】第3の実施例である薄膜トランジスタの製造方法を説明するための工程図である

# 【符号の説明】

1 …無アニールガラス基板、2 …拡散防止層、3 …アモルファスシリコン層、4 …多結晶シリコン層、5 …エキシマレーザ光、6 a …第1の絶縁層、6 b …第2の絶縁層、7 …ゲート領域、8 …ソース領域、9 …ドレイン領域、10 …層間絶縁層、11 …電極、12 …チャネル領域、13 …加速されたボロン(B)イオン

【図1】

【図2】

【図3】

【図4】

【図5】

### フロントページの続き

(51) Int.CI. F I

H 0 1 L 21/336 (2006.01)

H 0 1 L 29/78 6 1 7 T

H 0 1 L 29/78 6 1 7 U

H 0 1 L 29/78 6 1 7 V

H 0 1 L 29/78 6 2 6 C

H 0 1 L 29/78 6 2 7 G

(72)発明者 田村 太久夫

神奈川県横浜市戸塚区吉田町292番地 株式会社日立製作所生産技術研究所内

(72)発明者 中原 美和子

神奈川県横浜市戸塚区吉田町292番地 株式会社日立製作所生産技術研究所内

(72) 発明者 大倉 理

千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内

(72)発明者 折付 良二

千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内

(72)発明者 中野 泰

千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内

(72)発明者 芝 健夫

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

合議体

審判長 相田 義明

審判官 近藤 幸浩

審判官 松田 成正

(56)参考文献 特開平10-079516号公報

特開平04-177765号公報

特開平11-097691号公報

特開平04-326731号公報

特開平08-195494号公報

(58)調査した分野(Int.CI., DB名)

H01L21/336

H01L29/786