## (19) **日本国特許庁(JP)**

# (12)公開特許公報(A)

(11)特許出願公開番号

特開2008-5327 (P2008-5327A)

(43) 公開日 平成20年1月10日(2008.1.10)

| (51) Int.C1. |       |           | FΙ   |       |     | テーマコード (参考) |

|--------------|-------|-----------|------|-------|-----|-------------|

| H04J         | 3/00  | (2006.01) | HO4J | 3/00  | M   | 5C164       |

| HO4N         | 7/173 | (2006.01) | HO4N | 7/173 | 630 | 5KO28       |

| H04B         | 1/16  | (2006.01) | HO4B | 1/16  | Z   | 5KO61       |

審査譜求 未譜求 譜求項の数 6 〇 L. (全 11 百)

|           |                              | 田旦明小     | 不明不 明不填の数 0 0 0 (主 11 貝) |

|-----------|------------------------------|----------|--------------------------|

| (21) 出願番号 | 特願2006-174238 (P2006-174238) | (71) 出願人 | 000003078                |

| (22) 出願日  | 平成18年6月23日 (2006.6.23)       |          | 株式会社東芝                   |

|           |                              |          | 東京都港区芝浦一丁目1番1号           |

|           |                              | (74) 代理人 | 100058479                |

|           |                              |          | 弁理士 鈴江 武彦                |

|           |                              | (74) 代理人 | 100091351                |

|           |                              |          | 弁理士 河野 哲                 |

|           |                              | (74) 代理人 | 100088683                |

|           |                              |          | 弁理士 中村 誠                 |

|           |                              | (74)代理人  | 100108855                |

|           |                              |          | 弁理士 蔵田 昌俊                |

|           |                              | (74)代理人  | 100075672                |

|           |                              |          | 弁理士 峰 隆司                 |

|           |                              | (74) 代理人 | 100109830                |

|           |                              |          | 弁理士 福原 淑弘                |

|           |                              |          |                          |

|           |                              |          | 最終頁に続く                   |

#### (54) 【発明の名称】デジタル放送受信装置を搭載する情報処理装置

## (57)【要約】

【課題】デジタル放送受信装置は、TSパケットが途中で受信された場合にはエラーとして検出され、復号処理等を行う処理装置(CPU)によりエラー検出処理が行われ、CPUに負担させる処理量が大きく、その負荷の軽減を図ることが望まれている。

【解決手段】パケットデータで送信されるデジタル情報をデジタルチューナ部12で受信し、順次受信したパケットデータにおける瑕疵を有するパケットデータを同期バイトの間隔、同期バイトの値又は誤り表示の値からエラーを検出する同期バイト間隔検出回路21、同期バイト比較回路23、誤り表示比較回路24の少なくとも1つを有するエラー検出回路20を備え、瑕疵を有するパケットデータを排除したパケットデータから情報を再生するデジタル放送受信装置を搭載する情報処理装置である。

【選択図】 図3

⊠ 3

#### 【特許請求の範囲】

#### 【請求項1】

データ、音声及び画像からなる情報がパケットデータで送信されるデジタル放送を受信 するデジタルチューナ部と、

デジタルチューナ部から出力されるパケットデータにおける瑕疵を有するパケットデータを検出するエラー検出回路を有し、前記エラー検出回路によりエラー検出された瑕疵を有するパケットデータを排除したパケットデータをバスに送出する制御部と、

前記チューナ部から前記バスに出力された、瑕疵を有するパケットデータを排除したパケットデータから前記情報を再生する情報処理部と、

を具備することを特徴とする情報処理装置。

#### 【請求項2】

前記制御部は、

前記デジタルチューナ部から出力される暗号化されたパケットデータを暗号解除化するための暗号解除処理部と、

前記エラー検出回路により瑕疵を有するパケットデータを排除したパケットデータを再度、暗号化して前記バスに送出する暗号化処理部と、

を、さらに備えることを特徴とする請求項1に記載の情報処理装置。

#### 【請求項3】

前記エラー検出回路は、前記パケットデータのヘッダに設けられるパケット同期バイトの間隔を検出し、予め定めた間隔よりも短い前記パケットデータをエラーとして検出する同期バイト間隔検出回路を備えることを特徴とする請求項1に記載の情報処理装置。

#### 【請求項4】

前記エラー検出回路は、前記パケットデータのヘッダに設けられるパケット同期バイトの値を予め定めた基準値と比較し、同一でなかった際にエラーとして検出する同期バイト 比較回路を備えることを特徴とする請求項1に記載の情報処理装置。

#### 【請求項5】

前記エラー検出回路は、前記パケットデータのヘッダに設けられるパケット誤り表示の値を予め定めた基準値と比較し、同一でなかった際にエラーとして検出する誤り表示比較回路を備えることを特徴とする請求項1に記載の情報処理装置。

#### 【請求項6】

前記データ、音声及び画像からなる情報が、MPEG2のトランスポートストリームのデータ構造を有することを特徴とする請求項1乃至5のいずれか一項に記載の情報処理装置。

【発明の詳細な説明】

### 【技術分野】

#### [0001]

本発明は、デジタル放送やデジタル通信で用いられるパケットを受信するデジタル放送 受信装置を搭載する情報処理装置に関する。

### 【背景技術】

#### [0002]

近年、放送が開始された地上デジタル放送を始めとして、画質の向上や情報量の増大を図るためにアナログ放送からデジタル放送への切替が行われている。そのデジタル放送としては、例えば、OFDM方式が用いられている。このOFDM方式は、階層化伝送と狭帯域放送による連結送信に特徴があり、データ、音声及び画像といった異なる情報を、それぞれ3階層のTS(Transport Stream)に割り当て、これを多重化して1つのTSパケットとして送受信している。このようなTSパケットを用いた送信においては、例えば伝送路に障害が発生した場合には、特定の階層のTSが情報として利用できない事態が発生する。これを防止するため、実際にはデータが無い空データからなるヌルパケットを挿入して、受信装置における出力クロックを一定に保っている。このヌルパケットは、元々データが無いため、復号を行っても無駄な処理となっている。

20

10

30

#### [0003]

これに対して、特許文献1には、ヌルパケットを出力させないことで処理量を減少させて、装置の省電力化と記録データの削減を実現する技術が提案されている。つまり、誤り訂正部の後段に、出力指示部と階層選択部を配置するように構成する。階層選択部では、TSパケットに多重化された複数のTSのうち、出力指示部から出力の有効が支持された階層のTSパケットのみが選択され、後段の回路に出力される。これにより、後段の回路ではヌルパケットに対して無駄な処理を行うことがなく、またヌルパケットを含むTSパケットを記憶する必要がない。

【特許文献1】特開2003-273824

【発明の開示】

【発明が解決しようとする課題】

[0004]

前述したようなデジタル放送を受信するデジタル放送受信装置は、チャンネル切り換え操作により、例えば、204byteのTSパケットが途中で受信された場合には、エラーとして検出される。しかし特許文献1で開示されたものを含め従来の装置構成では、デジタルチューナ部が出力したエラーのTSパケットは、一旦メインメモリに書き込んでいる。このため、処理装置(CPU)によるテレビ再生プログラム処理は、MPEG2・TSの復号処理、分離処理及びデコード処理に加えて、TSパケットのエラー検出処理も実施するため、CPUが負担する処理量が大きくなっている。従って、CPUに対してより高性能な処理能力を有するCPUが要求されることとなる。

[00005]

特に近年は、従来からの専用のテレビジョン受信装置だけではなく、デジタル放送受信装置が1つの機能ユニットとしてパーソナルコンピュータや携帯情報端末(PDA)等の情報処理装置に搭載されるため、CPUに対する処理負担が大きくなると、他の処理性能に対して影響を与えるため、CPUに対する負荷の軽減を図ることが望まれている。

[0006]

そこで本発明は、制御部における処理負荷を軽減させるデジタル放送受信装置を搭載する情報処理装置を提供することを目的とする。

【課題を解決するための手段】

[0007]

上記目的を達成するために、本発明は、データ、音声及び画像からなる情報がパケットデータで送信されるデジタル放送を受信するデジタルチューナ部と、デジタルチューナ部から出力されるパケットデータにおける瑕疵を有するパケットデータを検出するエラー検出回路を有し、前記エラー検出回路によりエラー検出された瑕疵を有するパケットデータを排除したパケットデータをがスに送出する制御部と、前記チューナ部から前記バスに出力された、瑕疵を有するパケットデータを排除したパケットデータから前記情報を再生する情報処理部とを備える情報処理装置を提供する。

【発明の効果】

[0008]

本発明によれば、制御部における処理負荷を軽減させるデジタル放送受信装置を搭載する情報処理装置を提供することができる。

[0009]

デジタル放送受信装置にMPEG2-TSパケットのエラー検出回路を設けることにより、CPUによりテレビ再生プログラムが実行していたMPEG2-TSパケットエラー検出処理を省略または簡易化して、CPUに対する情報処理量及びメモリ使用量を軽減し、記録データサイズをさらに小さくすることができる。

【発明を実施するための最良の形態】

[0010]

以下、図面を参照して本発明の実施形態について詳細に説明する。

図1は、本発明の一実施形態に係るデジタル放送受信装置内蔵型情報処理装置(以下、

20

10

30

50

20

30

40

50

情報処理装置と称する)の概略的な構成を示すブロック図である。

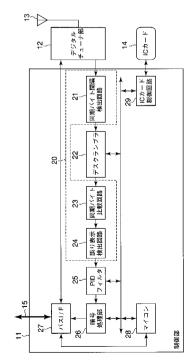

### [0011]

この情報処理装置100は、デジタル放送の受信に対応したPCに搭載され、CPU(中央処理ユニット)1と、ホストコントローラ2と、メインメモリ3と、表示コントローラ4と、表示用メモリ5と、I/O(入出力)コントローラ6と、記憶装置7と、オーディオコントローラ8と、コンテンツ保護機能を有する制御部11と、デジタルチューナ部12等を備える。尚、図1に示す構成部位については、本実施形態の要旨に係わる構成部位のみを代表的に示した構成であり、一般的な情報処理装置に設けられている入力装置(例えば、キーボードなど)等の構成部位は備えているものとして、その図示を省略している。

[0012]

これらの構成において、 C P U 1 は情報処理装置 1 0 0 の全体を制御するために設けられたプロセッサであり、記憶装置 7 からメインメモリ 3 にロードされる O S (オペレーティングシステム)、各種プログラムに基づき、種々の情報処理や演算を実行する。本実施形態においては、プログラムの 1 つとして予めインストールされている、受信した放送データを再生するテレビ再生プログラムによる処理動作が行われる。

[ 0 0 1 3 ]

ホストコントローラ 2 は、 C P U 1 のローカルバスと I / O コントローラ 6 を信号(情報)をやり取りするためのブリッジとして機能する。ホストコントローラ 2 にはメインメモリ 3 のアクセスを制御するメモリコントローラが内蔵されている。また、表示コントローラ 4 は、表示装置 9 における表示動作を制御する。表示コントローラ 4 には、表示用メモリ 5 が接続されており、 O S やプログラムに従って表示用メモリから読み出された画像データが表示装置 9 に表示される。また、テレビ再生プログラムの制御に従って、画像データの書き込みも実行される。

[0014]

I/Oコントローラ6は記憶装置7を制御するためのコントローラが内蔵されている。また、I/Oコントローラ6はバス15により接続されている各デバイスの制御も行う。オーディオコントローラ8は、OSやプログラムから送られてきたオーディオデータ(PCM等)を電気信号に変換して、スピーカ10を駆動させて音声が再生される。

[ 0 0 1 5 ]

デジタルチューナ部12は、デジタル放送のテレビ番組等の放送データを受信するためのデバイスであり、テレビ再生プログラムからのコマンドによって指定されたチャンネル番号の放送データを受信する。デジタルチューナ部12には、テレビアンテナ13が接続されている。デジタルチューナ部12は、テレビアンテナ13で受信した放送データを復調し、例えば、MPEG2-TS形式のトランスポートパケット(以下、TSパケット)を生成する。

[0016]

制御部11は、デジタルチューナ部12から出力されたTSパケットを入力し、ICカード14から読み出した鍵情報を用いてTSパケットの復号処理し、不要なTSパケットのフィルタリング処理を行った後、再度暗号化処理を行い、メインメモリ3に書き込む。この時、制御部11は、後述するエラー検出回路20を用いて、エラーを持つ瑕疵あるパケット(データ)を検出して排除した後、適正なデータのみを再度暗号化して、バス15を通じて情報処理部のメインメモリ3に送出している。ここでは、情報処理部は、CPU1、ホストコントローラ2、メインメモリ3、I/O(入出力)コントローラ6及び記憶装置7等を示唆する。さらに、主として制御部11、デジタルチューナ部12及びテレビアンテナ13によりデジタル放送受信装置が構成される。また、表示コントローラ4、表示用メモリ5、オーディオコントローラ8、表示装置9及びスピーカー10は、出力駆動部と称する。

[0017]

また、テレビ再生プログラムは、メインメモリ3に書き込まれた暗号化されたTSパケ

ットを復号し、画像/音声/データ放送等の付加情報に分離する。画像であれば分離した 画像データをデコードして表示用画像データを生成し表示用メモリ 5 へ書き込む。音声で あれば分離した音声データをデコードして再生用音声データを生成し、オーディオコント ローラ 8 に送る。データ放送のデータであればデータを解析し表示用データを生成し、表 示用メモリ 5 に書き込む。

[ 0 0 1 8 ]

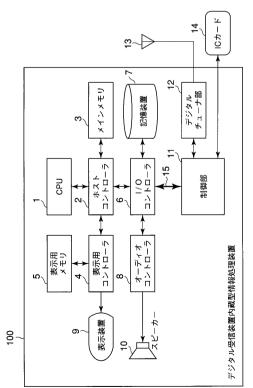

本実施形態のデジタル放送受信装置は、PC等の情報装置に実装されているCPUを用いてMPEG2-TSの処理をソフトウェアで実行している。ここで、MPEG2-TSについて簡単に説明する。

[0019]

図2には、MPEG2-TSのパケットとストリームの構造を示す。

TSパケットは、188バイト固定長のデータであり、先頭4バイト(32ビット)がTSパケットヘッダ、残りの184バイトがペイロード及びアダプテーションフィールドである。TSパケットヘッダは、パケットの先頭を示す同期バイト(8bit、データは0×47)、パケット中のビットエラーの有無を示す誤り表示(1ビット)、パケットの識別情報であるPID(PacketID、13bit)等からなる公知な構成である。さらに、デジタル放送ではTSパケットの後ろに続く16バイトの誤り訂正用データ(\*で図示)が付加されるため、計204バイト(188バイト+16バイト)を1つのパケットとして処理する。

[0020]

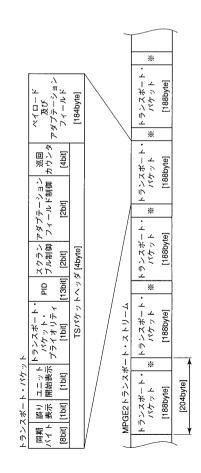

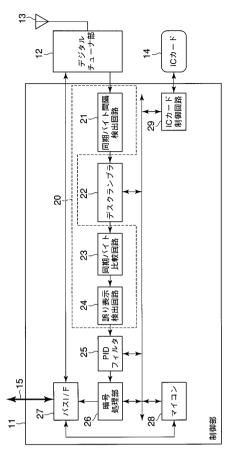

次に図3は、本実施形態の制御部11の具体的な構成を示すブロック図である。

[0021]

この制御部11は、TSパケットのエラー検出回路20と、暗号化されたTSパケットの復号処理を行うデスクランブラ(暗号解除処理部)22と、パケットの識別情報による認定を行うためのPIDフィルタ25と、暗号処理部26、バスI/F27、情報処理及び各構成部位の制御を行うマイコン28と、ユーザが所有するICカードによる認証を行うためのICカード制御回路29を備えている。TSパケットのエラー検出回路20は、後述する同期バイト間隔検出回路21、同期バイト比較回路23及び、誤り表示比較回路24で構成される。このエラー検出回路20は、第1に、同期バイト間隔検出回路21を用いてMPEG2・TSパケットにおける同期バイトの間隔から予め定めた間隔でなかったパケットに対してエラーを検出する。第2に、同期バイト比較回路23を用いてMPEG2・TSパケットにおける誤り表示の値からエラー検出する

[ 0 0 2 2 ]

PIDフィルタ25は、入力したTSパケット内のPIDの比較処理を行い、不要なTSパケットのフィルタリング処理を行う。デジタルチューナ部12から出力されるクロック信号に基づき動作し、誤り表示比較回路24から出力されたデータ4(DATA4)とバリッド信号VALID4を入力し、データ5(DATA5)とバリッド信号VALID5を出力する。出力されたデータ5は、フィルタリング処理されたTSパケットである。バリッド信号VALID5は、データ5が有効なデータならば"1"を出力し、無効なデータならば"0"を出力する。PIDの設定はマイコン28で行い、例えば0×1FFF(ヌルパケット又は、処理上不要なパケット)が設定されている。

[ 0 0 2 3 ]

暗号処理部26はPIDフィルタ25から出力されたデータ5とバリッド信号VALID5を入力し、データ6(DATA6)とバリッド信号VALID6を出力する。暗号処理部26の動作条件は、マイコン28で設定される。ここで、データ6は暗号処理を行ったTSパケットである。出力信号VALID6はDATA6が有効なデータならば"1"を、無効なデータならば"0"を出力する。

[0024]

50

40

10

20

20

30

40

50

バスI/F27は、暗号処理部から出力されたデータ6をバスI/Fに出力する制御を行う回路である。データ6をバスI/Fに適合するタイミングに変換してバス15にデータを出力する。出力したデータはメインメモリ3に書き込まれる。他に、番組再生プログラムから送られたチャンネル設定コマンドをデジタルチューナ部12に送る処理や、マイコン28の動作設定も行う。

[0025]

マイコン 2 8 は、ICカード 1 4 からの鍵データの処理やデスクランブラ 2 2、PIDフィルタ 2 5、暗号処理部 2 6 の動作設定を行う。またICカード制御回路 2 9 は、マイコン 2 8 から送信されたICカード制御コマンドをICカードに送信する処理と、ICカードから受信したデータをマイコン 2 8 に送信する処理を行う。

[0026]

制御部11にTSパケットのエラー検出回路20を設けることで、従来テレビ再生プログラムが行っていたTSパケットエラー検出処理を省略または簡易化しCPU1が行う処理量の削減が可能となる。また処理上不要な(処理できない)TSパケットの出力を抑制することでメモリ使用量や記録データサイズの削減も可能となる。

[0027]

図 4 に示すタイミングチャートを参照して、コンテンツ保護制御部内部の動作タイミングについて説明する。

[0028]

クロック信号(CLOCK)は、デジタルチューナ部12から出力されている動作タイミングの基準となるクロック信号であり、制御部11の動作タイミングの基準となっている。バリッド信号VALIDは、データ(DATA)が有効である場合に"1"、無効である場合に"0"を示す制御信号であり、クロック信号の立ち上がりに同期して、デジタルチューナ部12から出力されている。

[0029]

データはTSパケットであり、クロック信号の立ち上がりに同期してデジタルチューナ部12から出力されている。デジタルチューナ部12が正常なTSパケットを出力している場合、TSパケットのデータ先頭は、同期バイト(0×47)であり、次の同期バイト(0×47)は204サイクル目以降に出力される。但し、データにより、正確に204サイクル目に出力される場合もあれば、それ以降のサイクル数の場合もある。

[0030]

ここで、デジタルチューナ部12が異常なTSパケットを出力している場合、TSパケットのデータ先頭は、同期バイト(0×47)ではない値を示したり、次の同期バイトが204サイクル以前に出力されたり、又はTSパケットヘッダの誤り表示の値が"1"を示す(出力しているTSパケット内にエラーがあることを示す)というような状態になる

[0031]

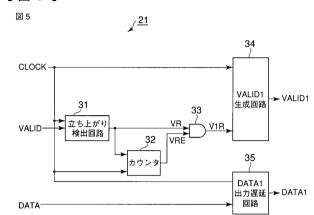

次に、図5には、同期バイト間隔検出回路21の回路図を示す。

この同期バイト間隔検出回路 2 1 は、クロック信号及び入力信号であるバリッド信号の立ち上がりを検出する立ち上がり検出回路 3 1、クロック信号及び立ち上がり検出回路 3 1 の出力により動作するカウンタ 3 2、後述する V R 信号及びカウンタ出力の積(A N D )をとる A N D 回路 3 3、バリッド信号 1 を生成する V A L I D 1 生成回路 3 4 及び、 D A T A 1 出力遅延回路 3 5 で構成される。

[0032]

同期バイト間隔検出回路 2 1 は、デジタルチューナ部 1 2 から出力されているクロック信号に基づき動作して、デジタルチューナ部 1 2 から出力されたデータ及びバリッド信号を入力し、データ 1 とバリッド信号 V A L I D 1 を出力する。立ち上がり検出回路 3 1 は、入力したバリッド信号の立ち上がりを検出する回路である。 V R 信号はバリッド信号の立ち上がりを検出した場合に 1 サイクルだけ " 1 "を出力し、それ以外は " 0 "を出力する。

30

50

[0033]

カウンタ3 2 は、TSパケットの同期バイトの間隔を検出するために用いられる。VR信号の立ち上がりを検出することでカウントを開始し、203までカウントするとカウント値を"0"にクリアし動作を停止する。また、カウンタは、動作中であれば"0"、停止中であれば"1"のVRE信号を出力する。VALID1生成回路34は、出力されたバリッド信号VALID1の制御回路である。VALID1生成回路34から出力されたバリッド信号VALID1は、V1R信号の立ち上がりを検出した際に"1"を出力する

[0034]

本実施形態においては、バリッド信号VALIDの1サイクル後にバリッド信号VALID1が出力される。V1R信号は、立ち上がり検出回路31が出力したVR信号とカウンタ33が出力したVRE信号の積(AND)を取った信号である。V1R信号は、カウンタ32が動作中の場合は"0"、カウンタ停止中の場合は、VR値を出力する。

[0035]

DATA1出力遅延回路35は、出力されたデータ1の出力タイミングをバリッド信号 VALID1と同期させる回路である。本実施形態の回路では、データ信号の1サイクル 後にデータ1が出力される。

[0036]

次に、デスクランブラ 2 2 は、ICカード 1 4 からの鍵情報を用いて暗号化されたTSパケットの復号処理(暗号解除処理)を行う。デジタルチューナ部 1 2 から出力されているクロック信号に基づき動作し、同期バイト間隔検出回路 2 1 から出力されたデータ 1 とバリッド信号 V A L I D 1 を入力する。データ 2 ( D A T A 2 ) は復号処理を行ったTSパケットである。バリッド信号 V A L I D 2 はデータ 2 が有効なデータならば" 1 "を出力し、無効なデータならば" 0 "を出力する。動作設定はマイコン 2 8 で行う。

[0037]

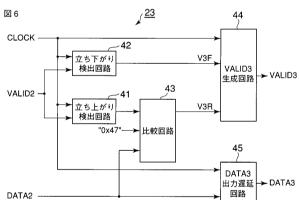

図6には、同期バイト比較回路23の回路図を示す。

[0038]

同期バイト比較回路23は、立ち上がり検出回路41、立ち下がり検出回路42、比較回路43、VALID3生成回路44、DATA3出力遅延回路45で構成される。尚、立ち下がり検出回路42は必ずしも設ける必要はない。

[0039]

同期バイト比較回路 2 3 は、デジタルチューナ部 1 2 から出力されるクロック信号に基づき動作し、デスクランブラ 2 2 から出力されたデータ 2 (DATA2)とバリッド信号VALID3を出力する

[0040]

立ち上がり検出回路41は、バリッド信号VALID2の立ち上がりを検出する回路である。V2R信号は、立ち上がりを検出した場合に1サイクルの期間だけ"1"を出力し、それ以外は"0"を出力する。また立ち下がり検出回路42は、バリッド信号VALID2の立ち下がりを検出する回路である。V2F信号は、立ち下がりを検出した場合1サイクルの期間だけ"1"を出力し、それ以外は"0"を出力する。

[0041]

比較回路43は、TSパケットの同期バイトの比較回路である。入力されたV2R信号が1の場合には、データ2(DATA2)と固定値0×47との比較処理を行う。出力されるV3R信号は、その比較結果が一致していれば(データ2が0×47であれば)1を出力し、一致していなければ(データ2が0×47でなければ)0を出力する。

[0042]

VALID3生成回路44は、バリッド信号VALID3の制御回路であり、バリッド信号VALID3は、入力されたV3R信号の立ち上がりを検出すると"1"を出力し、入力されたV3F信号の立ち上がりを検出すると"0"を出力する。本実施形態において

30

40

50

は、バリッド信号VALID2の1サイクル後にバリッド信号VALID3が出力される。さらに、DATA3出力遅延回路45は、出力されるデータ3(DATA3)の出力タイミングをバリッド信号VALID3と同期させる回路であり、データ2の1サイクル後にデータ3が出力される。

#### [0043]

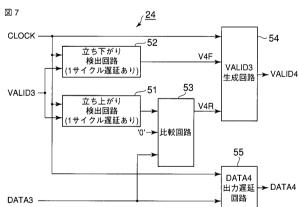

図7には、誤り表示比較回路24の回路図を示す。

この誤り表示比較回路 2 4 は、立ち上がり検出回路 5 1、立ち下がり検出回路 5 2、比較回路 5 3、 V A L I D 4 生成回路 5 4 及び D A T A 4 出力遅延回路 5 5 により構成される。デジタルチューナ部 1 2 から出力されるクロック信号に基づき動作し、同期バイト比較回路 2 3 から出力された D データ 3 (A T A 3)とバリッド信号 V A L I D 3 を入力し、データ 4 (D A T A 4)とバリッド信号 V A L I D 4 を出力する。

#### [0044]

立ち上がり検出回路 5 1 は、入力されたバリット信号 V A L I D 3 の立ち上がりを検出する回路である。出力される V 3 R 信号は、立ち上がりを検出した場合に 1 サイクルだけ " 1 "、それ以外は " 0 "を出力する制御を行う回路で、誤り表示が T S パケットの 2 バイト目に存在するため 1 サイクル遅延させて出力する。

#### [0045]

立ち下がり検出回路52は、入力信号VALID3の立ち下がりを検出する回路で、V3F信号は立ち下がりを検出した場合に1サイクルだけ"1"、それ以外は"0"を出力する制御を行う回路で、誤り表示がTSパケットの2バイト目に存在するため1サイクル遅延させて出力する。

#### [0046]

比較回路 5 3 は T S パケットの誤り表示の比較回路で、 V 3 R 信号が " 1 " の場合にデータ 3 と固定値 " 0 " との比較処理を行う。 V 4 R 信号は、比較結果が一致していれば(入力されたデータ 3 の誤り表示が " 0 " ならば) " 1 "を出力し、一致していなければ(入力されたデータ 3 の誤り表示が " 1 " ならば) " 0 " を出力する。 V A L I D 3 生成回路 5 4 は、バリッド信号 V A L I D 4 として、 V 4 R 信号の立ち上がりを検出すると " 1" を出力し、 V 4 F 信号の立ち上がりを検出すると " 0 " を出力する。

### [0047]

本実施形態における構成では、バリッド信号VALID3の2サイクル後にバリッド信号VALID4が出力される。DATA4出力遅延回路55は、データ4(DATA4)の出力タイミングをバリッド信号VALID4と同期させるための回路であり、データ3の2サイクル後に、データ4が出力される。

## [0048]

以上説明したように、本実施形態は、TSパケットのエラー検出を回路(ハードウェア)より行う構成であり、従来のプログラム処理でエラー検出に対して、エラー検出のためのCPUに掛かる処理の負荷を大きく軽減している。特に、本実施形態のデジタル放送受信装置がパソコンやPDA等の情報処理装置に搭載された際に、情報処理装置のCPUに対するエラー検出処理の負担を軽減させることができる。

#### [0049]

本実施形態は、ハードウェアからなるTSパケットのエラー検出回路を設けることにより、CPUに対する情報処理量及びメモリ使用量を軽減し、記録データサイズをさらに小さくすることができる。従って、情報処理装置が同じ性能でよければ、現在よりも性能が低いCPUを採用でき、またメモリ容量も低容量化によるコスト低下を実現することができる。また、現状の情報処理装置であれば、CPUに対する情報処理量及びメモリ使用量に余裕ができ、他の情報に対する処理や他の機能を搭載することができる。

#### [0050]

尚、本実施形態は、デジタル放送の受信に対応したテレビ等では専用回路を実装してMPEG2-TSの処理を行っているのに対して、デジタル放送受信装置は、PC等の情報装置に実装されているCPUを用いて、MPEG2-TSの処理を軽負荷のソフトウェア

で実行することにより実現でき、専用回路が不要であり、実装コストを抑えることができる。

【図面の簡単な説明】

[0051]

【図1】一実施形態に係るデジタル放送受信装置の概略的な構成を示すブロック図である

【図2】MPEG2-TSのパケットとストリームの構造を示す図である。

【図3】本実施形態のコンテンツ保護機能を有する制御部の具体的な構成例を示すブロック図である。

【図4】本実施形態のコンテンツ保護機能を有する制御部内部の動作タイミングについて 説明するためのタイミングチャートである。

【図5】図3に示す同期バイト間隔検出回路21の回路図を示す。

【図6】図3に示す同期バイト比較回路を示す図である。

【図7】図3に示す誤り表示比較回路を示す図である。

【符号の説明】

[0052]

1 … C P U (中央処理ユニット)、2 … ホストコントローラ、3 … メインメモリ、4 … 表示コントローラ、5 … 表示用メモリ、6 … I / O (入出力) コントローラ、7 … 記憶装置、8 … オーディオコントローラ、1 1 … コンテンツ保護機能を有する制御部、1 2 … デジタルチューナ部、2 0 … エラー検出回路、2 1 … 同期バイト間隔検出回路、2 2 … デスクランブラ、2 3 … 同期バイト比較回路、2 4 …、2 5 … P I D フィルタ、2 6 … 暗号処理部、2 7 … バス I / F、2 8 … マイコン、2 9 … I C カード制御回路、1 0 0 …情報処理装置。

【図1】

図 1

【図2】

図 2

20

## 【図3】

図3

## 【図4】

EX 4

CLOCK

VALID

DATA

0x47

188byte

204byte

## 【図5】

# 【図6】

# 【図7】

## フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 安田 広行

東京都青梅市末広町2丁目9番地 株式会社東芝青梅事業所内

F ターム(参考) 5C164 UB23P UB42P

5K028 EE03

5K061 AA13 BB06