### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-85479 (P2008-85479A)

(43) 公開日 平成20年4月10日(2008.4.10)

| (51) Int.Cl. |           | F 1       |      | テーマコード(参考) |

|--------------|-----------|-----------|------|------------|

| HO4N 5/335   | (2006.01) | HO4N 5/3  | 35 Z | 4M118      |

| HO1L 27/146  | (2006.01) | HO1L 27/1 | 4 A  | 5CO24      |

|              |           | HO4N 5/3  | 35 F |            |

### 審査請求 未請求 請求項の数 8 OL (全 12 頁)

| (21) 出願番号 | 特願2006-261058 (P2006-261058) | (71) 出願人 | 000005821           |

|-----------|------------------------------|----------|---------------------|

| (22) 出願日  | 平成18年9月26日 (2006.9.26)       |          | 松下電器産業株式会社          |

|           |                              |          | 大阪府門真市大字門真1006番地    |

|           |                              | (74) 代理人 | 100090446           |

|           |                              |          | 弁理士 中島 司朗           |

|           |                              | (74) 代理人 | 100072442           |

|           |                              |          | 弁理士 松村 修治           |

|           |                              | (74) 代理人 | 100125597           |

|           |                              |          | 弁理士 小林 国人           |

|           |                              | (72) 発明者 | 石本 久人               |

|           |                              | , , ,    | 大阪府門真市大字門真1006番地 松下 |

|           |                              |          | 電器産業株式会社内           |

|           |                              | (72) 発明者 | 村上雅史                |

|           |                              |          | 大阪府門真市大字門真1006番地 松下 |

|           |                              |          | 電器産業株式会社内           |

|           |                              |          | 最終頁に続く              |

(54) 【発明の名称】固体撮像装置、及びデジタルカメラ

### (57)【要約】

【課題】高ゲインを実現しつつ、ゲインのばらつきを抑制することができる固体撮像装置を提供する。

【解決手段】画素信号を出力する単位セルが複数個配列された画素アレイ1と、列毎に画素信号を増幅して出力するカラムアンプ5と、オフセット電圧を除去して出力するノイズキャンセル部6と、各列毎の画素信号を順につ出力する水平読出部7と、水平読出部から出力アンプは列毎に電える撮像装置100であって、カラムアンプは列毎に電流源となる電流源トランジスタと画素信号を増幅するる負荷トランジスタとを含み、出力アンプは負荷となる負荷トランジスタと水平読出部から出力される画素信号を増幅する第2増幅トランジスタとを含み、電流源トランジスタとない、同一プロセスにおいて形成されるMOSトランジスタにより構成されている

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

受光量に応じた画素信号を出力する単位セルが複数個配列された画素アレイ部と、

1列の単位セルに共通に接続され、列毎に、該当列中のいずれかの単位セルから出力される画素信号を増幅して出力するカラムアンプ部と、

前記カラムアンプに1対1で接続され、列毎に、単位セル毎に画素信号からオフセット 電圧を除去して出力するノイズキャンセル部と、

前記ノイズキャンセル部に接続され、前記ノイズキャンセル部から出力された各列毎の画素信号を順次選択して出力する水平読出部と、

前記水平読出部に接続され、前記水平読出部から出力された画素信号を増幅して出力する出力アンプとを備える固体撮像装置であって、

前記カラムアンプは、列毎に、電流源となる電流源トランジスタと、前記画素信号を増幅する第1増幅トランジスタとを含み、

前記出力アンプは、負荷となる負荷トランジスタと、水平読出部から出力される画素信号を増幅する第2増幅トランジスタとを含み、

前記電流源トランジスタ、前記第1増幅トランジスタ、前記負荷トランジスタ、及び前記第2増幅トランジスタの全てが、同一プロセスにおいて形成されるMOSトランジスタにより構成されていること

を特徴とする固体撮像装置。

### 【請求項2】

前記電流源トランジスタ、前記第1増幅トランジスタ、前記負荷トランジスタ、及び前記第2増幅トランジスタの全てが、NチャネルMOSであること

を特徴とする請求項1に記載の固体撮像装置。

#### 【請求項3】

前記電流源トランジスタ、前記第1増幅トランジスタ、前記負荷トランジスタ、及び前記第2増幅トランジスタの全てが、エンハンスメント型であること

を特徴とする請求項1に記載の固体撮像装置。

#### 【請求項4】

前記出力アンプにおいて、

前記負荷トランジスタのゲート端子には、前記負荷トランジスタのソース端子に印加されている電源電圧よりも高い電圧が印加されていること

を特徴とする請求項1に記載の固体撮像装置。

#### 【請求項5】

前記カラムアンプにおいては、前記第1増幅トランジスタによる出力電位が、前記画素信号が大きくなるとともに増加し、かつ前記出力アンプにおいては、前記第2増幅トランジスタによる出力電位が、前記画素信号が大きくなるとともに減少すること

を特徴とする請求項1に記載の固体撮像装置。

### 【請求項6】

前記出力アンプは、

さらに、前記第 2 増幅トランジスタの前段に接続されたレベルシフトトランジスタを含み、

前記出力アンプの入出力特性は、前記レベルシフトトランジスタによって、前記カラムアンプの入出力特性に比べて、入力電位の高い側へシフトしていること

を特徴とする請求項5に記載の固体撮像装置。

#### 【請求項7】

前記カラムアンプにおいては、前記第1増幅トランジスタによる出力電位が、前記画素信号が大きくなるとともに減少し、かつ前記出力アンプにおいては、前記第2増幅トランジスタによる出力電位が、前記画素信号が大きくなるとともに増加すること

を特徴とする請求項1に記載の固体撮像装置。

## 【請求項8】

50

10

20

30

前記カラムアンプは、

さらに、前記第1増幅トランジスタの前段に接続されたレベルシフトトランジスタを含 み、

(3)

前記カラムアンプの入出力特性は、前記レベルシフトトランジスタによって、前記出力アンプの入出力特性に比べて、入力電位の高い側へシフトしていること

を特徴とする請求項7に記載の固体撮像装置。

【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、光を入射して光電変換する単位セルが、半導体基板上に1次元又は2次元に配置してなる固体撮像装置及び当該固体撮像装置を備えるデジタルカメラに関し、特に、 ゲインのばらつきを抑制するための技術に関する。

#### 【背景技術】

## [0002]

近年、デジタルカメラ付き携帯電話等の撮像機器が一般に普及している。

これらの撮像機器は、軽量化及び連続使用時間を延ばす為に消費電力を抑えることが必須であるので、CCD型撮像素子と比べ消費電力が著しく低いMOS型撮像素子を搭載しているものが多い。

ここで、CMOSイメージセンサの信号読み出し方式は、画素アレイの中のある一行を選択しそれらを同時に列方向へと読み出す列並列出力型が一般的である。

#### [0003]

上記列並列出力型の信号出力回路は、画素の出力をスイッチドキャパシタでサンプリングして読み出す方式のもの、列毎にアンプを搭載して読み出す方式のもの、及び A D コンバータを列毎に設ける方式のもの等がある。

上記列毎にアンプを搭載して読み出す方式のものは、例えばシングルエンドアンプを用いたものであり、特許文献 1 及び特許文献 2 にその詳細が開示されている。

### [0004]

特許文献 1 では、電流源のMOSトランジスタ及び増幅用のMOSトランジスタで構成されるシングルエンドアンプについて記載されており、このような構成においては、画素毎にオフセット電圧を除去して信号成分だけを取り出すことが可能であり、また読み出しのゲインを容量素子の比で任意に設定可能であることが記載されている。

しかしながら、特許文献 1 に記載されているようなソース接地型のアンプの回路構成では、ゲインが低いという短所がある。

### [0005]

また特許文献 2 には、ソース接地型のアンプの回路構成にカスコード接続のトランジスタを付加することで、特許文献 1 のようなソース接地型のアンプの回路構成におけるゲインが低いという短所を克服した固体撮像装置が記載されている。

しかしながらカスコード接続のトランジスタを制御するためのトランジスタや電流源が付加されることで、回路を構成する素子数および素子間の配線数が増加するという短所がある。

【特許文献1】特開平5-207220号公報

【特許文献2】特開2005-252529号公報

### 【発明の開示】

【発明が解決しようとする課題】

### [0006]

近年のCMOSイメージセンサは、高画素化やチップサイズの縮小化が急速に進んでいるため、各画素のサイズが微細化している。 1 画素あたりのサイズが微細化すると、受光量が減少するので感度が低下する傾向があり、出力段のアンプのゲインを従来よりもさらに高める必要がある。

しかしながら、アンプのゲインを高めるほどゲインのばらつきが顕著になる。

10

20

30

50

40

#### [0007]

また、同形式のアンプを複数用いると、入力電圧の増加に対するゲインの変動が重複し、トータルゲインの変動が相乗的に大きくなり、画素信号の全般にわたって良好な感度を得ることができない。

本発明は、高ゲインを実現しつつ、ゲインのばらつきを抑制することができる固体撮像装置を提供することを第1の目的とし、また、トータルゲインの変動をフラットに近づけることを第2の目的とする。

### 【課題を解決するための手段】

### [0008]

上記目的を達成するために、本発明に係る固体撮像装置は、受光量に応じた画素信号を出力する単位セルが複数個配列された画素アレイ部と、1列の単位セルに共通に接続するに、列毎に、該当列中のいずれかの単位セルから出力される画素信号を増位セル毎に正力するクラムアンプ部と、前記カラムアンプに1対1で接続され、前記ノイズキャンセル部から出力された各列毎に、単位セル毎にで接続され、前記ノイズキャンセル部から出力を表に表が正式を関立された手を順力された各別の画素に見出力する出力する出力で接続され、前記出力を増幅して表に接続され、前記の第1増幅がある出力を増幅がある第2増幅がある負荷を含み、前記出力を増幅がある第2増幅がある負荷を含み、前記出がありまた。 ジスタとを含み、前記出力では、負荷となる負荷トランジスタとを増幅がある第2増幅がある。 前記第1増幅トランジスタ、前記第2増幅トランジスタの全でが、同一プロセスにおいて形成されるMOSトランジスタにより構成されていることを特徴とする。

### 【発明の効果】

#### [0009]

課題を解決するための手段に記載した構成により、製造ばらつきに拠るゲインのばらつきを抑制することができる。

従って、高ゲインを実現しつつ、ゲインのばらつきを抑制することができる。

ここで、固体撮像装置において、前記電流源トランジスタ、前記第1増幅トランジスタ、前記負荷トランジスタ、及び前記第2増幅トランジスタの全てが、NチャネルMOSであることを特徴とすることもできる。

### [0010]

これにより、 増幅にかかる M O S トランジスタを N チャネル M O S に統一することができる。

ここで、固体撮像装置において、前記電流源トランジスタ、前記第1増幅トランジスタ、前記負荷トランジスタ、及び前記第2増幅トランジスタの全てが、エンハンスメント型であることを特徴とすることもできる。

### [0011]

これにより、 増幅にかかる M O S トランジスタをエンハンスメント型に統一することが できる。

ここで、固体撮像装置において、前記出力アンプにおいて、前記負荷トランジスタのゲート端子には、前記負荷トランジスタのソース端子に印加されている電源電圧よりも高い電圧が印加されていることを特徴とすることもできる。

## [0012]

これにより、負荷トランジスタによる電圧のドロップ分を抑制することができるので、 特に有用である。

ここで、固体撮像装置において、前記カラムアンプにおいては、前記第1増幅トランジスタによる出力電位が、前記画素信号が大きくなるとともに増加し、かつ前記出力アンプにおいては、前記第2増幅トランジスタによる出力電位が、前記画素信号が大きくなるとともに減少することを特徴とすることもできる。

10

20

30

40

#### [ 0 0 1 3 ]

これにより、カラムアンプの極性と出力アンプの極性が反対なので、カラムアンプと出 カアンプとのゲイン特性の弱点を補い合うことができる。

ここで、固体撮像装置において、前記出力アンプは、さらに、前記第2増幅トランジスタの前段に接続されたレベルシフトトランジスタを含み、前記出力アンプの入出力特性は、前記レベルシフトトランジスタによって、前記カラムアンプの入出力特性に比べて、入力電位の高い側へシフトしていることを特徴とすることもできる。

### [0014]

これにより、一方のアンプを、画素信号に対して、ゲインの高いところからゲインが下がる方向に使用し、もう一方のアンプを、画素信号に対して、ゲインの低いところからゲインが上がる方向に使用することができるので、トータルゲインの変動をフラットに近づけることができる。

ここで、固体撮像装置において、前記カラムアンプにおいては、前記第1増幅トランジスタによる出力電位が、前記画素信号が大きくなるとともに減少し、かつ前記出力アンプにおいては、前記第2増幅トランジスタによる出力電位が、前記画素信号が大きくなるとともに増加することを特徴とすることもできる。

### [0015]

これにより、カラムアンプの極性と出力アンプの極性が反対なので、カラムアンプと出 カアンプとのゲイン特性の弱点を補い合うことができる。

ここで、固体撮像装置において、前記カラムアンプは、さらに、前記第1増幅トランジスタの前段に接続されたレベルシフトトランジスタを含み、前記カラムアンプの入出力特性は、前記レベルシフトトランジスタによって、前記出力アンプの入出力特性に比べて、入力電位の高い側へシフトしていることを特徴とすることもできる。

#### [0016]

これにより、一方のアンプを、画素信号に対して、ゲインの高いところからゲインが下がる方向に使用し、もう一方のアンプを、画素信号に対して、ゲインの低いところからゲインが上がる方向に使用することができるので、トータルゲインの変動をフラットに近づけることができる。

【発明を実施するための最良の形態】

## [0017]

(実施の形態1)

### < 構成 >

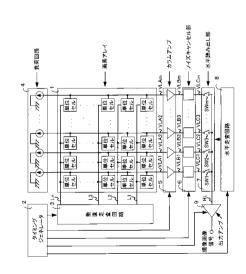

図1は、本発明の実施の形態1における撮像装置100の概要を示す図である。

図1に示すように、本発明の実施の形態1における撮像装置100は、画素アレイ1、タイミングジェネレータ2、垂直走査回路3、負荷回路4、カラムアンプ5、ノイズキャンセル部6、水平読み出し部7、水平走査回路8、出力アンプ9から構成される。

#### [ 0 0 1 8 ]

なお、タイミングジェネレータ 2 、カラムアンプ 5 、ノイズキャンセル部 6 を除く他の 構成要素の詳細は特許文献 2 と同様である。

画素アレイ1は、初期化時の電圧であるリセット電圧及び読み出し時の電圧であるリード電圧を、列毎にそれぞれ垂直信号線VLA1~VLAmに出力する単位セルが1次元又は2次元上に配列された撮像領域であり、ここでは記載を簡略化しているが、実際の画素数は、1次元で数千個、2次元で数十万~数百万個程度である。

## [0019]

タイミングジェネレータ 2 は、垂直走査回路 3 、カラムアンプ 5 、ノイズキャンセル部 6 、水平走査回路 8 、及び出力アンプ 9 に制御信号を供給して駆動及び制御する周辺回路 であり、外部から撮影指示が入力されるのを待ち、撮影指示が入力されると、適切な露光時間の経過後に全ての単位セルから順次輝度情報を読み出させる。

ここで、タイミングジェネレータ 2 からは、垂直走査回路 3 ヘリセットパルス(初期化信号:RESET)、及び、リードパルス(読み出しパルス:READ)が、ノイズキャ

10

20

30

40

ンセル部 6 ヘサンプリングパルス(SP)、及び、クランプパルス(CP)が決められた タイミングで供給され、これら各制御パルスにそれぞれ対応するトランジスタが開閉(OFF/ON)される。

#### [0020]

垂直走査回路 3 は、横 1 行毎に、" R E S E T "、" R E A D 1 "、" R E A D 2 "の 3 本の制御線( L 1 ~ L n )を備え、画素アレイ 1 の画素に対して、行単位で、リセット (初期化)、リード (読み出し)を制御する。

負荷回路4は、縦1列毎に同一の回路が1個接続されており、出力電位を読み出す為に 、列単位で画素アレイ1の各画素に負荷をかける回路である。

### [0021]

カラムアンプ 5 は、列毎に同一の回路が 1 個接続されており、画素アレイ 1 からの列単位のリセット電圧及びリード電圧を増幅して順次、列毎に垂直信号線 V L B 1 ~ V L B m に出力する。

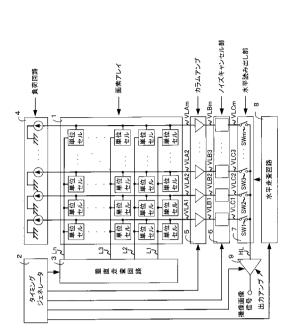

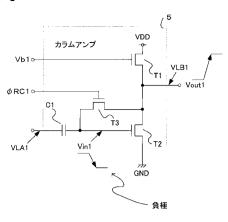

図2は、本発明の実施の形態1におけるカラムアンプ5の回路構成を示す図である。

図2に示すように、カラムアンプ5は、画素信号が大きくなるとともに出力電位が増加する負極のアンプであり、電源電圧VDDと出力端子との間に接続され電流源となる電流源トランジスタT1、画素信号を増幅する増幅トランジスタT2、増幅トランジスタT2のゲート端子と出力端子とを一定時間閉じてリセットをかけるリセットトランジスタT3、及び、輝度情報を蓄積するコンデンサC1を含む。ここで、電流源トランジスタT1のゲートには電源電圧よりも高い電圧Vb1が印加され、リセットトランジスタT3のゲートにはリセット信号線が接続され、コンデンサC1には入力信号線が接続されている。

#### [0022]

図3は、カラムアンプ5の入出力特性(Vin1-Vout1特性)を示す図である。 図3に示すように、カラムアンプ5の入出力特性は入力に対して一様ではなく、入力電位(Vin1)が中間のあたりでは、出力電位(Vout1)は入力電位(Vin)に応じて十分に変化するが、入力電位(Vin1)が低い場合及び高い場合には、入力電位(Vin1)に対する出力電位(Vout1)の変化量が小さい。

### [0023]

本実施の形態では、入力電位(Vin1)が図3中のVA1の状態において、図2におけるリセットトランジスタT3のゲートを一定時間閉じてリセットをかけ、その後増幅トランジスタT2のベース電位の変動量( Vin1)に応じた出力電位の変動量( Vout1)を得ることとし、図3中のVA1からVB1までの間が動作領域となる(図3中の太線矢印)。

### [ 0 0 2 4 ]

ここでカラムアンプ 5 は負極のアンプなので、リセット後、時間 t が経過するにつれて、入力電圧 V i n 1 は負方向へ向かう。

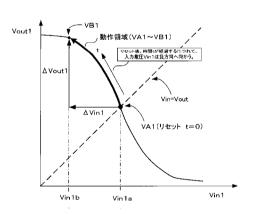

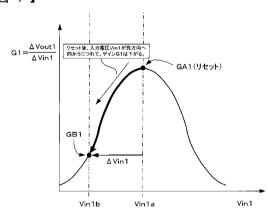

図 4 は、カラムアンプ 5 のゲイン特性 ( V i n 1 - G 1 特性 : G 1 = V o u t 1 / V i n 1 )を示す図である。

図4に示すように、カラムアンプ5のゲインは入力に対して一定ではなく、ゲインG1は図3に示したVin1-Vout1特性の傾きに相当するので、入力電位(Vin1)が中間のあたりでゲインG1が高く、入力電位(Vin1)が低い場合及び高い場合にはゲインG1は低い。

## [0025]

本実施の形態では、Vin1-Vout1特性の傾きが最も大きいVA1(図3)の時の入力電圧Vin1aにおいて最高のゲインGA1が得られ、カラムアンプ5は負極のアンプなので、リセット後、入力電圧Vin1が負方向へ向かうにつれてゲインG1は下がり、VB1(図3)の時の入力電圧Vin1bにおいて最も低いゲインGB1が得られる(図4中の太線矢印)。

### [0026]

50

10

20

30

10

20

30

40

50

ノイズキャンセル部 6 は、カラムアンプ 5 より列毎に出力されるリセット電圧とリード電圧との差分を示す輝度情報を、それぞれ列毎の垂直信号線 V L C 1 ~ V L C mに出力する。

水平読み出し部7は、水平信号線HLと、当該水平信号線HLと垂直信号線VLC1~VLCmのそれぞれとの接続を水平走査回路8の制御に基づいて切り替えるスイッチSW1~SWmを備え、ノイズキャンセル部6より出力される列毎の輝度情報を、選択的に水平信号線HLに出力する。

### [0027]

水平走査回路8は、水平読み出し部7のスイッチSW1~SWmを順次切り替えて、各垂直信号線を順番に水平信号線HLと接続して、列毎の輝度情報の読み出しを制御する。 出力アンプ9は、水平信号線HLと接続されており、水平読み出し部7からの輝度情報を増幅して、撮像画像信号を外部に出力する。

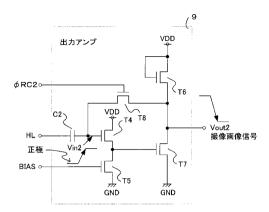

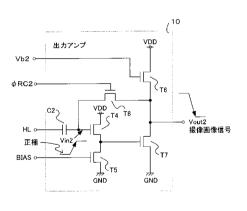

図5は、本発明の実施の形態1における出力アンプ9の回路構成を示す図である。

## [ 0 0 2 8 ]

図5に示すように、出力アンプ9は、画素信号が大きくなるとともに出力電位が減少する正極のアンプであり、入力信号の電圧レベルを変動させ、出力アンプ9の入出力特性を、カラムアンプ5の入出力特性に比べて、入力電位の高い側へシフトさせるレベルシフトランジスタT4、T5、電源電圧VDDと出力端子との間に接続され負荷となる負荷トランジスタT6、電圧が変動された入力信号を増幅する増幅トランジスタT7、レベルシフトトランジスタT5のゲート端子と出力端子とを一定時間閉じてリセットをかけるリセットトランジスタT8、及び、輝度情報を蓄積するコンデンサC2を含む。ここで、負荷トランジスタT6のゲートはリセット信号線が接続され、コンデンサC2には入力信号線が接続され、負荷トランジスタT6と増幅トランジスタT7の間には出力信号線が接続されている。

### [0029]

また、カラムアンプ 5 と出力アンプ 9 とに用いられるトランジスタの種類を、例えば、N チャネル M O S やエンハンスメント M O S 等の同一種類のトランジスタに統一したり、同一プロセスにおいて形成される M O S トランジスタにより構成すると、製造ばらつきが揃うので特性上望ましい。

特に、従来は、製造プロセスや出力電位の優位性等の理由から、カラムアンプの電流源トランジスタと増幅トランジスタ、及び出力アンプの増幅トランジスタは、エンハンスメント型のNチャネルMOSで構成し、出力アンプの負荷トランジスタはデプレッションMOSで構成することが一般的であったので、同様の構成のままでアンプのゲインを高めと、種類の異なるそれぞれのトランジスタによる製造ばらつきが無秩序に影響しあい、トータルゲインのばらつきが顕著になってしまうという問題が生じるが、本実施の形態においては、少なくとも出力アンプ9の負荷トランジスタT6と増幅トランジスタT7の2つ、もしくは、カラムアンプ5の電流源トランジスタT1と増幅トランジスタT2、及び出力アンプ9の負荷トランジスタT6と増幅トランジスタT7の4つを、NチャネルMOSやエンハンスメントMOS等の同一種類のトランジスタに統一したり、同一プロセスにおいて形成されるMOSトランジスタにより構成するものとし、製造ばらつきに拠るゲインのばらつきを抑制する。

### [0030]

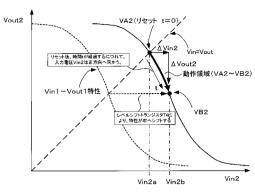

図6は、出力アンプ9の入出力特性(Vin2-Vout2特性)を示す図である。 図6に示すように、出力アンプ9の入出力特性は入力に対して一様ではなく、入力電位 (Vin2)が中間のあたりでは、出力電位(Vout2)は入力電位(Vin2)に応 じて十分に変化するが、入力電位(Vin2)が低い場合及び高い場合には、入力電位( Vin2)に対する出力電位(Vout2)の変化量が小さい。

### [0031]

また、出力アンプ9の入出力特性は、図6中の左方に点線で示したカラムアンプ5の入

出力特性(Vin1 - Vout1特性)に比べて、レベルシフトトランジスタT4による電圧変動(Vth)に相当する分だけ、入力電圧の高い側へシフトする。

本実施の形態では、入力電位(Vin2)が図6中のVA2の状態において、図5におけるリセットトランジスタT8のゲートを一定時間開いてリセットをかけ、その後レベルシフトトランジスタT4のベース電位の変動量( Vin2)に応じた出力電位の変動量 ( Vout2)を得ることとし、図6中のVA2からVB2までの間が動作領域となる(図6中の太線矢印)。

### [0032]

ここで出力アンプ 9 は正極のアンプなので、リセット後、時間 t が経過するにつれて、 入力電圧 V i n 2 は正方向へ向かう。

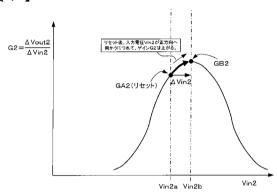

図 7 は、出力アンプ 9 のゲイン特性 ( V i n 2 - G 2 特性 : G 2 = V o u t 2 / V i n 2 ) を示す図である。

図7に示すように、出力アンプ9のゲインは入力に対して一定ではなく、ゲインG2は図6に示したVin2 - Vout 2特性の傾きに相当するので、入力電位(Vin2)が中間のあたりでゲインG2が高く、入力電位(Vin2)が低い場合及び高い場合にはゲインG2は低い。

### [0033]

本実施の形態では、Vin2-Vout2特性の傾きが小さいVA2(図6)の時の入力電圧Vin2aにおいて最も高いゲインGA2が得られ、出力アンプ9は正極のアンプなので、リセット後、入力電圧Vin2が正方向へ向かうにつれてゲインG2は上がり、Vin2-Vout2特性の傾きが最も大きいVB2(図6)の時の入力電圧Vin2bにおいて最高のゲインGB2が得られる(図6中の太線矢印)。

#### [ 0 0 3 4 ]

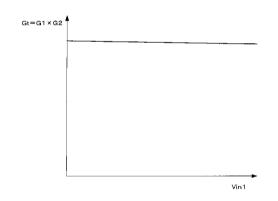

図 8 は、トータルゲイン特性(Vin1‐G t 特性:G t = G 1 x G 2 ) を示す図である。

図8に示すトータルゲインGtは、図4に示すカラムアンプ5のゲインG1と、図7に示す出力アンプ9のゲインG2とを掛け合わせたものであって、カラムアンプ5のゲインは画素信号の増加にともない下がる特性があり、出力アンプ9のゲインは画素信号の増加にともない上がる特性があるので、お互いの特性をキャンセルすることになり、トータルゲインGtを全般にわたってフラットに近づけることができる。

### [ 0 0 3 5 ]

なお、本実施の形態では、カラムアンプ 5 を負極のアンプとし、出力アンプ 9 を正極のアンプとして、トータルゲインを全般にわたってフラットに近づけることができたが、カラムアンプ 5 の特性と出力アンプ 9 の特性とが反対であればよいので、カラムアンプ 5 を正極のアンプとし、出力アンプ 9 を負極のアンプとしてもよい。

< 変形例1 >

図9は、本発明の変形例1における出力アンプ10の回路構成を示す図である。

### [0036]

図9に示す出力アンプ10は、実施の形態1の出力アンプ9の一部を変更したものであり、負荷トランジスタT6のゲートに、電源電圧VDDよりも高い電圧Vb2を印加する点のみが異なり、その他の部分は実施の形態1とまったく同じである。

このようにすることで、出力アンプ10の出力信号の上限値を上げることができ、ダイナミックレンジを広げることができる。

## [ 0 0 3 7 ]

なお、負荷トランジスタT6、及び増幅トランジスタT7をエンハンスメントMOSで構成した場合には、負荷トランジスタT6における電圧のドロップ分を抑制することができるので、特に有用である。

### <まとめ>

以上のように、本発明の実施の形態1、及び変形例1によれば、カラムアンプや出力アンプにおいて増幅にかかるトランジスタの種類を統一するか、当該トランジスタを同一プ

10

20

30

40

ロセスにおいて形成するので、製造ばらつきに拠るゲインのばらつきを抑制することができる。

## [0038]

また、カラムアンプと出力アンプとの極性を反対にして、お互いのゲイン特性の弱点を補い合うことができるので、トータルゲインを全般にわたってフラットに近づけることができる。

#### 【産業上の利用可能性】

### [0039]

本発明は、ビデオカメラやデジタルスチルカメラなどの撮像機器に適用することができる。本発明によって、当該撮像機器に使用する固体撮像装置において、高ゲインを実現しつつ製品毎の出力のばらつきを抑制したり、トータルゲインを全般にわたってフラットに近づけることができ、撮像機器の画質の向上に寄与することができるので、その産業的利用価値は極めて高い。

【図面の簡単な説明】

### [0040]

- 【図1】本発明の実施の形態1における撮像装置100の概要を示す図である。

- 【図2】本発明の実施の形態1におけるカラムアンプ5の回路構成を示す図である。

- 【図3】カラムアンプ5の入出力特性を示す図である。

- 【図4】カラムアンプ5のゲイン特性を示す図である。

- 【図5】本発明の実施の形態1における出力アンプ9の回路構成を示す図である。

- 【図6】出力アンプ9の入出力特性を示す図である。

- 【図7】出力アンプ9のゲイン特性を示す図である。

- 【図8】トータルゲイン特性を示す図である。

- 【 図 9 】 本 発 明 の 変 形 例 1 に お け る 出 力 ア ン プ 1 0 の 回 路 構 成 を 示 す 図 で あ る 。

#### 【符号の説明】

### [ 0 0 4 1 ]

- 1 画素アレイ

- 2 タイミングジェネレータ

- 3 垂直走杳回路

- 4 負荷回路

- 5 カラムアンプ

- 6 ノイズキャンセル部

- 7 水平読出部

- 8 水平走査回路

- 9 出力アンプ

- 10 出力アンプ

- 1 0 0 撮像装置

- T 1 電流源トランジスタ

- T2 増幅トランジスタ

- T3 リセットトランジスタ

- T4 レベルシフトトランジスタ

- T5 レベルシフトトランジスタ

- T6 負荷トランジスタ

- T 7 増幅トランジスタ

- T8 リセットトランジスタ

- C 1 コンデンサ

- C 2 コンデンサ

20

10

30

【図1】

【図2】

【図3】

【図4】

【図5】

# 【図7】

【図8】

【図9】

## フロントページの続き

F ターム(参考) 4M118 AA05 AA10 AB01 BA14 DD09 DD12 FA06 5C024 AX01 BX01 CX41 CY47 GX03 GX16 GY31 HX01 HX02 HX17