# (19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12) 特 許 公 報(B2)

FL

(11)特許番号

特許第4229652号 (P4229652)

最終頁に続く

(45) 発行日 平成21年2月25日(2009.2.25)

(24) 登録日 平成20年12月12日(2008.12.12)

| (01) 1110.011  |                 |                |          |          |      |          |          |

|----------------|-----------------|----------------|----------|----------|------|----------|----------|

| G11C 29/02     | (2006.01)       | G11C           | 29/00    | 675L     |      |          |          |

| G11C 29/56     | (2006.01)       | G11C           | 29/00    | 659      |      |          |          |

| G 1 1 C 11/401 | (2006.01)       | G11C           | 11/34    | 371A     |      |          |          |

| GO1R 31/28     | (2006.01)       | GO1R           | 31/28    | V        |      |          |          |

|                |                 | GO1R           | 31/28    | В        |      |          |          |

|                |                 |                |          |          |      | 請求項の数 6  | (全 30 頁) |

| (21) 出願番号      | 特願2002-211081   | (P2002-211081) | (73) 特許権 | 替 50312  | 1103 |          |          |

| (22) 出願日       | 平成14年7月19日      | (2002. 7. 19)  |          | 株式会社     | Lルネ† | ナステクノロジ  |          |

| (65) 公開番号      | 特開2004-55030 (F | P2004-55030A)  |          | 東京都千     | 代田日  | 区大手町二丁目( | 6番2号     |

| (43) 公開日       | 平成16年2月19日      | (2004. 2. 19)  | (74) 代理人 | 1000647  | 46   |          |          |

| 審查請求日          | 平成17年4月22日      | (2005. 4. 22)  |          | 弁理士      | 深見   | 久郎       |          |

|                |                 |                | (74) 代理人 | 1000851  | 32   |          |          |

|                |                 |                |          | 弁理士      | 森田   | 倰雄       |          |

|                |                 |                | (74) 代理人 | 1000837  | 03   |          |          |

|                |                 |                |          | 弁理士      | 仲村   | 義平       |          |

|                |                 |                | (74) 代理人 | 10009678 | 81   |          |          |

|                |                 |                |          | 弁理士      | 堀井   | 豊        |          |

|                |                 |                | (74) 代理人 | 1000983  | 16   |          |          |

|                |                 |                |          | 弁理士      | 野田   | 久登       |          |

||(74)代理人 100109162

弁理士 酒井 將行

# (54) 【発明の名称】半導体回路装置

## (57)【特許請求の範囲】

# 【請求項1】

メモリクロック信号に同期して動作するメモリコア、

テストクロック信号に同期して、前記メモリコアへ信号 / データを転送するメモリ転送 回路、

少なくとも前記メモリクロック信号およびテストクロック信号を受け、少なくとも前記 メモリクロック信号およびテストクロック信号のいずれかを選択するタイミング選択回路 、および

前記タイミング選択回路の出力信号を補正用テストクロック信号に同期して取込み、外部へ転送するタイミング転送回路を備える、半導体回路装置。

# 【請求項2】

ラッチタイミング信号に同期して、前記メモリコアから転送された信号 / データを取込 み外部へ転送するラッチ転送回路をさらに備え、

前記タイミング選択回路は、前記メモリクロック信号、前記テストクロック信号および前記ラッチタイミング信号のいずれかを選択指示信号に応答して選択する、請求項1記載の半導体回路装置。

# 【請求項3】

前記タイミング選択回路の入力から前記タイミング転送回路の出力までの前記メモリクロック信号、前記テストクロック信号および前記ラッチタイミング信号の遅延時間は実質的に同じである、請求項2記載の半導体回路装置。

#### 【請求項4】

前記メモリ転送回路は、前記メモリコアに対してデータを転送するデータ転送回路を含み、

前記半導体回路装置は、さらに、

前記データ転送回路と同じ特性を有するレプリカ回路、

前記メモリクロック信号と前記レプリカ回路の出力信号の一方を選択するテストデータ 選択回路、および

前記補正用クロック信号に同期して前記テストデータ選択回路の出力信号を取込み転送するテストデータ転送回路を備える、請求項1記載の半導体回路装置。

#### 【請求項5】

前記テストデータ転送回路と前記タイミング転送回路は、前記補正用クロック信号に同期して与えられた信号を取込み転送するラッチ回路を共有する、請求項4記載の半導体回路装置。

# 【請求項6】

前記タイミング転送回路と前記テストデータ転送回路とは、それぞれ別々に配置されて前記補正用クロック信号に同期して動作するラッチ回路を備える、請求項4記載の半導体回路装置。

#### 【発明の詳細な説明】

#### [00001]

#### 【発明の属する技術分野】

この発明は、半導体回路装置に関し、特に、メモリとロジックとが同一半導体基板上に集積化されるシステム L S I と称される半導体回路装置に関する。より特定的には、この発明は、内蔵メモリを信号 / データのタイミング条件を外部からテストするための構成に関する。

#### [00002]

# 【従来の技術】

DRAM(ダイナミック・ランダム・アクセス・メモリ)とロジックデバイスまたはマイクロプロセッサとを同一半導体基板上に集積化するDRAM内蔵システムLSIが普及してきている。このDRAM内蔵システムLSIは、個別のDRAMとロジックデバイスまたはマイクロプロセッサをプリント基板上にはんだ付けなどにより実装する従来のシステムと比べて以下の利点を有している。

# [0003]

(1) ピン端子の制約がないため、DRAMとロジックデバイスの間のデータバス幅を大きくすることができ、データ転送速度を向上させることができ、応じてシステム性能を向上させることができる。

### [0004]

(2) DRAMとロジックデバイスの間に形成されるデータバスは、チップ上配線であり、プリント基板上の配線と比べて容量が小さく、データ転送時の動作電流を小さくすることができ、また、高速でデータを転送することができる。

# [0005]

(3) 単一パッケージでシステムが構成されるため、外部のデータバス配線および制御信号配線が不要となり、プリント基板上での占有面積を小さくすることができ、システムを小型化することができる。

# [0006]

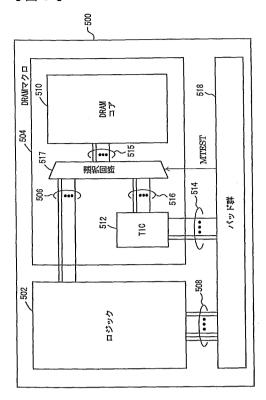

図 8 は、従来の D R A M 内蔵システム L S I の構成の一例を概略的に示す図である。図 8 において、 D R A M 内蔵システム L S I 5 0 0 は、所定の演算処理を行なうロジック 5 0 2 と、少なくともロジック 5 0 2 の必要なデータを格納する D R A M マクロ 5 0 4 と、ロジック 5 0 2 をパッド群 5 1 8 を介して外部装置に接続するロジック外部バス 5 0 8 を含む。

## [0007]

10

20

30

ロジック502は、所定の演算処理を行なう専用のロジックデバイスであってもよく、またマイクロプロセッサであってもよい。ロジック502は、DRAMマクロ504に格納されるデータを用いて処理を行なう回路であればよい。

#### [00008]

DRAMマクロ504は、データを記憶するDRAMコア510と、このDRAMコア510に対し外部から直接アクセスしてテストを行なうためのテストインターフェイス回路(TIC)512と、テストモード指示信号MTESTに従ってロジック502の内部ロジックバス506とテストインターフェイス回路512からの内部テストバス516の一方を選択して内部メモリバス515に接続する選択回路517を含む。この内部メモリバス515は、DRAMコア510に接続される。テストインターフェイス回路512は、外部テストバス514を介してパッド群518に結合される。

10

### [0009]

これらのバス506、508、514、515および516は、それぞれ、制御信号、アドレス信号およびデータを伝達する信号線を含む。内部ロジックバス506、内部メモリバス515および内部テストバス516は、ピン端子の制約条件がないため、そのバス幅を十分広くすることができる。

## [0010]

DRAMコア510からの読出データは、選択回路517を介することなく直接テストインターフェイス回路512およびロジック502に転送される。しかしながら、図8においては、図面を簡略化するために、この内部読出データの転送経路は示していない。

20

## [0011]

ロジック外部バス508と外部テストバス514は、図8においては、共通にパッド群518に結合されるように示す。しかしながら、この外部テストバス514とロジック外部バス508は、テストモード指示信号(MTEST)に従って選択的に共通のパッドに接続されるように構成されてもよい。このテストモード指示信号MTESTに従って、選択回路517が、テストインターフェイス回路512をDRAMコア510に結合する。

### [0012]

図9は、DRAMコア510に対する信号を一覧にして示す図である。図9において、DRAMコア510に対しては、クロック信号CLKが動作タイミング決定信号として与えられる。DRAMコア510は、このクロック信号CLKに同期して与えられた信号 / データの取込みおよびデータの出力を行う。

30

# [0013]

DRAMコア510に対して、動作制御信号として、DRAMコア510における内部クロック信号の有効/無効を設定するクロックイネーブル信号CKE、内部での行選択動作を活性化するロウ活性化信号/ACT、選択行を非選択状態へ駆動するためのロウ非活性化信号/PRE、DRAMコア510におけるメモリセルデータのリフレッシュを指示するオートリフレッシュ指示信号/REFA、データの読出を指示するリード動作指示信号/RE、およびデータの書込動作を指示するライト動作指示信号/WRが与えられる。

[0014]

40

DRAMコア510に対しては、さらに、メモリセルのアドレス指定のために13ビットのロウアドレス信号RA<12:0>、4ビットのコラムアドレス信号CA<3:0>、スペアメモリセル行を指定するためのスペアロウ空間アドレッシング用アドレス信号RAspおよびスペア列を指定するためのスペアコラム空間アドレッシング用アドレス信号CAspが与えられる。

# [0015]

スペアロウ空間アドレッシング用アドレス信号RASPおよびスペアコラム空間アドレッシング用アドレス信号CASPは、不良アドレスのヒューズプログラム前に行なわれる試験時において、DRAMコア510のスペアメモリセルヘアクセスし、スペアメモリセルの良/不良を判定するために用いられる。

# [0016]

20

30

40

50

これらのスペア空間アドレッシング用アドレス信号RASPおよびCASPは、Hレベルのときにスペアメモリセル空間を指定し、Lレベルのときにノーマルメモリセル空間を指定する。

#### [0017]

DRAMコア510に対して、さらに、128ビットの書込データD<127:0>および2ビットのスペア書込データSD<1:0>が与えられ、また、DRAMコア510からは、128ビットの読出データQ<127:0>および2ビットのスペア読出データSQ<1:0>が出力される。スペアメモリセル空間がアドレス指定されたときには、冗長置換のためのスペアメモリセルが指定される。したがって、スペア空間アドレッシング用アドレス信号RASPおよびCASPによりスペアメモリセルを指定し、この指定されたスペアメモリセルに対しデータの書込/読出を行なうことにより、スペアメモリセルを、直接外部から試験することができる。

#### [0018]

図9に示すように、DRAMコア510は、個別素子の汎用DRAMに比べて多くの入出力信号を有している。テストインターフェイス回路512は、テスト動作時において、DRAMコア510に対し、図9に示すような信号 / データを、外部からのテスタにより与えられる信号に従って生成する。

### [0019]

テストインターフェイス回路 5 1 2 が、外部テストバス 5 1 4 によりパッド群 5 1 8 を介して図 9 に示す信号 / データを外部テスタとの間で転送した場合、外部テスタのピン数よりもこれらの信号 / データ線の数が多くなり、テストを行なうことができなくなる。また、たとえテストを行なうことができる場合においても、1 つの被試験装置に必要とされる信号線 / データ線の数が多いため、同時に測定することのできるデバイスの数が低減され、テストコストが増大する。

#### [0020]

テストインターフェイス回路 5 1 2 は、このテスト時に必要とされるピン数を低減し、また DRAMコア 5 1 0 へ外部から直接アクセスして DRAMコア 5 1 0 のテストを容易に行なうために設けられる。

# [0021]

図10は、テストインターフェイス回路512に対する外部信号を一覧にして示す図である。この図10に示す信号は、図8に示す外部テストバス514を介して外部のテスト装置とテストインターフェイス回路512との間で転送される。

#### [0022]

図10において、テストインターフェイス回路512に対し、テストクロック信号TCLKとテストクロックイネーブル信号TCKEが与えられる。これらのテストクロック信号TCLKおよびテストクロックイネーブル信号TCKEは、通常動作モード時にDRAMコア510へ与えられるクロック信号CLKおよびクロックイネーブル信号CKEに代えて、テスト動作モード時に用いられる。

# [0023]

テストインターフェイス回路 5 1 2 に対し、さらに、チップセレクト信号 / C S 、ロウアドレスストローブ信号 / R A S 、コラムアドレスストローブ信号 / C A S およびライト動作指示信号 / W E が与えられる。これらの制御信号 / C S 、 / R A S 、 / C A S および / W E のテストクロック信号のたとえば立上がりエッジにおける論理レベルの組合せにより、D R A M コアの動作モードが指定される。

#### [0024]

テストインターフェイス回路 5 1 2 は、これらの外部制御信号をデコードし、図 9 に示すような口ウ活性化信号 / A C T、ロウ非活性化信号 / P R E、オートリフレッシュ指示信号 / R E F A、リード動作指示信号 / R E およびライト動作指示信号 / W E を、そのデコード結果に従って選択的に活性化する。

# [0025]

20

40

50

アドレス信号として、テストインターフェイス回路 5 1 2 に対し、1 3 ビットのアドレス信号 A D < 1 2 : 0 > とスペア空間アドレッシング用アドレス信号 A D s p が与えられる。ロウアドレスとコラムアドレスは同じパッド(端子)を介して時分割的に与えられる。また、スペア空間アドレッシング用アドレス信号 A D s p も、スペアロウおよびスペアコラムに対し時分割的に与えられる。

### [0026]

データとして、 8 ビットのテスト書込データTD < 7 : 0 > と 8 ビットのテスト読出データTQ < 7 : 0 > と 1 ビットのマルチビットテスト結果指示信号TQmbtが、外部テスト装置とテストインターフェイス回路 5 1 2 の間で転送される。

#### [0027]

#### [0028]

テストデータ読出時において、テストインターフェイス回路 5 1 2 は、 D R A M コア 5 1 0 から読出された 1 2 8 ビットのデータを、 8 ビット単位で順次出力する。

#### [0029]

マルチビットテスト結果指示信号TQmbtは、128ビットのテスト読出データについてのマルチビットテスト結果を示す信号である。このマルチビットテスト結果指示信号TQmbtを用いることにより、128ビットのデータを個々に良/不良を判定する必要がなくなり、8ビット単位でデータを出力しても、不良の特定はマルチビット結果が不良を示しているときにのみ行なうことにより、試験時間を短縮することができる。

#### [0030]

図11は、テストインターフェイス回路512に与えられる外部制御信号(TIC制御信号)とDRAMコア510に与えられる制御信号(DRAM制御信号)の関係を真理値表の形態で示す図である。指定される動作モードを、ニモーニックで示す。

# [0031]

図11において、DRAMマクロの非選択状態(DSEL)は、チップセレクト信号/CSがHレベルのときに設定される。この状態において、残りの制御信号/RAS、/CASおよび/WEの論理レベルにかかわらず、DRAMコア510は、非選択状態を維持する。

# [0032]

チップセレクト信号 / C S が L レベルに設定されると、 D R A M コア 5 1 0 に対する動作 モードが指定される。

# [0033]

動作モードが指定されないNOP(ノーオペレーション)の場合、制御信号/RAS、/CASおよび/WEがすべてHレベルに設定される。この場合、DRAMコア510に与えられる制御信号はすべてHレベルを維持し、DRAMコア510に対する新たな動作モードは指定されない。DRAMコア510は、通常、このNOPコマンド印加時においては、スタンバイ状態を維持する。

# [0034]

チップセレクト信号 / CSとロウアドレスストローブ信号 / RASをともにLレベルに設定し、コラムアドレスストローブ信号 / CASとライト動作指示信号 / WEをともにHレベルに設定すると、アレイ活性化を示すACTが指定される。この状態においては、DRAMコア 5 1 0 に対し、ロウ活性化信号 / ACTがLレベルの活性状態に設定される。残りのDRAM制御信号は、Hレベルの非活性状態を維持する。

#### [0035]

ここで、テストインターフェイス回路512に対するTIC制御信号の論理レベルの判定

は、テストクロック信号TCLKの立上がりエッジまたは立下がりエッジにおいて行なわれる。

# [0036]

チップセレクト信号 / CS、ロウアドレスストローブ信号 / RASおよびライト動作指示信号 / WEをLレベルに設定し、コラムアドレスストローブ信号 / CASをHレベルに維持すると、プリチャージ動作を示す PREが指定される。この状態においては、DRAM制御信号として、ロウ非活性化信号 / PREがLレベルに設定され、DRAMコア 5 1 0 がプリチャージ状態に復帰する。

# [0037]

チップセレクト信号/CS、ロウアドレスストローブ信号/RASおよびコラムアドレスストローブ信号/CASをLレベルに設定し、ライト動作指示信号/WEをHレベルに設定した場合には、リフレッシュ動作を示すREFAが指定される。この場合には、DRAM制御信号のうち、オートリフレッシュ指示信号/REFAがLレベルに設定され、DRAMコア510においてリフレッシュが実行される。

#### [0038]

チップセレクト信号 / CSとコラムアドレスストローブ信号 / CASをともにLレベルに設定し、ロウアドレスストローブ信号 / RASとライト動作指示信号 / WEをともにHレベルに設定すると、データ読出を指示するREが指定される。この場合には、DRAM制御信号のうち、リード動作指示信号 / REがLレベルの活性状態に設定され、残りのDRAM制御信号はHレベルに維持される。

### [0039]

チップセレクト信号 / CS、コラムアドレスストローブ信号 / CASおよびライト動作指示信号 / WEをLレベルに設定し、ロウアドレスストローブ信号 / RASをHレベルに設定した場合には、データ書込を示すWEが指定される。この状態においては、DRAM制御信号において、ライト動作指示信号 / WRが、Lレベルに設定される。

# [0040]

テストインターフェイス回路 5 1 2 においては、この図 1 1 に示す真理値表に従って、 T I C 制御信号を D R A M 制御信号に変換する。テストインターフェイス回路 5 1 2 においてアドレスのマルチプレクス、データビット幅の変換および制御信号の変換を行なうことにより、外部テスタ(テスト装置)が、 D R A M コア 5 1 0 ヘアクセスしてテスト動作を行なうときに使用されるピン端子数を大幅に低減することができる。また、テストインターフェイス回路 5 1 2 に与えられる制御信号は、通常のクロック同期型の D R A M に用いられる制御信号と同じであり、標準のクロック同期型 D R A M に対するテスタを用いて、D R A M コア 5 1 0 のテストを行なうことができる。

# [0041]

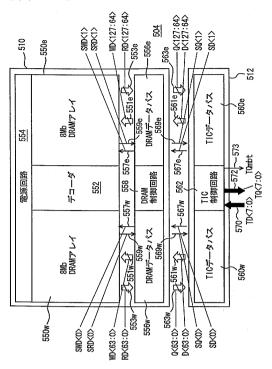

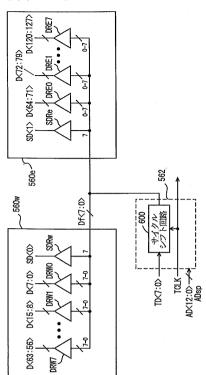

図12は、図8に示すDRAMコア510およびテストインターフェイス回路(TIC)512の構成を概略的に示す図である。図12においては、DRAMコア510とテストインターフェイス回路512の間に配置される選択回路517は、図面を簡略化するために示していない。

## [0042]

図 1 2 において、 D R A M コア 5 1 0 は、それぞれが行列状に配列される複数のメモリセルを有する D R A M アレイ 5 5 0 e および 5 5 0 w と、アドレス信号に従ってこれらの D R A M アレイ 5 5 0 e および 5 5 0 w からメモリセルを選択するデコーダ 5 5 2 を含む。

#### [0043]

DRAMアレイ550eおよび550wは、一例として、それぞれ8Mビットの記憶容量を有する。

#### [0044]

この D R A M アレイ 5 5 0 e および 5 5 0 w においては、不良メモリセルを救済するためのスペアロウおよびスペアコラムが配置される。

# [0045]

50

10

20

30

20

30

40

50

デコーダ 5 5 2 は、これらの D R A M アレイ 5 5 0 e および 5 5 0 w においてメモリセル行を選択するためのロウデコーダと、メモリセル列を選択するためのコラムデコーダ両者を含む。

[0046]

このローディングとコラムデコーダを同一方向に配置することにより、内部の多ビットデータバス線をメモリセルアレイ(DRAMアレイ)上に配線することができ、チップ面積を低減することができる。この列選択のコラムデコーダを行選択のロウデコーダと同一方向に配置する構成は、ロジック内蔵用DRAMマクロにおいて一般的に用いられる。

[0047]

DRAMコア510は、さらに、DRAMアレイ550eとデータの入出力を行なうためのDRAMデータパス556eと、DRAMアレイ550wとデータの入出力を行なうDRAMデータパス556wと、DRAMコア510の内部動作を制御するDRAM制御回路558を含む。

[0048]

DRAMデータパス556eおよび556wの各々は、内部書込データを対応のDRAMアレイ550eおよび550wに転送するライトドライバと、対応のDRAMアレイ550eおよび550wから読出されたメモリセルデータを増幅するプリアンプとを含む。

[0049]

DRAMデータパス 5 5 6 e は、 6 4 ビット幅のライトデータバス 5 5 1 e を介して書込データWD < 1 2 7 : 6 4 > を転送し、またDRAMアレイ 5 5 0 e から内部リードデータバス 5 5 3 e を介して転送される 6 4 ビットの内部読出データRD < 1 2 7 : 6 4 > を受ける。

[0050]

デコーダ 5 5 2 に設けられるコラムデコーダからの列選択線は、行方向に延在して配置され、DRAMアレイ 5 5 0 e において、スペア列もノーマル列と同時に選択される。したがって、DRAMデータパス 5 5 6 e は、不良列救済時においては、スペアライトデータ線 5 5 7 e を介してスペア書込データ SWD < 1 > を転送し、またスペアリードデータ線 5 5 9 e を介してスペアメモリセルから読出データ SRD < 1 > を受ける。

[0051]

DRAMデータパス556wも、同様、64ビット幅の内部ライトデータバス551wを介して内部書込データWD<63:0>をDRAMアレイ550wへ転送し、またDRAMアレイ550wから64ビット幅の内部読出データRD<63:0>を内部リードデータバス553wを介して受ける。

[0052]

DRAMデータパス556wは、さらに、不良列救済時において、スペア列から読出されたスペア読出データSRD<1>をスペアリードデータ線559wを介して受けてまたスペアライトデータ線557wを介してスペア列への書込データSWD<0>を転送する。

[0053]

DRAMデータパス556eは、通常動作モード時において不良列救済時においては、スペアライトデータ線557eを内部ライトデータバス550eの対応のライトデータ線と置換し、またはスペアリードデータ線559eを内部リードデータバス553eの対応の内部リードデータ線と置換する。同様、DRAMデータパス556wも、通常動作モード時において、不良列救済時においては、スペアリードデータ線559wを内部リードデータバス553wの対応の内部リードデータ線と置換し、またスペアライトデータ線557wを内部ライトデータバス551wの対応の内部ライトデータ線と置換する。

[0054]

不良列救済のための不良アドレスのプログラムを行なう前の救済判定のためのテストモード時においては、ノーマルメモリセルおよびスペアメモリセルが試験され、スペアメモリセルが正常であるかの試験が行なわれる。この救済判定のメモリ試験時においては、DRAMデータパス556eおよび556wのスペアリードデータ線559eおよび559w

20

30

40

50

とスペアライトデータ線 5 5 7 e および 5 5 7 w は、ノーマルデータ線との置換を行なうことなく、テストインターフェイス回路 5 1 2 とデータの転送を行なう。

### [0055]

テストインターフェイス回路 5 1 2 は、 D R A M データパス 5 5 6 e および 5 5 6 w それ ぞれに対応して設けられる T I C データパス 5 6 0 e および 5 6 0 w と、外部テスタとの間でテスト書込データ T D < 7 : 0 > およびテスト読出データ T Q < 7 : 0 > およびマルチビットテスト結果指示信号 T Q m b t を転送する T I C 制御回路 5 6 2 を含む。

# [0056]

TIC制御回路 5 6 2 は、また、外部のテスタから図 1 0 に示すようなアドレッシングおよび動作モードを指定する制御信号を受ける。しかしながら、図 1 2 においては、これらのTIC制御回路 5 6 2 へ与えられる制御信号およびアドレス信号は、図面を簡略化するために示していない。

### [0057]

### [0058]

#### [0059]

TICデータパス560eは、DRAMデータパス556eから64ビットのデータQ<127:64>をデータバス563eを介して受け、またDRAMデータパス556eを介して伝送されるスペア内部リードデータ線559eからのスペアリードデータSRD<1>を、スペアリードデータ線569eを介してスペアデータSQ<1>として受ける。

### [0060]

このTICデータパス 5 6 0 e は、 6 4 ビットの書込データ D < 1 2 7 : 6 4 > を内部書 込データバス 5 6 1 e を介して D R A M データパス 5 5 6 e へ転送し、また、内部スペア ライトデータ線 5 5 7 e へスペアライトデータ線 5 6 7 c を介してスペアライトデータ S D < 1 > を転送する。

# [0061]

# [0062]

TIC制御回路562は、データ読出時には、TICデータパス560eおよび560wに与えられた合計128のデータを、8ビットデータ単位で順次テストデータTQ<7: 0 > として出力する。

# [0063]

## [0064]

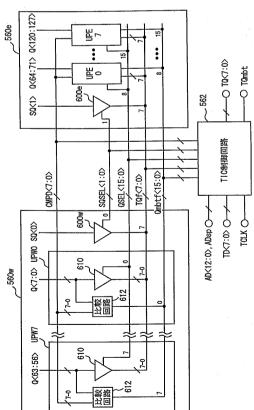

図 1 3 は、図 1 2 に示す T I C データパス 5 5 6 e および 5 5 6 w のデータ書込に関連す

る部分の構成を概略的に示す図である。図13においては、TIC制御性回路562の書込データを生成する部分の構成を併せて示す。

#### [0065]

TIC制御回路 5 6 2 は、テストクロック信号TCLKに従って 8 ビットのテストデータTD < 7 : 0 > を転送するサイクルシフト回路 6 0 0 を含む。このサイクルシフト回路 6 0 0 は、与えられたテストデータTD < 7 : 0 > をテストクロック信号TCLKの所定サイクル期間遅延して出力する。

# [0066]

TIC制御回路 5 6 2 へは、また、 1 3 ビットのアドレス信号 A D < 1 2 : 0 > およびスペアアドレス空間アドレッシング用アドレス信号 A D s p が与えられる。

[0067]

このサイクルシフト回路 6 0 0 から、テストクロック信号 T C L K に同期した 8 ビットのデータ D f < 7 : 0 > が生成される。

[0068]

TICデータパス560eは、データDf<7:0>をそれぞれコピーして8ビットのデータを生成するドライブ回路DRE0-DRE7と、1ビットデータDf<7>をコピーしてスペアデータSD<1>を生成するドライバSDReを含む。

[0069]

ドライブ回路 D R E 0 - D R E 7 は、それぞれ、 8 ビットのドライバを含み、それぞれ 8 ビットデータ D < 6 4 : 7 1 > 、 D < 7 2 : 7 9 > 、…および D < 1 2 0 : 1 2 7 > を生成する。これらの 8 ビットデータ D < 6 4 : 7 1 > 、 D < 7 2 : 7 9 > …および D < 1 2 0 : 1 2 7 > の各々は、データ D f < 7 : 0 > と同じデータパターン有する。

[0070]

ドライバ S D R e は、 1 ビットのドライブ回路で構成され、データ D f < 7 > をバッファ 処理 してスペア書込データ S D < 1 > を生成する。

[0071]

TICデータパス 5 6 0 w は、同様、データ D f < 7:0 > をそれぞれコピーして 8 ビットデータを生成するドライブ回路 D R W 0 - D R W 7 と、データ D f < 7 > をバッファ処理してスペアデータ S D < 0 > を生成するドライバ S D R w を含む。

[0072]

ドライブ回路 D R W 0 - D R W 7 から、それぞれ、 8 ビットデータ D < 7 : 0 > 、 D < 1 5 : 8 > 、…および D < 6 3 : 5 6 > が生成される。 T I C データパス 5 6 0 w から生成されるこれらの 8 ビットデータは、すべて同一パターンを有する。

[0073]

ここで、テストデータ < 7 : 0 > は、データパターンが以下の条件を満たすようにビット幅拡張が行なわれて 1 2 8 ビットのデータが生成される。

[0074]

$D < 8 \cdot n + m > = T D < m >$

ただし、nは0から15の整数であり、またmは、0から7の整数を示す。

[0075]

TICデータパス 5 6 0 e および 5 6 0 w において、データ D f < 7:0 > をコピーすることにより、8 ビット外部データから 1 2 8 ビット内部データを生成して D R A M コアへ伝達することができ、また、D R A M コアへスペアライトデータ S D < 0 > および S D < 1 > を転送することができる。このスペアライトデータ S D < 0 > および S D < 1 > は、テストデータ T D < 7 > と同じ論理レベルを有する。

[0076]

図 1 4 は、図 1 2 に示す T I C  $\vec{r}$  = 9  $\vec{r}$   $\sqrt{2}$   $\sqrt{$

10

20

30

40

20

30

40

50

#### [0077]

TICデータパス560wが、8ビットデータQ <7:0>ないしQ <63:56>それぞれに対応して配置される単位処理回路UPW0・UPW7と、スペア読出データSQ <0>に対して設けられるトライステートバッファ600eを含む。これらの単位処理回路UPW0・UPW7は、同一構成を有し、それぞれ、活性化時対応の8ビットデータQをバッファ処理して内部データTQ f <7:0>を生成するトライステートバッファ回路610と、対応の8ビット内部読出データと期待値データCMPD<7:0>とを比較し、その比較結果を1ビットデータに縮退して出力する比較回路612を含む。

## [0078]

トライステートバッファ回路 6 1 0 は、TIC制御回路 5 6 2 からアドレス信号に従って生成される 1 6 ビット選択信号 Q S E L < 1 5 : 0 > の対応の選択信号 Q S E L に従って活性化される。トライステートバッファ 6 0 0 e は、TIC制御回路からの選択信号 S Q S E L < 0 > に従って選択的に活性化される。

# [0079]

TICデータパス 5 6 0 e は、スペアデータ S Q < 1 > に対して設けられるトライステートバッファ回路 6 0 0 w と、 8 ビットデータ Q < 6 4 : 7 1 > ないし Q < 1 2 0 : 1 2 7 > それぞれに対して設けられる単位処理回路 U P E 0 - U P E 7 を含む。これらの単位処理回路 U P E 0 - U P E 7 も、また 1 6 ビット選択信号 Q S E L < 1 5 : 0 > の対応の選択信号に従って選択的に活性化される。

# [0800]

これらの単位処理回路 UPE 0 - UPE 7 は、それぞれ、活性化時対応の 8 ビットデータをバッファ処理して内部読出データ TQf < 7:0 > を生成するトライステートバッファ回路と、期待値データ CMPD < 7:0 > と対応のデータビットの一致 / 不一致を示すマルチビットテストを行なう比較回路 6 1 2 を含む。

#### [0081]

# [0082]

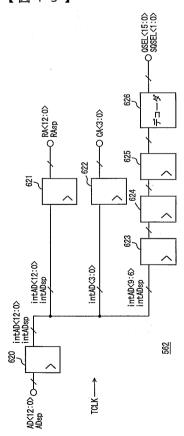

図15は、TIC制御回路562の図14に示す選択信号を発生する部分の構成を概略的に示す図である。図15において、TIC制御回路562は、テストクロック信号TCLKに同期してアドレス信号AD<12:0>およびADspを転送して内部アドレス信号intAD<12:0>およびintADspを生成するフリップフロップ回路620からの内部アドレス信号intAD<12:0>およびintADspを生成するフリップフロップ回路620がらの内部アドレス信号:ntAD<12:0>およびスペアロウアドレッシング用アドレス信号RAspを生成するフリップフロップ回路620からの4ビットのアドレスに同期して転送してコラムアドレス信号 に A < 1 2 : 0 >を生成するフリップフロップ回路622と、フリップフロップ回路622と、フリップフロップ回路622と、フリップフロップ回路622と、フリップフロップ回路620からの4ビットの内部アドレス信号intAD<9:6>およびintAD<9:6>およびintAD<9:6>およびintAD<9:6 >およびintAD<9:6 >およびintAD<9:6 >およびintAD<9:6 >および:1 :0 >を生成するデコーダ626を含む。

## [0083]

デコーダ626の前段に、3段のフリップフロップ回路623-625が配置されている

のは、テストデータ読出時におけるレイテンシに相当する期間、このデコーダ626の出力信号を遅延するためである。レイテンシは、テストインターフェイス回路512からDRAMコア510へデータ読出を指示するリード動作指示信号を与えてからDRAMコア510からテストデータが読出されてテストインターフェイス回路512に転送されるまでに要する時間を示す。ここでは、レイテンシは2が想定されている。

#### [0084]

フリップフロップ回路 6 2 0 - 6 2 5 は、それぞれ、テストクロック信号 T C L K の立上がりに同期して信号を取込みかつ出力する。

## [0085]

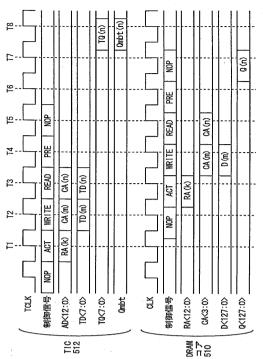

図16は、図12から図15に示すDRAMマクロのテストデータの読出時の動作を示す タイミング図である。以下、図16を参照して、このDRAMマクロのテストデータの読 出動作について説明する。

#### [0086]

テストインターフェイス回路(TIC)512は、外部からの制御信号を、テストクロック信号TCLKの1クロックサイクル遅延してDRAMコア510に転送する。DRAMコア510においては、したがって、テストインターフェイス回路512にテスタから制御信号等が与えられてから2クロックサイクル後のテストクロック信号TCLKの立上がりにおいて制御信号およびアドレス信号を取込み内部動作を実行する。ここで、図16においては、DRAMコア510に与えられるクロック信号CLKとテストクロック信号TCLKとは同一波形の信号であると仮定している。

### [0087]

時刻T1において、テストインターフェイス回路512へ、ロウ活性化ACTを示す制御信号が与えられ、同時に13ビットのロウアドレス信号RA(k)が与えれる。テストインターフェイス回路(TIC)512は、この外部から与えられる制御信号をデコードし、そのデコード結果に従ってDRAMコア510に対するロウ活性化信号/ACTをクロック信号TCLKの立上がりに同期して転送する。図10および図11に示すように、DRAMコア510へ与えられる制御信号は負論理の信号であるが、図16においては、図11に示すニモーニックで動作モード指示信号を示す。

#### [0088]

また、図15に示すように、ロウアドレス信号 R A ( k ) は、テストクロック信号 T C L K の立上がりに同期してフリップフロップ回路 6 2 1 から転送される。

# [0089]

DRAMコア510においては、時刻T3において、クロック信号CLKの立上がりに同期してこのロウ活性化信号ACTをロウアドレス信号RA(k)とともに取込み内部で行選択動作を実行する。

# [0090]

時刻T2において、テストインターフェイス回路(TIC)512に対し、データ書込を示す書込動作指示信号がコラムアドレス信号CA(m)およびテストデータTD(m)とともに与えられ、テストクロック信号TCLKの立上がりに同期してこれらの制御信号、コラムアドレス信号およびテストデータが、テストインターフェイス回路(TIC)512内に取込まれる。

# [0091]

このテストインターフェイス回路(TIC)512内部で、制御信号のデコード動作が行なわれ、DRAMコア510に対する書込動作指示信号WRITE、コラムアドレス信号 СА(m)およびテストデータTD(m)が時刻T3のクロック信号TCLKの立上がりに同期してDRAMコア510へ転送される。

## [0092]

DRAMコア510においては、時刻T4のクロック信号CLKの立上がりに同期して書 込動作指示信号WRITE、コラムアドレス信号CA(m)およびデータD(m)が取込 まれて列選択動作が実行され、コラムアドレスCA(m)により指定された列へ128ビ 20

10

30

40

20

30

40

50

ットのデータD(m)が書込まれる。

# [0093]

時刻T3において、テストインターフェイス回路(TIC)512に対しデータ読出を示すコマンド(READ)がコラムアドレス信号CA(n)とテストデータTD(n)とともに与えられる。このデータ読出時のテストデータTD(n)は、テストインターフェイス回路512のデータパスにおいて比較を行なうための期待値データCMPD<7:0>として用いられる。

# [0094]

時刻T3において、テストインターフェイス回路(TIC)512へ与えられるテストデータTD(n)は、TICデータパスにおいてはライト動作が実行されないため、DRAMコアに対しては転送されない。特に、図16に示すタイミングにおいては、比較データ(期待値データ)は、外部のテスタから与えられたデータをデータ読出時のコラムレイテンシを考慮して内部で所定サイクル期間シフトされて生成され、テストインターフェイス回路(TIC)512内に設けられた比較回路612へ与えられる。したがって、比較データ入力時においては、ライトコマンドにより書込まれる書込データがテストインターフェイス回路(TIC)512内部で転送されてDRAMコアへ転送されるため、テストインターフェイス回路(TIC)512に対してリードコマンドとともに書込データを与えても何ら問題は生じない。

## [0095]

ただし、内部での比較データ生成の遅延段数の制約により、比較データCMPD<7:0 >の入力が、リードコマンド印加よりも早いサイクルにおいて行なうことを要求される場合には、この比較用のデータ入力サイクルにおいてライト動作を行なえないという制約などが生じる。

#### [0096]

時刻T3においてテストインターフェイス回路(TIC)512へ与えられたコマンド(READ)は、テストインターフェイス回路(TIC)512においてデコードされ、リード動作指示信号READが生成され、時刻T4のテストクロック信号TCLKの立上がリエッジに同期してDRAMコア510へリード動作指示信号READとコラムアドレス信号CA(n)が与えられる。なお、コマンドは、先に、図11において示したニモーニックにおいて複数の制御信号の組合せにより与えられる動作モード指示を示すものとして用いる。

# [0097]

DRAMコア510においては、時刻T5におけるクロック信号CLKの立上がリエッジに同期して、このリード動作指示信号READ(/RE)とコラムアドレス信号CA(n)に従って列選択動作が開始され、内部でテストデータの読出が行なわれる。

# [0098]

時刻T4において、テストインターフェイス回路(TIC)512に対しプリチャージ動作を示す制御信号(PRE)が与えられ、テストインターフェイス回路(TIC)512においてこの制御信号がデコードされ、ロウ非活性化信号PREが生成され、DRAMコア510に対し転送される。時刻T6において、DRAMコア510において、このロウ非活性化信号PREが取込まれて内部のプリチャージ動作が実行される。

## [0099]

DRAMコア 5 1 0 において、コラムレイテンシが 2 サイクルであり、時刻 T 5 に与えられたリード動作指示信号 R E A D に従って内部で読出されたデータが、時刻 T 6 から始まるクロックサイクルにおいて読出され、読出データ Q ( n ) がテストインターフェイス回路 ( T I C ) 5 1 2 へ与えられる。

#### [0100]

テストインターフェイス回路(TIC) 5 1 2 においては、この時刻T6から始まるクロックサイクルにおいて、図 1 5 に示すデコーダ 6 2 6 からの選択信号に従ってバッファ回路 6 1 0 を選択的に活性化して、DRAMコア 5 1 0 から転送された 1 2 8 ビットのデー

20

30

40

50

タQ(n)から8ビットデータを生成し、また比較回路612において時刻T3において 取込んだデータTD(n)と読出したデータとの比較を行ない、その比較結果を示す信号 を生成する。これらの8ビットデータの生成および比較結果指示信号の生成が、時刻T7 までに行われる。

## [0101]

時刻T7から始まるクロックサイクルにおいて、テストインターフェイス回路(TIC)5 1 2 が、8 ビットテストデータTQ(n)をマルチビットテスト結果指示信号Qmbt(n)とともに出力する。図15 に示すデコーダ626 およびフリップフロップ回路620・625 は、テストクロック信号TCLKに同期して常時動作している。したがって、図15 に示すアドレス信号intAD<9:6>およびADspを各クロックサイクルにおいて順次与えることにより、デコーダ626 の出力する選択信号QSEL<15:0>およびSQSEL<1:0>に従って8 ビットデータが順次選択されてテストインターフェイス回路(TIC)5 1 2 から読出される。

# [0102]

なお、デコーダ626が、アドレスカウンタを含み、内部でテストクロック信号TCLKに同期してカウント動作を行なって、列アドレスを生成し、その列アドレス信号をデコードして選択信号QSEL<15:0>を生成してもよい。

# [0103]

外部のテスタにおいては、8ビットテストデータTQ(n)に対しマルチビットテスト結果指示信号Qmbt(n)(TQmbt)が不一致を示すときにテスト期待値データTD(n)とテスト読出データTQ(n)を8ビット単位で各ビットごとに比較し、不良メモリセルの位置を特定する。マルチビット結果指示信号TQmbtは、同時に選択された128ビットのデータについての一致/不一致を示す信号であり、マルチビットテスト結果指示信号Qmbt(n)が一致を示している場合には、128ビットテストデータTQ(n)の各ビットはすべて正常であると判定される。

## [0104]

外部のテスタにおいて、各8ビットのテストデータごとに不良メモリセルの位置の特定を すべての8ビットデータについて行なう必要がなく、テスト時間が短縮される。

# [0105]

上述のようなテストインターフェイス回路 5 1 2 を利用することにより、 DRAMコア 5 1 0 を外部からアクセスしてメモリセルの良 / 不良を判定することができる。

# [0106]

DRAMコア510のテスト内容としては、この他に、セットアップ時間、ホールド時間、およびアクセス時間などの測定がある。従来、このようなDRAMコア510の信号のタイミング関係についての試験は以下のようにして行なわれている。

#### [ 0 1 0 7 ]

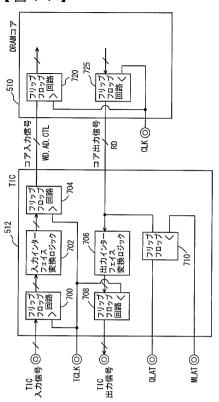

図17はテストインターフェイス回路512およびDRAMコア510の入出力信号の関係を概略的に示すプロック図である。図17において、テストインターフェイス回路(TIC)512は、テストクロック信号TCLKの立上がりに同期してTIC入力信号を取込み転送するフリップフロップ回路700と、このフリップフロップ回路700からの信号/データを、DRAMコアのインターフェイスに応じた信号/データに変換する入力インターフェイス変換ロジック702の出力信号/データをテストクロック信号TCLKの立上がりエッジに同期して取込み転送するフリップフロップ回路704を含む。

#### [0108]

このTIC入力信号は、外部のテスタから与えられるテスト書込データ、アドレス信号、および制御信号(コマンド)を含む。入力インターフェイス変換ロジック702は、テスト書込データのビット幅拡張回路、およびコマンドをデコードして、DRAMコアに対する動作モード指示信号を生成するデコーダを含む。したがって、フリップフロップ回路700は、図15に示すフリップフロップ回路620を含み、またフリップフロップ回路7

20

30

40

50

0 4 は、図 1 5 に示すフリップフロップ回路 6 2 1 および 6 2 2 を含む。

#### [0 1 0 9]

テストインターフェイス回路(TIC)5 1 2 は、さらに、DRAMコア 5 1 0 から読出された信号(読出データ R D)を、出力インターフェイスに応じたデータ / 信号に変換する出力インターフェイス変換ロジック 7 0 6 と、出力インターフェイス変換ロジックの出力信号 / データを、テストクロック信号 T C L K に従って取込み転送して、TIC出力信号を生成するフリップフロップ回路 7 0 8 を含む。

## [0110]

この出力インターフェイス変換ロジック 7 0 6 は、図 1 4 に示す T I C データパスおよび T I C 制御回路 5 6 2 における出力データ T Q < 7 : 0 > およびマルチビットテスト結果 指示信号 T Q m b t を生成する回路部分を含む。

#### [0111]

テストインターフェイス回路(TIC)512は、さらに、外部のテスタからのラッチタイミング信号MLATに従ってDRAMコアから読出されたデータを取込み転送するフリップフロップ710からの出力信号QLATが、テスタへ与えられ、正確に読出されたかの判定が行なわれる。

## [0112]

DRAMコア510においては、その信号 / データ入力部に、クロック信号 CLKの立上がリエッジに同期して与えられた信号 / データを取込むフリップフロップ回路 7 2 0 が設けられる。また、データ出力部においては、このクロック信号 CLKに同期してデータを出力するフリップフロップ回路 7 2 5 が設けられる。DRAMコア510に対する信号 / データのセットアップ / ホールド時間は、このフリップフロップ回路 7 2 0 に与えられるクロック信号 CLKの立上がリエッジに関して測定される。アクセス時間は、フリップフロップ 7 2 5 から読出されたコア出力信号 (読出データ RD)がテストインターフェイス回路 (TIC) 5 1 2 の出力インターフェイス変換ロジック 7 0 6 に到達するまで要する時間で与えられる。

### [0113]

このセットアップ / ホールド時間を測定する場合、テストインターフェイス回路(TIC:以下、単にテストインターフェイス回路と称す)5 1 2 のフリップフロップ回路 7 0 4 から、メモリ書込データW D、アドレス信号 A D および制御信号 C T L がテストクロック信号 T C L K に同期して転送されるため、このテストクロック信号 T C L K とフリップフロップ回路 7 2 0 へ与えられるクロック信号 C L K の位相をずらせることにより測定される。

# [0114]

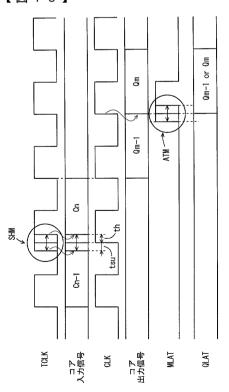

図18は、このセットアップ / ホールド時間およびアクセス時間などの信号パラメータの 測定動作を示すタイミング図である。以下、図18を参照して、図17に示すテストイン ターフェイス回路512における信号パラメータ測定動作について説明する。

## [0115]

セットアップ / ホールド時間の測定時においては、図18において波形SHMで示すように、テストクロック信号TCLKの位相を、クロック信号CLKに対して変化させる。すなわちDRAMコア510においてフリップフロップ回路720が信号 / データを取込むクロック信号CLKのエッジに対し、テストクロック信号TCLKの位相の進み具合を変化させ、セットアップ時間tsuの測定時においては、バイナリサーチ方式に従ってDRAMコア510のセットアップ時間の測定が行なわれる。このバイナリサーチ方式に従ったセットアップ時間の測定においては、以下の手順でセットアップ時間の測定が行なわれる。すなわち、すべてのDRAMコアが正常に動作するセットアップ時間(最大測定値と称す)とすべてのDRAMコアが誤動作するセットアップ時間(最大測定値と称す)とすべてのDRAMコアが誤動作するセットアップ時間(のが正常に動作するかを測定する。正常に動作する場合には、この初期値と最小測定値

の中間値を第2測定値としてDRAMコア510を動作させて、正常に動作するかを測定する。その測定結果に従って次の測定値を設定する。すなわち正常に動作する場合には、第2測定値と最小測定値の中間値を用いてさらに測定を行ない、誤動作が生じている場合には、第2測定値と初期値との中間値を用いて測定する。以下この測定動作を繰返し実行し、DRAMコア510が正常に動作するセットアップ時間と誤動作するセットアップ時間との境界値を求め、この境界値をDRAMコア510のセットアップ時間とする。

#### [ 0 1 1 6 ]

ホールド時間 t h についても同様であり、テストクロック信号TCLKの位相をクロック信号CLKに対して遅らせることにより、図18に示すコア入力信号Cn-1のホールド時間 t h を変化させる。同様、このホールド時間に対しては、テストクロック信号TCLKのクロック信号CLKに対する位相遅れ量をバイナリサーチ方式に従って調整してホールド時間 t h を測定する。

#### [0117]

アクセス時間の測定においては、DRAMコア510から、この同一半導体基板上に搭載されるロジック502までの読出データの伝達時間を測定する必要がある。したがって、この場合には、フリップフロップ710を用い、DRAMコア510のフリップフロップ回路725からの読出データの特定のビットを、外部テスタからのラッチタイミング信号MLATの位相を変化させて、目標データが読出されたかを測定する。すなわち、図18において、波形ATMで示すように、クロック信号CLKの立上がリエッジに対し、ラッチタイミング信号MLATの位相を変更して、フリップフロップ710からの出力データQLATが、データQm・1であるかデータQmであるかを識別し、目標データQmが正常に読出されるアクセス時間と、データQm・1が読出されるアクセス時間の境界値をバイナリサーチ方式に従って求め、このDRAMコア510のアクセス時間を測定する。

#### [0118]

## 【発明が解決しようとする課題】

図18においては、クロック信号 C L K およびテストクロック信号 T C L K を同一波形の信号としている。これらのクロック信号 C L K および T C L K およびラッチタイミング信号 M L A T は、外部のテスタから印加される。これらの信号 C L K、 T C L K および M L A T の位相関係は、外部のテスタで決定することができ、各設定された位相差に応じて、バイナリサーチ方式に従ってセットアップ / ホールド時間およびアクセス時間を測定することができる。

# [0119]

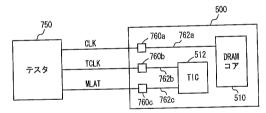

図19は、外部に設けられたテスタ750とDRAM内蔵システムLSI(半導体集積回路装置)500の間の信号CLK、TCLKおよびMLATの転送経路を概略的に示す図である。図19において、システムLSI500においては、パッド760a、760bおよび760cに、それぞれクロック信号CLK、テストクロック信号TCLKおよびラッチタイミング信号MLATを受ける。パッド760aに与えられたクロック信号CLKは内部配線762aを介してDRAMコア510へ転送される。パッド760bに与えられたテストクロック信号TCLKは内部配線762bを介してテストインターフェイス回路(TIC)512へ転送され、パッド760cへ転送されたラッチタイミング信号MLATは、内部配線762cを介してテストインターフェイス回路512へ転送される。

#### [ 0 1 2 0 ]

これらの内部配線762a、762bおよび762cは、それぞれ配線長が異なり、また負荷も異なるため、それぞれの信号伝搬遅延量が異なる。また、パッド760a、760bおよび760cは、パッケージ実装時にはリードフレームへボンディングワイヤを介して接続される。したがって、このリードフレームとパッド760a、760bおよび760cの間の配線長が異なる場合、同様、信号伝搬遅延が異なる。

#### [0121]

したがって、外部のテスタ750において、設定した信号CLK、TCLKまたはMLA Tの相対的なタイミング関係が、このシステムLSI500内部での信号伝搬遅延量が異 10

20

30

40

なるため、相対的な位相関係が設定時と異なり、正確なセットアップ時間、ホールド時間 またはアクセス時間を測定することができなくなるという問題が生じる。

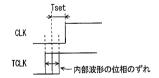

#### [0122]

図20に示すように、たとえばテストクロック信号TCLKのクロック信号CLKに対する設定位相変化量Tsetに対し、信号伝搬遅延のずれにより内部波形の位相がずれた場合、この補正を行なうためには、内部信号波形を、オシロスコープ等の装置を用いて測定して、予め補正値を測定する必要がある。しかしながら、1つのデバイスについて補正値を測定しても、ユーザロジックが異なる他の種類のデバイスにおいては、パッド配置またはフレームが異なり、この補正値を使用することができない。また、同一種類のデバイスであっても、内部配線の抵抗値/容量値の製造工程時のバラツキにより、1つのデバイスについて測定された補正値を利用することはできない可能性がある。

[0123]

また、モールド樹脂等のパッケージ実装後においては、内部波形を全く観測することができず、補正値の測定自体を行なうことができない。

### [0124]

特に、仕様値の条件が厳しくなる高速クロック信号に同期して動作する場合、セットアップ時間、ホールド時間およびアクセス時間を高精度で測定することができない場合には、DRAMマクロ単体試験で、不良デバイスをスクリーニングすることができない。この場合、最終製品に、不良DRAMマクロが組込まれることになり、最終製品試験での歩留りが低下し、製品コストが高くなるという問題が生じる。

[0125]

それゆえに、この発明の目的は、内蔵クロック同期型メモリの内部信号タイミングを高精度で測定することのできる半導体回路装置を提供することである。

[ 0 1 2 6 ]

この発明の他の目的は、内蔵メモリのセットアップ / ホールド時間 / またはアクセス時間を正確に測定することのできるテストインターフェイス回路を提供することである。

[0127]

この発明のさらに他の目的は、高精度で不良内蔵DRAMコアをスクリーニングし、最終製品の歩留りを改善することのできるテストインターフェイス回路を提供することである

[0128]

【課題を解決するための手段】

この発明の第1の観点に係る半導体回路装置は、メモリクロック信号に同期して動作するメモリコアと、テストクロック信号に同期して、メモリコアへ信号 / データを転送するメモリ転送回路と、少なくともメモリクロック信号およびテストクロック信号を受け、メモリクロック信号およびテストクロック信号の一方を選択するタイミング選択回路と、この選択回路の出力信号を補正用テストクロック信号に同期して取込み外部へ転送するタイミング転送回路とを含む。

[0129]

好ましくは、ラッチタイミング信号に同期して、メモリコアから転送された信号 / データを外部へ転送するラッチ転送回路が設けられる。タイミング選択回路は、メモリクロック信号およびテストクロック信号とラッチタイミング信号のいずれかを選択指示信号に応答して選択する。

[0130]

このタイミング選択回路の入力からタイミング転送回路の出力までのメモリクロック信号 およびテストクロック信号およびラッチタイミング信号の遅延時間は実質的に同じである

[0131]

好ましくは、メモリ転送回路は、メモリコアに対して多ビットデータを転送するデータ転 送回路を含む。この構成において、さらに、データ転送回路と同一特性を有するレプリカ 10

20

30

40

回路と、メモリクロック信号とレプリカ回路の出力信号の一方を選択するテストデータ選択回路と、補正用クロック信号に同期してテストデータ選択回路の出力信号を転送するテストデータ転送回路が備けられる。

### [0132]

好ましくは、テストデータ転送回路とタイミング転送回路は、補正用クロック信号に同期 して与えられた信号を取込みラッチするラッチ回路を共有する。

#### [0133]

これに代えて、好ましくは、タイミング転送回路とテストデータ転送回路とは、それぞれ 別々に配置されて、補正用クロック信号に同期して動作するラッチ回路を備える。

# [0140]

メモリクロック信号とテストクロック信号の一方を選択して、補正用クロック信号に同期して転送することにより、外部のテスタにおいて、補正用クロック信号に対するテストクロック信号およびメモリクロック信号の相対的位相を検出することができ、応じてメモリクロック信号とテストクロック信号との位相差を検出することができる。この位相差を用いることにより、セットアップ時間、ホールド時間またはアクセス時間の測定値を補正することができ、高精度でセットアップ時間、ホールド時間またはアクセス時間を測定することができる。

# [0141]

また、データ転送回路と同一の転送特性を有するレプリカ回路の出力信号とメモリクロック信号を選択的に補正用クロック信号に同期して転送することにより、外部テスタにおいて書込データとメモリクロック信号の位相差を補正用クロック信号を基準として検出することができ、書込データについてのセットアップ時間およびホールド時間を高精度で補正することができ、応じてセットアップ時間またはホールド時間を高精度で測定することができる。

## [0142]

また、ラッチタイミング信号とメモリクロック信号の一方を補正用クロック信号に同期して転送することにより、ラッチタイミング信号とメモリクロック信号との位相差を検出することができ、アクセス時間の測定値を正確に補正して正確なアクセス時間を決定することができる。

# [0143]

【発明の実施の形態】

# [実施の形態1]

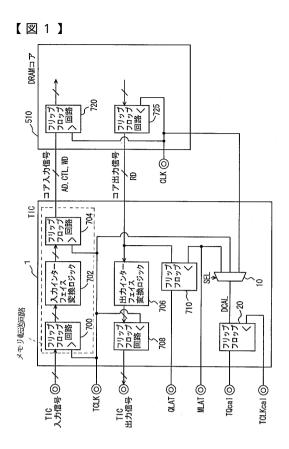

図1は、この発明の実施の形態1に従うテストインターフェイス回路の構成を概略的に示す図である。この図1に示すテストインターフェイス回路(TIC)1は、以下の点において、図19に示すテストインターフェイス回路512と構成が異なる。フリップフロップ回路700、入力インターフェイス変換ロジック702およびフリップフロップ回路704により、メモリコア(DRAMコア)に信号/データを、テストクロック信号TCLKに同期して転送するメモリ転送回路が構成される。

# [0144]

すなわち、ラッチタイミング信号MLATとテストクロック信号TCLKとクロック信号CLKの1つを選択信号SELに従って選択する選択回路10と、この選択回路10の出力信号DCALを補正用テストクロック信号TCLKcalに従って取込み転送するフリップフロップ20が設けられる。フリップフロップ20の出力信号TQcalが、外部のテスタへ与えられる。この図1に示すテストインターフェイス回路1の他の構成は、図17に示すテストインターフェイス回路512の構成と同じであり、対応する部分には同一参照番号を付し、その詳細説明は省略する。

#### [0145]

選択信号SELは、図示しないテストモードレジスタ内に、外部のテスタの制御の下に設定されたデータに基づいて生成される。選択信号SELは、レジスタの格納データをデコードして生成されてもよく、また、レジスタ内のデータ自体が選択信号として用いられて

10

20

30

40

もよい。

## [0146]

フリップフロップ 2 0 は、補正用テストクロック信号TCLKcalの立上がりエッジに同期して選択回路 1 0 の出力信号DCALを取込みラッチし、かつテストクロック信号TCLKcalの立上がりエッジで出力信号TQcalを出力する構成であれば、任意の構成を利用することができる。例えば、相補クロック信号に同期して動作する二段の従属接続されるラッチ回路でフリップフロップ 2 0 を構成することができる。

## [0147]

また、補正用のデータTQca1を出力する端子および補正用テストクロック信号TCLKca1を入力する端子は、図示しないテストモードレジスタの設定により、他のピン端子(たとえばTIC入力信号またはTIC出力信号)の端子と切換えて用いられてもよい。またテストインターフェイス回路1において、これらの補正用データTQcalおよび補正用テストクロック信号TCLKcal専用のピン端子が設けられてもよい。

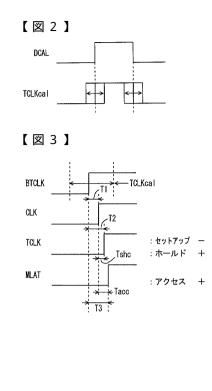

## [0148]

図 2 は、この図 1 に示すテストインターフェイス回路 1 の動作を示すタイミング図である。以下、図 2 を参照して、図 1 に示すテストインターフェイス回路 1 の動作について説明する。

# [0149]

選択回路10は、選択信号SELに従って、ラッチタイミング信号MLAT、クロック信号CLKおよびテストクロック信号TCLKのいずれかを選択して、その出力信号DCALを生成する。補正用テストクロック信号TCLKcalの立上がリタイミングを、外部テスタの制御の下に変化させる。フリップフロップ20は、この補正用テストクロック信号TCLKcalの立上がリエッジで、選択回路10の出力信号DCALを取込みラッチし、補正用データTQcalを生成する。このデータTQcalを外部テスタへ転送し、外部のテスタにおいて、バイナリサーチ方式に従って、この選択回路10の出力信号DCALの立上がリエッジまたは立下がリエッジを検出する。この選択信号SELを順次切換えて、補正用テストクロック信号TCLKcalにより、ラッチタイミング信号MLAT、テストクロック信号TCLKおよびクロック信号CLKの遷移エッジを検出する。

# [0150]

図3は、ラッチタイミング信号MLAT、テストクロック信号TCLKおよびクロック信号CLKの位相関係の一例を示す図である。図3に示すように、テスタにおいては、基本テストクロック信号BTCLKを基準として、補正用テストクロック信号TCLKcalの位相を変化させて、このテストインターフェイス回路1へ与えている。したがって、この補正用テストクロック信号TCLKcalのテスト基本クロック信号BTCLKに対する相対的な位相を用いて、選択回路10の出力信号DCAL、すなわちラッチタイミング信号MLAT、テストクロック信号TCLKおよびクロック信号CLKの遷移エッジの相対的な位相関係を検出することができる。図3においては、クロック信号CLK、テストクロック信号TCLK、およびラッチタイミング信号MLATの立上がリエッジが、基本テストクロック信号BTCLKの立上がリエッジに対し、それぞれ、時間T1、T2およびT3だけ遅れている。

# [0151]

したがって、テストクロック信号TCLKとクロック信号CLKの位相差Tshcは、時間T2-T1で与えられ、ラッチタイミング信号MLATとクロック信号CLKの位相差Taccは、時間T3-T1で与えられる。

#### [0152]

この図3に示すように、テストクロック信号TCLKとクロック信号CLKの位相差Tshcが正の場合、実際には、DRAMコアに対して転送される信号の転送タイミングが、時間Tshcだけ遅れている。したがって、実際のセットアップ時間は、テスタにおける設定値よりも時間Tshcだけ短くなる。一方、ホールド時間の測定時においては、時間Tshcだけホールド時間が長くなる。したがって、セットアップ時間測定時においては

10

20

30

40

20

30

40

50

、このテストクロック信号TCLKとクロック信号CLKの位相差Tshcを測定値から減算し、ホールド時間測定時には、この位相差Tshcを測定値に加算することにより、 実際のセットアップ時間およびホールド時間を求めることができる。

#### [0153]

アクセス時間については、図3に示すタイミングにおいては、ラッチタイミング信号MLATの立上がリエッジが、クロック信号CLKに対して時間Tacc遅れており、実際には、DRAMコア510からのデータの転送時間が時間Taccだけ長くなっている。

# [0154]

テストインターフェイス回路512からは、テストクロック信号TCLKの立上がりに同期してデータが転送される。テストクロック信号TCLKは、クロック信号CLKに対して時間T1遅れている。しかしながら、クロック信号の立上り時においてDRAMコア510においてデータ読出が実行される。従って、アクセス時間の測定時には、テストクロック信号TCLKとクロック信号CLKとの位相差を考慮する必要がなく、クロック信号CLKとラッチタイミング信号との位相関係が測定されれば、アクセス時間を補正することができる。したがって、テスタにおける設定値に比べて、実際のアクセス時間を、この位相差(時間)Taccを測定値に加算することにより求めることができる。

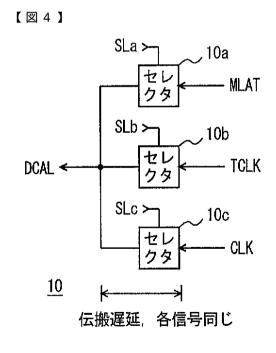

# [ 0 1 5 5 ]

図4は、図1に示す選択回路10の構成を概略的に示す図である。図4において、選択回路10は、選択信号SLaの活性化時選択され、ラッチタイミング信号MLATに従って出力信号DCALを生成するセレクタ10aと、選択信号SLbの活性化時選択され、テストクロック信号TCLKに従って出力信号DCALを生成するセレクタ10bと、選択信号SLcの活性化時選択され、クロック信号CLKに従って出力信号CALを生成するセレクタ10cを含む。

#### [0156]

これらのセレクタ10a-10cの各々は、CMOSトランスミッションゲートで構成されてもよく、またトライステートバッファ回路で構成されてもよい。セレクタ10a-1 0cは、非選択時には、出力ハイインピーダンス状態に設定される。

# [0157]

この選択回路10において、セレクタ10a‐10cそれぞれにおいて、入力部から出力部の信号伝搬遅延はすべて同じである。したがって、ラッチタイミング信号MLAT、テストクロック信号TCLKおよびクロック信号CLKの伝搬遅延が同じでありる。また、次段においては、共通のフリップフロップ20を用いてこの選択回路10の出力信号DCALを転送しており、これらの信号MLAT、TCLKおよびCLKの伝播遅延は同一である。したがって、セレクタ10およびフリップフロップ20の伝搬遅延の影響を受けることなく正確に、これらの信号MLAT、TCLKおよびCLKの相対的な位相関係を正確に求めることができる。

## [0158]

以上のように、この発明の実施の形態 1 に従えば、テストインターフェイス回路内部においてテストクロック信号とクロック信号とテストタイミングクロック信号を補正用のテストクロック信号により取込んで転送し、外部のテスタにおいて、この補正用テストクロック信号を基準として各信号の相対的位相を検出しており、このテストインターフェイス回路内において実際に生じている各信号の位相差を検出することができ、高精度でセットアップ時間、ホールド時間およびアクセス時間を補正することができる。これにより、正確にセットアップ時間、ホールド時間およびアクセス時間を測定することができ、セットアップ異常などを検出することができ、製品歩留りの低下を抑制することができる。

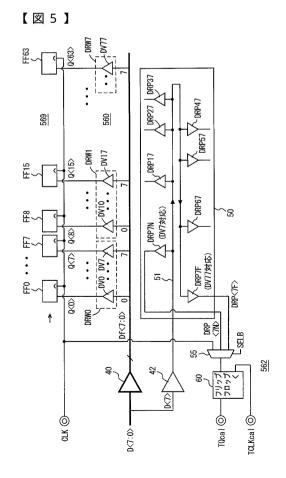

## [0159]

# 「実施の形態21

図 5 は、この発明の実施の形態 2 に従うテストインターフェイス回路の要部の構成を概略的に示す図である。図 5 において、TICデータパス 5 6 0 ( 5 6 0 e または 5 6 0 w )

20

30

40

50

においては、それぞれ8ビットデータを転送するためのバスドライブ回路DRW0-DRW7が設けられる。これらのドライブ回路DRW0-DRW7に対し、データを転送するために、大きな駆動力を有するバッファ回路40が設けられ、このバッファ回路40により、8ビットデータD<7:0>から8ビットデータDf<7:0>を生成して、バスドライブ回路DRW0-DRW7へ伝達する。バスドライブ回路DRW0-DRW7のそれぞれは、8ビットのドライバを有しており、バスドライブ回路DRW0は、ドライバDV0-DV7を有し、バスドライブ回路DRW7は、ドライバDV70-DV77を有する。

[0160]

これらのドライバ D V 0 - D V 7、 D V 1 0 - D V 1 7 ... D V 7 7 に対応して、 D R A M データパス 5 6 9 ( 5 6 9 e または 5 6 9 w ) において、 フリップフロップ F F 0 - F F 6 3 が設けられる。このフリップフロップ F F 0 - F F 6 3 に対し、 クロック信号 C L K が与えられる。

[0161]

したがって、このDRAMコアに対する書込データWDについては、ビット幅拡張動作のために、他の制御信号およびアドレス信号の信号伝播経路と、信号転送経路に設けられるバッファ回路の段数および配線遅延が異なるため、先の実施の形態 1 と異なる手法を用いてセットアップ / ホールド時間を測定する。

[0162]

すなわち、図5に示すように、TIC制御回路562において、バッファ回路40に含まれるバッファと同じ伝達特性を有するバッファ42と、バスドライブ回路DRW0-DR W7と同じ転送特性を有し、このバッファ42の出力信号に従って、バスドライブ回路DRW0-DRW7と同一転送タイミングで信号を生成するレプリカ回路50を設ける。

[ 0 1 6 3 ]

このバッファ40は、テストデータD < 7 > を受ける。レプリカ回路50においては、バスドライブ回路DRW0-DRW7における最も遅延の大きい(バッファ回路40から遠い)ドライバDV7、DV17、…DV77に対応して、バッファDRP7N、DRP17、DRP27、DRP37、DRP57、DRP67およびDRP7Fを設ける。レプリカバッファDRP7Nは、バスドライブ回路DRW0のドライバDV7に対応し、レプリカバッファDRP7Fは、バスドライブ回路DRW7のドライバDV77に対応する。

[0164]

レプリカ回路 5 0 において、バッファ 4 2 の出力信号を転送する信号線 5 1 を、その中央部付近で折返す構造とし、データバスの最遠点に対応して配置されるドライバ D V 7 7 に対応するレプリカバッファ D R P 7 F を、レプリカ回路 5 0 の入力部に配置する。レプリカ回路 5 0 の入力部近傍から、バスドライブ回路の最遠点に配置されたドライバ D V 7 7 の出力するデータと実質的に同じタイミングでデータを出力することができる(信号線 5 1 を直線状に配置した場合、遠方のドライバ D R P 7 F の出力信号をレプリカ回路 5 0 の入力部にまで伝達するための信号伝播遅延が生じ、正確な測定ができない)。

[0165]

レプリカ回路 5 0 において、データビット D < 7 > に対するドライバに対応するレプリカバッファ D R P 7 N - D R P 7 F を配置しているのは、信号線 5 1 の負荷をドライブ回路 4 0 のドライバの出力負荷と同一とするためである。また。データビット D < 7 > を利用するのは、以下の理由による。すなわち、バスドライブ回路 D R W 0 - D R W 7 それぞれにおいて、データ到達の遅延時間が最も大きくなるのはバッファ回路 4 0 から遠いドライバであり、このドライバにおいて、セットアップ時間が各バスドライブ回路 D R W 0 - D R W 7 において最悪ケースとなる。最悪ケースに対してセットアップ時間を測定する必要があるためである。

[0166]

このTIC制御回路562において、さらに、選択信号SELBに従ってクロック信号C

L K とレプリカ回路 5 0 のレプリカバッファ D R P 7 N および D R P 7 F の出力信号の 1 つを選択するセレクタ 5 5 と、このセレクタ 5 5 の出力信号を補正用テストクロック信号 T C L K c a 1 の立上がりに同期して取込み転送するフリップフロップ 6 0 が設けられる。このフリップフロップ 6 0 の出力信号 T Q c a 1 がデータに対する位相補正用の信号として外部テスタへ与えられる。

#### [0167]

なお、レプリカ回路 5 0 において、レプリカバッファ D R P 7 N および D R P 7 F の出力信号を用いているのは以下の理由による。

#### [0168]

セットアップ時間は、クロック信号CLKの立上がりに対して、入力データが確定状態にある時間を示し、ホールド時間は、クロック信号CLKの立上がりエッジ後のデータの確定状態の保持時間を示す。したがって、セットアップ時間については、信号の遅延の最も大きなドライバDV77の出力信号が最悪ケースを示す。また、同様、このデータビットD<7>について、ホールド条件が最悪ケースとなるのは、データビットD<7>について遅延時間が最も短いドライバDV7である。したがって、ホールド時間についての最悪ケースとなるレプリカバッファDRP7Fの出力信号を用いてクロック信号CLKとの位相差を外部のテスタで測定する。

# [0169]

ホールド条件の厳密な意味での最悪ケースは、データバスドライブ回路 DRW 0 - DRW 7 において最も遅延の小さなドライバ DV 0 である。したがって、ホールド条件に対するクロック補正のために、データビット D < 0 > に対して、このレプリカ回路 5 0 と同様の構成を設け、その最小遅延のレプリカバッファの出力信号を選択してもよい。

# [0170]

しかしながら、この図5に示すレプリカ回路50の構成において、ドライブ回路DRW0において、ドライバDV0-DV7に対する信号の遅延時間が、ほぼ無視することができる程度であれば、このレプリカバッファDRP7Nを用いて、最悪ケースのホールド時間に対するクロック補正を正確に行なうことができる。また、データビットD<7>に対するレプリカ回路50を設けるだけで、ホールド条件に対するクロック補正およびセットアップ条件に対するクロック補正両者を行なうことができ、回路占有面積を低減することができる。

# [0171]

なお、選択回路55に対する選択信号SELBは、図示しないテストモードレジスタに外部のテスタの制御の下に設定されて、クロック信号CLK、およびレプリカバッファDRP7NおよびDRP7Fの出力信号が選択される。この選択回路55においても、その入力部から出力部までの各信号についての遅延はすべて同じである。

#### [ 0 1 7 2 ]

補正用テストクロック信号TCLKcalは、先の実施の形態1において用いられた補正用テストクロック信号TCLKcalと同じである。

# [0173]

以上のように、この発明の実施の形態 2 に従えば、テストデータを転送経路と同じ転送特性を有するレプリカ回路を用い、そのレプリカ回路の出力信号とメモリクロック信号を補正用テストクロック信号に従って取込んで、これらのクロック信号およびテストデータの位相のずれを測定しており、正確に、書込データについても、セットアップ条件、およびホールド条件を正確に測定することができる。

## [0174]

# [実施の形態3]

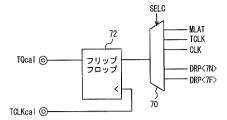

図6は、この発明の実施の形態3に従うテストインターフェイス回路の要部の構成を概略的に示す図である。図6において、このテストインターフェイス回路においては、選択信号SELCに従って、ラッチタイミング信号MLAT、テストクロック信号TCLK、クロック信号CLK、図5に示すレプリカバッファDRP7Nの出力信号DRP<7N>、

10

20

30

40

20

30

40

50

およびレプリカバッファDRP7Fの出力信号DRP<7F>の出力信号の1つを選択する選択回路70と、選択回路70の出力信号を補正用テストクロック信号の立上がリエッジに同期して取込み転送するフリップフロップ72とが設けられる。このフリップフロップ72の出力信号TQcalが外部のテスタへ与えられる。選択信号SELCは、図示しないテストモードレジスタに、外部のテスタの制御の下に格納される。

### [ 0 1 7 5 ]

選択回路70の各信号についての入力部から出力部までの信号伝播遅延は同じである。選択回路70の出力信号が共通のフリップフロップ72を介して転送される。従って、これらの信号MLAT、TCLK、CLK、DRP<7N>およびDRP<7F>のこの経路における信号伝播遅延は全て等しい。選択信号SELCを用いて各信号の補正テストクロック信号TLCKcalを基準とする相対的な位相を検出することができる。検出動作は先の実施の形態1および2と同様である。

#### [0176]

この図 6 に示す構成の場合、選択回路 7 0 およびフリップフロップ 7 2 を用いて、信号およびデータのセットアップ時間、ホールド時間、およびアクセス時間の補正を行なうことができ、回路占有面積を低減することができる。

#### [0177]

#### 「変更例 ]

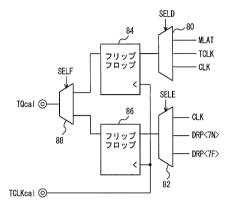

図7は、この発明の実施の形態3の変更例のテストインターフェイス回路の要部の構成を概略的に示す図である。この図7に示すテストインターフェイス回路の構成においては、選択信号SELDに従ってラッチタイミング信号MLAT、テストクロック信号TCLKおよびクロック信号CLKの1つを選択する選択回路80と、選択信号SELEに従ってクロック信号CLKと、レプリカバッファDRP7Nの出力信号DRP<7N>とレプリカバッファDRP7Fの出力信号DRP<7F>の1つを選択する選択回路82が設けられる。これらの選択回路80および82は、それぞれ、図1に示す選択回路10および図5に示す選択回路55に対応する。

### [0178]

テストインターフェイス回路において、さらに、選択回路80の出力信号を補正用テストクロック信号TCLKcalの立上がりエッジに同期して取込み転送するフリップフロップ84と、選択回路82の出力信号を補正用テストクロック信号TCLKcalの立上がりエッジに同期して転送するフリップフロップ86と、選択信号SELFに従ってフリップフロップ84および86の出力信号の一方を選択する選択回路88が設けられる。選択回路88から、外部テスタに対する補正用データTQcalが出力される。

# [0179]

選択回路80および82の各信号についてその入力部から出力部までの信号伝播遅延は同一であり、また、フリップフロップ84および86の動作特性、特に補正用テストクロック信号TCLKcalに対する応答特性も同じである。

## [0180]

この図 7 に示すテストインターフェイス回路の構成においては、実施の形態 1 および 2 の構成がそれぞれ別々に設けられる。したがって、レプリカ回路 5 0 の配置位置に応じて、選択回路 8 2 およびフリップフロップ 8 6 を配置することができ、回路レイアウトの自由度が改善される。

# [0181]

また、この図7に示す構成において、選択回路82により、クロック信号CLKおよびレプリカバッファの出力信号DRP<7N>およびDRP<7F>の1つを選択することにより、同じ経路を介してクロック信号CLK、レプリカバッファ出力信号DRP<7N>およびDRP<7F>が転送されるため、正確に、これらのクロック信号と書込データとの位相差を検出することができる。しかしながら、フリップフロップ84および86の伝送特性の相違を無視することができる程度であれば、この選択回路82は、選択信号SELEに従ってレプリカバッファDRP<7N>およびDRP<7F>の一方を選択する構

成とされてもよい。

## [0182]

以上のように、この発明の実施の形態3に従えば、ラッチタイミング信号MLAT、テストクロック信号TCLK、クロック信号CLK、およびレプリカバッファ出力信号DRP<フN>およびDRPマフF>を選択して、補正用テストクロック信号TCLKcalの立上がリエッジに同期して取込み転送しており、正確に、この補正用テストクロック信号を基準として、各信号 / データの位相差を検出することができ、正確にセットアップ時間、ホールド時間、およびアクセス時間を、信号およびデータについて測定することができる。

# [0183]

10

# [他の適用例]

上述の説明においては、同一半導体チップ上にロジックと混載されるDRAMのテストインターフェイス回路について説明している。しかしながら、このメモリとしては、ロジックと混載されるメモリであればよく、DRAMに限定されない。たとえば他のクロック同期型のSRAM(スタティック・ランダム・アクセス・メモリ)または不揮発性メモリであってもよい。すなわち、本発明、内蔵クロック同期型メモリに対するテストインターフェイス回路に対して適用することができる。

### [0184]

また、テストインターフェイス回路 5 1 2 においては、信号 / データの入力部および出力部にフリップフロップが配置されており、クロック信号の立上りで外部信号 / データを取込みかつクロック信号の立ち上がりで信号 / データを転送している。しかしながら、入力部と出力部とに相補的に動作するラッチ回路を配置し、外部信号 / データをクロック信号の立上りに同期して取込み、クロック信号の立下りに同期して信号 / データを転送してもよい。 DRAMコアは、この構成において、クロック信号の立上りに同期して信号 / データを取込む。

## [0185]

### 【発明の効果】

以上のように、この発明に従えば、内蔵クロック同期型メモリのテストインターフェイス 回路において、内部信号 / データと内部クロック信号との位相のずれを測定することがで きるようにしており、正確に内蔵メモリの信号パラメータを測定することができ、製品歩 留りを改善することができる。

30

20

# [0186]

すなわち、メモリへの信号転送タイミングを決定するテストクロック信号とメモリの信号 取込みタイミングを決定するメモリクロック信号との補正テストクロック信号に対する相 対的な位相を検出するように構成することにより、この補正用テストクロック信号を基準 としてテストクロック信号とメモリクロック信号との実際の位相差を検出することができ 、信号タイミングの測定値を高精度で補正することができ、セットアップ時間などのタイ ミング条件を高精度で測定することができる。

# [0187]

また、メモリから転送された信号を取込むタイミングを与えるラッチタイミング信号に対して、補正用テストクロック信号に対する相対的な位相を検出するように構成することにより、メモリから読出されたデータに対するアクセス時間の補正値を高精度で検出することができ、正確にアクセス時間を測定することができる。

[0188]

また、このラッチタイミング信号、メモリクロック信号およびテストクロック信号を選択する選択回路の各信号についての入力から出力までの遅延時間をすべて同じとすることにより、高精度で実際の各信号間の位相差を検出することができる。

#### [0189]

また、テストデータ転送回路とタイミング転送回路とに対し共通に、補正テストクロック 信号に同期して与えられた信号を取込み転送するラッチ回路を配置することにより、同一

50

経路を介して補正用テストクロック信号に従って選択された信号を転送することができ、 正確に相対的な位相を検出することができる。

#### [0190]

また、テストデータ転送回路とタイミング転送回路とに対し別々に、補正テストクロック 信号に同期して与えられた信号を取込み転送するラッチ回路を配置することにより、各信 号の伝播経路に応じてラッチ回路を最適配置することができる。

#### [0191]

また、メモリに対するデータ転送回路と同一転送特性を有するレプリカ回路を設け、このレプリカ回路の出力信号を補正用テストクロック信号に同期して取込み転送することにより、データバスの負荷が大きく、他の信号と伝送特性が異なる場合においても、正確に、書込データに対するセットアップ時間およびホールド時間に対する補正値を検出することができる。

#### [0192]

また、レプリカ回路において、所定のテストデータビットについての最小遅延および最大遅延のバスドライバそれぞれに対応するレプリカドライバを配置し、このレプリカドライバの出力信号について、補正用テストクロック信号に対する相対的位相を検出することにより、書込データに対するホールド時間およびセットアップ時間に対する補正値を高精度で検出することができる。

#### [ 0 1 9 3 ]

また、レプリカ回路において、バス信号線に接続されるバスドライバと同数のレプリカドライバレプリカ信号線に接続し、レプリカ信号線の負荷をバス信号線と同一とすることができ、また、このレプリカ信号線を折返し構造とすることにより、セットアップ時間測定のための最大遅延のレプリカバッファの出力信号をレプリカ回路入力部から出力することができ、直線構造のレプリカバス信号線の構成に比べて、この信号伝搬遅延を、正確に、メモリへの書込データを転送するバスドライバと同じとすることができ、正確にメモリクロック信号と書込データとの位相差を検出することができる。

### [0194]

また、メモリ転送回路のバスドライバを複数のグループに分割し、レプリカ回路において、各グループの同一ビットのバスドライバに対応してレプリカドライバを配置することにより、正確に、セットアップ / ホールド時間に対する最悪ケースを用いて、補正値を検出することができる。

# [0195]

また、メモリコアから転送された信号 / データを取込むタイミングを与えるラッチタイミング信号とメモリクロック信号をそれぞれ補正用テストクロック信号にしたがって転送することにより、メモリクロック信号とラッチタイミング信号との位相差を検出することができ、正確に測定アクセス時間を補正して、正確なアクセス時間を検出することができる

## [0196]

また、メモリクロック信号とラッチタイミング信号の一方を選択回路に従って選択し、この選択回路の出力信号を補正用テストクロック信号に従って転送することにより、正確に補正用テストクロック信号に対する各信号の相対的な位相を検出することができる。

#### 【図面の簡単な説明】

【図1】 この発明の実施の形態1に従うテストインターフェイス回路の構成を概略的に示す図である。

- 【図2】 図1に示すテストインターフェイス回路の動作を示すタイミング図である。

- 【図3】 この発明の実施の形態1におけるセットアップ時間、ホールド時間およびアクセス時間の補正動作を示す図である。

- 【図4】 図1における選択回路の構成を概略的に示す図である。

- 【図5】 この発明の実施の形態2に従うテストインターフェイス回路の要部の構成を概略的に示す図である。

10

20

30

40

20

30

- 【図 6 】 この発明の実施の形態 3 に従うテストインターフェイス回路の要部の構成を概略的に示す図である。

- 【図7】 この発明の実施の形態3に従うテストインターフェイス回路の他の構成を概略的に示す図である。

- 【図8】 従来のシステムLSIの構成を概略的に示す図である。

- 【図9】 図8に示すシステムLSIのDRAMコアに対する信号を一覧にして示す図である。

- 【図10】 図8に示すテストインターフェイス回路へ与えられる信号を一覧にして示す図である。

- 【図11】 テストインターフェイス回路へ与えられる信号とDRAMコアへ与えられる 信号の対応関係を一覧にして示す図である。

- 【図12】 図8に示すDRAMコアおよびテストインターフェイス回路の構成をより具体的に示す図である。

- 【図13】 図12に示すTICデータパスのデータ書込部の構成を概略的に示す図である。

- 【図14】 図12に示すTICデータパスのデータ読出部の構成を概略的に示す図である。

- 【図15】 図14に示すRIC制御回路の構成を概略的に示す図である。

- 【図 1 6 】 図 1 2 から図 1 5 に示すテストインターフェイス回路および D R A M コアの動作を示すタイミング図である。

- 【図17】 従来のテストインターフェイス回路の信号タイミングパラメータを測定する 部分の構成を概略的に示す図である。

- 【図18】 従来のテストインターフェイス回路におけるセットアップ / ホールド時間およびアクセス時間の測定動作を示すタイミング図である。

- 【図19】 従来のシステムLSIのテスト環境を概略的に示す図である。

- 【図20】 従来のテスト環境の問題点を説明するための図である。

# 【符号の説明】

# 【図6】

# 【図7】

# 【図8】

# 【図9】

| 信号名      | ファンクション                |

|----------|------------------------|

| CLK      | クロック信号                 |

| CKE      | クロックイネーブル信号            |

| /ACT     | ロウ活性化信号                |

| /PRE     | ロウ非活性化信号               |

| /REFA    | オートリフレッシュ指示信号          |

| /RE      | リード動作指示信号              |

| /WR      | ライト動作指示信号              |

| RA<12:0> | ロウアドレス信号               |

| CA<3:0>  | コラムアドレス信号              |

| RAsp     | スペアロウ空間アドレッシング用アドレス信号  |

| CAsp     | スペアコラム空間アドレッシング用アドレス信号 |

| Q<127:0> | 読出データ                  |

| D<127:0> | 書込みデータ                 |

| SQ<1:0>  | スペア読出データ               |

| SD<1:0>  | スペア書込データ               |

# 【図10】

| 信号名      | ファンクション             |

|----------|---------------------|

| TCLK     | クロック信号              |

| TCKE     | クロックイネーブル信号         |

| /CS      | チップセレクト信号           |

| /RAS     | ロウアドレスストローブ信号       |

| /CAS     | コラムアドレスストローブ信号      |

| /WE      | ライト動作指示信号           |

| AD<12:0> | ロウ/コラムアドレス          |

| ADsp     | スペア空間アドレッシング用アドレス信号 |

| TQ<7:0>  | 読み出しデータ出力信号         |

| TQmbt    | マルチビットテスト結果出力信号     |

| TD<7:0>  | 書き込みデータ入力信号         |

# 【図11】

| DRAM制御信号 | /WR    | Ŧ    | н   | Н   | Ξ   | н    | Н | _  |

|----------|--------|------|-----|-----|-----|------|---|----|

|          | /RE    | H    | Ξ   | Ξ   | ¥   | Н    | 7 | Н  |

|          | /REFA  | H    | Н   | Н   | Ŧ   | 7    | Н | Ŧ  |

|          | /PRE   | Ξ    | Ξ   | H   | 7   | Ξ    | Н | Н  |

|          | /ACT   | Н    | Ξ   | 7   | Н   | Н    | Ξ | H  |

|          |        | _    |     |     |     | _    | _ |    |

| TIC制御信号  | Æ      | ,    | ェ   | ±   | _   | ェ    | ェ | _  |

|          | /CAS   | ı    | Ŧ   | Ŧ   | H   | _    |   | 7  |

|          | /RAS   | 1    | Н   | 7   | 7   | 7    | н | Н  |

|          | 89/    | Н    | ٦   | 7   | ٦   | _    | _ | 7  |

|          | ニモーニック | DSEL | NOP | ACT | PRE | REFA | 끮 | W. |

【図12】

【図13】

【図14】

【図15】

【図17】

【図18】

【図19】

【図20】

# フロントページの続き

(72)発明者 山崎 彰

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 萬行 厚雄

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 堀江 義隆

(56)参考文献 特開2002-008393(JP,A)

特開2003-218216(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C 29/02

G11C 29/56

G11C 11/401

G01R 31/28