# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 111129204 B (45) 授权公告日 2021.07.16

(21)申请号 201910932176.3

(22)申请日 2019.09.29

(65) 同一申请的已公布的文献号 申请公布号 CN 111129204 A

(43) 申请公布日 2020.05.08

(30) 优先权数据 16/174,978 2018.10.30 US

(73) 专利权人 群创光电股份有限公司 地址 中国台湾新竹科学工业园区苗栗县竹 南镇科学路160号

(72) 发明人 柴田淳也 稲田利彌

(74) 专利代理机构 上海专利商标事务所有限公司 31100

代理人 骆希聪

(51) Int.CI.

H01L 31/113 (2006.01) H01L 31/0224 (2006.01) H01L 27/146 (2006.01)

审查员 廖艳闺

权利要求书1页 说明书17页 附图27页

### (54) 发明名称

电子装置

#### (57) 摘要

- 1.一种电子装置,其特征在于包括多个双栅极薄膜晶体管(DGTFT),其中上述双栅极薄膜晶体管包括一第一双栅极薄膜晶体管,上述第一双栅极薄膜晶体管包括:

- 一基板:

- 一第一透明导电层,被设置在上述基板上方;以及

- 一第一金属层,于上述第一透明导电层上设置,其中上述第一金属层电性连接至上述 第一透明导电层,并且部分重叠上述第一透明导电层以形成一开口区,使得光能够通过上 述开口区和上述第一透明导电层。

- 2. 如权利要求1所述的电子装置,其特征在于上述第一双栅极薄膜晶体管更包括:

- 一通道层,对应于上述第一透明导电层设置,其中上述第一金属层延伸超过上述通道层的至少一边界。

- 3. 如权利要求1所述的电子装置,其特征在于上述第一双栅极薄膜晶体管更包括:

- 一绝缘层,具有一开口,且该开口暴露上述第一透明导电层的一部分。

- 4.如权利要求3所述的电子装置,其特征在于上述第一金属层在上述开口中更加延伸以形成上述开口区。

- 5. 如权利要求4所述的电子装置,其特征在于更包括:

- 一不透明材料层,设置在上述第一透明导电层上方,其中在俯视上述电子装置的方向上,上述不透明材料层不与上述开口区重叠。

- 6. 如权利要求5所述的电子装置,其特征在于更包括:

- 一钝化层,设置在上述不透明材料层与上述第一金属层之间。

- 7.如权利要求4所述的电子装置,其特征在于在上述开口中延伸的上述第一金属层的一延伸方向的一角度相对于第一透明导电层大于或等于85度,并且小于或等于95度。

- 8.如权利要求7所述的电子装置,其特征在于上述角度大于或等于85度,并且小于或等于90度。

- 9. 如权利要求4所述的电子装置,其特征在于更包括:

- 上述双栅极薄膜晶体管的一第二双栅极薄膜晶体管,与上述第一双栅极薄膜晶体管相邻,其中上述第二双栅极薄膜晶体管包括:

- 一第二透明导电层,设置在上述基板上方:以及

- 上述第一金属层,对应于上述第二透明导电层设置,并且在俯视上述电子装置的方向上与上述第二透明导电层至少部分地重叠。

- 10.如权利要求9所述的电子装置,其特征在于更包括:

- 一第二金属层,设置在上述绝缘层中,并且位于上述第一双栅极薄膜晶体管与上述第二双栅极薄膜晶体管之间。

# 电子装置

#### 技术领域

[0001] 本申请是关于一种电子装置,特别是关于一种具有至少一个双栅极薄膜晶体管 (DGTFT) 的电子装置,其中双栅极薄膜晶体管的金属层电性连接至透明导电层。

## 背景技术

[0002] 在电子装置中,例如光感测装置,多个双栅极型晶体管(例如:双闸及薄膜晶体管 (double gate thin-film transistor;DGTFT))以阵列布置以感测光或影像(例如:指纹图案)。在双栅极型晶体管的已知结构中,透明电极材料被用作上栅极(top gate)电极以将光发射到半导体层。

[0003] 然而,近代的光感测装置需要高电压电位解析度(high voltage level resolution)和更准确的识别。这种上栅极电极可能具有高电压电位电阻,并且可能导致光感测装置的每个影像感测区中的电路操作延迟和影像数据的变化。另外,影像感测区不仅可以通过从物体所反射的光来曝光,还可以通过来自其他方向的杂散光来曝光。此外,当影像感测区中的每个像素的双栅极型晶体管的特性有相应的变化时,也可能导致数据变化。使用双栅极型晶体管的已知光感测装置输出模拟数据,因此很容易受到这些变化的影响。

## 发明内容

[0004] 本申请提供一种电子装置。电子装置包括多个双栅极薄膜晶体管 (DGTFT)。双栅极薄膜晶体管包括第一双栅极薄膜晶体管。双栅极薄膜晶体管包括基板、设置在基板上方的第一透明导电层以及第一金属层。第一金属层对应于第一透明导电层设置。第一金属层电性连接至第一透明导电层。

## 附图说明

[0005] 为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

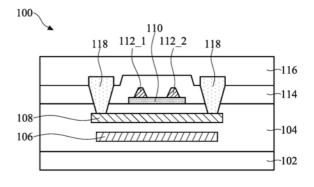

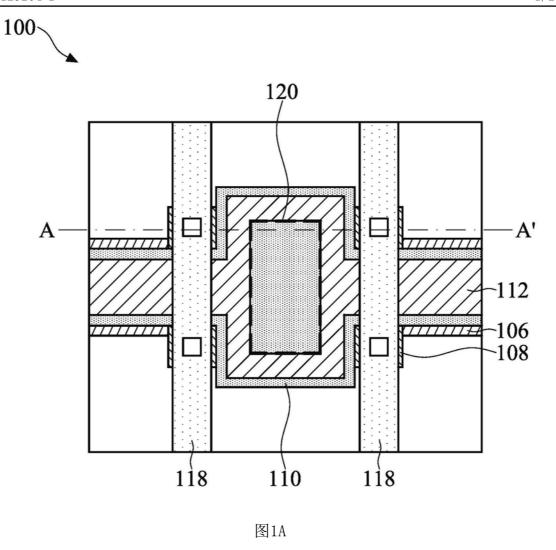

[0006] 图1A显示了根据本申请实施例的在电子装置中的双栅极薄膜晶体管 (DGTFT) 的俯视图 (布局)。

[0007] 图1B显示了沿着在图1A中所示的线段A-A'截取的双栅极薄膜晶体管的剖面图。

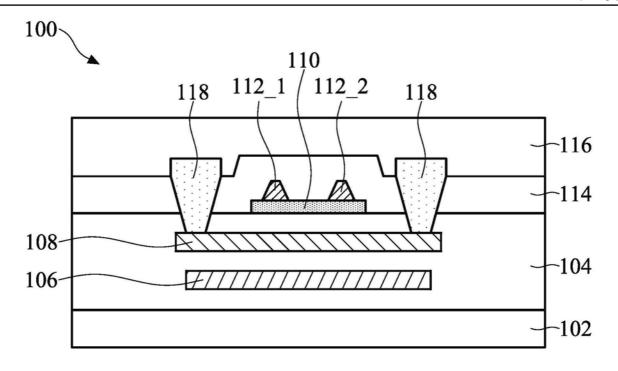

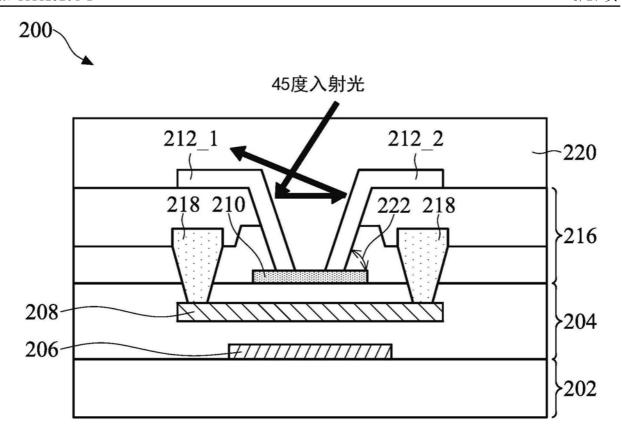

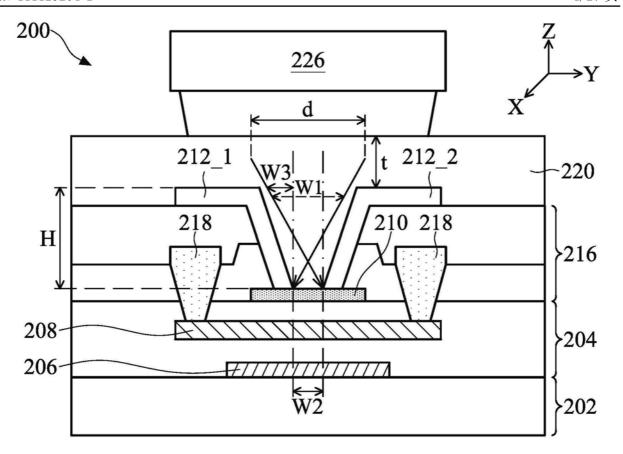

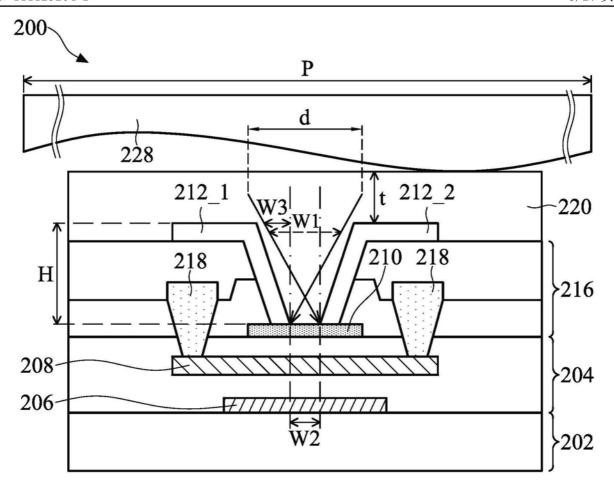

[0008] 图2A和图2B显示了根据本申请实施例的双栅极薄膜晶体管的剖面图。

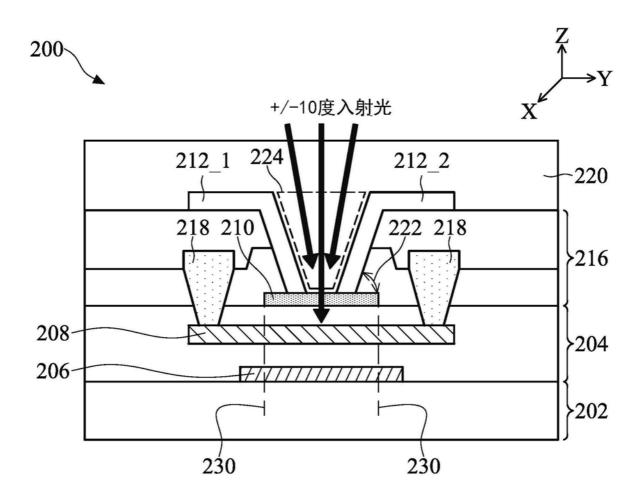

[0009] 图2C和图2D显示了根据本申请实施例的感测物体的双栅极薄膜晶体管的示意图。

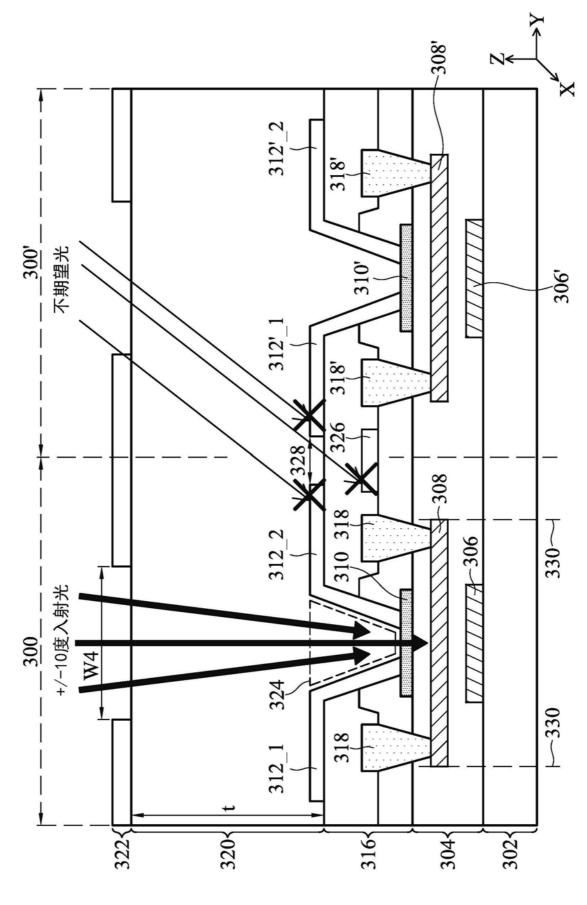

[0010] 图3显示了根据本申请实施例的两个相邻的双栅极薄膜晶体管的剖面图。

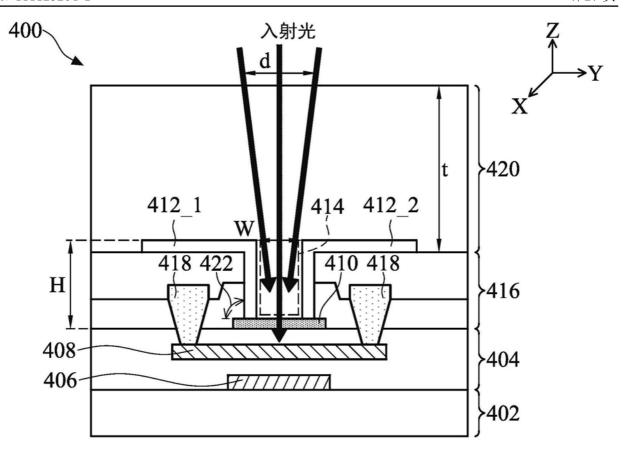

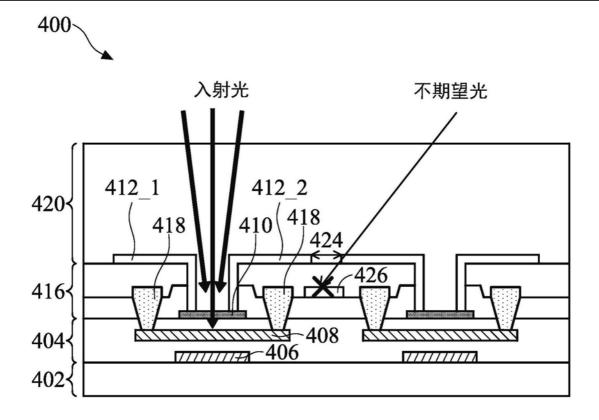

[0011] 图4A显示了根据本申请实施例的双栅极薄膜晶体管的剖面图。

[0012] 图4B显示了根据本申请实施例的两个相邻的双栅极薄膜晶体管的剖面图,其中它们之间具有金属层。

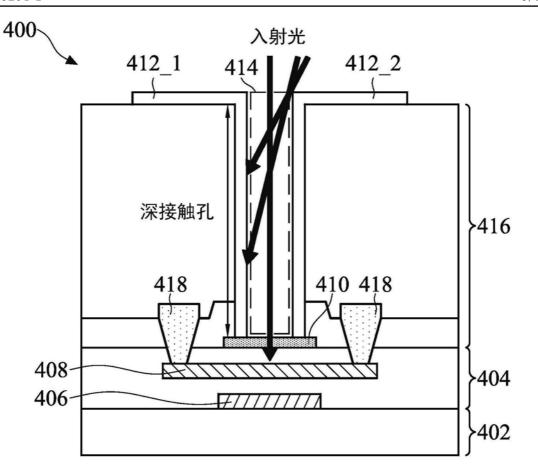

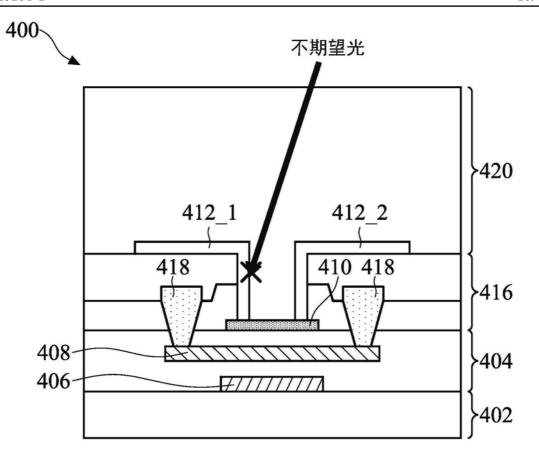

[0013] 图4C和图4D显示了根据本申请实施例的双栅极薄膜晶体管的剖面图。

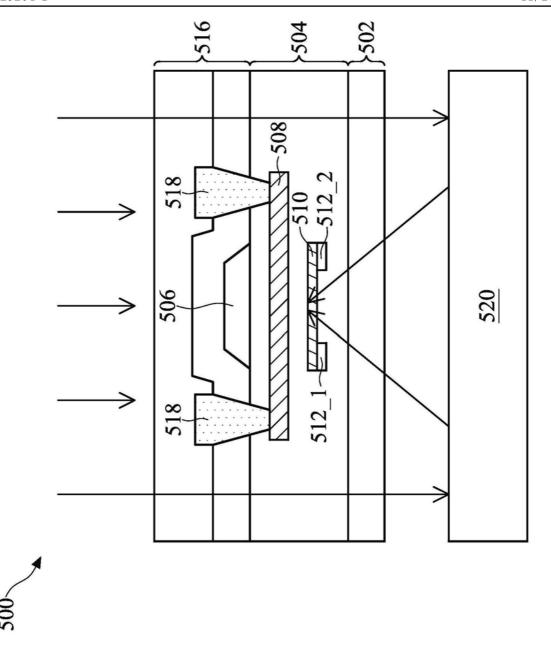

[0014] 图5显示了根据本申请实施例的具有相反结构的双栅极薄膜晶体管的剖面图。

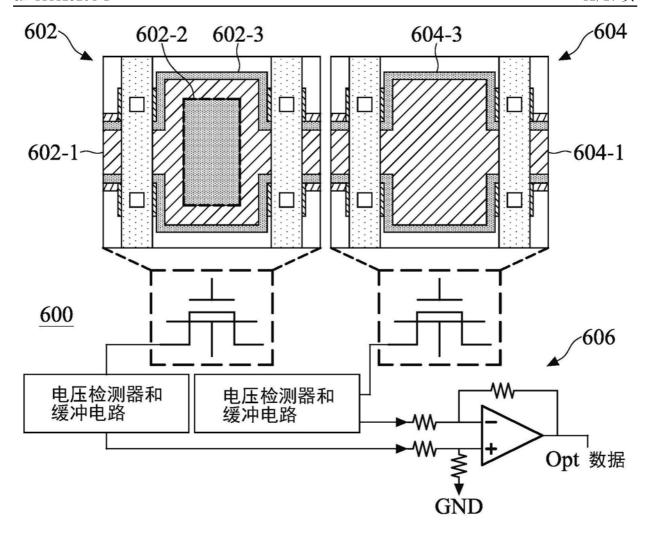

- [0015] 图6显示了根据本申请实施例的光感测装置的示意图。

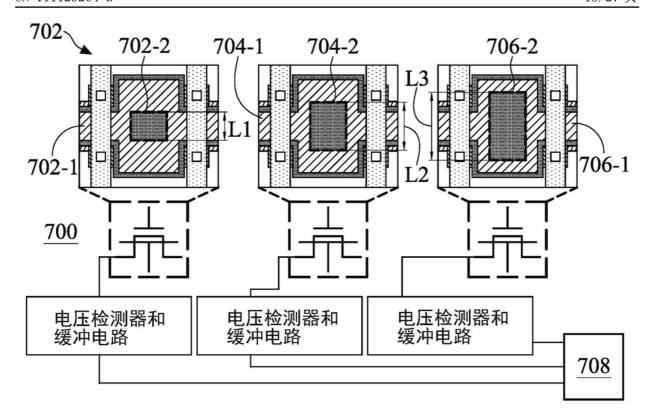

- [0016] 图7显示了根据本申请实施例的光感测装置的示意图。

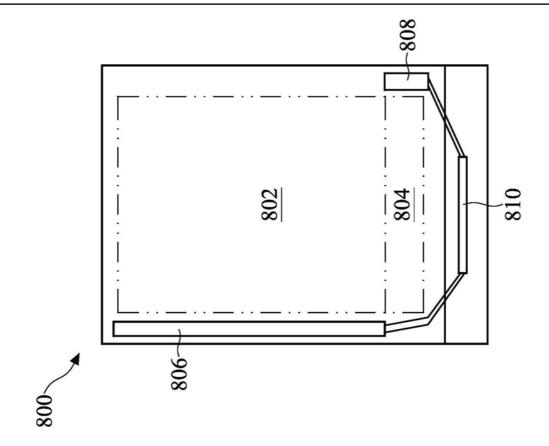

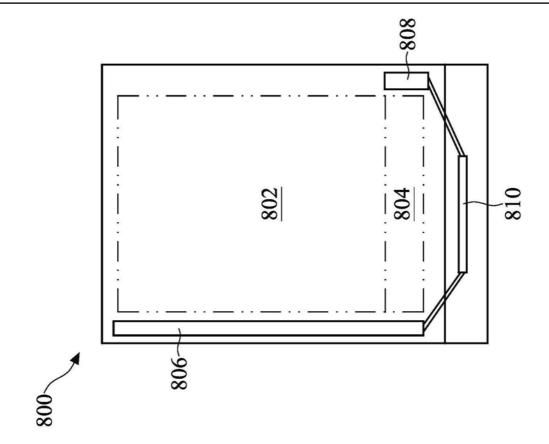

- [0017] 图8A和图8B显示了根据本申请实施例的与光感测装置组合的显示装置的示意图。

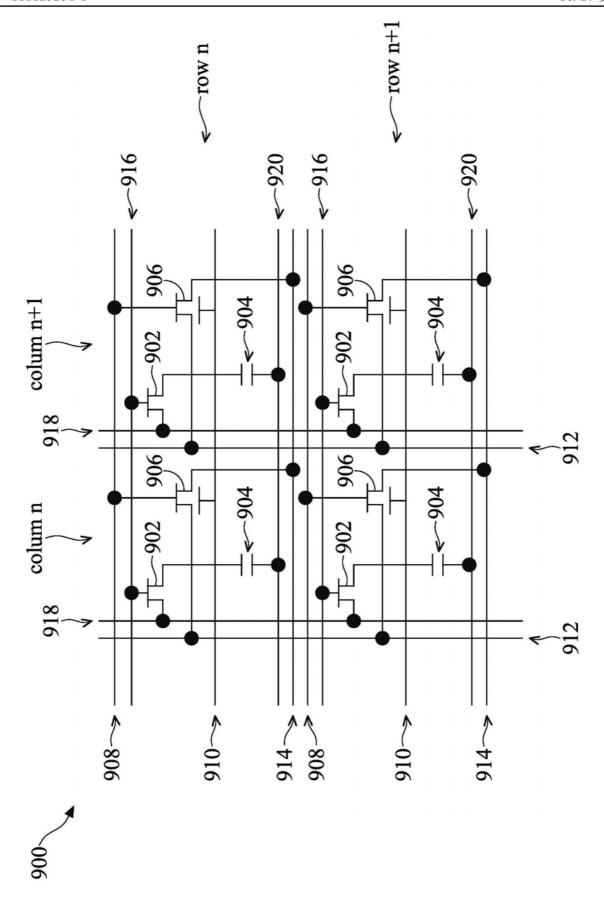

- [0018] 图9显示了根据本申请实施例的整合到在液晶显示器中的显示区的薄膜晶体管阵列中的双栅极薄膜晶体管阵列。

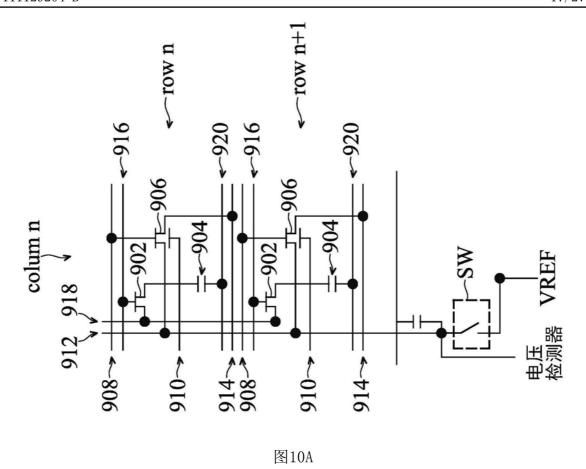

- [0019] 图10A显示了根据本申请实施例的在图9中的阵列的一部分的示意图。

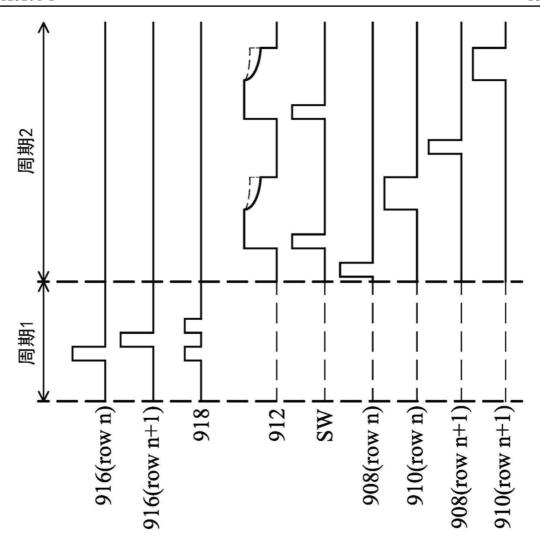

- [0020] 图10B显示了根据本申请实施例的在图10A中的阵列的光感测的时序图。

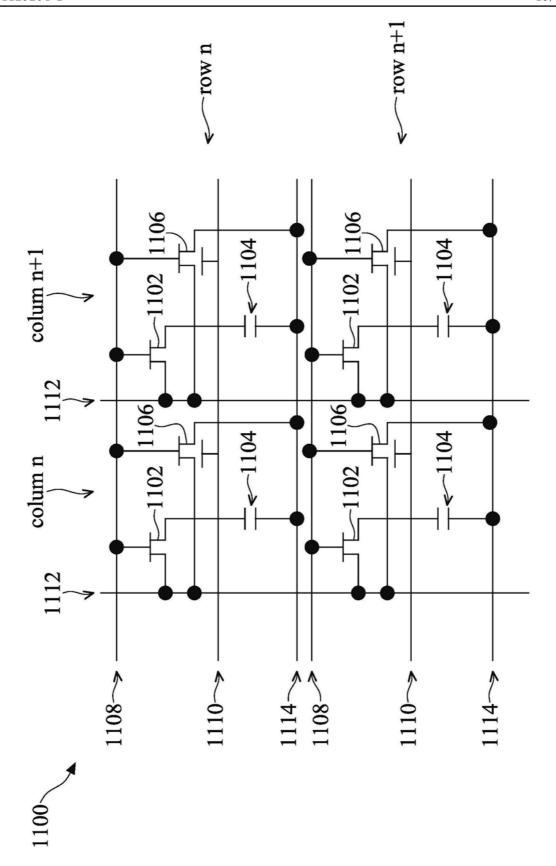

- [0021] 图11显示了根据本申请实施例的整合到在液晶显示器中的显示区的薄膜晶体管阵列中的双栅极薄膜晶体管阵列。

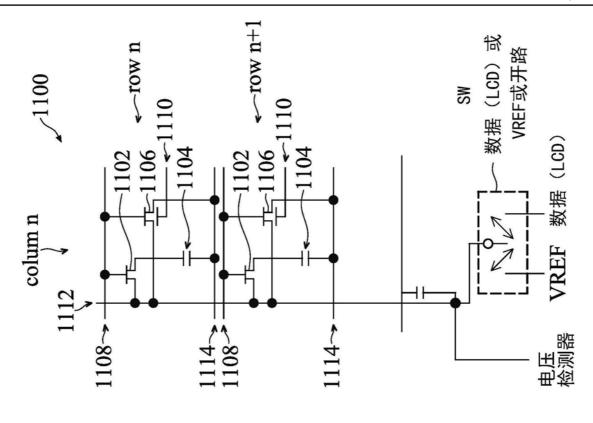

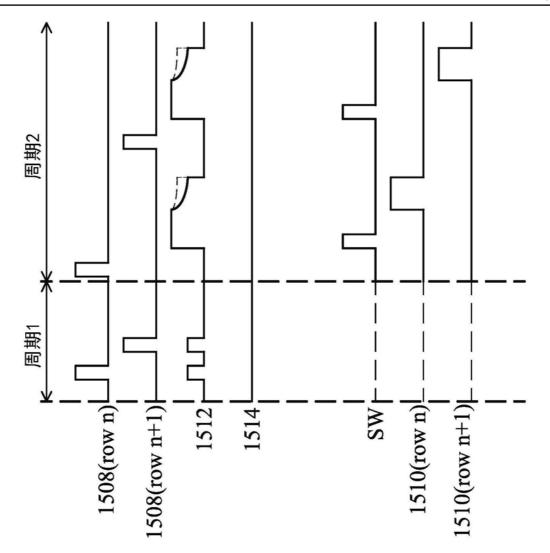

- [0022] 图12A显示了根据本申请实施例的在图11中的阵列的一部分的示意图。

- [0023] 图12B显示了根据本申请实施例的在图12A中的阵列的光感测的时序图。

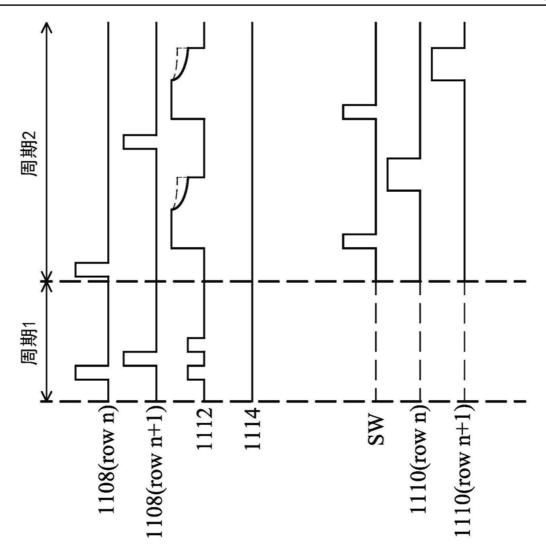

- [0024] 图13显示了根据本申请实施例的整合到在发光二极管显示器中的显示区的薄膜晶体管阵列中的双栅极薄膜晶体管阵列。

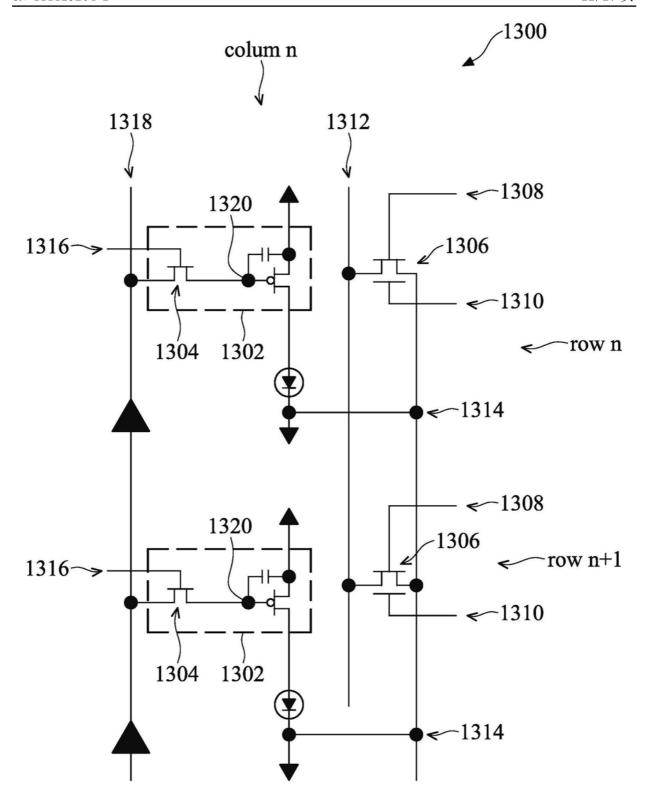

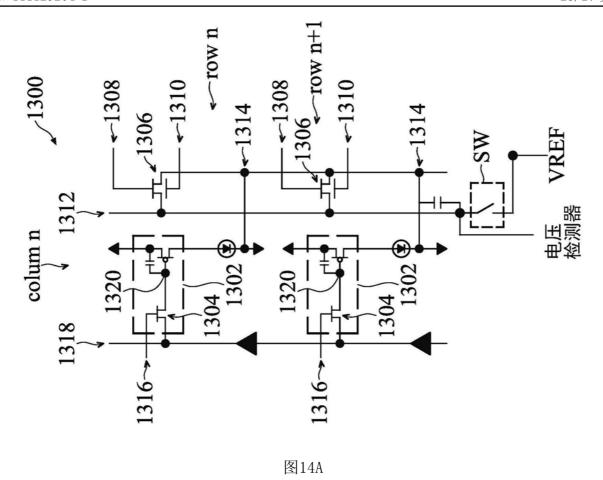

- [0025] 图14A显示了根据本申请实施例的在图13中的阵列的示意图。

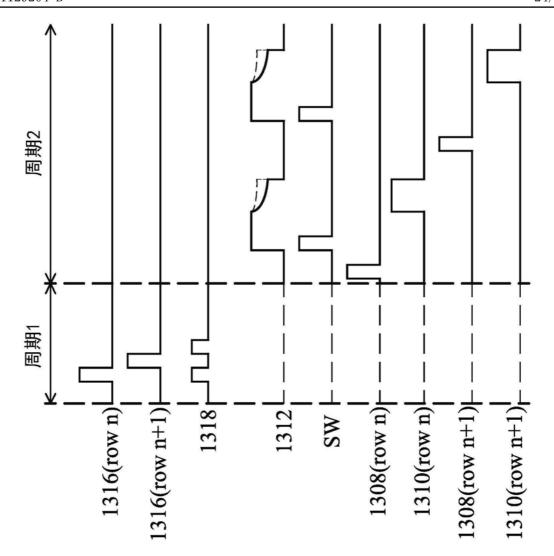

- [0026] 图14B显示了根据本申请实施例的在图14A中的阵列的光感测的时序图。

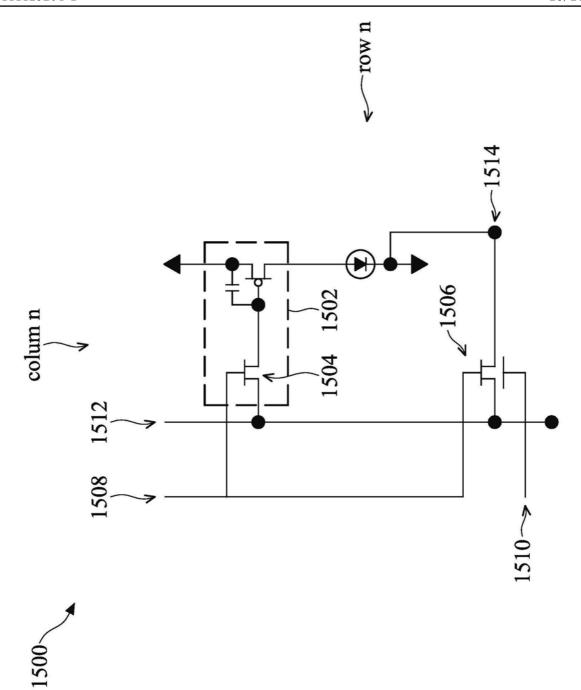

- [0027] 图15显示了根据本申请实施例的整合到在发光二极管显示器中的显示区的薄膜晶体管阵列中的双栅极薄膜晶体管阵列。

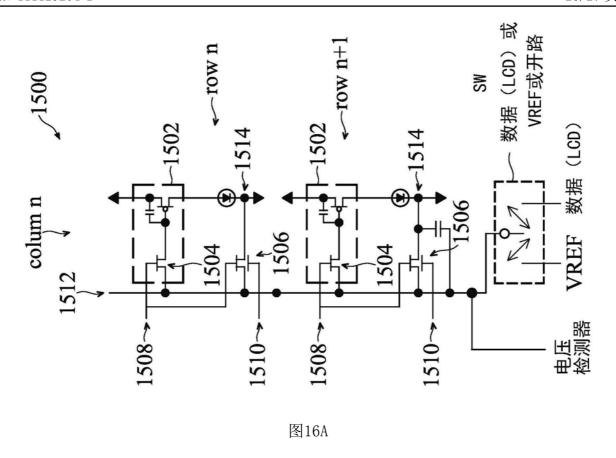

- [0028] 图16A显示了根据本申请实施例的发光二极管显示器的全阵列的一部分的示意图。

- [0029] 图16B显示了根据本申请实施例的在图16A中的阵列的光感测的时序图。

- [0030] 图中元件标号说明:

- [0031] 100~双栅极薄膜晶体管

- [0032] 102~基板

- [0033] 104、114、116~绝缘层

- [0034] 106~栅极电极

- [0035] 108~半导体层

- [0036] 110~透明导电层

- [0037] 112、112 1、112 2~金属层

- [0038] 118~源极/漏极

- [0039] 120~开口区

- [0040] 200~双栅极薄膜晶体管

- [0041] 202~基板

- [0042] 204、216~绝缘层

- [0043] 206~栅极电极

- [0044] 208~半导体层

- [0045] 210~透明导电层

- [0046] 212、212 1、212 2~金属层

- [0047] 218~源极/漏极

- [0048] 220~钝化层

- [0049] 222~角度

- [0050] 224~开口区

- [0051] 226~物体

- [0052] 228~指纹图案

- [0053] 230~边界

- [0054] 300、300'~双栅极薄膜晶体管

- [0055] 302~基板

- [0056] 304、316~绝缘层

- [0057] 306、306、~栅极电极

- [0058] 308、308、~半导体层

- [0059] 310、310、一透明导电层

- [0060] 312、312\_1、312\_2、312'\_1、312'\_2、326~金属层

- [0061] 318、318、~源极/漏极

- [0062] 320~钝化层

- [0063] 322~不透明材料层

- [0064] 324~开口区

- [0065] 328~间隙

- [0066] 330~边界

- [0067] 400~双栅极薄膜晶体管

- [0068] 402~基板

- [0069] 404、416~绝缘层

- [0070] 406~栅极电极

- [0071] 408~半导体层

- [0072] 410~透明导电层

- [0073] 412、412 1、412 2、426~金属层

- [0074] 418~源极/漏极

- [0075] 420~钝化层

- [0076] 422~角度

- [0077] 424~间隙

- [0078] 502~基板

- [0079] 504、516~绝缘层

- [0080] 506~栅极电极

- [0081] 508~半导体层

- [0082] 510~透明导电层

- [0083] 512、512 1、512 2~金属层

- [0084] 518~源极/漏极

- [0085] 520~物体

- [0086] 600~光感测装置

- [0087] 602、604~双栅极薄膜晶体管

- [0088] 602-1、604-1~金属层

- [0089] 602-2~开口区

- [0090] 602-3、604-3~透明导电层

- [0091] 606~差分减法器电路

- [0092] 700~光感测装置

- [0093] 702、704、706~双栅极薄膜晶体管

- [0094] 708~比较器电路

- [0095] 702-2、704-2、706-2~开口区

- [0096] L1、L2、L3~长度

- [0097] 800~电子装置

- [0098] 802、804~区域

- [0099] 806、808~栅极驱动电路

- [0100] 810~集成电路

- [0101] 900~阵列

- [0102] 902~薄膜晶体管

- [0103] 904~电容

- [0104] 906~双栅极薄膜晶体管

- [0105] 908、910、912、914、916、918、920~线路

- [0106] SW~开关

- [0107] 1100~阵列

- [0108] 1102~薄膜晶体管

- [0109] 1104~电容

- [0110] 1106~双栅极薄膜晶体管

- [0111] 1108、1110、1112、1114~线路

- [0112] 1300~阵列

- [0113] 1302~显示单元

- [0114] 1304~薄膜晶体管

- [0115] 1306~双栅极薄膜晶体管

- [0116] 1308、1310、1312、1316、1318、1320~线路

- [0117] 1314~节点

- [0118] 1500~阵列

- [0119] 1502~显示单元

- [0120] 1504~薄膜晶体管

- [0121] 1506~双栅极薄膜晶体管

- [0122] 1508、1510、1512~线路

- [0123] 1514~节点

#### 具体实施方式

[0124] 以下的申请内容提供许多不同的实施例或范例以实施本案的不同特征。以下的申

请内容叙述各个构件及其排列方式的特定范例,以简化说明。当然,这些特定的范例并非用以限定。举例来说,若是本申请书叙述了一第一特征形成于一第二特征之上或上方,即表示其可能包含上述第一特征与上述第二特征是直接接触的实施例,亦可能包含了有附加特征形成于上述第一特征与上述第二特征之间,而使上述第一特征与第二特征可能未直接接触的实施例。另外,以下申请书不同范例可能重复使用相同的参考符号及/或标记。这些重复是为了简化与清晰的目的,并非用以限定所讨论的不同实施例及/或结构之间有特定的关系。

[0125] 为本申请内容的详述目的,除非特定否认,单数词包含复数词,反之亦然。并且字词"包含"其意为"非限制性地包含"。此外,进似性的(approximation)用语例如"大约"、"几乎"、"相当地"、"大概"等,可用于本申请实施例,其意义上如"在、接近或接近在"或"在3至5%内"或"在可接受制造公差内"或任意逻辑上的组合。

[0126] 此外,其与空间相关用词。例如"在…下方"、"下方"、"较低的"、"上方"、"较高的"及类似的用词,是为了便于描述附图中一个元件或特征与另一个(些)元件或特征之间的关系。除了在附图中绘示的方位外,这些空间相关用词意欲包含使用中或操作中的装置的不同方位。举例来说,若在示意图中的装置被反转,被描述在其他元件或特征的"下方"或"在…下方"的元件也会因而变成在另外其他元件或特征的"上方"。如此一来,示范词汇"下方"会涵盖朝上面与朝下面的两种解读方式。除此之外,设备可能被转向不同方位(旋转90度或其他方位),则在此使用的空间相关词也可依此相同解释。

[0127] 为了方便起见,"对应于"表示一个元件可以设置在另一个元件的上方/下方,或者这两个元件可以在俯视图中至少部分地重叠。

[0128] 图1A显示了根据本申请实施例的在电子装置(例如:光感测装置)中的双栅极薄膜晶体管(DGTFT)的俯视图(布局)。图1B显示了沿着在图1A中所示的线段A-A'截取的双栅极薄膜晶体管的剖面图。

[0129] 参照图1A和图1B,双栅极薄膜晶体管100包括基板102、设置在基板102上方的绝缘层104、设置在绝缘层104中并且在基板102上方的栅极电极106、设置在绝缘层104中并且在栅极电极106上方的半导体层108、对应于半导体层108和基板102设置的透明导电层110、对应于透明导电层110设置的金属层112、在俯视双栅极薄膜晶体管100的方向上至少部分地与透明导电层110重叠的绝缘层114和绝缘层116、以及电性连接至半导体层108的两个源极/漏极118。源极/漏极118亦可称为双栅极薄膜晶体管100的源极/漏极端子(或端子(terminal))。在一个实施例中,在俯视双栅极薄膜晶体管100的方向上,透明导电层110至少部分地与半导体层108和基板102重叠;金属层112至少部分地与透明导电层110重叠。

[0130] 绝缘层104可包括多个子层(plural sub-layers)(未显示)。多个子层中的至少一部分设置在栅极电极106与半导体层108之间。多个子层的至少另一部分设置在栅极电极106与基板102之间。多个子层的至少另一部分设置在半导体层108与透明导电层110之间。在另一实施例中,多个子层的第一部分、栅极电极106、多个子层的第二部分、半导体层108以及多个子层的第三部分可以依次设置,但是本申请不限于此。

[0131] 在一个实施例中,基板102可以是硬性基板或软性基板,并且是透明或不透明的。举例来说,硬性基板是玻璃,并且软性基板是由例如聚酰亚胺(polyimide;PI)或聚对苯二甲酸乙二酯(polyethylene terephthalate;PET)制造,但不限于此。在另一个实施例中,基

板102包括合适的元素(el em ental)半导体,例如锗或钻石;合适的化合物半导体,例如碳化硅、氮化镓、砷化镓或磷化铟;或合适的合金半导体,例如硅锗、硅锡、砷化铝镓或砷化镓磷,但不限于此。

[0132] 如图1A和图1B所示,在此实施例中,栅极电极106用来作为双栅极薄膜晶体管100的下栅极(bottom gate)。栅极电极106包括一些种类的金属材料,例如铜、铝、金、银、另一合适金属材料或其组合,但不限于此。在此实施例中,源极/漏极118亦可包括金属材料。半导体层108用来作为双栅极薄膜晶体管100的通道层。在此实施例中,半导体层108包括多晶硅(亦称为poly-Si)。在一些实施例中,半导体层108可包括非晶硅(亦称为a-Si),氧化铟镓锌(亦称为IGZO(Indium Gallium Zinc Oxide)),另一合适半导体材料或其组合,但不限于此。

[0133] 在本申请中,透明导电层110和金属层112可共同称为双栅极薄膜晶体管100的上栅极。透明导电层110可包括氧化铟锡(indium tin oxide;ITO)、氧化锌(zinc oxide;ZnO)、氧化铟镓锌(IGZO)、另一透明导电材料或其组合,但不限于此。金属层112包括金属材料(例如:铜、铝、金、银、另一合适金属材料或其组合),但不限于此。

[0134] 在本申请中,金属层112个别对应于透明导电层110设置,并且在俯视双栅极薄膜晶体管100的方向上至少部分地与透明导电层110或半导体层108重叠,如图1A和图1B所示。在金属层112\_1和金属层112\_2之间设置有开口(或开孔(aperture))区。应理解开口区120可以设计成任何尺寸(面积)和形状。透明导电层110的一部分暴露在开口区120中。透明导电层110是透明或半透明的(但不限于此),使得光可以穿过透明导电层110以影响半导体层108,从而双栅极薄膜晶体管100可以感测光。

[0135] 绝缘层104、114以及116包括绝缘或介电材料,例如氧化硅(Si0<sub>x</sub>)、氮化硅(SiN<sub>x</sub>)或其他合适绝缘或介电材料。如图1B所示,绝缘层104将透明导电层110、半导体层108以及栅电极106彼此分开,使得透明导电层110和栅极电极106可以是双栅极薄膜晶体管100的栅极(上栅极或下栅极),以控制半导体层108(双栅极薄膜晶体管100的通道)的临界电压(threshold voltage)。

[0136] 在本申请中,如图1B所示,金属层112对应于透明导电层110设置,并且电性连接至透明导电层110。金属层112和透明导电层110可共同称为栅极电极(例如:双栅极薄膜晶体管100的上栅极)。这导致其电阻低于仅由透明导电材料(例如:ITO)制造的栅极电极的电阻。它可能导致较低的电路操作延迟时间(时间常数)。举例来说,在双栅极薄膜晶体管中,栅极线性电容约为11pF、借由ITO制造的栅极线性电阻约为826千欧姆(ohm)以及借由金属制造的栅极线性电阻约为9.4千欧姆,但不限于此。因此,对应ITO的电路操作延迟时间为9.1μs,对应金属的电路操作延迟时间为103.4ns,但不限于此。对应金属的电路操作延迟时间比对应ITO的电路操作延迟时间小约100倍。

[0137] 图2A和图2B显示了根据本申请实施例的双栅极薄膜晶体管的剖面图。双栅极薄膜晶体管200与双栅极薄膜晶体管100有许多相似之处,但有一些细微差异。双栅极薄膜晶体管200包括基板202、设置在基板202上方的绝缘层204、设置在绝缘层204中并且在基板202上方的栅极电极206、设置在绝缘层204中并且在栅极电极206上方的半导体层208、设置在半导体层208和基板202上方的透明导电层210、对应于透明导电层210设置的金属层212、设置在金属层212和透明导电层210之间的绝缘层216、以及电性连接至半导体层208的源极/

漏极218。绝缘层204的结构可类似于绝缘层104。钝化层220覆盖双栅极薄膜晶体管200的栅极电极206、半导体层208、透明导电层210以及金属层212。在此实施例中,钝化层220包括绝缘或介电材料,如上面所述的绝缘层的材料,但不限于此。

[0138] 如图2A所示,金属层212通过具有开口的绝缘层216覆盖透明导电层210的边界230的至少一者,以形成开口区224。在一个实施例中,边界代表透明导电层210在Y方向上的最突出点。相似地,金属层212对应于透明导电层210设置。透明导电层210的一部分暴露在开口区域224中。此外,金属层212在开口中延伸并且电性连接至透明导电层210。具体来说,金属层212沿着绝缘层216的侧壁延伸,以电性连接至透明导电层210。

[0139] 如图2A所示,金属层212在开口中以相对于第一透明导电层210的角度222延伸。在一个实施例中,角度222大于或等于85度,并且小于或等于90度(degree)。在其他实施例中,角度222大于或等于45度,并且小于或等于90度,但不限于此。在另一个实施例中,角度222亦可小于或等于45度。

[0140] 利用此实施例的结构和角度222,入射光可以被阻挡,除了垂直于透明导电层210的顶表面的正轴(on-axis)方向附近的入射光。因此,双栅极薄膜晶体管200可以感测清晰的物体影像(或物体数据)。举例来说,在+10度与-10度之间的角度范围的入射光可借由双栅极薄膜晶体管200感测和收集,如图2A所示。具有45度或更大角度的入射光可被双栅极薄膜晶体管200的金属层212阻挡,如图2B所示。来自其他方向(离轴方向)的杂散光可不被双栅极薄膜晶体管200感测和收集。

[0141] 图2C和图2D显示了根据本申请实施例的感测物体的双栅极薄膜晶体管的示意图。为了检测更准确的物体数据或影像,双栅极薄膜晶体管200的金属层孔洞的长宽比( $\frac{W2}{H}$ 和 $\frac{W3}{H}$ )可遵循以下公式:

$$[0142] 2t\left(\frac{W2}{H} + \frac{W3}{H}\right) + W1 \le d$$

[0143] 在上面的公式中,d是双栅极薄膜晶体管200可以感测的沿着Y方向的最小宽度范围、t是钝化层220的沿着Z方向的厚度、W1是金属层212\_1与金属层212\_2之间的沿着Y方向的最大开口宽度、W2是金属层212\_1与金属层212\_2之间的沿着Y方向的最小开口宽度、W3是(W1-W2)/2、以及H是从透明导电层210的顶表面到金属层212的顶表面的沿Z方向的高度,如图2C所示。使用上述公式,可以设计金属层孔洞的长宽比以感测物体226。

[0144] 举例来说,如图2D所示,在双栅极薄膜晶体管200感测指纹图案228的情况下,指纹图案228的间距p平均为约400 $\mu$ m。为了感测清晰的物体影像,最好聚焦在要识别的间距p的四分之一(100 $\mu$ m)。假设d为100 $\mu$ m、W1为10 $\mu$ m、W2为5 $\mu$ m、t为10 $\mu$ m:可以计算出高度H应不小于1.67 $\mu$ m。可以使用上述公式可设计双栅极薄膜晶体管200结构的尺寸。此外,应理解根据上述公式,如果钝化层220的厚度t增加,则金属层212需要更多的层堆叠(layer stack)以增加高度H。

[0145] 图3显示了根据本申请实施例的两个相邻的双栅极薄膜晶体管的剖面图。双栅极薄膜晶体管300与双栅极薄膜晶体管200相似。双栅极薄膜晶体管300包括基板302、绝缘层304、栅极电极306、半导体层308、透明导电层310、具有开口的绝缘层316、第一金属层312、

两个源极/漏极318。第一金属层312在开口中延伸以形成开口区324。钝化层320设置在双栅极薄膜晶体管300上方、不透明材料层322设置在钝化层320上方,并且在俯视双栅极薄膜晶体管300的方向上不覆盖开口区324。具体来说,不透明材料层322还具有与开口区324至少部分地重叠的开口区。值得注意的是,金属层312被扩大以沿着Y方向延伸超过半导体层308的边界330的至少一者。在一个实施例中,绝缘层304的结构可类似于绝缘层104。

[0146] 不透明材料层322亦称为黑矩阵(black matrix;BM)。不透明材料层322可包括不透明材料,例如铬(Cr)、聚酰亚胺或其他合适不透明材料。不透明材料层322借由钝化层320与金属层312分开,以控制(或限制)入射光角度。具体来说,不透明材料层322被设置为不覆盖开口区324,并且钝化层320沿着Z方向设置在不透明材料层322与金属层312之间,使得入射光的角度可被控制。

[0147] 相似地,利用不透明材料层322的开口区和开口区324,入射光可以被阻挡,除了垂直于透明导电层210的顶表面的正轴(on-axis)方向附近的入射光。双栅极薄膜晶体管300可以感测清晰的物体影像(或物体数据)。举例来说,在+10度与-10度之间的角度范围的入射光可借由双栅极薄膜晶体管300感测和收集,如图3所示。

[0148] 如上面所述,为了检测更准确的物体数据或影像,双栅极薄膜晶体管的金属层孔洞的长宽比可遵循公式。在此实施例中,可以假设公式中的钝化层厚度(例如:在图3中的钝化层320的厚度t)的参数为0。因此,双栅极薄膜晶体管300可遵循以下公式:

[0149] W4≤d

[0150] 在此公式中,d是双栅极薄膜晶体管300可以感测的最小宽度范围,并且W4是沿着Y方向的不透明材料层322的最大开口宽度。应理解使用上述公式,不透明材料层322的开口区可以控制双栅极薄膜晶体管300的感测宽度。

[0151] 在此实施例中,如上面所述,金属层312被扩大。此扩大的金属层312可以阻挡来自不透明材料层322的相邻开口区的入射光。如图3所示,双栅极薄膜晶体管300'的结构与双栅极薄膜晶体管300的结构相同,此不再详细描述。来自双栅极薄膜晶体管300'的不透明材料层322的开口区的入射光可被金属层312阻挡,并且可不影响双栅极薄膜晶体管300。双栅极薄膜晶体管300的金属层与双栅极薄膜晶体管300'的金属层之间的间隙328越小,阻挡越有效。因此,双栅极薄膜晶体管300可以感测未受不期望的光影响的清晰物体图像(或物体数据)。

[0152] 在一些实施例中,金属层326对应于透明导电层310设置,并且设置在绝缘层316中以及两个相邻的双栅极薄膜晶体管300与双栅极薄膜晶体管300'之间,如图3所示。在一个实施例中,双栅极薄膜晶体管300'与双栅极薄膜晶体管300相邻,其表示双栅极薄膜晶体管300'在Y方向上最接近双栅极薄膜晶体管300。金属层326在间隙328下方,并且在双栅极薄膜晶体管300的金属层312\_2与双栅极薄膜晶体管300'的金属层312'\_1之间,使得穿过间隙328的入射光可被阻挡。因此,双栅极薄膜晶体管300可以感测未受不期望的光影响的清晰物体图像(或物体数据)。在一些实施例中,金属层326和源极/漏极318具有相同的制程。换句话说,金属层326和源极/漏极318可以同时形成。

[0153] 图4A显示了根据本申请实施例的双栅极薄膜晶体管的剖面图。双栅极薄膜晶体管400与双栅极薄膜晶体管200相似。双栅极薄膜晶体管400包括基板402、绝缘层404、栅极电极406、半导体层408、透明导电层410、金属层412、绝缘层416、两个源极/漏极418及钝化层

420。在一个实施例中,绝缘层404的结构可类似于绝缘层104。

[0154] 在此实施例中,与在图2A至图2D中的双栅极薄膜晶体管200类似,金属层412在绝缘层416的开口中以相对于第一透明导电层410的角度422延伸,如图4A所示。然而,角度422大抵等于90°。换句话说,在金属层412与透明导电层410之间具有陡峭的锥角(precipitous taper angle)。在这种情况下,金属层412可以限制进入开口区414的入射光的不期望光(例如:杂散光或离轴光),如图4A所示。具体来说,利用此实施例的结构和角度422(即大抵90°),入射光可以被阻挡,除了垂直于透明导电层410的顶表面的正轴方向附近的入射光。因此,双栅极薄膜晶体管400可以感测清晰物体图像(或物体数据)。值得注意的是,在此该实施例中的金属层412控制双栅极薄膜晶体管400的感测宽度,使得具有开口区的不透明材料层可以不需要。在一些实施例中,金属层426亦可设置在绝缘层416中以及双栅极薄膜晶体管400与相邻的双栅极薄膜晶体管之间,如图4B所示。穿过在双栅极薄膜晶体管400与相邻双栅极薄膜晶体管之间的间隙424的入射光(不期望光)可被阻挡。

[0155] 在一些实施例中,绝缘层416的厚度大,使得开口区414较深。深的开口区414形成深接触孔(深CH(contact hole)),如图4C所示。由于此深接触孔,双栅极薄膜晶体管400可以感测清晰物体图像(或物体数据)。

[0156] 在其他实施例中,金属层412包括低反射率材料,其具有对可见光低于60%的反射率。低反射率材料包括铬(Cr)、金(Au)、镍(Ni)或具有低反射率的其他合适材料,但不限于此。照射金属层412的不期望光(例如:杂散光或轴外光)可不严重影响双栅极薄膜晶体管400的感测,如图4D所示。双栅极薄膜晶体管400可以感测清晰物体图像(或物体数据)。

[0157] 相似地,为了检测更准确的物体数据或影像,双栅极薄膜晶体管400的金属层孔洞的长宽比 $(\frac{W}{H})$ 可遵循以下公式:

$$[0158] 2t\left(\frac{W}{H}\right) + W \le d$$

[0159] 在上面的公式中,d是双栅极薄膜晶体管400可以感测的最小宽度范围、t是钝化层420的沿着Z方向的厚度、W是金属层212\_1与金属层212\_2之间的沿着Y方向的最大开口宽度、以及H是从透明导电层410的顶表面到金属层412的顶表面的沿Z方向的高度,如图4A所示。使用上述公式,可以设计金属层孔洞的长宽比。

[0160] 如图1A至图4D所示,透明导电层和金属层共同形成双栅极薄膜晶体管的上栅极。然而,在一些实施例中,透明导电层和金属层可以共同形成为双栅极薄膜晶体管的下栅极。具体来说,栅极电极(即图1A至图4D中所示的原下栅极)可设置为双栅极薄膜晶体管的上栅极,并且透明导电层和金属层(即图1A至图4D中所示的原上栅极)可共同地设置为双栅极薄膜晶体管的下栅极。

[0161] 图5显示了根据本申请实施例的具有相对于图1A至图4D的相反结构的双栅极薄膜晶体管的剖面图。双栅极薄膜晶体管500包括基板502、设置在基板502上表面上的绝缘层504、设置在绝缘层504中并且在基板502上方的透明导电层510、对应于透明导电层510设置的金属层512、设置在绝缘层504中并且在透明导电层510上方的半导体层508、设置在半导体层508上方的栅极电极506、设置在栅极电极506上方的绝缘层516、以及电性连接至半导体层508的两个源极/漏极518。在一个实施例中,绝缘层504的结构可类似于绝缘层104。

[0162] 如上面所述,在此实施例中,透明导电层510和金属层512共同用来作为双栅极薄膜晶体管500的下栅极,并且栅极电极506用来作为双栅极薄膜晶体管500的上栅极。相似地,在俯视基板502的方向上,金属层512与透明导电层510或半导体层508至少部分地重叠。

[0163] 在此实施例中,双栅极薄膜晶体管500借由来自物体520的反射光来感测物体520。具体来说,背光(back light)可以照射物体520,并接着成为反射光反射回双栅极薄膜晶体管500。根据上面所讨论的实施例,金属层512还可以保护双栅极薄膜晶体管500免受来自另一方向的杂散光的影响。此外,在这种情况下,基板502应更薄并且包括透明且绝缘的材料以使光通过,从而避免影像模糊(image blur)。举例来说,基板502可包括氧化硅(SiO<sub>x</sub>)、氮化硅(SiN<sub>x</sub>)、玻璃或其他合适材料,但不限定于此。

[0164] 在一个实施例中,光感测装置在一个像素中包括两个双栅极薄膜晶体管。其中一个双栅极薄膜晶体管是在上述实施例中具有开口区的双栅极薄膜晶体管,另一个是在上述实施例中没有开口区的双栅极薄膜晶体管(参考晶体管)。

[0165] 图6显示了根据本申请实施例的光感测装置的示意图。光感测装置600包括双栅极薄膜晶体管602、双栅极薄膜晶体管604以及差分减法器电路606。根据上面所讨论的实施例,双栅极薄膜晶体管602包括金属层602-1、开口区602-2以及透明导电层602-3。双栅极薄膜晶体管604与双栅极薄膜晶体管602相邻,并且包括金属层604-1和透明导电层604-3。然而,双栅极薄膜晶体管602与双栅极薄膜晶体管604不同,因为双栅极薄膜晶体管604没有开口区。换句话说,金属层604-1覆盖透明导电层604-3(金属层604-1在透明导电层604-3上方)。如图6所示,双栅极薄膜晶体管602的源极/漏极端子和双栅极薄膜晶体管604的源极/漏极端子个别地电性连接至差分减法器电路606的两个输入端子,并且其中通过(或不通过)电压检测器和缓冲电路。当光照射至光感测装置600时,双栅极薄膜晶体管602和604各自通过源极/漏极端子产生输出数据到电压检测器和缓冲电路。电压检测器和缓冲电路接收输出数据,并且将输出数据转换成表示输出数据和参考电压(VREF)之间的电压差(也称为电压的下降量,将在下面讨论)的另一输出数据。电压检测器和缓冲电路亦具有另一个缓冲电路,用于减少小输入阻抗(small input impedance)对后续电路或长输出布线(longoutput wiring)的影响。

[0166] 差分减法器电路606比较来自双栅极薄膜晶体管602和604的源极/漏极端子(或来自电压检测器和缓冲电路)的两个输出数据,并且接着输出双栅极薄膜晶体管602和604的差值。双栅极薄膜晶体管602和604以大抵相同的制程制造。由于双栅极薄膜晶体管604没有开口区,因此双栅极薄膜晶体管604不能感测光。因此,在此实施例中,当光感测装置600感测到光时,光感测装置600可以借由比较来自两个双栅极薄膜晶体管的两个输数据来消除由制程和外源噪声(exogenous noise)引起的双栅极薄膜晶体管的特性的变化。此外,应注意差分减法器电路606可以是任何合适差分减法器电路。图6中所示的差分减法器电路606仅为示例,并不限制本申请。在一些实施例中,每多个通常晶体管(具有开口区的双栅极薄膜晶体管,例如双栅极薄膜晶体管602)放置一个参考晶体管(没有开口区的双栅极薄膜晶体管,例如双栅极薄膜晶体管604),以增加可用面积。应理解开口区的面积或形状仅为示例,并不限制本申请。

[0167] 在一个实施例中,光感测装置700在一个像素中包括多个双栅极薄膜晶体管。那些双栅极薄膜晶体管具有开口区(如上面所述),然而,那些双栅极薄膜晶体管的开口区的面

积是不同的。图7显示了根据本申请实施例的光感测装置的示意图。光感测装置700包括双 栅极薄膜晶体管702、双栅极薄膜晶体管704、双栅极薄膜晶体管706以及比较器电路708。双 栅极薄膜晶体管702、704以及706各自具有开口区702-2、704-2以及706-2,如上面所述的双 栅极薄膜晶体管的实施例。此外,双栅极薄膜晶体管702、704以及706彼此相邻。

如图7所示,开口区702-2、704-2以及706-2的面积不同。开口区706-2的长度L3大 于开口区702-1和704-1的长度L1和L2。开口区704-2的长度L2大于开口区702-2的长度L1。 具体来说,在此实施例中,开口区706-2的面积最大,并且开口区702-2的面积最小。双栅极 薄膜晶体管702、704以及706的开口区具有不同的面积,双栅极薄膜晶体管702、704以及706 可能受到光的不同影响,因此输出不同的数据。应理解开口区的面积或形状仅为示例,并不 限制本申请。

双栅极薄膜晶体管702的源极/漏极端子、双栅极薄膜晶体管704的源极/漏极端子 [0169] 以及双栅极薄膜晶体管706的源极/漏极端子个别地电性连接至比较器电路708的输入端 子,并且其中通过(或不通过)电压检测器和缓冲电路。在此实施例中,光感测装置700被光 照射。接着,比较器电路708将来自双栅极薄膜晶体管702、704以及706的每个输出数据个别 地与既定量的光进行比较,并且输出二元数据(binary data)。借由取得哪个双栅极薄膜晶 体管输出"1"(源极/漏极输出"高电压电位"),可以将光感测的强度作为数字数据接收。因 此,双栅极薄膜晶体管702、704以及706的输出组合可以被编码作为与光感测装置700所感 测的光对应的2比特数据。值得注意的是,比较器电路708可以是任何合适比较器电路。

举例来说,下面表格显示了当光感测装置700感测到四种不同的光强度(对应于不 [0170] 同的灰度级(gray scale level))时,双栅极薄膜晶体管702、704以及706的输出数据和对 应的2比特数据。

| [0171] | 光的数据编码 (4 级灰度) |                          |                          |                          |        |

|--------|----------------|--------------------------|--------------------------|--------------------------|--------|

|        | 感 测 的光的灰度级     | 栅 极 薄<br>膜晶体管 702<br>的输出 | 栅 极 薄<br>膜晶体管 704<br>的输出 | 栅 极 薄<br>膜晶体管 706<br>的输出 | 2 比特数据 |

|        | 0              | 0                        | 0                        | 0                        | 00     |

|        | 1              | 0                        | 0                        | 1                        | 01     |

|        | 2              | 0                        | 1                        | 1                        | 10     |

|        | 3              | 1                        | 1                        | 1                        | 11     |

如表格所示,双栅极薄膜晶体管702、704以及706有四种不同的输出组合,对应四 种光的灰度级。这些输出组合可以编码为2比特数据"00"、"01"、"10"以及"11"。因此,光的 灰度级或光的强度可以作为数字数据进行传输。在另一个实施例中,因为双栅极薄膜晶体 管702、704以及706的开口区具有不同的面积,因此,当光的强度增大时,光的灰度级或传输 的数字数据增加。在一些实施例中,如图7所示,来自具有开口区的双栅极薄膜晶体管的每 个输出数据借由每个A/D转换器编码,以接收比起使用一个具有开口区的双栅极薄膜晶体 管更精细的比特。光感测装置700包括三个双栅极薄膜晶体管702、704以及706,然而,应理 解在一些实施例中,光感测装置可包括多个双栅极薄膜晶体管,例如四个双栅极薄膜晶体

管或更多。

[0173] 上面所述的双栅极薄膜晶体管用来作为光感测装置。在一些实施例中,上面所述的双栅极薄膜晶体管可以与显示装置组合,例如有机发光二极管显示装置、量子发光二极管显示装置、小型发光(mini light emitting)二极管显示装置,微型发光(micro light emitting)二极管显示装置,或者液晶显示装置,但不限于此。多个双栅极薄膜晶体管用来作为显示装置中的光感测区,以感测光或物体(例如:指纹图案)。举例来说,光感测区可用于感测指纹图案。双栅极薄膜晶体管的结构和制程与在显示装置中的薄膜晶体管(TFT)的制程相同或相似。因此,可以同时形成用于光感测区的双栅极薄膜晶体管和用于显示器的像素的薄膜晶体管。

[0174] 图8A和图8B显示了根据本申请实施例的与光感测装置组合的显示装置的示意图。电子装置800包括区域802、区域804、栅极驱动电路806、栅极驱动电路808以及和集成电路(integrated circuit;IC)810。区域802用于显示影线,区域804用于同时感测光或物体(例如:指纹图案)或显示影线且感测光或物体,但不限于此。多个双栅极薄膜晶体管设置在区域804中。区域802与区域804分开。在一些实施例中,栅极驱动电路806用于控制区域802,并且栅极驱动电路808用于控制区域804,如图8A所示。在其他实施例中,栅极驱动电路806不仅用于控制区域802,还用于控制区域804的一部分,并且栅极驱动电路808用于控制区域804的其他部分,如图8B所示。

[0175] 如图8A和图8B所示,区域802与区域804分开。具体来说,用于感测的双栅极薄膜晶体管未整合到显示区中。在一些实施例中,双栅极薄膜晶体管被整合到显示区中。因此,显示区可用来显示影线或感测光或物体。下面讨论用作光感测的双栅极薄膜晶体管和在显示装置的薄膜晶体管整合。

图9显示了根据本申请实施例的整合到在液晶显示器(Liquid Crystal Display; LCD) 中的显示区的薄膜晶体管阵列中的双栅极薄膜晶体管阵列。为了方便起见,图9仅显示 了全阵列(full array)的一部分。阵列900包括布置在全阵列的行(column)n、n+1和列 (row) n、n+1中的四个薄膜晶体管902、四个电容904以及四个双栅极薄膜晶体管906。每个双 栅极薄膜晶体管906与薄膜晶体管902中的一者相邻(或一个薄膜晶体管902与双栅极薄膜 晶体管906中的一者相邻)。双栅极薄膜晶体管906的上栅极(例如:金属层212)电性连接到 线路908(亦称为上栅极线)、双栅极薄膜晶体管906的下栅极电性连接到线路910(亦称为下 栅极线)、双栅极薄膜晶体管906的一个源极/漏极端子电性连接到线路912(亦称为读出线 (readout line))、以及双栅极薄膜晶体管906的另一个源极/漏极端子电性连接到线路914 (亦称为地线)。同一列中的双栅极薄膜晶体管906电性连接到同一条线路908、线路910、线 路914,并且同一行中的双栅极薄膜晶体管906电性连接到同一条线路912,如图9所示。薄膜 晶体管902的栅极电性连接到线路916(亦称为栅极线)、薄膜晶体管902的一个源极/漏极端 子电性连接到线路918(亦称为数据线)、以及薄膜晶体管902的另一个源极/漏极端子通过 一个电容904电性连接到线路920(也称为共线(common line))。同一列中的薄膜晶体管902 电性连接到同一条线路916、线路920,并且同一行中的薄膜晶体管902电性连接到同一条线 路918,如图9所示。使用该实施例中的布置,阵列900可以用来作为显示装置,并且可以感测 光和物体(例如:指纹图案)。

[0177] 图10A显示了根据本申请实施例的在图9中的阵列的一部分。为了方便起见,两个

薄膜晶体管902、两个电容904以及两个双栅极薄膜晶体管906排列在行n和列n、n+1中。如图 10A所示,双栅极薄膜晶体管906的一个源极/漏极端子借由线路912和开关SW电性连接到参考电压VREF。可以借由对线路916施加栅极关闭 (0FF) 电压 (例如:-10V) 来关闭用于液晶显示器的薄膜晶体管902。当对双栅极薄膜晶体管906的上栅极施加导通 (0N) 电压 (例如:+5V) 时,线路912电性连接到线路914。当对双栅极薄膜晶体管906的上栅极施加关闭 (0FF) 电压 (例如:-10V) 时,线路912变为浮动 (floating)。线路912亦通过电压测量线电性连接到电压检测器 (或电压检测器和缓冲电路)。在此实施例中,当双栅极薄膜晶体管906感测物体 (例如:指纹图案) 时,对双栅极薄膜晶体管906的下栅极施加导通 (0N) 电压 (例如:+15V)。

[0178] 图10B是在图10A中的阵列900的光感测的时序图。为了防止由在液晶显示器中的各种液晶(liquid-crystal;LC)排列所引起的散射或延迟引起的感测误差,可以在双栅极薄膜晶体管906感测光或物体之前将显示影像改变为白色或黑色,但不限定于此。如图10B所示,在周期1中(即在双栅极薄膜晶体管906开始感测光或物体之前),在列n中的线路916切换到"高电压电位",并且线路918切换到偏压电位(biased voltage level),使得在列n中的像素改变为白色(或黑色)。在列n+1中的线路916接着切换到"高电压电位",并且线路918切换到偏压电位,使得在列n+1中的像素改变为白色(或黑色)。尽管在图10A中仅显示了阵列的两个列(n、n+1),但应理解此操作可以重复应用于在液晶显示器中的整个阵列的所有例,使得在液晶显示器中的所有像素都改变为白色(或黑色)。

[0179] 在周期2中(即双栅极薄膜晶体管906开始感测光或物体),在列n中的线路908切换到"高电压电位",使得在列n的双栅极薄膜晶体管906中的剩余电荷可被移除。开关SW接着切换到"高电压电位",使得线路912可以电性连接到参考电压VREF(即线路912切换到"高电压电位")。接着,在列n中的线路910切换到"高电压电位",从而在列n中的双栅极薄膜晶体管906可以感测光或物体。如果从物体反射的光(例如:反射光)照射到双栅极薄膜晶体管906,则双栅极薄膜晶体管906的临界电压(Vth)将不同。此Vth差异导致线路912通过在列n中的双栅极薄膜晶体管906漏电到线路914,使得线路912的电压由于漏电而下降。举例来说,如图10B所示,线路912的电压可能由于在列n中的双栅极薄膜晶体管906的漏电而下降。由于光的不同亮度电位(bright level)影响Vth差异,列n中的双栅极薄膜晶体管906的漏电也将不同。这导致线路912的电压的不同下降量,如图10B所示(实线和虚线)。列n中的双栅极薄膜晶体管906可以检测来自物体的光的亮度电位。在列n中的双栅极薄膜晶体管906检测之后,在列n+1中的双栅极薄膜晶体管906检测开始,并且以相同的方式重复每一列的检测。因此,阵列900可以感测光和物体。

[0180] 图11显示了根据本申请实施例的整合到在液晶显示器中的显示区的薄膜晶体管阵列中的双栅极薄膜晶体管阵列。为了方便起见,图11仅显示了全阵列的一部分。阵列1100包括布置在全阵列的行n、n+1和列n、n+1中的四个薄膜晶体管1102、四个电容1104以及四个双栅极薄膜晶体管1106。每个双栅极薄膜晶体管1106与薄膜晶体管1102中的一者相邻。双栅极薄膜晶体管1106的上栅极(金属层)电性连接到线路1108(亦称为上栅极线)、双栅极薄膜晶体管1106的下栅极电性连接到线路1110(亦称为下栅极线)、双栅极薄膜晶体管1106的一个源极/漏极端子电性连接到线路1112、以及双栅极薄膜晶体管1106的另一个源极/漏极端子电性连接到线路1114(亦称为共线)。同一列中的双栅极薄膜晶体管1106电性连接到同一条线路1108、线路1110、线路1114,并且同一行中的双栅极薄膜晶体管1106电性连接到同

一条线路1112,如图11所示。薄膜晶体管1102的栅极电性连接到线路1108、薄膜晶体管1102的一个源极/漏极端子电性连接到线路1112、以及薄膜晶体管1102的另一个源极/漏极端子通过一个电容1104电性连接到线路1114。同一列中的薄膜晶体管1102电性连接到同一条线路1108、线路1114,并且同一行中的薄膜晶体管1102电性连接到同一条线路1112,如图11所示。

[0181] 如图11所示,同一列中的薄膜晶体管1102的栅极和与薄膜晶体管1102相邻的双栅极薄膜晶体管1106的上栅极电性连接到同一条线路1108。换句话说,薄膜晶体管1102的栅极连接至与薄膜晶体管1102相邻的双栅极薄膜晶体管1106的上栅极(例如:金属层212)。薄膜晶体管1102的一个源极/漏极端子和与薄膜晶体管1102相邻的双栅极薄膜晶体管1106的一个源极/漏极端子电性连接到同一条线路1112。换句话说,薄膜晶体管1102的一个源极/漏极端子电性连接至与薄膜晶体管1102相邻的双栅极薄膜晶体管1106的一个源极/漏极端子。线路1108可被称为栅极线(用于薄膜晶体管)或上栅极线(用于双栅极薄膜晶体管)。线路1112可被称为数据线(用于薄膜晶体管)或读出线(用于双栅极薄膜晶体管)。使用这种布置,阵列1100可以用来作为显示装置,并且可以感测光和物体(例如:指纹图案)。

[0182] 图12A显示了根据本申请实施例的在图11中的阵列的一部分。为了方便起见,两个薄膜晶体管1102、两个电容1104以及两个双栅极薄膜晶体管1106排列在行n和列n、n+1中。如图12A所示,同一列中的薄膜晶体管1102的一个源极/漏极端子和双栅极薄膜晶体管1106的一个源极/漏极端子借由线路1112和开关SW电性连接到参考电压VREF或液晶显示器的数据电压。线路1114的电压与地(GND)相同。在薄膜晶体管1102的操作周期中,双栅极薄膜晶体管1106应关闭(例如:双栅极薄膜晶体管1106的下栅极的电压是-10V),使得线路1114不会电性连接至线路1112。

[0183] 图12B是在图12A中的阵列1100的光感测的时序图。如图12B所示,在周期1中(即在双栅极薄膜晶体管1106开始感测光或物体之前),在列n中的线路1108切换到"高电压电位",并且线路1112切换到偏压电位,使得在列n中的像素改变为白色(或黑色)。在列n+1中的线路1108接着切换到"高电压电位",并且线路1112切换到偏压电位,使得在列n+1中的像素改变为白色(或黑色)。线路1114保持在"低(low)"(例如:在GND中)。线路1110保持在"低"以关闭双栅极薄膜晶体管1106,使得线路1114不通过双栅极薄膜晶体管1106电性连接到线路1112,如上面所述。尽管在图12A中仅显示了阵列的两个列(n、n+1),但应理解此操作可以重复应用于在液晶显示器中的整个阵列的所有列,使得在液晶显示器中的所有像素都改变为白色(或黑色)。

[0184] 在周期2中(即双栅极薄膜晶体管1106开始感测光或物体),在列n中的线路1108切换到"高电压电位",使得在列n的双栅极薄膜晶体管1106中的剩余电荷可被移除。开关SW接着切换到"高电压电位",使得线路1112可以电性连接到参考电压VREF。接着,在列n中的线路1110切换到"高电压电位",从而在列n中的双栅极薄膜晶体管1106可以感测光或物体。如果来自物体的光(例如:反射光)照射到双栅极薄膜晶体管1106,则双栅极薄膜晶体管1106的临界电压(Vth)将不同。此Vth差异导致线路1112通过在列n中的双栅极薄膜晶体管1106漏电到线路1114,使得线路1112的电压由于漏电而下降。举例来说,如图128所示,线路1112的电压可能由于在列n中的双栅极薄膜晶体管1106的漏电而下降。由于光的不同亮度电位影响Vth差异,列n中的双栅极薄膜晶体管1106的漏电也将不同。这接着导致线路1112的电

压的不同下降量,如图12B所示(实线和虚线)。列n中的双栅极薄膜晶体管1106可以检测来自物体的光的亮度电位。在列n中的双栅极薄膜晶体管1106检测之后,在列n+1中的双栅极薄膜晶体管1106检测开始,并且以相同的方式重复每一列的检测。因此,阵列1100可以感测光和物体。

[0185] 图13显示了根据本申请实施例的整合到在发光二极管(LED)显示器中的显示区的 薄膜晶体管阵列中的双栅极薄膜晶体管阵列。为了方便起见,图13仅显示了全阵列的一部 分。阵列1300包括布置在全阵列的行n和列n、n+1中的两个显示单元(display cell)1302和 两个双栅极薄膜晶体管1306。显示单元1302包括薄膜晶体管1304。每个双栅极薄膜晶体管 1306与显示单元1302中的一者(或薄膜晶体管1304中的一者)相邻。双栅极薄膜晶体管1306 的上栅极电性连接到线路1308(亦称为上栅极线)、双栅极薄膜晶体管1306的下栅极电性连 接到线路1310(亦称为下栅极线)、双栅极薄膜晶体管1306的一个源极/漏极端子电性连接 到线路1312(亦称为读出线)、以及双栅极薄膜晶体管1306的另一个源极/漏极端子电性连 接到节点1314。节点1314电性连接到地(GND)。同一列中的双栅极薄膜晶体管1306电性连接 到同一条线路1308和线路1310(未显示),并且同一行中的双栅极薄膜晶体管1306电性连接 到同一条线路1312,如图13所示。薄膜晶体管1304的栅极电性连接到线路1316(亦称为栅极 线)、薄膜晶体管1304的一个源极/漏极端子电性连接到线路1318(亦称为数据线)、以及薄 膜晶体管1304的另一个源极/漏极端子耦接到节点1320。同一列中的显示单元1302电性连 接到同一条线路1316(未显示),并且同一行中的显示单元1302电性连接到同一条线路 1318,如图13所示。使用该实施例中的布置,阵列1300可以用来作为显示装置,并且可以感 测光和物体(例如:指纹图案)。

[0186] 图14A显示了根据本申请实施例的在图13中的阵列的一部分。如图14A所示,双栅极薄膜晶体管1306的一个源极/漏极端子借由线路1312和开关SW电性连接到参考电压VREF。可以借由对线路1316施加栅极关闭(0FF)电压(例如:-10V)来关闭用于发光二极管显示器的薄膜晶体管1304。当对双栅极薄膜晶体管1306的上栅极施加导通(0N)电压(例如:+5V)时,线路1312电性连接到节点1314。当对双栅极薄膜晶体管1306的上栅极施加关闭(0FF)电压(例如:-10V)时,线路1312变为浮动。线路1312亦通过电压测量线电性连接到电压检测器(或电压检测器和缓冲电路)。在此实施例中,当双栅极薄膜晶体管1306感测物体(例如:指纹图案)时,对双栅极薄膜晶体管1306的下栅极施加导通(0N)电压(例如:+15V)。

[0187] 图14B是在图14A中的阵列1300的光感测的时序图。在此实施例中,如图14B所示,在周期1中(即在双栅极薄膜晶体管1306开始感测光或物体之前),在列n中的线路1316切换到"高电压电位",并且线路1318切换到偏压电位,使得在列n中的像素改变为白色。在列n+1中的线路1316接着切换到"高电压电位",并且线路1318切换到偏压电位,使得在列n+1中的像素改变为白色。尽管在图14A中仅显示了阵列的两个列(n、n+1),但应理解此操作可以重复应用于在发光二极管显示器中的整个阵列的所有列,使得在发光二极管显示器中的所有像素都改变为白色。

[0188] 在周期2中(即双栅极薄膜晶体管1306开始感测光或物体),在列n中的线路1308切换到"高电压电位",使得在列n的双栅极薄膜晶体管1306中的剩余电荷可被移除。开关SW接着切换到"高电压电位",使得线路1312可以电性连接到参考电压VREF。接着,在列n中的线路1310切换到"高电压电位",从而在列n中的双栅极薄膜晶体管1306可以感测光或物体。如

果来自物体的光 (例如:反射光) 照射到双栅极薄膜晶体管1306,则双栅极薄膜晶体管1306的临界电压 (Vth) 将不同。此Vth差异导致线路1312通过在列n中的双栅极薄膜晶体管1306漏电到节点1314 (电性连接至地 (GND)),使得线路1312的电压由于漏电而下降。举例来说,如图14B所示,线路1312的电压可能由于在列n中的双栅极薄膜晶体管1306的漏电而下降。由于光的不同亮度电位影响Vth差异,列n中的双栅极薄膜晶体管1306的漏电也将不同。这接着导致线路1312的电压的不同下降量,如图14B所示 (实线和虚线)。列n中的双栅极薄膜晶体管1306可以检测来自物体的光的亮度电位。在列n中的双栅极薄膜晶体管1306检测之后,在列n+1中的双栅极薄膜晶体管1306检测开始,并且以相同的方式重复每一列的检测。因此,阵列1300可以感测光和物体。

[0189] 图15显示了根据本申请实施例的整合到在发光二极管显示器中的显示区的薄膜晶体管阵列中的双栅极薄膜晶体管阵列。为了方便起见,图15仅显示了全阵列的一部分。阵列1500包括布置在全阵列的行n和列n中的一个显示单元1502和一个双栅极薄膜晶体管1506。显示单元1502包括薄膜晶体管1504。每个双栅极薄膜晶体管1506与显示单元1502中的一者(或薄膜晶体管1504中的一者)相邻。双栅极薄膜晶体管1506的上栅极电性连接到线路1508(亦称为上栅极线)、双栅极薄膜晶体管1506的下栅极电性连接到线路1510(亦称为下栅极线)、双栅极薄膜晶体管1506的一个源极/漏极端子电性连接到线路1512、以及双栅极薄膜晶体管1506的另一个源极/漏极端子电性连接到节点1514。节点1514电性连接到地(GND)。薄膜晶体管1504的栅极电性连接到线路1508、薄膜晶体管1504的一个源极/漏极端子电性连接到线路1512、以及薄膜晶体管1504的另一个源极/漏极端子电性连接到线路1512、以及薄膜晶体管1504的另一个源极/漏极端子电性连接到线路1512、以及薄膜晶体管1504的另一个源极/漏极端子通过发光二极管(LED)装置耦接到节点1514。

[0190] 如图15所示,薄膜晶体管1504的栅极和与薄膜晶体管1504相邻的双栅极薄膜晶体管1506的上栅极电性连接到同一条线路1508。换句话说,薄膜晶体管1504的栅极连接至与薄膜晶体管1504相邻的双栅极薄膜晶体管1506的上栅极。薄膜晶体管1504的一个源极/漏极端子电性连接到同一条线路1512。换句话说,薄膜晶体管1504的一个源极/漏极端子电性连接至与薄膜晶体管1504相邻的双栅极薄膜晶体管1504的一个源极/漏极端子电性连接至与薄膜晶体管1504相邻的双栅极薄膜晶体管1506的一个源极/漏极端子。线路1508可被称为栅极线(用于薄膜晶体管)或上栅极线(用于双栅极薄膜晶体管)。线路1512可被称为数据线(用于薄膜晶体管)或读出线(用于双栅极薄膜晶体管)。使用这种布置,阵列1500可以用来作为显示装置,并且可以感测光和物体(例如:指纹图案)。

[0191] 图16A显示了根据本申请实施例的发光二极管显示器的全阵列的一部分。为了方便起见,两个显示单元1502、两个薄膜晶体管1504以及两个双栅极薄膜晶体管1506排列在行n和列n、n+1中。如图16A所示,薄膜晶体管1504的一个源极/漏极端子和双栅极薄膜晶体管1506的一个源极/漏极端子借由线路1512和开关SW电性连接到参考电压VREF或发光二极管显示器的数据电压。如上面所述,节点1514电性连接到地(GND)。在薄膜晶体管1504的操作周期中,双栅极薄膜晶体管1506应关闭(例如:双栅极薄膜晶体管1506的下栅极的电压是-10V),使得节点1514不会电性连接至线路1512。

[0192] 图16B是在图16A中的阵列1500的光感测的时序图。如图16B所示,在周期1中(即在双栅极薄膜晶体管1506开始感测光或物体之前),在列n中的线路1508切换到"高电压电位",并且线路1512切换到偏压电位,使得在列n中的像素改变为白色。在列n+1中的线路

1508接着切换到"高电压电位",并且线路1512切换到偏压电位,使得在列n+1中的像素改变为白色。节点1514保持在"低"(例如:在GND中)。线路1510保持在"低"以关闭双栅极薄膜晶体管1506,使得节点1514不通过双栅极薄膜晶体管1506电性连接到线路1512,如上面所述。尽管在图16A中仅显示了阵列的两个列(n、n+1),但应理解此操作可以重复应用于在发光二极管显示器中的整个阵列的所有列,使得在发光二极管显示器中的所有像素都改变为白色。

[0193] 在周期2中(即双栅极薄膜晶体管1506开始感测光或物体),在列n中的线路1508切换到"高电压电位",使得在列n的双栅极薄膜晶体管1506中的剩余电荷可被移除。开关SW接着切换到"高电压电位",使得线路1512可以电性连接到参考电压VREF。接着,在列n中的线路1510切换到"高电压电位",从而在列n中的双栅极薄膜晶体管1506可以感测光或物体。如果来自物体的光(例如:反射光)照射到双栅极薄膜晶体管1506,则双栅极薄膜晶体管1506的临界电压(Vth)将不同。此Vth差异导致线路1512通过在列n中的双栅极薄膜晶体管1506漏电到节点1514(电性连接至地(GND)),使得线路1512的电压由于漏电而下降。举例来说,如图16B所示,线路1512的电压可能由于在列n中的双栅极薄膜晶体管1506的漏电而下降。由于光的不同亮度电位影响Vth差异,列n中的双栅极薄膜晶体管1506的漏电也将不同。这接着导致线路1512的电压的不同下降量,如图16B所示(实线和虚线)。列n中的双栅极薄膜晶体管1506可以检测来自物体的光的亮度电位。在列n中的双栅极薄膜晶体管1506检测之后,在列n+1中的双栅极薄膜晶体管1506检测之

[0194] 值得注意的是,用于感测的双栅极薄膜晶体管的上栅极和下栅极的操作(即施加到双栅极薄膜晶体管的上栅极和下栅极的电压)可以交换。换句话说,双栅极薄膜晶体管的下栅极可以切换到"高电压电位"以移除双栅极薄膜晶体管中的剩余电荷,并且双栅极薄膜晶体管的上栅极可以切换到"高电压电位"以使双栅极薄膜晶体管感测光或物体。此外,在图9至图16的实施例中所讨论的薄膜晶体管和双栅极薄膜晶体管是n通道类型(n-channel type)。然而,在其他实施例中,应理解可以应用p通道类型的薄膜晶体管和双栅极薄膜晶体管。各实施例间特征只要不违背发明精神或相冲突,均可任意混合搭配使用。

[0195] 此处所使用的术语仅用于描述特定实施例的目的,并且不限制本申请。如此处所使用的,除非上下文另外清楚的指出,否则单数形式"一"、"一个"以及"该"意旨在也包括复数形式。此外,就被用于详细描述及/或权利要求书中的"囊括"、"包含"、"具有"、"有"、"含"或其变体的术语来说,这些术语旨在以相似于"包括"的方式而具有包容性。

[0196] 除非另外定义,否则此处所使用的所有术语(包括技术和科学术语)具有与本领域技术人员通常理解的相同含义。此外,诸如在通用字典中定义的那些术语应该被解释为具有与其在相关领域的上下文中的含义中相同的含义,并且不会被理解为理想化或过度正式,除非在此处有明确地如此定义。

[0197] 虽然本发明已以较佳实施例揭示如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的修改和完善,因此本发明的保护范围当以权利要求书所界定的为准。

图1B

图2A

图2B

图2C

图2D

图3

图4A

图4B

图4C

图4D

图5

图6

图7

图8A

图8B

图9

图10B

图11

图12A

图12B

图13

42

图14B

图15

图16B