(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第5039277号 (P5039277)

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月13日(2012.7.13)

(51) Int. Cl. F. L.

**G11C** 11/4074 (2006.01) G11C 11/34 **G11C** 11/4096 (2006.01) G11C 11/34

請求項の数 14 (全 14 頁)

(21) 出願番号 特願2004-377173 (P2004-377173) (22) 出願日 平成16年12月27日 (2004.12.27)

(65) 公開番号 特開2006-18984 (P2006-18984A)

(43) 公開日 平成18年1月19日 (2006.1.19) 審査請求日 平成19年3月16日 (2007.3.16)

(31) 優先権主張番号 2004-049912

(32) 優先日 平成16年6月30日 (2004.6.30)

(33) 優先権主張国 韓国 (KR)

||(73)特許権者 310024033

354F

354R

エスケーハイニックス株式会社 SK hynix Inc.

大韓民国京畿道利川市夫鉢邑京忠大路20

91

2091, Gyeongchung-daero, Bubal-eub, Icheon-si, Gyeonggi-do, Korea

(74)代理人 100118913

弁理士 上田 邦生

|(74)代理人 100112737

弁理士 藤田 考晴

|(74)代理人 100136168

弁理士 川上 美紀

最終頁に続く

(54) 【発明の名称】入出力回路

### (57)【特許請求の範囲】

### 【請求項1】

メモリセルを含むコア領域と入出力ピンの周辺領域との間のデータ移動経路を形成する 入出カライン回路と、

前記コア領域にコア電圧を駆動電圧として付与するコア電圧発生器と;

入出力ピンの周辺領域に内部電圧を駆動電圧として付与する内部電圧発生器とを備えた 半導体メモリにおいて、

前記入出力ライン回路は、前記コア領域に格納されたデータを外部に出力するための出力ラインブロックと、外部から入力されたデータを前記コア領域内のメモリセルに格納するための入力ラインブロックとを備え、

読出しイネーブル信号に応じて活性化されて前記出力ラインブロックにライン電圧を付与する読出しライン電源生成部と、書込みイネーブル信号に応じて活性化されて前記入力ラインブロックにライン電圧を付与する書込みライン電源生成部とにより構成したライン電圧発生器を、複数のメモリBANKにそれぞれ備えるか或いは2個のメモリBANK毎にそれぞれ備えて基板上に配置して、前記入出力ライン回路に安定した電圧を供給されるようにしたことを特徴とする半導体メモリ素子。

# 【請求項2】

前記出カラインブロックが、

前記コア領域から出力されたデータを感知して増幅するための出力センスアンプ部と、 該出力センスアンプ部から増幅されたデータを受け取って前記周辺領域にデータを移動

させるための読出し用グローバル入出力ラインと、

該読出し用グローバル入出力ラインに載せられたデータを感知してラッチした後、前記 周辺領域の入出力ピンに出力するための読出しラッチング部と

を備えることを特徴とする請求項1に記載の半導体メモリ素子。

### 【請求項3】

前記入力ラインブロックが、

外部から入力されたデータを判定してラッチし、出力するための書込みラッチブロックと、

前記書込みラッチブロックからデータを受け取って、同データを前記コア領域に移動させるグローバル入出力ラインと、

該グローバル入出力ラインに載せられたデータを、前記コア領域の内部データ入出力ラインに送信するための書込みドライバブロックと

を備えることを特徴とする請求項1に記載の半導体メモリ素子。

### 【請求項4】

前記入力ラインブロックを制御するための入力制御ブロックと、

前記出カラインブロックを制御するための出力制御ブロックとを備え、

前記入力制御ブロック及び出力制御ブロックが、前記内部電圧を駆動電圧として使用することを特徴とする請求項1に記載の半導体メモリ素子。

### 【請求項5】

前記周辺領域と外部とを接続するために入出力パッドに接続された入力バッファ及び出力バッファに、インターフェス電圧を駆動電圧として供給するためのインターフェス電圧発生器をさらに備えることを特徴とする請求項1に記載の半導体メモリ素子。

#### 【請求項6】

素子内のコア領域から入出力ピンの周辺領域にデータを移動させるための複数の読出し 用グローバル入出力ラインと、

コア内部の入出力ラインに載せられたデータを感知して増幅するためのIOセンスアンプ部と、

前記読出し用グローバル入出力ラインに載せられたデータを感知してステップラッチした後、入出力ピンに出力するための読出しラッチング部と、

読出しイネーブル信号に応じてイネーブルされて外部電源電圧を印加され、前記IOセンスアンプ部及び読出しラッチング部に駆動電源を供給する読出しライン電源生成部とを備えることを特徴とする半導体メモリ素子における入出力ライン回路。

#### 【請求項7】

前記読出しライン電源生成部が、

前記IOセンスアンプ部に駆動電源を供給するためのコア読出しライン電源生成部と、前記読出しラッチング部に駆動電源を供給するための周辺読出しライン電源生成部とを備えることを特徴とする請求項6に記載の半導体メモリ素子における入出力ライン回路

### 【請求項8】

前記コア読出ライン電源生成部と前記周辺読出しライン電源生成部が、

カラムアドレスストローブ信号のイネーブル時に、共にイネーブルされることを特徴と する請求項 7 に記載の半導体メモリ素子における入出力ライン回路。

### 【請求項9】

素子内の周辺領域からコア領域にデータを移動させるための複数の書き込み用グローバル入出力ラインと、

入出力ピンから受け取ったデータを判定してラッチし、前記複数の書込み用グローバル 入出力ラインに出力するための書込みラッチブロックと、

前記複数の書込み用グローバル入出力ラインに載せられたデータを前記コア領域内部の データ入出力ラインに送信するための書込みドライバブロックと、

書込みイネーブル信号に応じてイネーブルされたとき外部電源電圧を印加されて前記書

10

20

30

40

込みラッチブロック及び書込みドライバブロックに駆動電源を供給する書込みライン電源 生成部とを備えることを特徴とする半導体メモリ素子における入出力ライン回路。

### 【請求項10】

前記書込みライン電源生成部が、

前記書込みラッチブロックに駆動電源を供給するための周辺書込みライン電源生成部と

前記書込みドライバブロックに駆動電源を供給するためのコア書込み電源生成部とを備えることを特徴とする請求項9に記載の半導体メモリ素子における入出力ライン回路。

#### 【請求項11】

前記書込みライン電源生成部が、

カラムアドレスストローブ信号のイネーブル時にイネーブルされることを特徴とする請求項10に記載の半導体メモリ素子における入出力ライン回路。

### 【請求項12】

素子内のコア領域から入出力ピンの周辺領域にデータを移動させるための複数の読出し 用グローバル入出力ラインと、

前記素子内の周辺領域から前記コア領域にデータを移動させるための複数の書込み用グローバル入出カラインと、

コア内部の入出力ラインに載せられたデータを感知し、増幅するためのIOセンスアン プ部と、

前記読出し用グローバル入出力ラインに載せられたデータを感知してステップラッチした後、前記入出力ピンに出力するための読出しラッチング部と、

前記入出力ピンから受け取ったデータを判定してラッチし、前記書込み用グローバル入出力ラインに出力するための書込みラッチブロックと、

前記書込み用グローバル入出力ラインに載せられたデータを、前記コア領域内部のデータ入出力ラインに送信するための書込みドライバブロックと、

読出しイネーブル信号に応じてイネーブルされて外部電源電圧を印加され、前記IOセンスアンプ部及び読出しラッチング部に駆動電源を供給し、書込みイネーブル信号に応じてイネーブルされて外部電源電圧を印加され、前記書込みラッチブロック及び書込みドライバブロックに駆動電源を供給するライン電源発生器とを備え、

前記ライン電源発生器が、

<u>読出し</u>イネーブル信号に応じて活性化されて前記IOセンスアンプ部及び読出しラッチング部に駆動電源を供給するための読出しライン電源生成部と、

<u>書込み</u>イネーブル信号に応じて活性化されて前記書込みラッチブロック及び書込みドライバブロックに駆動電源を供給するための書込みライン電源生成部とを備えることを特徴とする半導体メモリ素子における入出力ライン回路。

### 【請求項13】

前記ライン電源発生器が、

前記読出しラッチング部及び書込みラッチブロックに駆動電源を供給するための周辺ライン電源生成部と、

前記IOセンスアンプ部及び書込みドライバブロックに駆動電源を供給するためのコア 40 ライン電源生成部と

を備えることを特徴とする請求項12に記載の半導体メモリ素子における入出力ライン回路。

# 【請求項14】

前記ライン電源発生器が、

カラムアドレスストローブ信号のイネーブル時にイネーブルされることを特徴とする請求項13に記載の半導体メモリ素子における入出力ライン回路。

【発明の詳細な説明】

### 【技術分野】

[0001]

10

20

30

本発明は、半導体メモリ素子内のデータ入出力回路、特に別の電源供給装置を備えたデータ入出力回路に関する。

### 【背景技術】

### [0002]

一般に、半導体メモリ素子は外部素子とデータ及び命令語等をやり取りするための入力ピンと受け取ったデータを格納するための複数のメモリセルとを有する。この場合、半導体メモリ素子内で前記入力ピンの周辺を周辺領域 (peripheral area)と称し、前記メモリセルを含む領域をコア領域と称する。前記周辺領域とコア領域との間のデータ送信のために、半導体メモリ素子はグローバル入出力ラインを備えている。

### [0003]

最近、半導体メモリ素子の格納容量が増加し、半導体動作速度が増加するに伴なって、グローバル入出力ラインの数及びそれぞれのグローバル入出力ラインを介するデータの送信量も増加する。また、半導体メモリチップの構造上、前記周辺領域とコア領域とは、素子内でかなり隔離されており、これによって、グローバル入出力ラインの長さによってグローバル入出力ラインが有する抵抗もまた大きくなる。したがって、前記グローバル入出力ラインを駆動するためには相当量の駆動電源が必要となる。

### [0004]

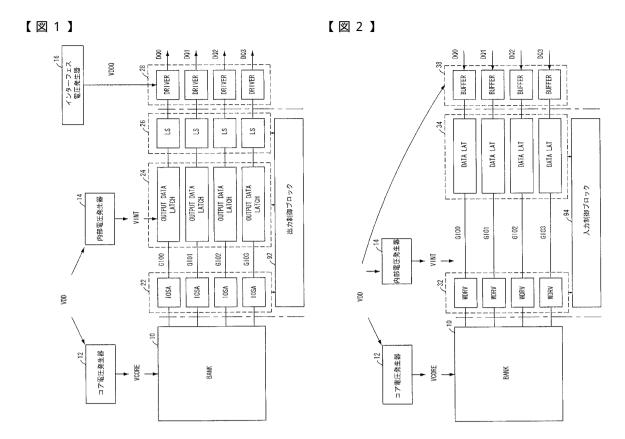

図1は、従来の技術の半導体メモリ素子の読み出し経路を示すブロック図であり、 図2は、従来の技術の半導体メモリ素子の書き込み経路を示すブロック図である。

### [00005]

まず、図1を説明すると、半導体メモリ素子は、外部から<u>印加される</u>電源電圧VDD<u>を</u> <u>コ</u>ア電圧発生器12、内部電圧発生器14及びインターフェス電圧発生器16に供給する 。前記電源電圧VDDを印加されたコア電圧発生器12は、半導体メモリ素子内の複数の セルを含んでいるBANK10で用いられるコア電圧VCOREを生成する。また、内部 電圧発生器14は、外部電源電圧VDDを印加されて所定レベルの内部電圧VINTを生 成し、これをグローバル入出力ラインGIOの駆動電圧として用いている。次いで、イン ターフェス電圧発生器16は、半導体メモリ素子内の出力バッファブロック28で用いら れるインターフェス電圧VDDQを生成する。ここで、インターフェス電圧VDDQと電 源電圧VDDの電圧レベルとは同一である。したがって、インターフェス電圧発生器16 を用いず、電源電圧VDDを出力バッファブロック28に印加することもできる。

### [0006]

前記内部電圧VINTは、周辺領域の回路モジュール等の駆動電源として用いられている。図1に示されているように、前記回路モジュールにはセルから出力されるデータを増幅するためのI/Oセンスアンプブロック22、複数の増幅されたデータをグローバルラインGIO0~GIO3を介し、順に送信されてラッチに一時的に格納し、また順に出力するための出力データラッチブロック24、データの電圧レベルを遷移させるための電圧レベルシフトブロック26、読み出し動作を制御するための出力制御ブロック92とを備える。ここで、出力データラッチブロック24は、パイプライン構造を有する複数のラッチから構成されている。

### [0007]

図2を説明すると、半導体メモリ素子は外部からデータを受け取る入力バッファブロック38、入力バッファブロック38から受け取ったデータをラッチするための入力データラッチブロック34、受け取ったデータをBANK10に送信する書き込みドライブブロック32、前記入力データラッチブロック34と書き込みドライブブロック32を接続するグローバルラインGIO0、GIO1、GIO2、GIO3及び書き込み動作を制御するための入力制御ブロック94とを備える。

#### [00008]

書き込み動作には、BANK10にコア電圧VCOREを供給するためのコア電圧発生器12と、外部電源電圧VDDから所定レベルの内部電圧VINTを生成するための内部電圧発生器14とが用いられる。入力バッファブロック38に図1のようなインターフェ

10

20

30

40

ス電圧生成器16から生成されたインターフェス電圧VDDQを印加することもできるが、ここでは外部から印加された外部電源VDDを使用する場合を示した。書き込み動作では、読み出し動作と異なり、入力バッファブロック38と入力データラッチブロック34との間にレベルシフトが必要ない。高い電圧レベルの電源電圧VDDから低い電圧レベルの内部電圧VINTに論理レベルハイであるデータが送信される時、電流損失が起こらないためである。

#### [0009]

図1及び図2に示されているように、グローバル入出力ラインは読み出し動作及び書き込み動作で共通に用いられている。したがって、読み出し/書き込み動作時、関連ロジック回路モジュールのような内部電源を使用することによって、内部電圧発生器14がグローバル入出力ラインを正常に駆動させるための内部電力VINTの供給の際に負担となり得る。また、グローバル入出力ラインの駆動によって不安定になった内部電圧VINTを使用する他の回路モジュールが非正常的に作動することがある。

# [0010]

また、周辺領域に各モジュールに電源を供給するための内部電圧発生器は、比較的長いRAS期間の間活性化されていなければならない。ところが、グローバル入出力ライン駆動による大きな電力消耗は、比較的短いCAS(column address strobe)期間の間にだけ発生するため、内部電圧発生器を効率的に動作させることが困難であった。

### [0011]

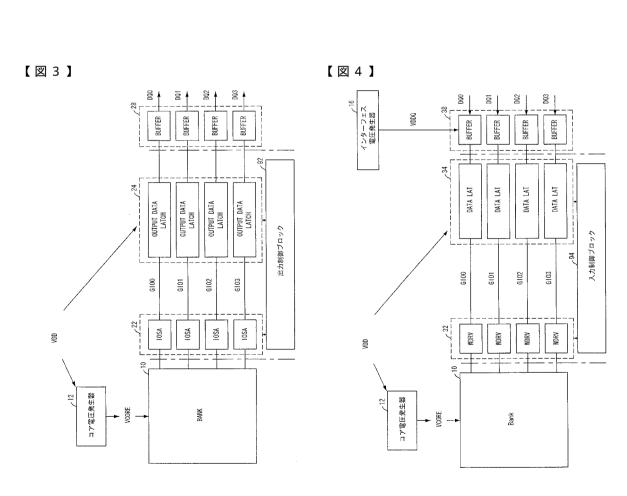

一方、図3は、他の従来の技術の半導体メモリ素子(低電圧用メモリ)の読み出し経路を示すブロック図であり、図4は、他の従来の技術の半導体メモリ素子(低電圧用メモリ)の書き込み経路を示すブロック図である。ここで図1及び図2に説明された構成要素に対しては同一の図面符号を付し、これに対する詳細な説明は省略する。図示された半導体メモリ素子では、周辺領域の回路の大部分に外部電源電圧VDDを駆動電圧として用いている

### [0012]

図3を説明すると、周辺領域で電源電圧 V D D を駆動電圧として用いることによって、レベルシフトブロック26がこれ以上必要がなくなった。周辺領域の駆動電圧である電源電圧 V D D と出力バッファブロック28の駆動電圧であるインターフェス電圧 V D D Q のレベルが同一であるためである。

### [0013]

図4に示されているように、書き込み経路でも周辺領域内の入力データラッチブロック34及び書き込みドライブブロック32に印加される駆動電圧は、内部電圧VINTではない電源電圧VDDであることが分かる。

# [0014]

しかし、図3及び図4は、従来の技術のように外部電源電圧VDDを直接グローバル入出力ライン用の駆動電圧として用いると、過度な負荷によってグローバル入出力ライン上に電力が安定的に供給されない可能性がある。すなわち、電源電圧が不安定になる。また、不安定な電圧レベルによって周辺領域内部の他の回路モジュールが影響され、反対に外部の他の素子に供給される電源電圧もまた影響され、入出力データに影響を与えるという問題が発生する。

#### [0015]

前記のような問題点は、ただメモリ素子だけではなく一定の大きさにパッケージングされる入出力端子を有する全ての半導体素子の共通した問題となる。

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0016]

本発明は、上述した従来の技術の問題点を解決するためになされたものであって、その目的は、効率的に使用することができる入出力ライン駆動回路を提供することにある。

### [0017]

30

10

20

40

また、本発明の他の目的は、内部の他の回路モジュールの動作に影響を与えない半導体素子内の入出力ライン駆動回路を提供することにある。

#### [0018]

また、本発明の他の目的は、外部の他の素子のノイズから影響されない半導体素子内の入出力ライン駆動回路を提供することにある。

### 【課題を解決するための手段】

#### [0019]

上記目的を達成するため、本発明は、メモリセルを含むコア領域と入出力ピンの周辺領域との間のデータ移動経路を形成する入出力ライン回路と、前記コア領域にコア電圧を駆動電圧として付与するためのコア電圧発生器と、前記周辺領域に内部電圧を駆動電圧として付与するための内部電圧発生器とを備えた半導体メモリ素子において、複数のメモリBANKにそれぞれ1つずつ備えられ、或いは2個のメモリBANK毎に1つずつ備えられて、前記周辺領域内の前記入出力ライン回路にライン電圧を駆動電圧として付与するための複数のライン電圧発生器を基板上に配置して、前記入出力ライン回路に安定した電圧を供給されるようにしたことを特徴とする半導体メモリ素子を提供するものである。

#### 【発明の効果】

### [0020]

本発明<u>の半導体メモリ素子における入出力ライン回路</u>によれば、RAS信号より活性化期間の短いCAS信号の活性化時にだけ入出力ラインに駆動電源を供給し、消費電力を低減できるという効果が得られる。

#### [0021]

また、本発明に係る入出力ライン回路を備えた半導体メモリ素子<u>においては、</u>入出力ライン回路が外部電源から独立することによって、内部の他の回路モジュール等の動作に影響を与えず、また外部の他の素子のノイズから影響されないという効果も得られる。

#### 【発明を実施するための最良の形態】

### [0022]

以下、本発明のもっとも好ましい実施の形態を添付する図面を参照して説明する。本実施の形態は本発明の思想を一般の半導体メモリ素子に具現したものであり、本実施の形態が具現される半導体メモリ素子のメモリセルを含むコア領域と入出力ピンの周辺領域との間の入出力ラインは、読出し動作時に前記コア領域から周辺領域へデータを送信する読出し用グローバル入出力ラインと、書込み動作時に前記周辺領域からコア領域へデータを送信する書込み用グローバル入出力ラインとから構成される。

#### [0023]

本実施の形態の<u>読出し用の</u>入出力ライン駆動回路は、素子内のコア領域から周辺領域にデータを移動させるための<u>読出し</u>用グローバル入出力ラインと、コア内部の入出力ラインに載せられたデータを感知し、増幅するためのIOセンスアンプ部と、前記読み出し用のグローバル入出力ラインに載せられたデータを感知してステップラッチした後、入出力ピンに出力するための<u>読出し</u>ラッチング部と、<u>読出し</u>イネーブル信号に応じてイネーブルされ、外部電源電圧を印加され、前記IOセンスアンプ部及び<u>読出し</u>ラッチング部に駆動電源を供給する読出しライン電源生成部とを備えることを特徴とする。

# [0024]

本実施の形態の<u>書込み用の</u>入出力ライン駆動回路は、周辺領域から素子内のコア領域にデータを移動させるための<u>書込み</u>用グローバル入出力ラインと、入出力ピンから受け取ったデータを判定しラッチして、前記<u>書込み</u>用グローバル入出力ラインに出力するための書き込みラッチブロックと、前記<u>書込み</u>用グローバル入出力ラインに載せられたデータをコア領域内部のデータ入出力ラインに送信するための<u>書込み</u>ドライバブロックと、<u>書込み</u>イネーブル信号に応じてイネーブルされ、外部電源電圧を印加されて前記<u>書込み</u>ラッチブロック及び<u>書込み</u>ドライバブロックに駆動電源を供給する<u>書込み</u>ライン電源生成部とを備えることを特徴とする。

### [0025]

20

10

30

具現によれば、前記<u>読出し</u>用グローバル入出力ラインと<u>書込み</u>用グローバル入出力ラインとを、<u>読出し動作</u>と<u>書込み</u>動作を兼ね備えるグローバル入出力ラインに代替することもでき、前記<u>読出し</u>ラッチング部の出力データは外部出力用ドライブを経由して入出力ピンに送信され、入出力ピンに入力された外部データは、入力バッファブロックを経由して前記書込みラッチブロックに送信される。

### [0026]

前記<u>読出し</u>ライン電源生成部及び<u>書込み</u>ライン電源生成部は、個別に具現する事もでき、2つの機能を兼ね備える電源生成部に統合し具現することも好ましい。電源生成部は、1つで周辺領域の配置モジュールとコア領域配置モジュール全部とに電源を供給するように具現する事もでき、周辺領域配置モジュールに供給する電源生成部とコア領域配置モジュールとに供給する電源生成部を個別に具現できる。

[0027]

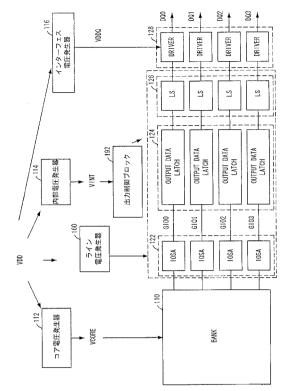

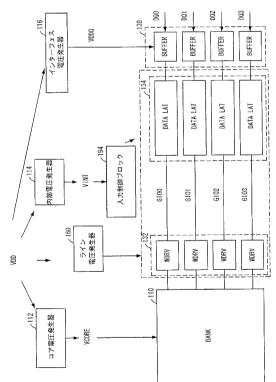

図 5 は、本発明の実施の形態に係る半導体メモリ装置内データの読み出し経路を説明するためのブロック図である。

### [0028]

図5<u>に示した半</u>導体メモリ装置は、BANK110、コア電圧発生器112、内部電圧発生器114、インターフェス電圧発生器116、ライン電圧発生器160、出力制御ブロック192、複数のI/Oセンス増幅器IOS-Aを含むI/Oセンスアンプブロック122、複数の出力データラッチ部を含む出力データラッチブロック124、複数のレベルシフトを含むレベルシフトブロック126及び複数の出力バッファを含む出力バッファブロック128とを備えている。

[0029]

読み出し経路は、コア領域のBANK110に格納されたデータが読み出し命令により、I/Oセンスアンプブロック122に印加される。前記I/Oセンスアンプブロックで増幅されたデータが、グローバル入出力ラインGIOを介し周辺領域の出力データラッチブロック124、レベルシフトブロック126及び出力バッファブロック128を経て、入出力ピンを介し外部素子に伝えられる。ここで、レベルシフトブロック126は、出力バッファブロック128の駆動電圧であるインターフェス電圧VDDQより出力データラッチブロック124の駆動電圧であるライン電圧VGIOの電圧レベルが低いため必要である。

[0030]

DRAMの各構造の電力供給を説明すると、メモリセルからなるDRAM BANK110には、コア電圧発生器112から生成されたコア電圧VCOREが供給され、読み出し動作を統制するための出力制御ブロック192には内部電圧発生器114から生成された内部電圧VINTが供給され、外部出力レベルを外部の信号規格と合わせるために、外部出力バッファブロック128にはインターフェス電圧発生器116から生成されたインターフェス電圧VDDQが供給される。

[0031]

ライン電圧発生器 1 6 0 から生成されたライン電圧 V G I O は、グローバル入出力ライン G I O に接続された構成要素に供給される。すなわち、 I / O センスアンプブロック 1 2 2、出力データラッチブロック 1 2 4 及びレベルシフトブロック 1 2 6 に駆動用電源として前記ライン電圧 V G I O が供給される。

[0032]

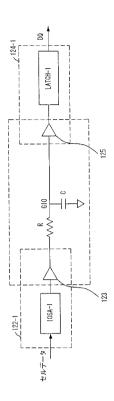

図6は、前記図5において本発明の実施の形態に係る半導体メモリ素子内の周辺領域のグローバル入出力ラインを詳細に説明するためのブロック図である。図6では、1つのグローバル入出力ライン及びこれに対応する1つのI/Oセンスアンプ部と1つの出力データラッチ部が示されており、これをそれぞれGIO、122-1及び124-1と示す。

### [0033]

図 6 に示されているように、周辺領域にはメモリBANKから出力されるデータを受けて増幅するためのI/Oセンスアンプ部122-1、増幅されたデータを送信するための

10

20

30

40

グローバル入出力ラインGIO及びグローバル入出力ラインを介し送信されたデータを順にラッチし、読み出しレイテンシ(Read latency)に合せてデータを出力するための出力データラッチ部124-1とを備える。

### [0034]

I/Oセンスアンプ部122-1と出力データラッチ部124-1とを接続するグローバル入出力ラインは、無視することの出来ない大きさの抵抗値R及びキャパシタンスCを有する。前記抵抗値R及びキャパシタンスCに影響されず円滑なデータ送信のために、本発明ではグローバル入出力ラインの始まりと終わりにそれぞれ第1ラインドライブ123及び第1ラインレシーバ125を接続した。

### [0035]

次いで、前記構成部分に本発明のライン電圧発生器160から生成されたライン電圧VGIOが印加されるが、図6を参照すれば、前記第1ラインドライブ123及び第1ラインレシーバ125にだけ前記ライン電圧VGIOを印加する方法もある。すなわち、前記I/Oセンスアンプ部122-1のセンス増幅器IOSA 1には、内部電圧VINTあるいは電源電圧VDDを印加し、第1ラインドライブ123にだけライン電圧VGIOを印加するものである。同様に、出力データラッチ部124-1のラッチ装置LATCH-1には、内部電圧VINTあるいは電源電圧VDDを印加し、第1ラインレシーバ125にだけ前記ライン電圧VGIOを印加する。この場合、本発明に係る半導体メモリ装置において読み出し動作時グローバル入出力ラインが有する抵抗値R及びキャパシタンスCにより発生するノイズを改善するのに効果的である。

#### [0036]

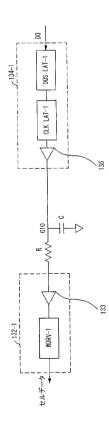

図7は、本発明の実施の形態に係るデータの書き込み経路側面から見たDRAMの内部 ブロック図である。

#### [0037]

図示された半導体メモリ装置は、BANK110、コア電圧発生器112、内部電圧発生器114、インターフェス電圧発生器116、ライン電圧発生器160、入力制御ブロック194、<u>書込み</u>ドライブブロック132、入力データラッチブロック<u>134</u>及び入力バッファブロック138とを備える。

### [0038]

書き込み経路は、入出力ピンを介し外部から入力されたデータが書き込み命令により、外部データ入力バッファブロック138の外部データバッファによってバッファリングされる。次いで、バッファリングされたデータは入力データラッチブロック134に入力されラッチされる。グローバル入出力ラインGIOを介し、入力データラッチブロック134から書き込みドライブブロック132に送信されたデータは、書き込みドライブブロック132により増幅され、コア領域内部のBANK10内の指定されたセルに格納される

# [0039]

DRAMの各構造の電源供給を説明すると、メモリセルからなるDRAM BANK110には、コア電圧発生器112から生成されたコア電圧VCOREが供給され、書き込み動作を統制するための入力制御ブロック194には別の内部電圧発生器114から生成された内部電圧VINTが供給され、所定の規格レベルの外部信号を受け取る入力バッファブロック138にはインターフェス電圧発生器116から生成されたインターフェス電圧VDDQが供給される。

# [0040]

ライン電圧発生器160から生成されたライン電圧VGIOは、書き込み用グローバル入出力ラインGIOに接続された構成要素に供給されるが、書き込みドライブブロック132及び入力データラッチブロック134に駆動用電源として供給される。

### [0041]

図8は、前記図7に示す本発明の実施の形態に係る半導体メモリ素子内周辺領域のグローバル入出力ラインを詳細に説明するためのブロック図である。図8では、1つのグロー

10

20

30

40

バル入出力ライン及びこれに対応する1つの入力データラッチ部及び1つの書き込みドライバ部が示されており、これをそれぞれGIO、134-1及び132-1と示す。

#### [0042]

図8に示されているように、周辺領域には入力されたデータをラッチするための入力データラッチ部134-1、ラッチされたデータを送信するためのグローバル入出力ラインGIOを介し入力されたデータをBANK110内に格納するための書き込みドライバブロック132-1とを備える。

#### [0043]

書き込みドライバブロック132 1は、データストローブラッチ装置とクロックラッチ装置とから構成される。データストローブラッチ装置は、入力されたデータをデータストローブラッチで書き、入力されたデータをデータストローブラッチブロックにより1時的にラッチされたデータを、クロックラッチブロックでまたクロックCLK信号を基準に基きデータをラッチする。なぜなら、チップ内部の全ての命令語及びアドレスは、クロックCLK信号に基づいて実行されるためである。すなわち、本発明の入力データラッチ部134-1は、仮りにデータストローブラッチ装置無してクロックラッチ装置だけを使用する場合、クロックCLKは広範囲にチップとコントローラとに供給するため、チップ間のデータスキューが多く生じるという短所を解消するため、データストローブラッチ装置及びクロックラッチ装置を使用し2回ラッチするという構造を有する。

### [0044]

図8に示されているように、グローバル入出力ラインGIOは無視することの出来ない大きさの抵抗値R及びキャパシタンスCを有しており、該抵抗値R及びキャパシタンスCの影響なしにデータを円滑に送信するために、グローバル入出力ラインの始まりと終わりにそれぞれ第2ラインドライブ135及び第2ラインレシーバ133とを備える。

#### [0045]

前記グローバル入出力ラインGIOは、<u>書込み</u>ドライバブロック132-1と入力データラッチ部134-1<u>に</u>接続される。前記<u>書込み</u>ドライバブロック132-1はコア領域と接続された<u>読出し</u>用コアラインにデータを送信するためのドライブモジュールWDRV-1と、グローバル入出力ラインGIOに載せられたデータを感知する第2ラインレシーバ133とを備える。前記入力データラッチ部134-1は、グローバル入出力ラインにデータを出力する第2ラインドライブ135を備える。

### [0046]

本発明のライン電圧発生器160から生成されたライン電圧VGIOを、書き込みドライバブロック132・1及び入力データラッチ部134・1の駆動電圧として入力する。しかし、図8に示されているように、第2ラインドライブ135及び第2ラインレシーバ133にだけ読み出しライン電源生成部から生成されたライン電圧VGIOを印加し、その他の回路には内部電圧VINTあるいは電源電圧VDDを印加することができる。この場合、データの書き込み動作の中でグローバル入出力ラインGIOから発生するノイズの影響を最小限にするという大きな効果を得られる。

#### [0047]

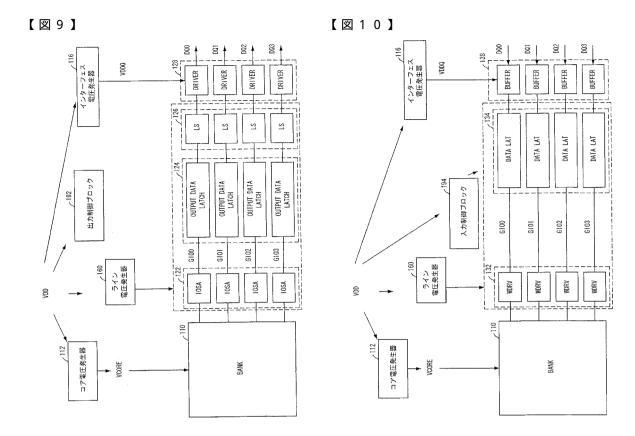

図9は、本実施の形態に係るデータの読み出し経路側面から低電圧用DRAM素子の内部プロックを示した図面であり、図10は本実施の形態に係るデータの書き込み経路側面から低電圧用DRAM素子の内部プロックを示した図面である。ここで、図5ないし図8で説明された同じ構成要素に対しては、同じ図面符号を付して、詳細な説明は省略する。

#### [0048]

低電圧用 D R A M の場合も、本発明の特徴部を構成するライン電圧発生器 1 6 0 及びライン電圧 V G I O の供給は、前記半導体メモリ素子の場合と同様に、読み出し及び/または書き込み動作を制御するための入力制御ブロック 1 9 4 及び出力制御ブロック 1 9 2 に外部電源電圧 V D D が駆動電圧として直接供給されることが相違する点である。

### [0049]

50

10

20

30

10

20

30

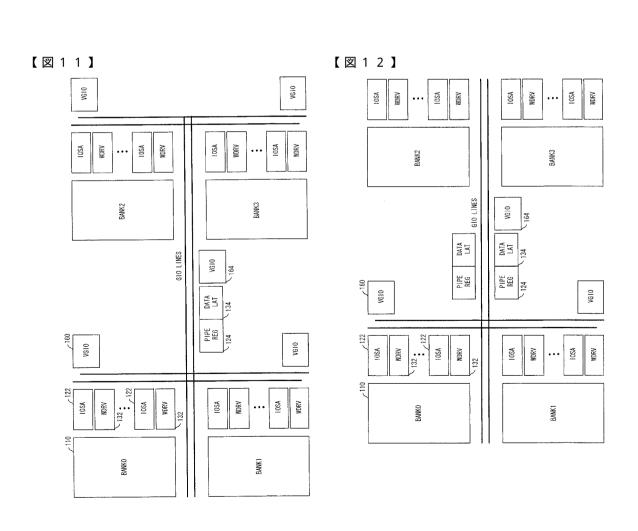

図11は、半導体メモリ素子内のそれぞれのBANKが1つのライン電圧発生器160 を備える場合の基板上の配置を示すものであり、図12は2つのBANK単位に1つのラ イン電圧発生器160を備える場合の基板上の配置を示すものである。

[0050]

図11と図12に示す具現によれば、ライン電圧供給の効率のために周辺領域に配置さ れる素子にライン電圧を供給するための周辺ラインの電位生成器164と、コア領域に配 置される素子にライン電圧を供給するためのコアライン電圧発生器162とを区別して具 現することが好ましい。

[0051]

ライン電圧発生器が生成したライン電圧が供給されるI/Oセンスアンプブロック及び 書き込みドライバブロックはメモリ素子入力信号の中CAS信号の活性化の間にだけ動作 を行い、読み出しラッチ部及び書き込みラッチ部は前記CAS信号の活性化の間にだけラ ッチデータを維持する。

[0052]

したがって、好ましい具現によれば、ライン電圧発生器はCAS信号を受け取ってCA S信号が活性化される間にだけ活性化するように具現できる。

[0053]

尚、本発明は、上記した本実施の形態に限られるものではなく、本発明の技術的思想か ら逸脱しない範囲内で多様に変更が可能であり、それらも本発明の技術的範囲に属する。

【図面の簡単な説明】

[0054]

【図1】従来の技術に係るメモリ素子の読み出し経路を示したブロック図である。

【図2】従来の技術に係るメモリ素子の書き込み経路を示したブロック図である。

【図3】従来の技術に係る低電圧用メモリ素子の読み出し経路を示したブロック図である

【図4】従来の技術に係る低電圧用メモリ素子の書き込み経路を示したブロック図である

【図5】本発明に係るメモリ素子の読み出し経路を示したブロック図である。

【図6】本発明に係る読み出し用入出カライン回路を示した回路図である。

【図7】本発明に係るメモリ素子の書き込み経路を示したブロック図である。

【図8】本発明に係る書き込み用入出力ライン回路を示したブロック図である。

【図9】本発明に係る低電圧用メモリ素子の読み出し経路を示したブロック図である。

【図10】本発明に係る低電圧用メモリ素子の書き込み経路を示したブロック図である。

【図11】本発明に係る入出力ライン回路の実施の形態に係る素子内配置を示した配置図 である。

【図12】本発明に係る入出力ライン回路の他の実施の形態に係る素子内配置を示した配 置図である。

【符号の説明】

[0055]40 1 1 0 DRAM BANK 1 1 2 コア電圧発生器 1 1 4 内部電圧発生器 1 2 2 I/Oセンスアンプブロック 1 2 4 読み出しラッチブロック 1 2 6 レベルシフトブロック 1 2 8 外部出力用ドライブ

1 3 2 書き込みドライバブロック 1 3 4 書き込みラッチブロック

1 3 8 入力バッファブロック

【図5】 【図6】

【図7】 【図8】

### フロントページの続き

(74)代理人 100064724

弁理士 長谷 照一

(74)代理人 100073302

弁理士 神谷 牧

(72)発明者 李 日豪

大韓民国京畿道利川市夫鉢邑牙美里山136-1 株式会社ハイニックスセミコンダクター内

審査官 堀田 和義

(56)参考文献 特開2000-21170(JP,A)

特開2003-7059(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C 11/4074