(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

FL

(11)特許番号

特許第5285375号 (P5285375)

(45) 発行日 平成25年9月11日(2013.9.11)

(24) 登録日 平成25年6月7日(2013.6.7)

(51) Int. Cl.

GO6F 13/36 (2006.01)

GO6F 13/36 53OA

請求項の数 8 (全 16 頁)

(21) 出願番号 特願2008-252459 (P2008-252459) (22) 出願日 平成20年9月30日 (2008.9.30)

(65) 公開番号 特開2009-110512 (P2009-110512A)

(43) 公開日 平成21年5月21日 (2009.5.21) 審査請求日 平成23年8月17日 (2011.8.17)

(31) 優先権主張番号 11/926212

(32) 優先日 平成19年10月29日 (2007.10.29)

(33) 優先権主張国 米国 (US)

前置審査

|(73)特許権者 390009531

インターナショナル・ビジネス・マシーン

ズ・コーポレーション

INTERNATIONAL BUSIN ESS MACHINES CORPOR

ATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74)代理人 100108501

弁理士 上野 剛史

|(74)代理人 100112690

弁理士 太佐 種一

最終頁に続く

(54) 【発明の名称】ネットワークオンチップ、およびネットワークオンチップで以ってデータを処理する方法

### (57)【特許請求の範囲】

# 【請求項1】

集積プロセッサ(IP) ブロック、ルーター、メモリ通信コントローラおよびネットワーク・インターフェイス・コントローラを含むネットワークオンチップ(NOC)であって、

各々の前記IPブロックが、前記メモリ通信コントローラおよび前記ネットワーク・イターフェイス・コントローラを介して、前記ルーターに結合され、

各々の前記メモリ通信コントローラが、前記IPブロック<u>間</u>および<u>前記IPブロックと</u>オンチップ・メモリ間の通信を制御し、

各々の前記ネットワーク・インターフェイス・コントローラが、前記ルーターを介して IPプロック間通信を制御し、

各々の前記ルーターが、通信タイプによって各々特徴付けられる 2 個もしくはそれ以上 の仮想通信チャネルを含み、

前記メモリ通信コントローラは、前記IPブロックから受け取ったメモリ通信命令をコマンド・フォーマットに変換して前記ネットワーク・インターフェイス・コントローラに送り、前記ネットワーク・インターフェイス・コントローラが、前記メモリ通信命令のコマンド・フォーマットをネットワーク・パケット・フォーマットへ変換して前記ルーターに送ることにより、前記IPブロック間および前記IPブロックとオンチップ・メモリ間のメモリ・アドレス・ベースの通信を可能にする、ネットワークオンチップ(NOC)。

【請求項2】

20

前記メモリ通信コントローラが、

前記メモリ通信命令を他のメモリ通信実行エンジンとは別個にかつ並行して<u>前記コマンド・フォーマットへの変換を含む処理を実行することができる</u>、複数のメモリ通信実行エンジンを含む、請求項1に記載のNOC。

# 【請求項3】

前記メモリ通信命令が、変換ルックアサイド・バッファ制御命令、キャッシュ制御命令、バリア命令、メモリ・ロード命令、及び、メモリ・ストア命令を含む、請求項2に記載のNOC。

## 【請求項4】

前記オンチップ・メモリが、

RAM

前記メモリ通信コントローラを介して前記IPブロックに直接に接続されたメモリ、 前記IPブロックとしてイネーブルされるオンチップ・メモリ、及び、

オンチップ・キャッシュを含む、請求項1に記載のNOC。

# 【請求項5】

各々の前記IPブロックが、

前記NOC内のデータ処理のため構築ブロックとして使用される同期もしくは非同期の 論理設計の再使用可能なユニットを含む、請求項1に記載のNOC。

#### 【請求項6】

各々の前記ネットワーク・インターフェイス・コントローラが、

ネットワーク・パケットをタイプによって特徴付ける仮想チャネルをネットワーク上に 実現する、請求項 1 に記載の N O C。

### 【請求項7】

各々の前記IPブロックが、

前記IPブロックのメモリ通信コントローラをバイパスし、かつ、

IPブロック間の、ネットワーク・アドレス通信をIPブロックのネットワーク・インターフェイス・コントローラを介して直接に前記ネットワークに送る、請求項1に記載のNOC。

#### 【請求項8】

ネットワークオンチップ(NOC)で以ってデータを処理する方法であって、

前記NOCは、

集積プロセッサ(IP)ブロック、ルーター、メモリ通信コントローラおよびネットワ ーク・インターフェイス・コントローラを含み、

各々の前記IPブロックが、前記メモリ通信コントローラおよび前記ネットワーク・インターフェイス・コントローラを介して前記ルーターに結合されており、

各々の前記ルーターが、通信タイプによって各々特徴付けられる 2 個もしくはそれ以上 の仮想通信チャネルを含み、

前記方法は、

各々の前記メモリ通信コントローラによって、前記IPブロック<u>間</u>および<u>前記IPブロ</u>ックとオンチップ・メモリ間の通信を制御するステップと、

各々の前記ネットワーク・インターフェイス・コントローラによって、前記ルーターを介してIPブロック間通信を制御するステップと、を含み、

前記メモリ通信コントローラは、前記IPブロックから受け取ったメモリ通信命令をコマンド・フォーマットに変換して前記ネットワーク・インターフェイス・コントローラに送り、前記ネットワーク・インターフェイス・コントローラが、前記メモリ通信命令のコマンド・フォーマットをネットワーク・パケット・フォーマットへ変換して前記ルーターに送ることにより、前記IPブロック間および前記IPブロックとオンチップ・メモリ間のメモリ・アドレス・ベースの通信を可能にする、方法。

# 【発明の詳細な説明】

# 【技術分野】

10

20

30

40

#### [00001]

本発明はデータ処理に関し、特にネットワークオンチップ(NOC)によりデータ処理を 行う装置および方法に関する。

# 【背景技術】

# [0002]

2つの広範に使用されるデータ処理のパラダイムがある。複数命令、複数データという「MIMD」と、単一命令、複数データという「SIMD」とである。MIMD処理では、コンピュータ・プログラムが、多かれ少なかれ独立に動作し、かつ大量の共有メモリに高速でランダムなアクセスをする必要が夫々ある、1個もしくはそれ以上の実行コードのスレッド (one or more threads of execution )として典型的には特徴付けられる。MIMDは、特定のクラスのプログラムのためにそれに適合するよう最適化され、たとえばワード・プロセッサ、スプレッドシート、データベース・マネジャ、ブラウザなど多くの形式のテレコミュニケーションを含むデータ処理パラダイムである。

## [00003]

SIMDは、多くのプロセッサ上で並行して同時に稼動する単一のプログラムによって特徴付けられ、またそのプログラムの各インスタンスが同じ態様でだがデータの別個のアイテム上で動作するように特徴づけられる。SIMDは特定のクラスのアプリケーションのためにそれに適合するように最適化され、たとえば多くの形式のディジタル信号処理、ベクトル処理などを含むデータ処理パラダイムである。

# 【発明の開示】

【発明が解決しようとする課題】

#### [0004]

他のクラスのアプリケーションもあるが、それは多くの現実の世界のシミュレーション・プログラムを含み、そのプログラムに対しては、たとえば純粋なSIMDのもしくは純粋なMIMDのデータ・プロセシングのいづれも最適化されていない。そのクラスのアプリケーションは並列処理の利益を得られるアプリケーションを含み、また共有メモリへの高速のランダムなアクセスを必要とする。そのクラスのプログラムに対し、純粋なMINDシステムは高度の並列性(parallelism )を提供せず、また純粋なSIMDシステムはメイン・メモリ・ストア(主メモリ格納装置)への高速のランダムなアクセスを提供しない。

### 【課題を解決するための手段】

# [0005]

ネットワークオンチップ(NOC)は、集積プロセッサ(IP)ブロック、ルーター、メモリ通信コントローラおよびネットワーク・インターフェイス・コントローラを含む。各IPブロックはルーターにメモリ通信コントローラおよびネットワーク・インターフェイス・コントローラを介して結合される。但し、各メモリ通信コントローラはIPブロックおよびメモリ間の通信を制御し、各ネットワーク・インターフェイス・コントローラはルーターを介してIPブロック間通信を制御する。

# 【発明を実施するための最良の形態】

#### [0006]

本発明の前述のおよび他の目的、特徴および効果は本発明の実施例についての以下のもっと具体的な説明から明らかになろう。その図面では一般に同様の参照番号は本発明の実施例の同様な部分を示す。

# [0007]

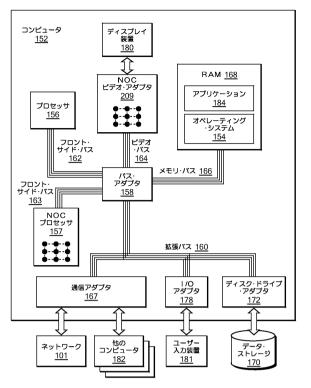

本発明によるNOCを備えたデータ処理のための実施例の装置および方法を図1から始まる添付図面に沿って説明する。図1は、本発明の実施例によるNOCを備えたデータ処理において有用な実施例のコンピュータ152を含む自動化されたコンピューティング・マシンのブロック図を開示する。図1のコンピュータ152は少なくとも1個のコンピュータ・プロセッサすなわちプロセッサ156と、プロセッサ156およびコンピュータ152の他のコンポーネントに高速のメモリ・バス166およびバス・アダプタ158を介し

10

20

30

40

て接続されるランダム・アクセス・メモリすなわちRAM168を含む。

[0008]

RAM168にストア(格納)されるのは、アプリケーション・プログラム184であり、ワード・プロセシング、スプレッドシート、データベース操作、ビデオ・ゲーム、株式市場のシミュレーション、原子量子プロセスのシミュレーションあるいは他のユーザーレベルのアプリケーションなど、特定のデータ処理タスクを実行するユーザーレベルのコンピュータ・プログラム命令のモジュールである。RAM168にはオペレーティング・システム154もストアされる。オペレーティング・システムは本発明の実施例によるNOCとともに有用なデータ処理を行うが、UNIX(登録商標)、Linux(商標)、Microsoft XP(商標)、AIX(商標)、IBMのi5/OS(商標)ほか当業者の想到するような他のものを含む。図1の実施例におけるオペレーティング・システム154およびアプリケーション・プログラム184はRAM168の中に示されているが、そのようなソフトウエアの多くのコンポーネントはディスク・ドライブないしデータ・ストレージ170などのような不揮発性メモリにもストアされる。

[0009]

実施例のコンピュータ152は本発明の実施例による2個のNOC、すなわちNOCビデオ・アダプタ209およびNOCコプロセッサ157を含む。NOCビデオ・アダプタ209は、ディスプレイ・スクリーンもしくはコンピュータ・モニタなどのディスプレイ装置180へのグラフィック出力のために特別に設計されたI/Oアダプタの一例である。NOCビデオ・アダプタ209は、高速のビデオ・バス164、バス・アダプタ158、およびフロント・サイド・バス162(これも高速のバスである)を介してプロセッサ156に接続される。

[0010]

実施例のNOCコプロセッサ157は、バス・アダプタ158、および高速バスであるフロント・サイド・バス(162および163)を介してプロセッサ156に接続される。 図1のNOCコプロセッサ157は主たるプロセッサ156の命令ないし要請で特定のデータ処理タスクを加速するように最適化される。

[0011]

図1の実施例のNOCビデオ・アダプタ209およびNOCコプロセッサ157は夫々本発明の実施例によるNOC(図2の102)を含む。NOC102は、図2に関連して後述するように、IP(集積プロセッサ)ブロック104、ルーター110、メモリ通信コントローラ106およびネットワーク・インターフェイス・コントローラ108を含み、各IPブロック104はメモリ通信コントローラ106およびネットワーク・インターフェイス・コントローラ108を介してルーター110につながれ、各メモリ通信コントローラ106はIPブロック104とメモリとの間の通信を制御し、各ネットワーク・インターフェイス・コントローラ108はルーター110を介してIPブロック間通信を制御する。NOCビデオ・アダプタ209およびNOCコプロセッサ157は、並列処理を用いるプログラムのために最適化され、また共有メモリへの高速のランダム・アクセスを必要とする。NOCの構造および動作の詳細は図2ないし図4で行う。

[0012]

図1のコンピュータ152は拡張バス160およびバス・アダプタ158を介してプロセッサ156に結合されたディスク・ドライブ・アダプタ172とコンピュータ152の他のコンポーネントとを含む。本発明の実施例によるNOCとともにデータ処理をするためにコンピュータで有用なディスク・ドライブ・アダプタは集積ドライブ・エレクトロニクス(IDE)アダプタ、SCSI(小型コンピュータシステム・インターフェイス)アダプタ、当業者の想到するような他のものを含む。不揮発性のコンピュータ・メモリは、また光ディスク・ドライブ、電子的に消去可能なプログラム可能読出し専用メモリ(いわゆるEEPROMもしくはフラッシュ・メモリ)、RAMドライブ、当業者の想到するような他のものを実装してもよい。

[0013]

10

20

30

40

20

30

40

50

図1の実施例のコンピュータ152は1個もしくはそれ以上の入出力(I/O)アダプタ178を含む。I/Oアダプタ178は、コンピュータ・ディスプレイ・スクリーンなどのディスプレイ装置への出力を制御するため、たとえばソフトウエア・ドライバおよびコンピュータ・ハードウエアを介してのユーザー起源の入出力と、キーボードおよびマウスなどユーザー入力装置181からのユーザーの入力とを使用する。

### [0014]

図1の実施例のコンピュータ152は、他のコンピュータ182とデータ通信するため、ならびにデータ通信用のネットワーク101と通信するための通信アダプタ167を含む。このようなデータ通信は、逐次にRS・232接続を介し、USB(ユニバーサル・シリアル・バス)のような外部バスを介し、またIPデータ通信ネットワークなどのデータ通信ネットワークおよび当業者が想到するような他の方法で逐次に行われてもよい。通信アダプタはハードウエア・レベルのデータ通信を用い、これによって一つのコンピュータが他のコンピュータに直接またはデータ通信ネットワークを介してデータを送る。本発明の実施例によるNOCを備えたデータ処理のために有用な通信アダプタの例は、有線のダイアルアップ通信用のモデム、有線のデータ通信ネットワークの通信用のEthernet(IEEE802.3)アダプタ、および無線のデータ通信ネットワークの通信用の802.11アダプタを含む。

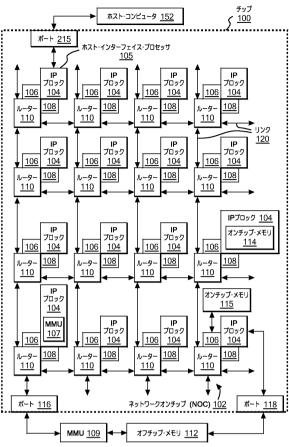

# [0015]

更に説明をすると、図2は本発明の実施例によるネットワークオンチップ(NOC)102の機能的なブロック図を開示する。図1の実施例のNOCはチップ100すなわち集積回路上に実装される。図2のネットワークオンチップ(NOC)102は集積(インテグレーテッド)プロセッサ(IP)プロック104,ルーター110,メモリ通信コントローラ106およびネットワーク・インターフェイス・コントローラ108を含む。各IPプロック104はメモリ通信コントローラ106およびネットワーク・インターフェイス・コントローラ108を介してルーター110につながれる。各メモリ通信コントローラ106はIPブロック104とメモリとの間の通信を制御し、また各ネットワーク・インターフェイス・コントローラ108はルーター110を介してIPブロック間通信を制御する。

# [0016]

図2のNOC102では、各IPブロック104がそのNOC102内でのデータ処理のため構築プロックとして使用される同期もしくは非同期の論理設計の再使用可能なユニットを表す。「IPブロック」という用語は、ときに「知的財産プロック」として拡張され、或る会社が所有する設計すなわち或る会社の知的財産としてのIPブロック104、あるいは半導体回路の他のユーザーもしくは設計者にライセンスされるべき設計のIPブロック104を効果的に指定する。しかし本発明の範囲では、IPブロック104が何らかの特定の所有権の対象である必要はなく、従ってその用語は常に「集積プロセッサ・ブロック」として本明細書では拡張される。ここで特定されるIPブロック104は、論理、セル、もしくはチップ・レイアウト設計の再使用可能なユニットであり、知的所有権の対象であってもなくてもよい。IPブロック104はASICチップ設計もしくはFPGA論理設計として形成されることができる論理コアである。

# [0017]

IPブロック104を類推で記述する一つの方法は、IPブロック104がNOC設計のためにコンピュータ・プログラミングにとってライブラリが何であるか、あるいは。個別の集積回路コンポーネントがプリント回路基盤の設計用であるかということである。本発明の実施例によるNOC102では、IPブロック104が、汎用のゲートのネットリスト(generic gate netlists)として、完全な特定目的のもしくは汎用目的のマイクロプロセッサとして、あるいは当業者が想到するような他の方法で実施されてもよい。ネットリストは、高レベルのプログラム・アプリケーションのためのアセンブリ・コード・リスティングに似た、IPブロック104の論理機能のブール代数表記(ゲート、標準セル)である。NOC102はまたVerilogもしくはVHDLのようなハードウエア記述

20

30

40

50

言語に記述される、たとえば同期可能な形式で実装されてもよい。ネットリストおよび同期可能な実装に加えて、NOCはまた低レベルの物理的な記述で配布され得る。SERDES、PLL、DAC、ADCなどのアナログのIPブロック・エレメントは、GDSIIのようなトランジスタ・レイアウト・フォーマットで配布されてもよい。IPブロック104のディジタル・エレメントは、レイアウト・フォーマットでもときには提供される

[0018]

図2の実施例における各IPブロック104はメモリ通信コントローラ106を介してルーター110につながれる。各メモリ通信コントローラ106はIPブロックおよびメモリ間のデータ通信を提供するようつながれる同期もしくは非同期の論理回路の集合である。IPブロック104およびメモリ間のそのような通信の例は、メモリ・ロード命令およびメモリ・ストア命令を含む。メモリ通信コントローラ106を、図3に関連して詳細に説明する。

[0019]

図 2 の実施例において各IPブロック 1 0 4 はまたネットワーク・インターフェイス・コントローラ 1 0 8 を介してルーター 1 1 0 につながれる。各ネットワーク・インターフェイス・コントローラ 1 0 8 は I P ブロック 1 0 4 相互間のルーター 1 1 0 を介しての通信を制御する。I P ブロック 1 0 4 相互間の通信の例は、並列のアプリケーションにおいてまたパイプライン化されたアプリケーションにおいて I P ブロック 1 0 4 相互間でデータを処理するために、データおよび命令を担持するメッセージを含む。ネットワーク・インターフェイス・コントローラ 1 0 8 を、図 3 に関連して以下で詳細に説明する。

[0020]

図2の実施例における各IPブロック104はルーター110につながれる。ルーター1 10およびルーター110相互間のリンク120がNOC102のネットワーク動作を行 う。リンク120は、全てのルーター110を接続する物理的な並列のワイヤのバス上で 実施されるパケット構造である。すなわち各リンク120は全てのヘッダー情報およびペ イロード・データを含むデータ・スイッチング・パケット全体を同時に収容するに足るだ けの幅のワイヤ・バス上で実施される。もしパケット構造がたとえば8バイトのヘッダー および56バイトのペイロード・データを含む64バイトを含むなら、各リンクを定める ワイヤ・バスは64バイト幅で512本のワイヤである。更に、各リンク120は双方向 であり、したがってもしリンクのパケット構造が64バイトなら、ワイヤ・バスはネット ワーク中の各ルーターとその各々の隣のものとの間に1024本のワイヤを含む。メッセ ージは1よりも多くのパケットを含むが、各パケットはワイヤ・バスの幅上に正確に適合 する。もしルーターとワイヤ・バスの各セクションとの間の接続をポートと呼ぶなら、各 ルーターは5個のポート、すなわちネットワーク上のデータ伝送の4つの方向の各々に1 個、そしてメモリ通信コントローラ106およびネットワーク・インターフェイス・コン トローラ108を介して特定のIPブロック104にルーター110をつなぐための第5 のポートを含む。

[0021]

図2の実施例における各メモリ通信コントローラ106はIPブロック104およびメモリ間の通信を制御する。メモリは、オフチップのメインRAM(オフチップ・メモリ)112、メモリ通信コントローラ106を介してIPブロック104に直接接続されたメモリ115、IPブロック104としてイネーブルされるオンチップ・メモリ、およびオンチップ・キャッシュを含むことができる。図2のNOC102では、オンチップ・メモリ114、115のいずれかが、たとえばオンチップ・キャッシュ・メモリとして実装されてもよい。これらの全ての形式のメモリは同じアドレス空間、物理的アドレスもしくは仮想アドレスに配設されることができる。これはIPブロック104に直接に取付けられたメモリの場合でもそうである。メモリにアドレスされるメッセージは従ってIPブロックに対して完全に両方向であり得る。何故ならばそのようなメモリはネットワーク上のどこかにあるいずれかのIPブロックから直接アドレスされることができる。IPブロック1

20

30

40

50

0 4 上のメモリ1 1 4 はその I P プロック 1 0 4 からもしくはその N O C における他のいずれかの I P プロック 1 0 4 からアドレスされることができる。或るメモリ通信コントローラ 1 0 6 に直接取付けられるメモリ 1 1 5 はそのメモリ通信コントローラ 1 0 6 によりそのネットワークにつながれるその I P ブロック 1 0 4 によってアドレスされることができ、そしてまたその N O C 中のどこかにある他のいずれかの I P ブロック 1 0 4 からアドレスされることもできる。

#### [0022]

実施例のNOC102は、本発明の実施例による(複数の)NOCのための2個の選択可能なメモリ・アーキテクチャを示している2個のメモリ管理ユニット(MMU)107、109を含む。MMU107は或るIPブロック104とともに実装されそのIPブロック104内のプロセッサが仮想メモリにおいて動作するのを許容しながら、一方でそのNOC102の残りのアーキテクチャ全体が物理的なメモリ・アドレス空間で動作するのを許容する。MMU109はオフチップに実装され、データ通信用のポート116を介してそのNOC102に接続される。そのポート116はそのNOC102とそのMMU107との間で信号を導通させるのに必要なピンおよび他の相互接続手段、ならびにそのNOC102のパケット・フォーマットからのメッセージ・パケットを、外部のMMU109により必要とされるバス・フォーマットに変換するのに足る機能を含む。そのMMU109の外部に位置するということは、そのNOC102の全てのIPブロック104における全てのプロセッサが仮想のメモリ・アドレス空間で動作することができ、そのオフチップのMMU109により処理されるオフチップのメモリ112の物理アドレスへ全て変換できることを意味する。

#### [0023]

MMU107、109を使用することにより示される2個のメモリ・アーキテクチャに加えて、データ通信用のポート118は本発明の実施例によるNOC102で有用な第3のメモリ・アーキテクチャを示す。ポート118はNOC102のIPブロック104とオフチップのメモリ112との間の直接接続を提供する。この処理経路にMMUがないので、このアーキテクチャはそのNOC102の全てのIPブロック104による物理的なアドレス空間を利用する。そのアドレス空間を双方向的に共有する際、そのNOC102の全てのIPブロック104は、ロードおよびストアされたものを含み、ポート118により直接接続されたIPブロックを介して差向けられるメモリ・アドレスされたメッセージによりそのメモリ空間でメモリをアクセスすることができる。このポート118はそのNOC102とオフチップのメモリ112との間の信号を導通させるのに必要なピンおよび相互接続を含むとともに、そのNOC102のパケット・フォーマットからのメッセージ・パケットを、オフチップのメモリ112により必要とされるバス・フォーマットに変換するのに足る機能を含む。

#### [0024]

図2の実施例では、IPブロック104の一つがホスト・インターフェイス・プロセッサ105はNOC102とホスト・インターフェイス・プロセッサ105はNOC102とホスト・コンピュータ152との間のインターフェイスを提供する。そのホスト・コンピュータ152にもNOCを設けてそのNOC上の他のIPブロックにデータ処理サービスはそのNOCのIPブロック相互間でよった。NOC102は、図1に関連して前述したとおり、大型のホスト・コンピュータ152からのデータ処理リクエストを受取り、ディスパッチすることをおい。NOC102は、図1に関連して前述したとおり、大型のホスト・コンピュータ157を導入してものい。図2の実施例では、ホスト・インターフェイス・プロセッサ105がデータ通信用のポート215を介して大型のホスト・コンピュータ152に接続される。ポート215はNOC102とホスト・コンピュータ152との間の信号を導通させるのに必要なりおよび他の相互接続手段を含むとともに、NOC102からのメッセージ・パケットを入下・コンピュータ152におけるNOCコプロセッサ157の実施例では

20

30

40

50

、 そのようなポートは N O C コプロセッサ 1 5 7 のリンク構造と、 N O C コプロセッサ 1 5 7 およびバス・アダプタ 1 5 8 間のフロント・サイド・バス 1 6 3 のために必要なプロトコルとの間で、 データ通信フォーマット変換を提供する。

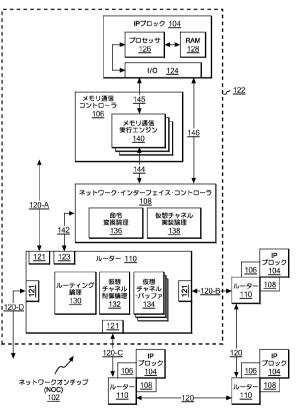

# [0025]

更に説明すると、図3は本発明の実施例による別のNOCの機能的なプロック図を開示する。図3の実施例のNOCは図2の実施例のNOCと、図3の実施例のNOCがチップ(図2の100)上に実装され、かつ図3のNOC102がIPブロック104、ルーター110、メモリ通信コントローラ106およびネットワーク・インターフェイス・コラ106およびネットワーク・インターフェイス・コントローラ108を介してルーター110につながれる。各IPブロック104はメモリ通信コントローラ106はIPブロック104とメモリとの間の通信を制御し、また各ネットワーク・インターフェイス・コントローラ108はルーター110を介してIPブロック間通信を制御する。図3の実施例では、メモリ通信コントローラ106およびネットワーク・インターフェイス・コントローラ108を介してルーター110につながれるIPブロック104の1セット122が、それらの構造おしてい動作の詳細な説明を助けるように拡張される。図3の実施例におけるIPブロック108およびルーター110は全てその拡張されたセット122と同じ態様で構成される。

#### [0026]

図3の実施例では、各IPブロック104がコンピュータ・プロセッサ126およびI/〇機能124を含む。この例では、コンピュータ・メモリが、各IPブロック104中のランダム・アクセス・メモリ(RAM)128のセグメントによって代表される。図2の実施例に関連して前述したようなこのメモリは、各IPブロック104上のコンテンツがそのNOC中の任意のIPブロックからアドレスされアクセスされる物理的なアドレス空間のセグメントを占めることができる。各IPブロック104上のプロセッサ126、I/〇機能124およびメモリ128はそのIPブロックを汎用のプログラマブル・マイクロコンピュータとして効果的に実装できる。しかし前述のとおり、本発明の範囲には、NOC内でのデータ処理のためのブロックを構築する際使用される同期もしくは非同期の再使用可能なユニットの機能をIPブロックが果たすことも含む。従って、汎用のプログラマブル・マイクロコンピュータとしてIPブロックを実装するというのは、説明目的で有用な共通の実施例ではあるが、本発明を限定しない。

# [0027]

図3のNOC102では、各メモリ通信コントローラ106が複数個のメモリ通信実行エンジン140を含む。各メモリ通信実行エンジン140はIPプロック104からのメモリ通信命令を実行し、そのネットワークとIPプロック104との間の双方向のメモリ通信命令の流れ142,144,145を実現する。このメモリ通信コントローラ106により実行されるメモリ通信命令は、IPプロック104から特定のメモリ通信コントローラ106により実行されるメモリ通信命令は、IPプロック104から特定のメモリ通信コントローラ100を介してルーター110につながれたIPプロック104から引き起こされるかもしれない。すなわち、そのNOC中の任意のIPプロックがメモリ通信命令を発生し、そのNOCのルーターを介してメモリ通信命令を、それを実行するため他のIPプロックに関連付けられている他のメモリ通信コントローラに伝送することができる。そのようなメモリ通信命令は、たとえば変換ルックアサイド・バッファ制御命令、キャッシュ制御命令、バリア命令およびメモリ・ロード命令、メモリ・ストア命令を含むことができる。

#### [0028]

各メモリ通信実行エンジン 1 4 0 は或る完全なメモリ通信メモリ命令を他のメモリ通信実行エンジンと並行してかつ別個に実行する。メモリ通信実行エンジン 1 4 0 は、メモリ通信命令の同時進行のスループットのために最適化されたスケーラブル・メモリ・トランザクション・プロセッサを実装する。メモリ通信コントローラ 1 0 6 は、複数個のメモリ通信実行エンジン 1 4 0 をサポートするが、その全ては複数個のメモリ通信命令の同時実行

20

30

40

50

のため同時に稼動する。新しいメモリ通信命令がメモリ通信コントローラ106によってメモリ通信実行エンジン140に割当てられ、そのメモリ通信実行エンジン140は複数個の応答イベントを同時に受取ることができる。この実施例では、全てのメモリ通信実行エンジン140は同一である。従ってメモリ通信コントローラ106によって同時に処理され得るメモリ通信命令の数のスケーリングは、メモリ通信実行エンジン140の数をスケーリングすることによって実装される。

#### [0029]

図3のNOC102において、各ネットワーク・インターフェイス・コントローラ108 は、ルーター110を介してのIPブロック104相互間の伝送のために命令フォーマッ トからの通信命令をネットワーク・パケット・フォーマットへ変換する。その通信命令は IPブロック104によってもしくはメモリ通信コントローラ106によってコマンド・ フォーマットに変換され、コマンド・フォーマットでネットワーク・インターフェイス・ コントローラ108に与えられる。このコマンド・フォーマットは、IPプロック104 およびメモリ通信コントローラ106のアーキテクチャの登録ファイルに合わせるような ネイティブ・フォーマットである。このネットワーク・パケット・フォーマットは、その ネットワークのルーター110を介して伝送するために必要なフォーマットである。1個 もしくはそれ以上のネットワーク・パケットから各メッセージが成立つ。コマンド・フォ ーマットからネットワーク・インターフェイス・コントローラ 1 0 8 におけるパケット・ フォーマットに変換されるそのような通信命令の例は、IPブロック104およびメモリ 間のメモリ・ロード命令およびメモリ・ストア命令を含む。そのような通信命令は、並列 アプリケーションおよびパイプライン化アプリケーションにおけるIPブロック相互間の データを処理するためのデータおよび命令を担持するIPブロック相互間でメッセージを 送る通信命令を含んでもよい。

#### [0030]

図3のNOC102では、各IPプロック104がメモリ・アドレス・ベースの通信をIPプロックのメモリ通信コントローラ106を介してメモリとそしてまたそのネットワーク・インターフェイス・コントローラ108を介してネットワークともやり取りする。メモリ・アドレス・ベースの通信は、IPプロックのメモリ通信コントローラ106のメモリ通信実行エンジン140によって実行される、ロード命令もしくはストア命令などのメモリ・アクセス命令である。そのようなメモリ・アドレス・ベースの通信は、典型的にはIPプロック104において引起され、コマンド・フォーマットで記述され、そしてメモリ通信コントローラ106に実行のために引き渡される。

#### [0031]

多くのメモリ・アドレス・ベースの通信は、メッセージ・トラフィックでもって実行され る。何故ならアクセスされるべき任意のメモリが、オンチップの、またはそのNOCにお けるいずれかのメモリ通信コントローラ106に直接取付けられ得るオフチップの、ある いはそのNOCのいずれかのIPブロックを介して究極的にアクセスされ得る、物理的な メモリ・アドレス空間のどこかの箇所に置かれることができるからである。その際、どの IPブロックが特定のメモリ・アドレス・ベースの通信を引起こすかは関係ない。メッセ ージ・トラフィックでもって実行される全てのメモリ・アドレス・ベースの通信は、メモ リ通信コントローラ 1 0 6 からその関連付けられているネットワーク・インターフェイス ・コントローラ108にパスされ、そこでコマンド・フォーマットからパケット・フォー マットに変換(命令変換論理136)し、ネットワークを介してメッセージで伝送する。 パケット・フォーマットに変換する際、ネットワーク・インターフェイス・コントローラ 108はまたメモリ・アドレス・ベースの通信によりアクセスされる1個もしくは複数個 のメモリ・アドレスに依存してそのパケットのためのネットワーク・アドレスを識別する 。メモリ・アドレス・ベースのメッセージはメモリ・アドレスでアドレスされる。各メモ リ・アドレスは、ネットワーク・インターフェイス・コントローラ108によって、メモ リ通信コントローラ106の、ネットワーク・アドレスの、典型的には、或る程度の範囲 の物理的メモリ・アドレスの範囲に亘るネットワークの箇所にマップされる。メモリ通信

20

30

40

50

コントローラ 1 0 6 のネットワークの位置は、自ずとそのメモリ通信コントローラ 1 0 6 の関連付けられているルーター 1 1 0、ネットワーク・インターフェイス・コントローラ 1 0 8 および I P ブロック 1 0 4 のネットワークの位置でもある。各ネットワーク・インターフェイス・コントローラ 1 0 8 内の命令変換論理 1 3 6 はMOCのルーター 1 1 0 を介してメモリ・アドレス・ベースの通信を伝送するために、メモリ・アドレスをネットワーク・アドレスに変換することができる。

#### [0032]

ネットワークのルーター110からのメッセージ・トラフィックを受取ると、各ネットワーク・インターフェイス・コントローラ108はメモリ命令の各パケットを検査する。メモリ命令を含む各パケットはその受取っているネットワーク・インターフェイス・コントローラ108と関連付けられているメモリ通信コントローラ106に渡され、これがそのパケットの残りのペイロードを更なる処理のためのIPブロック104に送る前にそのメモリ命令を実行する。このようにして、そのIPブロック104が特定のメモリ・コンテンツに依存するメッセージからの命令を実行する前に、メモリ・コンテンツがIPブロック104によるデータ処理をサポートするために常に準備される。

# [0033]

図2のNOC102では、各IPブロック104がそのメモリ通信コントローラ106を バイパスするように、そしてそのIPブロック104のネットワーク・インターフェイス ・コントローラ108を介してネットワークに直接、IPブロック間のネットワーク・ア ドレスの通信146を送る。ネットワーク・アドレスの通信146は、ネットワーク・ア ドレスによって他のIPブロックに差向けられるメッセージである。このようなメッセー ジは、パイプライン化されたアプリケーション中の作業データ、SIMDアプリケーショ ンにおけるIPブロック間での単一のプログラム処理のための複数のデータなど、当業者 の想到するようなものを伝送する。そのようなメッセージは、メモリ・アドレス・ベース の通信とは以下のような点で区別される。それらは、そのNOCのルーターを介してメッ セージが差向けられる先のネットワーク・アドレスを知る発生元のIPブロック104に よって、そのスタートからアドレスされるネットワークである点で区別される。そのよう なネットワーク・アドレスの通信は、IPブロック104によってそこを通り抜けるよう にパスされ、I/O機能124から直接にIPブロック104のネットワーク・インター フェイス・コントローラ108に、コマンド・フォーマットで送られ、それからIPブロ ックのネットワーク・インターフェイス・コントローラ 1 0 8 によりパケット・フォーマ ットに変換され、他のIPブロックのルーターを介して伝送される。そのようなネットワ ーク・アドレスの通信146は双方向であり、何か特定のアプリケーションでのそれらの 使用に依存してそのNOCの各IPブロックにもしくはそこから進み得る。しかし各ネッ トワーク・インターフェイス・コントローラ108は、関連付けられているルーター11 0とのそのような通信を(メモリ通信命令142で)送受し、そして各ネットワーク・イ ンターフェイス・コントローラ108は、関連付けられているIPブロック104とのそ のような通信を(ネットワーク・アドレス通信146で)直接に送受する。この直接に送 受する際は、関連付けられているメモリ通信コントローラ106をバイパスする。

### [0034]

図3の実施例における各ネットワーク・インターフェイス・コントローラ108はまたそのネットワーク上に仮想チャネルを実装し、ネットワーク・パケットをタイプによって特徴付ける。各ネットワーク・インターフェイス・コントローラ108は、各通信命令をタイプによって分類する仮想チャネル実装論理138を含み、そのネットワーク・パケット・フォーマットのフィールドにその命令のタイプを記録する。その記録後、パケット形式の命令はNOC上で伝送するためルーター110に渡される。通信命令のタイプの例は、エアブロック間ネットワーク・アドレス・ベースのメッセージ、リクエスト・メッセージ、メモリ・リクエスト・メッセージ、メモリ・ロード・メッセージ、メモリ・コード・メッセージ、メモリ・ストア・メッセージ、メモリ・ロード・メッセージ、メモリ・応答などを含む。

20

30

40

50

#### [0035]

図 3 の実施例の各ルーター 1 1 0 は、ルーティング論理 1 3 0 、仮想チャネル制御論理 1 3 2 および仮想チャネル・バッファ 1 3 4 を含む。ルーティング論理 1 3 0 は、ルーター 110、リンク120、およびルーター110相互間のバス・ワイヤにより形成されるネ ットワーク中のデータ通信のためのデータ通信プロトコル・スタックを実装する同期もし くは非同期の論理のネットワークとして実装される。ルーティング論理130は、当業者 ならルーティング・テーブルとオフチップのネットワークで関連付けることのできる機能 を含む。少なくとも幾つかの実施例におけるルーティング・テーブルはNOCで使用する にはあまりにも遅く扱いにくいと考えられている。同期および非同期の論理のネットワー クとして実装されるルーティング論理130は、単一のクロック・サイクルと同程度の速 さのルーティング決定を行うように構成されることができる。この実施例のルーティング 論理は、ルーター110で受取る各パケットを進めるためのポートを選択することにより パケットをルート付けする。各パケットはルート先のネットワーク・アドレスを含む。こ の実施例における各ルーター110は、5個のポート121、123を含み、そのうち4 個のポート121はバス・ワイヤ120-A、120-B、120-C、120-Dを介 して他のルーターに結合され、第5のポート123は各ルーター110をネットワーク・ インターフェイス・コントローラ 1 0 8 およびメモリ通信コントローラ 1 0 6 を介してそ の関連付けられているIPブロック104に結合している。

#### [0036]

前述のメモリ・アドレス・ベースの通信を説明する際、各メモリ・アドレスは、ネットワーク・インターフェイス・コントローラ108によりネットワーク・アドレス、すなもり通信コントローラ106のネットワーク位置にマップされると説明した。メモリ通信コントローラ106のネットワーク位置にマップされると説明した。メロットローラ106のネットワークで置にス・コントローラ108の、関連付けられたルーター110、ネットワーク・インターフェイス・コントローラ108おークワブロック104のネットワークである。エアブロック間もしくはネットワークはネットワークのアドレス・ベースの通信において、アプリケーション・レベルのぎゃらのもである。マーク・アドレスが、カーク・アドレスが、たとえばそのメッシュの関連付けられたルーター110、エア・ロック104、メモリ通信コントローラ106およびネットワーク・インターフェイスのリーク・アドレスが、たとえばそのメッシュの関連付けられたルーター110、エイスのリーク・アドレスが、たとえばそのメッシュの関連付けられたルーター110、エイスのメック104、メモリ通信コントローラ106およびネットワーク・オンターにおけるそのような各セットの×およびソ座標として実装されることができる。

### [0037]

図3のNOC102では、各ルーター110が2個もしくはそれ以上の仮想通信チャネルを実装する。そこでは各仮想通信チャネルが通信のタイプによって特徴付けられる。通信命令のタイプ、従って仮想チャネル・タイプは前述したものを含む。すなわちェアブロック間ネットワーク・アドレス・ベース・メッセージ、リクエスト・メッセージ、リクエスト・メッセージ、リクエスト・メッセージや、メモリ・ロード・メッセージ、メモリ・ストア・メッセージや、メモリ・ロード・メッセージ、メモリ・の応答などを含む。仮想チャネルをサポートするに際し、図3の実施例における各ルーターは、仮想チャネル制御論理132はその割当てられた通信タイプごとに受取ったパケットを調べ、そのNOC上の隣接するルーターにポートを介して、伝送用の通信タイプのため、出入りする仮想チャネル・バッファ中に各々のパケットを置く。

# [0038]

仮想チャネル・バッファ 1 3 4 は各々、有限のストレージ空間を有する。短期間に多くのパケットを受取ると、仮想チャネル・バッファが一杯になることがある。そうなるとバッファにはそれ以上のパケットを置くことができない。他のプロトコルでは、バッファが一杯の仮想チャネルに到来するパケットは落とされることになろう。しかしこの実施例の各

20

30

40

50

仮想チャネル・バッファ134 は、仮想チャネルにおける伝送を中断すなわち特定の通信タイプのパケットの伝送を中断するために仮想チャネル制御論理132を介して周囲のルーターにアドバイスするようバス・ワイヤの制御信号で以ってイネーブル(能動化)される。一つの仮想チャネルがそのように中断されると、他の全てのチャネルが影響を受けなくなり、その全能力で動作し続けることができる。この制御信号は各ルーターの関連付けられたネットワーク・インターフェイス・コントローラ108は、このようはると戻される。各ネットワーク・インターフェイス・コントローラ108は、このような信号を受取ると、その関連付けられたメモリ通信コントローラ106からまたはその関連付けられたエアブロック104から、その中断された仮想チャネルのための通信命令を受取るのを拒否するように構成される。このようにして、仮想チャネルの中断がその仮想チャネルを実装する全てのハードウエアに影響を及ぼし、その起源となっているエアブロック104までずっと戻される。

[0039]

仮想チャネルでパケットの転送を中断する一つの効果は図3のアーキテクチャでパケットが決して落ちないことである。インターネット・プロトコルのようなある種の信頼性のないプロトコルでパケットが落ちかねない状況にルーターが遭遇すると、図3の実施例におけるルーター110は仮想チャネル・バッファ134および仮想チャネル制御論理132により仮想チャネル中のパケットの全ての転送を中断する。それはバッファ空間が再び利用できるようになりパケットを落とす必要がなくなるまで中断する。このように、図3のNOC102は、ハードウエアの非常に薄い層とともに非常に信頼性の高いネットワーク通信プロトコルを実装する。

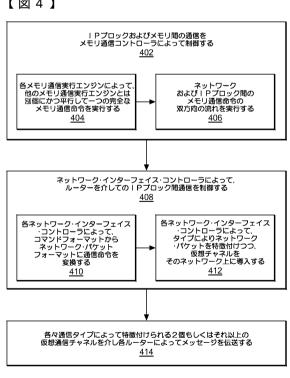

[0040]

更に説明すると、図4は、本発明の実施例によるNOCを備えた例示のデータ処理方法のフローチャートを開示する。図4の方法は、図3のIPブロック104、ルーター110、メモリ通信コントローラ106およびネットワーク・インターフェイス・コントローラ108とともに図3のチップ100上に図3のNOC102が実装されているような、この明細書で前述したNOC或いはその等価物で実行される。図3の各IPブロック104はルーター110にメモリ通信コントローラ106およびネットワーク・インターフェイス・コントローラ108を介してつながっている。図4の方法では、各IPブロックが、NOC内のデータ処理のための組立てブロックとして使用される同期もしくは非同期の論理設計の再使用可能なユニットとして実装されることができる。

[0041]

図4の方法は、IPブロックおよびメモリの間のメモリ通信コントローラ106(図3)によって制御するステップ402を含む。図4の方法では、メモリ通信コントローラ106(図3)が複数個のメモリ通信実行エンジン140(図3)を含む。また図4の方法では、IPブロック104およびメモリの間の通信を制御するステップ402は、各メモリ通信実行エンジン140によって他のメモリ通信実行エンジンとは別個にかつ並行してつの完全なメモリ通信命令を実行するステップ404と、そのネットワークおよびIPブロック104の間のメモリ通信命令の双方向の流れを実行するステップ406とによって行われる。図4の方法では、メモリ通信命令が、変換ルックアサイド・バッファの制御命令、キャッシュ制御命令、バリア命令、メモリ・ロード命令およびメモリ・ストア命令を含むことができる。図4の方法では、メモリが、オフチップ・メインRAM、IPブロックにメモリ通信コントローラ106を介して直接結合されたメモリIPブロック、IPブロックのオンチップ・メモリおよびオンチップ・キャッシュを含む。

[0042]

図4の方法は、また図3のネットワーク・インターフェイス・コントローラ108によって、ルーターを介してのIPブロック間通信を制御するステップ408を含む。図4の方法において、IPブロック間通信を制御するステップ408はまた、各ネットワーク・インターフェイス・コントローラ108によって、コマンド・フォーマットからの通信命令をネットワーク・パケット・フォーマットに変換するステップ410と、各ネットワーク

・インターフェイス・コントローラ 1 0 8 によって、そのネットワーク上に、ネットワーク・パケットをタイプにより特徴付つつ、仮想チャネルを導入するステップ 4 1 2 とを含む。

[0043]

図4の方法はまた、各々通信タイプによって特徴付けられる2個もしくはそれ以上の仮想通信チャネルを介し各ルーター110(図3)によってメッセージを伝送するステップ414を含む。通信命令タイプ、従って仮想チャネル・タイプは、たとえばIPブロック間ネットワーク・アドレス・ベース・メッセージ、リクエスト・メッセージ、リクエスト・メッセージ、リクエスト・メッセージ、メモリ・ロード・メッセージや、メモリ・ロード・メッセージへの応答、キャッシュに差し向けられる無効化メッセージや、メモリ・ロード・メッセードとができるむ。仮想チャネルをサポートする際、各ルーター110はまた仮想チャネル制御論理132(図3)および仮想チャネル・バッファ134(図3)を含む。この仮想チャネル制御論理132は、その割当てられた通信タイプごとに受取ったパケットを調べ、そのNOC上の隣接するルーターにポートを介して、伝送用の通信タイプのため、出入りする仮想チャネル・バッファ中に各々のパケットを置く。

[0044]

本発明の実施例はNOCを備えたデータ処理のための完全な機能のコンピュータ・システ ムとして記述されている。しかし本発明が任意の適当なデータ処理システムとともに使用 される信号担持媒体上に配設されたコンピュータ・プログラム製品で 具体化されてもよ いことを当業者は理解できよう。このような信号担持媒体はマシン読取り可能な情報のた めの伝送媒体もしくは記録可能媒体、磁気媒体、光媒体もしくは他の適当な媒体であって もよい。記録可能媒体の例は、ハード・ドライブにおける磁気ディスクもしくはディスケ ット(フロッピー・ディスク)、光ドライブのためのコンパクト・ディスク、磁気テープ その他当業者の想到するものなどを含む。伝送媒体の例は、音声通信のための電話網( ネットワーク)およびEthernet(登録商標)などのディジタル・データ通信ネッ トワーク、インターネット・プロトコルおよびWWW(ワールド・ワイド・ウエッブ)と 通信するネットワーク、ならびにスペックのIEEE802.11ファミリに従って導入 されるネットワークなどの無線伝送媒体を含む。当業者は直ぐに理解できると思うが、適 当なプログラミング手段を有するコンピュータ・システムが、プログラム製品で具体化さ れるのと本発明の方法の諸ステップを実行することができるであろう。当業者は直ぐに理 解できると思うが、この明細書に記述されているいくつかの実施例はソフトウエアがイン ストールされコンピュータ・ハードウエア上で実行されるものを指向しているものの、フ ァームウエアもしくはハードウエアとして導入される代替実施例も本発明の範囲内である

[0045]

本発明を好適な実施例に従って説明してきたが、本発明の種々の実施例において修正や変更をその真の精神から逸れずに行えることが前述の説明から理解できよう。本発明の記述は説明目的のためだけであり、限定する意味で解釈されてはならない。本発明の範囲は特許請求の範囲によってのみ限定される。

【図面の簡単な説明】

[0046]

【図1】本発明の実施例によるNOCを有し、データ処理において有用である例示のコン ピュータを含む自動化されたコンピューティング・マシンのブロック図である。

【図2】本発明の実施例による実施例のNOCの機能的なブロック図である。

【図3】本発明の実施例による別の実施例のNOCの機能的なブロック図である。

【図4】本発明の実施例によるNOCを備えたデータ処理のための実施例の方法を示すフローチャートである。

【符号の説明】

[0047]

100 チップ

20

10

30

40

```

101 ネットワーク

102 ネットワークオンチップ(NOC)

104 集積プロセッサ(IP)ブロック

105 ホスト・インターフェイス・プロセッサ

106 メモリ通信コントローラ

107、 109 メモリ管理ユニット(MMU)

108 ネットワーク・インターフェイス・コントローラ

110 ルーター

112 オフチップ・メインRAM

10

114、115 オンチップ・メモリ

116 ポート

120 リンク

120-A、120-B、120-C、120-D バス・ワイヤ

121、123 ポート

122 (IPブロックの)セット

124 I/O機能

126 プロセッサ

1 2 8

メモリ

130 ルーティング論理

20

132 仮想チャネル制御論理

134 仮想チャネル・バッファ

136 命令変換論理

138 仮想チャネル実装論理

140 メモリ通信実行エンジン

1 4 2 、 1 4 4 、 1 4 5 メモリ通信命令の流れ

146 ネットワーク・アドレス通信

152 コンピュータ

オペレーティング・システム

1 5 4

156 コンピュータ・プロセッサ(CPU)

30

157 NOCコプロセッサ

158 バス・アダプタ

160 拡張バス

162、163 フロント・サイド・バス

164 ビデオ・バス

メモリ・バス

1 6 6

167 通信アダプタ

1 6 8

ランダム・アクセス・メモリ( R A M )

1 7 0

データ・ストレージ

172 ディスク・ドライブ・アダプタ

40

1 7 8

I/Oアダプタ

180 ディスプレイ装置

1 8 1

ユーザー入力装置

1 8 2

他のコンピュータ

184 アプリケーション・プログラム

209 NOCビデオ・アダプタ

2 1 5 ポート

```

### 【図1】

# 【図2】

# 【図3】

# 【図4】

### フロントページの続き

(72)発明者 ラッセル・ディーン・フーヴァー

アメリカ合衆国 55906、ミネソタ州ロチェスタ、グレンビュー・レーン エヌ・イー 21 38

(72)発明者 エリック・オリヴァー・メイドリッチ

アメリカ合衆国 55901、ミネソタ州ロチェスタ、シクスティーセコンド・ストリート・エヌ・ダブリュ 2727

(72)発明者 ロバート・アラン・シェアラー

アメリカ合衆国 55902、ミネソタ州ロチェスタ、ティークウッド・レーン・エス・ダブリュ 2306

# 審査官 菅原 浩二

(56)参考文献 特開平07-311750(JP,A)

国際公開第2007/010461(WO,A1)

特開平06-075930(JP,A)

特開平08-185380(JP,A)

特開平06-223044(JP,A)

特開2001-167066(JP,A)

国際公開第2007/110914(WO,A1)

岡本 一晃,川口 正樹,三浦 宏喜,清水 雅久,データ駆動計算機 EDDEN とその性能評価 ,情報処理学会論文誌,日本,一般社団法人情報処理学会,1993年 4月15日,第34巻、第4号,681-689頁,URL,http://ci.nii.ac.jp/naid/110002722439/

山田 裕,鯉渕 道紘,松谷 宏紀,安生 健一朗,上樂 明也,天野 英晴,チップ内ネットワークにおけるトポロジに対する考察,情報処理学会研究報告.計算機アーキテクチャ研究会報告,日本,一般社団法人情報処理学会,2004年12月 1日,2004(123),35-40頁,URL,http://ci.nii.ac.jp/naid/110002722439/

Benini, L.; De Micheli, G., Networks on chips: a new SoC paradigm, Computer, IEEE, 2 0 0 2 年 1月, Vol.35, no.1, pp.70-78, URL, http://ieeexplore.ieee.org/xpls/abs\_all.jsp?arnumber=976921&tag=1

(58)調査した分野(Int.CI., DB名)

G06F 13/36