# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**G09G 3/36** (2006.01)

(21) 출원번호 **10-2010-0035631**

(22) 출원일자 **2010년04월19일**

심사청구일자 **2010년04월19일**

(65) 공개번호 10-2011-0069674

(43) 공개일자 **2011년06월23일**

(30) 우선권주장

1020090126071 2009년12월17일 대한민국(KR)

(56) 선행기술조사문헌

KR1020010100772 A

KR1020030083922 A

KR100761842 B1

JP2003295830 A

전체 청구항 수 : 총 16 항

(45) 공고일자 2012년03월23일

(11) 등록번호 10-1128690

(24) 등록일자 2012년03월14일

(73) 특허권자

매그나칩 반도체 유한회사

충북 청주시 흥덕구 향정동 1

(72) 발명자

정규영

서울특별시 송파구 백제고분로45길 13-17, 301호

(송파동)

(74) 대리인

이현수, 정홍식, 김태헌, 김종선

심사관 : 이성현

#### 전세 6 1 8 1 . 6 10 8

### (54) 발명의 명칭 숭압전압 생성회로 및 이의 동작방법

#### (57) 요 약

전류소모를 줄이기 위한 승압전압 생성회로가 개시된다. 승압전압 생성회로는, 입력전압을 승압배율만큼 승압하여 출력전압을 출력하는 승압회로; 상기 입력전압의 레벨을 피드백하여 승압배율을 설정하는 승압배율 설정부; 및 상기 출력전압의 목표레벨과 상기 승압배율에 응답하여 상기 입력전압의 레벨을 설정하는 입력전압 레벨 설정부를 포함한다.

#### 대 표 도 - 도2

## 특허청구의 범위

#### 청구항 1

입력전압을 승압배율만큼 승압하여 출력전압을 출력하는 승압회로;

상기 입력전압의 레벨을 피드백받아 승압배율을 설정하는 승압배율 설정부; 및

상기 출력전압의 목표레벨과 상기 승압배율에 응답하여 상기 입력전압의 레벨을 설정하는 입력전압 레벨 설정부를 포함하는 승압전압 생성회로.

#### 청구항 2

제 1항에 있어서,

상기 입력전압 레벨 설정부는,

(출력전압의 목표레벨/승압배율)을 상기 입력전압의 목표 레벨로 설정하는 것을 특징으로 하는 승압전압 생성회로.

#### 청구항 3

제 2항에 있어서,

상기 승압배율 설정부는,

상기 입력전압의 목표 레벨이 상기 입력전압이 가질 수 없는 레벨인 경우에 상기 승압배율을 높이는 것을 특징으로 하는 승압전압 생성회로.

## 청구항 4

제 3항에 있어서,

상기 승압배율 설정부는,

상기 승압배율이 낮아지더라도 상기 입력전압의 목표 레벨이 상기 입력전압이 가질 수 있는 레벨인 경우에 상기 승압배율을 낮추는 것을 특징으로 하는 승압전압 생성회로.

#### 청구항 5

제 1항에 있어서,

상기 입력전압 레벨 설정부는,

상기 승압배율에의해 결정되는 비율로 상기 출력전압을 전압분배해 출력하는 출력전압 분배부;

상기 출력전압의 목표레벨에 따라 생성된 다수의 전압 중 상기 승압배율에 따라 입력기준전압을 선택하는 입력 기준전압 선택부;

상기 출력전압 분배부의 출력전압과 상기 입력 기준전압 선택부의 출력전압을 비교해 예비 입력전압을 생성하는 비교부; 및

상기 예비 입력전압을 증폭해 상기 입력전압을 생성하는 증폭부

를 포함하는 것을 특징으로 하는 승압전압 생성회로.

#### 청구항 6

제 5항에 있어서,

상기 출력전압 분배부는,

상기 출력전압을 1/(승압배율\*증폭부의 증폭배율)비율로 전압분배하는 것을 특징으로 하는 승압전압 생성회로.

#### 청구항 7

제 6항에 있어서,

상기 입력 기준전압 선택부는,

상기 출력전압의 목표레벨/(숭압배율\*증폭부의 증폭배율)이 되는 상기 입력기준전압을 선택하는 것을 특징으로 하는 숭압전압 생성회로.

### 청구항 8

제 5항에 있어서,

상기 입력전압 레벨 설정부는,

상기 예비 입력전압이 지나치게 높아지거나 낮아지는 것을 방지하기 위한 전압클램프부를 더 포함하는 것을 특징으로 하는 승압전압 생성회로.

### 청구항 9

제 8항에 있어서,

상기 입력전압 레벨 설정부는,

상기 예비 입력전압의 레벨을 안정화시키기 위한 보상회로를 더 포함하는 것을 특징으로 하는 승압전압 생성회로.

### 청구항 10

제 5항에 있어서,

상기 승압배율 설정부는,

배율업 기준전압과 배율다운 기준전압을 생성하는 전압분배부;

상기 예비 입력전압이 상기 배율업 기준전압보다 높으면 배율업 플래그신호를 활성화시키고, 상기 예비 입력전 압이 상기 배율다운 기준전압보다 낮으면 배율다운 플래그신호를 활성화시키는 플래그신호 생성부; 및

상기 배율업 플래그신호 및 상기 배율다운 플래그신호에 응답하여 상기 승압배율을 설정하는 승압배율 제어부를 포함하는 것을 특징으로 하는 승압전압 생성회로.

#### 청구항 11

제 10항에 있어서,

상기 승압배율 설정부는,

상기 승압배율의 초기값에 관한 정보를 상기 승압배율 제어부로 제공하기 위한 초기값 결정부를 더 포함하는 것을 특징으로 하는 승압전압 생성회로.

#### 청구항 12

제 10항에 있어서,

상기 승압배율 제어부는,

상기 배율업 플래그 신호가 기준시간 이상 활성화되면 상기 승압배율을 높이고, 상기 배율다운 플래그 신호가 기준시간 이상 활성화되면 상기 승압배율을 낮추는 것을 특징으로 하는 승압전압 생성회로.

#### 청구항 13

제 10항에 있어서,

상기 배율업 기준전압은 전원전압/(증폭부의 증폭배율)의 레벨이고,

상기 배율다운 기준전압은 전원전압\*(승압배율-승압배율 변경의 단위)/(증폭부의 증폭배율\*승압배율)의 레벨인 것을 특징으로 하는 승압전압 생성회로.

#### 청구항 14

입력전압을 승압배율만큼 승압하여 출력전압을 생성하는 승압전압 생성회로의 동작방법에 있어서,

(출력전압의 목표전압/승압배율)의 레벨을 목표로하여 상기 입력전압을 생성하는 단계;

상기 입력전압의 목표 레벨이 상기 입력전압이 가질 수 없는 레벨인 경우에 상기 승압배율을 높이는 단계; 및 상기 승압배율이 낮아지더라도 상기 입력전압의 목표 레벨이 상기 입력전압이 가질 수 있는 레벨인 경우에 상기 숭압배율을 낮추는 단계

를 포함하는 승압전압 생성회로의 동작방법.

### 청구항 15

제 14항에 있어서,

상기 입력전압이 가질 수 없는 레벨은,

전원전압보다 높은 레벨인 것을 특징으로 하는 승압전압 생성회로의 동작방법.

#### 청구항 16

제 14항에 있어서,

상기 승압배율을 낮추는 단계는,

상기 입력전압이 전원전압\*(숭압배율 - 숭압배율 변경의 단위)/(숭압배율) 보다 낮은 경우에 상기 숭압배율을 낮추는 것을 특징으로 숭압전압 생성회로의 동작방법.

#### 명세서

### 기술분야

[0001] 본 발명은 입력전압보다 높은 레벨의 승압전압을 생성하는 승압전압 생성회로 및 이의 동작방법에 관한 것이다.

#### 배경기술

- [0002] 각종 반도체 장치는 외부에서 공급된 전압을 이용하여 내부의 회로를 동작시킨다. 그런데, 반도체 장치 내부에서 사용되는 전압의 종류는 매우 다양하기 때문에, 반도체 장치 내부에서 사용할 모든 전압을 외부에서 공급해주기는 힘들다. 따라서, 반도체 장치는 내부적으로 새로운 레벨의 전압을 생성해주기 위한 내부전압 생성회로를구비한다.

- [0003] 특히, 배터리(battery) 전원을 사용한는 디바이스(device)는, 배터리로부터 공급되는 전원전압의 레벨은 낮고 내부에서 사용해야 하는 구동 전압들은 이보다 높은 레벨인 경우에, 내부적으로 외부에서 입력된 전원전압보다 높은 전압을 생성해야 한다. 입력된 전압보다 높은 전압을 생성해주는 DC-DC 컨버터(converter)는 크게 인덕터 (inductor)를 사용하는 SMPS(Switched Mode Power Supply) 타입과 캐패시터(capacitor)를 사용하는 차지펌프 (Charhe pump) 타입이 있는데, 모바일 디바이스의 경우에 전류 소비가 높지 않으므로, 주로 차지펌프 타입을 사용하고 있다.

- [0004] 도 1은 승압전압 생성회로에 입력되는 전압, 정보 및 출력되는 전압을 나타낸 도면이다.

- [0005] 승압전압 생성회로(100)에는 입력전압(VCIN)과 배율정보(BT[a:0])가 입력된다. 그러면 승압전압 생성회로(100)는 입력전압(VCIN)을 배율정보(BT[a:0])가 나타내는 배율만큼 승압하여 승압전압(VOUT)을 생성한다. 예를 들어, 배율정보(BT[a:0])가 x2의 정보를 가지고 있는 경우 승압전압 생성회로(100)는 입력전압(VCIN)을 2배 승압하여 승압전압(VOUT)을 생성한다.

- [0006] 승압전압 생성회로(100)에서 승압전압(VOUT)의 목표(target) 값이 동일하더라도 입력전압(VCIN)과 배율정보 (BT[a:0])는 다양할 수 있다. 예를 들어, 승압전압(VOUT))의 목표 값이 3V인 경우 (1)1.5V의 입력전압(VCIN)을 2배 승압하여 3V의 승압전압(VOUT)을 생성할 수도 있으며, (2)1V의 입력전압(VCIN)을 3배 승압하여 3V의 승압전압(VOUT)을 생성할 수도 있다. 그런데, 동일한 승압전압(VOUT)을 생성하더라도 입력전압(VCIN) 및 승압배율(BT[a:0])을 어떻게 설정하는지에 따라 승압전압 생성회로(100)가 소비하는 전류량은 크게 달라진다.

- [0007] 따라서 승압전압(VOUT)의 목표 레벨에 따라 승압전압 생성회로(100)에 입력되는 입력전압(VCIN) 및 승압배율 (BT[a:0])을 최적화하기 위한 기술이 요구되고 있다.

#### 발명의 내용

#### 해결하려는 과제

[0008] 본 발명은 숭압전압(출력전압)의 목표 레벨에 따라 최적의 입력전압 및 숭압배율을 설정하여 최소한의 전류로 숭압전압을 생성하는 숭압전압 생성회로 및 그 동작방법을 제공하고자 하는데 그 목적이 있다.

#### 과제의 해결 수단

- [0009] 상기한 목적을 달성하기 위한 본 발명에 따른 승압전압 생성회로는, 입력전압을 승압배율만큼 승압하여 출력전압을 출력하는 승압회로; 상기 입력전압의 레벨을 피드백받아 승압배율을 설정하는 승압배율 설정부; 및 상기 출력전압의 목표레벨과 상기 승압배율에 응답하여 상기 입력전압의 레벨을 설정하는 입력전압 레벨 설정부를 포함한다.

- [0010] 상기 입력전압 레벨 설정부는, (출력전압의 목표레벨/승압배율)을 상기 입력전압의 목표 레벨로 설정하는 것을 특징으로 할 수 있다.

- [0011] 상기 승압배율 설정부는, 상기 입력전압의 목표 레벨이 상기 입력전압이 가질 수 없는 레벨인 경우에 상기 승압 배율을 높이는 것을 특징으로 할 수 있다.

- [0012] 상기 승압배율 설정부는, 상기 승압배율이 낮아지더라도 상기 입력전압의 목표 레벨이 상기 입력전압이 가질 수 있는 레벨인 경우에 상기 승압배율을 낮추는 것을 특징으로 할 수 있다.

- [0013] 상기한 목적을 달성하기 위한 본 발명은, 입력전압을 승압배율만큼 승압하여 출력전압을 생성하는 승압전압 생성회로의 동작방법에 있어서, (출력전압의 목표전압/승압배율)의 레벨을 목표로 하여 상기 입력전압을 생성하는 단계; 상기 입력전압의 목표 레벨이 상기 입력전압이 가질 수 없는 레벨인 경우에 상기 승압배율을 높이는 단계; 및 상기 승압배율이 낮아지더라도 상기 입력전압의 목표 레벨이 상기 입력전압이 가질 수 있는 레벨인 경우에 상기 승압배율을 낮추는 단계를 포함한다.

- [0014] 상기 입력전압이 가질 수 없는 레벨은, 전원전압보다 높은 레벨인 것을 특징으로 할 수 있다.

- [0015] 상기 승압배율을 낮추는 단계는, 상기 입력전압이 전원전압\*(승압배율 승압배율 변경의 단위)/(승압배율) 보다 낮은 경우에 상기 승압배율을 낮추는 것을 특징으로 할 수 있다.

### 발명의 효과

- [0016] 본 발명에 따른 승압전압 생성회로는 목표한 레벨의 승압전압을 생성하기 위해, 입력전압을 최대한 높이고 승압 배율을 최대한 낮춘다. 따라서 최소의 승압배율로 입력전압을 승압하여 목표한 레벨의 승압전압을 생성할 수 있도록 한다.

- [0017] 따라서 결국 승압전압 생성회로의 소비전류가 최소로 유지될 수 있다는 장점이 있다.

## 도면의 간단한 설명

- [0018] 도 1은 승압전압 생성회로에 입력되는 전압, 정보 및 출력되는 전압을 나타낸 도면.

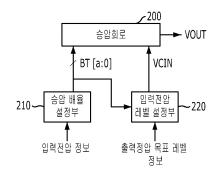

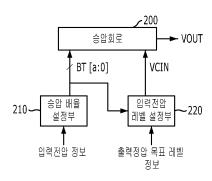

- 도 2는 본 발명에 따른 승압전압 생성회로의 일실시예 구성도.

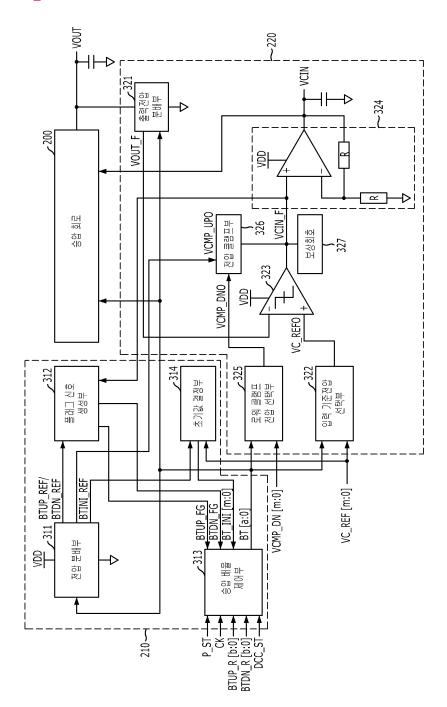

- 도 3은 도 2의 승압전압 생성회로의 상세 실시예 구성도.

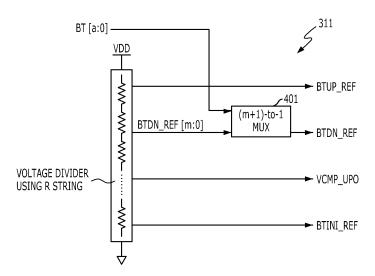

- 도 4는 전압분배부(311)의 일실시예 구성도.

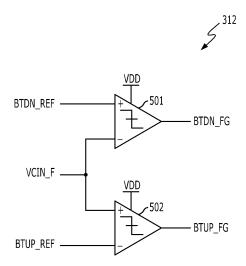

- 도 5는 플래그신호 생성부(312)의 일실시예 구성도.

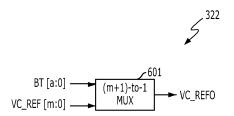

- 도 6은 입력 기준전압 선택부(322)의 일실시예 구성도.

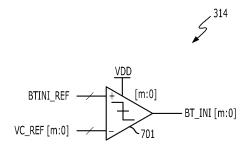

- 도 7은 초기값 결정부(314)의 일실시예 구성도.

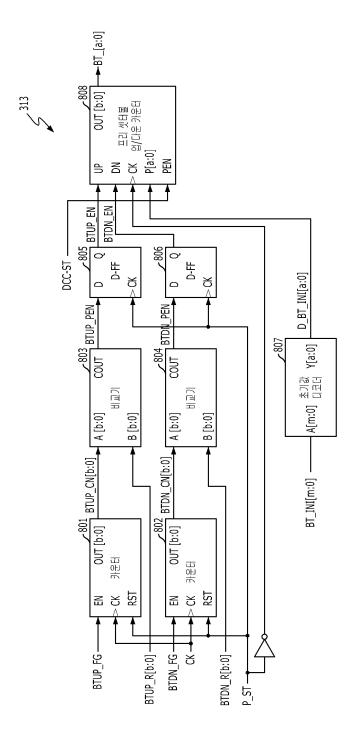

- 도 8은 승압배율 제어부(313)의 일실시예 구성도.

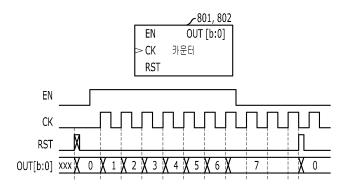

- 도 9는 카운터(801, 802)의 동작을 설명하기 위한 도면.

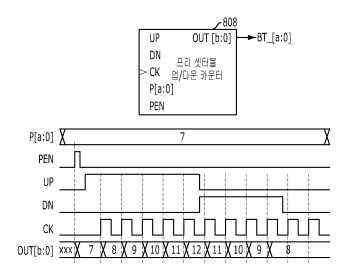

- 도 10은 프리 셋터블(pre settable) 업/다운 카운터(808)의 동작을 설명하기 위한 도면.

- 도 11~14는 승압배율 제어부(313)의 동작을 도시한 도면.

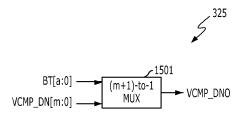

- 도 15는 로워 클램프 전압 선택부(325)의 구성도.

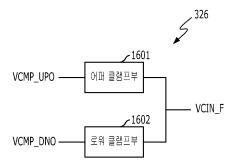

- 도 16은 전압 클램프부(326)의 구성도.

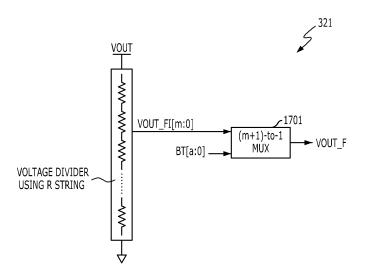

- 도 17은 출력전압 분배부(321)의 구성도.

- 도 18은 보상회로(327)의 구성도.

#### 발명을 실시하기 위한 구체적인 내용

[0019] 이하, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있도록 상세히 설명하기 위하여, 본 발명의 가장 바람직한 실시예를 첨부 도면을 참조하여 설명하기로 한다.

- [0020] 도 2는 본 발명에 따른 승압전압 생성회로의 일실시예 구성도이다.

- [0021] 도 2에 도시된 바와 같이, 본 발명에 따른 승압전압 생성회로는, 입력전압(VCIN)을 승압배율(BT[a:0])만큼 승압 하여 출력전압(VOUT)을 출력하는 승압회로(200); 입력전압(VCIN)의 레벨을 피드백받아 승압배율(BT[a:0])을 설정하는 승압배율 설정부(210); 및 출력전압(VOUT)의 목표레벨과 승압배율(BT[a:0])에 응답하여 입력전압(VCIN)의 레벨을 설정하는 입력전압 레벨 설정부(220)를 포함한다.

- [0022] 승압회로(200)는, 입력전압(VCIN)을 승압배율(BT[a:0])만큼 승압하여 출력전압(VOUT)을 생성한다. 따라서 출력 전압(VOUT)은 입력전압(VCIN)\*승압배율(BT[a:0])이 된다. 예를 들어, 승압배율(BT[a:0])이 x2이고 입력전압(VCIN)이 1V인 경우에는 출력전압(VOUT)이 2V가 되고, 승압배율(BT[a:0])이 x3이고 입력전압(VCIN)이 0.8V인 경우엔는 출력전압(VOUT)이 2.4V가 된다.

- [0023] 입력전압 레벨 설정부(220)는 출력전압(VOUT)의 목표레벨과 승압배율(BT[a:0])에 응답하여 입력전압(VCIN)의 레벨을 설정한다. 상세하게 입력전압 레벨 설정부(220)는 (출력전압의 목표레벨/승압배율)을 입력전압(VCIN)의 목표 레벨로 설정한다. 입력전압(VCIN)의 목표 레벨이 (출력전압의 목표레벨/승압배율)이라고 하더라도 입력전압(VCIN)의 레벨이 이보다 낮은 경우가 있을 수 있다. 입력전압(VCIN)은 전원전압(VDD)보다 높은 레벨일 수는 없는데 입력전압(VCIN)의 목표 레벨이 전원전압(VDD)의 레벨을 초과하는 경우도 있을 수 있기 때문이다.

- [0024] 승압배율 설정부(210)는 입력전압(VCIN)의 레벨을 피드백 받아 승압배율을 설정한다. 승압배율 설정부(210)는 입력전압(VCIN)의 목표 레벨이 입력전압(VCIN)이 가질 수 없는 레벨인 경우에 승압배율을 높인다. 입력전압 (VCIN)의 목표 레벨은 (출력전압의 목표레벨/승압배율)로 정해지는데 (출력전압의 목표레벨/승압배율)이 전원전 압(VDD)보다 높은 경우 입력전압(VCIN)은 자신의 목표 레벨에 도달할 수 없다. 이러한 경우 승압배율 설정부 (210)는 승압배율(BT[a:0])을 높인다. 승압배율(BT[a:0])을 높이는 것이 반드시 필요한 경우에만 승압배율 (BT[a:0])을 올리는 것이다. 입력전압(VCIN)의 목표 레벨은 (출력전압의 목표레벨/승압배율)이므로 승압배율을 높아지면 이에 따라서 입력전압(VCIN)의 목표 레벨도 낮아진다.

- [0025] 승압배율 설정부(210)는 승압배율(BT[a:0])이 한단계 낮아지더라도 입력전압(VCIN)의 목표 레벨이 입력전압 (VCIN)이 가질 수 있는 레벨인 경우에 승압배율(BT[a:0])을 낮춘다. 입력전압(VCIN)의 목표레벨은 (출력전압의 목표레벨/승압배율)이므로 승압배율(BT[a:0])이 낮아지면 입력전압(VCIN)의 목표 레벨이 높아지는데, 만약 승압배율(BT[a:0])이 낮아져서 입력전압(VCIN)의 목표 레벨이 높아지고 높아진 입력전압(VCIN)의 목표 레벨이 전원전압(VDD)보다 높아지는 경우에는 다시 승압배율(BT[a:0])을 높여야 하기 때문에 승압배율 설정부(210)가 이러한 동작을 하는 것이다.

- [0026] 즉, 승압배율 설정부(210)는 승압배율(BT[a:0])을 높이는 것이 반드시 필요할 때에만 승압배율(BT[a:0])을 높이고, 가능한 한 승압배율(BT[a:0])을 낮추는 동작을 한다고 볼 수 있다.

- [0027] 승압동작은 입력되는 전압보다도 높은 전압을 생성하는 동작으로, 승압배율이 높아질수록 소모되는 전류는 매우 크게 늘어난다. 따라서 동일한 전압을 생성하는데 있어서 되도록이면 승압배율을 낮출수록 승압동작에 소모되는 전류를 줄일 수 있다. 예를 들어, 1V를 3배 승압하여 3V의 전압을 생성하는 것보다는, 2V를 1.5배 승압하여 3V의 전압을 생성하는 것이 훨씬 전류가 적게 소모된다. 본 발명은 승압배율 설정부(210)와 입력전압 레벨 설정부(220)의 동작을 통하여, 가능한한 승압배율(BT[a:0])을 최소로 설정하여 주기 때문에 승압전압 생성희로의 전류소모를 최소화한다.

- [0028] 도 3은 도 2의 승압전압 생성회로의 상세 실시예 구성도이다.

- [0029] 도 3에 도시된 바와 같이, 승압배율 설정부(210)는 전압분배부(311), 플래그신호 생성부(312), 승압배율 제어부 (313), 및 초기값 결정부(314)를 포함하여 구성된다. 입력전압 레벨 설정부(220)는 출력전압 분배부(321), 입력 기준전압 선택부(322), 비교부(323), 증폭부(324), 로워 클램프전압 선택부(325), 전압 클램프부(326), 및 보상 회로(327)를 포함한다.

- [0030] 전압분배부(311)는 배율업 기준전압(BTUP\_REF)과 배율다운 기준전압(BTDN\_REF)을 생성한다. 플래그신호 생성부 (312)는 예비 입력전압(VCIN\_F)이 배율업 기준전압(BTUP\_REF)보다 높으면 배율업 플래그신호(BTUP\_FG)를 활성화시키고, 예비 입력전압(VCIN\_F)이 배율다운 기준전압(BTDN\_REF)보다 낮으면 배율다운 플래그신호(BTDN\_FG)를 활성화시킨다. 승압배율 제어부(313)는 배율업 플래그신호(BTUP\_FG)와 배율다운 플래그신호(BTDN\_FG)에 응답하여 승압배율(BT[a:0])을 설정한다. 초기값 결정부(314)는 승압배율(BT[a:0])의 초기값이 관한 정보(BT\_INI[m:0])를

승압배율 제공부(313)로 제공한다.

- [0031] 출력전압 분배부(321)는 승압배율(BT[a:0])에 의해 결정되는 비율로 출력전압(VOUT)을 전압분배해 출력한다. 입력 기준전압 선택부(322)는 출력전압(VOUT)의 목표레벨에 따라 생성된 다수의 전압(VR\_REF[m:0]) 중 승압배율(BT[a:0])에 따라 입력 기준전압(VC\_REFO)을 선택한다. 비교부(323)는 출력전압 분배부(321)의 출력전압(VOUT\_F)과 입력 기준전압 선택부(325)의 출력전압(VC\_REFO)을 비교해 예비 입력전압(VCIN\_F)을 생성한다. 증폭부(324)는 예비 입력전압(VCIN\_F)을 증폭해 입력전압(VCIN)을 생성한다. 로워 클램프전압 선택부(325)는 로워 클램프 전압(VCMP\_DNO)을 선택해 출력한다. 전압 클램프부(326)는 예비 입력전압(VCIN\_F)이 어퍼 클럼프 전압(VCMP\_UPO)보다 높아지지 않고 로워 클램프 전압(VCMP\_DNO)보다 낮아지지 않게 제어해, 예비 입력전압(VCIN\_F)이 지나치게 높아지거나 낮아지는 것을 방지한다. 보상회로(327)는 예비 입력전압(VCIN\_F)의 레벨을 안정화시키기 위해 구비된다.

- [0032] 각 부분의 상세한 구성 및 동작에 관하여는 개별 도면과 함께 상세히 설명하기로 한다.

- [0033] 도 4는 전압분배부(311)의 일실시예 도면이다.

- [0034] 도 4에 도시된 바와 같이, 전압분배부(311)는 전원전압단(VDD)과 접지단 사이에 연결된 다수의 저항들과, 아날로그 전압 먹스(401, Analog voltage MUX)를 포함하여 구성된다. (1)~(4)에서 전압분배부(311)가 생성하는 배율업 기준전압(BTUP\_REF), 배율다운 기준전압(BTDN\_REF), 어퍼 클램프 전압(VCMP\_UPO), 초기값 기준전압(BTINI\_REF)에 대해 알아본다.

- [0035] (1) 배율업 기준전압(BTUP\_REF)은 승압배율(BT[a:0])을 높이기 위한 기준이 되는 전압으로, 배율업 기준전압 (BTUP\_REF)과 예비 입력전압(VCIN\_F)이 비교되어 승압배율(BT[a:0])을 높일 것인지의 여부가 결정된다. 예비 입력전압(VCIN\_F)은 입력전압(VCIN)의 1/2의 레벨을 가진 전압인데, 입력전압(VCIN)이 전원전압(VDD)의 레벨과 동일한 경우 예비 입력전압(VCIN\_F)의 레벨이 더 높아져봐야 입력전압(VCIN)의 레벨이 더 이상 올라가는 것이 불가능하다. 즉, 예비 입력전압(VCIN\_F)의 레벨이 전원전압(VDD)/2의 레벨인 경우에 예비 입력전압(VCIN)의 레벨을 더 이상 높이더라도 출력전압(VOUT)은 높아질 수 없다. 따라서 이 지점의 전압이 배율업 기준전압(BTUP\_REF)의 레벨이 된다(BTUP\_REF=VDD/2). 여기서 배율업 기준전압(BTUP\_REF)의 레벨을 전원전압(VDD)/2로 설정한 것은, 증폭부(324)의 증폭배율을 x2로 예시하였기 때문이다. 따라서 배율업 기준전압(BTUP\_REF)을 보다 일반적으로 표현하면 배율업 기준전압(BTUP\_REF)의 레벨은 전원전압(VDD)/증폭부(324)의 증폭배율이 된다.

- [0036] (2) 배율다운 기준전압(BTDN\_REF)은 승압배율을 낮추기 위한 기준이 되는 전압으로, 배율다운 기준전압과 예비 입력전압이 비교되어 숭압배율을 낮출 것인지의 여부가 결정된다. m'은 숭압 단계를 나타내는 것으로 0단계부터 시작된다. 그리고 n'은 숭압배율을 나타내는 것으로 1.5배부터 0.5배 단위로 늘어난다.

- [0037] 하기의 표 1은 승압단계(m')와 이에 대응되는 승압배율(n')을 나타낸다.

[0038]

| <b>X</b> 1 |          |  |

|------------|----------|--|

| m'(승압단계)   | n'(승압배율) |  |

| 0단계        | x1.5     |  |

| 1단계        | x2       |  |

| 2단계        | x2.5     |  |

| 3단계        | х3       |  |

| 4단계        | x3.5     |  |

- [0039] 표 1을 통하여, 승압단계(m')와 승압배율(n')은 n'=(m'+3)/2의 관계를 갖는 것을 확인할 수 있다.

- [0040] 배율다운 기준전압(BTDN\_REF)은 승압배율(n')이 한단계 낮아지더라도 예비 입력전압(VCIN\_F)의 레벨이 전원전압 (VDD)/2보다 낮은 지점을 기준으로 설정된다. 따라서 배율다운 기준전압(BTDN\_REF)을 승압단계(m')로 나타내면 BTDN\_REF(m')=VDD(m'+2)/(2m'+6)로 설정되고, 배율다운 기준전압(BTDN\_REF)을 승압배율(n')로 나타내면 BTDN\_REF(n')=VDD(n'-0.5)/2n' 으로 설정된다. 이는 증폭부의 증폭배율이 x2이고, 승압단계 한단계의 차이가 x0.5인 것으로 가정한 값으로, 이를 보다 일반적으로 나타내면 BTDN\_REF(n')=VDD(n'-승압배율 변경의 단위)/(증폭부의 증폭배율xn')으로 나타낼 수 있다.

- [0041] 배율다운 기준전압(BTDN\_REF)을 선택하는 아날로그 전압 먹스(401)는 증폭배율(BT[a:0], 증폭배율(n')에 관한

정보를 갖는 코드임)에 따라서 상기와 같은 배율다운 기준전압(BTDN\_REF)이 선택되도록 동작한다.

- [0042] (3) 어퍼 클램프 전압(VCMP\_UPO)은 초기 입력전압(VCIN)의 레벨이 불필요하게 높아져서 로드(load) 조건이나 승압배율(BT[a:0])이 변경되었을 때 VCIN\_F가 목표 값으로 도달(converge)하는데 걸리는 시간이 증가하는 문제를 막기 위해, 전압 클램프부(326)로 입력되는 어퍼 클램프 전압(upper clamp voltage)이다. 초기 입력전압(VCIN\_F)이 의미있는 값을 갖는 지점은 VCIN\_F=VDD/2인 지점까지이다. 그런데, 초기 입력전압(VCIN\_F)이 이보다 높아지는 일이 발생하기도 하는데, 어퍼 클램프 전압(VCMP\_UPO)은 이를 막기 위해서 사용된다. 따라서 어퍼 클램프 전압(VCMP\_UPO)은 VDD/2+ a로 설정된다. 여기서 a는 마진으로 50mV 이내로 설정하면 된다.

- [0043] (4) 초기 기준전압(BTINI\_REF)은 최초 승압 동작시에 적정 승압배율(BT[a:0])을 결정하기 위해 사용되는 기준전 압이다. 최초 동작시에는 입력전압(VCIN)이 전원전압(VDD)과 동일한 상태에서 시작하는 것이 이상적이므로 초기 기준전압(BTINI\_REF)은 전원전압(VDD)/2로 설정된다. 여기에 승압전압 생성회로 자체의 동작 전류를 고려하여 약간의 마진을 준다면 초기 기준전압(BTINI\_REF)은 전원전압(VDD)/2+β로 하고 β는 50mV 내외의 값으로 설정하면 된다.

- [0044] 도 5는 플래그신호 생성부(312)의 일실시예 구성도이다.

- [0045] 도 5에 도시된 바와 같이, 플래그신호 생성부(312)는 2개의 비교기(501, 502)를 포함하여 구성된다. 비교기 (501)는 예비 입력전압(VCIN\_F)과 배율다운 기준전압(BTDN\_REF)을 비교하여 배율다운 플래그신호(BTDN\_FG)를 생성하고, 비교기(502)는 예비 입력전압(VCIN\_F)과 배율업 기준전압(BTUP\_REF)을 비교하여 배율업 플래그신호 (BTUP)FG)를 생성한다.

- [0046] 예비 입력전압(VCIN\_F)이 배율다운 기준전압(BTDN\_REF)보다 낮으면 승압배율(BT[a:0])을 낮추기 위한 배율다운 플래그신호(BYDN\_FG)가 활성화된다. 그리고 예비 입력전압(VCIN\_F)이 배율업 기준전압(BTUP\_REF)보다 높으면 승압배율(BT[a:0])을 높이기 위한 배율업 플래그신호(BTUP\_FG)가 활성화된다.

- [0047] 예비 입력전압(VCIN\_F)이 배율다운 기준전압(BTDN\_REF)보다 높고 배율업 기준전압(BTUP\_REF)보다 낮은 경우에는 배율업 플래그신호(BTUP\_FG)와 배율다운 플래그신호(BTDN\_FG)가 모두 비활성화된다. 이 경우에는 현재의 숭압배율(BT[a:0])이 적절하다는 것을 의미한다.

- [0048] 도 6은 입력 기준전압 선택부(322)의 일실시예 구성도이다.

- [0049] 도 6에 도시된 바와 같이, 입력 기준전압 선택부(322)는 아날로그 전압 먹스(601, analog voltage MUX)를 포함 하여 구성된다.

- [0050] 입력 기준전압(VC\_REFO)은 예비 입력전압(VCIN\_F)의 목표값이 되는 전압이다. 따라서 입력 기준전압(VC\_REFO)은 VOUT,tar/(2n')로 설정된다(VOUT,tar는 출력전압의 목표값). 이는 증폭부(324)의 증폭배율이 2배인 것을 가정한 것인데, 입력 기준전압(VC\_REFO)을 보다 일반적으로 나타내면 입력 기준전압(VC\_REFO)은 VOUT.tar/(증폭부의 증폭값?n')이 된다.

- [0051] 먹스(601)에 입력되는 VC\_REF[m']의 값을 구하기 위해 n'를 m'에 관한 값으로 변환하면 VC\_REF[m']는 VOUT,tar/(m'+3)이 된다. 따라서 VC\_REF[m:0]을 위와 같이 설정하고, 먹스(601)는 해당 승압배율(BT[a:0])에 맞는 전압을 입력 기준전압(VC\_REF0)으로 선택하면 된다.

- [0052] 도 7은 초기값 결정부(314)의 일실시예 구성도이다.

- [0053] 도 7에 도시된 바와 같이, 초기값 결정부(314)는 VC\_REF[m:0] 각각을 초기 기준전압(BTINI\_REF)과 비교하는 m+1 개의 비교기(701)를 포함하여 구성된다. m+1개의 비교기(701)에서는 각각 초기값에 관한 정보(BT\_INI[m:0])가 출력된다. 도면에서는 비교기(701)를 하나로만 도시하였지만, 실제로는 m+1개의 비교기가 구비된다. 첫번째 비교기는 VC\_REF[0]과 초기 기준전압(BTINI\_REF)을 비교하여 BT\_INI[0]를 출력하고 마지막 비교기는 VC\_REF[m]과 초기 기준전압(BTINI\_REF)을 비교하여 BT\_INI[m]을 출력한다.

- [0054] 전압분배부(311)에서 생성된 초기 기준전압(BTINI\_REF)은 VDD/2+β이므로, 결국 초기값에 관한 정보는 VC\_REF[m:0]이 VDD/2+β보다 높은지 아닌지에 관한 정보가 된다. VC\_REF[m:0] 중 몇개의 전압이 VDD/2+β보다

높으냐에 따라서 초기 승압배율이 결정되는데, 표 2는 이를 나타내고 있다.

丑 2

[0055]

| BT_INI[m:0]                                        | 초기 승압배율 |

|----------------------------------------------------|---------|

| 2 <sup>m</sup>                                     | n       |

| 2 <sup>m</sup> +2 <sup>m-1</sup>                   | n-0.5   |

| 2 <sup>m</sup> +2 <sup>m-1</sup> +2 <sup>m-2</sup> | n-1     |

|                                                    |         |

| $2^{m}+2^{m-1}+2^{m-2}+\ldots+2$                   | 2       |

| $2^{m}+2^{m-1}+2^{m-2}+\ldots+2+1=2^{m+1}-1$       | 1.5     |

- [0056] 표 2를 보면, BT\_INI[m:0]이 2m+1-1(즉, BT\_INI[m:0]의 모든 값이 '하이')이 경우에 가장 낮은 승압배율(x1. 5)을 초기 승압배율로 가지고 BT\_INI[m:0]이 2m(즉, BT\_INI[m]만 '하이')인 경우에 가장 높은 승압배율(xn)을 초기 승압배율로 가지는 것을 확인할 수 있다.

- [0057] 도 8은 승압배율 제어부(313)의 일실시예 구성도이다.

- [0058] 승압배율 제어부(313)는 배율업 플래그 신호(BTUP\_FG)가 기준시간 이상 활성화되면 승압배율(BT[a:0])을 높이고, 배율다운 플래그 신호(BTUP\_FG)가 기준시간 이상 활성화되면 승압배율(BT[a:0])을 낮춘다.

- [0059] 숭압배율 제어부(313)는 카운터(801, 802), 비교기(803, 804), D플립플롭(805, 806), 초기값 디코더(807), 및 프리 셋터블(pre settable) 업/다운 카운터(808)를 포함한다. 숭압배율 제어부(313)를 구성하는 각 부분에 대한 자세한 설명은 후술한다.

- [0060] 도 9는 카운터(801, 802)의 동작을 설명하기 위한 도면이다.

- [0061] 카운터(801, 802)는 EN단자로 입력되는 신호(BTUP\_FG or BTDN\_FG)가 '하이'인 구간 동안에 클럭(CK)의 라이징 에지(rising edge)에서 OUT[b:0]단자로 출려되는 코드값(BTUP\_CNT[b:0] or BTDN\_CNT[b:0])을 1씩 증가시키는 동작을 한다. 또한, RST단자로 입력되는 신호(P\_ST)가 '하이'가 되면 OUT[b:0]단자로 출력되는 코드의 모든 비트를 0으로 초기화한다. 도 9를 참조하면, 카운터(801, 802)의 동작을 명확히 이해할 수 있다.

- [0062] 여기서, RST단자로 입력되는 신호는 주기신호(P\_ST)인데, 주기신호(P\_ST)는 승압배율 제어부(313)가 승압배율 (BT[a:0])을 변경시키는 1주기 동안에 한번 활성화되는 신호이다.

- [0063] 다시 도 8을 참조하면, 비교기(803)는 카운터(801)에서 출력된 BTUP\_CNT[b:0]값과 배율업 기준값(BTUP\_R[b:0])을 비교하여 BTUP\_CNT[b:0]의 값이 배율업 기준값(BTUP\_R[b:0])보다 큰 경우에는 BTUP\_PEN 신호를 '하이'로 출력하고, BTUP\_CNT[b:0]의 값이 배율업 기준값(BTUP\_R[b:0])보다 작은 경우에는 BTUP\_PEN 신호를 '로우'로 출력하다.

- [0064] 비교기(804)는 카운터(802)에서 출력된 BTDN\_CNT[b:0]값과 배율다운 기준값(BTDN\_R[b:0])을 비교하여 BTDN\_CNT[b:0]의 값이 배율다운 기준값(BTDN\_R[b:0])보다 큰 경우에는 BTDN\_PEN 신호를 '하이'로 출력하고, BTDN\_CNT[b:0]의 값이 배율다운 기준값(BTDN\_R[b:0])보다 작은 경우에는 BTDN\_PEN 신호를 '로우'로 출력한다.

- [0065] 배율업 기준값(BTUP\_R[b:0])과 배율다운 기준값(BTDN\_R[b:0])이 클수록 승압배율(BT[a:0])을 변경하기 위해 필요한 배율업 플래그 신호(BTUP\_FG)와 배율다운 플래그 신호(BTDN\_FG)의 활성화 시간은 길어진다.

- [0066] 초기값 디코더(807)는 초기값 결정부(314)에서 생성된 BT\_INI[m:0]의 포맷을 변경하는 부분이다. 하기의 표 3은 BT\_INI[m:0]과 D\_BT\_INI[a:0]의 관계 및 이들이 의미하는 초기 승압배율을 나타낸 표이다.

丑 3

[0067]

| BT_INI[m:0]                                        | D_BT_INI[a:0] | 초기 승압배율 |

|----------------------------------------------------|---------------|---------|

| 2 <sup>m</sup>                                     | 2n-3          | n       |

| 2 <sup>m</sup> +2 <sup>m-1</sup>                   | 2n-4          | n-0.5   |

| 2 <sup>m</sup> +2 <sup>m-1</sup> +2 <sup>m-2</sup> | 2n-5          | n-1     |

|                                                    |               |         |

| $2^{m}+2^{m-1}+2^{m-2}+\ldots+2$                   | 1             | 2       |

| $2^{m}+2^{m-1}+2^{m-2}+\ldots+2+1=2^{m+1}-1$       | 0             | 1.5     |

- [0068] 도 10은 프리 셋터블(pre settable) 업/다운 카운터(808)의 동작을 설명하기 위한 도면이다.

- [0069] 프리 셋터블 업/다운 카운터(808)는 UP단자에 입력되는 신호(BTUP\_EN)가 '하이'인 경우에는 CK단자 신호(P\_ST 신호의 반전신호)의 라이징 에지에서 OUT[a:0]단자의 코드(BT[a:0])값을 1씩 증가시키고 DN단자에 입력되는 신호(BTDN\_DN)가 '하이'인 경우에는 CK단자 신호의 라이징 에지에서 OUT[a:0]단자의 코드값(BT[a:0])을 1씩 감소시키는 동작을 한다.

- [0070] 또한, PEN 단자의 신호(DCC\_ST)가 '하이'가 되면 P[a:0]단자의 코드(D\_BT\_INI[a:0])가 그대로 OUT[a:0] 단자의 코드(BT[a:0])가 된다. 즉, PEN단자의 신호가 '하이'가 되면 승압배율이 D\_BTINI{a:0]의 값으로 초기화된다.

- [0071] 여기서 PEN단자로 입력되는 DCC ST신호는 승압전압 생성회로의 동작 개시시에 '하이'로 활성화되는 신호이다.

- [0072] 표 4에는 승압배율을 나타내는 코드(BT[a:0])와 승압배율과의 관계를 나타낸다.

丑 4

[0073]

| BT[a:0]      | 승압배율   |

|--------------|--------|

| 0            | x1.5   |

| 1            | x2     |

| 2            | x2.5   |

|              |        |

|              | xn-0.5 |

| 2n-4<br>2n-3 | xn     |

- [0074] 도 11~14은 승압배율 제어부(313)의 동작을 도시한 도면이다. 도 11은 승압배율 제어부(313)의 초기 동작을 나타내고, 도 12는 초기동작 이후에 승압배율 제어부(313)가 승압배율을 올리는 동작을 나타내고, 도 13은 초기동 작 이후에 승압배율 제어부(313)가 승압배율을 내리는 동작을 나타낸다. 또한, 도 14는 초기동작시 설정된 승압배율을 승압배율 제어부(313)가 계속 유지되는 동작을 나타낸다.

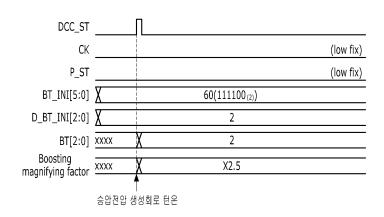

- [0075] 도 11을 참조하여, 승압배율 제어부(313)의 초기 동작을 살펴보기로 한다.

- [0076] 승압전압 생성회로의 동작이 개시된 이후에, DCC\_ST신호가 '하이'로 활성화된다. 그러면 프리 셋터블 업/다운 카운터(808)는 자신의 P[a:0] 단자로 입력된는 D\_BT\_INI[2:0]을 승압배율(BT[2:0])의 초기값으로 설정한다. 도 11을 보면, D\_BT\_INI[2:0]의 값이 2이며, 이에 따라 승압배율을 나타내는 코드(BT[2:0])의 값이 2가되고, 코드 (BT[2:0])값 2에 대응되는(표 4참조) 승압배율인 x2.5가 승압배율로 설정되는 것을 확인할 수 있다.

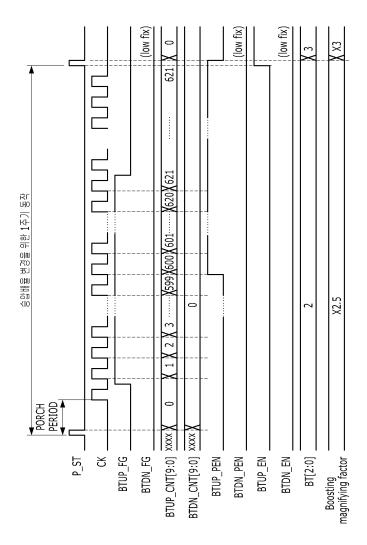

- [0077] 도 12는 도 11의 동작 이후에 승압배율이 높아지는 동작을 도시한다. 배율업 기준값(BTUP\_R[9:0])과 배율다운 기준값(BTDN\_R[9:0])은 600으로 설정된 것으로 가정한다.

- [0078] P\_ST 신호가 활성화된 이후에 안정화 구간(porch period)을 지나면 클릭(CK)이 토글하기 시작한다. 배율업 플래그 신호(BTUP\_FG)가 '하이'이므로 카운터(801)는 클릭(CK)을 카운팅하여 BTUP\_CNT[9:0]의 값을 늘려나간다. 증가하는 BTUP\_CNT[9:0]의 값이 배율다운 기준값(BTDN\_R[9:0]=600)에 도달하면 BTUP\_PEN신호가 '하이'로 활성화된다. '하이'로 활성화된 BTUP\_PEN신호에 의해 BTUP\_EN신호가 활성화되고, 다시 활성화되는 P\_ST신호에 응답하

여 프리 셋터블 업/다운 카운터(808)는 승압배율을 나타내는 코드값(BT[2:0])을 2에서 3으로 높인다. 따라서 승압배율이 x2.5에서 x3으로 높아진다.

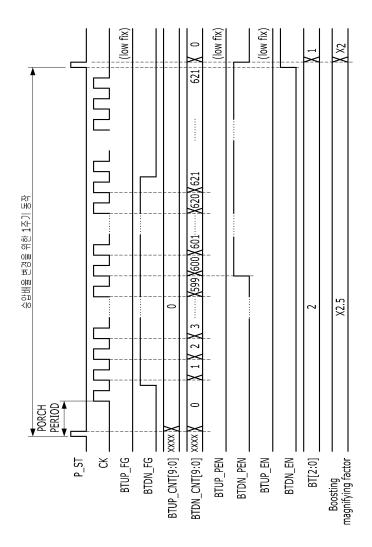

- [0079] 도 13은 도 11의 동작 이후에 승압배율이 낮아지는 동작을 도시한다. 배율업 기준값(BTUP\_R[9:0])과 배율다운 기준값(BTDN\_R[9:0])은 600으로 설정된 것으로 가정한다.

- [0080] P\_ST신호가 활성화된 이후에 안정화 구간(porch period)을 지나면 클럭(CK)이 토글하기 시작한다. 배율다운 플래그 신호(BTDN\_FG)가 '하이'이므로 카운터(802)는 클럭(CK)을 카운팅하여 BTDN\_CNT[9:0]의 값을 늘려나간다. 증가하는 BTDN\_CNT[9:0]의 값이 배율다운 기준값(BTDN\_R[9:0]=600)에 도달하면 BTDN\_PEN신호가 '하이'로 활성화된다. '하이'로 활성화된 BTDN\_PEN신호에 의해 BTDN\_EN신호가 활성화되고, 다시 활성화된는 P\_ST신호에 응답하여 프리 셋터블 업/다운 카운터(808)는 승압배율을 나타내는 코드값(BT[2:0])을 2에서 1로 낮춘다. 따라서 승압배율이 x2.5에서 x2로 낮아진다.

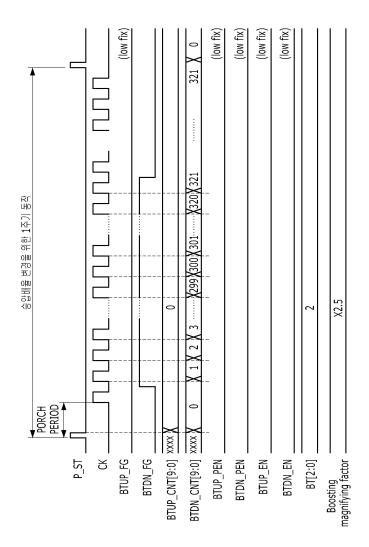

- [0081] 도 14는 도 11의 동작 이후에 승압배율이 변경되지 않는 동작을 도시한다. 배율업 기준값(BTUP\_R[9:0])과 배율 다운 기준값(BTDN[9:0])은 600으로 설정된 것으로 가정한다.

- [0082] P\_ST신호가 활성화된 이후에 안정화 구간(porch period)을 지나면 클럭(CK)이 토글하기 시작한다. 배율다운 플래그 신호(BTDN\_FG)가 '하이'이므로 카운터(802)는 클럭을 카운팅하여 BTDN\_CNT[9:0]의 값을 늘려나간다. BTDN\_CNT[9:0]의 값이 증가하던 중 배율다운 플래그 신호(BTDN\_FG)가 '로우'로 천이한다. 따라서 BTDN\_CNT[9:0]의 값은 321에서 더 이상 증가하지 못한다. BTDN\_CNT[9:0]의 값이 배율다운 기준값 (BTDN\_R[9:0]=600)에 도달하지 못하였으므로 BTUP\_PEN, BTUP\_EN신호는 활성화되지 못하고, 그 결과 프리 셋터블 업/다운 카운터(808)는 승압배율을 나타내는 코드(BT[2:0])값을 변경시키지 않는다. 따라서 승압배율은 계속 x2.5로 유지된다.

- [0083] 도 14의 경우 배율다운 플래그 신호(BTDN\_FG)가 활성화되는 시간이 기준시간(여기서는 600클럭)에 도달하지 못하므로 승압배율이 변경되지 않는다.

- [0084] 도 15는 로워 클램프 전압 선택부(325)의 구성도이다.

- [0085] 로워 클램프 전압 선택부(325)는 아날로그 먹스(1501)를 포함하여 구성되며, 승압배율(BT[a:0])에 응답하여 입력되는 전압들(VCMP\_DN[m:0]) 중 로워 클램프 전압(VCMP\_DNO)을 선택한다.

- [0086] 로워 클램프 전압(VCMP\_DNO)은 예비 입력전압(VCIN\_F)이 지나치게 낮아져서 로드 조건이나 승압배율(BT[a:0])이 변경되었을 때 예비 입력전압(VCIN\_F)이 목표값에 도달하는데 걸리는 시간이 증가하는 문제를 막기 위해, 전압 클램프부(326)로 입력되는 로워 클램프 전압(lower clamp voltage)이다.

- [0087] 로워 클램프 전압 선택부(325)로 입력되는 입력전압(VCMP\_DN[m:0])은 VCMP\_DN[m']=VC\_REF[m']- a(a는 50mV)가 되도록 생성하면 된다. 로워 클램프 전압 선택부(325)는 승압배율(BT[a:0])에 맞는 입력전압(VCMP\_DN[m:0])을 로워 클램프 전압(VCMP\_DNO)으로 선택한다.

- [0088] 도 16은 전압 클램프부(326)의 구성도이다.

- [0089] 전압 클램프부(326)는 어퍼 클램프부(1601)와 로워 클램프부(1602)를 포함하여 구성된다.

- [0090] 어퍼 클램프부(1601)는 예비 입력전압(VCIN\_F)이 어퍼 클램프 전압(VCMP\_UPO)보다 높아지면 예비 입력전압 (VCIN\_F)으로부터 접지단사이의 싱킹 전류(sinking current)를 발생시켜 예비 입력전압(VCIN\_F)이 어퍼 클램프 전압(VCMP\_UPO)보다 높아지는 것을 방지한다.

- [0091] 로워 클램프부(1602)는 예비 입력전압(VCIN\_F)이 로워 클램프 전압(VCMP\_DNO)보다 낮아지면 예비 입력전압 (VCIN\_F)으로부터 전원전압(VDD) 사이에 드라이빙 전류(driving current)를 발생시켜 예비 입력전압(VCIN\_F)이 로워 클램프 전압(VCMP\_DNO)보다 낮아지는 것을 방지한다.

- [0092] 도 17은 출력전압 분배부(321)의 구성도이다.

- [0093] 출력전압 분배부(321)는 출력전압(VOUT)을 전압분배하기 위한 직렬로 연결된 다수의 저항들과 아날로그 전압 먹 스(1701)를 포함하여 구성된다.

- [0094] 현재의 승압배율이 n'라고 하면, 출력전압 분배부(321)의 출력전압(VOUT\_F)의 레벨은 VOUT/2n'가 되어야 한다. 이는 증폭부의 증폭배율이 x2인 것을 가정한 것인데, 이를 보다 일반적으로 표현하면 VOUTF=VOUT/n'x(증폭부의 증폭배율)이 된다.

- [0095] VOUT/2n'를 m'에 관한 값으로 나타내면 VOUT/(m'+3)이 된다. 먹스(1701)는 승압배율(BT[a:0])에 따라 알맞은 출력전압(VOUT\_F)을 선택하도록 동작한다.

- [0096] 도 18은 보상회로(327)의 구성도이다.

- [0097] 보상회로(327)는 저항과 캐패시터를 포함하여 구성된다. 보상회로(327)는 예비 입력전압(VCIN\_F)을 생성하는 피드백 루프(feedback loop)의 안정성을 확보하기 위한 것으로 폴(pole) 및 제로(zero)를 루프상에 추가하여 안정성을 확보하게 해준다.

- [0098] 다시 도 3을 참조하면, 비교부(323)는 출력전압 분배부(321)의 출력전압(VOUT\_F)과 입력 기준전압 선택부(322)의 출력전압(VC\_REFO)을 비교해 예비 입력전압(VCIN\_F)을 생성한다.

- [0099] 출력전압 분배부(321)의 출력전압(VOUT\_F)이 입력 기준전압(VC\_REFO)보다 높을 경우에 비교부(323)는 예비 입력 전압(VCIN\_F)의 레벨을 낮춘다. 그리고 출력전압 분배부(321)의 출력전압(VOUT\_F)이 입력 기준전압(VC\_REFO)보다 낮을 경우에 비교부(323)는 예비 입력전압(VCIN\_F)의 레벨을 높인다.

- [0100] 출력전압 분배부(321)의 출력전압(VOUT\_F)이 입력 기준전압(VC\_REFO)보다 높은 경우에는, 예비 입력전압 (VCIN\_F)의 레벨이 낮아지므로 입력전압(VCIN)의 레벨도 낮아진다. 그리고 이는 출력전압(VOUT)에 반영되고, 그 결과 출력전압 분배부(321)의 출력전압(VOUTF)도 낮아지게 된다. 결국, 예비 입력전압(VCIN\_F)의 레벨은 입력 기준전압(VC\_REFO)에 근접해 나가게 된다.

- [0101] 출력전압 분배부(321)의 출력전압(VOUT\_F)이 입력 기준전압(VD\_REFO)보다 낮은 경우에는, 예비 입력전압 (VCIN\_F)의 레벨이 높아지므로 입력전압(VCIN)의 레벨도 높아진다. 그리고 이는 출력전압(VOUT)에 반영되고, 그 결과 출력전압 분배부(321)의 출력전압(VOUT\_F)도 높아지게 된다. 결국, 예비 입력전압(VCIN\_F)의 레벨은 입력 기준전압(VC\_REFO)에 근접해 나가게 된다.

- [0102] 도 3의 증폭부(324)는 리니어 레귤레이터(linear regulator)로서 비교기와 2개의 저항으로 구성된다. 증폭부 (324)는 예비 입력전압(VCIN\_F)을 2배로 증폭하여 입력전압(VCIN)을 생성한다. 물론, 증폭부(324)의 증폭배율을 2배가 아닌 다른 배율로 변경하는 것도 가능하다.

- [0103] 이제, 승압전압 생성회로의 전체 동작에 대해 알아보기로 한다.

- [0104] 입력전압 레벨 설정부(220)는 (출력전압의 목표전압/승압배율)의 레벨을 목표로 하여 입력전압(VCIN)을 생성한다. 즉, VCIN=VOUT, tar/n'이 되도록 입력전압(VCIN)의 레벨을 조절한다.

- [0105] 승압배율 설정부(210)는 입력전압(VCIN)의 목표 레벨(VOUT,tar/n')이 입력전압(VCIN)이 가질 수 없는 레벨(전원 전압을 초과하는 레벨)인 경우에 승압배율(BT[a:0])을 높인다. 그리고 승압배율(BT[a:0])이 한단계 낮아지더라도 입력전압(VCIN)의 목표 레벨이 입력전압(VCIN)이 가질 수 있는 레벨(전원전압보다 낮은 레벨)인 경우에는 승압배율(BT[a:0])을 낮춘다.

- [0106] 입력전압 레벨 설정부(220)와 승압배율 설정부(210)의 동작으로 인하여, 승압배율(BT[a:0])은 가능한 한 낮아지며, 입력전압(VCIN)은 가능한 한(전원전압의 레벨을 초과하지 않는 범위 내에서) 높아진다.

- [0107] 승압전압 생성회로는 승압배율(BT[a:0])이 높아질수록 소모 전류량이 크게 증가하는데, 본 발명은 승압배율 설정부(210)와 입력전압 레벨 설정부(220)의 동작을 통하여 승압배율(BT[a:0])을 가능한 한 낮추어, 승압전압 생

성회로의 전류소모를 줄이게 된다.

[0108] 본 발명의 기술사상은 상기 바람직한 실시예에 따라 구체적으로 기술되었으나, 상기한 실시옌는 그 설명을 위한 것이며 그 제한을 위한 것이 아님을 주의아여야 한다. 또한, 본 발명의 기술분야의 통상의 전문가라면 본 발명의 기술사상의 범위 내에서 다양한 실시예가 가능함을 알 수 있을 것이다.

### 부호의 설명

[0109]

200: 승압회로 210: 승압배율 설정부

220: 입력전압 레벨 설정부 311: 전압분배부

312 플래그신호 생성부 313: 승압배율 제어부

314: 초기값 결정부 321: 출력전압 분배부

322: 입력 기준전압 선택부 323: 비교부

324: 증폭부 325: 로워 클램프전압 선택부

326: 전압 클램프부 327: 보상회로

### 도면

### 도면1

## 도면5

### 도면10

## 도면17