(19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12)特 許 公 報(B2)

(11)特許番号

特許第4910576号 (P4910576)

(45) 発行日 平成24年4月4日(2012.4.4)

(24) 登録日 平成24年1月27日(2012.1.27)

HO4N 7/32 (2006.01)

HO4N 7/137

FL

Z

請求項の数 1 (全 21 頁)

(21) 出願番号 特願2006-238537 (P2006-238537) (22) 出願日 平成18年9月4日 (2006.9.4) (65) 公開番号 特開2008-61156 (P2008-61156A) 平成20年3月13日 (2008.3.13)

平成20年3月13日 (2008.3.13) 平成21年5月19日 (2009.5.19)

前置審査

審查請求日

||(73)特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

||(74)代理人 100092174

弁理士 平戸 哲夫

|(72)発明者 渡部 康弘

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 古市 徹

最終頁に続く

### (54) 【発明の名称】動画像処理装置

### (57)【特許請求の範囲】

### 【請求項1】

複数のデコード処理部又は複数のエンコード処理部を備える動画像処理装置であって、 前記複数のデコード処理部又は前記複数のエンコード処理部に共有されるプリフェッチ メモリを備え、

前記複数のデコード処理部又は前記複数のエンコード処理部は、

トップフィールドとボトムフィールドで構成される処理画面に対し、

参照画を全て共通とするトップフィールドとボトムフィールドについては、該トップフィールドと該ボトムフィールドを並行に処理し、

参照画を共通としない又は参照画の一部を共通とする<u>トップフィールド及びボトムフィールド</u>については、<u>該トップフィールド及び該ボトムフィールドの</u>処理画面内の上下に隣接するマクロブロックライン又はマクロブロックペアライン<u>を</u>並行<u>に</u>処理<u>する</u>こと

を特徴とする動画像処理装置。

### 【発明の詳細な説明】

#### 【技術分野】

### [0001]

本発明は、外部メモリが記憶する参照画の一部分をプリフェッチして記憶するためのプリフェッチメモリを備える動画像処理装置に関する。

#### 【背景技術】

[0002]

20

30

40

50

MPEG(Moving Picture Experts Group)などの動画像圧縮方式を用いたデコーダ又はエンコーダでは、外部メモリに参照画を格納しておき、復号過程又は符号化過程において外部メモリが記憶する参照画内の矩形領域を読み出す必要があるが、処理によっては、外部メモリ内の同一参照画領域に複数回の読み出しアクセスを行う必要があり、これが外部メモリとの間のデータ転送量増大の一因になっている。

#### [0003]

そこで、外部メモリ内の同一参照画領域に複数回の読み出しアクセスを行うことを避ける方法として、デコーダ又はエンコーダにプリフェッチメモリを搭載し、外部メモリが記憶する参照画の一部分を更新可能にプリフェッチメモリに記憶し、デコーダ又はエンコーダは、必要とする参照画像をプリフェッチメモリから読み出すという方法が考えられる。このようにすると、外部メモリとの間のデータ転送量を削減することができる。

[0004]

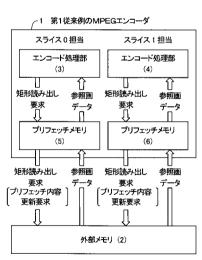

図11は第1従来例のMPEGエンコーダを外部メモリとともに示す図である。図11中、1は第1従来例のMPEGエンコーダであり、画像信号をMPEG方式で圧縮符号化してMPEGストリームを作成するものである。2はMPEGエンコーダ1が動きベクトル算出のために参照する参照画を記憶する外部メモリである。

[0005]

また、MPEGエンコーダ1において、3、4はMPEGストリームの作成に必要な演算処理を行うエンコード処理部であり、エンコード処理部3は画面の上半分のスライスを担当し、エンコード処理部4は画面の下半分のスライスを担当するものとされている。

[0006]

5 はエンコード処理部 3 に対応して設けられたプリフェッチメモリであり、外部メモリ 2 が記憶する参照画の上半分のスライスの一部分をプリフェッチして記憶するために使用 されるものである。 6 はエンコード処理部 4 に対応して設けられたプリフェッチメモリで あり、外部メモリ 2 が記憶する参照画の下半分のスライスの一部分をプリフェッチして記憶するために使用されるものである。

[0007]

第1従来例のMPEGエンコーダ1においては、エンコード処理部3は、動きベクトル算出のためにプリフェッチメモリ5が記憶する画像内の矩形領域を使用する場合には、プリフェッチメモリ5に対して矩形領域の読み出し要求(以下、矩形読み出し要求という場合がある。)を発行することになる。また、エンコード処理部4は、動きベクトル算出のためにプリフェッチメモリ6が記憶する画像内の矩形領域を使用する場合には、プリフェッチメモリ6に対して矩形読み出し要求を発行することになる。

[0008]

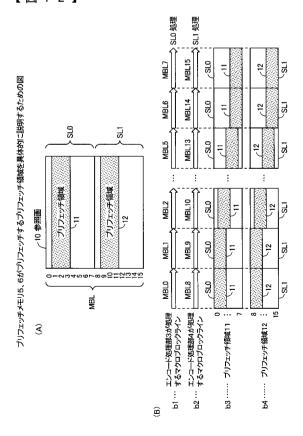

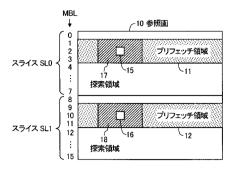

図12はプリフェッチメモリ5、6がプリフェッチするプリフェッチ領域を具体的に説明するための図であり、図12(A)はプリフェッチメモリ5、6が担当する参照画内の領域を示し、図12(B)はプリフェッチメモリ5、6がプリフェッチするプリフェッチ領域の遷移の様子を示している。

[0009]

図12中、10は外部メモリ2が記憶する参照画、MBL0~MBL15は参照画10のマクロブロックラインである。プリフェッチメモリ5は、参照画10のマクロブロックラインMBL0~MBL7までの8マクロブロックラインからなるスライスSL0を担当し、スライスSL0内の連続する3マクロブロックラインがプリフェッチ領域11とされる。

[0010]

また、プリフェッチメモリ 6 は、参照画 1 0 のマクロブロックラインM B L 8 ~ M B L 1 5 までの 8 マクロブロックラインからなるスライス S L 1 を担当し、スライス S L 1 内の連続する 3 マクロブロックラインをプリフェッチ領域 1 2 とされる。

[0011]

また、図12(B)において、(b1)は処理画面内のエンコード処理部3が処理する

20

30

40

50

マクロブロックラインの遷移、(b2)は処理画面内のエンコード処理部4が処理するマクロブロックラインの遷移、(b3)はプリフェッチメモリ5がスライスSL0からプリフェッチするプリフェッチ領域11の遷移、(b4)はプリフェッチメモリ6がスライスSL1からプリフェッチするプリフェッチ領域12の遷移を示している。

### [0012]

即ち、第1従来例のMPEGエンコーダ1においては、エンコード処理部3がマクロブロックラインMBL0を処理する場合には、エンコード処理部4はマクロブロックラインMBL8を処理する。この場合、プリフェッチメモリ5がプリフェッチするプリフェッチ領域11はマクロブロックラインMBL0~MBL2とされ、プリフェッチメモリ6がプリフェッチするプリフェッチ領域12はマクロブロックラインMBL8~MBL10とされる。

[0013]

次に、エンコード処理部 3 がマクロブロックライン M B L 1 を処理する場合には、エンコード処理部 4 はマクロブロックライン M B L 9 を処理する。この場合、プリフェッチメモリ 5 がプリフェッチするプリフェッチ領域 1 1 はマクロブロックライン M B L 0 ~ M B L 2 とされ、プリフェッチメモリ 6 がプリフェッチするプリフェッチ領域 1 2 はマクロブロックライン M B L 8 ~ M B L 1 0 とされる。

[ 0 0 1 4 ]

次に、エンコード処理部 3 がマクロブロックライン M B L 2 を処理する場合には、エンコード処理部 4 はマクロブロックライン M B L 1 0 を処理する。この場合、プリフェッチメモリ 5 がプリフェッチするプリフェッチ領域 1 1 は、1 マクロブロックライン分だけ下方向にシフトし、マクロブロックライン M B L 1 ~ M B L 3 とされる。また、プリフェッチメモリ 6 のプリフェッチ領域 1 2 は、1 マクロブロックライン分だけ下方向にシフトし、マクロブロックライン M B L 9 ~ M B L 1 1 とされる。

[0015]

その後、エンコード処理部3が1マクロブロックラインの処理を終了するごとに、プリフェッチメモリ5がプリフェッチするプリフェッチ領域11は、1マクロブロックライン分だけ下方向にシフトする。また、エンコード処理部4が1マクロブロックラインの処理を終了するごとに、プリフェッチメモリ6がプリフェッチするプリフェッチ領域12は、1マクロブロックライン分だけ下方向にシフトする。

[0016]

そして、エンコード処理部 3 がマクロブロックラインMBL 5 を処理する場合には、エンコード処理部 4 はマクロブロックラインMBL 1 3 を処理する。この場合、プリフェッチメモリ 5 がプリフェッチするプリフェッチ領域 1 1 は、マクロブロックラインMBL 4 ~ MBL 6 とされ、プリフェッチメモリ 6 がプリフェッチするプリフェッチ領域 1 2 は、マクロブロックラインMBL 1 2 ~ MBL 1 4 とされる。

[0017]

次に、エンコード処理部 3 がマクロブロックライン M B L 6 を処理する場合には、エンコード処理部 4 はマクロブロックライン M B L 1 4 を処理する。この場合、プリフェッチメモリ 5 がプリフェッチするプリフェッチ領域 1 1 は、マクロブロックライン M B L 5 ~ M B L 7 とされ、プリフェッチメモリ 6 がプリフェッチするプリフェッチ領域 1 2 は、マクロブロックライン M B L 1 3 ~ M B L 1 5 とされる。

[0018]

次に、エンコード処理部 3 がマクロブロックライン M B L 7 を処理する場合には、エンコード処理部 4 はマクロブロックライン M B L 1 5 を処理する。この場合、プリフェッチメモリ 5 がプリフェッチするプリフェッチ領域 1 1 は、マクロブロックライン M B L 5 ~ M B L 7 とされ、プリフェッチメモリ 6 がプリフェッチするプリフェッチ領域 1 2 は、マクロブロックライン M B L 1 3 ~ M B L 1 5 とされる。

[0019]

図13はプリフェッチメモリ5、6にプリフェッチされることが望ましい参照画10内

20

30

40

50

のプリフェッチ領域を説明するための図である。図13中、15はエンコード処理部3が現在処理しているマクロブロックと同じ位置の参照画10内のマクロブロック、16はエンコード処理部4が現在処理しているマクロブロックと同じ位置の参照画10内のマクロブロックを示している。

### [0020]

ここで、エンコード処理部 3 、 4 で行われる動きベクトル算出は、ブロックマッチング法により行われるのが一般的である。ブロックマッチング法は、参照画内の探索領域中から、処理マクロブロックと最も近い画像を探す方法であり、図 1 3 中、 1 7 はエンコード処理部 3 がマクロブロック 1 5 と同じ位置の処理画面内のマクロブロックを処理する場合に探索する探索領域、 1 8 はエンコード処理部 4 がマクロブロック 1 6 と同じ位置の処理画面内のマクロブロックを探索する探索領域を示している。

[0021]

プロックマッチング処理を行うためには、エンコード処理部3は、探索領域17の画像データを読み出す必要があるので、エンコード処理部3用のプリフェッチメモリ5がプリフェッチするプリフェッチ領域11には探索領域17の全てが含まれていることが望ましいし、また、エンコード処理部4は、探索領域18の画像データを読み出す必要があるので、エンコード処理部4用のプリフェッチメモリ6がプリフェッチするプリフェッチ領域12には探索領域18の全てが含まれていることが望ましい。

[0022]

図14は第2従来例のMPEGエンコーダを外部メモリとともに示す図である。図14中、20は第2従来例のMPEGエンコーダ、21、22はMPEGエンコーダ20が動きベクトル算出のために参照する参照画を格納するための外部メモリであり、外部メモリ21には参照画の偶数ラインが割り当てられる。

[0023]

また、MPEGエンコーダ20において、23はMPEGストリームの作成に必要な演算処理を行うエンコード処理部、24は外部メモリ21が記憶する参照画の偶数ラインの一部分をプリフェッチして記憶するためのプリフェッチメモリ、25は外部メモリ22が記憶する参照画の奇数ラインの一部分をプリフェッチして記憶するためのプリフェッチメモリである。

[0024]

第2従来例のMPEGエンコーダ20においては、エンコード処理部23は、動きベクトル算出のために必要とする参照画内の矩形領域のうち、プリフェッチメモリ24が記憶する奇数ライン部分については、プリフェッチメモリ24に矩形読み出し要求を発行し、プリフェッチメモリ25が記憶する偶数ライン部分については、プリフェッチメモリ25に矩形読み出し要求を発行することになる。

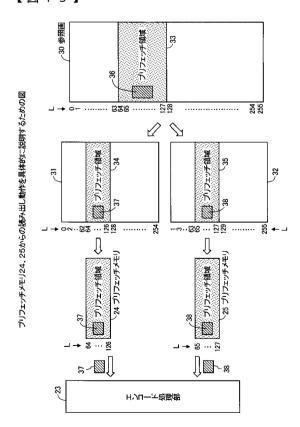

[0025]

図15は第2従来例のMPEGエンコーダ20におけるプリフェッチメモリ24、25からの読み出し動作を具体的に説明するための図である。図15中、30は参照画であり、31は参照画30内の偶数ラインL0、L2、…、L254部分の参照画、32は参照画30内の奇数ラインL1、L3、…、L255部分の参照画であり、参照画31は外部メモリ21に格納され、参照画32は外部メモリ22に格納される。

[0026]

この例では、参照画30内のラインL64~L127がプリフェッチ領域33とされ、プリフェッチ領域33内の偶数ラインL64、L66、...、L126の部分は、プリフェッチ領域34としてプリフェッチメモリ24にプリフェッチされ、プリフェッチ領域33 内の奇数ラインL65、L67、...、L127の部分は、プリフェッチ領域35としてプリフェッチメモリ25にプリフェッチされる。

[0027]

ここで、エンコード処理部23が参照画30内の矩形領域36を必要とする場合には、

エンコード処理部 2 3 は、矩形領域 3 6 内の偶数ライン部分 3 7 については、プリフェッチメモリ 2 4 に矩形読み出し要求を発行し、矩形領域 3 6 内の奇数ライン部分 3 8 については、プリフェッチメモリ 2 5 に矩形読み出し要求を発行することになる。

#### [0028]

この結果、矩形領域36内の偶数ライン部分37の画像データについては、プリフェッチメモリ24から読み出されてエンコード処理部23に転送され、矩形領域36内の奇数ライン部分38の画像データについては、プリフェッチメモリ25から読み出されてエンコード処理部23に転送される。

【特許文献1】特開2005-102144号公報

【特許文献2】特開2006-31480号公報

【発明の開示】

【発明が解決しようとする課題】

[0029]

[0030]

また、第2従来例のMPEGエンコーダ20においては、外部メモリ21、22に対応させてプリフェッチメモリ24、25を設け、プリフェッチメモリ24には参照画30内のプリフェッチ領域内の偶数ラインの一部分を記憶し、プリフェッチメモリ25には参照画30内のプリフェッチ領域内の奇数ラインの一部分を記憶するようにしているので、エンコード処理部23は、プリフェッチメモリ24、25に対して別々に矩形読み出し要求を発行しなければならず、画像データ読み出し効率が悪いという問題点があった。

[0031]

本発明は、かかる点に鑑み、外部メモリとプリフェッチメモリとの間のデータ転送量の 削減を図ることができるようにした動画像処理装置を提供することを第1の目的とし、プ リフェッチメモリからの画像データ読み出しの効率化を図ることができるようにした動画 像処理装置を提供することを第2の目的とする。

【課題を解決するための手段】

[0032]

本発明中、第1発明は、複数のデコード処理部又は複数のエンコード処理部を備える動画像処理装置であって、前記複数のデコード処理部又は前記複数のエンコード処理部に共有されるプリフェッチメモリを備えるというものである。

[0033]

本発明中、第2発明は、デコード処理部又はエンコード処理部を備え、参照画を分割して格納する複数の外部メモリを使用する動画像処理装置であって、前記参照画の一部分をプリフェッチして記憶するプリフェッチメモリとして前記複数の外部メモリに共有されるプリフェッチメモリを備えるものである。

【発明の効果】

[0034]

本発明中、第1発明においては、複数のデコード処理部又は複数のエンコード処理部に 共有されるプリフェッチメモリを備えるとしているが、この場合、複数のデコード処理部 又は複数のエンコード処理部に、例えば、処理画面内の上下に隣接するマクロブロックラ イン又はマクロブロックペアラインを並行処理させることができる。

[0035]

このようにする場合には、複数のデコード処理部の各々の参照領域の縦サイズ又は複数

10

20

30

50

20

30

40

50

のエンコード処理部の各々の探索領域の縦サイズを従来のように複数のデコード処理部の各々又は複数のエンコード処理部の各々に対応させて複数のプリフェッチメモリを設ける場合と同様にしても、参照領域又は探索領域の縦サイズを従来のように複数のプリフェッチメモリを設けるようにした場合の参照領域又は探索領域の合計縦サイズよりも小さくすることができる。

#### [0036]

したがって、プリフェッチメモリにプリフェッチさせるプリフェッチ領域の縦サイズを従来のように複数のプリフェッチメモリを設けるようにした場合のプリフェッチ領域の合計縦サイズよりも小さくすることができ、プリフェッチメモリに要求される記憶容量を従来のように複数のプリフェッチメモリを設けるようにした場合の合計記憶容量よりも小さくすることができる。

[0037]

また、複数のデコード処理部又は複数のエンコード処理部に、例えば、参照画を共通とする所定の複数処理画面を並行処理させることもできる。このようにする場合には、所定の複数処理画面が必要とする共通の参照画の一部分を別々にプリフェッチする必要はなく、外部メモリとプリフェッチメモリとの間のデータ転送量を削減することができる。

[0038]

本発明中、第2発明においては、参照画を分割して格納する複数の外部メモリを使用する場合であっても、プリフェッチメモリとして複数の外部メモリで共有されるプリフェッチメモリを備えるとしているので、デコード処理部又はエンコード処理部は、従来例のように複数のプリフェッチメモリに対して別々に矩形読み出し要求を発行する必要はなく、共有されるプリフェッチメモリに対して矩形読み出し要求を発行すれば足りる。したがって、プリフェッチメモリからの画像データ読み出しの効率化を図ることができる。

【発明を実施するための最良の形態】

[0039]

(第1発明の動画像処理装置の一実施形態)

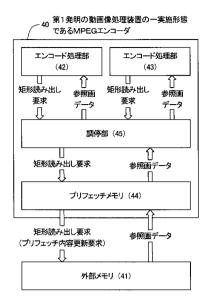

図1は第1発明の動画像処理装置の一実施形態であるMPEGエンコーダを外部メモリとともに示す図である。図1中、40は第1発明の動画像処理装置の一実施形態であるMPEGエンコーダであり、画像信号をMPEG方式で圧縮符号化してMPEGストリームを作成するものである。41はMPEGエンコーダ40が動きベクトル算出のために参照する参照画を格納するための外部メモリである。

[0040]

また、MPEGエンコーダ40において、42、43はMPEGストリームの作成に必要な演算処理を行うエンコード処理部である。これらエンコード処理部42、43は、上下に隣接したマクロブロックラインを並列処理するか、又は、参照画を共通とする複数の画面を並列処理するか、又は、上下に隣接したマクロブロックラインの並列処理と、参照画を共通とする複数の画面の並列処理とを切り替えて行うものである。

[0041]

また、44は外部メモリ41が記憶する参照画の一部分をプリフェッチして記憶するプリフェッチメモリ、45はエンコード処理部42が発行したプリフェッチメモリ44への矩形読み出し要求の転送とエンコード処理部43が発行したプリフェッチメモリ44への矩形読み出し要求の転送を調停する調停部である。

[0042]

エンコード処理部 4 2 、 4 3 は、プリフェッチメモリ 4 4 が記憶する画像内の矩形領域を参照画像として使用する場合には、それぞれ、矩形読み出し要求を調停部 4 5 に対して発行することになる。この矩形読み出し要求には、読み出し対象の矩形領域の位置情報及びサイズ情報などが含まれる。

[0043]

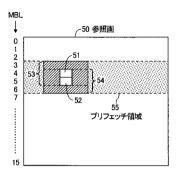

図 2 はエンコード処理部 4 2 、 4 3 が上下に隣接したマクロブロックラインを並列処理 する場合にプリフェッチメモリ 4 4 にプリフェッチされることが望ましい参照画内のプリ フェッチ領域を説明するための図である。図2中、50は外部メモリ41が記憶する参照画、51はエンコード処理部42が現在処理しているマクロブロックと同じ位置の参照画50内のマクロブロック、52はエンコード処理部43が現在処理しているマクロブロックと同じ位置の参照画50内のマクロブロックを示している。

#### [0044]

また、53はエンコード処理部42がマクロブロック51と同じ位置の処理画面内のマクロブロックについてのブロックマッチング処理のために探索する探索領域、54はエンコード処理部43がマクロブロック52と同じ位置の処理画面内のマクロブロックについてのブロックマッチング処理のために探索する探索領域を示している。

#### [0045]

ここで、エンコード処理部42、43による探索領域53、54の縦サイズを、図13に示すように、第1従来例のMPEGエンコーダ1が備えるエンコード処理部3、4の場合と同様に3マクロブロック分とすると、エンコード処理部42、43は、上下に隣接したマクロブロックラインを並行処理するので、エンコード処理部42、43が探索する探索領域53、54は、縦サイズを4マクロブロック分とする領域に含まれることになる。【0046】

そこで、例えば、エンコード処理部42がマクロブロックラインMBL4を処理し、エンコード処理部43がマクロブロックラインMBL5を処理する場合には、エンコード処理部42の探索領域53の縦領域はマクロブロックラインMBL3~MBL5部分であり、エンコード処理部43の探索領域54の縦領域はマクロブロックラインMBL4~MBL6部分である。したがって、この場合には、プリフェッチメモリ44がプリフェッチすべきプリフェッチ領域55は、マクロブロックラインMBL3~MBL6の4マクロブロックラインということになる。

#### [0047]

即ち、エンコード処理部42、43が上下に隣接したマクロブロックラインを並列処理する場合には、エンコード処理部42、43の探索領域53、54の縦サイズがそれぞれ3マクロブロックライン分であっても、プリフェッチメモリ44がプリフェッチすべきプリフェッチ領域55の縦サイズは、エンコード処理部42、43の探索領域53、54の縦サイズの2倍である6マクロブロックライン分ではなく、「エンコード処理部42、43の探索領域53、54の縦サイズの2倍・」である4マクロブロックライン分で足りる。

### [0048]

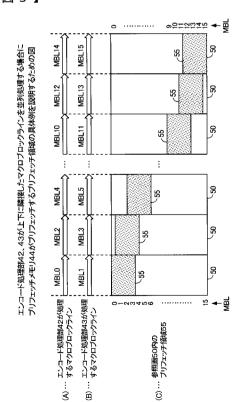

図3はエンコード処理部42、43が上下に隣接したマクロブロックラインを並列処理する場合にプリフェッチメモリ44がプリフェッチするプリフェッチ領域の具体例を説明するための図であり、図3(A)はエンコード処理部42が処理するマクロブロックラインの遷移、図3(B)はエンコード処理部43が処理するマクロブロックラインの遷移、図3(C)はプリフェッチメモリ44がプリフェッチする参照画50内のプリフェッチ領域55の遷移を示している。

### [0049]

即ち、エンコード処理部42、43が上下に隣接したマクロブロックラインを並列処理する場合においては、図3(A)に示すように、エンコード処理部42がマクロブロックラインMBL1を処理する場合には、プリフェッチメモリ44がプリフェッチするプリフェッチ領域55は、例えば、マクロブロックラインMBL0~MBL3とされる。

#### [0050]

次に、エンコード処理部 4 2 がマクロブロックラインMBL2を処理し、エンコード処理部 4 3 がマクロブロックラインMBL3を処理する場合には、プリフェッチメモリ 4 4 がプリフェッチするプリフェッチ領域 5 5 は、例えば、マクロブロックラインMBL1 ~ MBL4 とされる。

### [0051]

10

20

30

次に、エンコード処理部 4 2 がマクロブロックラインMBL 4 を処理し、エンコード処理部 4 3 がマクロブロックラインMBL 5 を処理する場合には、プリフェッチメモリ 4 4 がプリフェッチするプリフェッチ領域 5 5 は、例えば、マクロブロックラインMBL 3 ~ MBL 6 とされる。

### [0052]

その後、エンコード処理部42、43が1マクロブロックラインの処理を終了するごとに、プリフェッチメモリ44がプリフェッチするプリフェッチ領域55は、2マクロブロックライン分だけ下方向にシフトする。そして、エンコード処理部42がマクロブロックラインMBL10を処理し、エンコード処理部43がマクロブロックラインMBL11を処理する場合には、プリフェッチメモリ44がプリフェッチするプリフェッチ領域55は、例えば、マクロブロックラインMBL9~MBL12とされる。

[0053]

次に、エンコード処理部42がマクロブロックラインMBL12を処理し、エンコード 処理部43がマクロブロックラインMBL13を処理する場合には、プリフェッチメモリ 44がプリフェッチするプリフェッチ領域55は、例えば、マクロブロックラインMBL 11~MBL14とされる。

[0054]

次に、エンコード処理部42がマクロブロックラインMBL14を処理し、エンコード処理部43がマクロブロックラインMBL15を処理する場合には、プリフェッチメモリ44がプリフェッチするプリフェッチ領域55は、例えば、マクロブロックラインMBL12~MBL15とされる。

[0055]

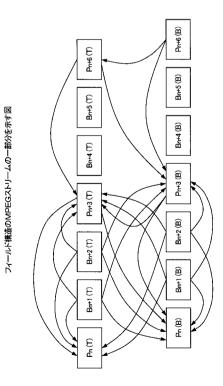

図 4 はフィールド構造の M P E G ストリームの一部分を示す図である。フィールド構造の画像信号を符号化する場合において、Pフィールド画面を符号化する場合には、必要とする参照画は 2 枚である。例えば、P<sub>n+3</sub>トップフィールド画面を符号化する場合には、P<sub>n</sub>トップフィールド及び P<sub>n</sub>ボトムフィールドの復号画面が参照され、P<sub>n+3</sub>ボトムフィールド画面を符号化する場合には、P<sub>n+3</sub>トップフィールド及び P<sub>n</sub>ボトムフィールドの復号画面が参照される。なお、図 4 及び図 5 では、トップを(T)、ボトムを(B)で示している。

[0056]

また、 $P_{n+6}$ トップフィールド画面を符号化する場合には、 $P_{n+3}$ トップフィールド及び $P_{n+3}$ ボトムフィールドの復号画面が参照され、 $P_{n+6}$ ボトムフィールド画面を符号化する場合には、 $P_{n+6}$ トップフィールド及び $P_{n+3}$ ボトムフィールドの復号画面が参照される。

[0057]

これに対して、 B フィールド画面を符号化する場合には、必要とする参照画は 4 枚である。例えば、 B  $_{n+1}$ トップフィールド画面、 B  $_{n+1}$ ボトムフィールド画面、 B  $_{n+2}$ トップフィールド画面及び B  $_{n+2}$ ボトムフィールド画面を符号化する場合には、 P  $_{n+3}$ トップフィールド、 P  $_n$ トップフィールド、 P  $_n$ トップフィールド、 Q び P  $_n$ ボトムフィールドの復号画面が参照される。

[0058]

図 5 は図 4 に示す  $P_{n+3}$ トップ / ボトム、  $B_{n+1}$ トップ / ボトム、  $B_{n+2}$ トップ / ボトム 及び  $P_{n+6}$ トップ / ボトムの各フィールド画面を符号化する場合に適用して好適な処理領域のエンコード処理部 4 2 、 4 3 への第 1 の割り当て方法及びプリフェッチメモリ 4 4 にプリフェッチさせるプリフェッチ領域を示す図である。この第 1 の割り当て方法は、エンコード処理部 4 2 、 4 3 は、画面によらず、上下に隣接したマクロブロックラインを並列処理する場合である。

[0059]

即ち、第1の割り当て方法では、エンコード処理部42には、 $P_{n+3}$ トップフィールド画面、 $P_{n+3}$ ボトムフィールド画面、 $B_{n+1}$ トップフィールド画面、 $B_{n+2}$ トップフィールド画面、 $B_{n+2}$ ボトムフィールド画面、 $B_{n+2}$ ボトムフィールド画面、 $B_{n+2}$ ボトムフィールド画面、 $B_{n+2}$ ボトムフィールド画面、 $B_{n+3}$

10

20

30

40

ルド画面及び P<sub>n+6</sub>ボトムフィールド画面の各偶数マクロブロックラインが割り当てられる。

### [0060]

また、エンコード処理部 4 3 には、 $P_{n+3}$ トップフィールド画面、 $P_{n+3}$ ボトムフィールド画面、 $B_{n+1}$ トップフィールド画面、 $B_{n+2}$ トップフィールド画面、 $B_{n+2}$ ボトムフィールド画面、 $P_{n+6}$ トップフィールド画面及び $P_{n+6}$ ボトムフィールド画面の各奇数マクロブロックラインが割り当てられる。

### [0061]

そして、エンコード処理部42によるP<sub>n+3</sub>トップフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部43によるP<sub>n+3</sub>トップフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ44にはP<sub>n</sub>トップフィールド及びP<sub>n</sub>ボトムフィールドの各復号画面の一部分が記憶される。

### [0062]

次に、エンコード処理部42による P<sub>n+3</sub>ボトムフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部43による P<sub>n+3</sub>ボトムフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ44には P<sub>n+3</sub>トップフィールド及び P<sub>n</sub>ボトムフィールドの各復号画面の一部分が記憶される。

### [0063]

次に、エンコード処理部 4 2 による  $B_{n+1}$  トップフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部 4 3 による  $B_{n+1}$  トップフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4 4 には  $P_n$  トップフィールド、  $P_n$  ボトムフィールド、  $P_{n+3}$  トップフィールド及び  $P_{n+3}$  ボトムフィールドの各復号画面の一部分が記憶される。

#### [0064]

次に、エンコード処理部 4 2 による  $B_{n+1}$  ボトムフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部 4 3 による  $B_{n+1}$  ボトムフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4 4 には  $P_n$ トップフィールド、  $P_n$ ボトムフィールド、  $P_{n+3}$ ドップフィールド及び  $P_{n+3}$ ボトムフィールドの各復号画面の一部分が記憶される。

### [0065]

次に、エンコード処理部 4 2 による  $B_{n+2}$  トップフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部 4 3 による  $B_{n+2}$  トップフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4 4 には  $P_n$  トップフィールド、  $P_n$  ボトムフィールド、  $P_{n+3}$  トップフィールド及び  $P_{n+3}$  ボトムフィールドの各復号画面の一部分が記憶される。

#### [0066]

次に、エンコード処理部 4 2 による  $B_{n+2}$ ボトムフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部 4 3 による  $B_{n+2}$ ボトムフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4 4 には  $P_n$ トップフィールド、 $P_n$ ボトムフィールド、 $P_{n+3}$ トップフィールド及び $P_{n+3}$ ボトムフィールドの各復号画面の一部分が記憶される。

## [0067]

次に、エンコード処理部42による P<sub>n+6</sub> トップフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部43による P<sub>n+6</sub> トップフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ44には P<sub>n+3</sub> トップフィールド及び P<sub>n+3</sub> ボトムフィールドの各復号画面の一部分が記憶される。

### [0068]

50

10

20

30

20

30

40

次に、エンコード処理部 4 2 による  $P_{n+6}$ ボトムフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部 4 3 による  $P_{n+6}$ ボトムフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4 4 には  $P_{n+6}$ トップフィールド及び  $P_{n+3}$ ボトムフィールドの各復号画面の一部分が記憶される。

### [0069]

図6は図4に示すB<sub>n+1</sub>トップ / ボトムの各フィールドを図5に示す第1の割り当て方法を使用して符号化する場合におけるエンコード処理部42、43の処理領域の遷移とプリフェッチメモリ44がプリフェッチするプリフェッチ領域の遷移を示す図である。

### [0070]

図6(A)はエンコード処理部42が処理するマクロブロックラインの遷移、図6(B)はエンコード処理部43が処理するマクロブロックラインの遷移、図6(C)はプリフェッチメモリ44がプリフェッチするP<sub>n</sub>トップフィールド参照画のプリフェッチ領域の遷移、図6(D)はプリフェッチメモリ44がプリフェッチするP<sub>n</sub>ボトムフィールド参照画のプリフェッチ領域の遷移を示している。

#### [0071]

なお、 6~0 は  $P_n$  トップフィールド参照画、 6~1 はプリフェッチメモリ 4~4 がプリフェッチする  $P_n$  トップフィールド参照画 6~0 内のプリフェッチ領域、 6~2 は  $P_n$  ボトムフィールド参照画、 6~3 はプリフェッチメモリ 4~4 がプリフェッチする  $P_n$  ボトムフィールド参照画 6~2 内のプリフェッチ領域である。

#### [0072]

また、図 6 では、プリフェッチメモリ 4 4 がプリフェッチする  $P_{n+3}$  トップフィールド 参照画のプリフェッチ領域の遷移及び  $P_{n+3}$  ボトムフィールド参照画のプリフェッチ領域 の遷移は、図示を省略しているが、それぞれ図 6 ( C ) 及び図 6 ( D ) に示す場合と同様 である。

#### [0073]

図 7 は図 4 に示す  $P_{n+3}$ トップ / ボトム、  $B_{n+1}$ トップ / ボトム、  $B_{n+2}$ トップ / ボトム 及び  $P_{n+6}$ トップ / ボトムの各フィールド画面を符号化する場合に適用して好適な処理領域のエンコード処理部  $4\ 2\$ 、  $4\ 3\$ への第  $2\$ の割り当て方法及びプリフェッチメモリ  $4\ 4$  にプリフェッチさせるプリフェッチ領域を示す図である。

### [0074]

この第2の割り当て方法は、エンコード処理部42、43に、上下に隣接したマクロブロックラインの並列処理と、参照画を共通とする複数の画面の並列処理とを切り替えて行わせるというものであり、具体的には、 $P_{n+3}$ トップ / ボトム及び $P_{n+6}$ トップ / ボトムの各フィールド画面を符号化する場合には、エンコード処理部42、43に上下に隣接したマクロブロックラインの並列処理を行わせ、 $B_{n+1}$ トップ / ボトム及び $B_{n+2}$ トップ / ボトムの各フィールド画面を符号化する場合には、エンコード処理部42、43にトップフィールド画面とボトムフィールド画面の並列処理を行わせるというものである。

### [0075]

即ち、第2の割り当て方法では、エンコード処理部42には、 $P_{n+3}$ トップフィールド画面の偶数マクロブロックライン、 $P_{n+3}$ ボトムフィールド画面の偶数マクロブロックライン、 $B_{n+1}$ トップフィールド画面、 $B_{n+2}$ トップフィールド画面、 $P_{n+6}$ トップフィールド画面の偶数マクロブロックライン及び $P_{n+6}$ ボトムフィールド画面の偶数マクロブロックラインが割り当てられる。

#### [0076]

また、エンコード処理部 4 3 には、 $P_{n+3}$ トップフィールド画面の奇数マクロブロックライン、 $P_{n+3}$ ボトムフィールド画面の奇数マクロブロックライン、 $B_{n+1}$ ボトムフィールド画面、 $P_{n+6}$ トップフィールド画面の奇数マクロブロックライン及び $P_{n+6}$ ボトムフィールド画面の奇数マクロブロックラインが割り当てられる。

### [0077]

そして、エンコード処理部42によるP<sub>n+3</sub>トップフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部43によるP<sub>n+3</sub>トップフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ44にはP<sub>n</sub>トップフィールド及びP<sub>n</sub>ボトムフィールドの各復号画面の一部分が記憶される。

### [0078]

次に、エンコード処理部42による P<sub>n+3</sub> ボトムフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部43による P<sub>n+3</sub> ボトムフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ44には P<sub>n+3</sub>トップフィールド及び P<sub>n</sub> ボトムフィールドの各復号画面の一部分が記憶される。

#### [0079]

次に、エンコード処理部 4 2 による  $B_{n+1}$  トップフィールド画面の符号化処理と、エンコード処理部 4 3 による  $B_{n+1}$  ボトムフィールド画面の符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4 4 には  $P_n$  トップフィールド、  $P_n$  ボトムフィールド、  $P_{n+3}$  トップフィールド及び  $P_{n+3}$  ボトムフィールドの各復号画面の一部分が記憶される

### [0800]

次に、エンコード処理部 4~2 による  $B_{n+2}$  トップフィールド画面の符号化処理と、エンコード処理部 4~3 による  $B_{n+2}$  ボトムフィールド画面の符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4~4 には  $P_n$  トップフィールド、  $P_n$  ボトムフィールド、  $P_{n+3}$  トップフィールド及び  $P_{n+3}$  ボトムフィールドの各復号画面の一部分が記憶される

### [0081]

次に、エンコード処理部 4 2 による  $P_{n+6}$  トップフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部 4 3 による  $P_{n+6}$  トップフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4 4 には  $P_{n+3}$  トップフィールド及び  $P_{n+3}$  ボトムフィールドの各復号画面の一部分が記憶される。

### [0082]

次に、エンコード処理部 4 2 による  $P_{n+6}$  ボトムフィールド画面の偶数マクロブロックラインの符号化処理と、エンコード処理部 4 3 による  $P_{n+6}$  ボトムフィールド画面の奇数マクロブロックラインの符号化処理とが並行して実行される。この場合、プリフェッチメモリ 4 4 には  $P_{n+6}$ トップフィールド及び  $P_{n+3}$  ボトムフィールドの各復号画面の一部分が記憶される。

### [0083]

図8は図4に示すB<sub>n+1</sub>トップ / ボトムの各フィールドを図7に示す第2の割り当て方法を使用して符号化する場合におけるエンコード処理部42、43の処理領域の遷移とプリフェッチメモリ44がプリフェッチするプリフェッチ領域の遷移を示す図である。

#### [0084]

図 8 ( A ) はエンコード処理部 4 2 が処理するマクロブロックラインの遷移、図 8 ( B ) はエンコード処理部 4 3 が処理するマクロブロックラインの遷移、図 8 ( C ) はプリフェッチメモリ 4 4 がプリフェッチする  $P_n$ トップフィールド参照画のプリフェッチ領域の遷移、図 8 ( D ) はプリフェッチメモリ 4 4 がプリフェッチする  $P_n$ ボトムフィールド参照画のプリフェッチ領域の遷移を示している。

### [0085]

なお、 6.5 は  $P_n$ トップフィールド参照画、 6.6 はプリフェッチメモリ 4.4 がプリフェッチする  $P_n$ トップフィールド参照画 6.5 内のプリフェッチ領域、 6.7 は  $P_n$ ボトムフィールド参照画、 6.8 はプリフェッチメモリ 4.4 がプリフェッチする  $P_n$ ボトムフィールド参照画 6.7 内のプリフェッチ領域である。

10

20

30

40

#### [0086]

また、図 8 では、プリフェッチメモリ 4 4 がプリフェッチする  $P_{n+3}$  トップフィールド 参照画のプリフェッチ領域の遷移及び  $P_{n+3}$  ボトムフィールド参照画のプリフェッチ領域 の遷移は、図示を省略しているが、それぞれ図 8 ( C ) 及び図 8 ( D ) に示す場合と同様 である。

### [0087]

ここで、図 5 に示す処理領域のエンコード処理部 4 2 、 4 3 への第 1 の割り当て方法の場合には、 $B_{n+1}$ トップフィールド画面と $B_{n+1}$ ボトムフィールド画面を符号化処理する場合、これらの符号化処理を並行して実行していないので、 $B_{n+1}$ トップフィールド画面を符号化処理する場合と $B_{n+1}$ ボトムフィールド画面を符号化処理する場合のそれぞれの場合にプリフェッチが必要であり、合計 2 回のプリフェッチが必要である。 $B_{n+2}$ トップフィールド画面及び  $B_{n+2}$ ボトムフィールド画面を符号化する場合も同様である。

### [0088]

これに対して、図 7 に示す処理領域のエンコード処理部 4 2 、 4 3 への第 2 の割り当て方法の場合には、 $B_{n+1}$ トップフィールド画面の符号化処理と $B_{n+1}$ ボトムフィールド画面の符号化処理は並行して実行されるので、プリフェッチは 1 回で済む。この結果、外部メモリ 4 1 からプリフェッチメモリ 4 4 にプリフェッチするデータ量は、 2 分の 1 で済むことになる。  $B_{n+2}$ トップフィールド画面及び  $B_{n+2}$ ボトムフィールド画面を符号化する場合も同様である。

### [0089]

以上のように、第1発明の動画像処理装置の一実施形態であるMPEGエンコーダ40においては、エンコード処理部42、43は、プリフェッチメモリ44を共有するとしているが、この場合、エンコード処理部42、43に、例えば、処理画面内の上下に隣接するマクロブロックラインを並行処理させることができる。

#### [0090]

このようにする場合には、エンコード処理部42、43の各々の探索領域の縦サイズを図11に示す第1従来例のMPEGエンコーダ1のようにエンコード処理部3、4の各々に対応させてプリフェッチメモリ5、6を設ける場合と同様にしても、探索領域の縦サイズを第1従来例のMPEGエンコーダ1のように2個のプリフェッチメモリ5、6を設けるようにした場合の探索領域の合計縦サイズよりも小さくすることができる。

#### [0091]

したがって、プリフェッチメモリ44にプリフェッチさせるプリフェッチ領域の縦サイズを第1従来例のMPEGエンコーダ1のように2個のプリフェッチメモリ5、6を設けるようにした場合のプリフェッチ領域の合計縦サイズよりも小さくすることができ、プリフェッチメモリ44に要求される記憶容量を第1従来例のMPEGエンコーダ1のように2個のプリフェッチメモリ5、6を設けるようにした場合の合計記憶容量よりも小さくし、外部メモリ41とプリフェッチメモリ44との間のデータ転送量を削減することができる。

### [0092]

なお、H.264/AVCのMBAFF (macroblock-adaptive frame/field coding) による符号化を行う場合には、エンコード処理部 42 は画面の偶数マクロブロックペアラインを担当し、エンコード処理部 43 は画面の奇数マクロブロックペアラインを担当し、これらエンコード処理部 42、43 は、上下に隣接したマクロブロックペアラインを並列処理するようにしても良い。

#### [0093]

また、第1発明の動画像処理装置の一実施形態であるMPEGエンコーダ40においては、エンコード処理部42、43に、参照画を共通とする所定の複数処理画面を並行処理させることもできる。例えば、図7に示すように、 $B_{n+1}$ トップ / ボトム及び  $B_{n+2}$ トップ / ボトムの各フィールド画面を符号化する場合、エンコード処理部42、43にトップフィールド画面とボトムフィールド画面の並列処理を行わせることができる。このようにす

10

20

30

40

る場合にも、外部メモリとプリフェッチメモリとの間のデータ転送量を削減することができる。

#### [0094]

また、第1発明の動画像処理装置の一実施形態では、第1発明の動画像処理装置をMPEGエンコーダに適用した場合について説明したが、第1発明の動画像処理装置は、MPEGデコーダにも適用することができ、この場合、エンコード処理部42、43の代わりに、2個のデコード処理部を備えることになる。

#### [0095]

(第2発明の動画像処理装置の一実施形態)

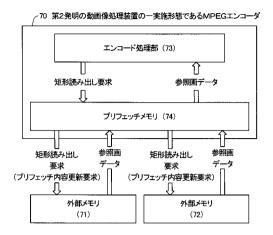

図9は第2発明の動画像処理装置の一実施形態であるMPEGエンコーダを外部メモリとともに示す図である。図9中、70は第2発明の動画像処理装置の一実施形態であるMPEGエンコーダ、71、72はMPEGエンコーダ70が動きベクトル算出のために参照する参照画を格納するための外部メモリであり、外部メモリ71には参照画の偶数ラインが割り当てられる。

#### [0096]

また、MPEGエンコーダ70において、73はMPEGストリームの作成に必要な演算処理を行うエンコード処理部、74は外部メモリ71、72が記憶する参照画の一部分をプリフェッチして記憶するために使用されるプリフェッチメモリである。

#### [0097]

エンコード処理部 7 3 は、動きベクトル算出のためにプリフェッチメモリ 7 4 が記憶する画像内の矩形領域を使用する場合には、プリフェッチメモリ 7 4 に対して矩形読み出し要求を発行することになる。この矩形読み出し要求には、読み出し対象の矩形領域の位置情報及びサイズ情報などが含まれる。

#### [0098]

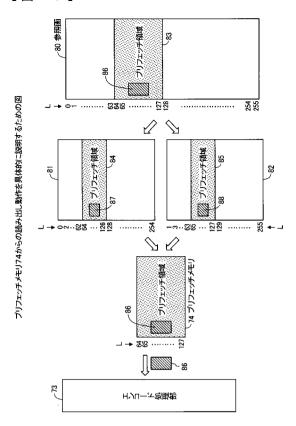

図10はプリフェッチメモリ74からの読み出し動作を具体的に説明するための図である。図10中、80は参照画であり、81は参照画80内の偶数ラインL0、L2、…、L254部分の参照画、82は参照画80内の奇数ラインL1、L3、…、L255部分の参照画であり、参照画81は外部メモリ71に格納され、参照画82は外部メモリ72に格納される。

### [0099]

この例では、参照画 8 0 内のラインL64~L127がプリフェッチ領域 8 3 とされており、プリフェッチ領域 8 3 内の偶数ラインL64、L66、…、L126の部分は、プリフェッチ領域 8 4 としてプリフェッチメモリ74にプリフェッチされ、プリフェッチ領域 8 3 内の奇数ラインL65、L67、…、L127の部分は、プリフェッチ領域 8 5 としてプリフェッチメモリ74にプリフェッチされている。

#### [0100]

したがって、プリフェッチメモリ74には、参照画80内のラインL64~L127が記憶される。この結果、エンコード処理部73が参照画80内の矩形領域86を必要とする場合には、エンコード処理部73は、矩形領域86を要求する矩形読み出し要求をプリフェッチメモリ74に発行することになり、矩形領域86の画像データは、プリフェッチメモリ74から読み出されてエンコード処理部73に転送される。なお、87は矩形領域86内の偶数ライン部分、88は矩形領域86内の奇数ライン部分である。

### [0101]

ここで、図14に示す従来のMPEGエンコーダ20においては、1個のエンコード処理部23に対して2個のプリフェッチメモリ24、25を設け、プリフェッチメモリ24には参照画30内のプリフェッチ領域内の偶数ラインの一部分を記憶させ、プリフェッチメモリ25には参照画30内のプリフェッチ領域内の奇数ラインの一部分を記憶させるようにしているので、エンコード処理部23は、プリフェッチメモリ24、25に対して別々に矩形読み出し要求を発行しなければならず、読み出し効率が悪いという問題点があった。

10

20

30

#### [0102]

これに対して、第2発明の動画像処理装置の一実施形態であるMPEGエンコーダ70によれば、参照画の一部分をプリフェッチして記憶するプリフェッチメモリとして1個のプリフェッチメモリ44を備えるとしているので、参照画を振り分けて記憶する2個の外部メモリ71、72を使用する場合であっても、エンコード処理部73は、図14に示す第2従来例のMPEGエンコーダ20のように2個のプリフェッチメモリ24、25を備える場合のように2個の矩形読み出し要求を発行する必要はなく、1個のプリフェッチメモリ44に対して矩形読み出し要求を発行すれば足りる。したがって、プリフェッチメモリ44からの画像データ読み出しの効率化を図ることができる。

#### [0103]

また、第2発明の動画像処理装置の一実施形態では、第2発明の動画像処理装置をMPEGエンコーダに適用した場合について説明したが、第2発明の動画像処理装置は、MPEGデコーダにも適用することができ、この場合、図14に示すエンコード処理部23の代わりに、デコード処理部を備えることになる。

#### [0104]

なお、H.264/AVCのMBAFFによる符号化を行う場合には、外部メモリ71には参照画の偶数マクロブロックペアラインを割り当て、外部メモリ72には参照画の奇数マクロブロックペアラインを割り当てるようにしても良い。

#### [0105]

ここで、本発明の動画像処理装置を整理すると、本発明の動画像処理装置には、少なくとも、以下の動画像処理装置が含まれる。

#### [0106]

(付記1)複数のデコード処理部又は複数のエンコード処理部を備える動画像処理装置であって、前記複数のデコード処理部又は前記複数のエンコード処理部に共有されるプリフェッチメモリを備えることを特徴とする動画像処理装置。

#### [0107]

(付記 2)前記複数のデコード処理部又は前記複数のエンコード処理部は、処理画面内の上下に隣接するマクロブロックライン又はマクロブロックペアラインを並行処理することを特徴とする付記 1 に記載の動画像処理装置。

### [0108]

(付記3)前記複数のデコード処理部又は前記複数のエンコード処理部は、参照画を共通とする所定の複数処理画面を並行処理することを特徴とする付記1に記載の動画像処理 装置。

#### [0109]

(付記4)前記複数のデコード処理部又は前記複数のエンコード処理部は、処理画面内の上下に隣接するマクロブロックライン又はマクロブロックペアラインの並行処理と、参照画を共通とする所定の複数処理画面の並行処理とを切り替えて行うことを特徴とする付記1に記載の動画像処理装置。

### [0110]

(付記5)前記複数のデコード処理部又は前記複数のエンコード処理部は、2個のデコード処理部又は2個のエンコード処理部であり、前記所定の複数処理画面は、同一フレームのトップフィールド画面とボトムフィールド画面であることを特徴とする付記3又は付記4に記載の動画像処理装置。

## [0111]

(付記5)デコード処理部又はエンコード処理部を備え、参照画を分割して格納する複数の外部メモリを使用する動画像処理装置であって、前記参照画の一部分をプリフェッチして記憶するプリフェッチメモリとして前記複数の外部メモリに共有されるプリフェッチメモリを備えることを特徴とする動画像処理装置。

#### [0112]

(付記6)前記複数の外部メモリは、第1の外部メモリ及び第2の外部メモリであり、

10

20

30

40

前記第1の外部メモリには、前記参照画の偶数ライン部分が格納され、前記第2の外部メモリには、前記参照画の奇数ライン部分が格納されることを特徴とする付記5に記載の動画像処理装置。

【図面の簡単な説明】

[0113]

【図1】第1発明の動画像処理装置の一実施形態であるMPEGエンコーダを外部メモリとともに示す図である。

【図2】第1発明の動画像処理装置の一実施形態において、2個のエンコード処理部が上下に隣接したマクロブロックラインを並列処理する場合にプリフェッチメモリにプリフェッチされることが望ましい参照画内のプリフェッチ領域を説明するための図である。

【図3】第1発明の動画像処理装置の一実施形態において、2個のエンコード処理部が上下に隣接したマクロブロックラインを並列処理する場合にプリフェッチメモリがプリフェッチするプリフェッチ領域の具体例を説明するための図である。

【図4】フィールド構造のMPEGストリームの一部分を示す図である。

【図 5 】図 4 に示す  $P_{n+3}$ トップ / ボトム、  $B_{n+1}$ トップ / ボトム、  $B_{n+2}$ トップ / ボトム 及び  $P_{n+6}$ トップ / ボトムの各フィールド画面を符号化する場合に適用して好適な処理領域の 2 個のエンコード処理部への第 1 の割り当て方法及びプリフェッチメモリにプリフェッチさせるプリフェッチ領域を示す図である。

【図6】図4に示すB<sub>n+1</sub>トップ / ボトムの各フィールドを図5に示す第1の割り当て方法を使用して符号化する場合における2個のエンコード処理部の処理領域の遷移とプリフェッチメモリがプリフェッチするプリフェッチ領域の遷移を示す図である。

【図 7 】図 4 に示す  $P_{n+3}$  トップ / ボトム、  $B_{n+1}$  トップ / ボトム、  $B_{n+2}$  トップ / ボトム 及び  $P_{n+6}$  トップ / ボトムの各フィールド画面を符号化する場合に適用して好適な処理領域の 2 個のエンコード処理部への第 2 の割り当て方法及びプリフェッチメモリ 4 4 にプリフェッチさせるプリフェッチ領域を示す図である。

【図8】図4に示すB<sub>n+1</sub>トップ / ボトムの各フィールドを図7に示す第2の割り当て方法を使用して符号化する場合における2個のエンコード処理部の処理領域とプリフェッチ メモリ44がプリフェッチするプリフェッチ領域の遷移を示す図である。

【図9】第2発明の動画像処理装置の一実施形態であるMPEGエンコーダを外部メモリとともに示す図である。

【図10】第2発明の動画像処理装置の一実施形態であるMPEGエンコーダが備えるプリフェッチメモリからの読み出し動作を具体的に説明するための図である。

【図11】第1従来例のMPEGエンコーダを外部メモリとともに示す図である。

【図12】第1従来例のMPEGエンコーダが備えるプリフェッチメモリがプリフェッチ するプリフェッチ領域を具体的に説明するための図である。

【図13】第1従来例のMPEGエンコーダが備えるプリフェッチメモリにプリフェッチ されることが望ましい参照画内のプリフェッチ領域を説明するための図である。

【図14】第2従来例のMPEGエンコーダを外部メモリとともに示す図である。

【図15】第2従来例のMPEGエンコーダにおけるプリフェッチメモリからの読み出し動作を具体的に説明するための図である。

【符号の説明】

[0114]

- 1 ... 第 1 従来例の M P E G エンコーダ

- 2 ... 外部メモリ

- 3、4…エンコード処理部

- 5、6…プリフェッチメモリ

- 10...参照画

- 1 1 、 1 2 ... プリフェッチ領域

- 15、16…マクロブロック

- 17、18...探索領域

10

20

\_ \_

30

- 20…第2従来例のMPEGエンコーダ

- 2 1 、 2 2 … 外部メモリ

- 23 ...エンコード処理部

- 24、25…プリフェッチメモリ

- 30~32...参照画

- 33~35...プリフェッチ領域

- 3 6 ~ 3 8 ... 矩形領域

- 40…第1発明の動画像処理装置の一実施形態であるMPEGエンコーダ

- 4 1 ... 外部メモリ

- 42、43...エンコード処理部

- 44...プリフェッチメモリ

- 4 5 ... 調停部

- 5 0 ... 参照画

- 51、52…マクロブロック

- 5 3 、 5 4 … 探索領域

- 55...プリフェッチ領域

- 60… P<sub>n</sub>トップフィールド参照画

- 6 1 ... プリフェッチ領域

- 62… P がトムフィールド参照画

- 63...プリフェッチ領域

- 65… P n トップフィールド参照画

- 6 6 ... プリフェッチ領域

- 67...P<sub>n</sub>ボトムフィールド参照画

- 68...プリフェッチ領域

- 70…第2発明の動画像処理装置の一実施形態であるMPEGエンコーダ

- 7 1 、 7 2 ... 外部メモリ

- 73 ... エンコード処理部

- 74...プリフェッチ領域

- 80~82...参照画

- 83~85...プリフェッチ領域

- 86~88...矩形領域

20

### 【図1】

第1発明の動画像処理装置の一実施形態である MPEGエンコーダを外部メモリとともに示す図

## 【図2】

エンコード処理部42、43が上下に隣接したマクロブロックラインを並列処理する場合にプリフェッチメモリ44にプリフェッチされることが望ましい参照画内のプリフェッチ領域を説明するための図

【図3】

【図4】

【図6】

図4に示すBiTップノボトムの各フィールドを図5に示す第1の割り当て方法を使用して符号化する

図4に示すB㎡ トップノボトムの各フィールドを図기に示す第2の割り当て方法を使用して符号化する

€ : @

: @

: ©

#### 【図5】 Pn+6 (B) 偶数 MBL Pn+6 (B) 奇数 MBL Pn+3 (B) Pn+6 (T) 図4に示すPn+3 トップ/ボトム、Bn+1 トップ/ボトム、Bn+2 トップ/ボトム及びPn+6 トップ/ボトムの各フィールド画面を符号化する場合に適用して好適な処理領域のエンコード処理部42、43への第1の割り当て方法及びプリフェッチメモリ44にプリフェッチさせるプリフェッチ領域を示す図 Pn+6(T) 網数 MBL Pn+6 (T) 奇数 MBL Pn+3 (T) Pn+3 (B) Bn+2 (B) 偶数 MBL Bn+2 (B) 奇数 MBL Pn+3 (T) Pn+3 (B) Pn∃ Pn (B) Bn+2 (T) 偶数 MBL Bn+2 (T) 奇数 MBL Pn+3 (T) Pn+3 (B) F E P<sub>n</sub> (B) Bn+1 (B) 偶数 MBL Bn+1 (B) Pn+3 (B) 奇数 MBL Pn+3 (T) E E Pn (B) Brr+1 (T) 偶数 MBL Brrt (T) 奇数 MBL Pn+3 (T) Pn+3 (B) P<sub>n</sub> P<sub>n</sub>(B) Pn+3 (B) 偶数 MBL 奇数 MBL Pn+3 (B) Pn+3 (T) P<sub>4</sub>(B) Pn+3 (T) 偶数 MBL Pn+3 (T) 奇数 MBL Pn (B) P<sub>n</sub>( プリフェッチメモリ44 に記憶させる領域 エンコード処理部42 エンコード処理部43 が処理する領域 が処理する領域 : (0) € : (B) 【図7】 Pn+6 (B) 偶数 MBL 奇数 MBL Pn+6 (T) Pn+3 (B) Pn+6 (B) 各フィールド画面を符号化する場合に適用して好適な処理領域のエンコード処理部42、43への第2の割り当て方法及びブリフェッチメモリ44にプリフェッチさせるプリフェッチ 確域を示す図 図4に示すPn+3トップノボトム、Bn+1トップノボトム、Bn+2トップノボトム及びPn+6トップノボトムの Pn+6 (T) Pn+3(T) Pn+3 (B) 偶数 MBL Pn+6 (T) 奇数 MBL Bn+2 (T) Pn+3 (T) Pn+3 (B) Bn+2 (B) P<sub>r</sub> Pn (B) Bn+1 (T) Bn+1 (B) Pn+3 (T) Pn+3 (B) P<sub>n</sub>(E) P<sub>n</sub> (B) Pn+3 (B) Pn+3 (B) 偶数 MBL Pn+3 (1) 奇数 MBL Pn (B) Pn+3 (T) 偶数 MBL Pn+3 (T) 奇数 WBL P<sub>n</sub>(T) ъ (В) エンコード処理部42 エンコード処理部43 が処理する領域 プリフェッチメモリ44 に記憶させる領域 が処理する領域

: €

: (B)

: (0)

MBL7 8 **29** MBL6 63 <u>1</u> 場合におけるエンコード処理部42、43の処理領域の遷移とプリフェッチメモリ44がプリフェッチする Bu+1 ボトムフィールド処理 MBL5 8 -62 MBL4 83 8 62 MBL2 MBL3 83 19 MBLO 96 79 MBL1 ဆု ē MBL7 99 MBL6 -62 8 19 Br+1 トップフィールド処理 MBL5 8 -62 MBL4 છ્ 6 プリフェッチ領域の遷移を示す図 MBL3 é 62 MBL2 -63 19 MBLO MBL1 8 9 છુ 19 ┿┪ 0=264697 0-064597 エンコード処理部42が処理 (A) … するマクロブロックライン エンコード処理部43が処理 するマクロブロックライン Pn(B)フィールド ・参照画62内の ブリフェッチ領域63 Pn(T)フィールド 参照画60内の プリフェッチ領域61 : @ : @ : © 【図8】 95 19 MBL7 MBL7 99 8 場合におけるエンコード処理部42、43の処理領域の遷移とプリフェッチメモリ44がプリフェッチする MBL<sub>6</sub> MBL6 65 8 -67 99 MBL5 MBL5 92 99 89 19 MBL4 92 -67 MBL4 99 86 188 MBL3 8 92 **79** MBL3 MBL2 92 MBL2 19 99 89 プリフェッチ領域の遷移を示す図 MBL1 65 MBL1 29 99 89 エンコード処理部42が処理 するマクロブロックライン MBLO 65 29 99 89 エンコード処理部43が処理 するマクロブロックライン Pn (B)フィールド ・参照画67内の プリフェッチ領域68 Pn(T)フィールド ・参照画65内の ブリフェッチ領域66

### 【図9】

第2発明の動画像処理装置の一実施形態である MPEGエンコーダを外部メモリとともに示す図

【図10】

### 【図11】

第1従来例のMPEGエンコーダを外部メモリとともに示す図

### 【図12】

## 【図13】

プリフェッチメモリ5、6にプリフェッチされることが望ましい 参照画10内のプリフェッチ領域を説明するための図

## 【図14】

第2従来例のMPEGエンコーダを外部メモリとともに示す図

【図15】

## フロントページの続き

(56)参考文献 特表2009-505549(JP,A)

特開2006-031480(JP,A)

特開平04-045684(JP,A)

特開2006-042143(JP,A)

特開2006-041898(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 4 N 7 / 2 4 - 7 / 6 8