# (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 30 November 2006 (30.11.2006)

**PCT**

### (10) International Publication Number WO 2006/126733 A1

- (51) International Patent Classification: H03K 3/03 (2006.01)

- (21) International Application Number:

PCT/JP2006/310955

- (22) International Filing Date: 25 May 2006 (25.05.2006)

- (25) Filing Language: English

- (26) Publication Language: English

- (30) Priority Data:

2005-155371 27 May 2005 (27.05.2005) JP 2005-268019 15 September 2005 (15.09.2005)

- (71) Applicant (for all designated States except US): MAT-SUSHITA ELECTRIC INDUSTRIAL CO., LTD. [JP/JP]; 1006, Oaza Kadoma, Kadoma-shi, Osaka, 5718501 (JP).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): DOSHO, Shiro. SAKIYAMA, Shiro. TAKEDA, Noriaki.

- (74) Agents: MAEDA, Hiroshi et al.; Osaka-Marubeni Bldg., 5-7, Hommachi 2-chome, Chuo-ku, Osaka-shi, Osaka 5410053 (JP).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: COUPLED RING OSCILLATOR AND METHOD FOR LAYING OUT THE SAME

(57) Abstract: A coupled ring oscillator includes n ring oscillators (20) each including m inverter circuits (10), and a phase-coupling loop (40) in which m x n phase-coupling circuits (30), each of which couples signal phases at two points in a certain phase mode, are connected with each other to form a loop. Connection points at which the inverter circuits (10) are connected with each other and the connection points at which the phase-coupling circuits (30) are connected with each other are connected bijectively; and each of the inverter circuits (10) is connected between two points that divide the phase-coupling circuits (30) into two parts at a certain ratio.

#### DESCRIPTION

# COUPLED RING OSCILLATOR AND METHOD FOR LAYING OUT THE SAME

#### 5 TECHNICAL FIELD

The present invention relates to ring oscillators and a method for laying out the ring oscillators, and more particularly relates to a coupled ring oscillator which uses a plurality of ring oscillators and is capable of generating highly accurate phase information and a method for laying out the coupled ring oscillator.

#### 10 BACKGROUND ART

15

20

25

In order to record information on optical disc media such as a DVD (digital versatile disc), it is necessary to generate a special write-operation waveform for suppressing interference of a write signal. Generation of such a special write-operation waveform requires highly accurate phase information that is finer than one-fortieth of the write data rate. However, it is difficult to realize such extremely fine phase accuracy by a single inverter chain (a ring oscillator), because the phase delay thereof is shorter than a delay of a single inverter circuit. Therefore, conventionally, a plurality of ring oscillators are used and the respective inverter circuits in the ring oscillators are connected by phase-coupling circuits so as to slightly change the output phase of each ring oscillator, whereby phase information finer than that that can be generated by a single ring oscillator is produced (see, for example, Patent Documents 1, 2, and 3).

Also, a resistor ring, in which a plurality of resistors are connected, is provided, and the connection points of the resistors in the resistor ring are connected with the connection points of phase delay elements in a plurality of ring oscillators are connected to thereby produce fine phase information (see Patent Document 4, for example)

Patent Document 1: Specification of Patent No. 550030

Patent Document 2: Specification of US patent No. 5475344

Patent Document 3: Specification of US patent No. 5717362

Patent Document 4: Specification of US patent application publication No. 2006/0049879

#### DISCLOSURE OF THE INVENTION

5

10

15

20

25

However, in the conventional layout in which the respective inverter circuits in the ring oscillators are connected by the phase-coupling circuits, the wire length of some of the signal wires is extremely increased and only some of the inverter circuits are thus under heavy load. Such layout errors cause variations in the driving timing of the inverter circuits, making it difficult to generate highly accurate phase information.

In view of the above problem, it is therefore an object of the present invention to provide a coupled ring oscillator including a plurality of ring oscillators and capable of generating highly accurate phase information. Another object of the present invention is to provide a simple method for laying out the coupled ring oscillator.

In order to solve the above problem, an inventive coupled ring oscillator includes: n ring oscillators each including m inverter circuits; and a phase-coupling loop in which  $m \times n$  phase-coupling circuits, each of which couples signal phases at two points in a certain phase mode, are connected with each other to form a loop, wherein connection points at which the inverter circuits are connected with each other and the connection points at which the phase-coupling circuits are connected with each other are connected bijectively; and each of the inverter circuits is connected between two points that divide the phase-coupling circuits into two parts at a certain ratio.

Then, the connection points at which the m inverter circuits in each of the n ring oscillators are connected with each other and the connection points at which the  $m \times n$  phase-coupling circuits are connected with each other are connected bijectively, and each of the inverter circuits is connected between two points that divide the  $m \times n$  phase-coupling circuits in the phase-coupling loop into two parts at a certain ratio. Therefore, all of the inverter circuits have substantially the same wire length, allowing highly accurate and fine phase information to be generated.

Specifically, the phase-coupling circuits each couple signal phases at two points in a reverse phase mode; and each of the inverter circuits is connected between two points that divide the phase-coupling circuits into n phase-coupling circuits and  $n \times (m-1)$  phase-coupling circuits.

Also, specifically, the phase-coupling circuits each couple signal phases at two points in a common mode; and each of the inverter circuits is connected between two points that divide the phase-coupling circuits into  $n \times (m-1)/2$  phase-coupling circuits and  $n \times (m+1)/2$  phase-coupling circuits.

5

10

15

20

25

An inventive method for laying out a coupled ring oscillator includes the steps of:

(a) connecting  $m \times n$  basic cells each including a phase-coupling element and a circuit element, wherein the phase-coupling element corresponds to two connected half-circuits, each equivalent to half of a phase-coupling circuit for coupling two signal phases at two points in a reverse phase mode, at both ends of the phase-coupling circuit, the circuit element includes an inverter circuit in which either an input terminal or an output terminal is connected to a connection point at which the two half-circuits are connected with each other, and the  $m \times n$  basic cells are connected into a loop so that each phase-coupling circuit is formed between adjacent ones of the phase-coupling elements; and (b) connecting, in any two of the basic cells existing (n-1) apart, the input terminal of the inverter circuit in one of the two basic cells with the output terminal of the inverter circuit in the other basic cell.

Then, the  $m \times n$  basic cells each including the phase-coupling element and the inverter circuit are appropriately laid out to form a loop, whereby the above-mentioned coupled ring oscillator is obtained that includes the n ring oscillators, in each of which the m inverter circuits are connected with each other, and the phase-coupling loop, in which the  $m \times n$  phase-coupling circuits are connected into a loop.

Another inventive method for laying out a coupled ring oscillator includes the steps of: (a) connecting  $m \times n$  basic cells each including a phase-coupling circuit for

coupling two signal phases at two points in a certain phase mode and a circuit element, wherein the circuit element includes an inverter circuit in which either an input terminal or an output terminal is connected to one end of the phase-coupling circuit, and the  $m \times n$  basic cells are connected into a loop so that the phase-coupling circuits are connected with each other; and (b) connecting, in any two of the basic cells existing (n-1) apart, the input terminal of the inverter circuit in one of the two basic cells with the output terminal of the inverter circuit in the other basic cell.

Specifically, each of the phase-coupling circuits couples signal phases at two points in a reverse phase mode; and in the step (a), the basic cells are connected so that adjacent ones of the phase-coupling circuits are connected with each other.

Also, specifically, each of the phase-coupling circuits couples signal phases at two points in a common mode; and in the step (a), the basic cells are connected so that alternate ones of the phase-coupling circuits are connected with each other.

Then, the  $m \times n$  basic cells each including the phase-coupling circuit and the inverter circuit are appropriately laid out to form a loop, whereby the above-mentioned coupled ring oscillator is obtained that includes the n ring oscillators, in each of which the m inverter circuits are connected with each other, and the phase-coupling loop, in which the  $m \times n$  phase-coupling circuits are connected into a loop.

As described above, the inventive coupled ring oscillator generates highly accurate and fine phase information. Also, the inventive coupled ring oscillator is easily formed by connecting the basic cells into a loop.

#### **BRIEF DESCRIPTION OF DRAWINGS**

5

10

15

20

25

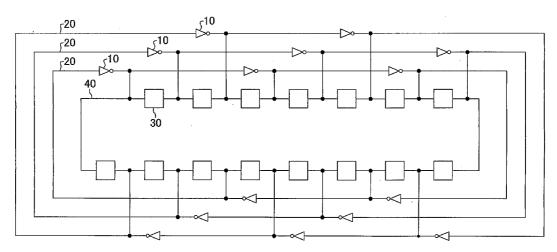

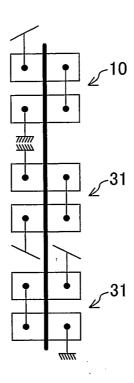

Figure 1 shows the configuration of a coupled ring oscillator according to a first embodiment.

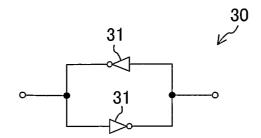

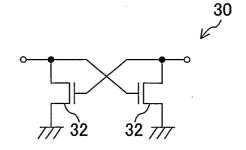

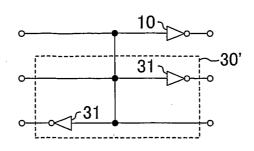

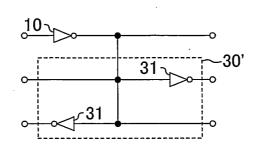

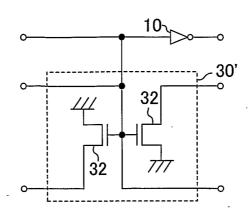

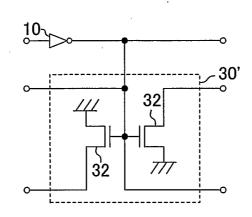

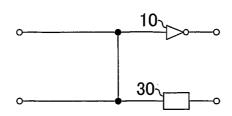

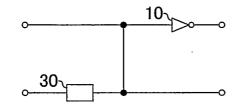

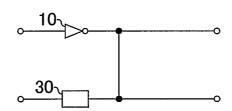

Figures 2A and 2B show circuit configurations of phase-coupling circuits shown in Figure 1.

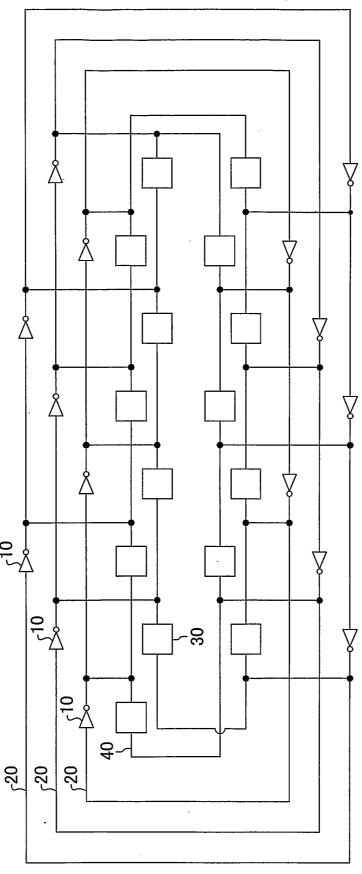

Figure 3 shows the configuration of a coupled ring oscillator according to a second

embodiment.

5

10

15

20

25

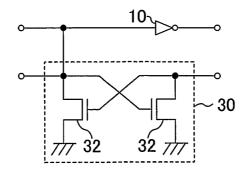

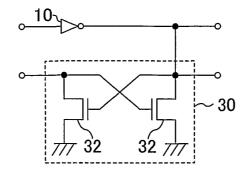

Figures 4A, 4B, 4C, and 4D show circuit configurations of phase-coupling circuits shown in Figure 3.

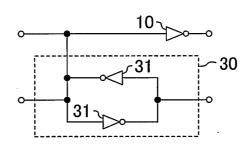

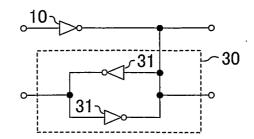

Figures 5A, 5B, 5C, and 5D show circuit configurations of basic cells in the coupled ring oscillator according to the first embodiment, in which inverter circuits are included.

Figures 6A, 6B, 6C, and 6D show circuit configurations of basic cells in the coupled ring oscillator according to the first embodiment, in which NMOS transistors are used.

Figure 7 shows an exemplary layout of the basic cell shown in Figure 5.

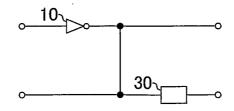

Figure 8 shows relation between phase-coupling elements and a phase-coupling circuit when the phase-coupling elements are composed of inverter circuits.

Figures 9A, 9B, 9C, and 9D show circuit configurations of basic cells in the coupled ring oscillator according to the second embodiment.

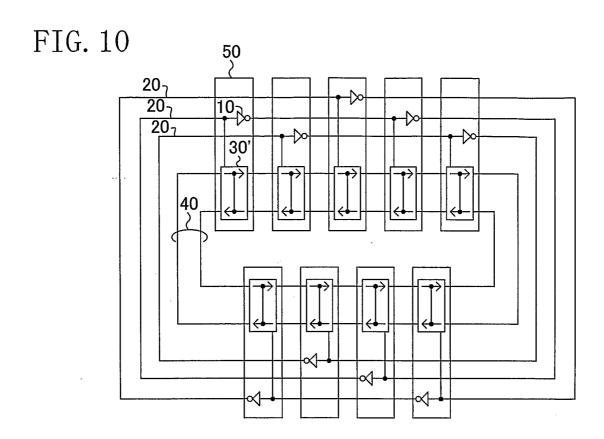

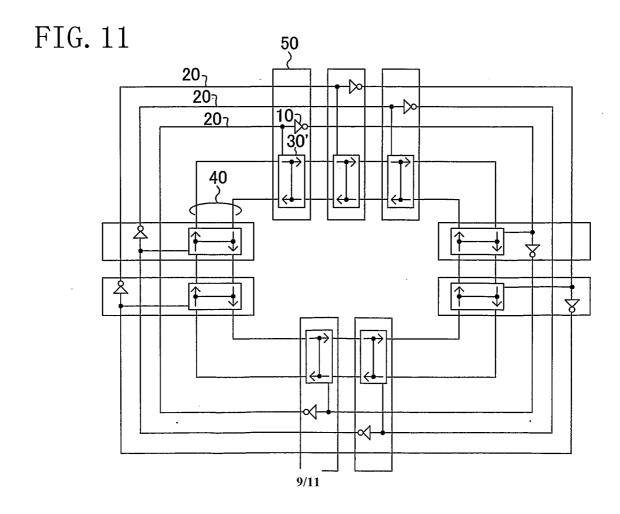

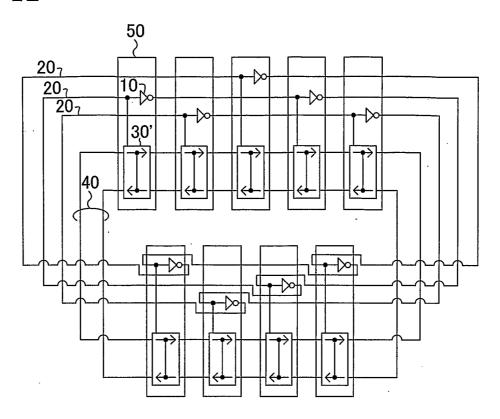

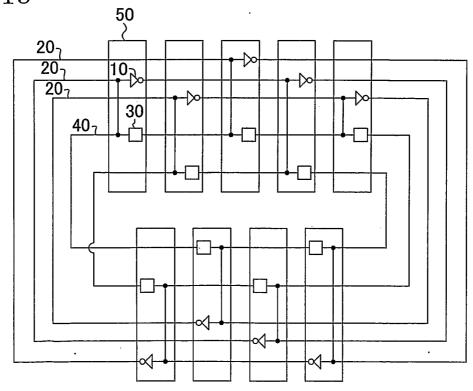

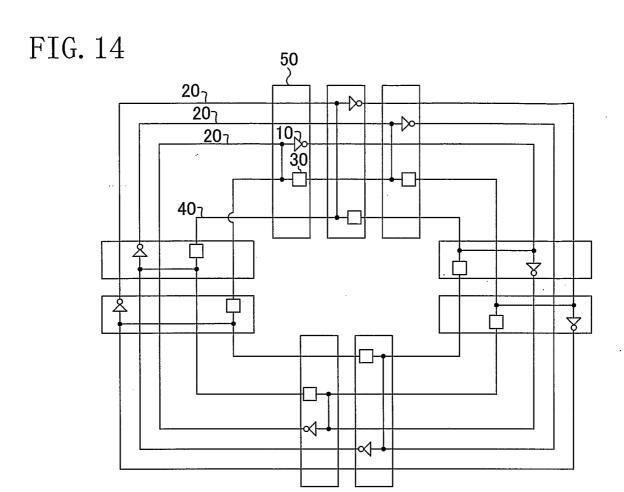

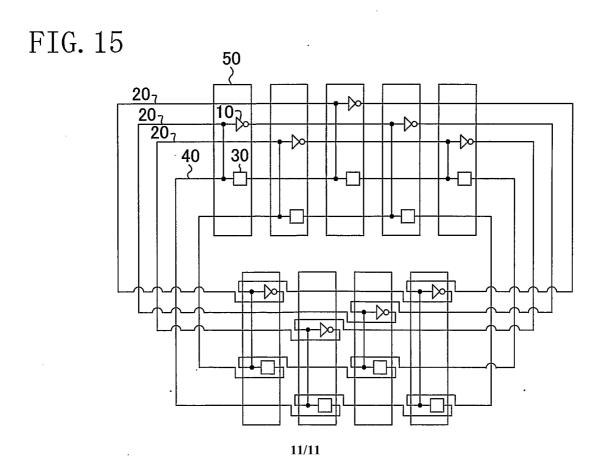

Figures 10, 11, 12, 13, 14, and 15 show exemplary configurations of a coupled ring oscillator of a three-stage, three-set type.

# BEST MODE FOR CARRYING OUT THE INVENTION

Hereinafter, preferred embodiments of the present invention will be described with reference to the accompanying drawings.

(First embodiment)

Figure 1 shows the configuration of a coupled ring oscillator according to a first embodiment. The coupled ring oscillator shown in Figure 1 includes three (n = 3) ring oscillators 20, each composed of five (m = 5) inverter circuits 10, and a phase-coupling loop 40 in which fifteen  $(m \times n = 15)$  phase-coupling circuits 30 are connected to form a loop.

The three ring oscillators 20 and the phase-coupling loop 40 are laid out in a nested pattern, in which the phase-coupling loop 40 is innermost. The connection points at

which the phase-coupling circuits 30 are connected with each other and the connection points at which the inverter circuits 10 are connected with each other are connected. That is, the connection points of the phase-coupling circuits 30 and the connection points of the inverter circuits 10 are connected bijectively. Furthermore, each inverter circuit 10 is parallel-connected with three connected phase-coupling circuits 30. In other words, each inverter circuit 10 is connected between two points that divide the fifteen  $(m \times n = 15)$  phase-coupling circuits 30 into three (n = 3) and twelve  $(n \times (m-1) = 12)$ .

Figures 2A and 2B show exemplary circuit configurations of the phase-coupling circuits 30 shown in Figure 1. Each phase-coupling circuit 30 of this embodiment couples signal phases at two points in a reverse phase mode. When the phase-coupling circuit 30 is composed of inverter circuits, the phase-coupling circuit 30 takes the form of a latch circuit in which the input terminal of one of the two inverter circuits 31 is connected to the output terminal of the other, as shown in Figure 2A. When the phase-coupling circuit 30 is composed of MOS transistors, for example, NMOS transistors, the phase-coupling circuit 30 takes the form of a latch circuit in which the gate of one of the two NMOS transistors 32 is connected to the drain of the other, as shown in Figure 2B.

The circuit layout of the coupled ring oscillator shown in Figure 1 is completely different from the conventional one, and all of the inverter circuits 10 have substantially the same wire length. In the coupled ring oscillator of this embodiment, the phenomenon in which only some of the inverter circuits are under heavy load does not occur, which enables highly accurate and fine phase information to be generated. Also, each phase information can be taken out from each connection point of the phase-coupling circuits 30 in the phase-coupling loop 40, such that the phase information can be taken very easily.

(Second embodiment)

5

10

15

20

25

Figure 3 shows the configuration of a coupled ring oscillator according to a second embodiment. As in the first embodiment, the coupled ring oscillator shown in Figure 3 includes n (n = 3) ring oscillators 20, each composed of five (m = 5) inverter circuits 10,

and a phase-coupling loop 40 in which fifteen  $(m \times n = 15)$  phase-coupling circuits 30 are connected to form a loop.

As in the first embodiment, the three ring oscillators 20 and the phase-coupling loop 40 are laid out in a nested pattern in which the phase-coupling loop 40 is innermost. The connection points of the phase-coupling circuits 30 and the connection points of the inverter circuits 10 are connected bijectively.

5

10

15

20

25

Unlike in the first embodiment, the phase-coupling circuits 30 of this embodiment each couple signal phases at two points in a common mode. That is, the phase-coupling circuits 30 are connected in such a manner that each phase-coupling circuit 30 connects two of the connection points of the inverter circuits 10 in two ring oscillators 20 that should be in phase with each other. Therefore, the phase-coupling loop 40 forms two turns and is closed, while connecting the ring oscillators 20 in an alternate manner. In other words, each inverter circuit 10 is connected between two points that divide the fifteen phase-coupling circuits 30 into six  $(n \times (m-1)/2 = 6)$  and nine  $(n \times (m+1)/2 = 9)$ .

The phase-coupling circuits 30 of this embodiment each couple signal phases at two points in a common mode, and thus can be realized by resistive elements. Exemplary configurations of the phase-coupling circuits 30 will be described below.

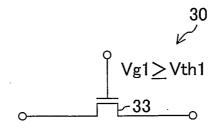

Figure 4A shows an example in which the phase-coupling circuit 30 is composed of an NMOS transistor 33, in which a voltage Vg1 that is higher than a threshold voltage Vth1 is applied between the gate and the source or between the gate and the drain. Preferably, a control voltage of the oscillation frequency of the ring oscillators 20 is applied to the gate of the NMOS transistor 33. Then, when the control voltage rises, for example, gm (transconductance) of the NMOS transistor 33 increases with the oscillation frequency and the amplitude of the ring oscillators 20, whereby the strength of the common mode coupling is increased. Therefore, the linearity of signal phase interpolation by the phase-coupling circuit 30 is maintained in a wide band.

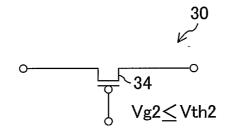

Figure 4B shows an example in which the phase-coupling circuit 30 is composed

of a PMOS transistor 34, in which a voltage Vg2 that is lower than a threshold voltage Vth2 is applied between the gate and the source or between the gate and the drain. Preferably, the gate of the PMOS transistor 34 is grounded. Then, when the control voltage of the oscillation frequency of the ring oscillators 20 rises, for example, gm (transconductance) of the PMOS transistor 34 increases with the oscillation frequency and the amplitude of the ring oscillators 20, whereby the strength of the common mode coupling is increased. Therefore, the linearity of signal phase interpolation by the phase-coupling circuit 30 is maintained in a wide band.

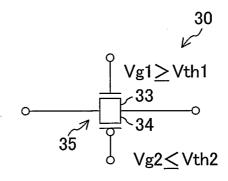

Figure 4C shows an example in which the phase-coupling circuit 30 is composed of a transfer gate 35 in which the NMOS transistor 33 and the PMOS transistor 34 are combined. The combination of the NMOS and PMOS transistors increases the effect of linearity further.

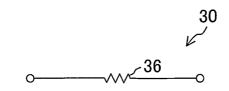

Figure 4D shows an example in which the phase-coupling circuit 30 is composed of a resistance element 36. Although the resistance element 36 has the highest linearity, the resistance value does not change with the oscillation frequency of the ring oscillators 20. Therefore, the resistive element 36 is not so effective in signal phase interpolation.

As described above, in this embodiment, since the phases of the ring oscillators 20 are coupled by the resistive elements having high linearity, signal phase interpolation is performed more accurately.

It should be noted that the phase-coupling loop 40 is not limited to the configuration in which the phase-coupling loop 40 forms two turns and is closed. However, if the phase-coupling loop 40 is formed according to the below-described layout method, the phase-coupling loop 40 has the configuration shown in Figure 3.

In the coupled ring oscillator according to the present invention, the number of ring oscillators 20 is not limited to three and the number of inverter circuits 10 forming each ring oscillators 20 is not limited to five.

(Layout method)

5

10

15

20

25

Next, a method for laying out the coupled ring oscillators helpful for understanding the present invention will be described. The coupled ring oscillators according to the preferred embodiments have a geometrical regularity as shown in Figures 1 and 3 and thus can be easily formed by laying out a plurality of "basic cells".

5

10

15

20

25

Figures 5A-5D and 6A-6D show exemplary circuit configurations of basic cells in the coupled ring oscillator of the first embodiment. In Figures 5A-5D, the basic cells are formed using inverter circuits, while in Figures 6A-6D, the basic cells are formed using NMOS transistors. The basic cells shown in Figures 5A and 5B and Figures 6A and 6B are each composed of an inverter circuit 10, which is part of a ring oscillator 20, and a The phase-coupling element 30' is equivalent to a phase-coupling element 30'. configuration in which two half-circuits, each corresponding to half of a phase-coupling circuit 30 having a symmetrical circuit configuration, are connected at both ends of the phase-coupling circuit 30. For example, the phase-coupling elements 30' shown in Figures 5A and 5B have a circuit configuration in which the input terminals of two inverter circuits 31 are connected with each other. This corresponds to a configuration in which two inverter circuits 31 as half-circuits of the phase-coupling circuit 30 shown in Figure 2A are connected at both ends of the phase-coupling circuit 30. Also, the phase-coupling elements 30' shown in Figures 6A and 6B have a circuit configuration in which the gates of two NMOS transistors 32 are connected with each other. This corresponds to a configuration in which two NMOS transistors 32 as half-circuits of the phase-coupling circuit 30 shown in Figure 2B are connected at both ends of the phase-coupling circuit 30.

The basic cells shown in Figures 5A and 6A have a configuration in which the input terminal of the inverter circuit 10 is connected with the phase-coupling element 30′. On the other hand, the basic cells shown in Figures 5B and 6B have a configuration in which the output terminal of the inverter circuit 10 is connected with the phase-coupling element 30′. In this way, either the input terminal or the output terminal of the inverter circuit 10 may be connected with the phase-coupling element 30′. However, it is

preferable that the input terminal be connected with the phase-coupling element 30′. Figure 7 shows an exemplary layout of the basic cell shown in Figure 5A. By connecting the input terminal of the inverter circuit 10 with the phase-coupling element 30′, the gates of the transistors forming the inverter circuit 10 are connected by a common wire with the transistors forming the inverter circuits 31. The configuration of the basic cell is thus simplified significantly. This effect is also obtained in the basic cell shown in Figure 6A.

5

10

15

20

25

On the other hand, Figure 5C shows an exemplary configuration of a basic cell in which the input terminal of an inverter circuit 10 as part of a ring oscillator 20 is connected with the phase-coupling circuit 30 shown in Figure 2A. Figure 5D shows an exemplary configuration of a basic cell in which the output terminal of an inverter circuit 10 as part of a ring oscillator 20 is connected with the phase-coupling circuit 30 shown in Figure 2A. Figure 6C shows an exemplary configuration of a basic cell in which the input terminal of an inverter circuit 10 as part of a ring oscillator 20 is connected with the phase-coupling circuit 30 shown in Figure 2B. Figure 6D shows an exemplary configuration of a basic cell in which the output terminal of an inverter circuit 10 as part of a ring oscillator 20 is connected with the phase-coupling circuit 30 shown in Figure 2B. In this manner, the basic cell may be composed of a single inverter circuit 10 and a single phase-coupling circuit 30.

The coupled ring oscillator of the first embodiment is formed in the following manner. First,  $m \times n$  basic cells are laid out appropriately so as to form a loop. The phase-coupling elements 30' or the phase-coupling circuits 30 in adjacent basic cells are connected with each other to form a single phase-coupling loop 40. The input terminal of the inverter circuit 10 in one of any two basic cells existing (n-1) apart is connected with the output terminal of the inverter circuit 10 in the other basic cell, thereby forming m ring oscillators 20. If the layout is performed with m=5 and n=3, the coupled ring oscillator of the five-stage, three-set type shown in Figure 1, for example, is obtained.

Figure 8 shows the relation between the phase-coupling elements 30' and the

phase-coupling circuit 30 when the phase-coupling elements 30' are composed of inverter circuits. As shown in Figure 8, when two phase-coupling elements 30' are connected to each other, a single phase-coupling circuit 30 is formed. More specifically, in the adjacent phase-coupling elements 30', the input terminal of one inverter circuit 31 in one of the two phase-coupling elements 30' is connected with the output terminal of one inverter circuit 31 in the other phase-coupling element 30'. Where the phase-coupling elements 30' are composed of NMOS transistors, the gate of one NMOS transistor 32 in one of the adjacent phase-coupling elements 30' is connected with the gate of one NMOS transistor 32 in the other phase-coupling element 30'. In this manner,  $m \times n$  phase-coupling elements 30' are connected to form a loop, whereby the phase-coupling loop 40 is obtained in which the  $m \times n$  phase-coupling circuits 30 are connected into a loop.

Figures 9A-9D show exemplary circuit configurations of the basic cells in the coupled ring oscillator according to the second embodiment. Figures 9A and 9B show exemplary configurations of the basic cells in which the input terminal of an inverter circuit 10 is connected with a phase-coupling circuit 30. Figures 9C and 9D show exemplary configurations of the basic cells in which the output terminal of an inverter circuit 10 is connected with a phase-coupling circuit 30.

The coupled ring oscillator of the second embodiment is formed in the following manner. First,  $m \times n$  basic cells are laid out appropriately so as to form a loop. The phase-coupling circuits 30 in adjacent basic cells are connected with each other to form a single phase-coupling loop 40. Also, the input terminal of the inverter circuit 10 in one of any two basic cells existing (n-1) apart is connected with the output terminal of the inverter circuit 10 in the other basic cell, thereby forming m ring oscillators 20. If the layout is performed with m=5 and n=3, the coupled ring oscillator of the five-stage, three-set type shown in Figure 3, for example, is obtained.

(Exemplary configurations)

5

10

15

20

25

Exemplary configurations of coupled ring oscillators of a three-stage, three-set type formed according to the above layout methods will be shown.

Figures 10, 11 and 12 show exemplary configurations of a coupled ring oscillator according to the first embodiment. In the exemplary configuration shown in Figure 10, nine basic cells 50 are divided into four and five and the layout is performed so that the four basic cells 50 and the five basic cells 50 face each other. In the exemplary configuration shown in Figure 11, the layout is performed so that the basic cells 50 are located on four sides. In the exemplary configuration shown in Figure 12, nine basic cells 50 are divided into four and five and the layout is performed so that the four basic cells 50 and the five basic cells 50 face in the same direction. In each of the exemplary configurations, the basic cell shown in Figure 5A or 6A is used.

5

10

15

20

25

On the other hand, Figures 13, 14, and 15 show exemplary configurations of a coupled ring oscillator of the second embodiment. The configurations in Figures 13, 14, and 15 correspond to those shown in Figures 10, 11 and 12, respectively. In each of the exemplary configurations shown in Figures 13, 14, and 15, the basic cell shown in Figure 9A is used.

As shown in Figures 12 and 15, in the coupled ring oscillators according to the preferred embodiments, the ring oscillators 20 and the phase-coupling loop 40 do not necessarily have to be arranged in a nested pattern. In cases where the ring oscillators 20 and the phase-coupling loop 40 are laid out in a nested pattern, the phase-coupling loop 40 is placed innermost. This is because the number of stages in which the phase-coupling circuits 30 are connected in the phase-coupling loop 40 is greater than the number of stages in which the inverter circuits 10 are connected in each ring oscillator 20, which causes more delays in the phase-coupling loop 40. However, the operation speed of the phase-coupling loop 40 must be higher than that of the ring oscillators 20. Therefore, in order to reduce the delays as much as possible, the phase-coupling loop 40 is preferably placed innermost in the nest so that the wire length thereof is shortened.

# INDUSTRIAL APPLICABILITY

The inventive coupled ring oscillator generates highly accurate and fine phase information and is thus applicable, for example, to a high-resolution phase generating circuit such as a write strategy circuit for generating a write clock in an optical disk drive.

5

#### **CLAIMS**

1. A coupled ring oscillator comprising:

5

10

15

20

n ring oscillators each including m inverter circuits; and

a phase-coupling loop in which  $m \times n$  phase-coupling circuits, each of which couples signal phases at two points in a certain phase mode, are connected with each other to form a loop,

wherein connection points at which the inverter circuits are connected with each other and the connection points at which the phase-coupling circuits are connected with each other are connected bijectively; and

each of the inverter circuits is connected between two points that divide the phase-coupling circuits into two parts at a certain ratio.

2. The coupled ring oscillator of Claim 1, wherein the phase-coupling circuits each couple signal phases at two points in a reverse phase mode; and

each of the inverter circuits is connected between two points that divide the phase-coupling circuits into n phase-coupling circuits and  $n \times (m-1)$  phase-coupling circuits.

- 3. The coupled ring oscillator of Claim 2, wherein the phase-coupling circuits each include two inverter circuits and an input terminal and an output terminal of one of the inverter circuits are connected with an output terminal and an input terminal of the other inverter circuit, respectively.

- 4. The coupled ring oscillator of Claim 2, wherein the phase-coupling circuits each

include two MOS transistors of the same polarity and a gate and a drain of one of the MOS transistors are connected with a drain and a gate of the other MOS transistor, respectively.

5. The coupled ring oscillator of Claim 4, wherein the MOS transistors are NMOS transistors.

6. The coupled ring oscillator of Claim 1, wherein the phase-coupling circuits each couple signal phases at two points in a common mode; and

5

10

15

each of the inverter circuits is connected between two points that divide the phase-coupling circuits into  $n \times (m-1)/2$  phase-coupling circuits and  $n \times (m+1)/2$  phase-coupling circuits.

- 7. The coupled ring oscillator of Claim 6, wherein the phase-coupling loop forms two turns and is closed.

- 8. The coupled ring oscillator of Claim 6, wherein each of the phase-coupling circuits is a MOS transistor in which a source and a drain are used as input/output terminals and a predetermined voltage is applied to a gate.

- 9. The coupled ring oscillator of Claim 8, wherein the MOS transistor is an NMOS transistors, and

- a control voltage for an oscillation frequency of the ring oscillators is applied to a gate of the NMOS transistor.

- 10. The coupled ring oscillator of Claim 6, wherein the phase-coupling circuits are transfer gates.

- 25 11. The coupled ring oscillator of Claim 6, wherein the phase-coupling circuits are resistance elements.

12. The coupled ring oscillator of Claim 1, wherein the n ring oscillators and the phase-coupling loop are laid out in a nested pattern.

- 13. The coupled ring oscillator of Claim 1, wherein the phase-coupling loop is laidout to be innermost in a nested pattern.

- 14. A method for laying out a coupled ring oscillator, comprising the steps of:

- (a) connecting  $m \times n$  basic cells each including a phase-coupling element and a circuit element,

wherein the phase-coupling element corresponds to two connected half-circuits, each equivalent to half of a phase-coupling circuit for coupling two signal phases at two points in a reverse phase mode, at both ends of the phase-coupling circuit,

10

15

20

25

the circuit element includes an inverter circuit in which either an input terminal or an output terminal is connected to a connection point at which the two half-circuits are connected with each other, and

the  $m \times n$  basic cells are connected into a loop so that each phase-coupling circuit is formed between adjacent ones of the phase-coupling elements; and

- (b) connecting, in any two of the basic cells existing (n-1) apart, the input terminal of the inverter circuit in one of the two basic cells with the output terminal of the inverter circuit in the other basic cell.

- 15. The method of Claim 14, wherein each of the phase-coupling elements includes two inverter circuits as the two half-circuits, and input terminals of the two inverter circuits are connected with each other; and

the method further includes the step (c) of connecting, in adjacent two of the phase-coupling elements, the input terminal of one of the inverter circuits in one of the two phase-coupling elements with an output terminal of one of the inverter circuits in the other

phase-coupling element.

5

10

15

20

25

16. The method of Claim 15, wherein the input terminals of the two inverter circuits in each phase-coupling element are connected with the input terminal of the inverter circuit in each of the basic cells.

17. The method of Claim 14, wherein each of the phase-coupling elements includes two MOS transistors as the two half-circuits, and gates of the two MOS transistors are connected with each other; and

the method further includes the step (c) of connecting, in adjacent two of the phase-coupling elements, the gate of one of the MOS transistors in one of the two phase-coupling elements with a drain of one of the MOS transistors in the other phase-coupling element.

- 18. The method of Claim 17, wherein the gates of the two MOS transistors in each phase-coupling element are connected with the input terminal of the inverter circuit in each of the basic cells.

- 19. The method of Claim 17, wherein the MOS transistors are NMOS transistors.

20. A method for laying out a coupled ring oscillator, comprising the steps of:

(a) connecting  $m \times n$  basic cells each including a phase-coupling circuit for coupling two signal phases at two points in a certain phase mode and a circuit element,

wherein the circuit element includes an inverter circuit in which either an input terminal or an output terminal is connected to one end of the phase-coupling circuit, and

the  $m \times n$  basic cells are connected into a loop so that the phase-coupling circuits are connected with each other; and

(b) connecting, in any two of the basic cells existing (n-1) apart, the input terminal of the inverter circuit in one of the two basic cells with the output terminal of the inverter circuit in the other basic cell.

21. The method of Claim 20, wherein each of the phase-coupling circuits couples signal phases at two points in a reverse phase mode; and

in the step (a), the basic cells are connected so that adjacent ones of the phase-coupling circuits are connected with each other.

22. The method of Claim 20, wherein each of the phase-coupling circuits couples signal phases at two points in a common mode; and

in the step (a), the basic cells are connected so that alternate ones of the phase-coupling circuits are connected with each other.

- 23. The method of Claim 22, wherein each of the phase-coupling circuits is a MOS transistor in which a source and a drain are used as input/output terminals and a predetermined voltage is applied between a gate and the source or between the gate and the drain.

- 24. The method of Claim 22, wherein the phase-coupling circuits are transfer gates.

- 25. The method of Claim 22, wherein the phase-coupling circuits are resistance elements.

5

10

. 15

<sub>5</sub>20

1/11

FIG. 2A

FIG. 2B

F1G. 3

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 5D

FIG. 6A

FIG. 6B

FIG. 6C

FIG. 6D

6/11

FIG. 7

FIG. 8

FIG. 9A

FIG. 9B

FIG. 9C

FIG. 9D

FIG. 12

FIG. 13

### INTERNATIONAL SEARCH REPORT

International application No PCT/JP2006/310955

A. CLASSIFICATION OF SUBJECT MATTER INV. H03K3/03

According to International Patent Classification (IPC) or to both national classification and IPC

#### **B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols) H03K

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

#### EPO-Internal

| C. DOCUM  | ENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                             |                       |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                         | Relevant to claim No. |

| A         | US 5 717 362 A (J MANEATIS) 10 February 1998 (1998-02-10) column 2, line 34 - line 39 column 2, line 43 - line 53 column 4, line 1 - column 6, line 13; figures 4,5 column 6, line 35 - column 7, line 54; figures 7,8 column 9, line 58 - column 10, line 5; figure 10 column 14, line 35 - column 15, line 10; figure 19 | 1-25                  |

| A         | US 5 592 126 A (A BOUDEWIJJNS) 7 January 1997 (1997-01-07) column 4, line 34 - column 6, line 11; figures 1,2                                                                                                                                                                                                              | 1–25                  |

| Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents:  "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier document but published on or after the international filling date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filling date but later than the priority date claimed | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.  "&" document member of the same patent family |

| Date of the actual completion of the international search  6 September 2006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Date of mailing of the international search report  19/09/2006                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Name and mailing address of the ISA/  European Patent Office, P.B. 5818 Patentlaan 2  NL – 2280 HV Rijswijk  Tel. (+31–70) 340–2040, Tx. 31 651 epo nl,  Fax: (+31–70) 340–3016                                                                                                                                                                                                                                                                                                                                                                                                                   | Authorized officer Butler, Nigel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## INTERNATIONAL SEARCH REPORT

International application No

PCT/JP2006/310955

| C(Continua | tion). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                    | PC1/JP2006/310955     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category*  | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                            | Relevant to claim No. |

| A          | US 5 357 217 A (G MARCHESI)<br>18 October 1994 (1994-10-18)<br>column 4, line 66 - column 8, line 18;<br>figures 1,2                                                                                                                          | 1-25                  |

| A          | US 2004/263265 A1 (A ALLEN) 30 December 2004 (2004-12-30) paragraph [0021] - paragraph [0022] paragraph [0023] - paragraph [0026]; figures 1,2 paragraph [0028] - paragraph [0029]; figure 3 paragraph [0032] - paragraph [0036]; figures 4,5 | 1-25                  |

| A          | US 2004/012453 A1 (W DALLY)<br>22 January 2004 (2004-01-22)<br>figures 6,14,15                                                                                                                                                                | 1–25                  |

|            | US 6 025 756 A (S MIYABE) 15 February 2000 (2000-02-15) column 3, line 24 - column 4, line 50; figure 1                                                                                                                                       | 1-25                  |

|            |                                                                                                                                                                                                                                               |                       |

#### INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/JP2006/310955

| 10-02-1998<br>07-01-1997<br>18-10-1994 | US<br>NONE<br>DE | 5475344 A                                             | 12-12-19                                                               |

|----------------------------------------|------------------|-------------------------------------------------------|------------------------------------------------------------------------|

|                                        |                  |                                                       |                                                                        |

| 18-10-1994                             | DF               |                                                       |                                                                        |

|                                        | DE<br>EP<br>JP   | 69226627 D3<br>69226627 T2<br>0569658 A3<br>6152335 A | 2 24-12-19<br>1 18-11-19                                               |

| 30-12-2004                             | NONE             |                                                       |                                                                        |

| 22-01-2004                             | US               | 2002113660 A                                          | 1 22-08-20                                                             |

| 15-02-2000                             | JP<br>JP<br>TW   | 3613779 B2<br>11068522 A<br>384566 B                  | 09-03-19                                                               |

|                                        | 22-01-2004       | 22-01-2004 US<br>15-02-2000 JP<br>JP                  | 22-01-2004 US 2002113660 A<br>15-02-2000 JP 3613779 B<br>JP 11068522 A |