(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4110926号 (P4110926)

(45) 発行日 平成20年7月2日(2008.7.2)

(24) 登録日 平成20年4月18日 (2008.4.18)

(51) Int. Cl.

HO2M 3/155 HO2M (2006, 01) 3/155 HO2M 3/155

FL

請求項の数 13 (全 35 頁)

特願2002-319634 (P2002-319634) (21) 出願番号 (22) 出願日 平成14年11月1日(2002.11.1) (65) 公開番号 特開2004-96982 (P2004-96982A) 平成16年3月25日 (2004.3.25) (43) 公開日 平成17年5月17日 (2005.5.17) 審査請求日

特願2002-202090 (P2002-202090) (31) 優先権主張番号

平成14年7月11日 (2002.7.11) (32) 優先日

(33) 優先権主張国 日本国(JP) ||(73)特許権者 503361248

富士電機デバイステクノロジー株式会社 東京都品川区大崎一丁目11番2号

||(74)代理人 100092152

弁理士 服部 毅巖

||(74)代理人 100088339

弁理士 篠部 正治

Н

В

(72)発明者 吉田 豊

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

審査官 安池 一貴

最終頁に続く

(54) 【発明の名称】 DC-DCコンバータ

## (57)【特許請求の範囲】

## 【請求項1】

半導体スイッチをオンオフして、負荷に対して所定の電圧レベルに変換された直流電圧を 供給するDC・DCコンバータにおいて、

少なくとも第1のフィードバック制御方式と第2のフィードバック制御方式とのいずれか に切替え可能に構成され、前記負荷を流れる負荷電流が所定値を越えて小さくなる領域に おいては前記第2のフィードバック制御方式を選択するとともに、前記負荷に供給される 電圧レベルが変化するときは前記負荷電流の大きさにかかわらず前記第1のフィードバッ ク制御方式を選択することを特徴とするDC - DCコンバータ。

## 【請求項2】

前記第1のフィードバック制御方式をパルス幅変調(PWM)制御方式、第2のフィード バック制御方式をパルス周波数(PFM)制御方式とすることを特徴とする請求項1記載 のDC - DCコンバータ。

## 【請求項3】

半導体スイッチをオンオフして、負荷に対して所定の電圧レベルに変換された直流電圧を 供給するDC・DCコンバータにおいて、

前記半導体スイッチのスイッチング周波数を規定する三角波信号を生成する発振手段と、 基準電圧として指令される出力電圧制御信号と前記負荷に供給した電圧レベルに応じてフ ィードバックされる検出電圧との差電圧を増幅する増幅手段と、

PWM制御方式、あるいはPFM制御方式のいずれかのフィードバック制御方式に切り替

えて前記発振手段の三角波信号と前記増幅手段の差電圧とを比較するとともに、前記半導体スイッチをオンオフする駆動用パルス信号のパルス幅を変調するパルス幅変調制御手段と、

前記パルス幅変調制御手段のフィードバック制御方式を切り替える際に、前記負荷に流れる負荷電流が所定値を越えて小さくなる領域においては前記PFM制御方式を選択するとともに、前記負荷に供給される電圧レベルが変化するときは前記負荷電流の大きさにかかわらず前記PWM制御方式を選択する制御方式選択手段と、

を備えることを特徴とするDC-DCコンバータ。

#### 【請求項4】

前記制御方式選択手段は、前記負荷電流の大きさを判定する負荷電流判定回路と、前記負荷に供給される電圧レベルの変化を検出する電圧変化検出回路とを備えることを特徴とする請求項3記載のDC-DCコンバータ。

#### 【請求項5】

前記電圧変化検出回路は、前記基準電圧として指令される出力電圧制御信号の変化量、及び前記負荷に実際に供給された出力電圧信号の変化量に基づいて、前記負荷に供給される電圧レベルの変化を検出することを特徴とする請求項4記載のDC-DCコンバータ。

## 【請求項6】

前記電圧変化検出回路は、<u>前記増幅手段の入出力端子間に設けた位相補償用抵抗に所定値を超えて電流が流れているか否かに応じて</u>、前記負荷に供給される電圧レベルの変化を検出することを特徴とする請求項4記載のDC-DCコンバータ。

#### 【請求項7】

前記増幅手段は、動作点が固定の第1のアナログ増幅回路と、動作点が固定の第2のアナログ増幅回路とのカスケード接続により構成され、かつ、前記第1のアナログ増幅回路を 差動増幅回路とすることを特徴とする請求項3記載のDC-DCコンバータ。

#### 【請求項8】

前記発振手段は、前記制御方式選択手段により前記 P F M 制御方式が選択されている場合には、前記増幅手段で増幅された差電圧と第 1 の基準電圧との差に比例する発振周波数の 三角波信号を生成することを特徴とする請求項 3 記載の D C - D C コンバータ。

## 【請求項9】

前記発振手段は、前記制御方式選択手段により前記 P F M 制御方式が選択されている場合には、前記増幅手段で増幅された差電圧と同電位に設定されるノードと、第1の基準電圧に設定されるノードとを接続する第1の抵抗回路に流れる電流の大きさに比例する発振周波数の三角波信号を生成し、

前記制御方式選択手段により前記PWM制御方式が選択されている場合には、第2の基準電圧と接地電位とを接続する第2の抵抗回路に流れる電流の大きさに比例する発振周波数の三角波信号を生成することを特徴とする請求項3記載のDC-DCコンバータ。

#### 【請求項10】

前記発振手段は、生成される三角波信号の下限値を規定するための監視回路を備えていることを特徴とする請求項9記載のDC-DCコンバータ。

#### 【請求項11】

前記発振手段では、前記第1の基準電圧を前記監視回路における三角波信号の下限値に等 しい値としたことを特徴とする請求項10記載のDC-DCコンバータ。

## 【請求項12】

前記発振手段では、前記第1の基準電圧を前記監視回路における三角波信号の下限値より 大きい値とし、

PWM制御時における前記エラーアンプ出力信号が前記第1の基準電圧と一致したときの出力電圧信号の大きさを、前記出力電圧信号の下限電圧値とした

ことを特徴とする請求項10記載のDC-DCコンバータ。

#### 【請求項13】

前記発振手段では、前記第1の基準電圧が前記監視回路における三角波信号の下限値より

10

20

30

30

40

小さい値とし、

PFM制御時における前記エラーアンプ出力信号が前記三角波信号の下限値と一致したときの発振周波数の大きさを、前記発振周波数の下限周波数値とした

(3)

ことを特徴とする請求項10記載のDC-DCコンバータ。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

この発明は、半導体スイッチをオンオフして、所定の電圧レベルに変換された直流電圧を 負荷に供給するDC - DCコンバータに関し、特に、出力電圧が変化する場合でも半導体 スイッチのスイッチング損失を低減するようにしたDC - DCコンバータに関する。

[00002]

【従来の技術】

半導体スイッチをオンオフして直流電圧の変換を行うDC-DCコンバータは、負荷に供給される出力電圧を一定の目標値に保つように、半導体スイッチをオンオフするフィードバック制御を行っている。この場合に、負荷電流が定格電流の20~30%以下になってくると、半導体スイッチのオンオフによる電圧変換効率が極端に低下してくる。そこで、軽負荷においても電圧変換効率を低下させないためには、負荷電流の減少に対応してスイッチング周波数を低下させて、スイッチングに伴う損失を低減する方法が知られている。

[0003]

従来から、DC-DCコンバータにおけるフィードバック制御方式には、PWM(Pulse Width Modulation)やPFM(Pulse Frequency Modulation)などの方式が知られている。また、例えば、特開平11-155281、特開2001-157446などの公報には、負荷電流の減少に伴いスイッチング周波数を下げることで、広い負荷領域において高い効率を維持するPFM制御方式をPWM制御方式に併用するDC-DCコンバータの発明が示されている。

[0004]

最初に、DC・DCコンバータのPWM制御について説明する。

図29は、PWM制御方式の降圧DC-DCコンバータの一例を示す回路図である。

[0005]

このDC-DCコンバータは、入力電源電圧Vinを所定の電圧レベルに変換して、負荷LOADに供給するものであって、エラーアンプAmp1、位相補償用コンデンサC1、位相補償用抵抗R1、帰還抵抗R2,R3、発振回路OSC2、パルス幅変調用コンパレータCmp1、出力用のPchトランジスタ(MOSFET)P1、Nchトランジスタ(MOSFET)N1、チョークコイルL、ドライブ回路Dr1,Dr2、及び平滑コンデンサCoutから構成されている。

[0006]

PWM制御方式の降圧DC-DCコンバータは、出力電圧信号Voutを定める出力電圧制御信号Vcontに対して、DC-DCコンバータの出力電圧信号Voutが抵抗分圧されたフィードバック信号Vfbを等しくするように動作する。例えば出力電圧信号Voutの分圧を行う帰還抵抗R2とR3の抵抗値が等しい場合には、出力電圧信号Voutは出力電圧制御信号Vcontの2倍の電圧値となる。

[0007]

エラーアンプ(オペアンプ) Amp 1 には、出力電圧制御信号 V c o n t がプラス入力端子に接続され、フィードバック信号 V f b がマイナス入力端子に供給されている。また、エラーアンプ Amp 1 は位相補償用の抵抗 R 1 とコンデンサ C 1 を使って積分回路を形成している。エラーアンプ出力信号 V e r r と発振回路 O S C 2 から出力される三角波信号 V o s c 2 は、それぞれパルス幅変調用コンパレータ C m p 1 に入力される。 P c h トランジスタ P 1 は、そのソース、及びドレインがそれぞれ入力電源電圧 V i n とチョークコイル L とに接続され、ドライブ回路 D r 1 によりゲートが駆動される。 N c h トランジス

10

20

30

40

20

30

40

50

タN1は接地電位(GND)とチョークコイル L とに接続され、ドライブ回路 Dr2によりゲートが駆動される。チョークコイル L と平滑コンデンサ Coutにより直流化された出力電圧信号 Voutは、負荷 LOADに供給される。

#### [00008]

つぎに、DC-DCコンバータのPWM制御動作について説明する。

パルス幅変調用コンパレータCmp1には、予め定められた周波数で発振する発振回路OSC2から出力される三角波信号Vosc2と、エラーアンプ出力信号Verrとが入力され、パルス幅変調信号Vcmpがドライブ回路Dr1,Dr2に対して出力される。パルス幅変調信号VcmpがLowのときPchトランジスタP1がオンし、HighのときNchトランジスタN1がオンする。PchトランジスタP1とNchトランジスタN1のゲートが同時にオンして入力電源電圧Vinから接地電位GNDに向けて貫通電流が流れないように、それぞれドライブ回路Dr1,Dr2ではタイミング調整を行っている

. 【0009】

PchトランジスタP1のオン期間には、入力電源電圧VinからチョークコイルLを介して平滑コンデンサCoutに電荷が流れ込み、チョークコイルLを流れる電流値はオン期間に増加する。一方、NchトランジスタN1のオン期間には、接地電位GNDから平滑コンデンサCoutに電荷を送り込み、この期間にチョークコイルLを流れる電流値は減少する。出力電圧信号Voutを帰還抵抗R2,R3で分圧して生成したフィードバック信号Vfbは、出力電圧制御信号VcontとともにエラーアンプAmp1に入力されることによって、Vfb=Vcontとなるようフィードバック制御が働く。

[0010]

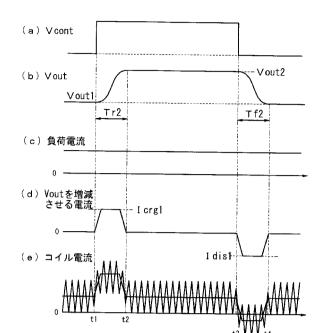

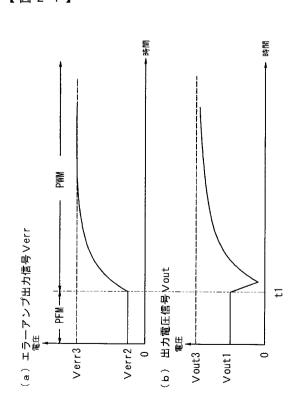

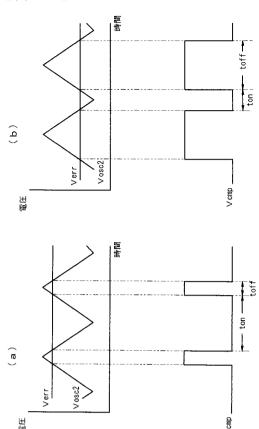

このフィードバック制御について、図30に示す動作波形を用いて具体的に説明する。図30(a)(b)は、降圧DC-DCコンバータにおけるPWM制御の動作波形を示す波形図である。

[0011]

Vout/Vin=ton/(ton+toff)

の関係がある。以下では、この{ton/(ton+toff)}をデューティ比という

[0012]

ここで、エラーアンプ出力信号Verrが図30(a)の状態から同図(b)に示すように低下する場合を考える。負荷LOADに流れる電流(負荷電流)が変動して出力電圧信号Voutが上昇した場合、出力電圧信号Voutを抵抗分圧しているフィードバック信号Vfbも上昇する。その結果、エラーアンプ出力信号Verrは低下するので、PchトランジスタP1のオン期間tonが減り、NchトランジスタN1のオン期間toffが増えて、出力電圧信号Voutの電圧値を下げようとする。このようにDC-DCコンバータにおけるフィードバック制御が働くために、負荷LOADに流れる電流が変化しても出力電圧信号Voutが一定に保たれることになる。

[0013]

つぎに、PFM制御方式について説明する。

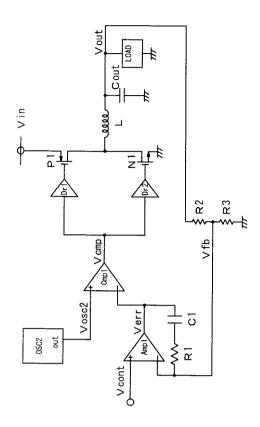

図31は、PFM制御方式のDC-DCコンバータの一例を示す回路図である。このDC-DCコンバータは、エラーアンプAmp1、位相補償用コンデンサC1、位相補償用抵抗R1、帰還抵抗R2,R3、発振回路OSC3、パルス幅変調用コンパレータCmp1、ワンショット回路Oneshot、出力用のPchトランジスタ(MOSFET)P1、ダイオードD1、チョークコイルL、ドライブ回路Dr1、及び平滑コンデンサCoutから構成されている。

## [0014]

図29に示した回路と同様に、DC-DCコンバータの出力電圧信号Voutの抵抗分圧

されたフィードバック信号 V f b が、外部から与えられる出力電圧制御信号 V c o n t に対して等しくなるように動作する。例えば出力電圧信号 V o u t の分圧を行う帰還抵抗 R 2 と R 3 の抵抗値が等しい場合には、出力電圧信号 V o u t は出力電圧制御信号 V c o n t の 2 倍の電圧値となる。

[0015]

エラーアンプAmp1には、出力電圧制御信号Vcontがプラス入力端子に接続され、フィードバック信号Vfbがマイナス入力端子に接続されている。また、エラーアンプA mp1は位相補償用の抵抗R1とコンデンサC1を用いた積分回路を形成している。エラーアンプ出力信号Verrと発振回路OSC3から出力される三角波信号Vosc3は、それぞれパルス幅変調用コンパレータCmp1に入力される。また、エラーアンプ出力信号Verrは発振回路OSC3にも入力されている。PchトランジスタP1のソース、グロ路Dr1によりゲートを駆動される。PchトランジスタP1のゲートには、ブショット回路Oneshotは、パルス幅変調信号Vcmpの立下り変化点をトリガーに対ット回路Oneshotは、パルス幅である。還流ダイオードD1は接地での口とチョークコイルLとの間に接続される。チョークコイルLと平滑コンデンサCoutにより直流化された出力電圧信号Voutは、負荷LOADに供給される。

[0016]

出力電圧制御信号 V c o n t の電圧値を上げた場合は、エラーアンプ出力信号 V e r r が上昇し、発振回路 O S C 3 から出力される三角波信号 V o s c 3 の発振周波数は上昇する。この結果、P c h トランジスタ P 1 のスイッチング周波数が増えるため、チョークコイル L を通って平滑コンデンサ C o u t に流れ込む電流は増え、出力電圧信号 V o u t は上昇する。このように、P F M 制御方式においても、出力電圧制御信号 V c o n t の電圧値に応じて出力電圧信号 V o u t の大きさがフィードバック制御される。

[0017]

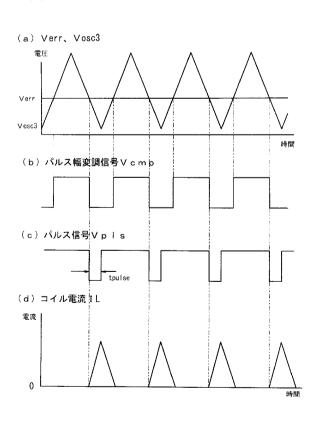

図32は、DC-DCコンバータにおけるPFM制御の動作波形を示す波形図である。 同図(a)には、パルス幅変調用コンパレータCmp1に入力するエラーアンプ出力信号 Verrと三角波信号Vosc3を示している。発振回路OSC3からはエラーアンプ出 力信号Verrに応じた周波数の三角波信号Vosc3が入力される。

[0018]

同図(b)には、パルス幅変調信号Vcmpを示している。パルス幅変調用コンパレータ Cmp1では、入力したエラーアンプ出力信号Verrと三角波信号Vosc3とが比較 され、パルス幅変調信号Vcmpをワンショット回路Oneshotに出力する。

[0019]

同図(c)には、ワンショット回路Oneshotから出力されるパルス信号Vplsを示している。パルス信号Vplsは、パルス幅変調信号Vcmpの立下り信号をトリガーにして、一定の時間幅tpulseのパルスとしてドライブ回路Dr1に出力される。このパルス信号VplsがLowの期間に、PchトランジスタP1はドライブ回路Dr1によりオンされるため、チョークコイルLには入力電源電圧VinからPchトランジスタP1を通って電流が流れ込む。

[0020]

同図(d)には、チョークコイルLに流れる電流波形を示している。このコイル電流ILは、PchトランジスタP1がオンした後、0から(Vin-Vout)/Lの時間に対する傾きで電流値が増加する。PchトランジスタP1がオフした後、チョークコイルLには接地電位GNDから還流ダイオードD1を通って電流が流れる。このときの電流値はVout/Lの時間に対する傾きで減少する。

[0021]

出力電圧信号 Voutを帰還抵抗 R 2 , R 3 で分圧することにより生成したフィードバック信号 Vf bは、出力電圧制御信号 Vcontとともにエラーアンプ Amp 1 に入力され

10

20

30

40

る。その結果、Vfb=Vcontとなるようフィードバック制御が働く。

## [0022]

出力電圧信号 Voutは、実際には、平滑コンデンサ Coutから負荷 LOADに流れ出す電流と、チョークコイル Lを介して平滑コンデンサ Coutに流れ込む電流の和によって決まるため、両者が等しくなるようフィードバック制御が行われている。すなわち、負荷電流が減少した場合には出力電圧信号 Voutは上昇し、出力電圧信号 Voutを抵抗分圧しているフィードバック信号 Vfbも上昇する。そのためエラーアンプ出力信号 Verが低下して、三角波信号 Vosc3の発振周波数を低下させる。この結果、Pchトランジスタ P1のスイッチング周波数が減るため、チョークコイル Lを通って平滑コンデンサ Coutに流れ込む電流は減る。

10

## [0023]

このようにして、 P F M 制御方式の D C - D C コンバータにおいてもフィードバック制御が働き、負荷電流が変化しても出力電圧信号 V o u t を一定に保つことができる。

## [0024]

一方、近年になって出力電圧を高速に変化させながら D C - D C コンバータを使用したいという要望が多くなっている。従来の D C - D C コンバータでは、固定の基準電圧をもとに一定の出力電圧を生成するものであったが、固定した基準電圧に代えて、例えば変化する外部入力電圧を基準電圧として与え、この基準電圧に D C - D C コンバータの出力電圧を追従して変化させるという回路方式が望まれている。

20

## [0025]

例えば、W - C D M A 方式の携帯電話機に使われるパワーアンプにおいては、携帯電話機に内蔵した電源の消費電力を抑える必要があった。そこで、携帯電話機と電波の送受信を行う基地局との距離が近いときに送信電力を小さく抑えるなど、パワーアンプへ供給する電源電圧も、必要とされる送信電力の大きさに応じて変えるようにしている。

#### [0026]

こうした広範囲の入力電圧変動、及び負荷変動に対応して出力電圧を安定して制御可能にするために、特許文献 1 には、広範囲の入力電圧変動及び負荷変動に対して一次側駆動回路のスイッチを時比率変調方式及び周波数変調方式に切り替えるようにしたコンバータの発明が開示されている。

[0027]

30

また、図29のエラーアンプAmp1、抵抗R1、コンデンサC1で構成される積分回路については、Vcontがステップ状に変動するとそれがエラーアンプAmp1の出力に直接影響してオーバーシュートを生じさせることが特許文献2に示されている。

[0028]

#### 【特許文献1】

特開2001-258245号公報(段落番号[0008]~[0011]、図1)

#### 【特許文献2】

特開2002-78326号公報(段落番号[0004]~[0005]、図11、図1 2)

[0029]

40

## 【発明が解決しようとする課題】

このように、PWM/PFM切替え機能を有するDC-DCコンバータでは、一般に幅広い負荷領域で高効率を維持しながら、出力電圧信号Voutを一定に保つことができることが知られている。ところが、軽負荷条件下において基準電圧として入力される出力電圧制御信号Vcontが急激に変化する場合があって、DC-DCコンバータを一律にPFM制御によって動作させると、こうした変化に対する出力電圧信号Voutの応答性が悪くなる。

#### [0030]

この出力電圧信号Voutの応答性について、さらに説明する。

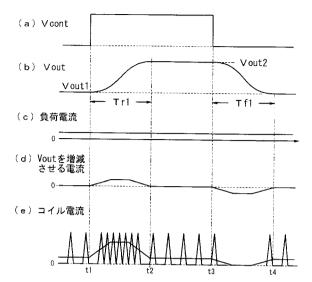

図33は、PFM制御において出力電圧信号Voutが変化する様子を示す信号波形図で

ある。同図(a)に示すように、出力電圧制御信号Vcontを時刻t1で上げ、時刻t3で下げる。このような出力電圧制御信号Vcontの変動に伴って、出力電圧信号Voutも電位Vout1から電位Vout2まで、時間Tr1をかけて上昇し、電位Vout2から電位Vout1まで、時間Tf1をかけて下降する(同図(b))。平滑コンデンサCoutにより形成された出力容量に対する電流量は、出力電圧信号Voutの増減に伴い平滑コンデンサCoutの電荷が増減するための電流と、負荷電流との和である。ここでは、説明を簡単化するために、同図(c)に示すように負荷電流は出力電圧信号Voutの大きさにかかわらず一定とする。また、同図(d)に示すように、平滑コンデンサCoutの電荷を増減するため電流の流れ込みと吐き出しが生じる。

#### [0031]

ところが、PFM制御の場合は図33(e)のコイル電流波形に示すように、電流値の増減をスイッチング周波数の増減で制御しているために、PWM制御とは異なり、急激な変化には対応できないという問題があった。

## [0032]

また、上述したW - C D M A 方式の携帯電話機では、電源電圧の変化時間として数 1 0 μ s が要求されている。しかし、電圧が下降するタイミング(時刻 t 3 から時刻 t 4 )には、マイナス方向に電流が流せないため負荷 L O A D に電流を流すことでしか平滑コンデンサ C o u t の電荷を吐き出す手段がなく、負荷電流が小さい場合には電位 V o u t 2 から電位 V o u t 1 まで出力電圧信号 V o u t を低減するために必要な時間 T f 1 が非常に長くなって、こうした要求に対応できないという問題があった。

#### [0033]

この発明の第1の目的は、広い負荷領域において高効率を維持すると同時に、軽負荷条件 下でも出力電圧信号の応答性を低下させないDC-DCコンバータを提供することにある

#### [0034]

この発明の第 2 の目的は、出力電圧制御信号にステップ状の変動があっても、出力電圧信号にオーバーシュートが生じないようにした D C - D C コンバータを提供することにある

## [0035]

この発明の第3の目的は、PWM / PFM 切替え時に発生するアンダーシュート、オーバーシュートを抑制して、その絶対値を小さくするとともに、継続時間の短縮を可能としたDC-DCコンバータを提供することにある。

#### [0036]

## 【課題を解決するための手段】

上記第1の目的を達成するために、半導体スイッチをオンオフして、負荷に対して所定の電圧レベルに変換された直流電圧を供給するDC-DCコンバータが提供される。このDC-DCコンバータは、少なくとも第1のフィードバック制御方式と第2のフィードバック制御方式とのいずれかに切替え可能に構成され、前記負荷を流れる負荷電流が所定値を越えて小さくなる領域においては前記第2のフィードバック制御方式を選択するとともに、前記負荷に供給される電圧レベルが変化するときは前記負荷電流の大きさにかかわらず前記第1のフィードバック制御方式を選択するものである。

#### [0037]

この発明の D C - D C コンバータでは、出力電圧が変化するときは負荷状態にかかわらず P W M 制御を行わせることで、出力容量の充放電電流を短期間で増減でき、出力電圧の遷移時間を短縮できる。

# [0038]

また、請求項3の発明では、半導体スイッチをオンオフして、負荷に対して所定の電圧レベルに変換された直流電圧を供給するDC-DCコンバータにおいて、前記半導体スイッチのスイッチング周波数を規定する三角波信号を生成する発振手段と、基準電圧として指令される出力電圧制御信号と前記負荷に供給した電圧レベルに応じてフィードバックされ

10

20

30

40

る検出電圧との差電圧を増幅する増幅手段と、PWM制御方式、あるいはPFM制御方式のいずれかのフィードバック制御方式に切り替えて前記発振手段の三角波信号と前記増幅手段の差電圧とを比較するとともに、前記半導体スイッチをオンオフする駆動用パルス信号のパルス幅を変調するパルス幅変調制御手段と、前記パルス幅変調制御手段のフィードバック制御方式を切り替える際に、前記負荷に流れる負荷電流が所定値を越えて小さくなる領域においては前記PFM制御方式を選択するとともに、前記負荷に供給される電圧レベルが変化するときは前記負荷電流の大きさにかかわらず前記PWM制御方式を選択する制御方式選択手段と、を備えることを特徴とする。

## [0039]

上記請求項3の発明においては、前記増幅手段は、動作点が固定の第1のアナログ増幅回路と、動作点が固定の第2のアナログ増幅回路とのカスケード接続により構成され、かつ、前記第1のアナログ増幅回路を差動増幅回路とすることによって、上記第2の目的を達成できる。

## [0040]

さらに、上記請求項3の発明においては、前記発振手段は、前記制御方式選択手段により前記PFM制御方式が選択されている場合には、前記増幅手段で増幅された差電圧と同電位に設定されるノードと、前記第1の基準電圧に設定されるノードとを接続する第1の抵抗回路に流れる電流の大きさに比例する発振周波数の三角波信号を生成し、前記制御方式選択手段により前記PWM制御方式が選択されている場合には、第2の基準電圧と接地電位とを接続する第2の抵抗回路に流れる電流の大きさに比例する発振周波数の三角波信号を生成することによって、上記第3の目的を達成できる(請求項9の発明)。

#### [0041]

#### 【発明の実施の形態】

以下、この発明の実施の形態について、図面を参照して説明する。

#### (第1の実施の形態)

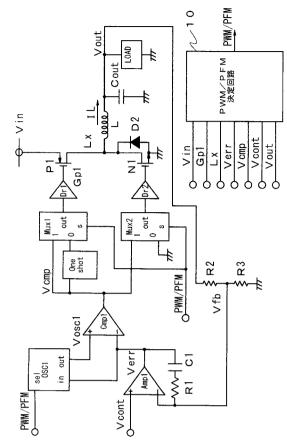

図1は、この発明のDC-DCコンバータの一例を示す回路図である。

#### [0042]

このDC-DCコンバータは、入力電源電圧Vinを所定の電圧レベルに変換して、負荷LOADに供給するものであって、エラーアンプ(オペアンプ)Amp1、位相補償用コンデンサC1、位相補償用抵抗R1、帰還抵抗R2,R3、発振回路OSC1、パルス幅変調用コンパレータCmp1、ワンショット回路Oneshot、マルチプレクサ回路Mux1,Mux2、ドライブ回路Dr1,Dr2、出力用のPchトランジスタ(MOSFET)P1、Nchトランジスタ(MOSFET)N1、チョークコイルL、ダイオードD2、平滑コンデンサCout、及びPWM/PFM決定回路10から構成されている

#### [0043]

PWM/PFM決定回路10は、入力電源電圧Vin、ドライブ回路Dr1から出力されるゲート信号Gp1、電圧信号Lx、エラーアンプ出力信号Verr、パルス幅変調信号Vcmp、出力電圧制御信号Vcont、及び出力電圧信号Voutが供給され、制御方式を切り替えるための切替え信号PWM/PFMを出力するものである。

## [0044]

エラーアンプAmp1には、出力電圧制御信号 V c o n t がプラス入力端子に接続され、出力電圧信号 V o u t を抵抗 R 2 , R 3 で分圧して生成したフィードバック信号 V f b がマイナス入力端子に接続されている。エラーアンプAmp1は位相補償用抵抗 R 1 と位相補償用コンデンサ C 1 を使って積分回路が形成される。エラーアンプAmp1からは、エラーアンプ出力信号 V e r r がパルス幅変調用コンパレータ C m p 1 のマイナス入力端子と発振回路 O S C 1 の入力端子に供給されている。また、発振回路 O S C 1 から出力される三角波信号 V o s c 1 は、パルス幅変調用コンパレータ C m p 1 のプラス入力端子に入力される。

## [0045]

10

20

30

パルス幅変調用コンパレータ Cmp10のパルス幅変調信号 Vcmpは、ワンショット回路 Oneshot、及びマルチプレクサ回路 Mux1,Mux20入力端子「1」に供給される。また、ワンショット回路 Oneshot の出力はマルチプレクサ回路 Mux10入力端子「0」に接続される。さらに、マルチプレクサ回路 Mux20入力端子「0」は接地されている。マルチプレクサ回路 Mux1,Mux20出力端子「0UT」は、それぞれドライブ回路 Dr1とドライブ回路 Dr2を介して Pch トランジスタ P1と Nch Nch

## [0046]

出力用のPchトランジスタP1のソース、及びドレインはそれぞれ入力電源電圧VinとチョークコイルLとに接続され、ドライブ回路Dr1によりゲートを駆動される。NchトランジスタN1は接地電位GNDとチョークコイルLとに接続され、ドライブ回路Dr2によりゲートを駆動される。チョークコイルLと平滑コンデンサCoutにより直流化された出力電圧信号Voutは負荷LOADに供給され、また抵抗分圧されたフィードバック信号Vfbを生成する。発振回路OSC1にはエラーアンプ出力信号Verrとともに、PWM/PFMが入力され、この切替え信号PWM/PFMが入力され、この切替え信号PWM/PFMのHigh、Lowに応じて発振動作モードを異ならせている。また、ドライブ回路Dr1への入力信号は、切替え信号PWM/PFMのHigh、Lowに応じてパルス幅変調信号Vcmp、あるいはワンショット回路Oneshotのいずれかに切り替えられる。ドライブ回路Dr2への入力信号は、切替え信号PWM/PFMのHigh、Lowに応じてパルス幅変調信号Vcmp、あるいは接地電位GNDに切り替えられる。

#### [0047]

このDC-DCコンバータは、第1のフィードバック制御方式であるPWM制御と第2のフィードバック制御方式であるPFM制御とのいずれかに切替え可能に構成され、負荷LOADを流れる負荷電流が所定値を越えて小さくなる領域においてはPFM制御を選択するとともに、負荷LOADに供給される電圧レベルが変化するときは負荷電流の大きさにかかわらずPWM制御を選択するように構成されている。ここでは、PWM制御とPFM制御とでは回路動作が異なるために、DC-DCコンバータは切替え信号PWM/PFMが必要となる。そこで、PWM/PFM決定回路10で生成された切替え信号PWM/PFMを使って、発振回路OSC1の動作モードとマルチプレクサ回路Mux1,Mux2の入力を切り替えている。

## [0048]

なお、 PWM 制御動作のとき切替え信号 PWM/PFM をHigh とする。また、図 1 において、マルチプレクサ回路  $Mu \times 1$  ,  $Mu \times 2$  は、それぞれ同じ回路構成である。

## [0049]

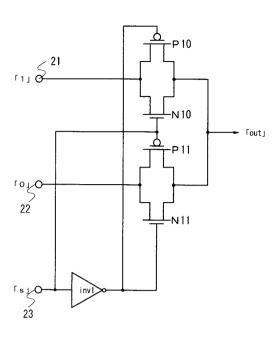

図 2 は、図 1 の D C - D C コンバータにおけるマルチプレクサ回路の具体的な構成例を示す回路図である。

図2において、入力端子21には第1の入力信号「1」が、入力端子22には第2の入力信号「0」が供給される。P10,P11はPchトランジスタ(MOSFET)であり、N10,N11はNchトランジスタ(MOSFET)であり、これらは2組のアナログスイッチを構成している。入力端子23は、それぞれNchトランジスタN10とPchトランジスタP11のゲートに接続され、そこにはセット信号「s」が供給される。また、入力端子23は、インバータ回路inv1を介してそれぞれNchトランジスタN11とPchトランジスタP10のゲートに接続されている。

#### [0050]

ここで、図2に示すマルチプレクサ回路では、入力端子23に供給されるセット信号「s」がHighのとき、NchトランジスタN10とPchトランジスタP10が導通し、入力端子21に供給された入力信号「1」が出力信号「out」として出力される。その

10

20

30

40

20

30

40

50

際、NchトランジスタN11とPchトランジスタP11がオフすることで入力端子22の入力信号「0」は遮断される。反対に、セット信号「s」がLowのときには、入力端子22に供給された入力信号「0」が出力信号「out」として出力される。

#### [0051]

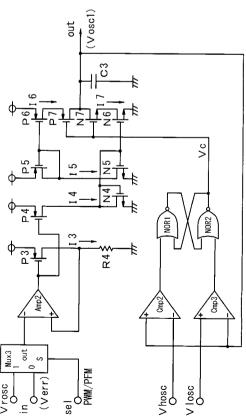

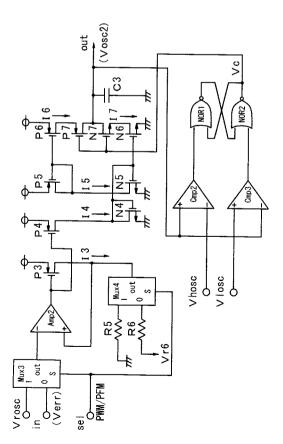

図 3 は、図 1 の D C - D C コンバータにおける発振回路の具体的な構成例を示す回路図である。

この発振回路OSC1は、オペアンプAmp2、マルチプレクサ回路Mux3、コンパレータCmp2,Cmp3、Pchトランジスタ(MOSFET)P3~P7、Nchトランジスタ(MOSFET)N4~N7、抵抗R4、ノアゲートNOR1,NOR2、及びコンデンサC3から構成されている。

## [0052]

図3において、この発振回路OSC1を構成するオペアンプAmp2のマイナス入力には、マルチプレクサ回路Mux3からセレクト端子Sへの入力信号電圧に応じて、内部基準電圧Vrosc、あるいは入力端子inからのエラーアンプ出力信号Verrのいずれか一方が印加される。マルチプレクサ回路Mux3は、図2で説明したマルチプレクサ回路Mux1,Mux2と同じ機能をもつ。このマルチプレクサ回路Mux3では、セレクト端子Sに供給される切替え信号PWM/PFMがPWMモードであるときは内部基準電圧Vroscを出力し、PFMモードのときはエラーアンプ出力信号Verrを出力する。

#### [0053]

オペアンプAmp2とPchトランジスタP3、抵抗R4の構成により、PWMモードのときに抵抗R4に流れる電流I3の大きさはVrosc/R4となり、PFMモードのときにはVerr/R4となる。また、PchトランジスタP4はPchトランジスタP3とゲートへの入力が共通であり、ゲート・ソース間電圧が等しいため、PchトランジスタP4のドレイン電流I4は抵抗R4に流れる電流I3にPchトランジスタP4とPchトランジスタP3のゲート幅/ゲート長の比をかけた値になる。このことは、他のトランジスタを流れる電流I5,I6,I7に対しても同様に成り立つ。Pchトランジスタトフのゲートには、RSフリップフロップを構成するノアゲートNOR2に接続され、その出力信号Vcが供給される。RSフリップフロップの出力信号VcがHighのときNchトランジスタNフがオン、PchトランジスタPフがオフのためコンデンサC3からNchトランジスタNフ,N6の経路で電流I7が放電される。PchトランジスタPフがオンのため、コンデンサC3にPchトランジスタP6,Pフの経路で電流I6が充電される。

## [0054]

コンデンサ C 3 の充電電圧として出力される三角波信号 V o s c 1 は、 V h o s c > V l o s c の関係にある内部基準電圧をそれぞれ入力する 2 つのコンパレータ C m p 2 , C m p 3 によって、その電位が監視されている。すなわち、 R S フリップフロップの出力信号 V c が L o w のとき三角波信号 V o s c 1 は電位が上がり、それが内部基準電圧 V h o s c を超えた時点でコンパレータ C m p 2 の出力が H i g h になって出力信号 V c が H i g h に変わる。その後、三角波信号 V o s c 1 は電位が下がり、それが内部基準電圧 V l o s c より低くなった時点でコンパレータ C m p 3 の出力が H i g h になって出力信号 V c は再び L o w になる。

## [0055]

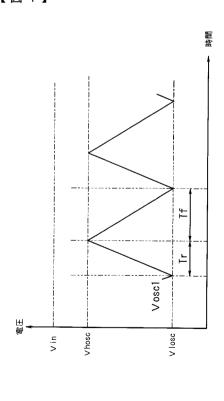

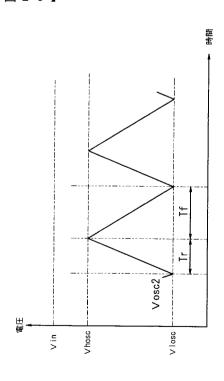

図4に、三角波信号Vosc1の信号波形を示す。

この三角波信号 Vosc1は、下限値を Vlosc、上限値を Vhoscとするとき、その電位上昇の周期 Trは、

$Tr = C3 \times (Vhosc - Vlosc) / I6$

となる。また、同様にして電位下降の周期Tfは、

$Tf = C3 \times (Vhosc - Vlosc) / I7$

として表すことができる。ここで、電流I6,I7は電流I3の大きさと比例関係にある

20

30

40

50

。したがって、三角波信号Vosc1の発振周波数(fosc)は、抵抗R4の大きさ、内部基準電圧Vrosc、あるいは入力端子inに印加されるエラーアンプ出力信号Verrの電圧値を変えることによって、それぞれ調整することが可能である。

#### [0056]

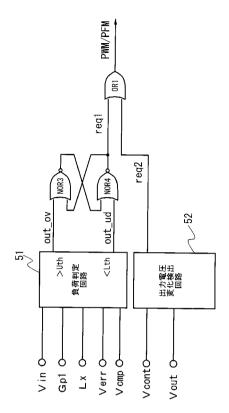

図 5 は、図 1 の D C - D C コンバータにおける P W M / P F M 決定回路 1 0 の具体的な構成例を示す回路図である。

PWM/PFM決定回路10では、DC-DCコンバータのフィードバック制御方式をPWM制御とPFM制御のいずれかに決定する。そのためには、接続される負荷LOADの大きさの程度と、出力電圧信号Voutの変化が要求されているか否かの判定を行わなければならない。ここでは、PWM/PFM決定回路10は、負荷判定回路51、出力電圧変化検出回路52、ノアゲートNOR3,NOR4、及びオアゲートOR1から構成されている。

#### [0057]

負荷判定回路51は、入力電源電圧Vin、ドライブ回路Dr1から出力されるゲート信号Gp1、電圧信号Lx、エラーアンプ出力信号Verr、及びパルス幅変調信号Vcmpが供給され、しきい値Uth,Lthに基づいて2つのパルス信号out\_ov,out\_udを出力している。このしきい値Uthは、PFM制御からPWM制御に移る際の基準とされる。ここでは、負荷判定回路51での安定した動作を保障するため、2つのしきい値にはUth>Lthのようなヒステリシス特性を持たせている。負荷LOADがしきい値Uthを超えると、パルス信号out\_ovがHighになり、ノアゲートNOR3,NOR4で構成されるRSフリツプフロツプの働きによって判定信号rea1がHighに保持される。また、負荷LOADがしきい値Lthを下回ると、パルス信号out\_udがHighになり、判定信号rea1がLowに保持される。

#### [0058]

#### [0059]

図 6 は、 P W M / P F M 決定回路 1 0 における負荷変動及び出力電圧変化に対する切替え信号 P W M / P F M の関係を示す図である。

PWM / PFM決定回路 1 0 では、負荷 L O A D が軽負荷で、かつ出力電圧信号 V o u t の変化がないと判断されたときにのみ、切替え信号 PWM / PFMは L o wになって、 D C - D C コンバータでは PFM制御が選択される。

#### [0060]

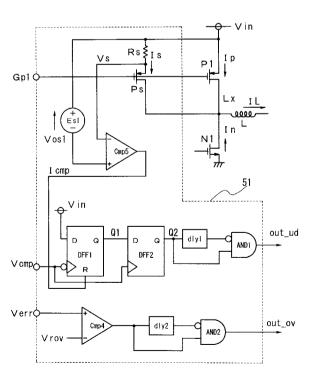

図 7 は、図 5 の P W M / P F M 決定回路における負荷判定回路 5 1 の具体的な構成例を示す回路図である。

負荷判定回路51では、負荷LOADの大きさを出力用のPchトランジスタP1に流れる電流Ipで判断する。この電流Ipを測るため、PchトランジスタP1のゲートへの入力とドレインとを共通にしたセンス用のPchトランジスタPsを設けている。このPchトランジスタPsのソースは、電流センス用抵抗Rsを介して入力電源電圧Vinに接続される。PchトランジスタP1に電流Ipが流れると、PchトランジスタPsに電流Isが流れる。このとき電流センス用抵抗Rsに生じる電圧降下がゲート・ソース間電圧に対し充分小さくなるよう設定することにより、電流Isは電流Ipに比例した値となる。電流Isにより変化するソース電圧VsはコンパレータCmp5のマイナス入力端子に供給され、内部電圧源Es1が入力電源電圧VinとコンパレータCmp5のプラス

入力端子の間に挿入される。その結果、ソース電圧VsはコンパレータCmp5において内部基準電圧(Vin・Vos1)と比較される。ここで、コンパレータCmp5の出力電圧をIcmpとする。

## [0061]

この出力電圧Icmpはリセット端子付きのDフリップフロップDFF1のリセット端子Rに入力される。DフリップフロップDFF1は、パルス幅変調用コンパレータCmp1からのパルス幅変調信号Vcmpの立下りでHighを取り込むように構成され、その出力Q1は後段のDフリップフロップDFF2に、パルス幅変調信号Vcmpの立ち上がりで取り込まれる。DフリップフロップDFF2の出力Q2からは、アンドゲートAND1において遅延回路dly1により遅延した信号の反転信号と出力Q2自身のアンド論理信号が形成され、パルス信号out\_udとして出力される。

10

## [0062]

また、エラーアンプ出力信号 Verrはコンパレータ Cmp4を用いて内部基準電圧 Vrovと比較される。このコンパレータ Cmp4には、遅延回路 d 1 y 2 とアンドゲート AND 2 とが接続され、遅延回路 d 1 y 2 により遅延した信号の反転信号とコンパレータ Cmp4 自身の出力とのアンド論理信号が、アンドゲート AND 2 からパルス信号 out\_ovとして出力される。

## [0063]

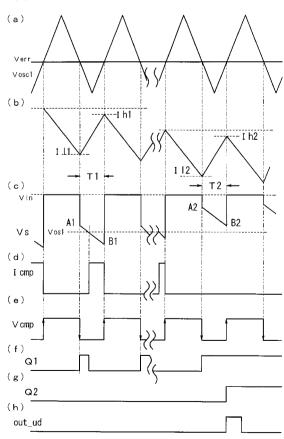

つぎに、この負荷判定回路51の動作について説明する。

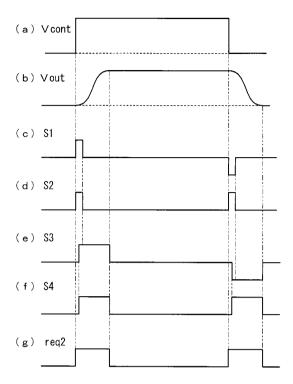

図8は、図7の負荷判定回路51の動作波形を示す図である。ここでは、負荷電流が減ってきて、PWM制御からPFM制御に移る場合を表している。

20

#### [0064]

同図(a)は、エラーアンプ出力信号Verrと三角波信号Vosc1の変化を示している。ここでは、Vosc1>Verrのとき出力段のNchトランジスタN1がオンし、 Vosc1<Verrのとき出力段のPchトランジスタP1がオンする。

## [0065]

同図(b)は、チョークコイルLに流れるコイル電流ILの変化を示している。コイル電流ILは、PchトランジスタP1がオンしているときに増加し、NchトランジスタN1がオンしているときには減少する。図の左側に示される波形は負荷電流が大きい場合であり、右側に示される波形は負荷電流が小さい場合である。いずれも負荷電流は時間とともに減少している。

30

## [0066]

同図(c)は、PchトランジスタPsのソースと電流センス用抵抗Rsとの接続点におけるソース電圧Vsの変化を示している。このソース電圧Vsは、PchトランジスタP1を流れる電流Ipに応じた電圧値となっている。NchトランジスタN1がオンの期間には、電流センス用抵抗Rsに電流が発生しないため、ソース電圧Vsは入力電源電圧Vinを維持する。PchトランジスタP1がオンして電流Ipが増加するにつれてソース電流Isも増え、ソース電圧Vsは低下してくる。

## [0067]

同図(d)は、コンパレータCmp5の出力電圧Icmpの変化を示している。同図(b)~(d)に示すように、チョークコイルLに流れるコイル電流ILがI11からIh1に増加するタイミングT1では、ソース電圧VsはA1からB1に低下し、コイル電流ILがI12からIh2に増加するタイミングT2では、ソース電圧VsはA2からB2に低下する。そして、ソース電圧Vsは内部基準電圧(Vin・Vos1)と比較され、ソース電圧Vsが低くなるときには、出力電圧IcmpがHighになる。すなわち、ソース電圧VsがA1からB1に移るタイミングT1では、内部基準電圧Vos1を超えたところで出力電圧IcmpはHighになる。しかし、ソース電圧VsがA2からB2に移るタイミングT2では内部基準電圧Vos1を超えないため、出力電圧IcmpはLowを維持したままである。

[0068]

50

20

30

40

50

同図(e)(f)(g)(h)は、それぞれパルス幅変調信号Vcmpの信号波形、DフリップフロップDFF1の出力Q1、DフリップフロップDFF2の出力Q2、パルス信号out\_\_ udを示している。

## [0069]

DフリップフロップDFF1は、パルス幅変調信号Vcmpの各パルスの立下りタイミングでHighを取り込み、出力電圧IcmpのHighレベルでリセットされるため、出力電圧IcmpがHighにならなくなった時点で、出力Q1はHighを維持する。DフリップフロップDFF1の出力Q1は、さらにパルス幅変調信号Vcmpの立上りにおいてDフリップフロップDFF2で取り込まれ、出力Q2として出力される。出力Q2の立上り時にパルス信号out\_udとして出力される。

[0070]

このように、負荷電流が時間とともに減少していく場合、 Pch > 0 ンジスタ P1 を流れる電流 Ipo ピーク値がある所定のレベル Lth を下回ると、パルス信号  $out_u$  dが出力される。

## [0071]

つぎに、負荷電流が増えてきて、パルス信号 out\_ovによって PFM制御から PWM制御に移る場合について説明する。 PFM制御動作の状態で負荷 LOADが重くなってくると、エラーアンプ出力信号 Verrを高くして、スイッチング周波数を上げるようにフィードバック制御が働く。図 7に示す負荷判定回路 5 1 から分かるように、エラーアンプ出力信号 Verrの電圧値が高くなり内部基準電圧 Vrovを超えると、コンパレータ Cmp4の出力が Highに変わる。コンパレータ Cmp4の出力を受ける遅延回路 dly2とアンドゲート AND 2により Highになった時点で、パルス信号 out\_ovとしてパルスが出力される。

[0072]

このように、負荷電流が時間とともに増加していく場合、 P c h トランジスタ P 1 を流れる電流 I p のピーク値がある所定のレベル U t h を超えるとき、パルス信号 o u t \_\_ o v が出力される。

[0073]

なお、これらのパルス信号を出力するしきい値となるUth,Lthは、切替え信号PWM/PFMが所定のヒステリシス特性をもつように、Uth>Lthの関係に設定されている。

[0074]

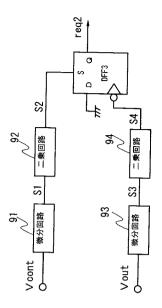

図9は、図5のPWM/PFM決定回路における出力電圧変化検出回路の具体的な構成例を示す回路図である。

この出力電圧変化検出回路52は、微分回路91,93、二乗回路92,94、及びセット付きDフリップフロップDFF3とから構成されている。微分回路91には出力電圧制御信号Vcontが供給され、その微分出力S1を二乗回路92により絶対値信号S2に変換している。また、出力電圧信号Voutは、微分回路93に供給され、その微分出力S3を二乗回路94により絶対値信号S4に変換している。二乗回路92,94は、それぞれDフリップフロップDFF3のセット端子sとクロック端子に接続されている。したがって、二つの絶対値信号S2,S4に基づいて出力電圧の変化に対応する判定信号reg2が、DフリップフロップDFF3のQ信号として出力される。

[0075]

図10は、出力電圧変化検出回路の各部動作信号波形を示している。出力電圧制御信号 V c o n t の微分出力 S 1 の絶対値をとることで、同図(d)に示すように出力電圧制御信号 V c o n t の変化時に H i g h となる絶対値信号 S 2 が得られる。出力電圧信号 V o u t についても同様に、出力電圧信号 V o u t の変化時に H i g h となる絶対値信号 S 4 を得る。そして、 D フリップフロップ D F F 3 を用いて、出力電圧制御信号 V c o n t を変えた直後から出力電圧信号 V o u t が変化していって、それが安定するまでの間、判定信号 r e q 2 を H i g h に 保持することができる。

#### [0076]

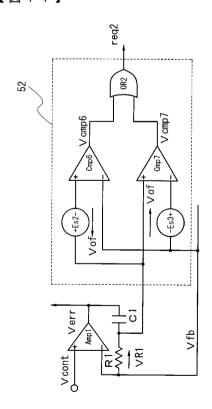

図11は、図9とは別の出力電圧変化検出回路の具体的な構成例を示す回路図である。同図において、出力電圧変化検出回路52は、電圧源Es2,Es3、コンパレータCmp6,Cmp7、及びオアゲートOR2から構成されている。エラーアンプAmp1、位相補償用抵抗R1、位相補償用コンデンサC1は、図1のDC-DCコンバータを構成する増幅手段であって、出力電圧制御信号Vcontを基準電圧として負荷LOADに供給される電圧レベルに応じて変化するフィードバック信号との差電圧を増幅するものである。位相補償用抵抗R1の端子間に発生する電圧VR1は、電圧源Es2を介してコンパレータCmp6のプラス入力端子にオフセット電圧・Vofを加えて供給され、コンパレータCmp7のプラス入力端子にそのまま供給されている。また、フィードバック信号Vfbは、電圧源Es3を介してコンパレータCmp7のマイナス入力端子にオフセット電圧Vofを加えて供給され、コンパレータCmp6のマイナス入力端子にはそのまま供給されている。

## [0077]

コンパレータ Cmp6, Cmp7の各出力信号 Vcmp6、Vcmp7は、オアゲートOR2に入力され、このオアゲートOR2において出力電圧変化検出回路52の出力として判定信号req2が生成される。

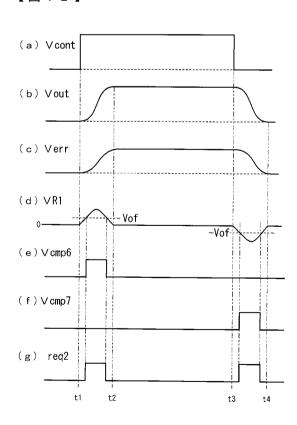

## [0078]

つぎに、出力電圧変化検出回路 5 2 の動作について説明する。図 1 2 は、図 1 1 の出力電圧変化検出回路における各部の動作信号波形を示す図である。

## [0079]

## [0800]

コンパレータCmp6,Cmp7の各出力信号Vcmp6、Vcmp7に基づいて、オアゲートOR2から出力される検出信号req2は、出力電圧変化の検出信号として、出力電圧信号Voutの変化時にHighとなる(同図(g))。

# [0081]

このように図11に示す出力電圧変化検出回路52では、増幅手段であるエラーアンプAmp1から出力されるエラーアンプ出力信号VerrとエラーアンプAmp1へのフィードバック信号Vfbとのバランスに基づいて、負荷LOADに供給される電圧レベルの変化を検出することができる。言い換えれば、出力電圧をレギュレートするエラーアンプAmp1の入出力端子間に設けた位相補償用抵抗R1に対して、<u>所定値を超える</u>電流が発生していない場合にはバランスしている状態とみなして、出力電圧信号Voutは一定で

10

20

30

40

あると判断している。これに対して、位相補償用抵抗 R 1 に対して<u>所定値を超える</u>電流が発生しているときは、バランスしていない状態であって、出力電圧信号 V o u t に変化が生じているものとみなすことができる。

#### [0082]

図 1 3 は、負荷電流が急激に変動した場合の出力電圧変化検出回路における各部の動作信号波形を示す図である。

ここでは、出力電圧制御信号 V c o n t は変化しないまま一定に保たれているが、負荷電流 I o u t が時刻 t 1 で急激に減少し、その後、時刻 t 3 で急激に上昇する場合の、図 1 1 に示す出力電圧変化検出回路 5 2 の動作信号を示す。ここでも、オフセット電圧 V o f の大きさに応じて、一定以上の急激な負荷電流の変化が検出されることにより、オアゲート O R 2 から出力される検出信号 r e q 2 が H i g h になって、D C - D C コンバータのフィードバック制御方式が P F M から P W M に切り替えられる。

#### [0083]

つぎに、図1に示したDC - DCコンバータの動作について説明する。

切替え信号 P W M / P F M が H i g h のときは、発振回路 O S C 1 は一定の周波数の三角波信号 V o s c 1を出力する。マルチプレクサ回路 M u x 1 , M u x 2 はそれぞれパルス幅変調用コンパレータ C m p 1 の出力をドライブ回路 D r 1 , D r 2 に伝える。したがって、切替え信号 P W M / P F M が H i g h のときは通常の P W M 制御と同じ制御動作を行う。

## [0084]

切替え信号 P W M / P F M が L o w のときは、発振回路 O S C 1 はエラーアンプ出力信号 V e r r に応じた発振周波数の三角波信号 V o s c 1を出力する。 P c h トランジスタ P 1 のゲート信号には、パルス幅変調用コンパレータ C m p 1 の出力をトリガー入力とする ワンショット回路 O n e s h o t の出力が使用される。 N c h トランジスタ N 1 のゲート信号は接地電位 G N D に固定され、 N c h トランジスタ N 1 は常にオフ状態となり、接地電位 G N D とチョークコイル L の間には、 N c h トランジスタ N 1 の基板ダイオード D 2 が電流経路として存在する。 したがって、この場合の D C - D C コンバータの構成は図 3 1 に示した従来の P F M 制御方式の D C - D C コンバータと同じ構成となり、同じ P F M 制御動作を行うものとなる。

## [0085]

以上のことから、出力電圧信号 Voutに変化がなく、req2=Lowの場合に、重負荷(req1=High)では切替え信号 PWM / PFMがHighとなってDC-DCコンバータは PWM動作を行い、軽負荷(req1=Low)のときは PFM動作に切り替わる。したがって、DC-DCコンバータのスイッチング損失を少なくして、広い負荷範囲において高い変換効率が維持できる。

#### [0086]

つぎに、出力電圧信号Voutが変化して、req2=Highとなる場合を考えると、 重負荷(req1=High)では出力電圧信号Voutの変化にかかわらずPWM動作 を続けるから、短い期間で出力電圧信号Voutの変化に追従した制御を行うことができ る。

## [0087]

図14は、PWM制御において出力電圧信号Voutが変化する様子を示す信号波形図である。

出力電圧制御信号 V c o n t を時刻 t 1 で立上げ、時刻 t 3 で立下げる。このことに伴い出力電圧信号 V o u t は電位 V o u t 1 から電位 V o u t 2 まで時間 T r 2 をかけて上昇し、電位 V o u t 2 から電位 V o u t 1 まで時間 T f 2 をかけて下降する。平滑コンデンサ C o u t に対する電流は、出力電圧信号 V o u t の増減に伴い平滑コンデンサ C o u t の電荷が増減するための電流と、負荷電流との和である。簡単のため、負荷電流は出力電圧信号 V o u t の大きさにかかわらず一定とする。平滑コンデンサ C o u t の電荷を増減するため電流の流れ込みと吐き出しが生じる。

10

20

30

40

#### [0088]

この流れ込みの電流値Icrg1は、

Icrg1 = Coutx(Vout2 - Vout1)/Tr2

と表すことができる。また、吐き出し電流Idis1は

Idis1 = Coutx(Vout2 - Vout1)/Tf2

と表すことができる。これらの式から、出力電圧信号 Voutの変化時間を短縮するためには電流値を速く、かつ大きく変化させることが必要となる。

## [0089]

出力段のトランジスタ(MOSFET)N1,P1と、チョークコイルLとを介して平滑コンデンサCoutを充放電するときの電流波形は、出力電圧信号Voutの電位を変えるために必要な充放電と負荷電流との和の電流を中心にしたスイッチング電流波形となる。PWM制御ではスイッチタイミング毎にデューティ比を変えているために比較的短時間で電流値を増減させることが可能である。また、スイッチング周波数を高くすることによって、より短時間に電流値を変えることが可能となる。さらに、出力電圧を下げるときに平滑コンデンサCoutからNchトランジスタN1を介して接地電位GNDにマイナスの電流を放電することで、早い電圧降下が可能となる。

## [0090]

つぎに、出力電圧信号 V o u t が変化して r e q 2 = H i g h となる場合であって、しかも軽負荷(すなわち、 r e q 1 = L o w ) のときの動作について説明する。

#### [0091]

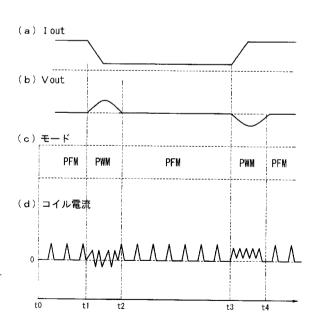

図 1 5 は、図 1 の D C - D C コンバータの軽負荷時における出力電圧の変化を示す波形図である。

時刻 t 0 において出力電圧信号 V o u t は変化前であるため、判定信号 r e q 2 と切替え信号 P W M / P F M は L o w であり、 D C - D C コンバータは P F M 動作を行っている。 そのため、チョークコイル L を流れるコイル電流 I L は不連続になっている。

## [0092]

出力電圧制御信号 V c o n t が高く変化する時刻 t 1 で判定信号 r e q 2 と切替え信号 P W M / P F M は H i g h になり、 P W M 動作に移る。コイル電流 I L は連続的に流れるようになり、 平滑コンデンサ C o u t に流れ込む電流の平均値が著しく大きくなるため、出力電圧信号 V o u t を短期間に上昇させることができる。出力電圧信号 V o u t の変化が終了する時刻 t 2 以降は P F M 動作に戻り、低消費動作を続ける。

## [0093]

出力電圧制御信号 V c o n t が低く変化する時刻 t 3 で P W M 動作に移ると、コイル電流 I L は連続的に流れ、かつ電流の一部あるいは全体がマイナスの値になる。コイル電流 I L がマイナスのときは、平滑コンデンサ C o u t の電荷がチョークコイル L を介して放電する方向を示す。したがって、通常の P F M 動作では、マイナスの電流を流せないため出力電圧信号 V o u t を下げるときは、平滑コンデンサ C o u t と負荷電流の時定数より短い時間で低下できなかったが、この発明の D C - D C コンバータでは出力電圧信号 V o u t を短期間に低下させることが可能となる。出力電圧信号 V o u t の変化が終了する時刻t 4 以降は再び P F M 動作に戻り、低消費動作を続ける。

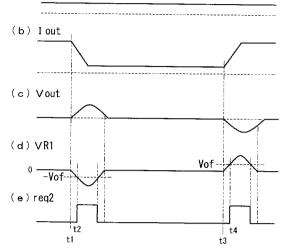

# [0094]

図16は、図1のDC-DCコンバータに出力電圧変化検出回路として図11に示す回路を使用した場合における負荷電流の急変時での出力電圧の変化を示す波形図である。

## [0095]

## [0096]

負荷電流Ioutが急激に減少する時刻t1では、出力電圧信号Voutが上昇する。このとき、判定信号rea2と切替え信号PWM/PFMはHighになってPWM動作に

10

20

30

40

移り、コイル電流ILは連続的に流れるようになる。したがって、PFM制御の場合に比較して、出力電圧信号Voutを短期間に収束させることができる。出力電圧信号Voutの変化が終了する時刻t2以降は再びPFM動作に戻り、低消費動作を続ける。

#### [0097]

負荷電流Ioutが急激に増加する時刻t3では、出力電圧信号Voutが下降する。このときPWM動作に移ることによって、コイル電流ILは連続的に流れる。したがって、出力電圧制御信号Vcontが変化しないで、負荷電流Ioutが変わった場合にも、この発明のDC-DCコンバータでは出力電圧信号Voutを短期間に収束させることが可能となる。出力電圧信号Voutが収束する時刻t4以降には、再びPFM動作に戻り、低消費動作を続ける。

[0098]

以上、第1の実施の形態に係るDC-DCコンバータは、出力電圧が変化するときは負荷状態にかかわらずPWM制御を行わせることで、出力容量の充放電電流を短期間で増減でき、出力電圧の遷移時間を短縮できるから、広い負荷領域において高効率を維持すると同時に、軽負荷条件下でも出力電圧信号の応答性を低下させない利点がある。

(第2の実施の形態)

上述したDC-DCコンバータでは、広い負荷領域において高効率を維持すると同時に、軽負荷条件下でも出力電圧信号Voutの応答性を低下させないことができる。ところが、このDC-DCコンバータには、出力電圧制御信号Vcontにステップ状の変動があると、エラーアンプAmp1の動作点も同時にステップ状に変化し、その値を初期値として目標値が決定されるために、出力電圧信号Voutにオーバーシュートが生じるという問題があった。また、PWM/PFM決定回路10では、負荷LOADが軽負荷で、かつ出力電圧信号Voutの変化がないとして、PWM/PFM切替え信号がLowになり、あるいは再びHighになる時、出力電圧信号Voutにアンダーシュートやオーバーシュートが発生するという問題もあった。

(第2の実施の形態についての構成の説明)

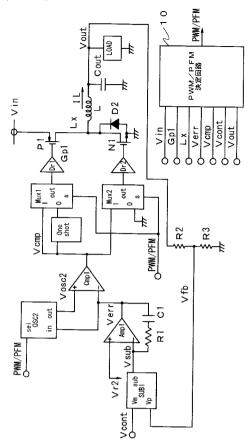

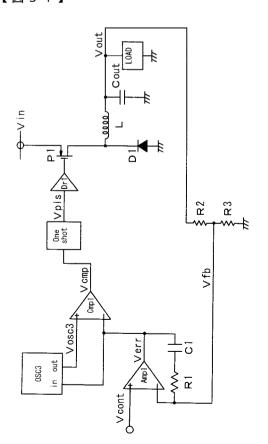

最初に、これら 2 つの問題を解決した別の D C - D C コンバータの構成について説明する。図 1 7 は、第 1 の実施の形態とは別の D C - D C コンバータの一例を示す回路図である

[0099]

第2の実施の形態に係るDC-DCコンバータは、入力電源電圧Vinを所定の電圧レベルに変換して、負荷LOADに供給するものであって、エラーアンプAmp1、位相補償用コンデンサC1、位相補償用抵抗R1、帰還抵抗R2,R3、発振回路OSC2、パルス幅変調用コンパレータCmp1、ワンショット回路Oneshot、マルチプレクサ回路Mux1,Mux2、ドライブ回路Dr1,Dr2、出力用のPchトランジスタ(MOSFET)P1、Nchトランジスタ(MOSFET)N1、チョークコイルL、ダイオードD2、平滑コンデンサCout、PWM/PFM決定回路10、及び減算回路SUB1から構成されている。

[0100]

この D C - D C コンバータでは、後述する図 1 9 に示す構成の発振回路 O S C 2 に置き換えられている点で、第 1 の実施の形態とは異なっている。

また、負荷LOADに供給された出力電圧信号Voutを抵抗R2,R3で分圧して生成したフィードバック信号Vfbが、減算回路SUB1のVp入力端子に接続されるとともに、出力電圧制御信号Vcontが減算回路SUB1のVm入力端子に接続されている。減算回路SUB1では、これらフィードバック信号Vfbと出力電圧制御信号Vcontとの差信号Vsubが生成されている。

[0101]

さらに、エラーアンプAmp1は位相補償用抵抗R1と位相補償用コンデンサC1を使って積分回路が形成される。このエラーアンプAmp1のプラス入力端子には基準電圧信号Vr2が接続され、マイナス入力端子には減算回路SUB1のsub出力端子から出力さ

10

20

30

40

れる差信号Vsubが接続されている。

## [0102]

この D C - D C コンバータの上述した回路以外の構成については、第 1 の実施の形態で説明したのものと同じであるから、それぞれ対応する部分に同一の符号を付けて、それらの詳細な説明を省く。

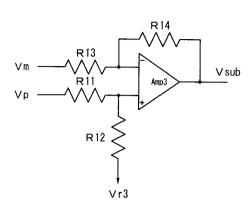

## [0103]

図18は、減算回路の具体的な構成例を示す回路図である。この減算回路SUB1は、オペアンプAmp3と4つの抵抗R11~R14によって構成され、オペアンプAmp3には、フィードバック信号Vfb(=Vp)と基準電圧信号Vr3がそれぞれ抵抗R11、R12を介してプラス入力端子に接続され、出力電圧制御信号Vcont(=Vm)が抵抗R13を介してマイナス入力端子に接続されている。R11=R12=R13=R14とすると、このオペアンプAmp3から出力される差信号Vsubは、Vp・Vm+Vr3となる。したがって、図17のDC-DCコンバータにおけるエラーアンプAmp1には、マイナス入力端子にVfb・Vcont+Vr3が印加される。

## [0104]

ここでは、エラーアンプAmp1の基準電圧信号Vr2が減算回路SUB1の基準電圧信号Vr3と等しい大きさに設定されていれば、フィードバック信号Vfbが出力電圧制御信号Vcontを下回ったとき(Vcont>Vfb)には、エラーアンプ出力信号Verrの電位が上がり、フィードバック信号Vfbが出力電圧制御信号Vcontを上回ったとき(Vcont<Vfb)には、エラーアンプ出力信号Verrの電位が下がる。したがって、PWM制御されるDC-DCコンバータは、出力電圧制御信号Vcontをステップ状に変化させても出力電圧信号Voutにオーバーシュートが生じることなく、所望する動作を安定して実現できる。

#### [ 0 1 0 5 ]

図 1 9 は、図 1 7 の D C - D C コンバータにおける発振回路の具体的な構成例を示す回路 図である。

## [0106]

図19において、この発振回路OSC2を構成するオペアンプAmp2のマイナス入力には、マルチプレクサ回路Mux3からセレクト端子Sへの入力信号電圧に応じて、内部基準電圧Vrosc、あるいは入力端子inからのエラーアンプ出力信号Verrのいずれか一方が印加される。マルチプレクサ回路Mux3は、図2で説明したマルチプレクサ回路Mux1,Mux2と同じ機能をもつ。このマルチプレクサ回路Mux3では、セレクト端子Sに供給される切替え信号PWM/PFMがPWMモードであるときは内部基準電圧Vroscを出力し、PFMモードのときはエラーアンプ出力信号Verrを出力する

## [0107]

PchトランジスタP3のドレインとオペアンプAmp2のプラス入力は、ともにマルチプレクサ回路Mu×4の出力端子outに接続される。マルチプレクサ回路Mu×4の「1」入力端子は、第2の抵抗回路である抵抗R5を介してグランドに接続され、「0」入力端子は、第1の抵抗回路である抵抗R6を介して基準電圧Vr6に接続される。マルチプレクサ回路Mu×4のセレクト端子Sには、切替え信号PWM/PFMが供給されている。

## [0108]

オペアンプAmp2とPchトランジスタP3、抵抗R5,R6、及び基準電圧Vr6の 構成により、PWMモードのときにPchトランジスタP3に流れる電流I3の大きさは 10

20

30

40

20

30

40

50

Vrosc/R5となり、PFMモードのときには(Verr‐Vr6)/R6となる。また、PchトランジスタP4はPchトランジスタP3とゲートへの入力が共通であり、ゲート・ソース間電圧が等しいため、PchトランジスタP4のドレイン電流I4は電流I3にPchトランジスタP4とPchトランジスタP3のゲート幅/ゲート長の比をかけた値になる。このことは、他のトランジスタを流れる電流I5,I6,I7に対しても同様に成り立つ。PchトランジスタP7及びNchトランジスタN7のゲートには、RSフリップフロップを構成するノアゲートNOR2に接続され、その出力信号Vcが供給される。RSフリップフロップの出力信号VcがHighのときNchトランジスタN7がオン、PchトランジスタP7がオフのためコンデンサC3からNchトランジスタN7がオフ、PchトランジスタP7がオンのため、コンデンサC3にPchトランジスタP6,P7の経路で電流I6が充電される。

[0109]

コンデンサ C 3 の充電電圧として出力される三角波信号 V o s c 2 は、 V h o s c > V l o s c の関係にある内部基準電圧をそれぞれ入力する 2 つのコンパレータ C m p 2 , C m p 3 によって、その電位が監視されている。すなわち、 R S フリップフロップの出力信号 V c が L o w のとき三角波信号 V o s c 2 は電位が上がり、それが内部基準電圧 V h o s c を超えた時点でコンパレータ C m p 2 の出力が H i g h になって出力信号 V c が H i g h に変わる。その後、三角波信号 V o s c 2 は電位が下がり、それが内部基準電圧 V l o s c より低くなった時点でコンパレータ C m p 3 の出力が H i g h になって出力信号 V c は再び L o w になる。

[0110]

図20は、図19の発振回路から出力される三角波信号Vosc2を示す信号波形図である。

この三角波信号 Vosc2は、下限値を Vlosc、上限値を Vhoscとするとき、その電位上昇の周期 Trは、

$Tr = C3 \times (Vhosc - Vlosc) / I6$

となる。また、同様にして電位下降の周期Tfは、

$Tf = C3 \times (Vhosc - Vlosc) / I7$

として表すことができる。ここで、電流 I 6 , I 7 は電流 I 3 の大きさと比例関係にある。したがって、三角波信号 V 0 s c 2 の発振周波数 ( f 0 s c 2 ) は、抵抗 R 5 , R 6 の大きさ、内部基準電圧 V V 0 s c、基準電圧 V V 6 あるいは入力端子 V 1 n に印加されるエラーアンプ出力信号 V V 8 r V 7 の電圧値を変えることによって調整することが可能である。

[0111]

なお、 P W M / P F M 決定回路 1 0 の具体的な構成などは、第 1 の実施の形態で説明した ものと同じである。

(第1の実施の形態における問題点の説明)

つぎに、上記構成の発振回路OSC2を用いたDC-DCコンバータの動作を説明する前に、第1の実施の形態に係るDC-DCコンバータ(図1)において、PWM/PFM制御の切替え時に発生するアンダーシュート、オーバーシュートについて説明する。

[0112]

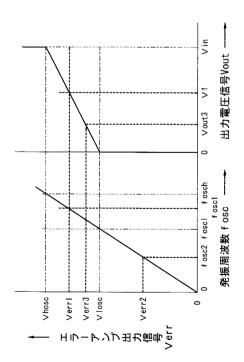

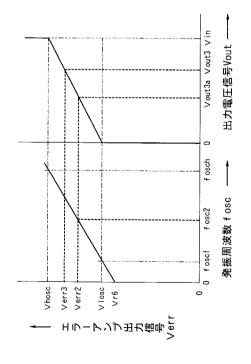

図21は、図1のDC-DCコンバータを三角波信号Vosc1に基づいてPWM制御する場合の、定常状態におけるエラーアンプ出力信号Verrと出力電圧信号Voutとの関係を示す図である。

[0113]

図1のDC-DCコンバータは、PWMモードのときには、図3に示す発振回路OSC1から出力された三角波信号Vosc1がエラーアンプ出力信号Verrと比較され、エラーアンプ出力信号Verrの大きさに応じて出力電圧信号Voutが決定される。ただし、エラーアンプ出力信号Verrの大きさが設定された下限値Vlosc以下のとき、出力電圧信号Vout

は入力電源電圧Vinに等しくなる。

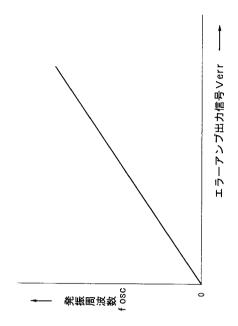

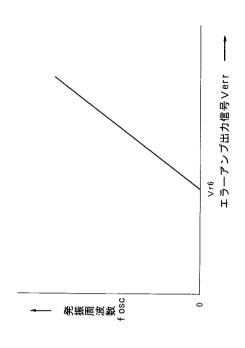

## [0114]

図22は、図1のDC-DCコンバータを三角波信号Vosc1に基づいてPFM制御する場合の、エラーアンプ出力信号Verrと発振周波数foscとの関係を示す図である。PFMモードで動作するとき、図3に示す発振回路OSC1ではエラーアンプ出力信号Verrの大きさに比例して発振周波数foscが決定され、その結果としてDC-DCコンバータの出力電流が定まる。

## [0115]

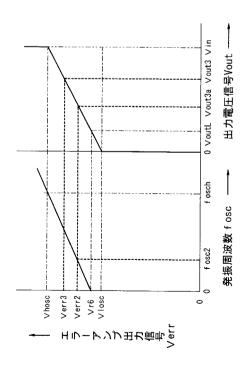

図23は、エラーアンプ出力信号Verrに対するPFM制御とPWM制御での動作点を 説明する図である。

図23では、例えば、エラーアンプ出力信号 Verrの大きさが Verr1のとき、PWMモードでは出力電圧信号 Voutは V1であり、PFMモードでは発振周波数 foscは fosc1である。すなわち、PFMモードで動作する場合に、Verrと foscとは比例関係にあり、またfoscは負荷電流 Ioutにも比例する。このことから、エラーアンプ出力信号 Verrは負荷電流 Ioutに応じて上限値 Vhoscから 0 V近辺まで下がる可能性があることがわかる。また、PWMモードでは出力電圧信号 Voutはエラーアンプ出力信号 Verrの大きさで決定される。

#### [0116]

いま、DC-DCコンバータの出力電圧信号Voutが変化し、あるいは負荷LOADが 重負荷に変わって、PFMモードからPWMモードに切替わる場合を考える。図24は、 PFM制御からPWM制御に切替わる過程で生じる出力電圧信号Voutのアンダーシュートを説明する図である。

#### [0117]

P F M モード時に初期の出力電圧信号 V o u t が V o u t 1 であって、それに対応する発 振周波数をfosc2とする。いま、出力電圧信号Voutが変動してPWMモードに切 替わったときに、電位Vout3に対応するエラーアンプ出力信号Verrも電位Ver r 3 に変化するものとする。ところが、時刻 t 1 のタイミングで P F M モードから P W M モードへ切替わっても、第1の実施の形態に係るDC-DCコンバータでは位相補償用コ ンデンサC1、位相補償用抵抗R1の働きによって、エラーアンプ出力信号Verrは急 激に変化しない。すなわち、PWMモードに切替わった直後において暫くの間は、エラー アンプ出力信号Verrが発振周波数fosc2に対応する電位Verr2の近傍に留ま ることになる。また、この電位Verr2は下限値Vloscより低いため、パルス幅変 調用コンパレータCmp1の働きによって出力段のNchトランジスタ(MOSFET) N 1 は常にオンし、Pchトランジスタ(MOSFET)P 1 はオフしてしまう。しかも 、出力電圧信号VoutのノードはチョークコイルLとNchトランジスタ(MOSFE T) N1とを介して接地されているために、出力電圧信号 Voutは時刻 t1のタイミン グで0Vに向かって急激に低下する。その後、出力電圧信号Voutからのフィードバッ ク信号Vfbが低下することによって、エラーアンプAmp1の働きによりエラーアンプ 出力信号Verrは再び上昇しはじめて電位Verr3に到達し、出力電圧信号Vout も対応する電位Vout3に落ち着く。

# [0118]

第1の実施の形態に係るDC-DCコンバータでは、PWMモードからPFMモードに切替わるときでも、同様の問題が生じる。図25は、PWM制御からPFM制御に切替わる過程で生じる出力電圧信号Voutのオーバーシュートを説明する図である。

#### [0119]

PWMモード時の出力電圧信号 VoutがVout3であって、PFMモードに切替わったときに発振周波数がfosc2に変化するものとする。最初に電位 Verr3であったエラーアンプAmp1は、時刻t2のタイミングでPWMモードからPFMモードへ切替わっても、そのエラーアンプ出力信号 Verrは急激に変化できず、ワンショット回路Oneshotではfosc2より高い周波数でPchトランジスタ(MOSFET)P1

10

20

30

40

20

30

40

50

に対するスイッチング信号が生成される。そのため、平滑コンデンサCoutには余分な電流が流れ込むことになり、出力電圧信号Voutは時刻t2のタイミングから上昇しはじめる。その後、出力電圧信号Voutからのフィードバック信号Vfbが上昇することによって、エラーアンプAmp1の働きによりエラーアンプ出力信号Verrは下降しはじめて電位Verr2に到達し、スイッチング信号の発振周波数はfosc2となり、出力電圧信号Voutも対応する電位Vout1に落ち着く。

(第2の実施の形態についての動作の説明)

つぎに、図17に示したDC-DCコンバータの動作について説明する。

## [0120]

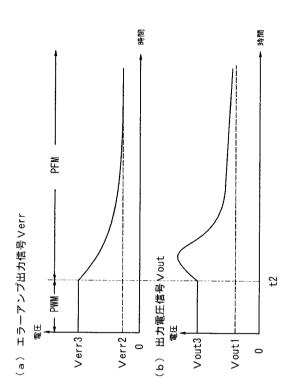

図26は、三角波信号Vosc2に基づくPFM制御動作におけるエラーアンプ出力信号 Verrと発振周波数foscとの関係を示す図、図27及び図28は、いずれもエラーアンプ出力信号Verrに対するPFM制御とPWM制御での動作点を説明する図である

## [0121]

以下、図19に示すような発振回路OSC2を用いたDC-DCコンバータの動作を説明する。ここでは、出力電圧信号Voutのアンダーシュート、オーバーシュートを抑制することができる。

## [0122]

三角波信号 Vosc2の発振周波数 foscは、図19の発振回路OSC2では電流I3の大きさによって決定される。したがって、PFM制御動作には電流I3が(Verr-Vr6)/R6であることから、エラーアンプ出力信号 Verrが基準電圧 Vr6より大きい範囲(Verr> Vr6)では、図26に示すように、発振周波数 foscを(Verr-Vr6)の大きさに比例して決定できる。

#### [0123]

また、Verr Vr6では、図19においてオペアンプAmp2にはそれぞれマルチプレクサ回路 $Mu \times 3$ , $Mu \times 4$ からの2入力が比較され、出力信号がHighになる。したがって、PchhランジスタP3、P4が遮断され、電流I3 = I4 = 0となるから、図26に示すように、発振周波数fosc8

## [0124]

図27は、エラーアンプ出力信号Verrに対するPFM制御とPWM制御での動作点を説明する図である。ここでは、基準電圧Vr6がエラーアンプ出力信号Verrの下限値Vloscより大きい場合を想定している。

## [0125]

まず、PFMモードで動作するDC-DCコンバータの出力電圧信号Voutが変化して、PWMモードに切替わる場合を考える。PFMモード時に初期の出力電圧信号VoutがVout3aであって、それに対応する発振周波数をfosc2とする。また、出力電圧信号Voutが変動してPWMモードに切替わったとき、その電位Vout3に対応するエラーアンプ出力信号Verrが電位Verr3に変化するものとする。

## [ 0 1 2 6 ]

PFMモードからPWMモードへ切替わっても、位相補償用コンデンサC1、位相補償用抵抗R1の働きによってエラーアンプ出力信号Verrは、第1の実施の形態に係るDC-DCコンバータと同様に急激に変化しない。すなわち、PWMモードに切替わった直後において暫くの間は、エラーアンプ出力信号Verrが発振周波数fosc2に対応する電位Verr2の近傍に留まることになる。しかし、この例ではPWMモードに切り替えた直後に、出力電圧信号Voutはエラーアンプ出力信号Verrに対応する電圧Vout3aに向かい、その後は出力電圧信号Voutのフィードバック信号であるフィードバック信号Vfbが下がったことで、エラーアンプAmp1の働きによりエラーアンプ出力信号Verrが上昇する。ここでは、基準電圧Vr6の大きさによって決まる発振周波数fosc2に対応するエラーアンプ出力信号Verrは、その電位Verr2をPWMモードにおける電位Verr3との電位差が小さくなるように設定しておくことができるの

20

30

40

50

で、PWMモードに切替わった後の本来のエラーアンプ出力信号Verrの電位Verr 3にセットリングされるまでの時間を短縮できる。したがって、PWM制御における動作 点のずれが少なくなって、アンダーシュートの絶対値を小さくできる。

## [0127]

第2の実施の形態に係るDC-DCコンバータでは、PWMモードからPFMモードに切替わるときも、同様の効果がある。PWMモード時の出力電圧信号VoutがVout3であって、PFMモードに切替わったときに発振周波数がfosc2に変化するものとする。最初に電位Verr3であったエラーアンプAmp1は、時刻t2のタイミングでPWMモードからPFMモードへ切替わっても、そのエラーアンプ出力信号Verrは急激に変化できないで、発振周波数はfosc2より高い周波数でPchトランジスタ(MOSFET)P1をスイッチングしている。しかし、エラーアンプ出力信号Verrの電位Verr2とPWMモードにおける電位Verr3との電位差を小さく設定しておくことで、エラーアンプ出力信号Verrが電位Verr2に到達するまでの時間を短縮できる。したがって、PFM制御におけるオーバーシュートの大きさを小さくできる効果がある

#### [0128]

このように、エラーアンプ出力信号Verrに対するPFM制御とPWM制御での動作点が図27に示すように設定されていれば、PFMモードからPWMモードに移行するとき、発振周波数foscが0に近いときでも、エラーアンプ出力信号Verrの電位Verr2は必ず下限値Vloscより高くなる。したがって、PWMモードに移行した後に、出力段のNchトランジスタ(MOSFET)N1が継続してオンしたり、Pchトランジスタ(MOSFET)P1がオフになったりしないし、出力電圧信号Voutが0Vに向かって急激に低下することもない。また、PWMモードからPFMモードに切替わるときでも、出力電圧信号Voutのオーバーシュートを小さくできるが、PWMモードでのVoutが基準電圧Vr6に対応する電位VoutLより低い場合には、PFMモードへの切替えは好ましくない。電位VoutL以下の出力電圧信号Voutに対応するエラーアンプ出力信号Verrの大きさでは、PFMモードでの発振周波数foscが0になって、発振停止状態となるからである。

## [0129]

図28は、エラーアンプ出力信号Verrに対するPFM制御とPWM制御での動作点を説明する図である。ここでは、図27の場合と異なり、基準電圧Vr6をエラーアンプ出力信号Verrの下限値Vloscより小さな電圧値としている。これにより、PWMモードからPFMモードに切替わるとき、PFMモードでの発振周波数foscは0にならず、発振停止状態を回避できる。

## [0130]

つぎに、PFMモードからPWMモードに切替わる場合を考える。初期の出力電圧信号VoutがVout3a、対応する発振周波数をfosc2とする。PWMモードに切替わった後の出力電圧信号Voutが電位Vout3で、対応するエラーアンプ出力信号Verrを電位Verr3としている。図27について説明したものと同様に、ここでも基準電圧Vr6の大きさによって決まる発振周波数fosc2に対応するエラーアンプ出力信号Verrは、その電位Verr2をPWMモードにおける電位Verr3との電位差が小さくなるように設定しておくことができるので、PWMモードに切替わった後の本来のエラーアンプ出力信号Verrの電位Verr3にセットリングされるまでの時間を短縮できる。したがって、PWM制御における動作点のずれが少なくなって、アンダーシュートの絶対値を小さくできる。

## [0131]

なお、PFMモードからPWMモードに移行するとき、移行前のPFMモードでの発振周波数foscがエラーアンプ出力信号の下限値Vloscに対応する下限周波数値fosclより低い場合には、PWMモードに移行した後に、出力段のNchトランジスタ(MOSFET)N1が継続してオンするから、出力電圧信号Voutが0Vに向かって急激

に低下する問題が残る。この問題を回避するためには、PFMモードでの発振周波数foscを下限周波数値foscl以下で使用しないことが好ましい。

(第2の実施の形態についての効果の説明)

以上に説明したように、第2の実施の形態に係るDC-DCコンバータでは、出力電圧信号 VoutorR 電圧値に制約を付ける場合には、基準電圧 Vr6orR 大きさをエラーアンプ出力信号 VerrorR 値 Vlosc より大きく設計し(Vr6>Vlosc)、反対に、出力電圧信号 VouterR の Vter V

[0132]

なお、図27、図28では、エラーアンプ出力信号Verrの上限値Vhoscに対応するPFM制御の動作点を上限周波数値foschとしており、それより高い周波数でのPFM動作は考慮していない。これは、PFM制御に切り替える目的が、そもそも負荷電流の減少に伴いスイッチング周波数を下げて、広い負荷領域において高い効率を維持することにあるためである。

[0133]

この実施の形態に係る発振回路OSC2(図19)では、PWMモードでの発振周波数とPFMモードでのエラーアンプ出力信号Verrに対応する発振周波数との関係を独立して設定することができる利点がある。従来から、DC-DCコンバータは、PWMモードでの発振周波数をユーザ側で適当な値に選択して使用する場合が多く、そのためにはIC化された発振回路OSC2を構成する抵抗R5を外付け部品としておくことが好ましい。また、集積回路の外部回路として抵抗R6や基準電圧Vr6の設定回路を構成することにより、PFMモードでの動作特性をユーザ側が任意に調整できるようになる。しかも、PWMモードとPFMモードのいずれにおいても、これらの周波数設定値を独立に決定できるので、いずれか一方のみを調整するにしても、両者ともに調整するにしても、それぞれの調整に際して制約が課されないという利点がある。

[0134]

【発明の効果】

以上に説明したように、この発明によれば、PWM/PFM切替え機能を有するDC-DCコンバータにおいて、広い負荷範囲において高い効率を維持して、しかも軽負荷条件でPFM動作を行っているときでも出力電圧を高速に変化できる。

[0135]

また、この発明の D C - D C コンバータは、出力電圧制御信号にステップ状の変動があっても、出力電圧信号にオーバーシュートが生じない。

さらに、PWM / PFM切替え時に発生するアンダーシュート、オーバーシュートを抑制 して、その絶対値を小さくするとともに、継続時間の短縮を可能とする。

【図面の簡単な説明】

【図1】この発明のDC-DCコンバータの一例を示す回路図である。

【図2】図1のDC-DCコンバータにおけるマルチプレクサ回路の具体的な構成例を示 40 す回路図である。

【図3】図1のDC-DCコンバータにおける発振回路の具体的な構成例を示す回路図である。

【図4】図3の発振回路から出力される三角波信号を示す信号波形図である。

【図 5 】図 1 の D C - D C コンバータにおける P W M / P F M 決定回路の具体的な構成例を示す回路図である。

【図 6 】図 5 の P W M / P F M 決定回路における負荷変動及び出力電圧変化に対する切替え信号 P W M / P F M の関係を示す図である。

【図7】図5のPWM/PFM決定回路における負荷判定回路の具体的な構成例を示す回路図である。

10

20

30

- 【図8】図7の負荷判定回路における各部の動作信号波形を示す図である。

- 【図9】図5のPWM/PFM決定回路における出力電圧変化検出回路の具体的な構成例 を示す回路図である。

- 【図10】図9の出力電圧変化検出回路における各部の動作信号波形を示す図である。

- 【図11】図9とは別の出力電圧変化検出回路の具体的な構成例を示す回路図である。

- 【図12】図11の出力電圧変化検出回路における各部の動作信号波形を示す図である。

- 【図13】負荷電流が急激に変動した場合の出力電圧変化検出回路における各部の動作信 号波形を示す図である。

- 【図14】図1のDC-DCコンバータをPWM制御する場合の出力電圧信号が変化する 様子を示す信号波形図である。

- 【図15】図1のDC-DCコンバータの軽負荷時における出力電圧の変化を示す波形図 である。

- 【図16】図1のDC-DCコンバータにおける負荷電流の急変時での出力電圧の変化を 示す波形図である。

- 【図17】別のDC-DCコンバータの一例を示す回路図である。

- 【図18】図17のDC-DCコンバータにおける減算回路の具体的な構成例を示す回路 図である。

- 【図19】図17のDC-DCコンバータにおける発振回路の具体的な構成例を示す回路 図である。

- 【図20】図19の発振回路から出力される三角波信号を示す信号波形図である。

- 【図21】図1のDC-DCコンバータを三角波信号Vosc1に基づいてPWM制御す る場合のエラーアンプ出力信号と出力電圧信号との関係を示す図である。

- 【図22】図1のDC-DCコンバータを三角波信号Vosc1に基づいてPFM制御す る場合のエラーアンプ出力信号と発振周波数との関係を示す図である。

- 【図23】図1のDC-DCコンバータにおけるエラーアンプ出力信号に対するPFM制 御とPWM制御での動作点を説明する図である。

- 【図24】図1のDC-DCコンバータをPFM制御からPWM制御に切り替える過程で 生じるアンダーシュートを説明する図である。

- 【図25】図1のDC-DCコンバータをPWM制御からPFM制御に切り替える過程で 生じるオーバーシュートを説明する図である。

- 【図26】図17のDC-DCコンバータを三角波信号Vosc2に基づいてPFM制御 する場合のエラーアンプ出力信号と発振周波数との関係を示す図である。

- 【図27】図17のDC-DCコンバータにおけるエラーアンプ出力信号に対するPFM 制御とPWM制御での動作点を説明する図である。

- 【図28】図17のDC-DCコンバータにおけるエラーアンプ出力信号に対するPFM 制御とPWM制御での動作点を説明する図である。

- 【図29】従来のPWM制御方式の降圧DC-DCコンバータの一例を示す回路図である

- 【図30】図29の降圧DC-DCコンバータにおけるPWM制御の動作波形を示す波形 図である。

- 【図31】PFM制御のDC-DCコンバータの一例を示す回路図である。

- 【図32】PFM制御のDC-DCコンバータにおける動作波形を示す波形図である。

- 【図33】PFM制御において出力電圧信号の変化する様子を示す信号波形図である。

【符号の説明】

- Amp 1 エラーアンプ

- R 1 位相補償用抵抗

- C 1 位相補償用コンデンサ

- R 2 , R 3 帰還抵抗

- OSС1,ОSС2,ОSС3 発振回路

- Сmp1 パルス幅変調用コンパレータ

10

20

30

```

P1 Pchトランジスタ(MOSFET)

```

L チョークコイル

Dr1, Dr2 ドライブ回路

N 1 N c h トランジスタ (MOSFET)

Cout 平滑コンデンサ

LOAD 負荷

Oneshot ワンショット回路

Mux1, Mux2, Mux3, Mux4 マルチプレクサ回路

D 1 , D 2 還流ダイオード

10 PWM/PFM決定回路

Vfb フィードバック信号

Vcont 出力電圧制御信号

Vout 出力電圧信号

Verr エラーアンプ出力信号

Vosc1, Vosc2, Vosc3 三角波信号

Vlosc 下限値

Vhosc 上限値

Vin 入力電源電圧

PWM/PFM 切替え信号

Vcmp パルス幅変調信号

Vr2 基準電圧信号

Vsub 差信号

fosc 発振周波数

fosch 上限周波数值

foscl 下限周波数值

IL コイル電流

Iout 負荷電流

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

| 変化あり        | PWM/PFM    | PWM/PFM     |

|-------------|------------|-------------|

| (req2=High) | =High      | =High       |

| 変化なし        | PWM/PFM    | PWM/PFM     |

| (req2=Low)  | =Low       | =High       |

| 出力電圧        | 軽負荷        | 重負荷         |

| 負荷状態        | (req1=Low) | (req1=High) |

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

# 【図15】

t0

t1

t2

# (a) Vcont (b) Vout (c) モード PFM PWM PFM PWM PFM (d) コイル電流

# 【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

# 【図33】

# フロントページの続き

(56)参考文献 特開平10-014217(JP,A)

特開平11-089222(JP,A)

特開平09-051675(JP,A)

特開2001-112251(JP,A)

特開2002-078326(JP,A)

(58)調査した分野(Int.CI., DB名)

H02M 3/155