(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5169419号 (P5169419)

(45) 発行日 平成25年3月27日(2013.3.27)

(24) 登録日 平成25年1月11日(2013.1.11)

| (51) Int.Cl. |      | F 1       |      |      |   |  |

|--------------|------|-----------|------|------|---|--|

| H03F         | 3/45 | (2006.01) | нозг | 3/45 | Z |  |

| H03F         | 3/34 | (2006.01) | нозг | 3/34 | A |  |

| G05F         | 3/30 | (2006.01) | GO5F | 3/30 |   |  |

請求項の数 3 (全 14 頁)

| (21) 出願番号<br>(22) 出願日 | 特願2008-104889 (P2008-104889)<br>平成20年4月14日 (2008.4.14) | (73) 特許権者 |                     |

|-----------------------|--------------------------------------------------------|-----------|---------------------|

|                       |                                                        |           |                     |

| (65) 公開番号             | 特開2009-260490 (P2009-260490A)                          |           | 京都市下京区塩小路通堀川東入南不動堂町 |

| (43) 公開日              | 平成21年11月5日 (2009.11.5)                                 |           | 801番地               |

| 審査請求日                 | 平成23年2月4日(2011.2.4)                                    | (74) 代理人  | 100127030           |

|                       |                                                        |           | 弁理士 増井 義久           |

|                       |                                                        | (74) 代理人  | 100125944           |

|                       |                                                        |           | 弁理士 比村 潤相           |

|                       |                                                        | (72) 発明者  | 籠島 謙知               |

|                       |                                                        |           | 京都府京都市下京区塩小路通堀川東入南不 |

|                       |                                                        |           | 動堂町801番地 オムロン株式会社内  |

|                       |                                                        | (72) 発明者  | 大渡 恵史               |

|                       |                                                        |           | 京都府京都市下京区塩小路通堀川東入南不 |

|                       |                                                        |           | 動堂町801番地 オムロン株式会社内  |

|                       |                                                        |           |                     |

|                       |                                                        |           | 最終頁に続く              |

(54) 【発明の名称】 差動増幅回路及びそれを用いた電源回路

## (57)【特許請求の範囲】

## 【請求項1】

所定の電位差を持つ差動電圧入力である第1及び第2の電圧入力を第1及び第2の電流 出力に変換する入力変換手段と、

前記第1の電流出力に対応する第3の電流出力と前記第2の電流出力との間で演算を行い、前記第1の電圧入力と前記第2の電圧入力との電位差に応じた第4の電流出力を得る出力演算手段と、

前記第1の電圧入力と前記第2の電圧入力とを同電位とすることが可能な同電位手段と

前記同電位手段が前記第1の電圧入力と前記第2の電圧入力とを同電位とした場合において、前記出力演算手段が前記第2の電流出力と前記第3の電流出力との間で演算を行ったときに生じる電位を保持する電位保持手段と を備え、

前記出力演算手段は、前記電位保持手段に保持された電位に基づいて前記出力演算手段が行う演算の偏差を補償する差動増幅回路であって、

前記出力演算手段から入力される前記第4の電流出力を前記差動増幅回路の外部に出力する出力バッファ手段と、

前記出力演算手段から入力される前記第4の電流出力を記憶する電流出力記憶手段とをさらに備え、

前記出力バッファ手段は、前記同電位手段が前記第1の電圧入力と前記第2の電圧入力

とを同電位とした場合においては、前記電流出力記憶手段に記憶された前記第4の電流出力を前記差動増幅回路の外部に出力することを特徴とする差動増幅回路。

#### 【請求項2】

前記出力バッファ手段の電圧入力は、前記同電位手段が前記第1の電圧入力と前記第2の電圧入力とを同電位とする前後にわたって前記出力演算手段の電圧出力と前記出力バッファ手段の電圧入力とを等電位にするように設定されていることを特徴とする請求項1に記載の差動増幅回路。

#### 【請求項3】

請求項1または2に記載の差動増幅回路と、

前記第4の電流出力に基づいて基準電圧を生成する基準電圧生成手段とを備えることを特徴とする電源回路。

【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、半導体集積回路に使用される電源回路に好適な差動増幅回路、及び、その差動増幅回路を用いた電源回路に関する。

#### 【背景技術】

#### [0002]

半導体集積回路に使用される電源回路には、環境温度や素子ばらつきによる出力電圧値のばらつきが少なく、低ノイズのものが要求される。また、近年、CMOS技術の採用により電源電圧の低電圧化が活発になってきており、それらに合わせて低電圧駆動の電源回路も要求されるようになって来ている。

#### [0003]

図7に、半導体集積回路の電源回路として広く使用されている構成の1つで、バンドギャップレギュレータと呼ばれる構成を持つ電源回路の回路図を示す。従来の電源回路20は、図7に示すように、pnpバイポーラトランジスタQ1、Q2と、抵抗R1、R2、R3と、差動増幅回路200と、から構成されている。また、GNDはGND電圧、Vrefは基準電圧出力端子、IN+は差動増幅回路200の非反転入力端子、IN-は差動増幅回路200の反転入力端子をそれぞれ示している。基準電圧出力端子Vrefを約1.25Vにすることで、温度依存性のない基準電圧を得ることができ、環境温度の変化に対して非常に強い回路である。

## [0004]

図7に示した電源回路20は、比較的単純な回路構成から基準電圧を容易に発生することができる利点を持っている。しかしながら、実際の半導体集積回路においては、能動素子の特性ばらつきに起因し、差動増幅回路200の入力端子IN+、IN-の各々の入力電圧が完全には一致しない。通常、2つの入力端子間における入力電圧差を「オフセット電圧」と呼んでいる。このため、電源回路20の基準電圧出力端子Vrefから出力される基準電圧は、電源回路20を構成する差動増幅回路200のオフセット電圧の影響を受ける。つまり、差動増幅回路200のオフセット電圧により、出力すべき基準電圧の精度が悪くなる。

#### [00005]

上記の能動素子の特性ばらつきの原因としては、例えば、MOSトランジスタのゲート 絶縁膜の膜厚ばらつきやソース、ドレイン等の不純物濃度ばらつき、あるいは、素子サイ ズばらつきがある。これらの製造ばらつきはMOSトランジスタの製造プロセスに依存す るものであり、不可避な問題である。

#### [0006]

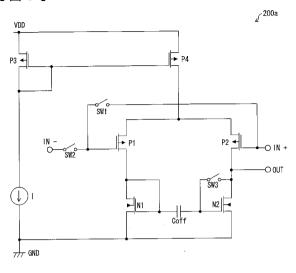

そこで、上記のオフセット電圧をキャンセルする方法として、チョッパ回路を導入した 差動増幅回路が提案されている(例えば、特許文献1)。図8に示すチョッパ型の差動増 幅回路200aは、入力変換回路を構成するpMOSトランジスタP1、P2と、定電流 回路を構成するpMOSトランジスタP3、P4及び電流源Iと、出力演算回路を構成す 10

20

30

40

る n M O S トランジスタ N 1 、 N 2 及び容量 C o f f と、スイッチ S W 1 ~ 3 と、から構成されている。また、 V D D は電源電圧、 G N D は G N D 電圧、 I N + は非反転入力端子、 I N - は反転入力端子、 O U T は出力端子をそれぞれ示している。

#### [0007]

図8の差動増幅回路200aにおいて、スイッチSW1とスイッチSW3は同時にオン/オフするように構成され、スイッチSW2は、スイッチSW1、SW3がオンする期間にオフし、スイッチSW1、SW3がオフする期間にオンするように構成されている。スイッチSW1、SW3がオンする期間(スイッチSW2はオフ)においては、オフセット電圧が検出され、その検出電圧が容量Coffに記憶される一方、スイッチSW2がオンする期間(スイッチSW1、3はオフ)においては、上記のオフセット検出期間において検出されたオフセット電圧を用いてオフセット電圧をキャンセルさせた基準電圧を出力する。このため、オフセット電圧に起因する基準電圧の誤差が低減されることになる。

【特許文献 1 】特開 2 0 0 2 - 2 0 2 7 4 8 号公報

【発明の開示】

【発明が解決しようとする課題】

#### [0008]

上述したように、図8に示した特許文献1の差動増幅回路200aにおいては、オフセット電圧を検出するための期間であるオフセット検出期間と、実際に基準電圧を発生する期間である電圧出力期間とが交互に切り替わることになる。このため、差動増幅回路200aの出力は離散動作することになる。したがって、特許文献1の差動増幅回路200aを電源回路に使用した場合、オフセット検出期間と電圧出力期間との和を1周期として、出力される基準電圧が振動し、リップルが生じる。すなわち、従来の差動増幅回路200aはノイズが増大する問題を有している。

[0009]

上記問題点に鑑み、本発明の目的は、オフセットが少なく、低ノイズの差動増幅回路、 及び、その差動増幅回路を用いた電源回路を提供することである。

【課題を解決するための手段】

#### [0010]

上記目的を達成するために、本発明にかかる差動増幅回路は、所定の電位差を持つ差動電圧入力である第1及び第2の電圧入力を第1及び第2の電流出力に変換する入力変換手段と、前記第1の電流出力に対応する第3の電流出力との電位差に応じた第4の電流出力と前記第1の電圧入力と前記第2の電圧入力とを同電位とすることが可能な同電位手段と、前記同電位手段が前記第1の電圧入力と前記第2の電圧入力とを同電位とすることが可能な同電位手段と、前記同電位手段が前記第1の電圧入力と前記第2の電圧入力と前記第3の電圧入力と前記間第3の電圧入力と前記第3の電圧入力と前記第3の電流出力を前記に生じる電位を保持する電位保持手段とを備え、前記出力演算手段が行う演の偏差を補償する差動増幅回路であって、前記出力減算手段から入力される前記第4の電流出力する出力バッファ手段と、前記出力演算手段からバッファ手段は、前記電位手段が前記第1の電圧入力と前記第2の電圧入力とを同電位とった場合においては、前記電流出力記憶手段に記憶された前記第4の電流出力を前記差動増幅回路の外部に出力を記憶手段に記憶された前記第4の電流出力を前記差動増幅回路の外部に出力することを特徴とする。

# [0011]

上記の差動増幅回路では、同電位手段が第1の電圧入力と第2の電圧入力とを同電位とし、出力演算手段が第2の電流出力と第3の電流出力との間で演算を行う場合においては、出力バッファ手段が電流出力記憶手段に記憶された第4の電流出力を出力するようにしているので、同電位手段が第1の電圧入力と第2の電圧入力とを同電位とする前後にわたって、安定して第4の電流出力を出力することができる。このため、リップルの少ない低ノイズの差動増幅回路を実現することができる。

10

20

30

40

#### [0012]

前記出力バッファ手段の電圧入力は、前記同電位手段が前記第1の電圧入力と前記第2の電圧入力とを同電位とする前後にわたって前記出力演算手段の電圧出力と前記出力バッファ手段の電圧入力とを等電位にするように設定されていることが好ましい。

#### [0013]

この場合、同電位手段が第1の電圧入力と第2の電圧入力とを同電位とする前後において、前記出力演算手段の電圧出力と前記出力バッファ手段の電圧入力との間における電位差が実質的に無くなるので、同電位手段が第1の電圧入力と第2の電圧入力とを同電位とした場合において出力演算手段が第2の電流出力と第3の電流出力との間で演算を行ったときに生じる電位の安定化を図ることができる。このため、上記の差動増幅回路を駆動する電源電圧の低電圧化が進んだ場合でも、上記の電位が変動することが無く、その結果、その電位に基づいて出力演算手段が行う演算の偏差の補償を精度よく行うことができる。

#### [0014]

本発明にかかる電源回路は、上記の差動増幅回路と、前記第4の電流出力に基づいて基準電圧を生成する基準電圧生成手段とを備えることを特徴とする。

#### [0015]

上記の電源回路では、上記の差動増幅回路を用いているので、素子ばらつきによる出力電圧値のばらつきが少なく、低ノイズの電圧を供給でき、かつ低電圧起動が可能な電源回路が実現できる。

## 【発明の効果】

#### [0016]

本発明に係る差動増幅回路は、以上のように、前記出力演算手段から入力される前記第4の電流出力を前記差動増幅回路の外部に出力する出力バッファ手段と、前記出力演算手段から入力される前記第4の電流出力を記憶する電流出力記憶手段とを備え、前記出力バッファ手段は、前記同電位手段が前記第1の電圧入力と前記第2の電圧入力とを同電位とした場合においては、前記電流出力記憶手段に記憶された前記第4の電流出力を前記差動増幅回路の外部に出力するので、同電位手段が第1の電圧入力と第2の電圧入力とを同電位とする前後にわたって、安定して第4の電流出力を出力することができる。このため、リップルの少ない低ノイズの差動増幅回路を実現することができる。

# 【発明を実施するための最良の形態】

#### [0017]

以下、本発明の実施の形態について、図面を参照しながら説明する。なお、同一部分には同一符号を付し、図面で同一の符号が付いたものは、説明を省略する場合もある。

#### [0018]

#### (実施の形態1)

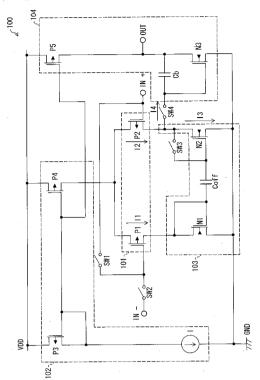

図1は、本発明の実施の形態1にかかる差動増幅回路の構成を示す回路図である。本実施の形態にかかる差動増幅回路100はチョッパ回路を導入したチョッパ型の差動増幅回路であって、図1に示すように、入力変換回路101と、定電流回路102と、出力演算回路103と、出力バッファ回路104と、スイッチSW1~4と、を備えている。また、VDDは電源電圧、GNDはGND電圧、IN+は非反転入力端子、IN-は反転入力端子、OUTは出力端子をそれぞれ示している。

#### **[** 0 0 1 0 ]

入力変換回路101は、pMOSトランジスタP1、P2を有している。pMOSトランジスタP1、P2は入力差動対を構成しており、pMOSトランジスタP1のゲート端子が反転入力端子IN・に接続され、pMOSトランジスタP2のゲート端子が非反転入力端子IN+に接続されている。

#### [0020]

定電流回路102は、pMOSトランジスタP3、P4と、電流源Iと、を有しており、pMOSトランジスタP3、P4はカレントミラー回路を構成している。pMOSトランジスタP3のゲート端子とドレイン端子とが短絡されおり、電流源Iから印加される電

10

20

30

40

流を p M O S トランジスタ P 3 が検出してその電流に応じたゲート電圧を出力する。 p M O S トランジスタ P 3 のゲート端子は p M O S トランジスタ P 4 のゲート端子に接続されており、 p M O S トランジスタ P 3 がゲート電圧を p M O S トランジスタ P 4 のゲート端子に出力すると、 p M O S トランジスタ P 4 のドレイン端子には p M O S トランジスタ P 4 の素子の寸法比に比例した電流がコピーされる。

### [0021]

出力演算回路103は、nMOSトランジスタN1、N2と、容量Coff(電位保持手段)と、を有している。nMOSトランジスタN1、N2は、定電流回路102のpMOSトランジスタP3、P4と同様、カレントミラー回路を構成している。入力変換回路101のpMOSトランジスタP1、P2の各々のゲート端子に入力電圧が入力されると、pMOSトランジスタP1には第1の電流I1が流れ、pMOSトランジスタP2には第2の電流I2が流れる。ここで、出力演算回路103においては、pMOSトランジスタP2にはのの電流I1をnMOSトランジスタN1が検出し、検出した電流をnMOSトランジスタN2にコピーする。そして、pMOSトランジスタP2を流れる第2の電流I2とnMOSトランジスタN2にコピーされた第3の電流I3との差に応じた第4の電流I4が出力されることになる。その出力電圧はnMOSトランジスタN2のソース端子とドレイン端子間の電位差である。なお、容量Coffの配置に起因する効果については後述する。

# [0022]

出力バッファ回路104は、pMOSトランジスタP5と、nMOSトランジスタN3と、容量Cb(電流出力記憶手段)と、を有している。pMOSトランジスタP5は、定電流回路102のpMOSトランジスタP3との間でカレントミラー回路を構成している。pMOSトランジスタP3のゲート端子はpMOSトランジスタP5のゲート端子に接続されており、pMOSトランジスタP3がゲート電圧をpMOSトランジスタP5のゲート端子に出力すると、pMOSトランジスタP5のドレイン端子にはpMOSトランジスタP5の素子の寸法比に比例した電流がコピーされる。出力バッファ回路104は、出力演算回路103からの出力電圧を一時的に保持するものであり、具体的には、出力演算回路103からの出力電圧を容量Cbに蓄えることができる。

#### [0023]

スイッチSW1(同電位手段)は、pMOSトランジスタP1のゲート端子とpMOSトランジスタP2のゲート端子間に、スイッチSW2は、反転入力端子とpMOSトランジスタP1のゲート端子間に、スイッチSW3は、nMOSトランジスタN2のゲート端子とドレイン端子間に、スイッチSW4は、出力演算回路103の出力と出力バッファ回路104の入力間に、それぞれ配置されている。スイッチSW1~4は、例えば、nMOSトランジスタやpMOSトランジスタから構成すればよい。

#### [0024]

スイッチSW1、SW3と、スイッチSW2、SW4とは、それぞれ一対になっており、スイッチSW1、SW3がオンのときは、スイッチSW2、SW4はオフ(以下、「オフセット検出期間」と定義する。)し、スイッチSW1、SW3がオフのときは、スイッチSW2、SW4はオン(以下、「電圧出力期間」と定義する。)する。本実施の形態にかかる差動増幅回路100は、上記の2つの期間、つまり、オフセット検出期間と電圧出力期間においてそれぞれ異なる動作を実行する。以下、この点について説明する。

#### [0025]

本実施の形態にかかる差動増幅回路100においては、上記のオフセット検出期間及び電圧検出期間は所定の周期で繰り返し到来する。繰り返しの周期はスイッチSW1~4を制御するクロックによって制御されている。

#### [0026]

次に、上記のオフセット検出期間及び電圧検出期間における差動増幅回路100の動作について説明する。

## [0027]

10

20

30

まず、オフセット検出期間について説明する。

#### [0028]

オフセット検出期間においては、スイッチSW1、SW3がオンし、スイッチSW2、SW4がオフする。この場合、pMOSトランジスタP1、P2のゲート端子間、及び、nMOSトランジスタN2のゲート端子とドレイン端子間がそれぞれ接続される一方、pMOSトランジスタP1のゲート端子と入力端子IN-間、及び、出力演算回路103の出力と出力バッファ回路104の入力間がそれぞれ切断される。

#### [0029]

上記の接続状態においては、pMOSトランジスタP1のゲート端子とpMOSトランジスタP2のゲート端子とはオン状態のスイッチSW1を介して同電位となるので、2つのpMOSトランジスタP1、P2が飽和特性領域で動作している限り、理想的には、同一の電流が流れることになる。

#### [0030]

しかしながら、上述したように、2つのpMOSトランジスタP1、P2対に特性ばらつきが生じていると、pMOSトランジスタP1、P2を流れる電流は互いに異なるものとなる。

#### [0031]

一方、スイッチSW3がオンすることにより、nMOSトランジスタN2のゲート端子とドレイン端子間が短絡され、nMOSトランジスタN2はnMOSトランジスタN1と同様、ダイオード接続されたMOSトランジスタとなる。したがって、pMOSトランジスタP1、P2の各々を流れる電流が同一であれば、2つのnMOSトランジスタN1、N2間に特性ばらつきが無い限り、2つのnMOSトランジスタN1、N2のドレイン端子に出力される電流は同一のゲート電圧に変換されることになる。

#### [0032]

しかしながら、上述したように、2つのpMOSトランジスタP1、P2対に特性ばらつきがあると、pMOSトランジスタP1、P2を流れる電流は互いに異なり、その結果、それらから変換されるnMOSトランジスタN1、N2の各々のゲート電圧が異なる値となる。さらに、nMOSトランジスタN1、N2対自体に特性ばらつきがあった場合、pMOSトランジスタP1、P2の各々を流れる電流が同一であったとしても、やはり、nMOSトランジスタN1、N2の各々のゲート端子に互いに異なるゲート電圧が出力されてしまう。

# [0033]

すなわち、入力変換回路101を構成するpMOSトランジスタP1、P2対の特性ばらつき及び出力演算回路103を構成するnMOSトランジスタN1、N2対の特性ばらつきに起因するオフセット電圧がnMOSトランジスタN1、N2のゲート電圧の電位差として現れることになる。本実施の形態の出力演算回路103を構成するnMOSトランジスタN1、N2のゲート端子間には容量Coffが配置されており、上記のnMOSトランジスタN1、N2のゲート電圧の電位差は容量Coffの両端に印加され、記憶される。

#### [0034]

次に、電圧出力期間について説明する。

#### [0035]

電圧出力期間においては、スイッチSW2、SW4がオンし、スイッチSW1、SW3がオフする。この場合、pMOSトランジスタP1、P2のゲート端子間、及び、nMOSトランジスタN2のゲート端子とドレイン端子間がそれぞれ切断される一方、pMOSトランジスタP1のゲート端子と入力端子IN-間、及び、出力演算回路103の出力と出力バッファ回路104の入力間がそれぞれ接続される。

#### [0036]

上記の接続状態においては、 p M O S トランジスタ P 1 のゲート端子が反転入力端子 I N - に接続され、 p M O S トランジスタ P 2 のゲート端子が非反転入力端子 I N + に接続

10

20

30

40

され、 p M O S トランジスタ P 1 、 P 2 は入力差動対を再び構成する。また、 n M O S トランジスタ N 2 のゲート端子とドレイン端子間は切断され、 n M O S トランジスタ N 1 、 N 2 はカレントミラー回路を再び構成する。以下、電圧出力期間における差動増幅回路 1 0 0 の動作について説明する。

## [0037]

まず、2つの入力電圧の微小な差信号が、入力端子IN-、入力端子IN+の各々を介して、入力変換回路101のpMOSトランジスタP1、P2の各々のゲート端子に入力されると、pMOSトランジスタP1にはVDD側からGND側へ向かう第1の電流I1が流れ、pMOSトランジスタP2にはVDD側からGND側へ向かう第2の電流I2が流れる。

#### [0038]

一方、入力変換回路 1 0 1 の p M O S トランジスタ P 1 を流れる第 1 の電流 I 1 を検出する出力演算回路 1 0 3 においては、 p M O S トランジスタ P 1 を流れる第 1 の電流 I 1 を n M O S トランジスタ N 1 が検出し、検出した電流を n M O S トランジスタ N 2 にコピーして G N D ラインに出力し、 n M O S トランジスタ N 2 に第 3 の電流 I 3 を流す。 そして、 p M O S トランジスタ P 2 を流れる第 2 の電流 I 2 と n M O S トランジスタ N 2 にコピーされた第 3 の電流 I 3 との差に応じた第 4 の電流 I 4 が出力されることになる。 その出力電圧は n M O S トランジスタ N 2 のソース端子とドレイン端子間の電位差である。

#### [0039]

ここで、上述したように、上記のオフセット検出期間においてオフセット電圧が出力演算回路103の容量Coffに記憶済みである。このため、入力端子IN+、IN-が同電位のとき、すなわち、差動電圧がゼロのとき、オフセット検出期間で設定された容量Coffの電位差によってnMOSトランジスタN2のゲート電圧が補正されて、pMOSトランジスタP1を流れる第1の電流I1をnMOSトランジスタN1によってnMOSトランジスタN2にコピーした第3の電流I3と、pMOSトランジスタP2を流れる第2の電流I2が等しくなる。すなわち、出力演算回路103からの出力電流がゼロとなり、オフセット電圧がゼロとなる。したがって、入力端子IN+、IN-の電位差を Vinとすると、 Vinに相当する電圧がオフセット電圧の影響を受けることなく、出力バッファ回路104に出力されることになる。

### [0040]

出力バッファ回路104は、出力演算回路103から出力される電圧を出力端子に出力する一方、出力演算回路103からの出力電圧を容量Cbに記憶する。電圧出力期間において容量Cbに記憶される、出力演算回路103の出力電圧に相当する電位差は、引き続き実行されるオフセット検出期間において、出力演算回路103からの出力電圧として、出力端子から出力される。そうすることにより、出力バッファ回路104は、オフセット検出期間においては、オフセット電圧を検出するために出力バッファ回路104から切り離された出力演算回路103に代わって、出力端子に電圧を出力し続けることができる。

#### [0041]

実際の動作は、上述したように、上記のオフセット検出期間と電圧出力期間がクロック信号に基づき所定の周期で繰り返されるので、出力演算回路103からの出力は離散的なものになる。しかしながら、オフセット検出期間においては出力バッファ回路104の容量 C b に記憶された電位差によって直前の電圧出力期間における出力演算回路103の出力電圧が保持されているので、差動増幅回路100の出力端子からは、リップルの少ない出力を得ることができる。すなわち、本実施の形態にかかる差動増幅回路100は、直流アンプとして使用すると非常に有効である。

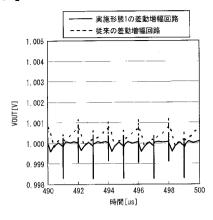

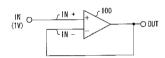

# [0042]

次に、本実施の形態にかかる差動増幅回路100の出力電圧の安定性について説明する。図2は、本実施の形態にかかる差動増幅回路100を用いた一般的なボルテージホロワの構成図である。このボルテージホロワは、差動増幅回路100の出力端子が反転入力端子に帰還接続されており、入力電圧の電圧を等倍して出力するバッファとして一般的に使

10

20

30

40

用されている構成である。

#### [0043]

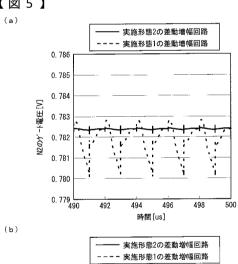

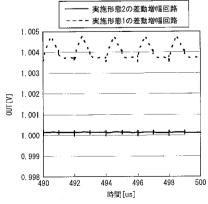

図3に、本実施の形態にかかる差動増幅回路100を用いた図2のボルテージホロワの出力波形と、図8の従来の差動増幅回路200aを用いたボルテージホロワの出力波形をそれぞれ示す。図3から明らかなように、本実施の形態にかかる差動増幅回路100を用いた場合の方が、リップルが少なく、安定した電圧を出力していることが分かる。

#### [0044]

なお、本実施の形態にかかる差動増幅回路100は、一般的なトランスコンダクタンス アンプの回路構成を用いたが、他の差動増幅回路の回路構成でも本実施の形態と同様の効 果がある。

## [0045]

また、本実施の形態にかかる差動増幅回路100においては、入力変換回路101をpMOSトランジスタP1、P2を用いて構成し、出力演算回路103をnMOSトランジスタN1、N2を用いて構成しているが、本発明はこの構成に限られるものではない。例えば、入力変換回路101はnMOSトランジスタ対を用いて構成し、出力演算回路103はpMOSトランジスタ対を用いて構成してもよい。この場合、差動増幅回路100の回路構成は、上記の入力変換回路101及び出力演算回路103を構成するトランジスタを含むすべてのトランジスタにおいて、n型とp型とを入れ替え、VDD及びGNDとの接続関係を逆にした構成となる。

#### [0046]

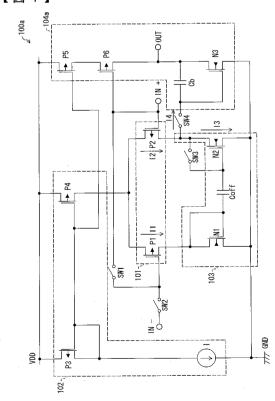

#### (実施の形態2)

次に、本発明の実施の形態 2 について説明する。図 4 は、本発明の実施の形態 2 にかかる差動増幅回路の構成を示す回路図である。本実施の形態にかかる差動増幅回路 1 0 0 a は、上記の実施の形態 1 の差動増幅回路 1 0 0 の出力バッファ回路 1 0 4 を構成する n M O S トランジスタ N 3 と p M O S トランジスタ P 5 間において p M O S トランジスタ P 6 が挿入された構成となっている。なお、本実施の形態にかかる差動増幅回路 1 0 0 a が上記の実施の形態 1 にかかる差動増幅回路 1 0 0 と異なる点は、上記の p M O S トランジスタ P 6 の挿入のみである。したがって、その他の構成については基本的には同一であるので、ここでは説明を繰り返さない。以下では、上記の p M O S トランジスタ P 6 の挿入に起因する効果について説明する。

# [0047]

まず、上記の p M O S トランジスタが存在しない場合、つまり、上記の実施の形態 1 にかかる差動増幅回路 1 0 0 における問題点について説明する。

#### [0048]

上記の実施の形態1にかかる差動増幅回路100においては、上述したように、オフセット電圧検出期間と電圧出力期間とが交互に繰り返される。このため、出力演算回路103を構成するnMOSトランジスタN2のドレイン端子の接続先は、上記の2つの期間の切り替えが行われる毎に、nMOSトランジスタN2のゲート端子とnMOSトランジスタN2のゲート端子間において遷移する。このため、nMOSトランジスタN2及びnMOSトランジスタN3の各々のゲート電圧が異なると、上記の2つの期間の切り替え毎に、nMOSトランジスタN2のドレイン電圧の変動を招くことになる。nMOSトランジスタN2のドレイン電圧の変動を招くことになる。nMOSトランジスタN2のドレイン電圧の変動を招くことになる。nMOSトランジスタN2のドレイン電圧の変動を招くことになる。その結果、容量Coffにかかる電圧は上記の2つの期間の切り替え周期毎に変動し、容量Coffに記憶されるオフセット電圧が安定せず、延いては、正しいオフセット補償が困難となってしまう。すなわち、差動増幅回路100にオフセット電圧が発生してしまうことになる。

#### [0049]

上記の問題点を解決するためには、 n M O S トランジスタ N 2 のゲート電圧と n M O S トランジスタ N 3 のゲート電圧とが極力等しくなるようにする必要がある。上記の実施の

10

20

30

40

形態 1 の差動増幅回路 1 0 0 では、V D D が十分大きければ、n M O S トランジスタN 2 に流れる電流はp M O S トランジスタP 4 から供給されるバイアス電流、n M O S トランジスタN 3 に流れる電流はp M O S トランジスタP 5 から供給されるバイアス電流とみなすことができる。このため、n M O S トランジスタN 2 とn M O S トランジスタN 3 の各々のゲート電圧は、p M O S トランジスタP 4、P 5 から供給されるバイアス電流によって決まり、p M O S トランジスタP 4、P 5 の各々バイアス電流と、n M O S トランジスタN 2 とn M O S トランジスタN 3 とのゲート面積の比を等しくすることで、n M O S トランジスタN 2 とn M O S トランジスタN 3 のゲート電圧をほぼ同一とすることができる

#### [0050]

ところが、低電源電圧化が進むにつれて、 n M O S トランジスタ N 2 に流れる電流を p M O S トランジスタ P 4 から供給されるバイアス電流とみなすことができなくなる状況が予想される。すなわち、電源電圧の低下に従って p M O S トランジスタ P 4 、 P 5 の A 2 に向かって流れる電流経路には入力変換回路 1 0 1 を構成する p M O S トランジスタ P 2 に対応する p M O S トランジスタ P 2 が配置されている。一方、 p M O S トランジスタ P 2 に対応する p M O S トランジスタ P 2 に対応する p M O S トランジスタ P 2 に対応する p M O S トランジスタ B は存在しない。したがって、 p M O S トランジスタ P 4 のバイアス電流の低下に伴って p M O S トランジスタ P 2 による電流値の減少が顕在化し、 このため、 p M O S トランジスタ P 4 、 P 5 のバイアス電流が等しい場合であっても、 n M O S トランジスタ N 2 、 N 3 の各々に流れ込むバイアス電流が異なるものとなってしまう。すなわち、 n M O S トランジスタ N 2 、 N 3 のゲート電圧間に差異が生じてしまう。

#### [0051]

これに対し、本発明の実施の形態2にかかる差動増幅回路100aは、上記の問題を解消するために、上記の実施の形態1の出力バッファ回路104においてnMOSトランジスタN3とpMOSトランジスタP5間にpMOSトランジスタP6が挿入された出力バッファ回路104に代えて備えている。pMOSトランジスタP6は、pMOSトランジスタP2に対応し、pMOSトランジスタP5からnMOSトランジスタN3に向かって流れる電流経路上に配置されている。

[ 0 0 5 2 ]

pMOSトランジスタP6のゲート端子は、pMOSトランジスタP2のゲート端子に接続されているので、電源電圧が小さくなった場合でも、nMOSトランジスタN2、N3に流れ込む電流は、pMOSトランジスタP2、P6の影響を受けて同じように減少する。したがって、nMOSトランジスタN2、N3のゲート電圧はほぼ一定に保たれる。【0053】

図 5 に、上記の実施の形態 1 にかかる差動増幅回路 1 0 0 を用いた図 2 のボルテージホロワの出力波形と、図 4 の本実施の形態 2 にかかる差動増幅回路 1 0 0 a を用いたボルテージホロワの出力波形をそれぞれ示す。なお、電源電圧は 1 . 9 V とした。

#### [0054]

図 5 (a)に示すように、上記の実施の形態 1 にかかる差動増幅回路 1 0 0 を用いた場合は、 n M O S トランジスタ N 2 のゲート電圧が変動しているのに対し、本実施の形態 2 にかかる差動増幅回路 1 0 0 a を用いた場合は、ほとんど変動していないことが分かる。

[0055]

また、図5(b)に示すように、上記の実施の形態1にかかる差動増幅回路100を用いた場合は、入力電圧1Vからずれた出力電圧が出ているのに対し、本実施の形態2にかかる差動増幅回路100aを用いた場合は、ほぼ1Vの出力が出ていることがわかる。

#### [0056]

本発明の実施の形態 2 においては、電源電圧が 1 . 9 V の場合を例に挙げたが、上記のバイアス電流の減少は電源電圧が 2 V 以下で起こり易くなるので、本発明の実施の形態 2 にかかる差動増幅回路 1 0 0 a は 2 V 以下で駆動するときに有用である。

10

20

30

40

#### [0057]

また、本発明の実施の形態 2 にかかる差動増幅回路 1 0 0 a は、上記の実施の形態 1 と同様に、一般的なトランスコンダクタンスアンプの回路構成を用いたが、他の差動増幅回路の回路構成でも本実施の形態と同様の効果がある。

#### [0058]

また、本発明の実施の形態 2 にかかる差動増幅回路 1 0 0 a においては、 p M O S トランジスタ P 6 を新たに挿入しているが、 p M O S トランジスタ P 6 に代えて、所定の抵抗値を持つ抵抗を挿入しても構わない。この場合、挿入される抵抗の抵抗値は、 p M O S トランジスタ P 2 によって減少する電流値に合わせて設定すればよい。

#### [0059]

さらに、本発明の実施の形態 2 にかかる差動増幅回路 1 0 0 a においては、入力変換回路 1 0 1を p M O S トランジスタ P 1、 P 2を用いて構成し、出力演算回路 1 0 3を n M O S トランジスタ N 1、 N 2を用いて構成しているが、本発明はこの構成に限られるものではない。例えば、入力変換回路 1 0 1 は n M O S トランジスタ対を用いて構成し、出力演算回路 1 0 3 は p M O S トランジスタ対を用いて構成してもよい。この場合、差動増幅回路 1 0 0 の回路構成は、上記の入力変換回路 1 0 1 及び出力演算回路 1 0 3を構成するトランジスタを含むすべてのトランジスタにおいて、 n 型と p 型とを入れ替え、 V D D 及び G N D との接続関係を逆にした構成となる。

#### [0060]

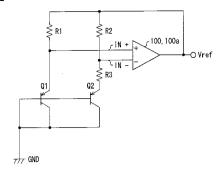

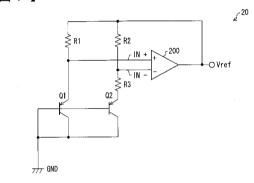

# (実施の形態3)

次に、本発明の実施の形態3について説明する。本実施の形態は、上記の実施の形態1 及び2にかかる差動増幅回路を用いた電源回路にかかる形態である。図6は、本発明の実 施の形態1及び2にかかる差動増幅回路を用いた電源回路の構成を示す図である。

#### [0061]

#### [0062]

本実施の形態にかかる電源回路においては、ダイオード接続されたpnpバイポーラトランジスタQ1、Q2のベース端子とエミッタ端子間電圧の差を検出して基準電圧出力端子から出力される電圧を得る形式で、出力電圧を約1.25Vとすることで温度依存性のない基準電圧を得ることができ、一般的に用いられる回路形式である。基準電圧のばらつき要因として最も支配的なものは、上述したように差動増幅回路のオフセット電圧であり、このオフセット電圧をVoff、オフセットがゼロの時の出力電圧をVrefとすると、オフセット電圧Voffがある場合の出力電圧Vref^は、以下の式で表わされる。

#### [0063]

Vref'=Vref-(1+(R2/R3)) x V o f f

上記の式から明らかなように、オフセット電圧 Voffは(1+R2/R3)倍されて出力電圧に現れる。

#### [0064]

本発明の実施の形態 3 にかかる電源回路においては、上記の実施の形態 1 及び 2 にかかる差動増幅回路 1 0 0 、 1 0 0 a を用いることにより、オフセット電圧が非常に少ないので、ばらつきの少ない出力電圧を得ることができる。また、リップルも非常に小さいので、ノイズ性能についても優れている。

#### [0065]

また、上記の実施の形態 2 にかかる差動増幅回路 1 0 0 a を用いた場合であれば、 2 V 以下の低電圧の駆動でも良好な出力電圧を得ることができる。

10

20

30

40

#### [0066]

なお、本実施の形態の電源回路は、一般的にはバンドギャップレギュレータの回路構成 の一例であるが、差動増幅回路を利用した電源回路であれば、本実施の形態と同様の効果 がある。

## [0067]

本発明は上述した各実施の形態に限定されるものではなく、請求項に示した範囲で種々 の変更が可能であり、異なる実施の形態にそれぞれ開示された技術的手段を適宜組み合わ せて得られる実施の形態についても本発明の技術的範囲に含まれる。

【産業上の利用可能性】

[0068]

本発明にかかる差動増幅回路及びそれを用いた電源回路は、低電源電圧を用いて動作さ せる場合でも安定して基準電圧を発生することができるので、低電源電圧用アナログ回路 の基準電圧を発生する電源回路に適用できる。

【図面の簡単な説明】

[0069]

- 【図1】本発明の実施の形態1にかかる差動増幅回路の構成を示す回路図である。

- 【図2】本発明の実施の形態1にかかるボルテージホロワの構成図である。

- 【図3】本発明の実施の形態1にかかるボルテージホロワの出力波形を示すグラフ図であ

- 【図4】本発明の実施の形態2にかかる差動増幅回路の構成を示す回路図である。

- 【図5】本発明の実施の形態2にかかるボルテージホロワの出力波形を示すグラフ図であ

- 【図6】本発明の実施の形態3にかかる電源回路の構成を示す回路図である。

- 【図7】従来のバンドギャップレギュレータを用いた電源回路の構成を示す回路図である

- 【図8】従来の差動増幅回路の構成を示す回路図である。

【符号の説明】

[0070]

2 0 電源回路

100、100a、200、200a 差動増幅回路

入力变換回路(入力変換手段) 1 0 1

1 0 2 定電流回路

1 0 3 出力演算回路(出力演算手段)

104、104a 出力バッファ回路(出力バッファ手段)

IN-反転入力端子(第1の電圧入力)

非反転入力端子(第2の電圧入力) T N +

- I 1 第1の電流(第1の電流入力)

- I 2 第2の電流(第2の電流入力)

- Ι3 第3の電流(第3の電流入力)

- 第4の電流(第4の電流入力) I 4

スイッチ(同電位手段) S W 1

SW2、SW3、SW4

Coff 容量(電位保持手段)

C b 容量(電流出力記憶手段)

R 1 、 R 2 、 R 3 抵抗(基準電圧生成手段)

P1、P2、P3、P4、P5、P6 pMOSトランジスタ

N 1 、 N 2 、 N 3 nMOSトランジスタ

Ι 電流源 10

20

30

# 【図1】

# 【図3】

# 【図2】

# 【図4】

# 【図5】

# 【図6】

# 【図7】

# 【図8】

# フロントページの続き

# (72)発明者 加納 賢次 兵庫県伊丹市松ヶ丘1丁目185番地

審査官 矢頭 尚之

(56)参考文献 特開2002-202748(JP,A) 特開2005-182494(JP,A) 特開平08-320730(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 3 F 3 / 4 5 G 0 5 F 3 / 3 0 H 0 3 F 3 / 3 4