# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 117200752 A (43) 申请公布日 2023. 12. 08

(21)申请号 202311200252.4

(22)申请日 2023.09.18

(71) 申请人 江苏帝奥微电子股份有限公司 地址 226000 江苏省南通市崇州大道60号 南通创新区紫琅科技城8号楼6层

(72) 发明人 傅科成 周高翔

(74) **专利代理机构** 南京钟山专利代理有限公司 32252

专利代理师 陈亮亮

(51) Int.CI.

HO3K 3/012 (2006.01)

**HO3K** 5/22 (2006.01)

HO3K 19/20 (2006.01)

权利要求书2页 说明书4页 附图5页

#### (54) 发明名称

一种同步高频方波信号电路

#### (57)摘要

本发明公开了一种同步高频方波信号电路,包含上升沿触发脉冲电路、固定低电平发生器和电容电荷比较器,上升沿触发脉冲电路的输入端输入外部方波信号CLK\_IN,上升沿触发脉冲电路的输出端与固定低电平发生器的输入端连接,固定低电平发生器的第一输出端与电容电荷比较器的第一输入端连接,固定低电平发生器的第二输出端输出第一输出信号CLK\_OUT,电容电荷比较器的输出端输出第二输出信号CLK\_EN,电容电荷比较器的第二输入端输入第一偏置电流镜信号I1,电容电荷比较器的第三输入端输入第一偏置电流镜信号I1,电容电荷比较器的第三输入端输入第二偏置电流镜信号I2。本发明电路结构简单,占芯片面积小,功耗低的电路场合下,可以实现开关电源芯片同步外部高频方波信号的电路,而且相比传统方案有更大的同步频率范围。

- 1.一种同步高频方波信号电路,其特征在于:包含上升沿触发脉冲电路、固定低电平发生器和电容电荷比较器,上升沿触发脉冲电路的输入端输入外部方波信号CLK\_IN,上升沿触发脉冲电路的输出端与固定低电平发生器的输入端连接,固定低电平发生器的第一输出端与电容电荷比较器的第一输入端连接,固定低电平发生器的第二输出端输出第一输出信号CLK\_OUT,电容电荷比较器的输出端输出第二输出信号CLK\_EN,电容电荷比较器的第二输入端输入第一偏置电流镜信号I1,电容电荷比较器的第三输入端输入第二偏置电流镜信号I2。

- 2.根据权利要求1所述的一种同步高频方波信号电路,其特征在于:所述上升沿触发脉冲电路包含第一反相器、第二反相器、第三反相器、第一异或门、第一电阻和第一电容,第一反相器的输入端和第二反相器的输入端相连并且输入外部方波信号CLK\_IN,第一反相器的输出端与第一异或门的第一输入端连接,第二反相器的输出端与第一电阻的一端连接,第一电阻的另一端与第三反相器的输入端和第一电容的一端连接,第一电容的另一端接地,第三反相器的输出端与第一异或门的第二输入端连接,第一异或门的输出端输出第一方波信号R。

- 3.根据权利要求1所述的一种同步高频方波信号电路,其特征在于:所述固定低电平发生器包含第二电阻、第二电容、PNP三极管、第二异或门、第三异或门和第四反相器,第二异或门的第一输入端输入第一方波信号R,第二异或门的第二输入端与第三异或门的输出端、第四反相器的输入端、PNP三极管的基极和第二电阻的一端连接并产生第四信号QB,第二异或门的输出端与第三异或门的第一输入端连接并输出第二方波信号Q,第四反相器的输出端输出第一输出信号CLK\_OUT,PNP三极管的发射极与第二电阻的另一端、第二电容的一端和第三异或门的第二输入端连接并产生第三信号S,PNP三极管的集电极接地,第二电容的另一端接地。

- 4.根据权利要求1所述的一种同步高频方波信号电路,其特征在于:所述电容电荷比较器包含低压增强型NMOS管、第一低压增强型PMOS管、第二低压增强型PMOS管、第三电容、施密特触发器和第五反相器,第一低压增强型PMOS管的源极连接电源VIN,第一低压增强型PMOS管的栅极输入第一偏置电流镜信号I1,第一低压增强型PMOS管的漏极连接第二低压增强型PMOS管的源极,第二低压增强型PMOS管的栅极输入第二方波信号Q,第二低压增强型PMOS管的漏极与低压增强型NMOS管的漏极、第三电容的一端和施密特触发器的输入端连接并产生第五信号V\_CMP,低压增强型NMOS管的栅极输入第二偏置电流镜信号I2,低压增强型NMOS管的源极接地,第三电容的另一端接地,施密特触发器的输出端与第五反相器的输入端连接,第五反相器的输出端输出第二输出信号CLK EN。

- 5.根据权利要求2所述的一种同步高频方波信号电路,其特征在于:所述第一方波信号 R是一个固定20ns的窄脉冲。

- 6.根据权利要求3所述的一种同步高频方波信号电路,其特征在于:所述第二方波信号 Q是一个固定低电平时间的方波信号。

- 7.根据权利要求6所述的一种同步高频方波信号电路,其特征在于:所述第二方波信号 Q的低电平时间T0FF的值由第二电阻44和第二电容46的取值大小决定。

- 8.根据权利要求7所述的一种同步高频方波信号电路,其特征在于:所述第一偏置电流 镜信号I1和第二偏置电流镜信号I2由开关电源芯片内部电流镜偏置产生。

9.根据权利要求8所述的一种同步高频方波信号电路,其特征在于:所述外部方波信号 CLK\_IN的周期T < [TOFF\*(I1+I2)]/I2时,实现高频方波信号同步。

# 一种同步高频方波信号电路

#### 技术领域

[0001] 本发明涉及一种方波信号电路,特别是一种同步高频方波信号电路,属于半导体集成电路技术领域。

### 背景技术

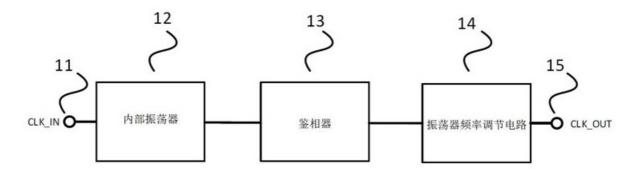

[0002] 在开关电源芯片等应用中,一般在芯片内部集成振荡器作为开关电源的开关,但是内部振荡器产生的方波频率会随工艺,供电电压,温度的变化而变化;随着芯片应用的多样化,很多开关电源兼容通过MCU直接对芯片引脚输入周期性的方波信号,作为开关电源的开关;如果要同步MCU发出的方波信号给芯片内部用,传统的做法是:芯片内部做一个带频率调节功能的振荡器12,鉴相器13用于比较芯片内部振荡器的频率和外部方波频率的差值,频率调节电路14根据频率差值来调节芯片内部振荡器的频率,直至芯片内部振荡器的频率和外部方波频率一致,作为开关电源的开关;这种传统做法的缺点是电路较为复杂,如图7所示:需要振荡器12,鉴相器13,以及频率调节电路14;这些模块电路结构都较为复杂,占用较大的芯片面积,功耗过高,而且频率可调节范围较小;在芯片集成度越来越高,功耗越来越低的背景下,传统方案不具备优势。

## 发明内容

[0003] 本发明所要解决的技术问题是提供一种同步高频方波信号电路,电路结构简单且占用芯片面积小、功耗低。

[0004] 为解决上述技术问题,本发明所采用的技术方案是:

一种同步高频方波信号电路,包含上升沿触发脉冲电路、固定低电平发生器和电容电荷比较器,上升沿触发脉冲电路的输入端输入外部方波信号CLK\_IN,上升沿触发脉冲电路的输出端与固定低电平发生器的输入端连接,固定低电平发生器的第一输出端与电容电荷比较器的第一输入端连接,固定低电平发生器的第二输出端输出第一输出信号CLK\_OUT,电容电荷比较器的输出端输出第二输出信号CLK\_EN,电容电荷比较器的第二输入端输入第一偏置电流镜信号I1,电容电荷比较器的第三输入端输入第二偏置电流镜信号I2。

[0005] 进一步地,所述上升沿触发脉冲电路包含第一反相器、第二反相器、第三反相器、第一异或门、第一电阻和第一电容,第一反相器的输入端和第二反相器的输入端相连并且输入外部方波信号CLK\_IN,第一反相器的输出端与第一异或门的第一输入端连接,第二反相器的输出端与第一电阻的一端连接,第一电阻的另一端与第三反相器的输入端和第一电容的一端连接,第一电容的另一端接地,第三反相器的输出端与第一异或门的第二输入端连接,第一异或门的输出端输出第一方波信号R。

[0006] 进一步地,所述固定低电平发生器包含第二电阻、第二电容、PNP三极管、第二异或门、第三异或门和第四反相器,第二异或门的第一输入端输入第一方波信号R,第二异或门的第二输入端与第三异或门的输出端、第四反相器的输入端、PNP三极管的基极和第二电阻的一端连接并产生第四信号QB,第二异或门的输出端与第三异或门的第一输入端连接并输

出第二方波信号Q,第四反相器的输出端输出第一输出信号CLK\_OUT,PNP三极管的发射极与第二电阻的另一端、第二电容的一端和第三异或门的第二输入端连接并产生第三信号S,PNP三极管的集电极接地,第二电容的另一端接地。

[0007] 进一步地,所述电容电荷比较器包含低压增强型NMOS管、第一低压增强型PMOS管、第二低压增强型PMOS管、第三电容、施密特触发器和第五反相器,第一低压增强型PMOS管的源极连接电源VIN,第一低压增强型PMOS管的栅极输入第一偏置电流镜信号I1,第一低压增强型PMOS管的漏极连接第二低压增强型PMOS管的源极,第二低压增强型PMOS管的栅极输入第二方波信号Q,第二低压增强型PMOS管的漏极与低压增强型NMOS管的漏极、第三电容的一端和施密特触发器的输入端连接并产生第五信号V\_CMP,低压增强型NMOS管的栅极输入第二偏置电流镜信号I2,低压增强型NMOS管的源极接地,第三电容的另一端接地,施密特触发器的输出端与第五反相器的输入端连接,第五反相器的输出端输出第二输出信号CLK\_EN。

[0008] 进一步地,所述第一方波信号R是一个固定20ns的窄脉冲。

[0009] 讲一步地,所述第二方波信号Q是一个固定低电平时间的方波信号。

[0010] 进一步地,所述第二方波信号Q的低电平时间T0FF的值由第二电阻44和第二电容46的取值大小决定。

[0011] 进一步地,所述第一偏置电流镜信号I1和第二偏置电流镜信号I2由开关电源芯片内部电流镜偏置产生。

[0012] 进一步地,所述外部方波信号CLK\_IN的周期T < [T0FF\*(I1+I2)]/I2时,实现高频方波信号同步。

[0013] 本发明与现有技术相比,具有以下优点和效果:本发明提供了一种同步高频方波信号电路,通过上升沿触发脉冲电路、固定低电平发生器和电荷比较器三个简单的结构即可正常工作,电路结构简单,占芯片面积小,功耗低的电路场合下,可以实现开关电源芯片同步外部高频方波信号的电路,而且相比传统方案有更大的同步频率范围;本发明除了开关电源芯片,也可应用于其他需要同步芯片外部高频方波信号的芯片。

#### 附图说明

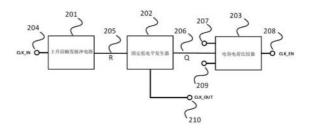

[0014] 图1是本发明的一种同步高频方波信号电路的示意图。

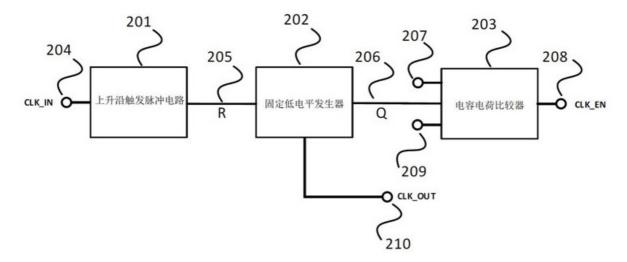

[0015] 图2是本发明的一种同步高频方波信号电路的电路图。

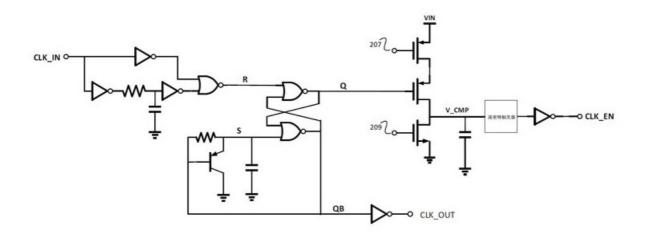

[0016] 图3是本发明的上升沿触发脉冲电路的电路图。

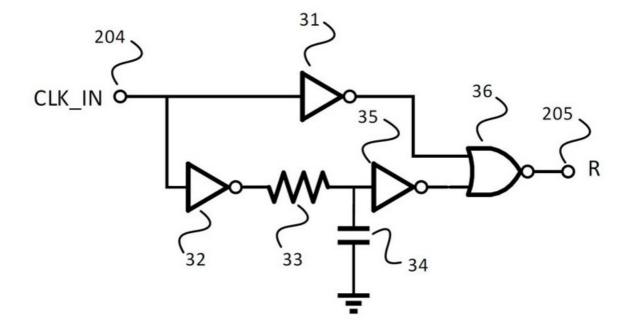

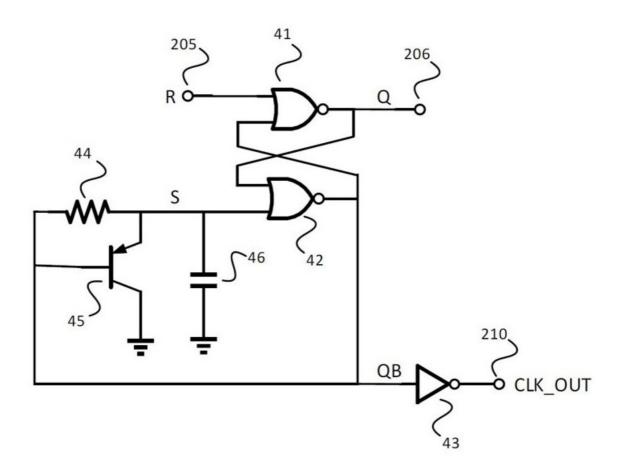

[0017] 图4是本发明的固定低电平发生器的电路图。

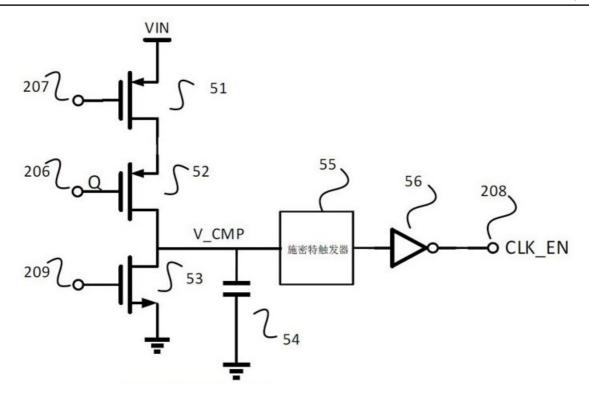

[0018] 图5是本发明的电容电荷比较器的电路图。

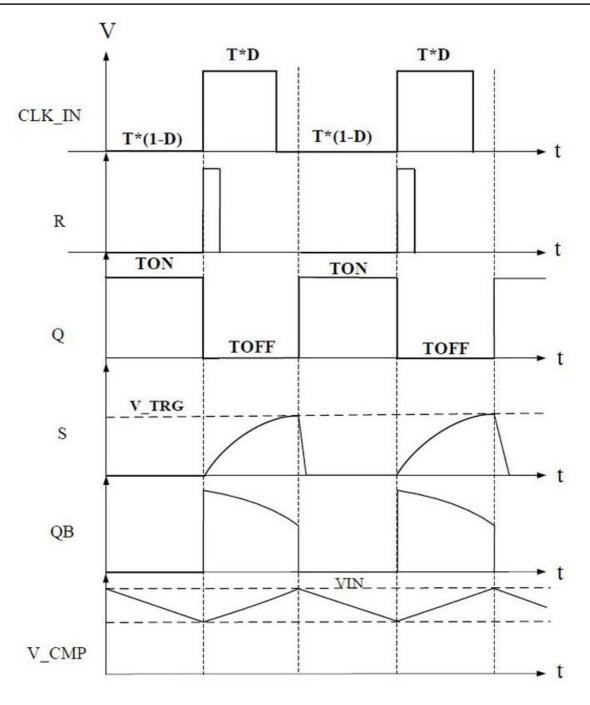

[0019] 图6是本发明的实施例的各信号波形图。

[0020] 图7是现有技术的同步高频锁定电路的电路图。

#### 具体实施方式

[0021] 为了详细阐述本发明为达到预定技术目的而所采取的技术方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清晰、完整地描述,显然,所描述的实施例仅仅是本发明的部分实施例,而不是全部的实施例,并且,在不付出创造性劳动的前提下,本发明的实施例中的技术手段或技术特征可以替换,下面将参考附图并结合实施例

来详细说明本发明。

[0022] 如图1和图2所示,本发明的一种同步高频方波信号电路,包含上升沿触发脉冲电路201、固定低电平发生器202和电容电荷比较器203,上升沿触发脉冲电路201的输入端输入外部方波信号CLK\_IN,上升沿触发脉冲电路201的输出端与固定低电平发生器202的输入端连接,固定低电平发生器202的第一输出端与电容电荷比较器203的第一输入端连接,固定低电平发生器202的第二输出端输出第一输出信号CLK\_OUT,电容电荷比较器203的输出端输出第二输出信号CLK\_EN,电容电荷比较器203的第二输入端输入第一偏置电流镜信号I1,电容电荷比较器203的第三输入端输入第二偏置电流镜信号I2。

[0023] 如图3所示,上升沿触发脉冲电路201包含第一反相器31、第二反相器32、第三反相器35、第一异或门36、第一电阻33和第一电容34,第一反相器31的输入端和第二反相器32的输入端相连并且输入外部方波信号CLK\_IN,第一反相器31的输出端与第一异或门36的第一输入端连接,第二反相器32的输出端与第一电阻33的一端连接,第一电阻33的另一端与第三反相器35的输入端和第一电容34的一端连接,第一电容34的另一端接地,第三反相器35的输出端与第一异或门36的第二输入端连接,第一异或门36的输出端输出第一方波信号R。 [0024] 其中,第一方波信号R是一个固定20ns的窄脉冲。无论外部方波信号CLK\_IN的占空比是什么值,经过上升沿触发脉冲电路201都会产生一个固定20ns左右的窄脉冲的第一方波信号R。

[0025] 上升沿触发脉冲电路201的工作原理为:外部方波信号CLK\_IN的上升沿经过第一反相器31输出一个相对外部方波信号CLK\_IN没有延时的下降沿,外部方波信号CLK\_IN经过第二反相器32、第一电阻33、第一电容34和第三反相器35,输出一个相对外部方波信号CLK\_IN延时20ns的上升沿,第一异或门36的输出信号205(也就是第一方波信号R)是一个固定20ns的窄脉冲。无论外部方波信号CLK\_IN的占空比是什么值,经过上升沿触发脉冲电路201都会产生一个固定20ns左右的窄脉冲的第一方波信号R。

[0026] 如图4所示,固定低电平发生器202包含第二电阻44、第二电容46、PNP三极管45、第二异或门41、第三异或门42和第四反相器43,第二异或门41的第一输入端输入第一方波信号R,第二异或门41的第二输入端与第三异或门42的输出端、第四反相器43的输入端、PNP三极管45的基极和第二电阻44的一端连接并产生第四信号QB,第二异或门41的输出端与第三异或门42的第一输入端连接并输出第二方波信号Q,第四反相器43的输出端输出第一输出信号CLK\_OUT,PNP三极管45的发射极与第二电阻44的另一端、第二电容46的一端和第三异或门42的第二输入端连接并产生第三信号S,PNP三极管45的集电极接地,第二电容46的另一端接地。

[0027] 其中,第二方波信号Q是一个固定低电平时间的方波信号。上升沿触发脉冲电路201输出的第一方波信号R经过固定低电平发生器电路202,产生一个固定低电平时间的方波信号,即第二方波信号Q。第一输出信号CLK\_OUT是同步输入方波信号后的输出信号,第一输出信号CLK\_OUT是否给芯片内部使用,取决于第二输出信号CLK\_EN的高低。

[0028] 如图5所示,电容电荷比较器203包含低压增强型NMOS管53、第一低压增强型PMOS管51、第二低压增强型PMOS管52、第三电容54、施密特触发器55和第五反相器56,第一低压增强型PMOS管51的源极连接电源VIN,第一低压增强型PMOS管51的栅极输入第一偏置电流镜信号I1,第一低压增强型PMOS管51的漏极连接第二低压增强型PMOS管52的源极,第二低

压增强型PMOS管52的栅极输入第二方波信号Q,第二低压增强型PMOS管52的漏极与低压增强型NMOS管51的漏极、第三电容54的一端和施密特触发器55的输入端连接并产生第五信号 V\_CMP,低压增强型NMOS管53的栅极输入第二偏置电流镜信号I2,低压增强型NMOS管53的源极接地,第三电容54的另一端接地,施密特触发器55的输出端与第五反相器56的输入端连接,第五反相器56的输出端输出第二输出信号CLK\_EN。

[0029] 固定低电平发生器202的输出的第二方波信号Q经过电容电荷比较器203,判断输入的外部方波信号CLK\_IN是否符合频率要求。如果符合要求,外部方波信号CLK\_IN就供芯片使用;如果不符合频率要求,阻断外部方波信号CLK\_IN给芯片使用。

[0030] 如图3和图6所示,外部方波信号CLK\_IN的周期是T,占空比是D,那么外部方波信号CLK\_IN的高电平的时间是T\*D,低电平的时间是T\*(1-D),无论外部方波信号CLK\_IN的占空比D的值是多少,第一方波信号R的高电平都是固定值20ns左右。

[0031] 第二方波信号Q的低电平时间TOFF的值由第二电阻44和第二电容46的取值大小决定。第三信号S的电压的上升曲线斜率取决于第二电阻44和第二电容46的取值大小,当第三信号S的电压升高到第三异或门42的阈值电压时,第二方波信号Q和第四信号QB的电压翻转,因此,第二电阻44和第二电容46的取值大小决定了第二方波信号Q的低电平时间TOFF的值。

[0032] 第一偏置电流镜信号I1和第二偏置电流镜信号I2由开关电源芯片内部电流镜偏置产生。

[0033] 第二电容46的电容值为C,外部方波信号CLK\_IN假设周期是T,根据图3和图6,第一方波信号R是一个周期为T,高电平时间是20ns的方波信号,第二方波信号Q是一个周期为T,低电平时间是T0FF的方波信号,第二低压增强型PMOS管52的栅端206(也就是第二方波信号Q),是一个周期为T,低电平时间是T0FF的方波信号;第一低压增强型PMOS管51的栅极输入第一偏置电流镜信号I1,低压增强型NMOS管53的栅极输入第二偏置电流镜信号I2。

[0034] 综上所述,外部方波信号CLK\_IN在一个周期后,第五信号V\_CMP=[T0FF\*I1-(T-T0FF)\*I2]/C=[T0FF\*(I1+I2)-T\*I2]/C,当 T=[T0FF\*(I1+I2)]/I2时,外部方波信号CLK\_IN经过多个周期后第五信号V\_CMP既不升高也不降低,维持电压;当 T>[T0FF\*(I1+I2)]/I2时,外部方波信号CLK\_IN经过多个周期后第五信号V\_CMP降低至0,则第二输出信号CLK\_EN=0,外部方波信号CLK\_IN到芯片内部传输关闭;当 T<[T0FF\*(I1+I2)]/I2时,外部方波信号CLK\_IN经过多个周期后第五信号V\_CMP升高至VIN,则第二输出信号CLK\_EN=1,外部方波信号CLK\_IN到芯片内部传输打开。因此,外部方波信号CLK\_IN的周期T<[T0FF\*(I1+I2)]/I2时,也就是说外部方波信号CLK\_IN的频率要高于I2/[T0FF\*(I1+I2)],才能实现高频方波信号同步。

[0035] 以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容做出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案内容,依据本发明的技术实质,在本发明的精神和原则之内,对以上实施例所作的任何简单的修改、等同替换与改进等,均仍属于本发明技术方案的保护范围之内。

图 1

图 2

图 3

图 4

图 5

图 6

图 7