# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*G11C* 11/4076 (2006.01) *G11C* 7/22 (2015.01) *H03L* 7/081 (2006.01) *H03L* 7/085 (2006.01)

(52) CPC특허분류 G11C 11/4076 (2013.01) G11C 7/22 (2018.05)

(21) 출원번호 **10-2020-0118435**

(22) 출원일자 **2020년09월15일**

심사청구일자 **없음**

(11) 공개번호 10-2022-0036175

(43) 공개일자

(71) 출원인

#### 삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

2022년03월22일

(72) 발명자

#### 최훈대

경기도 화성시 동탄순환대로21길 53 (청계동, 롯 데캐슬 알바트로스) 1306동 1701호

(74) 대리인

특허법인씨엔에스

전체 청구항 수 : 총 10 항

#### (54) 발명의 명칭 메모리 장치 및 그것의 클록 라킹 방법

#### (57) 요 약

본 발명의 메모리 장치의 클록 라킹 방법은, 내부 전압이 안정화 되기 전에, 지연 고정 루프 회로에서 이니셜 락동작을 수행하는 단계, 상기 내부 전압이 안정화 된 후에, 윈도우 검출 회로를 이용하여 기준 클록과 피드백 클록 사이의 클록 스큐를 모니터링 하는 단계, 및 상기 지연 고정 루프 회로에서 상기 클록 스큐에 대응하는 다이나믹 지연 제어를 이용하여 리-락 동작을 수행하는 단계를 포함할 수 있다.

#### 대표도

## (52) CPC특허분류

**HO3L** 7/0814 (2013.01) **HO3L** 7/085 (2013.01)

#### 명 세 서

#### 청구범위

#### 청구항 1

제 1 코드값에 따라 기준 클록을 지연시킴으로써 제 1 지연 클록을 출력하는 제 1 지연 라인; 제 2 코드값에 따라 제 1 지연 클록을 지연시킴으로써 제 2 지연 클록을 출력하는 제 2 지연 라인; 제 1 위상 차이값에 따라 상기 제 1 코드값을 생성하거나, 제 2 위상 차이값에 따라 상기 제 1 코드값을 생성하는 제 1 지연 라인 제어기; 상기 제 2 위상 차이값에 따라 상기 제 2 지연 라인 제어기;

상기 기준 클록과 피드백 클록의 클록 스큐에 대응하는 모니터 검출 신호에 응답하여 상기 제 2 위상 차이값을 상기 제 1 지연 라인 제어기 및 상기 제 2 지연 라인 제어기 중에서 어느 하나로 출력하는 디-멀티플렉서;

상기 기준 클록과 상기 피드백 클록 사이의 상기 제 1 위상 차이값을 검출하는 제 1 위상 검출기; 상기 기준 클록과 상기 피드백 클록 사이의 상기 제 2 위상 차이값을 검출하는 제 2 위상 검출기; 상기 제 2 지연 클록을 수신하고 내부 클록을 발생하는 클록 패스; 상기 내부 클록에 동기하여 데이터 스트로브 신호를 출력하는 출력 버퍼; 상기 클록 패스의 지연량만큼 상기 제 2 지연 클록을 지연시키는 클록 패스 레플리카; 및 상기 클록 패스 레플리카로부터 출력하는 클록을 상기 출력 버퍼의 지연량만큼 지연시킴으로써 상기 피드백 클록을 발생하는 출력 버퍼 레플리카를 포함하는 메모리 장치.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 위상 검출기를 활성화 하기 위한 제 1 활성화 신호 및 상기 제 2 위상 검출기를 활성화 하기 위한 제 2 활성화 신호를 발생하는 지연 고정 루프 제어기를 더 포함하는 메모리 장치.

#### 청구항 3

제 1 항에 있어서,

이니셜 락 구간에서.

상기 제 1 위상 검출기를 활성화시킴으로써 코어스 락 동작이 수행되고.

상기 코어스 락 동작 이후에 상기 제 2 위상 검출기를 활성화시킴으로써 파인 락 동작이 수행되는 것을 특징으로 하는 메모리 장치.

#### 청구항 4

제 3 항에 있어서,

상기 파인 락 동작이 수행된 후에, 상기 제 2 위상 검출기는 활성화 상태를 유지하는 것을 특징으로 하는 메모리 장치.

### 청구항 5

제 1 항에 있어서,

상기 기준 클록과 상기 피드백 클록의 클록 스큐를 감지함으로써 상기 모니터 검출 신호를 발생하는 윈도우 검출 회로를 더 포함하는 메모리 장치.

#### 청구항 6

제 5 항에 있어서,

상기 윈도우 검출 회로는 내부 전압 안정화 신호에 응답하여 활성화되는 것을 특징으로 하는 메모리 장치.

#### 청구항 7

제 5 항에 있어서,

상기 윈도우 검출 회로는,

상기 기준 클록과 상기 피드백 클록의 클록 스큐에 대응하는 위상 검출 신호를 발생하는 클록 스큐 모니터;

상기 위상 검출 신호를 내부 클록에 동기화시킴으로써 동기화된 위상 검출 신호를 발생하는 클록 동기 회로; 및

상기 동기화된 위상 검출 신호에 응답하여 상기 모니터 검출 신호를 발생하는 모니터 검출 신호 발생기를 포함하는 메모리 장치.

#### 청구항 8

제 7 항에 있어서,

상기 클록 스큐 모니터는 내부 전압 안정화 신호에 응답하여 활성화 되는 것을 특징으로 하는 메모리 장치.

#### 청구항 9

제 7 항에 있어서,

상기 클록 스큐 모니터는 TMRS(Test Mode Register Set)에 의해 강제적으로 비활성화 되는 것을 특징으로 하는 메모리 장치.

#### 청구항 10

메모리 장치의 클록 라킹 방법에 있어서,

내부 전압이 안정화 되기 전에, 지연 고정 루프 회로에서 이니셜 락 동작을 수행하는 단계;

상기 내부 전압이 안정화 된 후에, 윈도우 검출 회로를 이용하여 기준 클록과 피드백 클록 사이의 클록 스큐를 모니터링 하는 단계; 및

상기 지연 고정 루프 회로에서 상기 클록 스큐에 대응하는 다이나믹 지연 제어를 이용하여 리-락 동작을 수행하는 단계를 포함하는 방법.

#### 발명의 설명

#### 기술분야

[0001] 본 발명은 메모리 장치 및 그것의 클록 라킹 방법에 관한 것이다.

#### 배경기술

[0002] 일반적으로, DRAM(dynamic random access memory) 등의 반도체 소자가 고속화됨에 따라, DLL(delay locked loop) 회로는 지연 분해능(delay resolution)이 큰 코어스 지연 라인(coarse delay line)과 지연 분해능이 작은 파인 지연 라인(fine delay line)으로 나누어 동작하고 있다.

#### 발명의 내용

#### 해결하려는 과제

[0003] 본 발명의 목적은, 파워 노이즈 상황에서 보다 빠르게 클록 라킹을 수행하는 메모리 장치 및 그것의 클록 라킹 방법을 제공하는데 있다.

#### 과제의 해결 수단

[0004] 본 발명의 실시 예에 따른 메모리 장치는, 제 1 코드값에 따라 기준 클록을 지연시킴으로써 제 1 지연 클록을 출력하는 제 1 지연 라인; 제 2 코드값에 따라 제 1 지연 클록을 지연시킴으로써 제 2 지연 클록을 출력하는 제 2 지연 라인; 제 1 위상 차이값에 따라 상기 제 1 코드값을 생성하거나, 제 2 위상 차이값에 따라 상기 제 1 코드값을 생성하는 제 2 지연 라인 제어기; 상기 제 2 위상 차이값에 따라 상기 제 2 코드값을 생성하는 제 2 지

연 라인 제어기; 상기 기준 클록과 피드백 클록의 클록 스큐에 대응하는 모니터 검출 신호에 응답하여 상기 제 2 위상 차이값을 상기 제 1 지연 라인 제어기 및 상기 제 2 지연 라인 제어기 중에서 어느 하나로 출력하는 디므티플렉서; 상기 기준 클록과 상기 피드백 클록 사이의 상기 제 1 위상 차이값을 검출하는 제 1 위상 검출기; 상기 기준 클록과 상기 피드백 클록 사이의 상기 제 2 위상 차이값을 검출하는 제 2 위상 검출기; 상기 제 2 지연 클록을 수신하고 내부 클록을 발생하는 클록 패스; 상기 내부 클록에 동기하여 데이터 스트로브 신호를 출력하는 출력 버퍼; 상기 클록 패스의 지연량만큼 상기 제 2 지연 클록을 지연시키는 클록 패스 레플리카; 및 상기 클록 패스 레플리카로부터 출력하는 클록을 상기 출력 버퍼의 지연량만큼 지연시킴으로써 상기 피드백 클록을 발생하는 출력 버퍼 레플리카를 포함할 수 있다.

- [0005] 본 발명의 실시 예에 따른 메모리 장치의 클록 라킹 방법은, 내부 전압이 안정화 되기 전에, 지연 고정 루프 회로에서 이니셜 락 동작을 수행하는 단계; 상기 내부 전압이 안정화 된 후에, 윈도우 검출 회로를 이용하여 기준 클록과 피드백 클록 사이의 클록 스큐를 모니터링 하는 단계; 및 상기 지연 고정 루프 회로에서 상기 클록 스큐에 대응하는 다이나믹 지연 제어를 이용하여 리-락 동작을 수행하는 단계를 포함할 수 있다.

- [0006] 본 발명의 실시 예에 따른 메모리 장치는, 복수의 워드라인들과 복수의 비트라인들이 교차하는 곳에 배치되는 복수의 메모리 셀들을 갖는 메모리 셀 어레이; 로우 어드레스에 응답하여 상기 복수의 워드라인들 중에서 어느하나를 선택하는 로우 디코더; 읽기 동작시 상기 복수의 비트라인들 중에서 선택된 비트라인들에 연결된 메모리 셀들로부터 데이터를 감지 및 증폭하는 비트라인 감지 증폭 회로; 컬럼 어드레스에 응답하여 상기 복수의 비트라인들 중에서 상기 선택된 비트라인들을 선택하는 컬럼 디코더; 상기 읽기 동작시 상기 비트라인 감지 증폭 회로부터 데이터를 수신하고, 내부 클록에 동기화된 데이터 스트로브 신호에 응답하여 상기 수신된 데이터를 외부 장치로 출력하는 데이터 입출력 장치; 기준 클록을 수신하여 상기 내부 클록을 발생하는 지연 고정 루프 회로; 및 상기 기준 클록과 피드백 클록 사이의 클록 스큐에 대응하는 모니터 검출 신호를 발생하는 윈도우 검출 회로를 포함할 수 있다.

#### 발명의 효과

[0007] 본 발명의 실시 예에 따른 메모리 장치 및 그것의 클록 라킹 방법은, 파워 노이즈에 따른 클록 스큐의 변화를 모니터링하고, 모니터링 결과에 따라 다이나믹하게 지연 라인을 제어함으로써, 보다 빠르게 클록 락-동작을 수 행할 수 있다.

#### 도면의 간단한 설명

[0008] 이하에 첨부되는 도면들은 본 실시 예에 관한 이해를 돕기 위한 것으로, 상세한 설명과 함께 실시 예들을 제공한다.

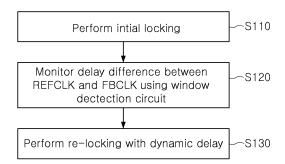

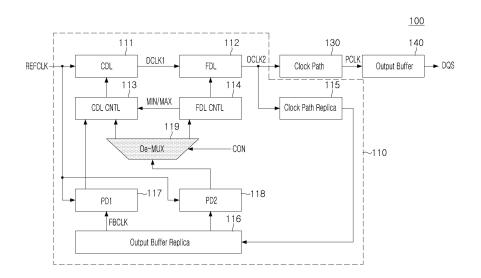

도 1은 본 발명의 실시 예에 따른 DLL(Delayed Locked Loop)를 갖는 메모리 장치(100)를 예시적으로 보여주는 도면이다.

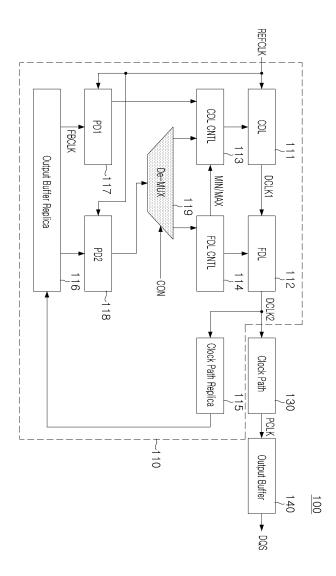

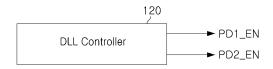

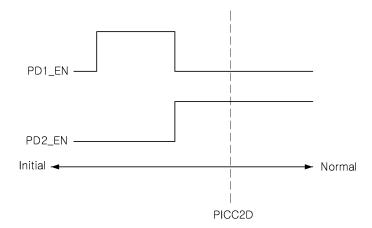

도 2a, 및 도 2b는 본 발명의 실시 예에 따른 DLL 제어기(120)의 위상 검출기들(PD1, PD2)을 제어하는 방식을 예시적으로 보여주는 도면들이다.

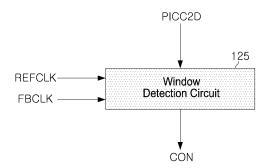

도 3은 본 발명의 실시 예에 따른 윈도우 검출 회로(125)를 예시적으로 보여주는 도면이다.

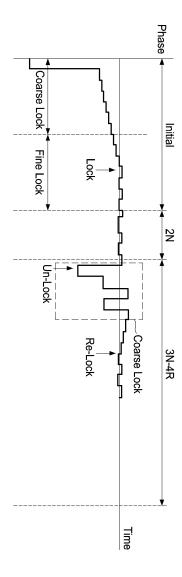

도 4는 본 발명의 실시 예에 따른 DLL(110)은 라킹 동작을 예시적으로 보여주는 도면이다.

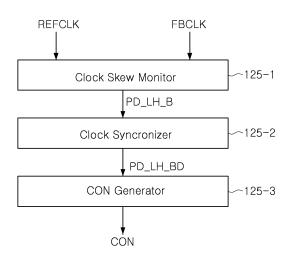

도 5는 본 발명의 실시 예에 따른 윈도우 검출 회로(125)의 내부 구성을 예시적으로 보여주는 도면이다.

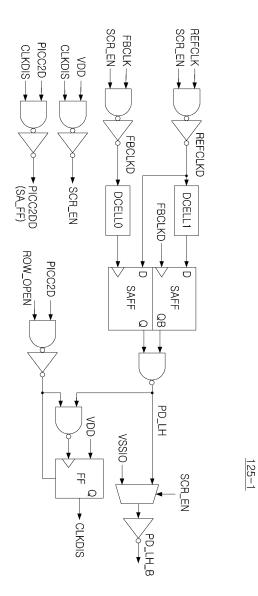

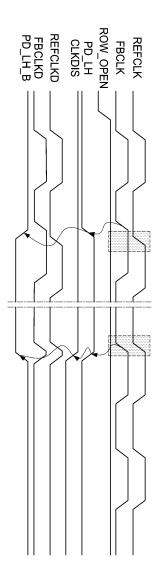

도 6 및 도 7은 본 발명의 실시 예에 따른 클록 스큐 모니터(125-1)의 동작을 설명하기 위한 도면들이다.

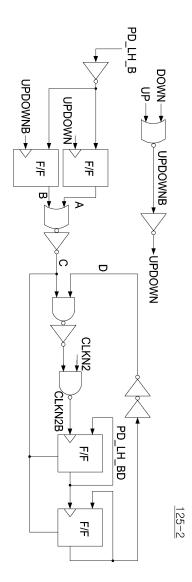

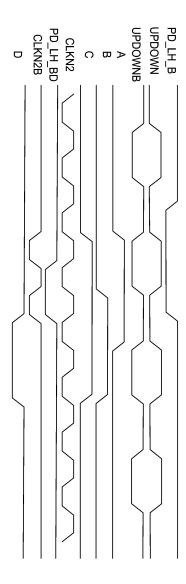

도 8 및 도 9는 본 발명의 실시 예에 따른 클록 동기화 회로(125-2)의 동작을 설명하기 위한 도면들이다.

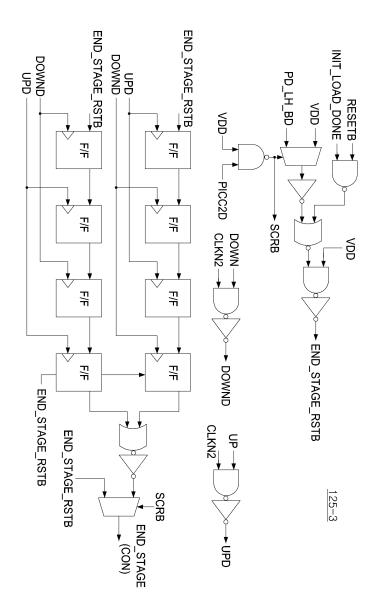

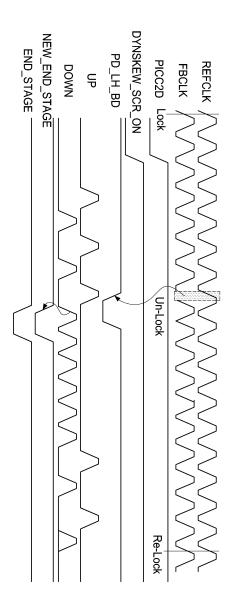

도 10 및 도 11은 본 발명의 실시 예에 따른 모니터 검출 신호 발생기(125-3)의 동작을 설명하기 위한 도면들이다.

도 12는 본 발명의 실시 예에 따른 메모리 장치(100)의 동작 방법을 예시적으로 보여주는 흐름도이다.

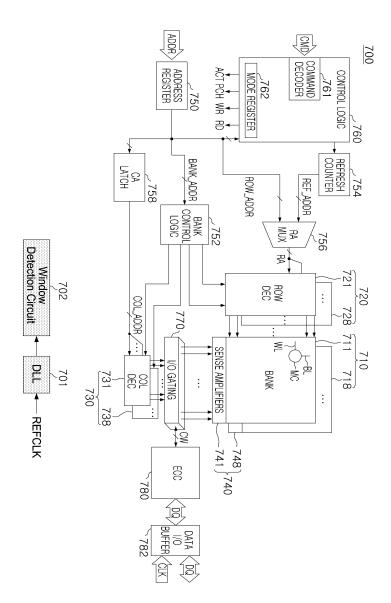

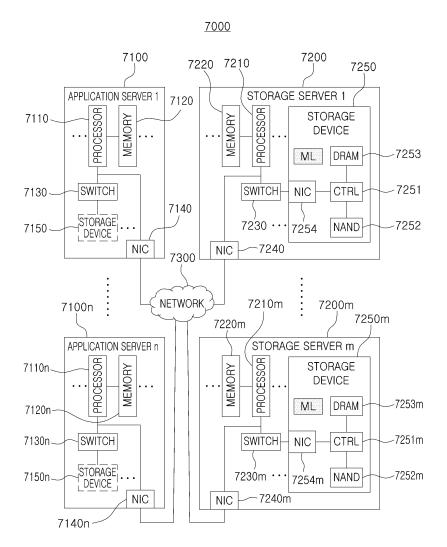

도 13은 본 발명의 실시 예에 따른 메모리 장치(700)를 예시적으로 보여주는 도면이다.

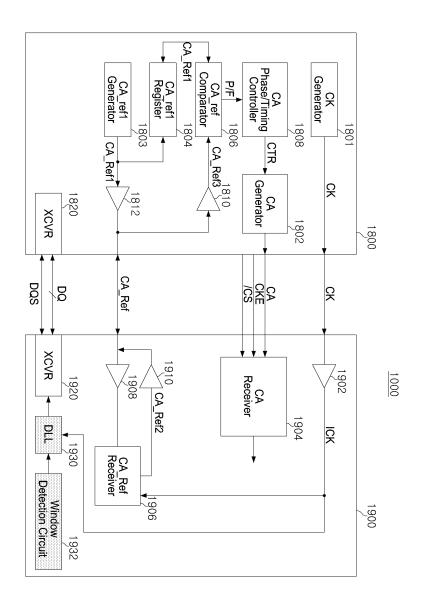

도 14는 본 발명의 실시 예에 따른 적어도 하나의 커맨드/어드레스 캘리브레이션을 수행하는 메모리 시스템을 예시적으로 보여주는 도면이다.

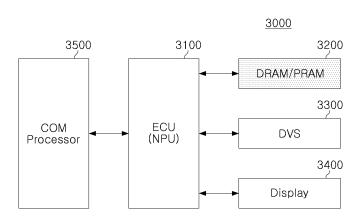

도 15는 본 발명의 실시 예에 따른 차량용 전자 시스템(3000)을 예시적으로 보여주는 도면이다.

도 16은 본 발명의 실시 예에 따른 메모리 장치가 적용된 데이터 센터를 예시적으로 보여주는 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0009] 아래에서는 도면들을 이용하여 본 발명의 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시 할 수 있을 정도로 본 발명의 내용을 명확하고 상세하게 기재할 것이다.

- [0010] 일반적으로, 메모리 장치의 DLL(delay locked loop, 지연 고정 루프)은 초기 락(initial lock) 구간에서 코어스 락(coarse lock) 동작을 수행한 후에 파인 락(fine lock) 동작을 수행하고 있다. 이후에 파워 드랍(power drop)에 따른 언-락(un-lock)이 발생할 때, DLL은 이러한 언-락을 다시 리-락(re-lock)하기 위하여 파인 락 동작을 수행하고 있다. 이는 DLL의 라킹 시간을 증가시키고, tDV(Data Valid Window) 감소시키고 있다.

- [0011] 본 발명의 실시 예에 따른 메모리 장치의 DLL은 초기 락 구간 이후에 윈도우 검출 회로를 동작시킴으로써, 기준 클록과 피드백 클록 사이의 지연 차이를 모니터링하고, 모니터링 결과값에 따라 코어스 락 동작을 활성화 시킬 수 있다. 그 결과로써, 본 발명의 실시 예에 따른 메모리 장치는 다이나믹 파워 노이즈에 대응하는 딜레이 스큐 (delay skew)를 모니터링 함으로써, 빠르게 클록을 동기화 시킬 수 있으며, 그에 따라 tDV 감소를 해결할 수 있다.

- [0012] 도 1은 본 발명의 실시 예에 따른 DLL(Delayed Locked Loop)를 갖는 메모리 장치(100)를 예시적으로 보여주는 도면이다. 도 1을 참조하면, 메모리 장치(100)는, DLL(110), 클록 패스(130), 및 출력 버퍼(140)를 포함할 수 있다.

- [0013] 메모리 장치(100)는 외부의 제어기로부터 수신된 데이터를 저장하거나, 읽혀진 데이터를 제어기로 출력하도록 구현될 수 있다. 메모리 장치(100)는, 컴퓨팅 시스템에서 연산 메모리(operation memory), 워킹 메모리(working memory) 혹은 버퍼 메모리(buffer memory)로써 이용될 수 있다. 실시 예에 있어서, 메모리 장치(100)는 SIMM(Single In-line Memory Module), DIMM(Dual In-line Memory Module), SODIMM(Small-Outline DIMM), UDIMM(Unbuffered DIMM), FBDIMM(Fully-Buffered DIMM), RBDIMM(Rank-Buffered DIMM), mini-DIMM, micro-DIMM, RDIMM(Registered DIMM) 혹은 LRDIMM(Load-Reduced DIMM)으로 구현될 수 있다.

- [0014] 실시 예에 있어서, 메모리 장치(100)는 휘발성 메모리로 구현될 수 있다. 예를 들어, 휘발성 메모리는, DRAM(Dynamic Random Access Memory), SDRAM(Synchronous DRAM), DDR SDRAM(Double Data Rate SDRAM), LPDDR SDRAM(Low Power Double Data Rate SDRAM), GDDR SDRAM(Graphics Double Data Rate SDRAM), RDRAM(Rambus DRAM) 및 SRAM(Static RAM)에서 적어도 하나를 포함할 수 있다. 다른 실시 예에 있어서, 메모리 장치(100)는 비휘발성 메모리로 구현될 수 있다. 예를 들어, 비휘발성 메모리는, 낸드 플래시 메모리, PRAM(Phase-change RAM), MRAM(Magneto-resistive RAM), ReRAM(Resistive RAM), FRAM(Ferro-electric RAM), 및 노아 플래시 메모리 중에서 어느 하나를 포함할 수 있다.

- [0015] DLL(110)은 제 1 지연 라인(코어스 지연 라인, 111), 제 2 지연 라인(파인 지연 라인, 112), 제 1 지연 라인 제 어기(CDL CNTL, 113), 제 2 지연 라인 제어기(FDL CNTL, 114), 클록 패스 레플리카(115), 출력 버퍼 레플리카(116), 제 1 위상 검출기(PD1, 117), 제 2 위상 검출기(PD2, 118), 및 디-멀티플렉서(De-MUX, 119)를 포함할 수 있다.

- [0016] 도시되지 않았지만, 메모리 장치(100)는 외부로부터 클록(CK)를 버퍼링 함으로써 기준 클록(REFCLK)을 생성하는 클록 버퍼를 더 포함할 수 있다.

- [0017] 제 1 지연 라인(코어스 지연 라인, 111)은 기준 클록(REFCK)을 수신하고, 기준 클록(REFCK)을 제 1 코드값에 따라 지연시킴으로써 제 1 지연 클록(DCLK1)을 발생하도록 구현될 수 있다. 실시 예에 있어서, 제 1 지연 라인은 직렬 연결된 제 1 지연 셀들을 포함할 수 있다. 실시 예에 있어서, 제 1 지연 셀들의 각각은 제 1 지연량을 가질 수 있다.

- [0018] 제 2 지연 라인(파인 지연 라인, 112)은 제 1 지연 클록(DCLK1)을 수신하고, 제 1 지연 클록(DCLK1)을 제 2 코 드값에 따라 지연시킴으로써 제 2 지연 클록(DCLK2)을 발생하도록 구현될 수 있다. 실시 예에 있어서, 제 2 지연 연 라인은 직렬 연결된 제 2 지연 셀들을 포함할 수 있다. 실시 예에 있어서, 제 2 지연 셀들의 각각은 제 2 지연량을 가질 수 있다. 여기서 제 2 지연량은 제 1 지연량보다 작을 수 있다.

- [0019] 제 1 지연 라인 제어기(CDL CNTL, 113)는 제 1 위상 차이값 혹은 제 2 위상에 차이값에 대응하는 제 1 코드값을

발생하도록 구현될 수 있다.

- [0020] 제 2 지연 라인 제어기(FDL CNTL, 114)는 제 2 위상 차이값에 대응하는 제 2 코드값을 발생하도록 구현될 수 있다.

- [0021] 클록 패스 레플리카(115)는 제 1 지연 클록(DCLK2)를 수신하고, 클록 패스(130)에 실질적으로 동일한 지연량을 갖도록 구현될 수 있다.

- [0022] 출력 버퍼 레플리카(116)는 클록 패스 레플리카(115)로부터 출력하는 클록을 출력 버퍼(140)에 실질적으로 동일 한 지연량만큼 지연시킴으로써 피드백 클록(FBCLK)을 갖도록 구현될 수 있다.

- [0023] 제 1 위상 검출기(PD1, 117)는 피드백 클록(FBCLK)에 따라 제 1 위상 차이값을 발생하도록 구현될 수 있다.

- [0024] 제 2 위상 검출기(PD2, 118)는 피드백 클록(FBCLK)에 따라 제 2 위상 차이값을 발생하도록 구현될 수 있다.

- [0025] 디-멀티플렉서(De-MUX, 119)는 모니터 검출 신호(CON)에 응답하여 제 2 위상 차이값을 제 1 지연 라인 제어기 (121) 및 제 2 지연 라인 제어기(122) 중에서 어느 하나로 출력하도록 구현될 수 있다. 여기서 모니터 검출 신호(CON)는 다이나믹 파워 노이즈에 따른 딜레이 스큐를 모니터링 한 신호일 수 있다.

- [0026] 클록 패스(Clock Path, 130)는, DLL(110)로부터 출력하는 클록을 내부 경로들을 통하여 메모리 장치(100)의 내 부로 전송하도록 구현될 수 있다.

- [0027] 출력 버퍼(140)는 클록 패스(130)로부터 출력하는 클록(PCLK)을 이용하여 데이터를 출력하는 데이터 스트로브 신호(DQS)를 출력하도록 구현될 수 있다.

- [0028] 본 발명의 실시 예에 따른 메모리 장치(100)는, 딜레이 스큐를 모니터링 한 모니터 검출 신호(CON)에 응답하여 코어스 라킹 동작을 수행하는 DLL(110)를 구비함으로써, 파워 노이즈에 따른 딜레이 스큐를 보다 빠르게 보상할 수 있다.

- [0029] 도 2a, 및 도 2b는 본 발명의 실시 예에 따른 DLL 제어기(120)의 위상 검출기들(PD1, PD2)을 제어하는 방식을 예시적으로 보여주는 도면들이다.

- [0030] 도 2a에 도시된 바와 같이, DLL 제어기(120)는 DLL(110)의 제 1 위상 검출기(PD1,117) 및 제 2 위상 검출기(PD2, 118)은 상보적으로 동작하도록, 제 1 활성화 신호(PD1\_EN) 및 제 2 활성화 신호(PD2\_EN)을 출력할 수 있다. 제 1 위상 검출기(117)는 제 1 활성화 신호(PD1\_EN)에 응답하여 활성화 될 수 있다. 제 2 위상 검출기(118)는 제 2 활성화 신호(PD2\_EN)에 응답하여 활성화 될 수 있다.

- [0031] 도 2b에 도시된 바와 같이, 메모리 장치(100)가 내부 전압이 안정화 될 때까지(PICC2D 이용하여 판단), 제 1 활성화 신호(PD1\_EN)가 먼저 하이 레벨 상태로써 코어스 라킹 동작이 수행되고, 이후에 제 2 활성화 신호(PD2\_EN)가 하이 레벨 상태로써 파인 라킹 동작이 수행될 수 있다. 이후에 메모리 장치(100)는 내부 전압 안정화 이후에 제 2 활성화 신호(PD2\_EN)를 하이 레벨 상태를 유지하고, 제 1 활성화 신호(PD1\_EN)은 로우 레벨 상태를 유지할 수 있다. 다른 실시 예에 있어서, DLL 제어기(120)는 내부 전압 안정화 이후에 모니터 검출 신호(CON)에 응답하여 제 2 활성화 신호(PD2\_EN)를 로우 레벨 상태로 변경하고, 제 1 활성화 신호(PD1\_EN)은 하이 레벨 상태로 변경할 수 있다.

- [0032] 도 3은 본 발명의 실시 예에 따른 윈도우 검출 회로(125)를 예시적으로 보여주는 도면이다. 도 3을 참조하면, 윈도우 검출 회로(125)는, 내부 전압 안정화 신호(PICC2D)을 수신하고, 기준 클록(REFCLK)과 피드백 클록 (FBCLK)의 사이의 딜레이 스큐가 사전에 결정된 값을 초과할 때 모니터 검출 신호(CON)를 발생하도록 구현될 수 있다.

- [0033] 도 4는 본 발명의 실시 예에 따른 DLL(110)은 라킹 동작을 예시적으로 보여주는 도면이다. 도 4를 참조하면, DLL(110)은 초기화 구간에서 코어스 락 동작과 파인 락 동작을 수행하고, 이후 파워 노이즈에 따라 언-락이 발생할 때 코어스 락 동작을 수행할 수 있다. 이는, 기존의 파인 락 동작으로 언-락을 리-락 할 때보다 보다 빠르게 클록 라킹을 달성하게 한다.

- [0034] 도 5는 본 발명의 실시 예에 따른 윈도우 검출 회로(125)의 내부 구성을 예시적으로 보여주는 도면이다. 도 5 를 참조하면, 윈도우 검출 회로(125)는 클록 스큐 모니터(125-1), 클록 동기화 회로(125-2), 모니터 검출 신호 발생기(125-3)를 포함할 수 있다.

- [0035] 클록 스큐 모니터(125-1)는, 기준 클록(REFCLK)과 피드백 클록(FBCLK) 사이의 클록 스큐를 모니터링 하고, 대응

하는 위상 검출 신호(PD\_LH\_B)를 출력하도록 구현될 수 있다.

- [0036] 실시 예에 있어서, 클록 스큐 모니터(125-1)는 내부 전압 안정화 신호(PICC2D)에 응답하여 활성화 될 수 있다. 제 8 항에 있어서, 실시 예에 있어서, 클록 스큐 모니터(125-1)는 TMRS(Test Mode Register Set)에 의해 강제 적으로 비활성화 될 수 있다.

- [0037] 클록 동기화 회로(125-2)는 위상 검출 신호(PD\_LH\_B) 수신하고, 내부 클록에 동기화시킨 위상 검출 신호 (PD\_LH\_BD)를 출력하도록 구현될 수 있다.

- [0038] 모니터 검출 신호 발생기(125-3)는 동기화된 위상 검출 신호(PD\_LH\_BD)를 수신하고, 기준 클록(REFCLK)과 피드 백 클록(FBCLK) 사이의 클록 스큐에 대응하는 모니터 검출 신호(CON)를 발생하도록 구현될 수 있다.

- [0039] 도 6 및 도 7은 본 발명의 실시 예에 따른 클록 스큐 모니터(125-1)의 동작을 설명하기 위한 도면들이다. 도 6 및 도 7을 참조하면, 클록 스큐 모니터(125-1)는, 기준 클록(REFCLK)과 피드백 클록(FBCLK) 사이의 클록 스큐를 모니터링 하고, 대응하는 위상 검출 신호(PD\_LH\_B)를 출력할 수 있다.

- [0040] 도 6에 도시된 바와 같이, 클록 스큐 모니터(125-1)는 기준 클록(REFCLK), 피드백 클록(FBCLK), 다이나믹 스큐 모니터 신호(DYNSKEW\_SCR\_ON), 내부 전압 안정화 신호(PICC2D), 로우 오픈 신호(ROW\_OPEN)를 수신할 수 있다. 여기서 다이나믹 스큐 모니터 신호(DYNSKEW\_SCR\_ON)는 다이나믹 스큐를 모니터링 하는 신호이다. 로우 오픈 신호(ROW\_OPEN)는 TMRS로 강제 디스에이블(L; 로우 레벨 상태)로 만들 수 있다.

- [0041] 실시 예에 있어서, 클록 비활성화 신호(CLKDIS)는 내부 전압 안정화 신호(PICC2D), 로우 오픈 신호(ROW\_OPEN), 및 위상 검출 신호(PD\_LJ)을 연산함으로써 발생될 수 있다. 모니터 활성화 신호(SCR\_EN)는 제 1 위상 검출기 (PD1)가 동작 하는 구간을 정의하는 신호이다.

- [0042] 실시 예에 있어서, 모니터 활성화 신호(SCR\_EN)는 다이나믹 스큐 모니터 신호(DYNSKEW\_SCR\_ON)과 클록 비활성 신호(CLKDIS)의 연산 동작에 의해 발생될 수 있다. 실시 예에 있어서, 내부 전압 안정화 신호(PICC2D)와 클록 비활성화 신호(CLKDIS)의 연산 결과에 따라 센스 앰프의 플립플롭에 제공되는 내부 전압 신호(PICC2DD)가 발생될 수 있다. 실시 예에 있어서, 지연 기준 클록(REFCLKD)은 기준 클록(REFCLK)과 모니터 활성화 신호(SCR\_EN)의 연산 동작에 의해 발생될 수 있다.

- [0043] 실시 예에 있어서, 지연 피드백 클록(FBCLKD)은 기준 클록(REFCLK)과 모니터 활성화 신호(SCR\_EN)의 연산 동작에 의해 발생될 수 있다. 실시 예에 있어서, 위상 검출 신호(PD\_LH)는 대응하는 지연 셀(DCELL1. DCELL2)과 플립플롭(SAFF)을 경유한 지연 기준 클록(REFCLKD)과 지연 피드백 클록(FBCLKD)의 연산 동작에 의해 발생될 수 있다. 멀티 플렉서는 모니터 활성화 신호(SCR\_EN)에 응답하여 위상 검출 신호(PD\_LH) 및 접지 신호(VSSIO) 중에서 어느 하나를 선택할 수 있다.

- [0044] 클록 스큐 모니터(125-1)는 멀티 플렉서의 출력 신호를 인버팅함으로써, 위상 검출 신호(PD\_LH\_B)를 출력할 수 있다.

- [0045] 도 8 및 도 9는 본 발명의 실시 예에 따른 클록 동기화 회로(125-2)의 동작을 설명하기 위한 도면들이다. 도 8 및 도9를 참조하면, 클록 동기화 회로(125-2)는 위상 검출 신호(PD\_LH\_B) 수신하고, 내부 클록에 동기화시킨 위상 검출 신호(PD\_LH\_BD)를 출력할 수 있다.

- [0046] 업다운 신호들(UPDOWN, UPDOWNB)은 업 신호(UP)와 다운 신호(DOWN)을 연산함으로써 발생될 수 있다.

- [0047] 플립플롭(F/F)은 위상 검출 신호(PD\_LH\_B)를 업다운 신호(UPDOWN)에 응답하여 신호(A)를 출력할 수 있다. 또한, 플립플롭(F/F)은 위상 검출 신호(PD\_LH\_B)를 상보 업다운 신호(UPDOWNB)에 응답하여 신호(B)를 출력할 수 있다. 신호(C)는 신호 (A)와 신호(B)의 연산 동작에 의해 발생될 수 있다.

- [0048] 플립플롭(F/F)은 신호(C) 및 신호(D)의 연산 결과 신호와 내부 클록(CLKN2)의 연산 결과 신호(CLKN2B)에 응답하여 위상 검출 신호(PD\_LH\_BD)를 입출력 할 수 있다. 여기서 신호(D)는 플립플롭(F/F)의 위상 검출 신호(PD\_LH\_BD)를 지연시킨 신호이다.

- [0049] 도 10 및 도 11은 본 발명의 실시 예에 따른 모니터 검출 신호 발생기(125-3)의 동작을 설명하기 위한 도면들이다. 도 10 및 도 11을 참조하면, 모니터 검출 신호 발생기(125-3)는 위상 검출 신호(PD\_LH\_BD)를 수신하고, 모니터 검출 신호(CON)를 발생할 수 있다.

- [0050] 초기화 로드 완료 신호(INIT\_LOAD\_DONE)는 제 1 위상 검출기(PD1)가 TDC(Time-to-Digital Converter)에 의한

코드값을 코어스 지연 라인(CDL)에 설정하도록 로딩하는 신호이다. 즉, 초기화 로드 완료 신호 (INIT\_LOAD\_DONE)는 제 1 위상 검출기(PD1) 이 동작 끝나면, 로우 레벨에서 하이 레벨로 발생할 수 있다.

- [0051] 리셋 신호(RESETB), 초기화 로드 완료 신호(INIT\_LOAD\_DONE), 위상 검출 신호(PD\_LH\_BD), 및 내부 전압 안정화 신호(PICC2D)을 연산함으로써, 완료 단계 리셋 신호(END\_STATE\_RSTB)가 발생될 수 있다.

- [0052] 다운 신호(DOWN)와 내부 클록(CLKN2)을 연산함으로써 지연된 다운 신호(DOWMD)가 발생될 수 있다. 업 신호(UP)와 내부 클록(CLKN2)을 연산함으로써 지연된 업 신호(UPD)가 발생될 수 있다.

- [0053] 직렬 연결된 제 1 플립플롭들은 완료 단계 리셋 신호(END\_STATE\_RSTB)을 지연된 업 신호(UPD)에 응답하여 출력할 수 있다. 직렬 연결된 제 2 플립플롭들은 완료 단계 리셋 신호(END\_STATE\_RSTB)을 지연된 다운 신호(DOWND)에 응답하여 출력할 수 있다.

- [0054] 제 1 플립플롭들의 출력 신호와 제 2 플립플롭들의 출력 신호를 연산함으로써, 완료 단계 신호(END\_STAGE)가 발생될 수 있다. 여기서 완료 단계 신호(END\_STAGE)는 완료 신호(END\_STAGE)는 제 2 위상 검출기(PD2) 동작 하도록 알려주는 신호이다.

- [0056] 기준 클록(REFCLK)과 피드백 클록(FBCLK)의 사이의 클록 스큐에 응답하여 위상 검출 신호(PD\_LH\_BD)가 발생될 수 있다. 도 11에 도시된 바와 같이, 업 신호(UP)의 로우 레벨 상태와 다운 신호(DOWN)의 라이징 엣지에 응답하여 위상 검출 신호(PD\_LH\_BD)에 대응하는 새로운 완료 단계 신호가 발생할 수 있다. 이렇게 새롭게 발생된 완료 단계 신호(NEW\_END\_STAGE)는 모니터 검출 회로(125)의 모니터 검출 신호(CON)로써 출력될 수 있다.

- [0057] 도 12는 본 발명의 실시 예에 따른 메모리 장치(100)의 동작 방법을 예시적으로 보여주는 흐름도이다. 도 1 내지 도 12을 참조하면, 메모리 장치(100)는 다음과 같이 동작할 수 있다.

- [0058] 메모리 장치(100)의 파워-업 시, 메모리 장치(100)는 이니셜 락 동작을 수행할 수 있다. 여기서 이니셜 락 동작은 코어스 락 동작과 파인 락 동작을 포함할 수 있다. 내부 전압이 안정화되면, 기본적으로 파인 락 동작이 수행될 수 있다(S110).

- [0059] 메모리 장치(100)의 윈도우 검출 회로(125)는 DLL의 입력 클록(REFCLK)과 출력 클록(FBCLK) 사이의 지연 스큐를 모니터링 할 수 있다(S120). 만일, 지연 스큐가 사전에 결정된 값을 초과할 때, 모니터 검출 신호(CON) 가 발생될 수 있다.

- [0060] DLL(110)는 모니터 검출 신호(CON)에 응답하여 코어스 락 동작을 수행함으로써 언-락 상태를 락 상태로 만들도 록 리-락 동작을 수행할 수 있다(S130).

- [0061] 한편, 본 발명의 실시 예에 따른 DLL은 메모리 장치에 적용 가능하다.

- [0062] 도 13은 본 발명의 실시 예에 따른 메모리 장치(700)를 예시적으로 보여주는 도면이다. 도 13을 참조하면, 메모리 장치(700)는, DLL(701), 윈도우 검출 회로(702), 메모리 셀 어레이(710), 로우 디코더(720), 컬럼 디코더(730), 감지 증폭 회로(740), 어드레스 레지스터(750), 뱅크 제어 로직(752), 리프레쉬 카운터(754), 로우 어드 레스 멀티플렉서(756), 컬럼 어드레스 래치(758), 제어 로직(760), 리페어 제어회로(766), 타이밍 제어 회로 (764), 입출력 게이팅 회로(770), 에러 정정 회로(780), 및 데이터 입출력 버퍼(782)를 포함할 수 있다.

- [0063] DLL(701)는 도 1 내지 도 12에서 설명된 바와 같이, 모니터 검출 신호(CON)에 응답하여 신속하게 코어스 락 동작을 수행할 수 있다. 또한, 모니터 검출 회로(702)는 도 1 내지 도 12에서 설명된 바와 같이 기준 클록 (REFCLK)과 피드백 클록(FBCLK) 사이의 딜레이 스큐를 모니터링 하고, 그 결과에 따른 모니터 검출 신호(CON)를 출력할 수 있다.

- [0064] 메모리 셀 어레이(710)는 제 1 내지 제 8 뱅크들(711 ~ 718)을 포함할 수 있다. 한편, 메모리 셀 어레이(710)의 뱅크의 개수는 여기에 제한되지 않는다고 이해되어야 할 것이다. 로우 디코더(720)는 제 1 내지 제 8 뱅크들 (711 ~ 718)에 각각 연결된 제 1 내지 제 8 뱅크 로우 디코더들(721 ~ 728)을 포함할 수 있다. 컬럼 디코더 (730)는 제 1 내지 제 8 뱅크들(711 ~ 718)에 각각 연결된 제 1 내지 제 8 뱅크 컬럼 디코더들(731 ~ 738)을 포함할 수 있다. 감지 증폭 회로(740)는 제 1 내지 제 8 뱅크들(711 ~ 718)에 각각 연결된 제 1 내지 제 8 뱅크센스 앰프들(741 ~ 748)을 포함할 수 있다.

- [0065] 한편, 제 1 내지 제 8 뱅크들(711 ~ 718), 제 1 내지 제8 뱅크 로우 디코더들(721 ~ 728), 제 1 내지 제 8 뱅

크 컬럼 디코더들(731 ~ 738), 제 1 내지 제 8 뱅크 센스 앰프들(741 ~ 748)은 제 1 내지 제 8 뱅크들을 각각 구성할 수 있다. 제 1 내지 제 8 뱅크들(711 ~ 718)의 각각은 워드라인(WL)들과 비트라인(BL)들이 교차하는 지점에 형성되는 복수의 메모리 셀(MC)들을 포함할 수 있다.

- [0066] 어드레스 레지스터(750)는 외부의 메모리 제어기로부터 뱅크 어드레스(BANK\_ADDR), 로우 어드레스(ROW\_ADDR) 및 컬럼 어드레스(COL\_ADDR)를 갖는 어드레스(ADDR)를 수신 및 저장할 수 있다. 어드레스 레지스터(750)는 수신된 뱅크 어드레스(BANK\_ADDR)를 뱅크 제어 로직(752)에 제공하고, 수신된 로우 어드레스(ROW\_ADDR)를 로우 어드레스 멀티플렉서(756)에 제공하며, 수신된 컬럼 어드레스(COL\_ADDR)를 컬럼 어드레스 래치(758)에 제공할 수 있다.

- [0067] 뱅크 제어 로직(752)은 뱅크 어드레스(BANK\_ADDR)에 응답하여 뱅크 제어 신호들을 생성할 수 있다. 뱅크 제어 신호들에 응답하여 제 1 내지 제 8 뱅크 로우 디코더들(721 ~ 728) 중에서 뱅크 어드레스(BANK\_ADDR)에 대응하는 뱅크 로우 디코더가 활성화될 수 있다. 뱅크 제어 신호들에 응답하여 제 1 내지 제 8 뱅크 컬럼 디코더들 (731 ~ 738) 중에서 뱅크 어드레스(BANK\_ADDR)에 대응하는 뱅크 컬럼 디코더가 활성화될 수 있다.

- [0068] 로우 어드레스 멀티플렉서(756)는 어드레스 레지스터(750)로부터 로우 어드레스(ROW\_ADDR)를 수신하고, 리프레 쉬 카운터(754)로부터 리프레쉬 로우 어드레스(REF\_ADDR)를 수신할 수 있다. 로우 어드레스 멀티플렉서(756)는 로우 어드레스(ROW\_ADDR) 혹은 리프레쉬 로우 어드레스(REF\_ADDR)를 로우 어드레스(RA)로서 선택적으로 출력할 수 있다. 로우 어드레스 멀티플렉서(756)로부터 출력된 로우 어드레스(RA)는 제 1 내지 제 8 뱅크 로우 디코더들(721 ~ 728)에 각각 인가될 수 있다.

- [0069] 제 1 내지 제 8 뱅크 로우 디코더들(721 ~ 728) 중에서 뱅크 제어 로직(752)에 의해 활성화된 뱅크 로우 디코더는 로우 어드레스 멀티플렉서(756)로부터 출력된 로우 어드레스(RA)를 디코딩하여 로우 어드레스에 대응하는 워드라인을 활성화할 수 있다. 예를 들어, 활성화된 뱅크 로우 디코더는 로우 어드레스에 대응하는 워드라인에 워드라인 구동 전압을 인가할 수 있다. 또한, 활성화된 뱅크 로우 디코더는 로우 어드레스에 대응하는 워드라인을 활성화하는 것과 동시에 리페어 제어회로(766)로부터 출력되는 리던던시 로우 어드레스에 대응하는 리던던시 워드라인을 활성화할 수 있다.

- [0070] 컬럼 어드레스 래치(758)는 어드레스 레지스터(750)로부터 컬럼 어드레스(COL\_ADDR)를 수신하고, 수신된 컬럼 어드레스(COL\_ADDR)를 일시적으로 저장할 수 있다. 또한, 컬럼 어드레스 래치(758)는, 버스트(burst) 모드에서, 수신된 컬럼 어드레스(COL\_ADDR)를 점진적으로 증가시킬 수 있다. 컬럼 어드레스 래치(758)는 일시적으로 저장 된 혹은 점진적으로 증가한 컬럼 어드레스(COL\_ADDR)를 제 1 내지 제 8 뱅크 컬럼 디코더들(731 ~ 738)에 각각 인가할 수 있다.

- [0071] 제 1 내지 제 8 뱅크 컬럼 디코더들(731 ~ 738) 중에서 뱅크 제어 로직(752)에 의해 활성화된 뱅크 컬럼 디코더는 입출력 게이팅 회로(770)를 통하여 뱅크 어드레스(BANK\_ADDR) 및 컬럼 어드레스(COL\_ADDR)에 대응하는 센스 앰프를 활성화할 수 있다. 또한, 활성화된 뱅크 컬럼 디코더는 리페어 제어회로(766)로부터 출력되는 컬럼 리페어 신호(CRP)에 응답하여 컬럼 리페어 동작을 수행할 수 있다.

- [0072] 제어 로직(760)은 메모리 장치(700)의 동작을 제어하도록 구현될 수 있다. 예를 들어, 제어 로직(760)은 반도체 메모리 장치(700)가 쓰기 동작 혹은 읽기 동작을 수행하도록 제어 신호들을 생성할 수 있다. 제어 로직(760)은 메모리 제어기로부터 수신되는 명령(CMD)을 디코딩하는 커맨드 디코더(761) 및 메모리 장치(700)의 동작 모드를 설정하기 위한 모드 레지스터 셋(762)를 포함할 수 있다.

- [0073] 예를 들어, 커맨드 디코더(761)는 라이트 인에이블 신호(/WE), 로우 어드레스 스트로브 신호(/RAS), 컬럼 어드레스 스트로브 신호(/CAS), 칩 선택 신호(/CS) 등을 디코딩함으로써 명령(CMD)에 대응하는 동작 제어 신호들(ACT, PCH, WE, RD)을 생성할 수 있다. 제어 로직(760)은 동작 제어 신호들(ACT, PCH, WE, RD)을 타이밍 제어 회로(764)에 제공할 수 있다. 제어 신호들(ACT, PCH, WR, RD)은 액티브 신호(ACT), 프리차지 신호(PCH), 쓰기신호(WR) 및 읽기 신호(RD)를 포함할 수 있다.

- [0074] 입출력 게이팅 회로(770)의 입출력 게이팅 회로들 각각은 입출력 데이터를 게이팅하는 회로들과 함께, 입력 데이터 마스크 로직, 제 1 내지 제 8 뱅크들(711 ~ 718)로부터 출력된 데이터를 저장하기 위한 읽기 데이터 래치들, 및 제 1 내지 제 8 뱅크들(711 ~ 718)에 데이터를 쓰기 위한 쓰기 드라이버들을 포함할 수 있다.

- [0075] 제 1 내지 제 8 뱅크들(711 ~ 718) 중에서 하나의 뱅크에서 읽혀질 코드워드(CW; codeword)는 하나의 뱅크에 대응하는 센스 앰프에 의해 감지되고, 읽기 데이터 래치들에 저장될 수 있다. 읽기 데이터 래치들에 저장된 코드워드(CW)는 에러 정정 회로(780)에 의하여 ECC 디코딩이 수행된 후, 데이터 입출력 버퍼(782)를 통하여 메모리

제어기에 제공될 수 있다. 제 1 내지 제 8 뱅크들(210 ~ 218) 중에서 하나의 뱅크에 쓰여질 데이터(DQ)는 에러 정정 회로(780)에서 ECC 인코딩을 수행한 후 쓰기 드라이버들을 통하여 하나의 뱅크에 쓰여 질 수 있다.

- [0076] 데이터 입출력 버퍼(782)는 쓰기 동작에서 메모리 제어기로부터 제공되는 클록 신호(CLK)에 근거로 하여 데이터 (DQ)를 에러 정정 회로(780)에 제공하고, 읽기 동작에서 에러 정정 회로(780)로부터 제공되는 데이터(DQ)를 메모리 제어기에 제공할 수 있다.

- [0077] 에러 정정 회로(ECC, 780)는 쓰기 동작에서 데이터 입출력 버퍼(782)로부터 제공되는 데이터(DQ)의 데이터 비트들에 근거로 하여 패리티 비트들을 생성하고, 데이터(DQ)와 패리티 비트들을 포함하는 코드워드(code word)를 입출력 게이팅 회로(770)에 제공하고, 입출력 게이팅 회로(770)은 코드워드를 뱅크에 쓸 수 있다. 또한, 에러 정정 회로(780)는 읽기 동작에서 하나의 뱅크에서 읽혀진 코드워드(CW)를 입출력 게이팅 회로(770)로부터 제공받을 수 있다. 에러 정정 회로(780)는 읽혀진 코드워드(CW)에 포함되는 패리티 비트들을 이용하여 데이터(DQ)에 대한 ECC 디코딩을 수행하여 데이터(DQ)에 포함되는 적어도 하나의 에러 비트를 정정하여 데이터 입출력 버퍼 (782)에 제공할 수 있다.

- [0078] 본 발명의 실시 예에 따른 메모리 장치(700)는, 내부 전압 안정화 상태에서 파워 노이즈에 따른 지터를 신속하 게 제거할 수 있다.

- [0079] 도 14는 본 발명의 실시 예에 따른 적어도 하나의 커맨드/어드레스 캘리브레이션을 수행하는 메모리 시스템을 예시적으로 보여주는 도면이다.

- [0080] 도 14를 참조하면, 메모리 시스템(1000)은 제어기(1800)와 메모리 장치(1900)를 포함할 수 있다. 제어기(180 0)는 클록 발생기(1801), 커맨드/어드레스(CA) 발생기(1802), 커맨드/어드레스 레퍼런스 발생기(1803), 레지스터(1804), 비교기(1806), 위상/타이밍 제어기(1808), 및 데이터 입출력기(1810, 1812)를 포함할 수 있다. 제어기(1800)는 클록 발생기(1801)에서 생성되는 클록 신호(CK)를 클록 신호 라인을 통해 메모리 장치(1900)로 제공할 수 있다.

- [0081] 실시 예에 있어서, 메모리 시스템(1000)은 인터페이스에 별도로 커맨드/어드레스의 레퍼런스 신호(CA\_Ref) 라인을 포함하고 있다. 커맨드/어드레스의 레퍼런스 신호(CA\_Ref) 라인은 캘리브레이션 모드에서 커맨드/어드레스의 기준값인 커맨드/어드레스의 레퍼런스 신호(CA\_Ref)를 송수신 하는 역할을 수행할 수 있다.

- [0082] 이러한 커맨드/어드레스의 기준값을 이용한 캘리브레이션 결과값을 위상/타이밍 제어기(1808)에 제공해서 커맨드/어드레스 신호(CA)의 위상/타이밍을 조정할 수 있다. 별도의 커맨드/어드레스의 레퍼런스 신호(CA\_Ref) 라인이 있으므로 커맨드/어드레스(CA) 신호를 전송하는 동작을 하면서 동시에 커맨드/어드레스(CA) 신호의 위상/타이밍을 조정할 수 있는 캘리브레이션 동작을 수행할 수 있는 장점이 있다.

- [0083] CA 발생기(1802)는 위상/타이밍 제어기(1808)의 제어 신호(CTR)에 응답하여 위상 혹은 타이밍을 조정된 커맨드/어드레스 신호(CA)를 발생하고, CA 버스를 통해 메모리 장치(1900)로 전송할 수 있다.

- [0084] 커맨드/어드레스 레퍼런스 발생기(1803)는 커맨드/어드레스 발생기(1802)와 동일하게 구성되며, 커맨드/어드레스 발생기(1802)에서 발생되는 커맨드/어드레스 신호(CA)와 동일한 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)를 발생할 수 있다.

- [0085] 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)는 레지스터(1804)로 제공된다. 또한, 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)는 데이터 출력기(1812)를 통해 CA 레퍼런스 버스(12)로 전송되고, CA 레퍼런스 버스(16)를 통해 메모리 장치(1900)로 제공된다.

- [0086] 레지스터(1804)는 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)를 저장할 수 있다. 비교기(1806)는 레지스터 (1804)에 저장된 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)와 데이터 입력기(1810)로부터 출력되는 제3 커맨드/어드레스 레퍼런스 신호(CA\_Ref3)를 비교할 수 있다. 비교기(1804)는 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref3)의 데이터를 비교하여 패스 혹은 페일 신호(P/F)를 발생할 수 있다.

- [0087] 위상/타이밍 제어기(1808)는 비교기(1806)의 패스 혹은 페일 신호(P/F)에 따라 커맨드/어드레스 신호(CA)의 위상 변이(shift)를 지시하는 제어 신호(CTR)를 발생할 수 있다. 제어 신호(CTR)는 커맨드/어드레스 신호(CA)의 위상 혹은 타이밍을 조정하여, 위상 조정된 커맨드/어드레스 신호(CA)를 발생시킬 수 있다.

- [0088] 데이터 입력기(1810)는, 메모리 장치(1900)로부터 CA 레퍼런스 버스를 통해 전달되는 제 2 커맨드/어드레스 레

퍼런스 신호(CA\_Ref2)를 수신하여 제3 커맨드/어드레스 레퍼런스 신호(CA\_Ref3)로서 비교기(1806)로 전달할 수 있다.

- [0089] 데이터 출력기(1812)는 커맨드/어드레스 레퍼런스 발생기(1803)에서 발생된 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)를 수신하여 CA 레퍼런스 버스(12)로 전송할 수 있다.

- [0090] 메모리 장치(1900)는 클록 버퍼(1902), 커맨드/어드레스(CA) 수신기(1904), 커맨드/어드레스 레퍼런스 수신기 (1906), 및 데이터 입출력기(1908, 910)를 포함할 수 있다. 클록 버퍼(1902)는 클록 신호 라인을 통해 전달되는 클록 신호(CK)를 수신하여 내부 클록 신호(ICK)를 발생할 수 있다. CA 수신기(1904)는 내부 클록 신호(ICK)에 응답하여 칩 선택 신호(/CS), 클록 인에이블 신호(CKE) 및 CA 버스를 통해 전달되는 커맨드/어드레스 신호(CA)를 수신할 수 있다.

- [0091] 클록 인에이블 신호(CKE)는 CA 버스를 통해 전달되는 커맨드/어드레스 신호(CA)의 리드 커맨드로 작용하는 의사 커맨드(pseudo command)로 사용될 수 있다. CA 수신기(1904)는 클록 인에이블 신호(CKE)가 활성화일 때에 커맨 드/어드레스 신호(CA)를 수신할 수 있다.

- [0092] 데이터 입력기(1908)는 제어기(1800)로부터 CA 레퍼런스 버스를 통해 전달되는 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)를 수신하여 커맨드/어드레스 레퍼런스 수신기(1906)로 전달할 수 있다. 커맨드/어드레스 레퍼런스 수신기(1906)는 CA 수신기(1904)와 동일하게 구성될 수 있다. 커맨드/어드레스 레퍼런스 수신기(1906)는 내부 클록 신호(ICK)에 응답하여 칩 선택 신호(/CS), 클록 인에이블 신호(CKE) 및 CA 레퍼런스 버스를 통해 전달되는 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)를 수신하여 제 2 커맨드/어드레스 레퍼런스 신호(CA\_Ref2)를 발생할 수 있다.

- [0093] 제 2 커맨드/어드레스 레퍼런스 신호(CA\_Ref2)는, CA 수신기(1904)에서 내부 클록 신호(ICK)에 응답하여 칩 선택 신호(/CS), 클록 인에이블 신호(CKE) 및 CA 버스를 통해 전달되는 커맨드/어드레스 신호(CA)를 수신하여 출력하는 신호와 동일할 수 있다. 제 2 커맨드/어드레스 레퍼런스 신호(CA\_Ref2)는 데이터 출력기(1910)를 통해 CA 레퍼런스 버스로 전달될 수 있다.

- [0094] 메모리 시스템(1000)에서 이루어지는 CA 캘리브레이션은 다음과 같다. 제어기(1800)의 CA 발생기(1802)는 위상/타이밍 제어기(1808)의 제어 신호(CTR)에 응답하여 커맨드/어드레스 신호(CA)의 위상 혹은 타이밍을 조정하여 커맨드/어드레스 신호(CA)를 CA 버스로 전송할 수 있다. 커맨드/어드레스 레퍼런스 발생기(1803)는 커맨드/어드레스 겐스 신호(CA)와 동일한 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)를 발생하여 CA 레퍼런스 버스로 전달할수 있다.

- [0095] 메모리 장치(1900)의 CA 레퍼런스 수신기(1906)는 내부 클록 신호(ICK)와 클록 인에이블 신호(CKE)에 따라 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)를 수신하여 제 2 커맨드/어드레스 레퍼런스 신호(CA\_Ref2)를 발생할 수 있다. 메모리 장치(1900)의 제 2 커맨드/어드레스 레퍼런스 신호(CA\_Ref2)는 CA 레퍼런스 버스로 전송될 수 있다.

- [0096] 제어기(1800)는 CA 레퍼런스 버스를 통해 전송되는 제 2 커맨드/어드레스 레퍼런스 신호(CA\_Ref2)를 제 2 커맨드/어드레스 레퍼런스 신호(CA\_Ref2)로써 비교기(1806)로 전송할 수 있다. 비교기(1806)는 제 1 커맨드/어드레스 레퍼런스 신호(CA\_Ref1)와 제 2 커맨드/어드레스 레퍼런스 신호(CA\_Ref2)의 데이터를 비교하여 패스 혹은 페일 신호(P/F)를 발생할 수 있다. 위상/타이밍 제어기(1808)는 비교기(1806)의 패스 혹은 페일 신호(P/F)에 따라 커맨드/어드레스 신호(CA)의 위상 변이(shift)를 지시하는 제어 신호(CTR)를 발생할 수 있다. CA 발생기(1802)는 제어 신호(CTR)에 따라 위상 조정된 커맨드/어드레스 신호(CA)를 발생시킬 수 있다.

- [0097] 이러한 CA 캘리브레이션 동작의 반복으로, 제어기(1800)의 위상/타이밍 제어기(1808)는 패스(P)된 위치들의 중간을 커맨드/어드레스 신호(CA) 윈도우의 중간으로 판별하고, 클록 신호(CK)의 엣지에 커맨드/어드레스 신호(CA) 윈도우의 중간이 오도록 커맨드/어드레스 신호(CA)를 발생하여 메모리 장치(1900)로 제공할 수 있다. 이에따라, 메모리 장치(1900)는 클록 신호(CK)의 상승/하강 엣지에서 클록 신호 쌍(CK, CKB)의 상승/하강 엣지에 유효 윈도우의 중간이 위치하는 커맨드/어드레스 신호(CA)를 수신할 수 있다.

- [0098] 도 14에 도시된 바와 같이, 메모리 시스템(1000)의 제어기(1800) 및 메모리 장치(1900)는 각각 대응하는 트랜시 버들(1820, 1920)을 포함할 수 있다. 특히, 메모리 장치(1900)는 DQS 신호를 생성하는 DLL(1930)과 윈도우 검출 회로(1932)를 포함할 수 있다. 메모리 장치(1900)는 도 1 내지도 12에서 설명된 바와 같이, 파워 노이즈에 따라 야기되는 언-락 상태를 빠르게 리-락 상태로 만들기 위한 DLL 동작을 수행할 수 있다.

- [0099] 한편, 본 발명의 실시 예에 따른 메모리 장치는 전장(automotive) 시스템에 적용 가능하다.

- [0100] 도 15는 본 발명의 실시 예에 따른 차량용 전자 시스템(3000)을 예시적으로 보여주는 도면이다. 도 15를 참조하면, 차량용 전자 시스템(3000)은, 적어도 하나의 ECU(s)(electronic control unit, 3100), 메모리 장치(3200), DVS(dynamic range sensor; 3300), 디스플레이 장치(3400) 및 통신 프로세서(3500)를 포함할 수 있다.

- [0101] ECU(electronic control unit, 3100)는 전반적인 동작을 제어하도록 구현될 수 있다. ECU(3100)는 DVS(3300)로 부터 수신된 이미지 데이터를 처리할 수 있다. ECU(3100)는 NPU(neural processing unit)을 포함할 수 있다. NPU는 DVS(3300)로부터 수신된 이미지를 학습 모델과 비교하여 주행을 위한 최적의 이미지를 빠르게 도출할 수 있다.

- [0102] 메모리 장치(3200)는 NPU의 동작 관련된 학습 모델을 저장하도록 구현될 수 있다. 메모리 장치(3200)는 휘발성 혹은 비휘발성 메모리 장치를 포함할 수 있다. 예를 들어, 메모리 장치(3200)는 DRAM 혹은 PRAM 일 수 있다. 특히, 메모리 장치(3200)는 도 1 내지 도 13에서 설명된 바와 같이 DLL 동작을 수행하도록 구현될 수 있다.

- [0103] DVS(dynamic range sensor; 3300)는 차량 외부의 환경을 감지하도록 구현될 수 있다. DVS(3300)는 상대적인 빛의 강도(intensity) 변화에 응답하여 이벤트 신호를 출력할 수 있다. DVS(3300)는 복수의 DVS 픽셀들을 포함하는 픽셀 어레이와, 어드레스 이벤트 처리기들을 포함할 수 있다.

- [0104] 디스플레이 장치(3400)는 ECU(3100)에서 처리된 이미지 혹은 통신 프로세서(3500)에 의해 전송된 이미지를 디스 플레이 하도록 구현될 수 있다.

- [0105] 통신 프로세서(3500)는 처리된 이미지를 외부장치, 예를 들어 외부 차량으로 전송하거나, 외부 차량으로부터 이미지를 수신하도록 구현될 수 있다. 즉, 통신 프로세서(3500)는 외부 장치와 유선 혹은 무선 통신하도록 구현될 수 있다.

- [0106] 한편, 본 발명의 실시 예에 따른 데이터 통신 방식은 데이터 센터에 적용 가능하다.

- [0107] 도 16은 본 발명의 실시 예에 따른 메모리 장치가 적용된 데이터 센터를 예시적으로 보여주는 도면이다. 도 16을 참조하면, 데이터 센터(7000)는 각종 데이터를 모아두고 서비스를 제공하는 시설로서, 데이터 저장 센터라고 지칭될 수도 있다. 데이터 센터(7000)는 검색 엔진 및 데이터 베이스 운용을 위한 시스템일 수 있으며, 은행 등의 기업 혹은 정부기관에서 사용되는 컴퓨팅 시스템일 수 있다. 데이터 센터(7000)는 어플리케이션 서버들(7100 내지 7100n) 및 저장 서버들(7200 내지 7200m)을 포함할 수 있다. 어플리케이션 서버들(7100 내지 7100n)의 개수 및 저장 서버들(7200 내지 7200m)의 개수는 실시 예에 따라 다양하게 선택될 수 있고, 어플리케이션 서버들 (7100 내지 7100n)의 개수 및 저장 서버들(7200 내지 7200m)의 개수는 서로 다를 수 있다.

- [0108] 어플리케이션 서버(7100) 혹은 저장 서버(7200)는 프로세서(7110, 7210) 및 메모리(7120, 7220) 중 적어도 하나를 포함할 수 있다. 저장 서버(7200)를 예시로 설명하면, 프로세서(7210)는 저장 서버(7200)의 전반적인 동작을 제어할 수 있고, 메모리(7220)에 액세스하여 메모리(7220)에 로딩된 커맨드 혹은 데이터를 실행할 수 있다. 메모리(7220)는 DDR SDRAM(Double Data Rate Synchronous DRAM), HBM(High Bandwidth Memory), HMC(Hybrid Memory Cube), DIMM(Dual In-line Memory Module), Optane DIMM 혹은 NVMDIMM(Non-Volatile DIMM)일 수 있다. 실시 예에 따라, 저장 서버(7200)에 포함되는 프로세서(7210)의 개수 및 메모리(7220)의 개수는 다양하게 선택될 수 있다.

- [0109] 실시 예에 있어서, 프로세서(7210)와 메모리(7220)는 프로세서-메모리 페어를 제공할 수 있다. 실시 예에 있어서, 프로세서(7210)와 메모리(7220)의 개수는 서로 다를 수도 있다. 프로세서(7210)는 단일 코어 프로세서 혹은 다중 코어 프로세서를 포함할 수 있다. 저장 서버(7200)에 대한 상기 설명은, 어플리케이션 서버(7100)에도 유사하게 적용될 수 있다. 실시 예에 따라, 어플리케이션 서버(7100)는 저장 장치(7150)를 포함하지 않을 수도 있다. 저장 서버(7200)는 적어도 하나 이상의 저장 장치(7250)를 포함할 수 있다. 저장 장치(7250)는 도 1 내지도 15에 설명된 바와 같이 파워 노이즈 환경에서 다이나믹 딜레이 제어하도록 클록 라킹을 수행하도록 구현될수 있다.

- [0110] 어플리케이션 서버들(7100 내지 7100n) 및 저장 서버들(7200 내지 7200m)은 네트워크(7300)를 통해 서로 통신할 수 있다. 네트워크(7300)는 FC(Fiber Channel) 혹은 Ethernet 등을 이용하여 구현될 수 있다. 이 때, FC는 상 대적으로 고속의 데이터 전송에 사용되는 매체이며, 고성능/고가용성을 제공하는 광 스위치를 사용할 수 있다. 네트워크(7300)의 액세스 방식에 따라 저장 서버들(7200 내지 7200m)은 파일 저장, 블록 저장, 혹은 오브젝트 저장으로서 제공될 수 있다.

- [0111] 실시 예에 있어서, 네트워크(7300)는 SAN(Storage Area Network)와 같은 저장 전용 네트워크일 수 있다. 예를 들어, SAN은 FC 네트워크를 이용하고 FCP(FC Protocol)에 따라 구현된 FC-SAN일 수 있다. 또 다른 예를 들어, SAN은 TCP/IP 네트워크를 이용하고 iSCSI(SCSI over TCP/IP 혹은 Internet SCSI) 프로토콜에 따라 구현된 IP-SAN일 수 있다. 다른 실시 예에 있어서, 네트워크(7300)는 TCP/IP 네트워크와 같은 일반 네트워크일 수 있다. 예를 들어, 네트워크(7300)는 FCoE(FC over Ethernet), NAS(Network Attached Storage), NVMe-oF(NVMe over Fabrics) 등의 프로토콜에 따라 구현될 수 있다.

- [0112] 아래에서는, 어플리케이션 서버(7100) 및 저장 서버(7200)를 중심으로 설명하기로 한다. 어플리케이션 서버 (7100)에 대한 설명은 다른 어플리케이션 서버(7100n)에도 적용될 수 있고, 저장 서버(7200)에 대한 설명은 다른 저장 서버(7200m)에도 적용될 수 있다.

- [0113] 어플리케이션 서버(7100)는 사용자 혹은 클라이언트가 저장 요청한 데이터를 네트워크(7300)를 통해 저장 서버 들(7200 내지 7200m) 중 하나에 저장할 수 있다. 또한, 어플리케이션 서버(7100)는 사용자 혹은 클라이언트가리드 요청한 데이터를 저장 서버들(7200 내지 7200m) 중 하나로부터 네트워크(7300)를 통해 획득할 수 있다. 예를 들어, 어플리케이션 서버(7100)는 웹 서버 혹은 DBMS(Database Management System) 등으로 구현될 수 있다.

- [0114] 어플리케이션 서버(7100)는 네트워크(7300)를 통해 다른 어플리케이션 서버(7100n)에 포함된 메모리(7120n) 혹은 저장 장치(7150n)에 액세스할 수 있고, 혹은 네트워크(7300)를 통해 저장 서버(7200 ~ 7200m)에 포함된 메모리(7220 ~ 7220m) 혹은 저장 장치(7250 ~ 7250m)에 액세스할 수 있다. 이로써, 어플리케이션 서버(7100)는 어플리케이션 서버들(7100 ~ 7100n) 혹은 저장 서버들(7200 ~ 7200m)에 저장된 데이터에 대해 다양한 동작들을 수행할 수 있다. 예를 들어, 어플리케이션 서버(7100)는 어플리케이션 서버들(7100 ~ 7100n) 혹은 저장 서버들(7200 ~ 7200m) 사이에서 데이터를 이동 혹은 카피(copy)하기 위한 커맨드를 실행할 수 있다. 이 때 데이터는 저장 서버들(7200 ~ 7200m)의 저장 장치로(7250 ~ 7250m)부터 저장 서버들(7200 ~ 7200m)의 메모리들(7220 ~ 7220m)을 거쳐서, 혹은 바로 어플리케이션 서버들(7100 ~ 7100n)의 메모리(7120 ~ 7120n)로 이동될 수 있다. 네트워크(7300)를 통해 이동하는 데이터는 보안 혹은 프라이버시를 위해 암호화된 데이터일 수 있다.

- [0115] 저장 서버(7200)를 예시로 설명하면, 인터페이스(7254)는 프로세서(7210)와 제어기(7251)의 물리적 연결 및 NIC(7240)와 제어기(7251)의 물리적 연결을 제공할 수 있다. 예를 들어, 인터페이스(7254)는 저장 장치(7250)를 전용 케이블로 직접 접속하는 DAS(Direct Attached Storage) 방식으로 구현될 수 있다. 또한, 예를 들어, 인터페이스(1254)는 ATA(Advanced Technology Attachment), SATA(Serial ATA), e-SATA(external SATA), SCSI(Small Computer Small Interface), SAS(Serial Attached SCSI), PCI(Peripheral Component Interconnection), PCIe(PCI express), NVMe(NVM express), IEEE 1394, USB(universal serial bus), SD(secure digital) 카드, MMC(multi-media card), eMMC(embedded multi-media card), UFS(Universal Flash Storage), eUFS(embedded Universal Flash Storage), CF(compact flash) 카드 인터페이스 등과 같은 다양한 인터페이스 방식으로 구현될 수 있다.

- [0116] 저장 서버(7200)는 스위치(7230) 및 NIC(7240)을 더 포함할 수 있다. 스위치(7230)는 프로세서(7210)의 제어에 따라 프로세서(7210)와 저장 장치(7250)를 선택적으로 연결시키거나, NIC(7240)과 저장 장치(7250)를 선택적으로 연결시킬 수 있다.

- [0117] 실시 예에 있어서, NIC(7240)는 네트워크 인터페이스 카드, 네트워크 어댑터 등을 포함할 수 있다. NIC(7240)는 유선 인터페이스, 무선 인터페이스, 블루투스 인터페이스, 광학 인터페이스 등에 의해 네트워크(7300)에 연결될 수 있다. NIC(7240)는 내부 메모리, DSP, 호스트 버스 인터페이스 등을 포함할 수 있으며, 호스트 버스 인터페이스를 통해 프로세서(7210) 혹은 스위치(7230) 등과 연결될 수 있다. 호스트 버스 인터페이스는, 앞서 설명한 인터페이스(7254)의 예시들 중 하나로 구현될 수도 있다. 실시 예에 있어서, NIC(7240)는 프로세서(7210), 스위치(7230), 저장 장치(7250) 중 적어도 하나와 통합될 수도 있다.

- [0118] 저장 서버(7200 ~ 7200m) 혹은 어플리케이션 서버(7100 ~ 7100n)에서 프로세서는 저장 장치(7130 ~ 7130n, 7250 ~ 7250m) 혹은 메모리(7120 ~ 7120n, 7220 ~ 7220m)로 커맨드를 전송하여 데이터를 프로그램 하거나 리드할 수 있다. 이 때 데이터는 ECC(Error Correction Code) 엔진을 통해 에러 정정된 데이터일 수 있다. 데이터는 데이터 버스 변경(Data Bus Inversion: DBI) 혹은 데이터 마스킹(Data Masking: DM) 처리된 데이터로서, CRC(Cyclic Redundancy Code) 정보를 포함할 수 있다. 데이터는 보안 혹은 프라이버시를 위해 암호화된 데이터일 수 있다.

- [0119] 저장 장치(7150 ~ 7150m, 7250 ~ 7250m)는 프로세서로부터 수신된 리드 커맨드에 응답하여, 제어 신호 및 커맨

드/어드레스 신호를 NAND 플래시 메모리 장치(7252-7252m)로 전송할 수 있다. 이에 따라 NAND 플래시 메모리 장치(7252-7252m)로부터 데이터를 리드하는 경우, RE(Read Enable) 신호는 데이터 출력 제어 신호로 입력되어, 데이터를 DQ 버스로 출력하는 역할을 할 수 있다. RE 신호를 이용하여 DQS(Data Strobe)를 생성할 수 있다. 커맨드와 어드레스 신호는 WE(Write Enable) 신호의 상승 엣지 혹은 하강 엣지에 따라 페이지 버퍼에 래치 될 수 있다.

- [0120] 제어기(7251)는 저장 장치(7250)의 동작을 전반적으로 제어할 수 있다. 실시 예에 있어서, 제어기(7251)는 SRAM(Static Random Access Memory)을 포함할 수 있다. 제어기(7251)는 라이트 커맨드에 응답하여 낸드 플래시(7252)에 데이터를 쓸 수 있고, 혹은 리드 커맨드에 응답하여 낸드 플래시(7252)로부터 데이터를 리드할 수 있다. 예를 들어, 라이트 커맨드 혹은 리드 커맨드는 저장 서버(7200) 내의 프로세서(7210), 다른 저장 서버(7200m) 내의 프로세서(7210m) 혹은 어플리케이션 서버(7100, 7100n) 내의 프로세서(7110, 7110n)로부터 제공될 수 있다. DRAM(7253)은 낸드 플래시(7252)에 쓰여질 데이터 혹은 낸드 플래시(7252)로부터 리드된 데이터를 임시 저장(버퍼링)할 수 있다. 또한, DRAM(7253)은 메타 데이터를 저장할 수 있다. 여기서, 메타 데이터는 사용자 데이터 혹은 낸드 플래시(7252)를 관리하기 위해 제어기(7251)에서 생성된 데이터이다. 저장 장치(7250)는 보안 혹은 프라이버시를 위해 SE(Secure Element)를 포함할 수 있다.

- [0121] 한편, 상술된 본 발명의 내용은 발명을 실시하기 위한 구체적인 실시 예들에 불과하다. 본 발명은 구체적이고 실제로 이용할 수 있는 수단 자체뿐 아니라, 장차 기술로 활용 할 수 있는 추상적이고 개념적인 아이디어인 기술적 사상을 포함 할 것이다.

#### 부호의 설명

[0122] 100: 메모리 장치

110: 지연 고정 루프 회로

111: 제 1 지연 라인

112: 제 2 지연 라인

113: 제 1 지연 라인 제어기

114: 제 2 지연 라인 제어기

115: 클록 패스 레플리카

116: 출력 버퍼 레플리카

117: 제 1 위상 검출기

118: 제 2 위상 검출기

119: 디-멀티플렉서

120: DLL 제어기

125: 윈도우 검출 회로

## 도면1

## 도면2a

## 도면2b

## <u>125</u>

도면12