(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

**PARIS**

(11) N° de publication :

(à n'utiliser que pour les commandes de reproduction)

(21) N° d'enregistrement national :

84 10206

2 549 997

(51) Int CI4: G 11 C 11/40; H 01 L 27/00.

DEMANDE DE BREVET D'INVENTION

Α1

(22) Date de dépôt : 28 juin 1984.

(12)

(30) Priorité: JP, 27 juillet 1983, nº 135 815.

(72) Inventeur(s): Makio Uchida.

(71) Demandeur(s): Société dite: HITACHI, LTD. — JP.

(43) Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 5 du 1er février 1985.

60 Références à d'autres documents nationaux apparentés :

73 Titulaire(s) :

74 Mandataire(s): Dupuy et Loyer.

54) Dispositif à circuits intégrés à semiconducteurs, en particulier « mémoires RAM ou ROM ».

67) L'invention concerne un dispositif à circuits intégrés à semiconducteurs.

Ce dispositif appliqué à un réseau de mémoire est subdivisé en un certain nombre de blocs de circuits constitués par des éléments de circuit et par des couches en polysilicium électriquement conductrices PSi, alimentées par une couche d'aluminium AL, les blocs de circuits constituant les éléments de mémoire étant situés au niveau des points d'intersection de lignes de transmission de données D9 D24 et de lignes de transmission de mots WO W5.

Application, notamment, aux dispositifs de mémoire RAM et ROM à grande vitesse de fonctionnement.

La présente invention concerne un dispositif à circuits intégrés à semiconducteurs et en particulier

une technique pouvant être effectivement adaptée à des

dispositifs à circuits intégrés à semiconducteurs, qui incluent des dispositifs à circuits intégrés à semiconducteurs

tels que des mémoires à accès direct ou aléatoire (désignées

ci-après sous le terme de mémoires RAM), des mémoires mortes

(désignées ci-après sous le terme de mémoires ROM) et analoques.

Un dispositif de mémoire à semiconducteurs, tel qu'une mémoire RAM ou ROM, est constitué par une couche de silicium polycristallin conducteur, dans laquelle des lignes de transmission de mots sont formées ainsi que des électrodes de grille d'éléments qui constituent les cellules de mémoire, afin d'accroître le degré d'intégration. La couche de silicium polycristallin électriquement conductrice possède une résistance de couche d'une valeur relativement élevée allant jusqu'à 30 ou 40 ohms/ Det entraîne un retard dans la propagation des signaux.

Afin de réduire le retard de propagation des signaux, il a été proposé de réaliser une couche de câblage métallique possédant une faible résistivité (par exemple quelques milliohms/d) en parallèle avec les moyens de câblage et de les raccorder au bout d'une distance prédéterminée.

Cependant les auteurs à la base de la présente invention ont trouvé que la construction ci-dessus entraîne l'apparition d'un problème tel que décrit ci-après. En effet dans le cas où la couche de câblage métallique est rompue par suite de défauts apparus pendant le processus de fabrication, la résistance de la couche de câblage formée sur la face distante de la partie rompue devient extrêmement supérieure à celle du circuit qui envoie des signaux aux lignes de transmission de mots. Cependant, du point de vue électrique, le circuit mentionné ci-dessus et une cellule de mémoire

sont accouplés par l'intermédiaire de la couche de silicium polycristallin électriquement conductrice possédant une résistivité relativement élevée. En d'autres termes la cellule de mémoire est sélectionnée même lorsque la couche de câblage 5 métallique a été rompue.

C'est pourquoi une rupture de la couche de câblage métallique dans le dispositif de mémoire à semiconducteurs ne peut plus être détectée lors du test de fonctionnement en courant continu conformément auquel les signaux de sortie sont simplement contrôlés grâce à l'envoi de signaux d'adresse au dispositif de mémoire à semiconducteurs.

Dans le cas où la couche de câblage métallique a été rompue, les cellules de mémoire formées sur la

face distante de la partie rompue sont alimentées par des signaux de sélection par l'intermédiaire de la couche de silicium polycristallin électroconductrice possédant une résistivité relativement élevée. C'est pourquoi la durée de sélection de telles cellules de mémoire devient supérieure à la

durée de sélection d'autres cellules de mémoire. L'essai ou

test de fonctionnement en courant continu mentionné ci-dessus

ne permet pas de détecter un dispositif de mémoire à semiconducteurs (désigné ci-après sous le nom de mémoire) qui contient des cellules de mémoire nécessitant des durées ou intervalles de temps différents pour l'opération de sélection.

Par conséquent, on expédie souvent des mémoires possédant

une faible fiabilité.

Afin de trier les mémoires qui sont considérées comme défectueuses, il est nécessaire d'effectuer un test de fonctionnement en courant alternatif, selon lequel

30 les signaux de sortie sont examinés après qu'un intervalle de temps prédéterminé se soit écoulé à partir de l'envoi de signaux d'adresses, ce qui entraîne une opération d'échantillonngage très génante.

En particulier dans le cas d'une mémoire 35 contenant un dispositif à circuits intégrés de grande taille

tels qu'un microcalculateur monopuce, il n'est en général pas possible d'envoyer directement des signaux d'adresses depuis l'unité extérieure et de prélever directement les signaux de sortie vers l'unité extérieure. Par conséquent, le test ou 5 l'essai de fonctionnement en courant alternatif doit être effectué en tenant compte du temps de délai d'un circuit logique interposé entre une borne d'un microcalculateur monopuce et d'une borne d'entrée d'adresses d'une mémoire contenue dans ce microcalculateur ainsi que du temps de retard d'un circuit logique interposé entre une borne d'entrée/sortie de données de la mémoire contenuedans le microcalculateur et une borne de ce dernier. C'est-à-dire que lorsque l'on prend en compte au moins les deux durées ou temps de retard mentionnés ci-dessus, on détermine l'instant auquel les signaux de sortie de la mémoire sont produits à partir du microcalculateur après que les signaux d'adresses ont été introduits dans ce dernier. Le test de fonctionnement est effectué en envoyant des signaux d'adresses au microcalculateur et en examinant les signaux de sortie de ce dernier après que l'intervalle de temps trouvé se soit écoulé. Comme cela a été décrit ci-dessus, il est nécessaire de trouver préalablement l'intervalle de temps mentionné ci-dessus, ce qui rend le test de fonctionnement plus difficile. En outre, on ne peut pas s'attendre non plus à des résultats corrects d'essai .

Le but de la présente invention est de fournir un dispositif à circuits intégrés à semiconducteurs, que l'on puisse aisément évaluer au moyen d'un test ou d'un essai simple.

Un autre but de la présente invention con30 siste à fournir un dispositif à circuits intégrés à semiconducteurs qui permet de réduire un temps de retard de propagation dans une ligne de transmission de signaux et qui peut

être évalué par l'intermédiaire d'un test de fonctionnement

simple.

35

Selon une première idée de l'invention,

ce problème est résolu à l'aide d'un dispositif à circuits intégrés à semiconducteurs caractérisé en ce qu'il comporte :

- une première couche de câblage,

- un premier circuit comportant un premier

transistor à effet de champ à grille isolée et une seconde couche de câblage qui est accouplée à l'électrode de grille dudit premier transistor à effet de champ à grille isolée et

dudit premier transistor à effet de champ à grille isolée et qui est alimentée par un signal provenant de ladite première couche de câblage, et

couche de câblage, et

- un second circuit comportant un second transistor à effet de champ à grille isolée, et une troisième couche de câblage qui est accouplée à l'électrode de grille dudit second transistor à effet de champ à grille isolée et qui est alimentée par un signal provenant de ladite première couche de câblage et ce essentiellement en même temps que s'effectue l'envoi du signal de ladite première couche de câblage à ladite seconde couche de câblage.

Selon une autre idée de la présente invention, le problème indiqué ci-dessus est résolu à l'aide d'un dispositif à circuits intégrés à semiconducteurs caractérisé en ce qu'il comporte :

- une pluralité de colonnes de cellules de mémoire comportant chacune :

- . une première couche de câblage,

- 25 . un premier circuit qui possède une cellule de mémoire qui contient un premier transistor à effet

de champ à grille isolée et qui possède également une seconde couche de câblage qui est accouplée à l'électrode de grille du premier transistor à effet de champ à grille isolée

30 et qui est alimentéepar un signal provenant de ladite première couche de câblage et,

. un second circuit qui possède une cellule de mémoire qui inclut un second transistor à effet de champ à grille isolée et qui possède également une troisième couche de câblage qui est accouplée à l'électrode de grille dudit second transistor à effet de champ à grille isolée qui est alimentée par un signal provenant de ladite première couche de câblage et ce essentiellement en même temps que s'effectue l'envoi du signal de ladite première couche de câblage à ladite seconde couche de câblage, et

- un circuit de sélection qui envoie de façon sélective un signal à ladite pluralité des premières couches de câblage, des colonnes de cellules de mémoire étant sélectionnées parmi une pluralité de colonnes de cellules de mémoire.

D'autres caractéristiques et avantages de la présente invention ressortiront de la description donnée ci-après prise en référence aux dessins annexés, sur lesquels:

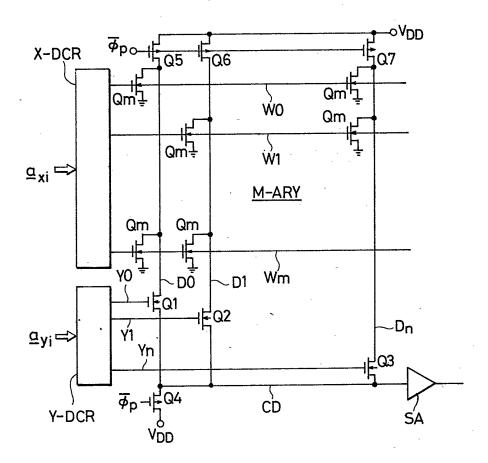

- la figure l'est un schéma d'une mémoire

- 15 ROM conforme à une première forme de réalisation dela présente invention ;

10

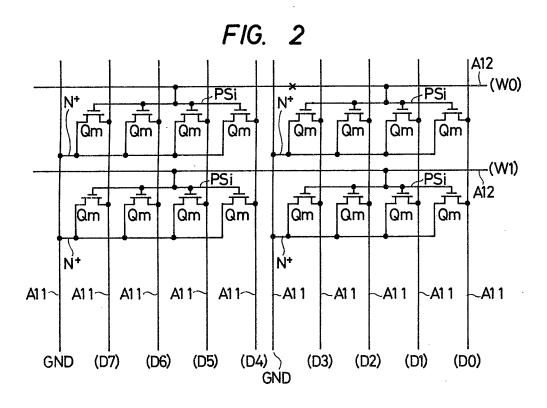

- la figure 2 représente un schéma illustrant l'agencement de la mémoire ROM ;

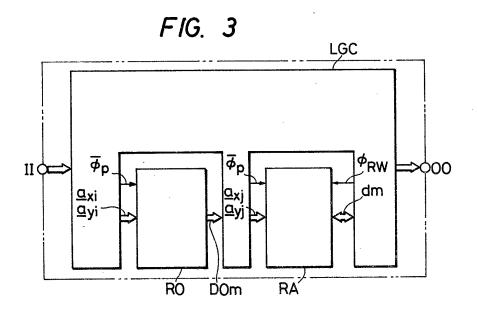

- la figure 3 est un schéma-bloc d'un dis-20 positif à circuits intégrés à haute densité d'intégration conforme à une forme de réalisation de la présente invention;

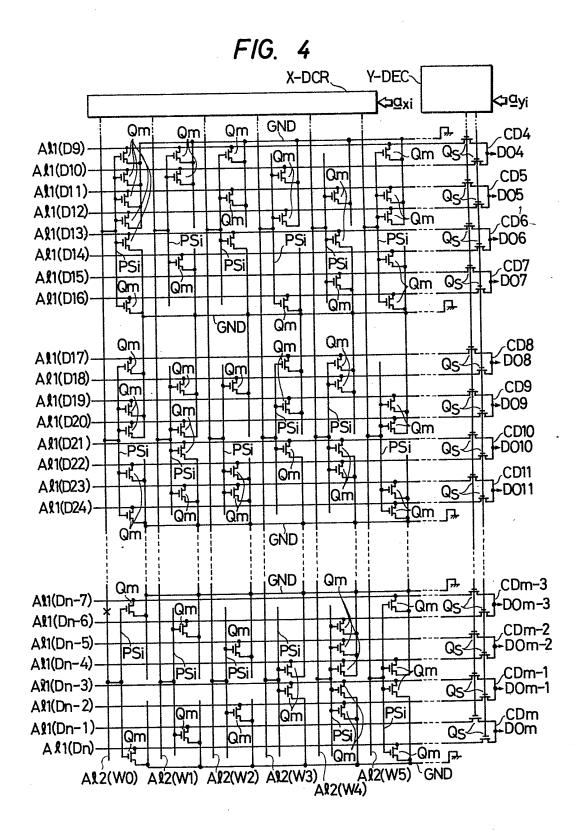

- la figure 4 est un schéma d'une mémoire ROM RO représentée sur la figure 3 représentant la forme de réalisation de l'invention ;

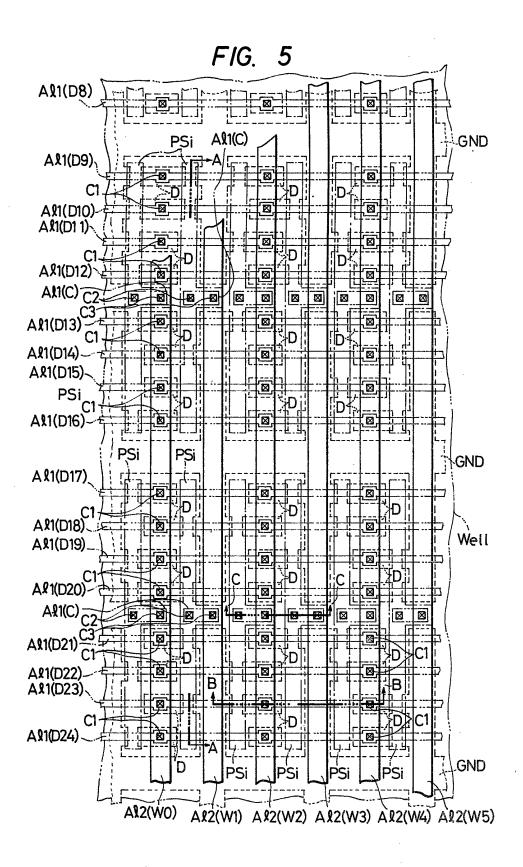

- 25 la figure 5 est une vue en plan illustrant l'agencement de la mémoire ROM qui correspond au schéma de la mémoire ROM de la figure 4 ;

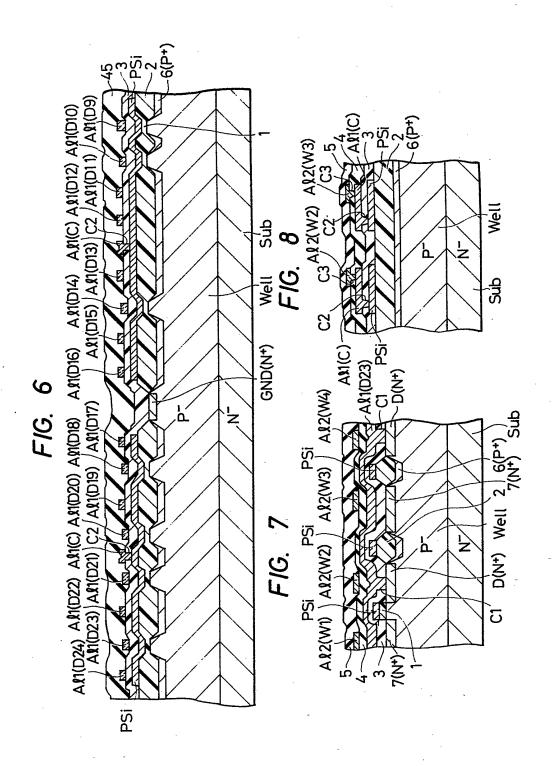

- la figure 6 est une vue en coupe prise suivant la ligne A-A du schéma de l'agencement de la figure 30 5;

- la figure 7 est une vue en coupe prise suivant la ligne B-B du schéma d'agencement de la figure 5 ; - la figure 8 est une vue en coupe prise suivant la ligne C-C du schéma d'agencement de la figure 5 ;

- 35 la figure 9 est un schéma de la mémoire

RAM RA de la figure 3 selon une forme de réalisation de la présente invention ;

5

15

20

25

30

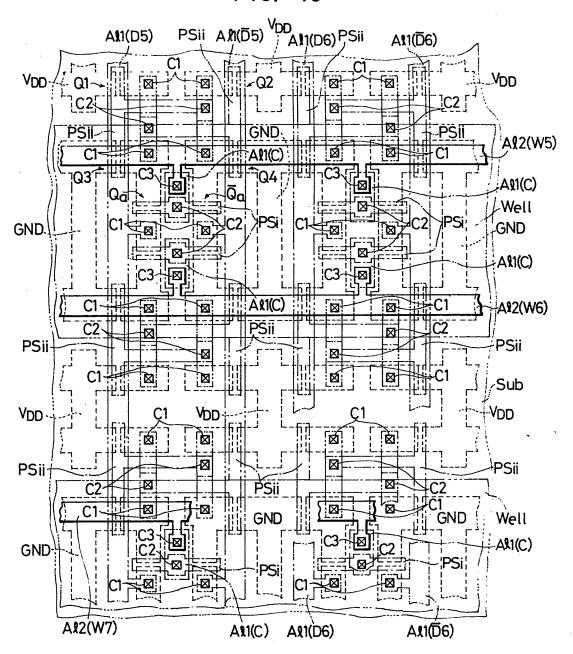

- la figure 10 est une vue en plan illustrant le schéma d'agencement de la mémoire RAM qui correspond au schéma du circuit de la figure 9 ; et

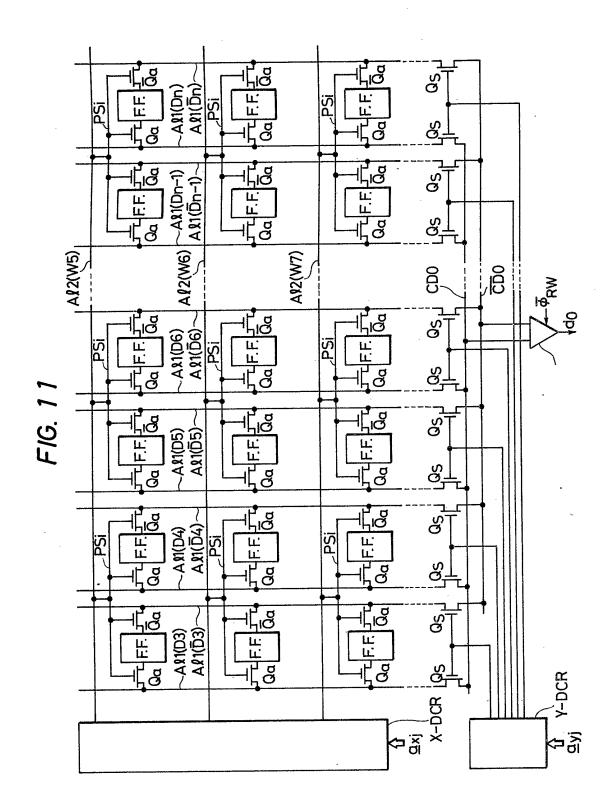

- la figure ll est un schéma d'une mémoire RAM conforme à une autre forme de réalisation de la présente invention.

Ci-après on va décrire les formes de réali-10 sation préférées de l'invention.

La figure l est le schéma d'un circuit d'une mémoire ROM latérale selon une forme de réalisation de la présente invention. Bien qu'il ne faille y voir aucune limitation particulière, les éléments de circuit sont formés sur un substrat semiconducteur tel qu'un monocristal de silicium, à l'aide d'une technique classique de fabrication des circuits intégrés CMOS (MOS complémentaires).

Un décodeur d'adresses X-DCR reçoit une pluralité de premiers signaux d'adresses complémentaires a constitués par une pluralité de signaux d'adresses internes et par une pluralité de signaux d'adresses internes possédant une phase essentiellement inversée par rapport à celle des signaux précédents, forme un signal de sélection et envoie ce signal de sélection à une ligne de transmission de mots W qui est sélectionnée par les signaux d'adresses complémentaires sortant d'une pluralitéde lignes de transmission de mots formées dans un réseau de mémoire M-ARY. Un décodeur d'adresses Y-DCR reçoit une pluralité de seconds signaux d'adresses complémentaires  $\underline{\mathbf{a}}_{\mathbf{Vi}}$ , forme un signal de sélection et envoie ce signal de sélection à un circuit de commutation de colonnes de telle sorte qu'une ligne de transmission de données D est sélectionnée par les signaux d'adresses complémentaires sortantd'une pluralité de lignes de transmission de données formées dans le réseau de mémoire M-ARY.

Le réseau de mémoire M-ARY est constitué

par une pluralité de lignes de transmission de mots WO à Wm, par une pluralité de lignes de transmission de données DO à Dn, par des transistors à effet de champ à grille isolée (désignés ci-après sous le terme de transistors MOSFET) pour 5 la mémorisation de données qui sont fournies de façon sélectives conformément aux données mémorisées en des points d'intersection de ces lignes de transmission de mots et de ces lignes de transmission de données, et des transistors MOSFET de commutation de colonnes Q1 à Q3 qui sont prévus entre les lignes de transmission de données D0 à Dn et une ligne commune de transmission de données CD. Ici, pour simplifier le dessin, la figure l représente à titre d'exemple des lignes de transmission de mots W0, W1, Wm et des lignes de transmission de données DO, D1, Dn parmi une pluralité de lignes de transmission de mots et de lignes de transmission de données. En outre la figure 1 montre uniquement les transistors MOSFET de mémoire dont la tension de seuil est branchée ou appliquée au niveau de sélection des lignes de transmission de mots, mais ne montre pas les transistors MOSFET de mémoire qui sont 20 bloqués, ni ceux dont les grilles ou les drains n'ont pas été raccordés. Dans le réseau de mémoire M-ARY, les grilles des transistors MOSFET de mémoire Qm disposées dans la même colonne sont raccordées aux lignes de transmission de mots WO à Wm qui leur correspondent respectivement. Les drains 25 des transistors MOSFET de mémoire Qm disposés sur la même ligne sont raccordés aux lignes de transmission de données DO à Dn qui leur correspondent respectivement. Bien qu'il ne faille y voir ici aucune limitation particulière, le transistor MOSFET de mémoire Qn et les transistors MOSFET de commutation de colonnes Q1 à Q3 sont constitués par des transis-30 tors MOSFET à canal n qui sont formés dans la même région de puits.

La ligne commune de transmission de données CD est raccordée à la borne d'entrée d'un amplificateur de détection ou de lecture SA qui amplifie les données des transistors MOSFET de mémoire (cellules de mémoire) transmises par la ligne commune de transmission de données CD. C'est pourquoi, en fonction des données des cellules de mémoire, l'amplificateur de lecture SA produit un signal de lecture possédant le niveau haut ou le niveau bas.

Dans cette forme de réalisation, bien qu'il ne s'agisse là d'aucune limitation particulière, des transistors MOSFET de précharge Q5 à Q7 sont prévus pour les lignes de transmission de données DO à Dn en plus d'un transistor 10 MOSFET de précharge Q4 qui est prévu pour la ligne commune de transmission de données CD, afin d'accroître la vitesse de fonctionnement de lecture. Bien qu'il ne faille y voir ici aucune limitation particulière, ces transistors MOSFET de précharge Q4 à Q7 sont constitués par des transistors MOSFET à enrichissement à canal p. Un signal de précharge  $\overline{\emptyset}$ p est appliqué en commun aux grilles de ces transistors MOSFET de précharge. Le signal de précharge Øp est produit par un générateur de signaux de cadencement (non représenté) qui est formé sur le même substrat semiconducteur que celui 20 de la mémoire ROM latérale.

La figure 2 est un schéma qui illustre concrètement un réseau de mémoire M-ARY conforme à la présente invention. En effet, dans cette forme de réalisation, le réseau de mémoire M-ARY est réalisé sous la forme décrite ci-après afin de réduire le temps de retard de propagation intervenant dans les lignes de transmission de mots et dans les lignes de masse du circuit, ce qui permet ainsi de détecter toute rupture des lignes.

C'est-à-dire que, comme cela est représen

té par les lignes de transmission de mots WO, Wl sur la figure 2, les grilles de quatre transistors MOSFET de mémoire

Qm (toutefois ce nombre n'est pas limité à quatre) disposés

dans la même ligne sont raccordées en commun par une couche

de silicium polycristallin électriquement conductrice PSi

qui est réalisée, en même temps que les électrodes de grille,

sous la forme d'une structure unitaire. En outre, bien qu'il ne faille y voir aucune limitation particulière, une seconde couche d'aluminium A22 est formée sur le substrat semiconducteur par l'intermédiaire d'une couche isolante pour chaque ligne, et est disposée essentiellement en parallèle avec la couche de silicium polycristallin électriquement conductrice PSi. Cette couche de silicium polycristallin électriquement conductrice PSi et la seconde couche d'aluminium A22 sont raccordées l'une à l'autre en un emplacement (en un point).

Les électrodes de source des quatre transistors MOSFET de mémoire Qm sont formées par une couche de diffusion commune N<sup>+</sup> et sont raccordées en commun les unes aux autres. La couche de diffusion commune est raccordée, en un emplacement (en un point), dans les lignes de masse GND du circuit, qui est constitué par une première couche d'aluminium qui est formée par le substrat semiconducteur par l'intermédiaire d'une couche isolante et qui s'étend suivant la même direction que la ligne de transmission de données D ou, en d'autres termes, qui est constituée par une première couche d'aluminium ALI formée essentiellement parallèlement à la ligne de transmission de données D.

En outre, bien qu'il ne faille y voir aucune limitation particulière, les régions de drain individuelles des transistors MOSFET de mémoire Qm situés sur la même colonne sont raccordées aux lignes de transmission de données DO à D7 et sont constituéespar des premières couches d'aluminium All formées sur le substrat semiconducteur par l'intermédiaire d'une couche isolante.

La couche de silicium polycristallin électriquement conductrice PSi est formée sur le substrat semiconducteur par l'intermédiaire d'une pellicule isolante. En outre une pellicule isolante est formée entre la couche de silicium polycristallin électriquement conductrice PSi et la première couche d'aluminium ALI, entre la première couche d'aluminium ALI et la seconde couche d'aluminium ALI et entre

la couche de silicium polycristallin électriquement conductrice PSi et la seconde couche d'aluminium A&2. C'est pourquoi, lorsque différentes couches de câblage doivent être accouplées l'une à l'autre comme dans le cas de l'accouplement de la se-5 conde couche d'aluminium Al2 et la couche de silicium polycristallin électriquement conductrice PSi, un trou de contact est formé dans une pellicule isolante qui est située entre ces câblages, et ces câblages sont accouplés l'un à l'autre par l'intermédiaire du trou. Comme cela a été décrit ci-des-10 sus, lorsque différentes couches de câblage doivent être accouplées l'une à l'autre en un emplacement (comme dans le cas de l'accouplement de la couche de silicium polycristallin PSi et de la seconde couche d'aluminium Al2, et dans le cas de l'accouplement d'une région semiconductrice formée dans le substrat semiconducteur et de la première couche d'aluminium A1), un trou de contact est formé dans la pellicule isolante interposée entre ces couches et les câblages sont accouplés ensemble par l'intermédiaire du trou de contact.

Le circuit de cette forme de réalisation 20 fonctionne comme cela est décrit ci-après.

Le signal de précharge \$\overline{\pi}\$p prend le niveau bas avant qu'intervienne la lecture des données mémorisées dans les cellules de mémoire. C'est pourquoi les transistors MOSFET de précharge Q4 à Q7 sont placés à l'état conducteur, et la ligne commune de transmission de données CD et les lignes individuelles de transmission de données D0 à Dn sont préchargées au niveau de la tension \$V\_{\text{DD}}\$ de la source d'alimentation. Ensuite le signal de précharge \$\overline{\pi}\$p prend le niveau haut afin de rendre non conducteur ou d'amener à l'état bloqué les transistors MOSFET de précharge Q4 à Q7, ce qui a pour effet que les cellules de mémoire sont sélectionnées par les décodeurs d'adresses X-DCR et Y-DCR. En fonction des données qui sont enregistrées dans les cellules de mémoire sélectionnées, ces dernières prennent la forme de transistors

MOSFET de mémoire (non représentés) comportant une tension

de seuil élevée par rapport au niveau de sélection des lignes de transmission de mots ou bien prennent la forme de transistors MOSFET Qm possédant une tension de seuil faible par rapport au niveau de sélection. Les cellules de mémoire sélec-5 tionnées sont alimentées par un niveau de sélection à partir du décodeur d'adresses X-DCR par l'intermédiaire de lignes de transmission de mots. C'est pourquoi les transistors MOS-FET de mémoire constituant les cellules de mémoire sont placés à l'état non conducteur ou bloqués ou à l'état conducteur 10 en fonction des données qui sont enregistrées en eux. C'est pourquoi, en fonction des données enregistrées dans les cellules de mémoire sélectionnées, les lignes de transmission de données prennent le niveau haut ou le niveau bas. Par conséquent les données des cellules de mémoire transmises aux 15 lignes de transmission de données sont envoyées à la ligne de transmission de données CD par l'intermédiaire de transistors MOSFET de commutation de colonnes qui sont rendus conducteurs par le décodeur d'adresses Y-DCR, en étant amplifiés par l'intermédiaire d'un amplificateur de détection ou de lecture SA, 20 et sont délivrés sous la forme de signaux de lecture.

Sur la figure 2, si la ligne de transmission de mots WO a été interrompue en une position repérée par X, des signaux de sélection du décodeur d'adresses des X X-DCR ne sont pas envoyés aux cellules de mémoire qui sont <sup>25</sup> formées sur le côté plus éloigné du décodeur d'adresses X X-DCR que la position interrompue (repère X). C'est-à-dire que sur la figure 2 les signaux de sélection ne sont pas envoyés aux quatre transistors MOSFET de mémoire Qm du côté gauche supérieur. C'est pourquoi, même lorsque des signaux 30 d'adresses complémentaires  $\underline{a}_{xi}$ ,  $\underline{a}_{vi}$ , qui sélectionnent ces quatre transistors MOSFET de mémoire, sont envoyés au décodeur des X X-DCR et au décodeur des Y Y-DCR, l'amplificateur de lecture SA produit des signaux prédéterminés à tout moment . C'est-à-dire que les données enregistrées dans les quatre 35 transistors MOSFET de mémoire ne sont pas produites.

C'est pourquoi une rupture de la ligne de transmission de mots (couche d'aluminium A£2) peut être détectée par l'intermédiaire du test de fonctionnement en courant continu qui a été mentionné précédemment, et on peut retirer de toute expédition les mémoires ROM qui sont considérées comme défectueuses.

Etant donné que la ligne de transmission de mots est constituée par la couche d'aluminium A£2, le temps de retard intervenant jusqu'à ce que le signal de sélection soit envoyé aux cellules de mémoire peut être réduit, ce qui permet d'accroître la vitesse de fonctionnement de la mémoire ROM.

La figure 3 est un schéma-bloc d'un dispositif à circuits intégrés à haute densité d'intégration, 15 auquel la présente invention est adaptée, les blocs entourés par une ligne formée de traits mixtes étant formés sur un substrat semiconducteur au moyen de la technique servant à former les circuits intégrés MOS.

Sur la figure 3, le symbole LGC désigne un circuit logique qui utilise des mémoires ROM RO et/ou RAM RA dans la phase de mise en oeuvre d'opérations prédéterminées. Comme cela sera décrit ultérieurement de façon détaillée en référence aux figures 4 et 8, la mémoire ROM RO reçoit des signaux d'adresses complémentaires axi et avi qui sont produits par le circuit logique LGC, et envoie les données des cellules de mémoire désignées par les signaux d'adresses complémentaires  $\underline{a}_{xi}$ ,  $\underline{a}_{yi}$  au circuit logique LGC. Comme cela sera décrit ultérieurement de façon détaillée en référence aux figures 9 et 10, la mémoire RAM RA reçoit les signaux d'adresses complémentaires  $\underline{a}_{xi}$ ,  $\underline{a}_{vi}$  produits par le circuit logique LGC, ainsi qu'un signal de validation d'enregistrement WE, et envoie les données mémorisées dans les cellules de mémoire désignées par les signaux d'adresses complémentaires  $\underline{a}_{xi}$ ,  $\underline{a}_{yi}$  au circuit logique LGC, ou bien mémorise les données du circuit logique LGC dans les cellules de mémoire

qui sont désignées par les signaux d'adresses complémentaires  $\underline{a}_{xi}$ ,  $\underline{a}_{yi}$ .

Sur la figure 3, la référence II désigne des bornes extérieures servant à envoyer des signaux depuis 5 une unité extérieure jusqu'au circuit logique LGC mentionné ci-dessus, et la référence IO désigne des bornes extérieures servant à envoyer des signaux produits par le circuit logique LGC à une unité extérieure. En outre le symbole \$\overline{\phi}\$p désigne un signal de précharge qui est le même que celui mentionné en 10 référence à la figure 1.

Au cours d'un essai visant à évaluer la mémoire ROM RO et la mémoire RAM RA contenues dans le dispositif à circuits intégrés à haute densité d'intégration, bien qu'il ne faille y voir là aucune limitation particulière, des signaux correspondant aux signaux d'adresses complémentaires envoyés à la mémoire ROM RO ou à la mémoire RAM RA sont envoyés par l'intermédiaire des bornes extérieures II, et de signaux correspondant aux signaux de sortie de la mémoire ROM RO et de la mémoire RAM RA sont produits par la borne extérieure 00. En outre, lors de l'essai de la mémoire RAM RA, lorsque les données doivent être enregistrées dans les cellules de mémoire, bien qu'il n'existe aucune limitation particulière, les signaux correspondant aux données devant être enregistrées sont envoyés par l'intermédiaire de la borne 25 extérieure II.

La figure 4 est un schéma de circuit de la mémoire ROM RO de la figure 3.

Afin de simplifier le dessin, la figure 4 représente uniquement une partie de la mémoire ROM RO. Les circuits principaux représentés sur la figure 4 décrivent l'agencement qui est réellement formé sur le substrat semi-conducteur. L'agencement du circuit sera décrit ultérieurement de façon détaillée en référence à la figure 5.

Sur la figure 4, le symbole X-DCR désigne 35 un décodeur d'adresses X et Y-DCR désigne un décodeur d'adres-

ses Y. Le décodeur d'adresses X X-DCR reçoit une pluralité de signaux d'adresses complémentaires avi envoyés à partir du circuit logique LGC, sélectionne les lignes de mots désignés par les signaux d'adresses complémentaires <u>a vi</u> parmi une pluralité de lignes de transmission de mots constituant le réseau de mémoire, et envoie le signal de sélection uniquement aux lignes de transmission de mots sélectionnées. Le décodeur d'adresses Y Y-DCR reçoit une pluralité de signaux d'adresses complémentaires <u>a</u>vi envoyés par le circuit logique LGC, forme un signal de sélection et envoie le signal de sélection à des transistors MOSFET qui constituent des commutateurs de colonnes. C'est pourquoi les transistors MOSFET Os constituant des commutateurs de colonnes travaillent de manière à accoupler les lignes de transmission de données désignées par les signaux d'adresses complémentaires a parmi une pluralité de lignes de transmission de données constituant le réseau de mémoire, aux lignes communes de transmission de données CD.

Le réseau de mémoire est constitué par une pluralité de lignes de transmission de mots A2 (WO) à A22 (Wn), une pluralité de lignes de transmission de données All(DO) à Dll(Dn), du transistor MOSFET de mémoire Qm qui sont prévues sélectivement en fonction des données d'enregistrement au niveau de points d'intersection des lignes de tranmission de 25 mots et des lignes de transmission de données, et des lignes de liaison à la masse GND qui appliquent un potentiel de masse du circuit aux transistors MOSFET Qm. Pour simplifier le dessin, la figure 4 représente des lignes de transmission de mots  $A\ell 2$  (WO) à  $A\ell 2$  (W5), des lignes de transmission de données All(D9) à All(D24) et All(Dn-7) à All(Dn) uniquement. Chacune des lignes de transmission de données est raccordée à une borne d'entrée du transistor MOSFET Qs qui sera commuté par un signal de sélection produit par le décodeur d'adresses Y Y-DCR. Dans cette forme de réalisation, bien qu'il ne faille y voir aucune limitation particu-

lière, deux lignes de transmission de données constituent un ensemble et une ligne de transmission de données est accouplée de façon sélective à la ligne commune de transmission de données CD en fonction d'un signal produit par le décodeur 5 d'adresses Y Y-DCR. En se référant par exemple à un ensemble de lignes de transmission de données constitué par les lignes de transmission de données D9 et D10, l'une ou l'autre des lignes de transmission de données est sélectionnée par un signal produit par le décodeur d'adresses Y Y-DCR, et la li-10 gne de transmission de données sélectionnée est raccordée à la ligne commune de transmission de données correspondante CD4. C'est pourquoi, les données, qui sont transmises depuis un transistor MOSFET de mémoire à la ligne de transmission de données sélectionnée, sont transmises à la ligne commune de 15 transmission de données CD4 et sont envoyées en tant que données de sortie DO4 au circuit logique LGC.

Bien que ceci ne soit pas représenté sur la figure 4, chacune des lignes de transmission de données comporte un transistor MOSFET de précharge servant à précharge ger la capacité parasite qui est présente dans les lignes de transmission de données. Bien qu'il n'y ait là aucune limitation spécifique, le transistor MOSFET de précharge est constitué par un transistor MOSFET à enrichissement à canal p, tout comme les transistors MOSFET de précharge Q4 à Q7 représentés sur la figure 1, et l'électrode de grille de ce transistor est alimentée par un signal de précharge \( \overline{Q} \)p produit par le circuit logique LGC.

La figure 4 représente uniquement les transistors MOSFET de mémoire Qm qui sont placés à l'état conducteur par un signal de sélection provenant du décodeur d'adresses X X-DCR. Les transistors MOSFET de mémoire Qm sont constitués par des transistors MOSFET à canal n. En effet la figure 4 représente uniquement les transistors MOSFET de mémoire qui sont placés à l'état conducteur uniquement lorsqu'un signal de sélection possédant un potentiel de sélec-

tion (par exemple 5 volts) est reçu par le décodeur d'adresses X X-DCR, mais ne représente pas les transistors MOSFET de mémoire qui ne travaillent pas essentiellement en tant que transistors MOSFET.

Dans le réseau de mémoire mentionné précédemment, les grilles des transistors MOSFET de mémoire Qm disposés sur la même colonne sont accouplées électriquement à la même ligne de transmission de mots et les drains des transistors MOSFET de mémoire Qm disposés suivant la même ligne sont accouplés électriquement à la même ligne de transmission de données.

Dans cette forme de réalisation, le réseau de mémoire est constitué comme décrit ci-dessous de manière à réduire le temps de retard de propagation des signaux dans les lignes de transmission de mots, et c'est ainsi qu'une rupture des lignes de transmission de mots peut être aisément détectée.

En effet, bien qu'il ne faille y voir aucune limitation particulière, les blocs de circuits sont constitués chacun essentiellement avec huit transistors de mémoire MOSFET Qm suivant la direction d'une colonne. En d'autres termes, chaque colonne comporte une pluralité de blocs de circuit dont chacun comporte essentiellement huit transistors MOSFET de mémoire. Ici, il faut attirer l'attention sur le 25 fait que les huit transistors MOSFET de mémoire constituant un bloc de circuit comprennent des transistors MOSFET de mémoire qui ne travaillent pas essentiellement en tant que transistors MOSFET même lorsque des données d'enregistrement y sont introduites. Les transistors MOSFET de mémoire constituant les blocs de circuit comportent des électrodes de grille qui sont réalisées sous la forme d'une structure unitaire avec la couche de silicium polycristallin électriquement conductrice. En d'autres termes, lorsqu'un bloc de circuit contient une pluralité de transistors MOSFET de mémoire, qui fonctionnent en tant que transistors MOSFET, leurs électrodes

de grille sont accouplées ensemble par la couche en silicium polycristallin électriquement conductrice. Ici on tiendra compte du fait que la couche de silicium polycristallin électriquement conductrice PSi accouple les électrodes de grille uniquement des transistors MOSFET de mémoire qui sont contenus dans le même bloc de circuit, mais n'accouple pas les électrodes de grille des transistors MOSFET de mémoire qui sont contenues dans d'autres blocs de circuit. Les blocs de circuit disposés suivant la même colonne sont accouplés l'un à l'autre par l'intermédiaire d'une couche d'aluminium qui constitue une ligne de transmission de mots. C'est-à-dire que les couches de silicium polycristallin électriquement conductrices PSi de différents blocs de circuit sont accouplées les unes aux autres par l'intermédiaire de la couche d'aluminium qui constitue une ligne de transmission de mots.

Dans cette forme de réalisation, bien qu'il ne faille y voir là aucune limitation particulière, les lignes de transmission de mots sont constituées par une seconde couche d'aluminium A 2, comme cela sera décrit ultérieurement en référence aux figures 5 à 8. En outre, bien qu'il ne faille y voir aucune limitation particulière, la seconde couche d'aluminium AL2 et la couche de silicium polycristallin électriquement conductrice PSi sont accouplées l'une à l'autre comme décrit ci-dessus. C'est-à-dire que, comme représenté sur la figure 8, la seconde couche d'aluminium Al2 est accouplée une fois la première couche d'aluminium All qui est accouplée à la couche de silicium polycristallin électriquement conductrice PSi. Ceci contribue à réduire la surface qui est nécessaire pour l'accouplement de la couche d'aluminium Al2 et de la couche de silicium polycristallin électriquement conductrice PSi.

Parmi les huit transistors MOSFET de mémoire constituant un bloc de circuit, quatre transistors MOSFET de mémoire possèdent des ragions de source qui sont constituées par une région semiconductrice commune de type N<sup>+</sup> qui

30

est accouplée à une ligne de masse GND, qui est formée essentiellement parallèlement à la ligne de transmission de données. Dans cette forme de réalisation, bien qu'il ne faille y voir aucune limitation particulière, la ligne de masse GND est constituée par une région semiconductrice de type N<sup>+</sup>; cette région semiconductrice de type N<sup>+</sup> GND et la région semiconductrice de type N commune mentionnée ci-dessus ont été réalisées sous la forme d'une structure unitaire. Les régions de drain des transistors MOSFET de mémoire disposés suivant la même ligne sont raccordées à la première couche d'aluminium All qui constitue une ligne de transmission de données.

La mémoire ROM conforme à cette forme de réalisation fonctionne presque de la même manière que la forme de réalisation mentionnée précédemment des figures 1 et 2 et n'est pas décrite ici.

Dans la figure 4, si la ligne de transmission de mots AD2 (WO) est rompue en une position repérée par X, le signal de sélection n'est pas envoyé aux blocs de circuits formés sur le côté qui est plus éloigné du décodeur d'adresses X X-CDR que la position interrompue, comme dans le cas de la forme de réalisation de la figure 1. En effet, sur la figure 4, le signal de sélection n'est pas envoyé aux blocs de circuit situés sur le côté inférieur gauche. C'est pourquoi, lorque le décodeur d'adresses X X-DCR et le décodeur d'adresses Y Y-DCR sont alimentés par les signaux d'adresses complémentaires a xi, a yi, qui sélectionnent des cellules de mémoire contenues dans ces blocs de circuit, la mémoire ROM RO envoie au circuit logique LGC uniquement des signaux prédéterminés, et non pas les données qui ont été enregistrées dans les cellules de mémoire sélectionnées.

Ceci permet de tester aisément les mémoires contenues dans un dispositif à circuits intégrés et à haute densité d'intégration.

35

En outre, étant donné que le signal de sé-

lection est envoyé aux blocs de circuit par l'intermédiaire d'une couche d'aluminium, la vitesse de fonctionnement de la mémoire ROM RO peut être accrue.

La figure 5 est une vue en plan montrant

5 une partie essentielle de la mémoire ROM RO de la figure 4.

En effet la figure 5 est une vue en plan du réseau de mémoire constitué par les lignes de transmission de données All (D9) à All(D24), par les lignes de transmission de mots Al2 (W0) à Al2(W5), par les transistors MOSFET de mémoire prévus au niveau des points d'intersection des lignes de transmission de données All(D9) à All(D24) et des lignes de transmission de mots Al2(WO) à Al2(W5), et par une pluralité de lignes de masse GND, qui sont représentées sur la figure 4.

Sur la figure 5, des régions entourées par 15 des lignes en traits mixtes représentent des régions semiconductrices de type N<sup>+</sup> formées sur la surface principale de régions de puits de type p repérées par le mot "puits" et qui sont formées sur le substrat semiconducteur (comme par exemple un substrat en silicium de type n ) Sub. Les régions 20 entourées par des lignes formées de tirets représentent des couches de silicium polycristallin électriquement conductrices formées sur les surfaces principales des régions de puits de type p Puits par l'intermédiaired'une pellicule isolante (telle qu'une pellicule de bioxyde de silicium) qui est for-25 mée sur les surfaces principales des régions de puits de type p Puits. Les régions entourées par des lignes formées par une alternance de tirets et d'ensembles de deux points, représentent les premières couches d'aluminium All, et les régions entourées par des lignes en trait plein représentent 30 les secondes couches d'aluminium Al2. Sur la figure 5, le symbôle D désigne en outre des régions semiconductrices de type  $N^+$  servant à former des régions de drain pour les transistors de mémoire MOSFET. La couche de silicium polycristallin électriquement conductrice PSi réalisée sous la forme

35 d'une structure unitaire avec les électrodes de grille d'une

pluralité de transistors MOSFET constituant le bloc de circuit est raccordée électriquement à la seconde couche d'aluminium A2(W) par l'intermédiaire de la première couche d'aluminium A1(C). C'est pourquoi les signaux produits par le

décodeur d'adresses X X-DCR sont transmis à l'électrode de

grille des transistors MOSFET de mémoire qui constituent les

blocs de circuit.

Bien que ceci ne soit pas représenté sur la figure 5, une pellicule isolante est formée entre la première couche d'aluminium ALI et la seconde couche d'aluminium ALI, et une autre pellicule isolante est également formée entre la première couche d'aluminium ALI et la couche de silicium polycristallin électriquement conductrice.

Sur les figures 4, 5, 6, 7 et 8, les mêmes  $^{5}$  parties sont désignées par les mêmes symboles.

La figure 6 est une vue en coupe prise suivant la ligne A-A de la figure 5.

Sur la figure 6, le chiffre de référence l désigne une pellicule isolante mince (par exemple une pelli-20 cule de bioxyde de silicium) qui constitue une pellicule isolante de grille pour des transistors de mémoire MOSFET. Les transistors MOSFET de mémoire du type à enrichissement sont formés dans la région dans laquelle la pellicule d'isolant de grille l est formée. C'est-à-dire que la couche de silicium polycristallin électriquement conductrice formée sur la pellicule d'isolant de grille 1 sert d'électrode de grille pour les transistors MOSFET de mémoire du type à enrichissement. D'autre part le chiffre de référence 2 désigne une pellicule isolante (par exemple une pellicule de bioxyde de silicium) qui est plus épaisse que la pellicule d'isolant de grille l et qui constitue une pellicule de bioxyde de champ. Le chiffre de référence 6 désigne une région semiconductrice de type p qui forme un dispositif d'arrêt de canal. GND désigne une région semiconductrice de type N<sup>+</sup> qui forme la ligne de masse 35 mentionnée précédemment. Le chiffre de référence 3 désigne

une pellicule isolante intermédiaire qui sépare la couche de silicium polycristallin électriquement conductrice PSi de la première couche d'aluminium All et qui est constituée par du verre au phosphosilicate (désignée ci-après sous le terme de 5 pellicule PSG). Le symbole C2 désigne un trou de contact formé dans la pellicule isolante intermédiaire 3. La première couche d'aluminium Al (C) et la couche de silicium polycristallin électriquement conductrice PSi sont raccordées par l'intermédiaire du trou de contact C2. Le chiffre de référen-10 ce 45 désigne une pellicule isolante qui est constituée par une pellicule isolante intermédiaire (par exemple une pellicule de PSG) interposée entre la première couche d'aluminium All et la seconde couche d'aluminium Al2, et une pellicule finale de passivation (par exemple en  $\mathrm{Si}_{3}\mathrm{N}_{4}$ ) est formée sur la seconde couche d'aluminium A&2. Sur la figure 6, le symbole Sub désigne un substrat semiconducteur de type n, et Puits désigne une région de puits de type p formé dans le substrat semiconducteur de type n.

La figure 7 est une vue en coupe prise 20 suivant la ligne B-B de la figure 5.

Sur la figure 7, All (D23) désigne une première couche d'aluminium qui constitue une ligne de transmission de donnée All (D23) et est accouplée à une région semiconductrice D de type n<sup>+</sup> par l'intermédiaire d'un trou de contact Cl formé dans la pellicule isolante intermédiaire 3. La région semiconductrice D de type n<sup>+</sup> est formée sur une surface principale de la région de puits de type p de manière à former des régions de drain pour les transistors MOSFET de mémoire. Le chiffre de référence 4 désigne une pellicule isolante intermédiaire formée sur la surface principale de la première couche d'aluminium All (D23). Ceci empêche une connexion électrique indésirable entre la première couche d'aluminium All et la seconde couche d'aluminium All. Les symboles All (W1) et All (W4) désignent des secondes couches d'aluminium qui constituent les lignes de transmission de mots All (W1) à

A22(W4). Le chiffre de référence 5 désigne une pellicule finale de passivation et la référence 7 désigne une région semiconductrice de type n<sup>+</sup> qui sert de région de source au transistor MOSFET de mémoire et qui, bien qu'il ne faille y voir aucune limitation particulière, est réalisée sous la forme d'une structure unitaire avec la région semiconductrice de type n<sup>+</sup> mentionnée ci-dessus GND.

Sur la figure 7, on notera le fait que les pellicules isolantes formées au-dessous des couches de silicium polycristallin électriquement conductrices PSi possèdent des épaisseurs différentes en fonction des couches de silicium polycristallin PSi. Ceci permet au transistor MOS-FET de mémoire constituant les cellules de mémoire, de travailler en tant que transistors MOSFET du type à enrichisse-15 ment ou bien de ne pas travailler essentiellement en tant que transistors MOSFET, en fonction des données devant être mémorisées dans les cellules de mémoire. Sur la figure 7, la pellicule isolante possède une faible épaisseur au-dessous de la couche de silicium polycristallin électriquement conductrice PSi, qui est formée sur le côté le plus à gauche. C'est pourquoi un transistor MOSFET de mémoire du type à enrichissement est formé dans cette région. D'autre part, les pellicules isolantes formées au-dessous du reste des couches de silicium polycristallin PSi possèdent une épaisseur importante de sorte que les transistors MOSFET de mémoire formés dans ces régions ne travaillent essentiellement pas en tant que transistors MOSFET.

La figure 8 est une vue en coupe suivant la ligne C-C de la figure 5.

30

Sur la figure 8, le symbole C2 désigne un trou de contact formé dans la pellicule isolante intermédiaire 3. La première couche d'aluminium All(C) et la couche de silicium polycristallin électriquement conductrice PSi sont accouplées l'une à l'autre par l'intermédiaire du trou de contact C2. Le symbole C3 désigne un trou de contact formé

dans la pellicule isolante intermédiaire 4. Les secondes couches d'aluminium Al2(W2), Al2(W3) et la première couche d'aluminium Al1(C) sont accouplées l'une à l'autre par l'intermédiaire du trou de contact C3. Par conséquent la seconde couche d'aluminium Al2(Wn) formant la ligne de transmission de mots Al2(W3) est accouplée électriquement à la couche de silicium polycristallin électriquement conductrice PSi qui est réalisée sous la forme d'une structure unitaire avec les électrodes de grille des transistors MOSFET de mémoire.

10

Par conséquent la seconde couche d'aluminium Al2 est accouplée à la couche de silicium polycristallin électriquement conductrice PSi par l'intermédiaire de la première couche d'aluminium All (C). Par conséquent, la seconde couche d'aluminium Al 2 est accouplée à la couche de silicium polycristallin électriquement conductrice (i) requérant une surface relativement faible. Si l'on essaie d'accoupler directement la seconde couche d'aluminium Al2 et la couche de silicium polycristallin électriquement conductrice PSi l'une à l'autre, il faut former un trou de contact important pour accoupler la couche d'aluminium A 2 et la couche de silicium polycristallin PSi l'une à l'autre, étant donné que l'épaisseur de la pellicule isolante intermédiaire devient relativement importante entre ces éléments. 25 Ceci requiert plutôt, pour l'accouplement, une surface accrue par rapport au cas où l'accouplement est réalisé dans la forme de réalisation de la présente invention.

En accouplant la seconde couche d'aluminium M2 et la couche de silicium polycristallin électriquement conductrice PSi comme cela est réalisé dans la forme de réalisation de la présente invention, on réduit la surface pour le couplage et le degré d'intégration peut être accru. Mais, dans la présente invention, le procédé d'accouplement n'a pas besoin d'être obligatoirement limité uniquement au procédé mentionné ci-dessus. La couche d'aluminium A22 et la

couche de silicium polycristallin électriquement conductrice peuvent être accouplées directement l'une à l'autre.

On va décrire ci-après un procédé de fabrication des dispositifs à circuits intégrés à semiconducteurs 5 (se reporter aux figures 5 à 8).

- Dans un substrat en silicium monocrystal-(A) lin de type n, on forme une région de puits de type p dans une région où les transistors MOSFET à canal n doivent être formés. Ensuite dans la région de puits de type n Puits et dans le substrat en silicium de type n, on forme une pellicule de bioxyde de silicium et une pellicule de  $Si_3N_4$  dans une région où les transistors MOSFET à canal n doivent être formés et dans une région où les transistors MOSFET à canal p (tels que les transistors MOSFET de précharge mentionnés ci-dessus) doivent être formés. Dans les régions où la pellicule de  $Si_3N_4$  n'est pas formée, on fait diffuser de façon sélective des ions de bore et de phosphore de manière à former des dispositifs d'arrêt de canal. Les figures 6 à 8 représentent uniquement un dispositif d'arrêt de canal 6 qui est formé dans la région de puits de type p . Ensuite, en utilisant la pellicule de  $Si_3N_4$  en tant que masque, on oxyde de façon sélective la surface du substrat, de manière

- Dans cette forme de réalisation, ni la pel

licule de SiO<sub>2</sub>, ni la pellicule de Si<sub>3</sub>N<sub>4</sub> ne sont formées

dans la région où on devra former des électrodes de grille

de transistors de mémoire MOSFET qui ne travaillent pas

essentiellement en tant que transistors MOSFET. C'est pourquoi, comme cela est représenté sur les figures 6 et 7, le

dispositif d'arrêt de canal de type p<sup>+</sup> 6 et la pellicule

d'oxyde de champ 2 sont également formés dans la région où

on ne formera aucune électrode de grille de transistor MOSFET de mémoire qui ne travaille pas essentiellement en tant

que transistor MOSFET. D'autre part, la pellicule de SiO<sub>2</sub>

et la pellicule de Si<sub>3</sub>N<sub>4</sub> sont formées dans la région où l'on

à former une pellicule de bioxyde de champ 2.

formera des transistors MOSFET de mémoire qui fonctionnent à la manière de transistors MOSFET du type à enrichissement. C'est pourquoi le dispositif d'arrêt de canal et la pellicule de bioxyde de champ 2 ne sont pas formés dans cette région. En d'autres termes, la pellicule de SiO<sub>2</sub> et la pellicule de Si<sub>3</sub>N<sub>4</sub> sont formées ou non en fonction des données qui doivent être enregistrées dans les transistors MOSFET de mémoire.

Ici, les transistors MOSFET de mémoire, qui travaillent en tant que transistors MOSFET du type à enrichissement, sont ceux qui sont placés à l'état conducteur ou bloqués par un signal envoyé par le décodeur d'adresses X X-DCR. D'autre part, les transistors MOSFET de mémoire, qui ne fonctionnement pas essentiellement en tant que transistors MOSFET, sont ceux qui restent placés à l'état bloqué à tout moment indépendamment des signaux envoyés par le décodeur d'adresses X X-DCR.

On va considérer à nouveau le procédé de fabrication.

- On élimine la pellicule de SiO<sub>2</sub> et la pellicule de Si<sub>3</sub>N<sub>4</sub> et l'on oxyde la surface principale de la région, où les transistors MOSFET (par exemple les transistors MOSFET de mémoire qui travaillent en tant que transistors MOSFET du type à enrichissement) doivent être formés, de manière à former une pellicule d'isolant de grille mince (pellicule de SiO<sub>2</sub>) l dans le substrat Sub et dans la région de puits Puits.

- (C) On forme une couche de silicium polycristallin en utilisant le procédé CVD (c'est-à-dire le procédé de dépôt chimique en phase vapeur) sur l'ensemble des surfaces de la pellicule de champ 2 et de la pellicule d'isolant de grille l. Ensuite, on fait diffuser des impuretés de type n telles que des ions de phosphore de manière à réduire la résistance de la couche de silicium polycristallin ou, en d'autres termes, de manière à former une couche

de silicium polycristallin électriquement conductrice. Dans ce cas, on fait diffuser des impuretés de type n à une concentration élevée. Ensuite on soumet la couche de silicium polycristallin (couche de silicium polycristallin électriquement conductrice) possédant une faible résistance à une attaque chimique sélective basée sur la technique d'attaque chimique photosensible. C'est-à-dire que la couche de silicium polycristallin est retirée des parties inutiles, hormis dans les parties qui correspondent aux électrodes de grille de transistors MOSFET et dans les parties qui correspondent aux couches de silicium polycristallin électriquement conductrice PSi mentionnées précédemment. Ensuite, on élimine par attaque chimique la pellicule d'isolant de grille qui est à nu.

15 (D) On forme un masque de résine photorésistante sur la région où les transistors MOSFET à canal p (par exemple les transistors MOSFET de précharge) doivent être formés, et l'on implante des impuretés de type n tels que des ions de phosphore. En effet on implante des ions de phosphore dans la surface principale de la région de puits de type p Puits qui est auto-alignée par rapport aux électrodes de grille (incluant des parties qui fonctionnent en tant qu'électrodes de grille dans la couche de silicium polycristallin électriquement conductrice PSi). C'est pourquoi il se produit la formation d'une région semiconductrice de type n<sup>+</sup> qui sert de région de source 7 pour le transistor MOSFET à canal n, ainsi qu'une région semiconductrice de type n qui sert de région de drain D pour ce transistor. Dans ce cas, le masque de résine photorésistante n'est pas formé dans la région où sera réalisée une région semiconductrice qui correspond à la ligne de masse GND. Par conséquent la région semiconductrice de type  $n^{\dagger}$  GND est formée dans la région de puits de type p comme représenté sur la figure 6.

La couche de silicium polycristallin élec-

triquement conductrice PSi forme une électrode de grille des transistors MOSFET de mémoire, et une couche de câblage qui relie la ligne de transmission de mots à l'électrode de grille du transistor MOSFET.

- Le masque de résine photorésistante formé lors de la phase opératoire (D) ci-dessus est éliminé. Ensuite on forme un masque de résine photorésistante sur la région dans laquelle les transistors MOSFET à canal n doivent être formés et dans la région où la couche de silicium polycristallin électriquement conductrice PSi doit être formée, et l'on implante des impuretés de type p tels que des ions de bore. En effet, les ions de bore ne sont implantés dans le substrat Sub qui est auto-aligné par rapport aux électrodes de grille des transistors MOSFET à canal p. Par conséquent, on réalise la formation d'une région semiconductrice de type p<sup>†</sup> qui sert de région de source pour le transistor MOSFET à canal p et une région semiconductrice de type p<sup>†</sup> qui sert de région de drain pour ce transistor.

- Dans cette phase opératoire, on implante 20 des ions de bore en une concentration relativement faible. C'est pourquoi, tout comme les électrodes de grille des transistors MOSFET à canal n, les électrodes de grille des transistors MOSFET à canal p sont formées au moyen de la couche de silicium polycristallin de type n.

- On élimine le masque de résine photorésistante formé lors de la phase opératoire ci-dessus (E) et l'on forme une pellicule de PSG 3 en utilisant le procédé de dépôt chimique en phase vapeur, sur l'ensemble des surfaces.

- 30 (G) On forme des trous de contact C1, C2 dans la pellicule de PSG 3 sur la région de drain D et dans la pellicule de PSG 3 sur la couche de silicium polycristallin électriquement conductrice PSi des transistors MOSFET de mémoire.

- 35 Ensuite on forme une couche d'aluminium All

par évaporation sur l'ensemble des surfaces et on lui donne les formes désirées au moyen d'une attaque chimique de manière à obtenir des premières couches d'aluminium ALI(C), ALI(D0) à ALI(Dn). Les lignes de transmission de données ALI(D0) à ALI(Dn) sont accouplées aux régions de drain D des transistors MOSFET de mémoire par l'intermédiaire de trous de contact respectifs Cl (figure 7). En outre, les câblage ALI(C) sont accouplés aux couches de silicium polycristallin électriquement conductrices PSi par l'intermédiaire de diaire de trous de contact respectifs C2 (figure 8).

On forme un trou de contact C3 dans la pellicule de PSG 4, qui est formée sur la première couche d'aluminium Al(C).

Ensuite, on forme une couche d'aluminium

15 Al2 par évaporation sur l'ensemble des surfaces et on lui

donne les formes désirées au moyen d'une attaque chimique

afin d'obtenir des secondes couches d'aluminium Al2 (WO) à

Al2 (Wn). Les secondes couches d'aluminium Al2 (WO) à Al2 (Wn)

sont accouplées aux premières couches d'aluminium Al1 (C)

20 par l'intermédiaire de trous de contact respectifs C3.

- (I) On forme une pellicule finale de passivation 5 sur l'ensemble des surfaces de manière à achever le dispositif à circuits intégrés à semiconducteurs, tel que représenté sur les figures 6 à 8.

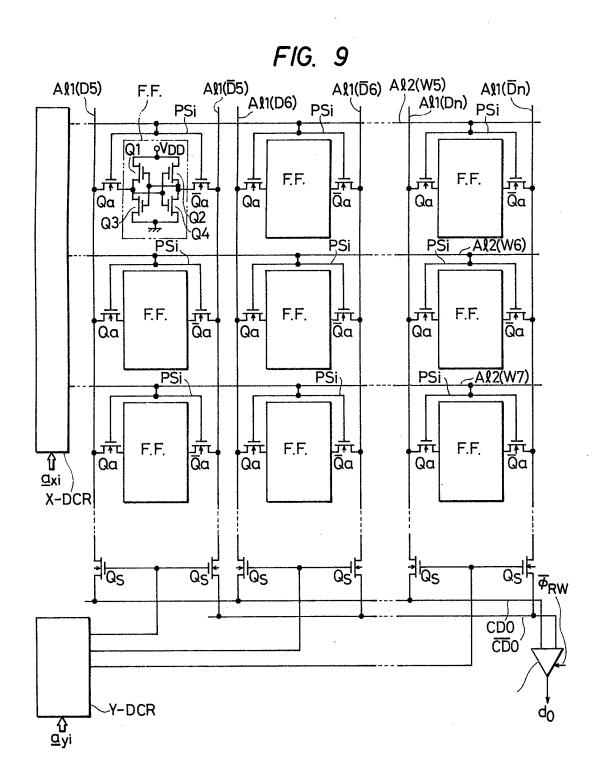

- La figure 9 représente le schéma du circuit de la mémoire RAM RA réprésenté sur la figure 3. Afin de simplifier le dessin, la figure 9 représente uniquement une partie de la mémoire RAM RA. Comme cela sera mentionné ultérieurement de façon détaillée en référence à la figure 10, les circuits principaux indiqués sur la figure 9 représentent l'agencement qui est réellement formé sur le substrat semiconducteur.

Sur la figure 9 le symbole X-DCR désigne un décodeur d'adresses X et le symbole Y-DCR désigne un décodeur d'adresses Y. Le décodeur d'adresses X X-DCR reçoit

une pluralité de signaux d'adresses complémentaires  $\underline{\underline{a}}_{xi}$ envoyés par le circuit logique LGC, sélectionne les lignes de transmission de mots désignées par les signaux d'adresses complémentaires  $\underline{a}_{xj}$  parmi une pluralité de lignes de transmission de mots constituant le réseau de mémoire, et envoie un signal de sélection uniquement dans la ligne de transmission de mots sélectionnée. Le décodeur d'adresses Y Y-DCR reçoit une pluralité de signaux d'adresses complémentaires  $\underline{a}_{\mathbf{x}\,\mathbf{j}}$  délivrés par le circuit logique LGC de manière à former un signal de sélection, et envoie le signal de sélection à des transistors MOSFET qui constituent des commutateurs de colonnes. C'est pourquoi les transistors MOSFET constituant les commutateurs de colonnes travaillent de manière à accoupler deux lignes de transmission de données 15 complémentaires désignées par les signaux d'adresses complémentaires  $\underline{a}_{vi}$  parmi une pluralité de couples de lignes de transmission de données complémentaires formant le réseau de mémoire, à un couple de lignes communes de transmission de données complémentaires CD0, CD0.

20 Le réseau de mémoire est constitué par une pluralité de lignes de transmission de mots Al2(WO) à Al2(Wn), par une pluralité de couples de lignes de transmission de données complémentaires All(D0),  $All(\overline{D}0)$  à All(Dn),  $All(\overline{D}n)$ , et par des cellules de mémoire prévues au niveau des points d'intersection des lignes de transmission de mots et des lignes de transmission de données. Afin de simplifier le dessin, la figure 9 représente uniquement les lignes de transmission de mots A $\ell$ 2(W5) à A $\ell$ 2(W7), des couples de lignes de transmission de données Al15D5), A $\ell$ 1( $\overline{D}$ 5), A $\ell$ 1(D6), A $\ell$ 1(D6) et AC1 (Dn), AC1 ( $\overline{D}$ n), et des cellules de mémoire prévues au niveau des points d'intersection des lignes de transmission de mots A2(W5) à A2(W7) et des couples de lignes de transmission de données All(D5), A $\ell$ 1( $\overline{D}$ 5), A $\ell$ 1(D6), A $\ell$ 1( $\overline{D}$ 6) et All (Dn), All (Dn). 35

Les couples de lignes de transmission de

données sont raccordés à des bornes d'entrée/sortie d'un côté du transistor MOSFET Qs qui seront commutés par un siqual de sélection envoyé par le décodeur d'adresses des Y Y-DCR. Les bornes d'entrée/sortie de l'autre côté de ces 5 transistors MOSFET Qs sont accouplés au couple des lignes de transmission de données complémentaires CDO, CDO. Parmi les pluralités de couples de lignes de transmission de données complémentaires, Al(D0),  $Al(\overline{D0})$  à Al(Dn),  $Al(\overline{Dn})$ , deux couples de lignes de transmission de données complémen-10 taires désignées par les signaux d'adresses complémentaires a\_v; sont accouplés aux deux lignes communes de transmission de données complémentaires CDO, CDO par l'intermédiaire des transistors MOSFET Qs. C'est pourquoi la donnée transmise depuis une cellule de mémoire au couple des lignes de trans-15 mission complémentaires est ensuite transmise au couple des lignes communes de transmission de données complémentaires par l'intermédiaire des transistors MOSFET Qs et est envoyée au circuit logique LGC par l'intermédiaire d'un circuit amplificateur/tampon de sortie.

20 Bien que ceci ne soit pas représenté sur la figure 9, la mémoire RAM RA est équipée d'un tampon d'entrée qui reçoit les données envoyées par le circuit logique LGC et qui envoie ces données au couple de lignes communes de transmission de données complémentaire CDO, CDO. Lors de l'opération d'enregistrement, les données envoyées par le circuit logique LGC sont transmises aux lignes communes de transmission de données complémentaires CDO, CDO par l'intermédiaire du tampon d'entrée. Les données sont ensuite transmises au couple de lignes de transmission de données complémentaires qui sont accouplées au couple de lignes communes de transmission de données complémentaires CD0, CD0 par l'intermédiaire des transistors MOSFET Qs, et sont enregistrées dans une cellule de mémoire. Les opérations du circuit amplificateur/tampon de sortie et du tampon d'entrée sont commandées par un signal de commande Øpw produit par

5

20

25

30

le circuit logique LGC. Par exemple, lorsque le signal de commande  $\emptyset_{RW}$  possède un niveau bas, le circuit amplificateur/tampon de sortie agit de manière à produire les données des cellules de mémoire. Dans ce cas, le tampon d'entrée reste inactif. D'autre part, lorsque le signal de commande  $\emptyset_{RW}$  possède le niveau haut, le tampon d'entrée agit de manière à enregistrer les données dans les cellules de mémoire. Dans ce cas, le circuit amplificateur/tampon de sortie est rendu inactif.

Bien que ceci ne soit pas représenté sur la figure 9, chacune des lignes de transmission de données est équipé d'un transistor MOSFET de précharge qui est construit de la même manière que le transistor MOSFET de précharge mentionné en référence à la figure 1 et qui reçoit un signal de précharge Ø p par l'intermédiaire de sa grille.

Chacune des cellules de mémoire est constituée par un circuit à bascule bistable FF possédant deux bornes d'entrée/sortie, un transistor MOSFET du type à enrichissement à canal n Qa possédant une première électrode d'entrée/sortie raccordée à une borne d'entrée/sortie dudit circuit à bascule bistable et possédant une seconde électrode d'entrée/sortie raccordée à la ligne de transmission de données All(D), et un transistor MOSFET à enrichissement à canal n Qa possédant une première électrode d'entrée/sortie accouplée à l'autre borne d'entrée/sortie dudit circuit à bascule bistable comportant une seconde borne d'entrée/ sortie accouplée à la ligne de transmission de données All (D). Bien que l'invention n'y soit pas spécifiquement limitée, le circuit à bascule bistable est constitué par des transistors MOSFET à canal p  $Q_1$ ,  $Q_2$  et par des transistors MOSFET à canal n  $Q_3$ ,  $Q_4$ , c'est-à-dire que l'on a un circuit à bascule bistable CMOS.

Dans le réseau de mémoire mentionné ci-dessus, les grilles des transistors MOSFET Qa, Qa constituant les cellules de mémoire disposées suivant la même ligne sont accouplées électriquement à la même ligne de transmission de mots. En outre les secondes électrodes d'entrée/sortie des transistors Qa, Qa constituant les cellules de mémoire situées le long de la même colonne sont accouplées à la même ligne de transmission de données.

L'électrode de grille du transistor MOSFET Qa et l'électrode de grille du transistor MOSFET Qa sont accouplées ensemble par l'intermédiaire de la couche de silicium polycristallin électriquement conductrice PSi. Ici, il faut tenir compte du fait que la couche de silicium polycristallin électriquement conductrice PSi n'a pas été accouplée aux électrodes de grille des transistors MOSFET d'autres cellules de mémoire. La couche de silicium polycristallin électriquement conductrice est accouplée à une ligne de transmission de mots correspondante. C'est pourquoi un signal provenant du décodeur d'adresses X X-DCR est transmis à la cellule de mémoire par l'intermédiaire de la ligne de transmission de mots. Lorsque le signal envoyé à la cellule de mémoire est un signal de sélection (par exemple un signal de 5 volts), les transistors MOSFET Qa, Qa constituant la cellule de mémoire sont placés à l'état conducteur, ce qui a pour effet que la donnée est lue hors de la cellule de mémoire ou est enregistrée dans cette dernière.

La mémoire RAM RA de la présente forme de réalisation reçoit et produit les données comportant une pluralité de bits sous la forme d'une unité, comme représenté sur la figure 3. Mais afin de simplifier la description, le circuit de la figure 9 reçoit ou produit les données comportant un bit sous la forme d'une unité. Dans la pratique, le circuit représenté sur la figure 9 est prévu de façon multiple ou en un certain nombre de fois. Le décodeur d'adresses X X-DCR et le décodeur d'adresses Y Y-DCR sont cependant utilisés en commun. Mais la présente invention n'est pas censée être limitée à la mémoire RAM(ROM) qui reçoit et produit les données comportant une pluralité de

bits sous la forme d'une unité.

Bien qu'il ne faille voir aucune limitation particulière, les lignes de transmission de mots de cette forme de réalisation sont constituées par des secondes couches d'aluminium Al2. En outre, les secondes couches d'aluminium Al2 constituant les lignes de transmission de mots et la couche de silicium polycristallin électriquement conductrice PSi sont accouplées l'une à l'autre par l'intermédiaire des premières couches d'aluminium Al1(C), de la même manière que cela est décrit en référence aux figures 5 à 8. Les lignes de transmission de données sont constituées par des premières couches d'aluminium Al1.

La mémoire RAM représentée sur la figure 9 fonctionne de la même manière que les mémoires RAM statiques 5 très connues, et ne sera pas décrite ici.

Dans le cas où une ligne de transmission de mots est rompue, le signal de sélection n'est pas transmis aux cellules de mémoire qui sont formées sur le côté plus écarté du décodeur d'adresses X X-DCR que la partie rompue, tout comme dans le cas de la mémoire ROM de la figure 4. C'est pourquoi les données mémorisées dans ces cellules de mémoire ne sont pas lues. Ceci permet de tester aisément les mémoires RAM contenues dans un dispositif à circuits intégrés à grande échelle. En outre, étant donné que les lignes de transmission de mots sont constituées par des couches d'aluminium, la mémoire RAM peut fonctionner à des vitesses élevées.

La figure 10 est une vue en plan illustrant une partie principale de la mémoire RAM de la figure 9.

30

En effet, la figure 10 est une vue en plan du réseau de mémoire constitué par des couples de lignes de transmission de données complémentaires  $\mathcal{A}(1)$  (D5),  $\mathcal{A}(1)$  (D6),  $\mathcal{A}(1)$  (D6), par des lignes de transmission de mots  $\mathcal{A}(1)$  (W5) à  $\mathcal{A}(1)$  (W7), et par des cellules de mémoire prévues au niveau des points d'intersection des couples de lignes de

transmission de données AL1(D5),  $AL1(\bar{D}5)$ , AL1(D6),  $AL1(\bar{D}6)$ , et de lignes de transmission de mots AL2(W5) à AL2(D7).

Sur la figure 10, les mêmes parties que celles représentées sur les figures 5 à 9 sont désignées 5 par les mêmes symbôles. En effet, la partie entourée par une ligne en traits mixtes interrompue par des ensembles de quatre points est un substrat en silicium de type n Sub et les régions entourées par des lignes en traits mixtes incluant les ensembles de trois points sont des régions de puits de type p Puits formées sur une surface principale du substrat en silicium de type n Sub. Les régions entourées par des lignes interrompues sont des régions semiconductrices de type p<sup>+</sup> formées sur la surface principale du substrat en silicium de type n Sub ou bien sont des régions semiconductrices de type n formées dans les régions de puits de type p Puits. Les régions entourées par des lignes formées de traits et de points alternés représentent des couches de silicium polycristallin électriquement conductrices PSi, PSii formées à la surface d'une pellicule isolante qui est formée sur la surface principale du substrat Sub ou sur les régions de puits Puits. Les régions entourées par les lignes en traits mixtes suivant des ensembles de deux tirets représentent des premières couches d'aluminium All(C), All (D5),  $All(\bar{D}5)$ , All(D6),  $All(\bar{D}6)$  formées sur la surface d'une pellicule isolante qui est formée sur les couches de silicium polycristallin électriquement conductrices PSi, PSii. Les régions entourées par les lignes en trait plein représentent les secondes couches d'aluminium Al (W5) à Al2(W7) formées sur la surface d'une pellicule isolante qui 30 est formée sur les premières couches d'aluminium.

Sur la figure 10, le symbole Cl désigne des trous de contact formés dans la pellicule isolante 3 en vue d'accoupler les régions semiconductrices du type p<sup>+</sup> ou du type n<sup>+</sup> et les premières couches d'aluminium Al les unes aux autres comme les trous de contact Cl représentés sur la

5

10

25

30

35

figure 7, et ce moyennant l'interposition de la pellicule isolante 3. Le symbole C2 désigne des trous de contact formés dans la pellicule isolante 3 et permettant d'accoupler les couches de silicium polycristallin électriquement conductrices PSi, PSii et les premières couches d'aluminium AL1 ensemble, tout comme les trous de contact C2 de la fiqure 8, avec interposition de la pellicule isolante 3, et le symbole C3 désigne les trous de contact formés dans une pellicule isolante 4 de manière à accoupler les premières couches d'aluminium AL1 et les secondes couches d'aluminium AL2 ensemble, tout comme les trous de contact C3 représentés sur la figure 8, moyennant l'interposition de la pellicule isolante 4.

De même, dans cette forme de réalisation,

on utilise des premières couches d'aluminium All(C) pour

accoupler les secondes couches d'aluminium All(Wn) constituant les lignes de transmission de mots et les couches de

silicium polycristallin électriquement conductrices PSi ensemble, tout comme dans le cas de la forme de réalisation

décrite en liaison avec la figure 5.

Les couches de silicium polycristallin électriquement conductrices PSi constituent des électrodes de grille des transistors MOSFET Qa,  $\bar{\mathbb{Q}}$ a et les couches de câblage, qui accouplent ces électrodes de grille aux lignes de transmission de mots (secondes couches d'aluminium) Al2(Wn). Les couches de silicium polycristallin électriquement conductrices PSi constituent des électrodes de grille des transistors MOSFET  $\mathbb{Q}_1$  à  $\mathbb{Q}_4$  et les couches de câblage servant à former des circuits à bascule bistable.

Sur la figure 10 les régions de source des transistors MOSFET à canal p Q<sub>1</sub>, Q<sub>2</sub> sont constituées par des régions conductrices de type p<sup>+</sup> V<sub>DD</sub>. Les régions semiconductrices de type p<sup>+</sup> sont accouplées les unes aux autres par l'intermédiaire de secondes couches d'aluminium A2 (non représentées), et une tension V<sub>DD</sub> est appliquée aux régions de

source des transistors MOSFET à canal p individuels par l'intermédiaire des secondes couches d'aluminium AL2. En outre les régions de source des transistors MOSFET à canal n sont constituées par des régions semiconductrices de type n GND qui sont accouplées les unes aux autres par l'intermédiaire par exemple des secondes couches d'aluminium AL2. Le potentiel de masse du circuit est appliqué aux régions de source des transistors MOSFET individuels à canal n par l'intermédiaire des secondes couches d'aluminium AL2.

Une pellicule finale de passivation 5 (non représentée) est formée sur les secondes couches d'aluminium Al2 tout comme dans le cas de la forme de réalisation mentionnée en référence aux figures 5 à 8.

La mémoire RAM conforme à cette forme de réalisation est fabriquée à l'aide du même procédé de fabrication que celui mentionné en référence aux figures 5 à 8, et n'est pas décrite ici.

Pour faciliter la compréhension, on a utilisé les symbôles des transistors MOSFET correspondant de la

figure 9, dans la vue en plan des cellules de mémoire décrite dans le côté supérieure gauche de la figure 10. En outre,

dans la vue en plan des cellules de mémoire décrites sur

le côté inférieur de la figure 10, la seconde couche d'aluminium A2 (W7) et les premières couches d'aluminium A2 (D6),

All (D6) ont été décrite dans un état où elles sont partiellement éliminées.

La figure ll représente une mémoire RAM conforme à une autre forme de réalisation de la présente invention.

Sur la figure 11, les mêmes parties que celles de la figure 9 sont désignées par les mêmes références. La constitution et le fonctionnement de la mémoire RAM de la figure 11 sont approximativement les mêmes que la constitution et le fonctionnement de la mémoire RAM de la figure 9.

35 C'est pourquoi les éléments décrits ci-après sont des diffé-

rences existant entre la mémoire RAM représentée sur la figure ll et la mémoire RAM représentée sur la figure 9, tandis que les éléments semblables ne sont pas mentionnés.

C'est-à-dire que dans la mémoire RAM repré-5 sentée sur la figure 11, un bloc de circuit est constitué par une pluralité (deux dans cette forme de réalisation) de cellules de mémoire qui sont formées le long de la même lique de cellules de mémoire. La couche de silicium polycristallin électriquement conductrice PSi est accouplée aux électrodes de grille du transistor MOSFET Qa, Qq prévu pour 10 la sélection d'adresses dans le même bloc de circuit, mais n'est pas accouplée aux électrodes de grille du transistor MOSFET Qa, Qa servant à la sélection d'adresses et prévu dans d'autres blocs de circuit. La couche de silicium poly-15 cristallin électriquement conductrice PSi est accouplée aux lignes de transmission de mots correspondantes tout comme la couche de silicium polycristallin électriquement conductrice PSi représentée sur la figure 9. En effet, sur la figure 9, un bloc de circuit est constitué par une cellule de 20 mémoire. Mais dans cette forme de réalisation, un bloc de circuit est constitué par une pluralité de cellules de mémoire. Ceci permet de réduire le nombre des trous de contact pour l'accouplement de la seconde couche d'aluminium A2 (Wn) et la couche de silicium polycristallin électriquement con-25 ductrice PSi ensemble. Ceci permet de réduire la limitation basée sur la nombre de trous de contacts ou de surfaces occupés par les trous de contact, lorsque l'on essaie de réduire la taille des cellules de mémoire.

Conformément à la présente invention, comme cela ressort à l'évidence de la description précédente, on obtient les effets qui sont mentionnés ci-après.

30

. 35

Les signaux sont transmis aux blocs de circuit individuels par l'intermédiaire de couches de câblage métallique. C'est-à-dire que les signaux sont transmis aux blocs de circuit avec des temps de retard relativement faibles.

Par conséquent des mémoires, ou les mémoires, qui sont contenues dans un dispositif à circuits intégrés à semiconducteurs, peuvent fonctionner à des vitesses élevées.

Lorsqu'un signal est envoyé par une première couche de câblage à une seconde couche de câblage contenue dans un premier bloc de circuit, le signal est également envoyé essentiellement simultanément depuis la première 10 couche de câblage à une troisième couche de câblage contenue dans un second bloc de circuit. La seconde couche de câblage et la troisième couche de câblage n'ont pas accouplées directement l'une à l'autre. C'est pourquoi, lorsque la première couche de câblage est rompue, le signal est envoyé 15 à la seconde couche de câblage, mais n'est pas envoyé à la troisième couche de câblage. Par conséquent le premier bloc de circuit fonctionne de façon correcte, mais le second bloc de circuit ne fonctionne pas de façon correcte (ou ne fonctionne pas du tout). Par conséquent, une rupture du premier câblage peut être aisément détectée par le test de fonctionnement en courant continu qui a été mentionné précédemment. En d'autres termes, le fait que le premier câblage est rompu ou non peut être détecté par un test simple.

Chacun des blocs de circuit contient des

25 éléments de circuits et des moyens de câblage possédant une

résistivité relativement importante pour le raccordement des

éléments de circuit. Les moyens de câblage possédant une

résistivité relativement importante sont raccordés , en un

emplacement, à une couche de câblage métallique qui réduit

30 le temps de retard de propagation. C'est pourquoi les blocs

de circuit sont alimentés à tous moments par des signaux

prédéterminés par l'intermédiaire de couches de câblage métallique. Si une couche de câblage métallique se rompt, le

signal n'est pas transmis auxblocs de circuit situés sur le

35 côté situé à une distance supérieure à celle de la partie

rompue. C'est pourquoi un défaut présent dans la couche de câblage métallique, qui réduit le temps de retard de propagation, peut être détecté par l'intermédiaire du test de fonctionnement en courant continu. Ce fait permet également de conserver le dispositif à circuits intégrés à semiconducteurs à des vitesses élevés maintenant une possibilité accrue. Les blocs de circuit situés à une distance plus importante que celle à laquelle se situe la partie rompue ne fonctionnent pas correctement (ou ne fonctionnent pas du tout). Par conséquent, les circuits internes faisant partie des circuits intégrés à grande échelle peuvent être évalués d'une manière relativement simple.

La présente invention a été décrite de façon concrète précédemment sur la base d'exemples. Cependant il faut noter que l'invention n'est en aucune manière limitée aux formes de réalisation mentionnées ci-dessus et qu'on peut apporter des modifications de différentes manières sans pour autant sortir du cadre de l'invention.

Dans ce qui précède on a décrit des exemples

dans lesquels l'invention était adaptée à une mémoire ROM

latérale et à une mémoire RAM statique. Suivant l'invention

il n'est pas nécessairement limité à de tels cas et peut

être largement utilisé pour des dispositifs à circuits inté

grés à semiconducteurs qui incluent un réseau de mémoire

(lignes de transmission de mots, lignes de transmission de

données ou lignes de masse du circuit) de différentes mémoi

res ROM programmables ou de différentes mémoires RAM dynami

ques, ou bien qui incluent des circuits dans lesquels un

certain nombre d'éléments de circuit sont raccordés à des

30 câblages relativement longs.

## REVENDICATIONS

- 1. dispositif à circuits intégrés à semiconducteurs, caractérisé en ce qu'il comporte :

- une première couche de câblage (A ),