### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5043357号 (P5043357)

(45) 発行日 平成24年10月10日(2012.10.10)

(24) 登録日 平成24年7月20日(2012.7.20)

| (51) Int.Cl. |         |           | FΙ   |       |      |

|--------------|---------|-----------|------|-------|------|

| HO1L         | 27/10   | (2006.01) | HO1L | 27/10 | 461  |

| HO1L         | 27/112  | (2006.01) | HO1L | 27/10 | 433  |

| HO1L         | 21/8246 | (2006.01) | G11C | 17/00 | 304B |

| G11C         | 17/12   | (2006.01) | G11C | 17/00 | 623Z |

| G11C         | 16/04   | (2006.01) |      |       |      |

請求項の数 7 外国語出願 (全 10 頁)

(21) 出願番号 特願2006-102753 (P2006-102753) (22) 出願日 平成18年4月4日 (2006.4.4) (65) 公開番号 特開2007-116084 (P2007-116084A) (43) 公開日 平成19年5月10日 (2007.5.10) 審査請求日 平成21年3月23日 (2009.3.23) (31) 優先権主張番号 11/252, 461

(32) 優先日 平成17年10月18日 (2005.10.18)

(33) 優先権主張国 米国 (US)

||(73)特許権者 506114322

キロパス・テクノロジー・インコーポレー

テッド

アメリカ合衆国、カリフォルニア州 95 054、サンタ・クララ、オクタビアス・

ドライブ 3333

||(74)代理人 100088683

弁理士 中村 誠

||(74)代理人 100108855

弁理士 蔵田 昌俊

|(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】 プログラム可能メモリセル

### (57)【特許請求の範囲】

### 【請求項1】

カラムビット線およびロウワード線を有するメモリアレイ中で用いられるように形成されたプログラム可能メモリセルであって、

ゲートをプログラムワード線と接続された降伏トランジスタと、

前記降伏トランジスタとセンスノードで直列に接続され、ゲートを書き込みワード線と接続された書き込みトランジスタと、

ゲートを前記センスノードと接続された第1センストランジスタと、

前記第1センストランジスタと直列に接続され、ゲートを読み出しワード線と接続され、ソースとカラムビット線と接続された第2センストランジスタと、

を具備する、プログラム可能メモリセル。

## 【請求項2】

前記書き込みトランジスタがソースをカラムソース線と接続されている、請求項 1 の $\underline{\mathcal{J}}$  ログラム可能メモリセル。

#### 【請求項3】

前記第1センストランジスタがソースをカラムソース線と接続されている、請求項2の プログラム可能メモリセル。

## 【請求項4】

前記第1センストランジスタのドレインが前記第2センストランジスタのソースと接続されている、請求項1のプログラム可能メモリセル。

#### 【請求項5】

前記降伏トランジスタが、MOSキャパシタまたはポリシリコン・酸化物・半導体キャパシタで置換され、前記プログラムワード線が前記キャパシタのポリシリコンまたは金属層と接続されている、請求項1のプログラム可能メモリセル。

### 【請求項6】

前記メモリセルが、前記プログラムワード線にプログラム電圧VPPを印加し且つ前記書き込みトランジスタをオンさせてプログラム電流を前記降伏トランジスタを介してカラムソース線上へと流すことによってプログラムされる、請求項1の<u>プログラム可能</u>メモリセル。

### 【請求項7】

前記メモリセルが、前記書き込みトランジスタをオフし、読み出し電圧VRDを前記プログラムワード線上へと印加し、VDDを前記第2センストランジスタのゲートに印加することによって読み出され、

前記カラムビット線が、前記メモリセルがプログラムされているときに減少する電圧を有し、前記メモリセルがプログラムされていないときに不変の電圧を有する、請求項 1 のプログラム可能メモリセル。

【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は、不揮発性プログラム可能半導体メモリに関し、より詳しくは、CMOSロジックプロセスを用いて製造される3.5トランジスタメモリセルに関する。

#### 【背景技術】

# [0002]

不揮発性メモリは、電源が取り去られたとき、保存されていたデータを保持する。このことは、電子機器の多くの異なるタイプにおいて望ましい。フラッシュメモリおよびヒューズに基づいたメモリが、不揮発性メモリの2つのタイプである。しかしながら、不揮発性メモリセルは、典型的に、CMOSロジックプロセスと両立できない、特化された製造プロセスを必要とする。

#### [0003]

不揮発性メモリを製造するために用いられる様々なプロセスの進歩は、先進のCMOSロジックプロセスのような広く用いられているプロセスの進歩に遅れを取る傾向がある。例えば、フラッシュEEPROMデバイスのようなデバイス用のプロセスは、標準的な先進のCMOSロジックプロセスより多くのマスクステップを用いて、このようなデバイスで典型的に見られる高電圧生成回路、トリプルウェル、フローティングゲート、ONO膜、特別なソースおよびドレイン接合のために要求される様々な特別な領域および構造を作製する。したがって、フラッシュデバイス用のプロセスは、標準的な先進のCMOSロジックプロセスに、1乃至2世代遅れを取る傾向がある。他の例として、アンチヒューズ用のプロセスは、様々なアンチヒューズ構造の製造に適していなければならず、標準的な先進のCMOSプロセスに1世代ほど遅れている。

## [0004]

上記のような所見は、概して、従来のメモリ技術ののそれぞれについての欠点が依然と して存在することを示している。

【発明を実施するための最良の形態】

## [0005]

以下の記載において、多くの具体的な詳細が、本発明の実施形態の十分な理解を提供するために提供される。しかしながら、当業者は、本発明が、1つ以上の具体的な細部を用いずに、または他の方法、要素、材料等を用いて、実施可能であることを認識するであろう。他の例では、公知の構造、材料、または動作は、本発明の側面を不明確にすることを避けるために、細かく示された記載されたりしない。

### [0006]

50

10

20

30

10

20

30

40

50

本明細書を通じての、「1つの実施形態」または「ある実施形態」という言及は、実施形態との関連で記載された具体的な特徴、構造、または特性が、本発明の少なくとも1つの実施形態に含まれることを意味している。したがって、本明細書を通じて様々な個所における「1つの実施形態において」または「ある実施形態において」という文言の登場は、必ずしも全てが同じ実施形態を指していない。さらに、具体的な特徴、構造、または特性は、1つ以上の実施形態において適当な手法で組合され得る。

#### [0007]

本発明は、本発明と同じ譲受人によって開発された、ゲート酸化物降伏に基づいた不揮発性メモリ設計の他のタイプに関する。例が、米国特許番号6,940,751、6,777,757および6,697,902に示されている。これらの特許に記載されているゲート酸化物降伏構造は、下記のトランジスタ要素の降伏に、1つの例として、用いられる。

#### [0008]

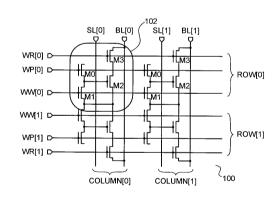

図1は、本発明に従って形成されたメモリアレイ100の例を示している。メモリアレイ100は、2列(カラム)×2行(ロウ)であるが、このアレイは任意の大きさであってよいことが理解されことができる。メモリアレイ100は、4つのメモリセル102を含む。メモリセルの各行は、3つの接続線、読み出しワード線WR、プログラムワード線WP、書き込みワード線WWを有する。メモリセルの各行は、2つの接続線、すなわちカラム接続線SL、カラムビット線BLを有する。

### [0009]

図2を参照して、各メモリセル102は、降伏(breakdown)トランジスタM0、書き込みトランジスタM1、第1センストランジスタM2、第2センスM3を含んでいる。降伏トランジスタM0は、ゲート酸化物の降伏によって「プログラムされる」素子である「ハーフ」トランジスタである。別の実施形態では、ハーフトランジスタは、MOSキャパシタ(またはポリシリコン・酸化物・半導体キャパシタ)またはフローティングソースを有する完全なトランジスタによっても置き換えられ得ることが理解されることができる。したがって、本明細書および特許請求の範囲で用いられる「降伏トランジスタ」という文言は、ゲート酸化物の降伏を用いてプログラムされるデバイスを指す。プログラムされる素子は、ゲート酸化物に対する降伏を用いてプログラムされるべきである。

### [0010]

降伏トランジスタM0を図1のメモリアレイ100におけるデータ記憶素子として用いることは有用である。なぜなら、このトランジスタが、1回のみのポリシリコン堆積ステップを用いてこれらに対するいかなるマスクステップを付加することなく多くの従来のCMOSプロセスを用いて製造されることができるからである。このことは、少なくとも2つのポリシリコン層を要する「フローティングゲート」型フラッシュメモリと対照的である。さらに、現代の技術の進展によって、トランジスタの大きさは非常に小さくされ得る。例えば、現在の0.13ミクロン、0.09ミクロン、これ以下の線幅のプロセスが、集積度を大きく増加させるであろう。

### [0011]

$2 \times 2$ のメモリアレイ 1 0 0 が示されているが、このようなメモリアレイは、例えば先進の 0 . 0 9  $\mu$  m C M O S D ジックプロセスを用いて製造した場合、実際には、およそ 3 2 k ビットから約 1 G ビット、またはこれ以上のメモリセルを含んでいる。より大きなメモリさえも、 C M O S D ジックプロセスがさらに進歩するに連れて、実現されるであろう。メモリアレイ 1 0 0 は、実際には、バイトおよびページおよび冗長ロウ(図示せぬ)へと編成され、これは、あらゆる所望の方法でなされ得る。多くの適当なメモリ編成が公知である。

## [0012]

図2に示されるように、書き込みトランジスタM1は、降伏トランジスタM0と直列に接続される。降伏トランジスタM0は、ゲートをプログラムワード線WPと接続される。書き込みトランジスタM1のゲートは、書き込みワード線WWと接続される。書き込みトランジスタ

10

20

30

M1のドレインは、カラムソース線SLと接続される。

## [0013]

降伏トランジスタM 0 と書き込みトランジスタM 1 との間のセンスノード S N は、センストランジスタM 2 のゲートと接続される。第 1 センストランジスタM 2 のソースはカラムソース線 S L と接続され、第 1 センストランジスタM 2 のドレインはM 2 とM 3 が直列になるように第 2 センストランジスタM 3 と接続される。第 2 センストランジスタM 3 のドレインはカラムビット線 B L と接続される。

## [0014]

メモリセル102をプログラムするために、カラム信号線SLはローにされる。プログラミングパルス(高電圧VPP)がプログラムワード線WPに印加される。さらに、書き込みトランジスタM1も、書き込みワード線WWを、一実施形態では、約VPP/2へとバイアスすることによってオンされる。このことは、降伏トランジスタM0のゲート酸化物の降伏を起こし、導電経路を形成する。プログラムすることは、VPPプログラミングパルスの振幅および幅によっても制御され得る。さらに、降伏トランジスタM0を流れるプログラミング電流の量は、カラム信号線SL上の電流ドライバトランジスタ(図示せぬ)によって制御され得る。なお、読み出しワード線WRはプログラム動作の間、0Vである。

### [0015]

以下の表 1 から分かるように、各信号線は、プログラムされている降伏トランジスタを 除いてどのトランジスタも端子間にVPP/ 2 を越える電圧がないようにバイアスされる

### [0016]

次に、読み出し動作が記載される。図1中の座標(0,0)のメモリセルが読み出されるとする。カラムビット線BLがVDDへとプリチャージされる。読み出し動作の間、読み出されるメモリセルの書き込みワード線WWは、0ボルトに維持される。読み出されるメモリセルのプログラムワード線WPはVRDである。読み出し動作の間、読み出されるメモリセルの読み出しワード線WRはVDDへとバイアスされる。

### [0017]

座標(0,0)の読み出されるメモリセルがプログラムされている場合、ストレージノードSNは、第1センストランジスタM2をオンさせるに足る高さの値まで上昇する。この場合、カラムビット線BLは、センストランジスタM3、M2を介して放電される。次いで、センスアンプ(図示せぬ)は、読み出しメモリセルのカラムビット線BL上の電圧が所定の参照電圧未満まで低下した時に信号を出力する。

## [0018]

しかしながら、メモリセルがプログラムされていない場合、ノードSNは、0ボルト近傍を維持する。従って、第2センストランジスタM3がオンしたとしても、第1センストランジスタM2はオフを維持し、このため、カラムビット線BL上の電荷は保持される。

#### [0019]

読み出されていないセル(非選択のカラムおよびロウ)については、電圧は、下記の表 40 1のように供給される。

## 【表1】

## 表 1

| ロウバイアス |           | 選択ロウ <i>(ROW[0])</i> |         | 非選択ロウ <i>(ROW[1])</i> |         |

|--------|-----------|----------------------|---------|-----------------------|---------|

| 信号     | 記述        | PGM M0               | READ M0 | PGM M0                | READ M0 |

| WP     | プログラムワード線 | VPP                  | VRD     | VPP/2                 | VRD     |

| ww     | 書き込みワード線  | VPP/2                | 0V      | VPP/2                 | 0V      |

| WR     | 読み出しワード線  | VO                   | VDD     | VDD                   | 0V      |

選択カラム

RD M0

0V

VDD (Pre-Q)

VDD

(COLUMN[0])

**PGM MO**

0V

**VDD**

非選択カラム (COLUMN[1]) PGM M0 RD M0 VPP/2 0V

**VDD**

20

30

10

## [0020]

信号

SL

BL

カラムバイアス

記述

ソース線

ビット線

概して、第1センストランジスタM2は、降伏トランジスタM0のプログラムされた抵抗が第1センストランジスタM2のゲートを素早く駆動できるように、小さい。

## [0021]

印加される電圧の正確な大きさは、ゲート酸化物の厚さおよび他の要因に依存する。したがって、例えば、0.09ミクロンのCMOSプロセスについては、ゲート酸化物は、 典型的にはより薄く、必要とするプログラム電圧はより少ない。

[0022]

さらに、トランジスタのサイズのも設計の考慮事項の要求によって変化し得る。一実施 形態では、 0 . 1 3 ミクロンの C M O S ロジックプロセスでは、トランジスタは以下のW / L 比を有し得る。

#### 【表2】

## 表 2

| トランジスタ | 「中国(中国) | 長さ(ミクロン) |

|--------|---------|----------|

| МО     | 0.32    | 0.24     |

| M1     | 0.32    | 0.18     |

| M2     | 0.3     | 0.13     |

| МЗ     | 0.3     | 0.13     |

10

#### [0023]

さらに、他の大きさおよび比が用いられ得、これらは本発明の思想および範疇内にあることが理解されることができる。

20

30

40

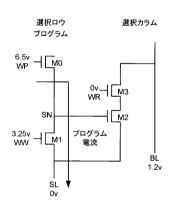

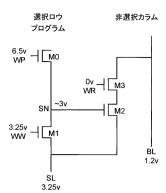

## [0024]

一実施形態では、様々の電圧が図3において見られる。図3は、メモリセルのプログラム動作を示している。示されるように、この実施形態でのVPPは、6.5ボルトであり、VDDは1.2ボルトである。考慮事項の1つは、プログラムされたハーフトランジスタ(M0)により生じる抵抗と、デバイスB(M1)によるインピーダンスは、ノードSN上の信号がVPP/2を越えないような比となるべきことである。

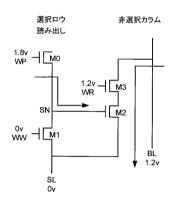

#### [0025]

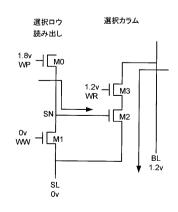

図4に移って、選択口ウと選択カラムでのメモリセルについての読み出し電圧が示される。書き込みワード線にはゼロボルトが印加される。1.8 ボルトの読み出し電圧VRDがプログラムワード線に印加され、1.2 ボルトが読み出しワード線とカラムビット線に印加される。カラムソース線はこの実施形態では、ゼロボルトに維持される。これらの電圧バイアスの下で、メモリセルがプログラムされていた場合、電荷が降伏トランジスタM0を介してセンスノードSN上へと流れる。これにより、カラムビット線上の電荷が、第1センストランジスタM2および第2センストランジスタM3を経由してカラムソース線上へと移る。カラムビット線上のセンスアンプは、電圧の降下をセンスする。これは、プログラムされたセルであることを示す。セルがプログラムされていない場合、降伏トランジスタM0は電荷をノードSN上に出さないであろうし、カラムビット線は電圧降下しないであろう。

#### [0026]

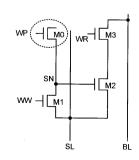

図5に示すように、メモリセルが選択ロウの中であるが非選択カラムの中である場合、プログラム動作の間、非選択カラムソース線は3.25ボルトを供給される。これにより、約3ボルトの電荷がソースノードSN上へと配置され、このことは、ソースノードSNに約3ボルトの電荷を与え、この結果、不十分な電圧が降伏トランジスタに印加されることになり、降伏トランジスタはプログラムされない。

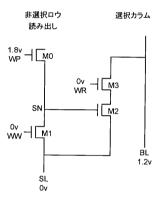

[0027]

図 6 に示すように、選択ロウで非選択カラムの読み出し動作の間、印加電圧とその結果は、メモリセルが選択ロウおよび選択カラムで読み出される場合と同じである。しかしながら、センスアンプはカラムビット線に沿っており、カラムビット線が非選択であるので、これはドントケア(don't care)状態である。

[0028]

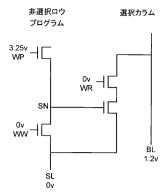

次に、図7に移って、非選択ロウおよび選択カラムでのメモリセルにプログラムするための印加電圧が示される。この状態では、降伏トランジスタM0は、この状況下でプログラムされることはできない。

#### [0029]

次に、図8に移って、非選択口ウおよび選択カラムでのメモリセルの「読み出し」動作中の印加電圧が示される。この状態では、降伏トランジスタM0がプログラムされているか否かは問題ではない。ノードSN上の電圧は、この場合、読み出しワード線が0ボルトに維持されているので何らの影響を持たない。

### [0030]

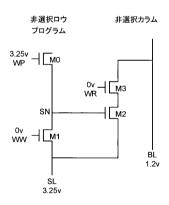

図9に移って、非選択ロウおよび非選択カラムでのメモリセルのプログラムの間、プログラムワード線は3.25ボルトであり、書き込みワード線はゼロボルトである。ノードSNは、降伏トランジスタM0が先にプログラムされていた場合、電位が上昇するが、これは何らの影響を持たない。降伏トランジスタM0がプログラムされていなかった場合、センスノードSNはM1トランジスタ、および可能性として降伏トランジスタを介して電荷を集めるが、これは、読み出しサイクル中に対処される。

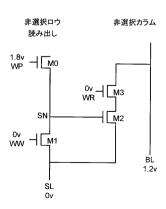

#### [0031]

詳しくは、図10に移って、非選択口ウと非選択メモリセルの読み出しサイクルの間、センスノードSNは、降伏トランジスタM0がプログラムされていれば、電位が上昇する。しかし、このことは、この場合、何らの結果ももたらさない。降伏トランジスタM0がプログラムされていなければ、センスノードSNは、可能性として降伏トランジスタM0を介して幾らかの電荷を受け取るかもしれないが、これは、選択口ウおよび選択カラムの読み出しサイクルにおいて対処される。

#### [0032]

図4に戻って、選択口ウおよび選択カラムの場合、読み出しワード線が論理的に有効とされる前に、書き込みワード線上の信号は、センスノードSN上に位置するあらゆる漏れ電流を除去するように設計された短期間の正のパルスを有し得る。このことは、センスノードSN上のあらゆる浮浪電荷の問題を解消するであろう。降伏トランジスタM0がプログラムされている場合、センスノードは引き下げられ、次いで、プログラムされた降伏トランジスタM0を介して再充電される。これは、典型的には、非常に短い時定数であり、従って、書き込みワード線上の正のパルスは非常に小さくされる。これが実行された後、読み出しワード線が論理的に有効とされる。

## [0033]

本発明および出願の本明細書に述べられたような記載は、例示的であり、本発明の範囲を限定することを意図していない。本明細書に開示された実施形態の変形および改変が可能であり、実施形態の様々の要素に対する実用的な代替物または、これの同等物は、当業者によって知られている。例えば、様々の例において述べられた様々の電圧は単なる例示であり、当業者が正確な電圧に関する思慮を持って電圧の範囲を選択するので、あらゆる事象での電圧はデバイスの特性に依存する。ロウワード線およびカラムビット線という文言は、メモリにおいて一般的に用いられている線の種類を記述するために用いられたが、一部のメモリは、これらに対する代替物を有し得る。さらに、様々のドーピングタイプが、上記のnチャネルトランジスタがpチャネルトランジスタに置換されるというように、反転され得る。本明細書に開示の実施形態の、これらおよび他の変形、改変が、本発明の範囲および思想から逸脱することなくなされ得る。

## 【図面の簡単な説明】

#### [0034]

- 【図1】図1は本発明に従ったメモリアレイの一部の概略的な回路図。

- 【図2】図2は図1に代表されるメモリアレイの一部の部分的なレイアウト図。

- 【図3】図3は選択および非選択セルに対するプログラムおよび読み出し電圧を示す。

- 【図4】図4は選択および非選択セルに対するプログラムおよび読み出し電圧を示す。

- 【図5】図5は選択および非選択セルに対するプログラムおよび読み出し電圧を示す。

10

20

30

40

- 【図6】図6は選択および非選択セルに対するプログラムおよび読み出し電圧を示す。

- 【図7】図7は選択および非選択セルに対するプログラムおよび読み出し電圧を示す。

- 【図8】図8は選択および非選択セルに対するプログラムおよび読み出し電圧を示す。

- 【図9】図9は選択および非選択セルに対するプログラムおよび読み出し電圧を示す。

- 【図10】図10は選択および非選択セルに対するプログラムおよび読み出し電圧を示す

0

## 【図1】 【図3】

【図2】 【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

#### フロントページの続き

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100092196

弁理士 橋本 良郎

(74)代理人 100100952

弁理士 風間 鉄也

(72)発明者 ジョン・エム・カラハン

アメリカ合衆国、カリフォルニア州 94583、サン・ラモン、アルコスタ・ブールバード 9610

(72)発明者 ヘマンシュ・ティー・バーネンカー

アメリカ合衆国、カリフォルニア州 95054、サンタ・クララ、パークビュー・ドライブ 6 30、アパートメント 114

(72)発明者 マイケル・ディー・フリースラー

アメリカ合衆国、カリフォルニア州 95062、サンタ・クラッツ、ハーバー・ドライブ 40。

(72)発明者 グレン・エー・ローゼンデール

アメリカ合衆国、カリフォルニア州 94301、パロ・アルト、フォレスト・アベニュー 68

(72)発明者 ハリー・エス・ルアン

アメリカ合衆国、カリフォルニア州 95070、サラトガ、カントリー・スクワイアー・レーン 12140

(72)発明者 ツォンシャン・リウ

アメリカ合衆国、テキサス州 75025、プラノ、ハニング・ドライブ 8125

#### 審査官 宮部 裕一

(56)参考文献 特開2005-269616(JP,A)

米国特許第06671040(US, B1)

特開平03-290900(JP,A)

米国特許出願公開第2003/0198085(US,A1)

特表2005-504434(JP,A)

米国特許第06243294(US,B1)

(58)調査した分野(Int.CI., DB名)

H01L 27/10

G11C 16/04

G11C 17/12

H01L 21/8246

H01L 27/112