# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 114978182 A (43) 申请公布日 2022. 08. 30

(21) 申请号 202210539431.X

(22)申请日 2022.05.17

(71) 申请人 芯海科技(深圳)股份有限公司 地址 518000 广东省深圳市南山区粤海街 道高新区社区科苑大道深圳湾创新科 技中心1栋301

(72) 发明人 刘维辉 陈敏

(74) 专利代理机构 深圳紫藤知识产权代理有限 公司 44570

专利代理师 徐世俊

(51) Int.CI.

HO3M 1/12 (2006.01)

**HO3M** 1/38 (2006.01)

H03F 1/02 (2006.01)

HO3F 3/68 (2006.01)

权利要求书5页 说明书16页 附图8页

#### (54) 发明名称

模数转换器、芯片及模数转换控制方法

#### (57) 摘要

本申请实施例提供一种模数转换器、芯片以及模数转换控制方法,模数转换器包括多级模数转换电路,任一相邻的两级模数转换电路之间设置有级间放大器,级间放大器包括至少两个放大器,至少两个放大器被配置为进行信号放大。本申请实施例提供的模数转换器中,将级间放大器设置为包括至少两个放大器,两个放大器的功耗都能够降低,因此相对于单个级间放大器而言,能够降低模数转换器的功耗。

- 1.一种模数转换器,其特征在于,包括多级模数转换电路,任一相邻的两级模数转换电路之间设置有级间放大器,所述级间放大器包括至少两个放大器,所述至少两个放大器被配置为进行信号放大。

- 2.根据权利要求1所述的模数转换器,其特征在于,所述多级模数转换电路包括第一级模数转换电路和第二级模数转换电路,所述第一级模数转换电路与所述第二级模数转换电路之间设置有所述级间放大器,所述级间放大器包括第一级放大器和第二级放大器,其中:

所述第一级模数转换电路,被配置为采样输入信号,并对所述输入信号进行模数转换, 以得到第一数字信号和残余电压信号;

所述第一级放大器,与所述第一级模数转换电路连接,被配置为对所述残余电压信号进行放大,得到并输出第一放大信号;

所述第二级放大器,与所述第一级放大器连接,被配置为对所述第一放大信号进行采 样和放大,得到并输出第二放大信号;

所述第二级模数转换电路,与所述第二级放大器连接,被配置为对所述第二放大信号 进行采样以及模数转换,并输出第二数字信号:

所述模数转换器被配置为根据所述第一数字信号和所述第二数字信号得到对所述输 入信号的模数转换结果。

- 3.根据权利要求2所述的模数转换器,其特征在于,所述第一级放大器为无源放大器。

- 4.根据权利要求2所述的模数转换器,其特征在于,所述第一级放大器为有源放大器。

- 5.根据权利要求4所述的模数转换器,其特征在于,所述输入信号为单端信号,所述第一级放大器包括第一放大器、第一电容和第一开关;

所述第一放大器的第一输入端与所述第一级模数转换电路连接,所述第一放大器的第二输入端连接到共模节点,所述第一放大器的输出端与所述第二级放大器连接;

所述第一电容的第一端与所述第一放大器的第一输入端连接,所述第一电容的第二端与所述第一放大器的输出端连接;

所述第一开关的第一端与所述第一放大器的第一输入端连接,所述第一开关的第二端与所述第一放大器的输出端连接;

其中,所述第一放大器的输出端用于输出所述第一放大信号。

- 6.根据权利要求5所述的模数转换器,其特征在于,所述第一级放大器还包括第二开关,所述第一放大器的第一输入端通过所述第二开关与所述第一级模数转换电路连接。

- 7.根据权利要求4所述的模数转换器,其特征在于,所述输入信号为差分信号,所述第一级模数转换电路包括第一输出端、第二输出端,所述第二级放大器包括第一输入端和第二输入端,所述第一级放大器包括第一放大器、第一电容、第二电容、第一开关和第三开关;

所述第一放大器的第一输入端与所述第一级模数转换电路的第一输出端连接,所述第一放大器的第二输入端与所述第一级模数转换电路的第二输出端连接,所述第一放大器的第一电源端与所述第二级放大器的第一输入端连接,所述第一放大器的第二电源端与所述第二级放大器的第二输入端连接;

所述第一电容的第一端与所述第一放大器的第一输入端连接,所述第一电容的第二端与所述第一放大器的第一电源端连接;

所述第一开关的第一端与所述第一放大器的第一输入端连接,所述第一开关的第二端

与所述第一放大器的第一电源端连接;

所述第二电容的第一端与所述第一放大器的第二输入端连接,所述第二电容的第二端与所述第一放大器的第二电源端连接;

所述第三开关的第一端与所述第一放大器的第二输入端连接,所述第三开关的第二端与所述第一放大器的第二电源端连接:

其中,所述第一放大器的第一电源端、第二电源端用于输出所述第一放大信号。

- 8.根据权利要求7所述的模数转换器,其特征在于,所述第一级放大器还包括第二开关和第四开关,所述第一放大器的第一输入端通过所述第二开关与所述第一级模数转换电路的第一输出端连接,所述第一放大器的第二输入端通过所述第四开关与所述第一级模数转换电路的第二输出端连接。

- 9.根据权利要求2所述的模数转换器,其特征在于,所述第二级放大器为无源放大器。

- 10.根据权利要求9所述的模数转换器,其特征在于,所述输入信号为单端信号,所述第二级放大器包括第三电容、第四电容、第六开关和第七开关;

所述第三电容的第一端与所述第一级放大器连接,并通过所述第六开关接地;所述第三电容的第二端与所述第四电容的第一端连接,并且所述第三电容的第二端与所述第四电容的第一端之间通过所述第七开关连接到共模节点;所述第四电容的第二端与所述第二级模数转换电路连接;

其中,所述第四电容的第二端用于输出所述第二放大信号。

- 11.根据权利要求10所述的模数转换器,其特征在于,所述第二级放大器还包括第五开关,所述第三电容的第一端通过所述第五开关与所述第一级放大器连接。

- 12.根据权利要求9所述的模数转换器,其特征在于,所述输入信号为差分信号,所述第一级放大器包括第三输出端、第四输出端,所述第二级模数转换电路包括第三输入端、第四输入端,所述第二级放大器包括第三电容、第四电容、第五电容、第六电容、第六开关、第七开关、第九开关和第十开关;

所述第三电容的第一端与所述第一级放大器的第三输出端连接,并通过所述第六开关接地;所述第三电容的第二端与所述第四电容的第一端连接,所述第三电容的第二端与所述第四电容的第一端之间通过所述第七开关连接到共模节点;所述第四电容的第二端与所述第二级模数转换电路的第三输入端连接;

所述第五电容的第一端与所述第一级放大器的第四输出端连接,并通过所述第九开关接地;所述第五电容的第二端与所述第六电容的第一端连接,所述第五电容的第二端与所述第六电容的第一端之间通过所述第十开关连接到共模节点;所述第六电容的第二端与所述第二级模数转换电路的第四输入端连接;

其中,所述第四电容的第二端、所述第六电容的第二端用于输出所述第二放大信号。

- 13.根据权利要求12所述的模数转换器,其特征在于,所述第二级放大器还包括第五开关和第八开关,所述第三电容的第一端通过所述第五开关与所述第一级放大器的第三输出端连接,所述第五电容的第一端通过所述第八开关与所述第一级放大器的第四输出端连接。

- 14.根据权利要求2所述的模数转换器,其特征在于,所述第二级放大器为有源放大器。

- 15.根据权利要求14所述的模数转换器,其特征在于,所述输入信号为单端信号,所述

第二级放大器包括第三电容、第四电容、第二放大器、第六开关和第十一开关;

所述第三电容的第一端与所述第一级放大器连接,并通过所述第六开关接地;所述第 三电容的第二端与所述第四电容的第一端连接,所述第四电容的第二端与所述第二级模数 转换电路连接;

所述第二放大器的第一输入端连接到所述第三电容的第二端与所述第四电容的第一端之间,所述第二放大器的第二输入端连接到共模节点,所述第二放大器的输出端与所述 第四电容的第二端连接;

所述第十一开关的第一端连接到所述第三电容的第二端与所述第四电容的第一端之间,所述第十一开关的第二端与所述第四电容的第二端连接;

其中,所述第二放大器的输出端用于输出第二放大信号。

16.根据权利要求15所述的模数转换器,其特征在于,所述第二级放大器还包括第五开关,所述第三电容的第一端通过所述第五开关与所述第一级放大器连接。

17.根据权利要求14所述的模数转换器,其特征在于,所述输入信号为差分信号,所述 第一级放大器包括第三输出端、第四输出端,所述第二级模数转换电路包括第三输入端、第 四输入端,所述第二级放大器包括第三电容、第四电容、第五电容、第六电容、第二放大器、 第六开关、第九开关、第十一开关和第十二开关;

所述第三电容的第一端与所述第一级放大器的第三输出端连接,并通过所述第六开关接地;所述第三电容的第二端与所述第四电容的第一端连接,所述第四电容的第二端与所述第二级模数转换电路的第三输入端连接;所述第十一开关的第一端连接到所述第三电容的第二端与所述第四电容的第一端之间,所述第十一开关的第二端与所述第四电容的第二端连接;

所述第五电容的第一端与所述第一级放大器的第四输出端连接,并通过所述第九开关接地;所述第五电容的第二端与所述第六电容的第一端连接,所述第六电容的第二端与所述第二级模数转换电路的第四输入端连接;所述第十二开关的第一端连接到所述第五电容的第二端与所述第六电容的第一端之间,所述第十二开关的第二端与所述第六电容的第二端连接;

所述第二放大器的第一输入端连接到所述第三电容的第二端与所述第四电容的第一端之间,所述第二放大器的第二输入端连接到所述第五电容的第二端与所述第六电容的第一端之间,所述第二放大器的第一电源端与所述第四电容的第二端连接,所述第二放大器的第二电源端与所述第六电容的第二端连接;

其中,所述第二放大器的第一电源端、第二电源端用于输出第二放大信号。

- 18.根据权利要求17所述的模数转换器,其特征在于,所述第二级放大器还包括第五开关和第八开关,所述第三电容的第一端通过所述第五开关与所述第一级放大器的第三输出端连接,所述第五电容的第一端通过所述第八开关与所述第一级放大器的第四输出端连接。

- 19.根据权利要求2至18任一项所述的模数转换器,其特征在于,所述第一级模数转换电路包括:

第一电容阵列,被配置为对输入信号进行采样并输出残余电压信号,所述第一级放大器与所述第一电容阵列连接;

第一比较器,与所述第一电容阵列连接,被配置为对所述残余电压信号进行比较,并输出第一比较结果;以及

第一逻辑控制电路,与所述第一电容阵列、所述第一比较器连接,被配置为基于所述第一比较结果对所述第一电容阵列进行逻辑控制以及输出第一数字信号。

20.根据权利要求2至18任一项所述的模数转换器,其特征在于,所述第二级模数转换电路包括:

第二电容阵列,与所述第二级放大器连接,被配置为对所述第二放大信号进行采样;

第二比较器,与所述第二电容阵列连接,被配置为对所述第二放大信号进行比较,并输出第二比较结果;以及

第二逻辑控制电路,与所述第二电容阵列、所述第二比较器连接,被配置为基于所述第二比较结果对所述第二电容阵列进行逻辑控制以及输出第二数字信号。

21.根据权利要求2至18任一项所述的模数转换器,其特征在于,还包括:

输出电路,与所述第一级模数转换电路、所述第二级模数转换电路连接,被配置为根据 所述第一数字信号和所述第二数字信号得到对所述输入信号的模数转换结果。

- 22.一种芯片,其特征在于,包括权利要求1至21任一项所述的模数转换器。

- 23.一种模数转换控制方法,其特征在于,包括:

在模数转换器的至少一组相邻的两级模数转换电路之间设置级间放大器,所述级间放大器包括至少两个放大器,所述至少两个放大器被配置为进行信号放大。

24.根据权利要求23所述的模数转换控制方法,其特征在于,所述相邻的两级模数转换 电路包括第一级模数转换电路和第二级模数转换电路,所述至少两个放大器包括第一级放 大器和第二级放大器,所述模数转换控制方法还包括:

控制第一级模数转换电路采样输入信号,对所述输入信号进行模数转换,以得到第一数字信号和残余电压信号,并对所述残余电压信号进行保持;

控制第一级放大器对所述残余电压信号进行放大,得到第一放大信号:

控制第二级放大器对所述第一放大信号依次进行采样和放大,得到第二放大信号;

控制第二级模数转换电路对所述第二放大信号依次进行采样和模数转换,得到第二数字信号;以及

根据所述第一数字信号和所述第二数字信号得到对所述输入信号的模数转换结果。

25.根据权利要求24所述的模数转换控制方法,其特征在干:

所述第二级放大器为有源放大器,控制所述第二级模数转换电路对所述第二放大信号 依次进行采样和模数转换时,同步控制所述第一级模数转换电路对所述输入信号进行下一 次的采样和模数转换。

26.根据权利要求24所述的模数转换控制方法,其特征在于:

所述第二级放大器为无源放大器,控制所述第一级模数转换电路对所述残余电压信号进行保持时,同步控制所述第二级模数转换电路对所述第二放大信号进行采样;

控制所述第二级模数转换电路对所述第二放大信号进行模数转换时,同步控制所述第一级模数转换电路对所述输入信号进行下一次的采样和模数转换。

27.根据权利要求24至26任一项所述的模数转换控制方法,其特征在于:

控制所述第一级模数转换电路对所述残余电压信号进行保持时,同步控制所述第一级

放大器对所述残余电压信号进行放大。

28.根据权利要求27所述的模数转换控制方法,其特征在于:

控制所述第一级放大器对所述残余电压信号进行放大时,同步控制所述第二级放大器对所述第一放大信号进行采样。

# 模数转换器、芯片及模数转换控制方法

#### 技术领域

[0001] 本申请涉及电子电路技术领域,特别涉及一种模数转换器、芯片及模数转换控制方法。

## 背景技术

[0002] 流水线逐次逼近型模数转换器 (Pipeline-SAR ADC) 是将流水线模数转换器 (Pipeline ADC) 中的全并行 (Flash) 结构用逐次逼近 (SAR) 结构代替,并利用第一级逐次逼近型模数转换器 (SAR ADC) 的采样保持网络实现传统Pipeline ADC的前端采样保持功能。虽然Pipeline-SAR ADC速度有所降低,但是大大减少了功耗和面积。而限制Pipeline-SAR ADC功耗的主要因素是级间放大器。级间放大器的开环放大倍数由Pipeline-SAR ADC的总分辨率N位 (N-bit) 决定,至少需要20 $\log(2^{N+1})$  dB。而级间放大器的开环带宽由Pipeline-SAR ADC的速度、第二级SAR ADC的分辨率和输出负载决定,至少需要 $(1+2^{M})$   $\ln(2^{-L+1})/(2*\pi*T_{RA})$  Hz (其中M为第一级模数转换器位数,L为第二级模数转换器位数, $T_{RA}$ 为级间放大器的放大时间)。级间放大器的负载为 $2^{-L}$ Cu (其中,Cu表示单位电容大小)。

[0003] 为了使Pipeline-SAR ADC实现如此高的开环放大倍数和开环带宽,级间放大器的功耗会非常高,因此传统Pipeline-SAR ADC的功耗依旧比SAR ADC高很多。

## 发明内容

[0004] 本申请实施例提供一种模数转换器、芯片及模数转换控制方法,可以降低模数转换器的功耗。

[0005] 本申请实施例提供一种模数转换器,包括多级模数转换电路,任一相邻的两级模数转换电路之间设置有级间放大器,所述级间放大器包括至少两个放大器,所述至少两个放大器被配置为进行信号放大。

[0006] 在一些实施例中,所述多级模数转换电路包括第一级模数转换电路和第二级模数转换电路,所述第一级模数转换电路与所述第二级模数转换电路之间设置有所述级间放大器,所述级间放大器包括第一级放大器和第二级放大器,其中:

[0007] 所述第一级模数转换电路,被配置为采样输入信号,并对所述输入信号进行模数转换,以得到第一数字信号和残余电压信号;

[0008] 所述第一级放大器,与所述第一级模数转换电路连接,被配置为对所述残余电压信号进行放大,得到并输出第一放大信号;

[0009] 所述第二级放大器,与所述第一级放大器连接,被配置为对所述第一放大信号进行采样和放大,得到并输出第二放大信号;

[0010] 所述第二级模数转换电路,与所述第二级放大器连接,被配置为对所述第二放大信号进行采样以及模数转换,并输出第二数字信号:

[0011] 所述模数转换器被配置为根据所述第一数字信号和所述第二数字信号得到对所述输入信号的模数转换结果。

[0012] 在一些实施例中,所述第一级放大器为无源放大器。

[0013] 在一些实施例中,所述第一级放大器为有源放大器。

[0014] 在一些实施例中,所述输入信号为单端信号,所述第一级放大器包括第一放大器、第一电容和第一开关;

[0015] 所述第一放大器的第一输入端与所述第一级模数转换电路连接,所述第一放大器的第二输入端连接到共模节点,所述第一放大器的输出端与所述第二级放大器连接;

[0016] 所述第一电容的第一端与所述第一放大器的第一输入端连接,所述第一电容的第二端与所述第一放大器的输出端连接;

[0017] 所述第一开关的第一端与所述第一放大器的第一输入端连接,所述第一开关的第二端与所述第一放大器的输出端连接;

[0018] 其中,所述第一放大器的输出端用于输出所述第一放大信号。

[0019] 在一些实施例中,所述第一级放大器还包括第二开关,所述第一放大器的第一输入端通过所述第二开关与所述第一级模数转换电路连接。

[0020] 在一些实施例中,所述输入信号为差分信号,所述第一级模数转换电路包括第一输出端、第二输出端,所述第二级放大器包括第一输入端和第二输入端,所述第一级放大器包括第一放大器、第一电容、第二电容、第一开关和第三开关;

[0021] 所述第一放大器的第一输入端与所述第一级模数转换电路的第一输出端连接,所述第一放大器的第二输入端与所述第一级模数转换电路的第二输出端连接,所述第一放大器的第一电源端与所述第二级放大器的第一输入端连接,所述第一放大器的第二电源端与所述第二级放大器的第二输入端连接;

[0022] 所述第一电容的第一端与所述第一放大器的第一输入端连接,所述第一电容的第二端与所述第一放大器的第一电源端连接;

[0023] 所述第一开关的第一端与所述第一放大器的第一输入端连接,所述第一开关的第二端与所述第一放大器的第一电源端连接;

[0024] 所述第二电容的第一端与所述第一放大器的第二输入端连接,所述第二电容的第二端与所述第一放大器的第二电源端连接:

[0025] 所述第三开关的第一端与所述第一放大器的第二输入端连接,所述第三开关的第二端与所述第一放大器的第二电源端连接;

[0026] 其中,所述第一放大器的第一电源端、第二电源端用于输出所述第一放大信号。

[0027] 在一些实施例中,所述第一级放大器还包括第二开关和第四开关,所述第一放大器的第一输入端通过所述第二开关与所述第一级模数转换电路的第一输出端连接,所述第一放大器的第二输入端通过所述第四开关与所述第一级模数转换电路的第二输出端连接。

[0028] 在一些实施例中,所述第二级放大器为无源放大器。

[0029] 在一些实施例中,所述输入信号为单端信号,所述第二级放大器包括第三电容、第四电容、第六开关和第七开关;

[0030] 所述第三电容的第一端与所述第一级放大器连接,并通过所述第六开关接地;所述第三电容的第二端与所述第四电容的第一端连接,并且所述第三电容的第二端与所述第四电容的第一端之间通过所述第七开关连接到共模节点;所述第四电容的第二端与所述第二级模数转换电路连接;

[0031] 其中,所述第四电容的第二端用于输出所述第二放大信号。

[0032] 在一些实施例中,所述第二级放大器还包括第五开关,所述第三电容的第一端通过所述第五开关与所述第一级放大器连接。

[0033] 在一些实施例中,所述输入信号为差分信号,所述第一级放大器包括第三输出端、 第四输出端,所述第二级模数转换电路包括第三输入端、第四输入端,所述第二级放大器包 括第三电容、第四电容、第五电容、第六电容、第六开关、第七开关、第九开关和第十开关;

[0034] 所述第三电容的第一端与所述第一级放大器的第三输出端连接,并通过所述第六 开关接地;所述第三电容的第二端与所述第四电容的第一端连接,所述第三电容的第二端 与所述第四电容的第一端之间通过所述第七开关连接到共模节点;所述第四电容的第二端 与所述第二级模数转换电路的第三输入端连接;

[0035] 所述第五电容的第一端与所述第一级放大器的第四输出端连接,并通过所述第九 开关接地;所述第五电容的第二端与所述第六电容的第一端连接,所述第五电容的第二端 与所述第六电容的第一端之间通过所述第十开关连接到共模节点;所述第六电容的第二端 与所述第二级模数转换电路的第四输入端连接;

[0036] 其中,所述第四电容的第二端、所述第六电容的第二端用于输出所述第二放大信号。

[0037] 在一些实施例中,所述第二级放大器还包括第五开关和第八开关,所述第三电容的第一端通过所述第五开关与所述第一级放大器的第三输出端连接,所述第五电容的第一端通过所述第八开关与所述第一级放大器的第四输出端连接。

[0038] 在一些实施例中,所述第二级放大器为有源放大器。

[0039] 在一些实施例中,所述输入信号为单端信号,所述第二级放大器包括第三电容、第四电容、第二放大器、第六开关和第十一开关;

[0040] 所述第三电容的第一端与所述第一级放大器连接,并通过所述第六开关接地;所述第三电容的第二端与所述第四电容的第一端连接,所述第四电容的第二端与所述第二级模数转换电路连接;

[0041] 所述第二放大器的第一输入端连接到所述第三电容的第二端与所述第四电容的第一端之间,所述第二放大器的第二输入端连接到共模节点,所述第二放大器的输出端与所述第四电容的第二端连接:

[0042] 所述第十一开关的第一端连接到所述第三电容的第二端与所述第四电容的第一端之间,所述第十一开关的第二端与所述第四电容的第二端连接;

[0043] 其中,所述第二放大器的输出端用于输出第二放大信号。

[0044] 在一些实施例中,所述第二级放大器还包括第五开关,所述第三电容的第一端通过所述第五开关与所述第一级放大器连接。

[0045] 在一些实施例中,所述输入信号为差分信号,所述第一级放大器包括第三输出端、 第四输出端,所述第二级模数转换电路包括第三输入端、第四输入端,所述第二级放大器包 括第三电容、第四电容、第五电容、第六电容、第二放大器、第六开关、第九开关、第十一开关 和第十二开关;

[0046] 所述第三电容的第一端与所述第一级放大器的第三输出端连接,并通过所述第六 开关接地: 所述第三电容的第二端与所述第四电容的第一端连接, 所述第四电容的第二端

与所述第二级模数转换电路的第三输入端连接;所述第十一开关的第一端连接到所述第三电容的第二端与所述第四电容的第一端之间,所述第十一开关的第二端与所述第四电容的第二端连接;

[0047] 所述第五电容的第一端与所述第一级放大器的第四输出端连接,并通过所述第九 开关接地;所述第五电容的第二端与所述第六电容的第一端连接,所述第六电容的第二端 与所述第二级模数转换电路的第四输入端连接;所述第十二开关的第一端连接到所述第五 电容的第二端与所述第六电容的第一端之间,所述第十二开关的第二端与所述第六电容的 第二端连接;

[0048] 所述第二放大器的第一输入端连接到所述第三电容的第二端与所述第四电容的第一端之间,所述第二放大器的第二输入端连接到所述第五电容的第二端与所述第六电容的第一端之间,所述第二放大器的第一电源端与所述第四电容的第二端连接,所述第二放大器的第二电源端与所述第六电容的第二端连接;

[0049] 其中,所述第二放大器的第一电源端、第二电源端用于输出第二放大信号。

[0050] 在一些实施例中,所述第二级放大器还包括第五开关和第八开关,所述第三电容的第一端通过所述第五开关与所述第一级放大器的第三输出端连接,所述第五电容的第一端通过所述第八开关与所述第一级放大器的第四输出端连接。

[0051] 在一些实施例中,所述第一级模数转换电路包括:

[0052] 第一电容阵列,被配置为对输入信号进行采样并输出残余电压信号,所述第一级 放大器与所述第一电容阵列连接;

[0053] 第一比较器,与所述第一电容阵列连接,被配置为对所述残余电压信号进行比较, 并输出第一比较结果:以及

[0054] 第一逻辑控制电路,与所述第一电容阵列、所述第一比较器连接,被配置为基于所述第一比较结果对所述第一电容阵列进行逻辑控制以及输出第一数字信号。

[0055] 在一些实施例中,所述第二级模数转换电路包括:

[0056] 第二电容阵列,与所述第二级放大器连接,被配置为对所述第二放大信号进行采样;

[0057] 第二比较器,与所述第二电容阵列连接,被配置为对所述第二放大信号进行比较,并输出第二比较结果;以及

[0058] 第二逻辑控制电路,与所述第二电容阵列、所述第二比较器连接,被配置为基于所述第二比较结果对所述第二电容阵列进行逻辑控制以及输出第二数字信号。

[0059] 在一些实施例中,所述模数转换器还包括:

[0060] 输出电路,与所述第一级模数转换电路、所述第二级模数转换电路连接,被配置为根据所述第一数字信号和所述第二数字信号得到对所述输入信号的模数转换结果。

[0061] 本申请实施例还提供一种芯片,包括上述任一项所述的模数转换器。

[0062] 本申请实施例还提供一种模数转换控制方法,包括:

[0063] 在模数转换器的至少一组相邻的两级模数转换电路之间设置级间放大器,所述级间放大器包括至少两个放大器,所述至少两个放大器被配置为进行信号放大。

[0064] 在一些实施例中,所述相邻的两级模数转换电路包括第一级模数转换电路和第二级模数转换电路,所述至少两个放大器包括第一级放大器和第二级放大器,所述模数转换

控制方法还包括:

[0065] 控制第一级模数转换电路采样输入信号,对所述输入信号进行模数转换,以得到第一数字信号和残余电压信号,并对所述残余电压信号进行保持;

[0066] 控制第一级放大器对所述残余电压信号进行放大,得到第一放大信号;

[0067] 控制第二级放大器对所述第一放大信号依次进行采样和放大,得到第二放大信号;

[0068] 控制第二级模数转换电路对所述第二放大信号依次进行采样和模数转换,得到第二数字信号:以及

[0069] 根据所述第一数字信号和所述第二数字信号得到对所述输入信号的模数转换结果。

[0070] 在一些实施例中,所述第二级放大器为有源放大器,控制所述第二级模数转换电路对所述第二放大信号依次进行采样和模数转换时,同步控制所述第一级模数转换电路对所述输入信号进行下一次的采样和模数转换。

[0071] 在一些实施例中,所述第二级放大器为无源放大器,控制所述第一级模数转换电路对所述残余电压信号进行保持时,同步控制所述第二级模数转换电路对所述第二放大信号进行采样:

[0072] 控制所述第二级模数转换电路对所述第二放大信号进行模数转换时,同步控制所述第一级模数转换电路对所述输入信号进行下一次的采样和模数转换。

[0073] 在一些实施例中,控制所述第一级模数转换电路对所述残余电压信号进行保持时,同步控制所述第一级放大器对所述残余电压信号进行放大。

[0074] 在一些实施例中,控制所述第一级放大器对所述残余电压信号进行放大时,同步控制所述第二级放大器对所述第一放大信号进行采样。

[0075] 本申请实施例提供的模数转换器中,将级间放大器设置为包括至少两个放大器,两个放大器的功耗都能够降低,因此相对于单个级间放大器而言,能够降低模数转换器的功耗。

#### 附图说明

[0076] 为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍。显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

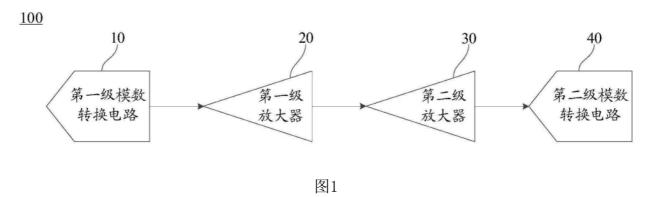

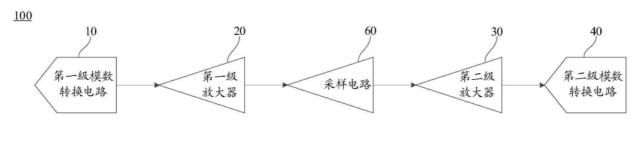

[0077] 图1为本申请实施例提供的模数转换器的第一种电路架构图。

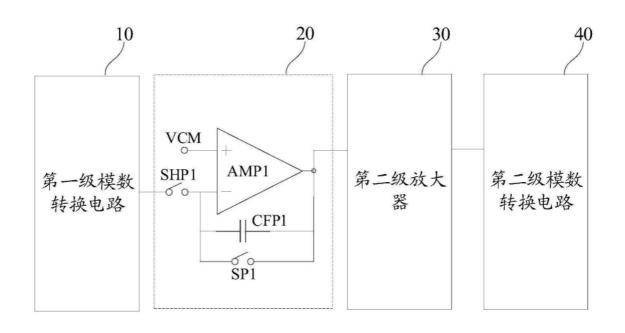

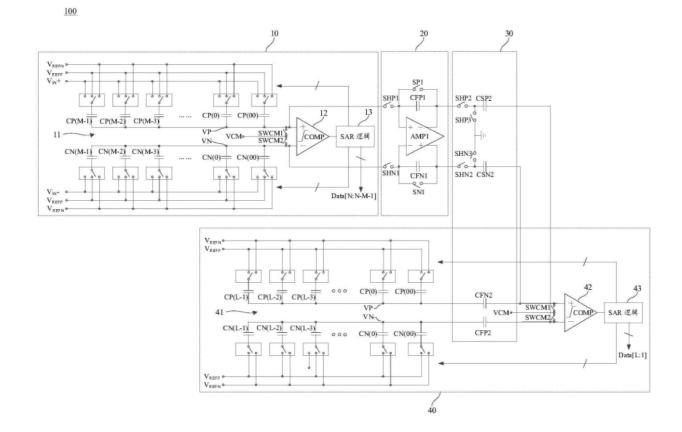

[0078] 图2为本申请实施例提供的模数转换器的第二种电路架构图。

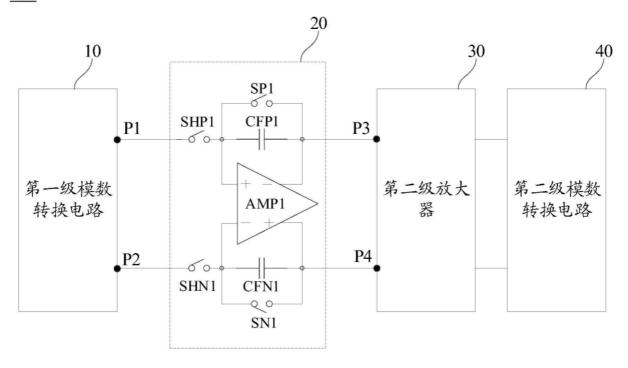

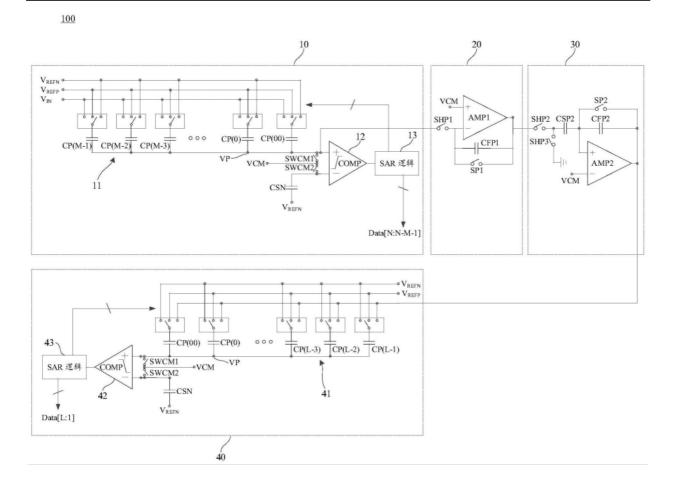

[0079] 图3为本申请实施例提供的模数转换器的第三种电路架构图。

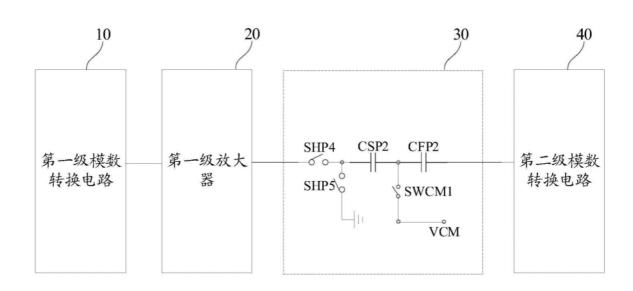

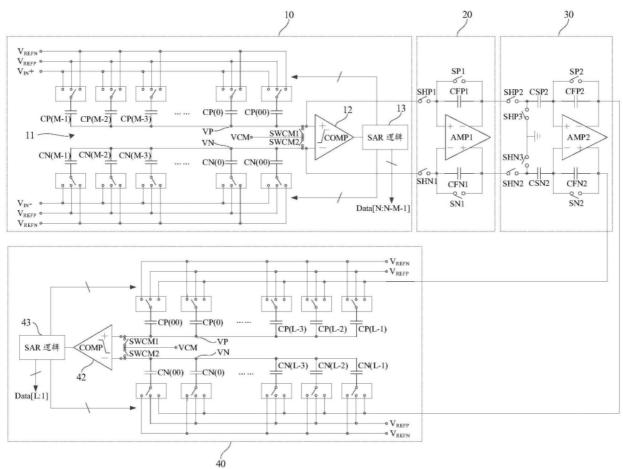

[0080] 图4为本申请实施例提供的模数转换器的第四种电路架构图。

[0081] 图5为本申请实施例提供的模数转换器的第五种电路架构图。

[0082] 图6为本申请实施例提供的模数转换器的第六种电路架构图。

[0083] 图7为本申请实施例提供的模数转换器的第七种电路架构图。

[0084] 图8为本申请实施例提供的模数转换器的第八种电路架构图。

6/16 页

[0085] 图9为本申请实施例提供的模数转换器的第九种电路架构图。

[0086] 图10为本申请实施例提供的模数转换器的第一种具体电路结构图。

[0087] 图11为图10所示模数转换器的运行时序图。

[0088] 图12为本申请实施例提供的模数转换器的第二种具体电路结构图。

[0089] 图13为本申请实施例提供的模数转换器的第三种具体电路结构图。

[0090] 图14为图13所示模数转换器的运行时序图。

[0091] 图15为本申请实施例提供的模数转换控制方法的流程示意图。

### 具体实施方式

[0092] 下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

[0093] 本申请实施例提供一种模数转换器,该模数转换器能够用于将输入信号转换为数字信号并输出,该输入信号例如可以为模拟信号。在实际应用中,该模数转换器可以为流水线模数转换器 (Pipeline -SAR ADC)。

[0094] 本申请实施例提供的模数转换器包括多级模数转换电路,例如两级、三级、四级等多级模数转换电路。其中,任一相邻的两级模数转换电路之间设置有级间放大器,该级间放大器包括至少两个放大器,例如包括两个、三个、四个甚至更多个放大器。该至少两个放大器被配置为进行信号放大。

[0095] 例如,在一些实施例中,该多级模数转换电路包括第一级模数转换电路和第二级模数转换电路,第一级模数转换电路与第二级模数转换电路之间设置有级间放大器,该级间放大器包括第一级放大器和第二级放大器。参考图1,图1为本申请实施例提供的模数转换器100的第一种电路架构图。其中,模数转换器100包括第一级模数转换电路10、第一级放大器20、第二级放大器30以及第二级模数转换电路40。第一级模数转换电路10的位数可以为M位(Mbit),第二级模数转换电路40的位数可以为L位(Lbit)。其中,M、L均为正整数。

[0096] 第一级模数转换电路10被配置为采样输入信号,并对输入信号进行模数转换,以得到第一数字信号和残余电压信号。例如,外部信号源可以将输入信号输入至第一级模数转换电路10,第一级模数转换电路10即可对该输入信号进行采样,并对输入信号进行模数转换,得到对应的数字信号和残余电压信号。该数字信号为第一数字信号,第一数字信号可以为Mbit的数字信号。该残余电压信号为模数转换结束后的量化残余误差电压信号。第一级模数转换电路10可以同时输出该残余电压信号和该第一数字信号。在实际应用中,基于不同场景的需求,该输入信号既可以为单端信号,也可以为差分信号。

[0097] 第一级放大器20与第一级模数转换电路10连接。第一级放大器20被配置为对该残余电压信号进行放大,得到并输出第一放大信号。

[0098] 第二级放大器30与第一级放大器20连接。第二级放大器30被配置为对第一放大信号进行采样和放大,得到并输出第二放大信号。例如,第二级放大器30可以先对第一放大信号进行采样,随后对采样得到的信号进行放大,得到第二放大信号,并输出第二放大信号。

[0099] 第二级模数转换电路40与第二级放大器30连接。第二级模数转换电路40被配置为

对第二放大信号进行采样以及模数转换,并输出第二数字信号。例如,第二级模数转换电路 40可以先对第二放大信号进行采样,随后对采样得到的信号进行模数转换,得到对应的数 字信号,即第二数字信号,第二数字信号可以为Lbit的数字信号。

[0100] 因此,本申请实施例提供的模数转换器100,可以通过第一级放大器20和第二级放大器30共同对输入信号进行放大,并通过第一级模数转换电路10和第二级模数转换电路40共同对输入信号进行模数转换,得到对应的数字信号。

[0101] 随后,模数转换器100可以根据第一数字信号和第二数字信号得到对该输入信号的模数转换结果。例如,可以将第一数字信号和第二数字信号结合,以得到完整数字信号, 并输出该完整数字信号,该完整数字信号可以为M+L bit的数字信号。举例而言,模数转换器100可以将第一数字信号、第二数字信号输入外部处理器,通过外部处理器对第一数字信号和第二数字信号进行结合。在一些实施方式中,对第一数字信号和第二数字信号进行结合时,可以将第一数字信号填充到完整数字信号的高位,并将第二数字信号填充到完整数字信号的低位,以得到最终的完整数字信号。

[0102] 本申请实施例提供的模数转换器100,将级间放大器设置为包括至少两个放大器,两个放大器的功耗都能够降低,因此相对于单个级间放大器而言,能够降低模数转换器100的功耗。

[0103] 在一些实施例中,第一级放大器20为有源放大器。

[0104] 在一些实施方式中,第一级放大器20为有源放大器时,参考图2,图2为本申请实施例提供的模数转换器100的第二种电路架构图。该电路架构的模数转换器100可以用于在输入信号为单端信号时,对输入信号进行模数转换。

[0105] 其中,第一级放大器20包括第一放大器AMP1、第一电容CFP1和第一开关SP1。

[0106] 第一放大器AMP1的第一输入端与第一级模数转换电路10连接,第一放大器AMP1的第二输入端连接到共模节点VCM,共模节点VCM可以提供共模电压,第一放大器AMP1的输出端与第二级放大器30连接。第一电容CFP1的第一端与第一放大器AMP1的第一输入端连接,第一电容CFP1的第二端与第一放大器AMP1的输出端连接。第一开关SP1的第一端与第一放大器AMP1的第一输入端连接,第一开关SP1的第二端与第一放大器AMP1的输出端连接。第一放大器AMP1的输出端用于输出第一放大信号。其中,第一放大器AMP1的第一输入端可以为负输入端,第二输入端可以为正输入端;或者,第一放大器AMP1的第一输入端可以为正输入端,第二输入端可以为负输入端,此时下级电路需要对信号进行反相。

[0107] 其中,第一级模数转换电路10输出的残余电压信号可以输入至第一放大器AMP1和第一电容CFP1,第一放大器AMP1、第一电容CFP1被配置为共同对该残余电压信号进行放大,并通过第一放大器AMP1的输出端输出第一放大信号。在进行放大时,第一开关SP1导通。其中,第一放大器AMP1的参数、第一电容CFP1的电容值大小可以根据实际需要进行设置。

[0108] 可以理解的,在实际应用中,第一级放大器20还可以包括第二开关SHP1,如图2所示。第一放大器AMP1的第一输入端通过第二开关SHP1与第一级模数转换电路10连接。在第一电容CFP1对残余电压信号进行采样时,第二开关SHP1导通。在第一放大器AMP1、第一电容CFP1共同对残余电压信号进行放大时,可以控制第二开关SHP1断开。

[0109] 需要说明的是,第一级模数转换电路10对输入信号进行采样和模数转换时,第一电容CFP1可以同步对残余电压信号进行采样,此时第二开关SHP1导通,第一开关SP1断开。

因此,第一级放大器20对残余电压信号进行采样的过程无需单独进行,从而可以节省第一级放大器20的处理时长,进而节省模数转换器100进行模数转换的时长,提高模数转换效率。

[0110] 在一些实施方式中,第一级放大器20为有源放大器时,参考图3,图3为本申请实施例提供的模数转换器100的第三种电路架构图。该电路架构的模数转换器100可以用于在输入信号为差分信号时,对输入信号进行模数转换。其中,第一级模数转换电路10包括第一输出端P1、第二输出端P2。第二级放大器30包括第一输入端P3、第二输入端P4。

[0111] 第一级放大器20包括第一电容CFP1、第二电容CFN1、第一放大器AMP1、第一开关SP1和第三开关SN1。

[0112] 第一放大器AMP1的第一输入端与第一级模数转换电路10的第一输出端P1连接,第一放大器AMP1的第二输入端与第一级模数转换电路10的第二输出端P2连接,第一放大器AMP1的第一电源端与第二级放大器30的第一输入端P3连接,第一放大器AMP1的第二电源端与第二级放大器30的第二输入端P4连接。第一放大器AMP1的第一电源端、第二电源端用于输出第一放大信号。其中,第一放大器AMP1的第一输入端例如可以为正输入端,第二输入端例如可以为负输入端,第一电源端例如可以为负电源端,第二电源端例如可以为正电源端。 [0113] 第一电容CFP1的第一端与第一放大器AMP1的第一输入端连接,第一电容CFP1的第二端与第一放大器AMP1的第一电源端连接。第一开关SP1的第一端与第一放大器AMP1的第一电源端连接。第二电容CFN1的第一端与第一放大器AMP1的第二端与第一放大器AMP1的第二端与第一放大器AMP1的第二端与第一放大器AMP1的第二端与第一放大器AMP1的第二端与第一放大器AMP1的第二端与第一放大器AMP1的第二端与第一放大器AMP1的第二端与第一放大器AMP1的第二端与第一放大器AMP1的第二电源端连接。

[0114] 第一级模数转换电路10输出的残余电压信号可以输入至第一电容CFP1、第二电容CFN1以及第一放大器AMP1。第一电容CFP1、第二电容CFN1以及第一放大器AMP1被配置为共同对该残余电压信号进行放大,并通过第一放大器AMP1的第一电源端、第二电源端输出第一放大信号。在进行放大时,第一开关SP1、第三开关SN1导通。其中,第一电容CFP1、第二电容CFN1的电容值大小、第一放大器AMP1的参数可以根据实际需要进行设置。

[0115] 可以理解的,在实际应用中,第一级放大器20还可以包括第二开关SHP1和第四开关SHN1。第一放大器AMP1的第一输入端通过第二开关SHP1与第一级模数转换电路10的第一输出端P1连接,第一放大器AMP1的第二输入端通过第四开关SHN1与第一级模数转换电路10的第二输出端P2连接。在第一电容CFP1、第二电容CFN1对残余电压信号进行采样时,第二开关SHP1、第四开关SHN1导通。在第一电容CFP1、第二电容CFN1以及第一放大器AMP1共同对残余电压信号进行放大时,可以控制第二开关SHP1、第四开关SHN1断开。

[0116] 需要说明的是,第一级模数转换电路10对输入信号进行采样和模数转换时,第一电容CFP1、第二电容CFN1可以同步对残余电压信号进行采样,此时第二开关SHP1、第四开关SHN1导通,第一开关SP1、第三开关SN1断开。因此,第一级放大器20对残余电压信号进行采样的过程无需单独进行,从而可以节省第一级放大器20的处理时长,进而节省模数转换器100进行模数转换的时长,提高模数转换效率。

[0117] 在一些实施例中,第一级放大器20还可以为无源放大器。第一级放大器20为无源放大器时,相对于第一级放大器20为有源放大器,能够节省第一放大器AMP1,因此能够减小

第一级放大器20的面积,从而减小模数转换器100的整体面积。

[0118] 在一些实施例中,第二级放大器30为无源放大器。

[0119] 在一些实施方式中,第二级放大器30为无源放大器时,参考图4,图4为本申请实施例提供的模数转换器100的第四种电路架构图。该电路架构的模数转换器100可以用于在输入信号为单端信号时,对输入信号进行模数转换。

[0120] 其中,第二级放大器30包括第三电容CSP2、第四电容CFP2、第六开关SHP5和第七开关SWCM1。

[0121] 第三电容CSP2的第一端与第一级放大器20连接,并通过第六开关SHP5接地。第三电容CSP2的第二端与第四电容CFP2的第一端连接,第三电容CSP2的第二端与第四电容CFP2的第一端之间通过第七开关SWCM1连接到共模节点VCM,共模节点VCM可以提供共模电压。第四电容CFP2的第二端与第二级模数转换电路40连接。第四电容CFP2的第二端用于输出第二放大信号。第三电容CSP2、第四电容CFP2的电容值大小可以根据实际需要进行设置。

[0122] 其中,第一级放大器20输出第一放大信号后,可以通过第三电容CSP2对第一放大信号进行采样。在进行采样时,第六开关SHP5断开,第七开关SWCM1导通。对第一放大信号进行采样后,可以通过第三电容CSP2、第四电容CFP2对第一放大信号进行放大。在进行放大时,第六开关SHP5导通,第七开关SWCM1断开。

[0123] 可以理解的,在实际应用中,第二级放大器30还可以包括第五开关SHP4。第三电容CSP2的第一端通过第五开关SHP4与第一级放大器20连接。在第三电容CSP2对第一放大信号进行采样时,第五开关SHP4导通。在第三电容CSP2、第四电容CFP2对第一放大信号进行放大时,可以控制第五开关SHP4断开,避免第二级放大器30的放大过程对第一级放大器20造成影响。

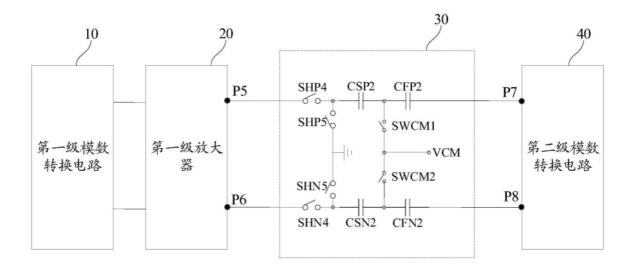

[0124] 在一些实施方式中,第二级放大器30为无源放大器时,参考图5,图5为本申请实施例提供的模数转换器100的第五种电路架构图。该电路架构的模数转换器100可以用于在输入信号为差分信号时,对输入信号进行模数转换。其中,第一级放大器20包括第三输出端P5、第四输出端P6。第二级模数转换电路40包括第三输入端P7、第四输入端P8。

[0125] 第二级放大器30包括第三电容CSP2、第四电容CFP2、第五电容CSN2、第六电容CFN2以及第六开关SHP5、第七开关SWCM1、第九开关SHN5、第十开关SWCM2。其中,第三电容CSP2、第四电容CFP2、第五电容CSN2、第六电容CFN2的电容值大小可以根据实际需要进行设置。

[0126] 第三电容CSP2的第一端与第一级放大器20的第三输出端P5连接,并通过第六开关SHP5接地。第三电容CSP2的第二端与第四电容CFP2的第一端连接,第三电容CSP2的第二端与第四电容CFP2的第一端之间通过第七开关SWCM1连接到共模节点VCM,共模节点VCM可以提供共模电压。第四电容CFP2的第二端与第二级模数转换电路40的第三输入端P7连接。

[0127] 第五电容CSN2的第一端与第一级放大器20的第四输出端P6连接,并通过第九开关SHN5接地。第五电容CSN2的第二端与第六电容CFN2的第一端连接,第五电容CSN2的第二端与第六电容CFN2的第一端之间通过第十开关SWCM2连接到共模节点VCM。第六电容CFN2的第二端与第二级模数转换电路40的第四输入端P8连接。

[0128] 其中,第四电容CFP2的第二端、第六电容CFN2的第二端用于输出第二放大信号。

[0129] 第一级放大器20输出第一放大信号后,可以通过第三电容CSP2、第五电容CSN2对第一放大信号进行采样。在进行采样时,第六开关SHP5、第九开关SHN5断开,第七开关

SWCM1、第十开关SWCM2导通。对第一放大信号进行采样后,可以通过第三电容CSP2、第四电容CFP2、第五电容CSN2、第六电容CFN2对第一放大信号进行放大。在进行放大时,第六开关SHP5、第九开关SHN5导通,第七开关SWCM1、第十开关SWCM2断开。

[0130] 可以理解的,在实际应用中,第二级放大器30还可以包括第五开关SHP4和第六开关SHP5。第三电容CSP2的第一端通过第五开关SHP4与第一级放大器20的第三输出端P5连接。第五电容CSN2的第一端通过第八开关SHN4与第一级放大器20的第四输出端P6连接。在第三电容CSP2、第五电容CSN2对第一放大信号进行采样时,第五开关SHP4、第八开关SHN4导通。在对第一放大信号进行放大时,可以控制第五开关SHP4、第八开关SHN4断开,避免第二级放大器30的放大过程对第一级放大器20造成影响。

[0131] 在一些实施例中,第二级放大器30为有源放大器。

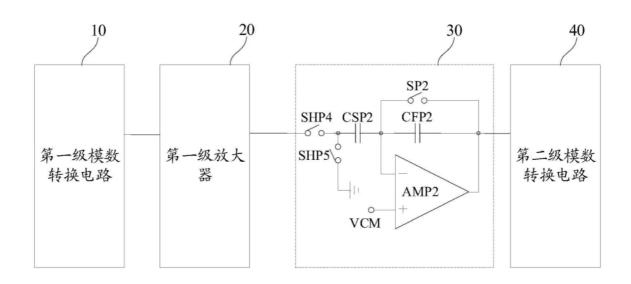

[0132] 在一些实施方式中,第二级放大器30为有源放大器时,参考图6,图6为本申请实施例提供的模数转换器100的第六种电路架构图。该电路架构的模数转换器100可以用于在输入信号为单端信号时,对输入信号进行模数转换。

[0133] 第二级放大器30包括第三电容CSP2、第四电容CFP2、第二放大器AMP2、第六开关SHP5和第十一开关SP2。其中,第三电容CSP2、第四电容CFP2的电容值和第二放大器AMP2的参数可以根据实际需要进行设置。

[0134] 第三电容CSP2的第一端与第一级放大器20连接,并通过第六开关SHP5接地。第三电容CSP2的第二端与第四电容CFP2的第一端连接,第四电容CFP2的第二端与第二级模数转换电路40连接。第二放大器AMP2的第一输入端连接到第三电容CSP2的第二端与第四电容CFP2的第一端之间,第二放大器AMP2的第二输入端连接到共模节点VCM,共模节点VCM可以提供共模电压,第二放大器AMP2的输出端与第四电容CFP2的第二端连接。第十一开关SP2的第一端连接到第三电容CSP2的第二端与第四电容CFP2的第一端之间,第十一开关SP2的第二端与第四电容CFP2的第二端连接。

[0135] 其中,第二放大器AMP2的输出端用于输出第二放大信号。

[0136] 第一级放大器20输出第一放大信号后,可以通过第三电容CSP2对第一放大信号进行采样。在进行采样时,第六开关SHP5断开,第十一开关SP2导通。对第一放大信号进行采样后,可以通过第三电容CSP2、第四电容CFP2、第二放大器AMP2对第一放大信号进行放大。在进行放大时,第六开关SHP5导通,第十一开关SP2断开。

[0137] 可以理解的,在实际应用中,第二级放大器30还可以包括第五开关SHP4。第三电容 CSP2的第一端通过第五开关SHP4与第一级放大器20连接。在对第一放大信号进行采样时,第五开关SHP4导通。在对第一放大信号进行放大时,可以控制第五开关SHP4断开,避免第二级放大器30的放大过程对第一级放大器20造成影响。

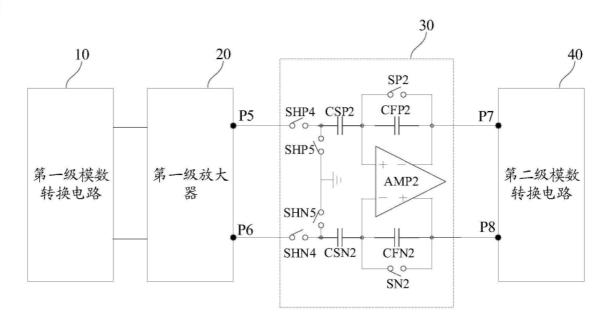

[0138] 在一些实施方式中,第二级放大器30为有源放大器时,参考图7,图7为本申请实施例提供的模数转换器100的第七种电路架构图。该电路架构的模数转换器100可以用于在输入信号为差分信号时,对输入信号进行模数转换。其中,第一级放大器20包括第三输出端P5、第四输出端P6。第二级模数转换电路40包括第三输入端P7、第四输入端P8。

[0139] 第二级放大器30包括第三电容CSP2、第四电容CFP2、第五电容CSN2、第六电容CFN2、第二放大器AMP2以及第六开关SHP5、第十一开关SP2、第九开关SHN5、第十二开关SN2。 其中,第三电容CSP2、第四电容CFP2、第五电容CSN2、第六电容CFN2的电容值和第二放大器 AMP2的参数可以根据实际需要进行设置。

[0140] 第三电容CSP2的第一端与第一级放大器20的第三输出端P5连接,并通过第六开关SHP5接地。第三电容CSP2的第二端与第四电容CFP2的第一端连接,第四电容CFP2的第二端与第二级模数转换电路40的第三输入端P7连接。第十一开关SP2的第一端连接到第三电容CSP2的第二端与第四电容CFP2的第一端之间,第十一开关SP2的第二端与第四电容CFP2的第二端连接。

[0141] 第五电容CSN2的第一端与第一级放大器20的第四输出端P6连接,并通过第九开关SHN5接地。第五电容CSN2的第二端与第六电容CFN2的第一端连接,第六电容CFN2的第二端与第二级模数转换电路40的第四输入端P8连接。第十二开关SN2的第一端连接到第五电容CSN2的第二端与第六电容CFN2的第一端之间,第十二开关SN2的第二端与第六电容CFN2的第二端连接。

[0142] 第二放大器AMP2的第一输入端连接到第三电容CSP2的第二端与第四电容CFP2的第一端之间,第二放大器AMP2第二输入端连接到第五电容CSN2的第二端与第六电容CFN2的第一端之间,第二放大器AMP2的第一电源端与第二级模数转换电路40的第三输入端P7连接,第二放大器AMP2的第二电源端与第二级模数转换电路40的第四输入端P8连接。第二放大器AMP2的第一电源端、第二电源端用于输出第二放大信号。其中,第二放大器AMP2的第一输入端例如可以为正输入端,第二输入端例如可以为负输入端,第一电源端例如可以为负电源端,第二电源端例如可以为正电源端。

[0143] 第一级放大器20输出第一放大信号后,可以通过第三电容CSP2、第五电容CSN2对第一放大信号进行采样。在进行采样时,第六开关SHP5、第九开关SHN5断开,第十一开关SP2、第十二开关SN2导通。对第一放大信号进行采样后,可以通过第三电容CSP2、第四电容CFP2、第五电容CSN2、第六电容CFN2以及第二放大器AMP2对第一放大信号进行放大。在进行放大时,第六开关SHP5、第九开关SHN5导通,第十一开关SP2、第十二开关SN2断开。

[0144] 可以理解的,在实际应用中,第二级放大器30还可以包括第五开关SHP4和第八开关SHN4。第三电容CSP2的第一端通过第五开关SHP4与第一级放大器20的第三输出端P5连接。第五电容CSN2的第一端通过第八开关SHN4与第一级放大器20的第四输出端P6连接。在对第一放大信号进行采样时,第五开关SHP4、第八开关SHN4导通。在对第一放大信号进行放大时,可以控制第五开关SHP4、第八开关SHN4断开,避免第二级放大器30的放大过程对第一级放大器20造成影响。

[0145] 由上述实施例的描述可知,第二级放大器30为无源放大器时,相对于第二级放大器30为有源放大器,能够节省第二放大器AMP2,因此能够减小第二级放大器30的面积,从而减小模数转换器100的整体面积。

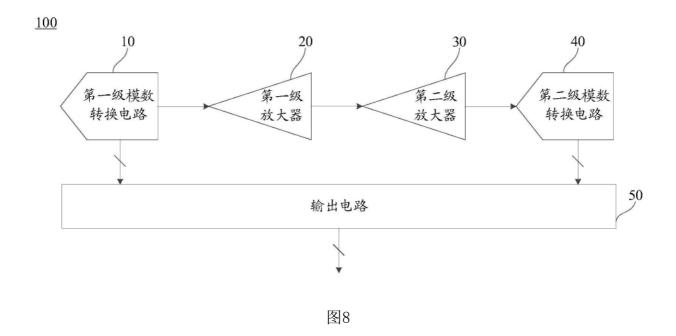

[0146] 在一些实施例中,参考图8,图8为本申请实施例提供的模数转换器100的第八种电路架构图。

[0147] 其中,模数转换器100还包括输出电路50。输出电路50与第一级模数转换电路10、第二级模数转换电路40连接。输出电路50被配置为根据第一级模数转换电路10输出的第一数字信号和第二级模数转换电路40输出的第二数字信号得到对输入信号的模数转换结果。例如,将第一级模数转换电路10输出的第一数字信号和第二级模数转换电路40输出的第二数字信号结合以得到完整数字信号,并输出该完整数字信号。

[0148] 举例而言,输出电路50可以将第一数字信号填充到完整数字信号的高位,并将第二数字信号填充到完整数字信号的低位,以得到最终的完整数字信号。

[0149] 可以理解的,在其他一些实施例中,模数转换器100可以不包括输出电路50,将第一数字信号和第二数字信号结合可以通过外部处理器进行。

[0150] 在一些实施例中,参考图9,图9为本申请实施例提供的模数转换器100的第九种电路架构图。

[0151] 图9所示模数转换器100与图1所示模数转换器100的区别在于:模数转换器100还包括采样电路60,采样电路60与第一级放大器20连接,被配置为对第一放大信号进行采样;第二级放大器30与采样电路60连接,被配置为对采样电路60输出的信号进行放大,并输出第二放大信号。其中,本实施例的采样电路60可以理解为上述实施例中第二级放大器30中的采样电路,而本实施例的第二级放大器30可以理解为上述实施例中第二级放大器30中除采样电路之外的电路。也即,上述实施例中,采样电路作为第二级放大器30的一部分,集成在第二级放大器30中;而本实施例中,采样电路独立于第二级放大器30之外,即为采样电路60。

[0152] 本实施例采样电路60的具体电路结构,可以参考上述实施例第二级放大器30中采样电路的结构,例如图6中的第三电容CSP2、图7中的第三电容CSP2和第五电容CSN2,故对采样电路60的具体结构在此不再赘述。

[0153] 上述各个实施例所描述的模数转换器100中,第一级模数转换电路10的位数为M位 (Mbit),第二级模数转换电路40的位数为L位 (Lbit)。因此,最终能够得到的完整数字信号的位数为N位,N=M+L。

[0154] 本申请实施例提供的模数转换器100,将级间放大器设置为包括至少两个放大器,因此相对于单个级间放大器而言,每一个放大器的放大时间都会缩短。以级间放大器包括第一级放大器20和第二级放大器30而言,当第一级放大器20的放大时间为单个级间放大器的一半时,根据前后级精度要求,那么第一级放大器20的带宽要求为单个级间放大器的两倍。由于带宽跟负载成负相关,因此第一级放大器20的负载减少非常大,因此所需要的电流减少也非常大,从而能够极大地降低第一级放大器20的功耗。当第二级放大器30的放大时间为单个级间放大器的一半时,根据前后级精度要求,那么第二级放大器30的带宽要求相对于单个级间放大器降低了。由于第二级放大器30的负载与单个级间放大器负载相同,但是所需要的带宽要求降低了,因此当实现第二级放大器30的带宽要求时,所要求的第二级放大器30的跨导降低了,因此第二级放大器30所需要的电流也降低了,因此能够降低第二级放大器30的功耗。从而,能够降低整个模数转换器100的功耗。

[0155] 上述实施例对模数转换器100的电路架构进行了描述,以下对模数转换器100的具体电路结构进行举例说明。

[0156] 在一些实施例中,参考图10,图10为本申请实施例提供的模数转换器100的第一种具体电路结构图,图10所示模数转换器100是第一级放大器20为有源放大器、第二级放大器30为无源放大器、输入信号为差分信号时的一种电路架构图。

[0157] 第一级模数转换电路10包括第一电容阵列11、第一比较器12以及第一逻辑控制电路13。第一电容阵列11被配置为对输入信号进行采样并输出残余电压信号,第一级放大器20与第一电容阵列11连接。第一比较器12与第一电容阵列11连接,被配置为对该残余电压

信号进行比较,并输出第一比较结果。第一逻辑控制电路13与第一电容阵列11、第一比较器12连接,被配置为基于第一比较结果对第一电容阵列11进行逻辑控制以及输出第一数字信号。

[0158] 其中,第一电容阵列11包括两组并联的电容,每一组电容均包括CP(00)、CP(0)、……CP(M-3)、CP(M-2)、CP(M-1)等多个电容。其中,一组电容的输入端通过多个开关连接到参考电压V<sub>REFN</sub>、V<sub>REFP</sub>以及输入信号V<sub>IN+</sub>,该组电容的输出端共同连接到节点VP,节点VP连接到第一比较器12的正输入端和第一级放大器20。此外,节点VP还可以通过开关SWCM1连接到共模节点VCM。另一组电容的输入端通过多个开关连接到参考电压V<sub>REFN</sub>、V<sub>REFP</sub>以及输入信号V<sub>IN-</sub>,该组电容的输出端共同连接到节点VN,节点VN连接到第一比较器12的负输入端和第一级放大器20。此外,节点VN还可以通过开关SWCM2连接到共模节点VCM。

[0159] 第一比较器12对第一电容阵列11采样到的输入信号进行比较动作,并将比较得到的第一比较结果输出至第一逻辑控制电路13。

[0160] 第一逻辑控制电路13基于第一比较结果对第一电容阵列11进行逻辑控制,并输出第一数字信号Data[N:N-M-1]。

[0161] 第二级模数转换电路40包括第二电容阵列41、第二比较器42以及第二逻辑控制电路43。第二电容阵列41与第二级放大器30连接,被配置为对第二级放大器30输出的第二放大信号进行采样。第二比较器42与第二电容阵列41连接,被配置为对第二放大信号进行比较,并输出第二比较结果。第二逻辑控制电路43与第二电容阵列41、第二比较器42连接,被配置为基于第二比较结果对第二电容阵列41进行逻辑控制以及输出第二数字信号。

[0162] 其中,第二电容阵列41包括两组并联的电容,每一组电容均包括CP(00)、CP(0)、……CP(L-3)、CP(L-2)、CP(L-1)等多个电容。其中,一组电容的输入端通过多个开关连接到参考电压V<sub>REFN</sub>、V<sub>REFP</sub>,该组电容的输出端共同连接到节点VP,节点VP通过第二级放大器30的第六电容CFN2连接到第二比较器42的正输入端和第五电容CSN2。此外,节点VP还可以通过第六电容CFN2、开关SWCM1连接到共模节点VCM。另一组电容的输入端通过多个开关连接到参考电压V<sub>REFN</sub>、V<sub>REFP</sub>,该组电容的输出端共同连接到节点VN,节点VN通过第二级放大器30的第四电容CFP2连接到第二比较器42的负输入端和第三电容CSP2。此外,节点VN还可以通过第四电容CFP2、开关SWCM2连接到共模节点VCM。

[0163] 第二比较器42对第二级放大器30输出的第二放大信号进行比较动作,并将比较得到的第二比较结果输出至第二逻辑控制电路43。

[0164] 第二逻辑控制电路43基于第二比较结果对第二电容阵列41进行逻辑控制,并输出第二数字信号Data[L:1]。

[0165] 同时参考图11,图11为图10所示模数转换器100的运行时序图。图中"SH1"表示第一级模数转换电路10的采样时序,"SAR1转换"表示第一级模数转换电路10的转换时序,"保持"表示第一级模数转换电路10的残余电压保持时序;"SH2"表示第二级模数转换电路40的采样时序,"SAR2转换"表示第二级模数转换电路40的转换时序;"RA1"表示第一级放大器20的放大时序,第一级放大器20的"关闭"表示第一级放大器20关闭;"SH4"表示第二级放大器30的采样时序,"RA2"表示第二级放大器30的放大时序,第二级放大器30的"关闭"表示第二级放大器30的放大时序,第二级放大器30的"关闭"表示第二级放大器30关闭。

[0166] 其中,模数转换器100运行时,第一级模数转换电路10首先进行采样,采样完成后

进行转换,转换完成后进行残余电压保持。在第一级模数转换电路10的残余电压保持阶段,第一级放大器20同步进行放大,放大完成后关闭。在第一级放大器20的放大阶段,第二级放大器30同步进行采样,采样完成后进行放大。在第二级放大器30的采样阶段,第二级模数转换电路40同步进行采样,采样完成后进行转换。至此,模数转换器100的一次模数转换过程完成。可以理解的,第二级放大器30在进行放大时,第二级模数转换电路40可以同时进行模数转换。

[0167] 需要说明的是,本申请实施例中,在第二级模数转换电路40进行转换时,第一级模数转换电路10可以同步进行下一次的采样和转换,并且第一级模数转换电路10的下一次转换和第二级模数转换电路40的本次转换同时完成。因此,模数转换器100的一次模数转换过程的完整周期为第一级模数转换电路10的采样时间、转换时间以及第一级放大器20的放大时间之和,能够节省第二级模数转换电路40的采样时间和转换时间,并且第一级放大器20的放大时间比传统级间放大器的放大时间小,因此能够减小模数转换器100的完整周期所需的时间,从而提高模数转换器100的处理效率。

[0168] 在一些实施例中,参考图12,图12为本申请实施例提供的模数转换器100的第二种具体电路结构图。图12所示模数转换器100是第一级放大器20为有源放大器、第二级放大器30为有源放大器、输入信号为单端信号时的一种电路架构图。

[0169] 其中,第一级模数转换电路10与上述实施例的不同之处在于:第一电容阵列11只包括一组电容CP(00)、CP(0)、……CP(M-3)、CP(M-2)、CP(M-1),第一比较器12的负输入端通过电容CSN连接到参考电压V<sub>REFN</sub>。第一级模数转换电路10与上述实施例的相同之处可以参考上述实施例中的描述,在此不再赘述。

[0170] 第二级模数转换电路40与上述实施例的不同之处在于:第二电容阵列41只包括一组电容CP(00)、CP(0)、……CP(L-3)、CP(L-2)、CP(L-1),第二比较器42的负输入端通过电容CSN连接到参考电压V<sub>REFN</sub>。第二级模数转换电路40与上述实施例的相同之处可以参考上述实施例中的描述,在此不再赘述。

[0171] 在一些实施例中,参考图13,图13为本申请实施例提供的模数转换器100的第三种具体电路结构图,图13所示模数转换器100是第一级放大器20为有源放大器、第二级放大器30为有源放大器、输入信号为差分信号时的一种具体电路结构图。

[0172] 其中,第一级模数转换电路10、第二级模数转换电路40与上述实施例相同,可以参考上述实施例的描述,在此不再赘述。

[0173] 同时参考图14,图14为图13所示模数转换器100的运行时序图。其中,第二级模数转换电路40的"关闭"表示第二级模数转换电路40关闭,时序图中其余各符号的含义与上述实施例相同,可以参考上述实施例的描述,在此不再赘述。

[0174] 本申请实施例中,模数转换器100运行时,第一级模数转换电路10首先进行采样,采样完成后进行转换,转换完成后进行残余电压保持。在第一级模数转换电路10的残余电压保持阶段,第一级放大器20同步进行放大,放大完成后关闭。在第一级放大器20的放大阶段,第二级放大器30同步进行采样,采样完成后进行放大,放大完成后关闭。在第二级放大器30的放大阶段,第二级模数转换电路40同步进行采样,采样完成后进行转换。至此,模数转换器100的一次模数转换过程完成。

[0175] 需要说明的是,本申请实施例中,在第二级模数转换电路40进行采样和转换时,第

一级模数转换电路10可以同步进行下一次的采样和转换,并且第一级模数转换电路10的下一次转换和第二级模数转换电路40的本次转换同时完成。因此,模数转换器100的一次模数转换过程的完整周期为第一级模数转换电路10的采样时间、转换时间以及第一级放大器20的放大时间之和,能够节省第二级模数转换电路40的采样时间和转换时间,并且第一级放大器20的放大时间比传统级间放大器的放大时间小,因此能够减小模数转换器100的完整周期所需的时间,从而提高模数转换器100的处理效率。

[0176] 由上述各个实施例的描述可知,本申请实施例的模数转换器100能够实现以下技术效果:

[0177] 第一方面,将级间放大器设置为包括至少两个放大器,两个放大器的功耗都能够降低,因此相对于单个级间放大器而言,能够降低模数转换器100的功耗。

[0178] 第二方面,模数转换器100的一次模数转换过程的完整周期,能够节省第二级模数转换电路40的采样时间和转换时间,或者能够节省第二级模数转换电路40的采样时间和转换时间并且第一级放大器20的放大时间比传统级间放大器的放大时间小,因此能够减小模数转换器100的完整周期所需的时间,从而提高模数转换器100的处理效率。

[0179] 第三方面,当第一级放大器20、第二级放大器30中的一个或者两个为无源放大器时,能够节省第一放大器AMP1和/或第二放大器AMP2,因此能够减小第一级放大器20和/或第二级放大器30的面积,从而减小模数转换器100的整体面积。

[0180] 本申请实施例还提供一种芯片,包括上述任一实施例所述的模数转换器100。

[0181] 本申请实施例还提供一种模数转换控制方法,包括:在模数转换器的至少一组相邻的两级模数转换电路之间设置级间放大器,级间放大器包括至少两个放大器,该至少两个放大器被配置为进行信号放大。该模数转换控制方法可以应用于上述各个实施例所描述的模数转换器100,以实现对模数转换器100的控制。

[0182] 在一些实施例中,该相邻的两级模数转换电路包括第一级模数转换电路和第二级模数转换电路,该至少两个放大器包括第一级放大器和第二级放大器。参考图15,图15为本申请实施例提供的模数转换控制方法的流程示意图。模数转换控制方法包括以下步骤:

[0183] 210,控制第一级模数转换电路采样输入信号,对输入信号进行模数转换,以得到第一数字信号和残余电压信号,并对残余电压信号进行保持:

[0184] 220,控制第一级放大器对残余电压信号进行放大,得到第一放大信号;

[0185] 230,控制第二级放大器对第一放大信号依次进行采样和放大,得到第二放大信号;

[0186] 240,控制第二级模数转换电路对第二放大信号依次进行采样和模数转换,得到第二数字信号:

[0187] 250,根据第一数字信号和第二数字信号得到对输入信号的模数转换结果。

[0188] 上述各个步骤的具体实施方式可以参考上述模数转换器100的各个实施例的描述,在此不再赘述。

[0189] 在一些实施例中,第二级放大器30为有源放大器时,控制第二级模数转换电路40对第二放大信号依次进行采样和模数转换时,同步控制第一级模数转换电路10对输入信号进行下一次的采样和模数转换。

[0190] 在一些实施例中,第二级放大器为无源放大器时,控制第一级模数转换电路10对

残余电压信号进行保持时,同步控制第二级模数转换电路40对第二放大信号进行采样;控制第二级模数转换电路40对第二放大信号进行模数转换时,同步控制第一级模数转换电路10对输入信号进行下一次的采样和模数转换。

[0191] 在一些实施例中,控制第一级模数转换电路10对残余电压信号进行保持时,同步控制第一级放大器20对残余电压信号进行放大。

[0192] 在一些实施例中,控制第一级放大器20对残余电压信号进行放大时,同步控制第二级放大器30对第一放大信号进行采样。

[0193] 上述各个步骤的具体实施方式可以参考上述模数转换器100的各个实施例的描述,在此不再赘述。

[0194] 在本申请的描述中,需要理解的是,诸如"第一"、"第二"等术语仅用于区分类似的对象,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。

[0195] 以上对本申请实施例提供的模数转换器、芯片以及模数转换控制方法进行了详细介绍。本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请。同时,对于本领域的技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。

100

图2

<u>100</u>

图3

<u>100</u>

图4

100

图5

100

图6

<u>100</u>

图7

图9

图10

| 第一级模数转换电路 | SH1 | SAR1转换 | 保持     | SH1 | SAR1转换 | 保持        | SH1  | SAR1转换 |  |

|-----------|-----|--------|--------|-----|--------|-----------|------|--------|--|

| 第一级放大器    | 关闭  |        | RA1    | 关闭  |        | RA1       | 关闭   |        |  |

| 第二级放大器    | 关闭  |        | SH4    | RA2 |        | SH4       | RA2  |        |  |

| 第二级模数转换电路 |     | SH2    | SAR2转换 |     | SH2    | H2 SAR2转换 |      |        |  |

|           |     |        |        |     |        | •         | 完整周昇 | 期 — ▶  |  |

图11

图12

<u>100</u>

图13

| 第一级模数转换电路 | SH1 | SAR1转换 | 保持  |          | SH1 | SAR1转换 | 保持  |        | SH1    | SAR1转换 |  |

|-----------|-----|--------|-----|----------|-----|--------|-----|--------|--------|--------|--|

| 第一级放大器    | 关闭  |        | RA1 | 关闭       |     | RA1    | 关闭  |        |        |        |  |

| 第二级放大器    | 2   | 关闭     |     | RA2      | 关闭  |        | SH4 | RA2    | 关闭     |        |  |

| 第二级模数转换电路 |     | 关闭     | SH2 | 2 SAR2转换 |     | 关闭     | SH2 | SAR2转换 |        |        |  |

|           |     |        |     |          |     | •      |     | 完整周昇   | 期 ———▶ |        |  |

图14

| 控制第一级模数转换电路采样输入信号,对输入信号进行模数转换,以得到第一数字信号和残余电压信号,并对残余电压信号进一2 | 10 |

|------------------------------------------------------------|----|

| 行保持                                                        |    |

| <b>\</b>                                                   |    |

| 控制第一级放大器对残余电压信号进行放大,得到第一放大信号—2                             | 20 |

| <b>↓</b>                                                   |    |

| _                                                          | 30 |

| 二放大信号                                                      |    |

| <b>\</b>                                                   |    |

| 控制第二级模数转换电路对第二放大信号依次进行采样和模数转2                              | 40 |

| 换,得到第二数字信号                                                 |    |

| <b>\</b>                                                   |    |

| 根据第一数字信号和第二数字信号得到对输入信号的模数转换结2                              | 50 |

| 果                                                          |    |

图15