### (19) **日本国特許庁(JP)**

(51) Int. CL.

# (12) 特 許 公 報(B2)

$\mathbf{F}$  L

(11)特許番号

特許第6806213号 (P6806213)

(45) 発行日 令和3年1月6日(2021.1.6)

(24) 登録日 令和2年12月8日 (2020.12.8)

| (01) 1110.01. | 1 1                           |           |                          |

|---------------|-------------------------------|-----------|--------------------------|

| HO1L 29/739   | (2006.01) HO1L                | 29/78     | 655G                     |

| HO1L 29/78    | ( <b>2006.01)</b> HO1L        | 29/78     | 653A                     |

| HO1L 21/823   | <b>4 (2006.01)</b> HO1L       | 29/78     | 652J                     |

| HO1L 27/06    | (2006.01) HO1L                | 29/78     | 657D                     |

| HO1L 29/12    | (2006.01) HO1L                | 29/78     | 652F                     |

|               |                               |           | 請求項の数 11 (全 15 頁) 最終頁に続く |

| (21) 出願番号     | 特願2019-181852 (P2019-181852)  | (73) 特許権者 | <b>省</b> 000006013       |

| (22) 出願日      | 令和1年10月2日(2019.10.2)          |           | 三菱電機株式会社                 |

| (62) 分割の表示    | 特願2017-536136 (P2017-536136)  |           | 東京都千代田区丸の内二丁目7番3号        |

|               | の分割                           | (74) 代理人  | 100082175                |

| 原出願日          | 平成27年8月26日 (2015.8.26)        |           | 弁理士 高田 守                 |

| (65) 公開番号     | 特開2019-220722 (P2019-220722A) | (74)代理人   | 100106150                |

| (43) 公開日      | 令和1年12月26日 (2019.12.26)       |           | 弁理士 高橋 英樹                |

| 審查請求日         | 令和1年10月2日(2019.10.2)          | (74) 代理人  | 100148057                |

|               |                               |           | 弁理士 久野 淑己                |

|               |                               | (72) 発明者  | 小西 和也                    |

|               |                               |           | 東京都千代田区丸の内二丁目7番3号 三      |

|               |                               |           | 菱電機株式会社内                 |

|               |                               | (72) 発明者  | 深田 祐介                    |

|               |                               |           | 東京都千代田区丸の内二丁目7番3号 三      |

|               |                               |           | 菱電機株式会社内                 |

|               |                               |           | 最終頁に続く                   |

# (54) 【発明の名称】半導体素子

## (57)【特許請求の範囲】

## 【請求項1】

半導体基板と、

前記半導体基板の上に形成されたエミッタ電極と、

前記半導体基板の上に形成されたゲート電極と、

前記半導体基板の上面側に形成された第1導電型のソース層と、

前記半導体基板の上面側に形成された第2導電型のベース層と、

前記半導体基板の下に形成されたコレクタ電極と、

前記半導体基板の上面側に形成された、前記ゲート電極と接続された複数のアクティブトレンチゲートと、

前記半導体基板の上面側に形成され、前記ゲート電極に接続されていない複数のダミートレンチゲートと、を備え、

前記アクティブトレンチゲートが3つ以上並ぶ第1構造と、前記ダミートレンチゲートが3つ以上並ぶ第2構造が、交互に設けられ、かつ<u>前記第1構造における前記アクティブ</u>トレンチゲートの数よりも前記第2構造における前記ダミートレンチゲートの数が大きく

前記ベース層は、前記第1構造と前記第2構造との間で前記エミッタ電極に接続されたことを特徴とする半導体素子。

### 【請求項2】

前記半導体基板は、

30

40

50

前記ソース層の下に形成された前記ベース層の下に設けられた、第1導電型のキャリア 蓄積層と、

前記キャリア蓄積層の下にある、第1導電型のドリフト層と、を備え、

前記キャリア蓄積層の不純物濃度は、前記ドリフト層の不純物濃度より大きく、前記ソース層の不純物濃度より小さく、

前記複数のアクティブトレンチゲートと前記複数のダミートレンチゲートは、前記ソース層、前記ベース層及び前記キャリア蓄積層を貫通することを特徴とする請求項1に記載の半導体素子。

#### 【請求項3】

前記ベース層のうち、前記アクティブトレンチゲートに隣接する部分は、前記エミッタ 10 電極に接続され、

前記ベース層のうち、前記ダミートレンチゲートに挟まれた部分は、前記エミッタ電極に接続されないことを特徴とする請求項1または2に記載の半導体素子。

## 【請求項4】

前記ベース層のうち、前記アクティブトレンチゲートに隣接する部分は、前記エミッタ 電極に接続され、

前記ベース層のうち、前記ダミートレンチゲートに挟まれた部分は、前記エミッタ電極に接続されたことを特徴とする請求項1又は2に記載の半導体素子。

#### 【請求項5】

前記第2構造には、前記ダミートレンチゲートに挟まれた前記ベース層が2箇所以上あり、1箇所は前記エミッタ電極に接続され、別の1箇所は前記エミッタ電極に接続されないことを特徴とする請求項1又は2に記載の半導体素子。

#### 【請求項6】

前記第1構造を構成する3つ以上の前記アクティブトレンチゲートが接続されることで、前記第1構造は、平面視でメッシュ状に形成されたことを特徴とする請求項1から5のいずれか1項に記載の半導体素子。

#### 【請求項7】

前記ソース層は、前記複数のアクティブトレンチゲート及び前記複数のダミートレンチ ゲートに対し交差する、第1ソース層と第2ソース層を有し、

第 1 ソース層と第 2 ソース層の間隔は一定ではないことを特徴とする請求項 1 から 6 のいずれか 1 項に記載の半導体素子。

## 【請求項8】

トレンチMOSFETを構成することを特徴とする請求項1から7のいずれか1項に記載の半導体素子。

# 【請求項9】

R C - I G B T を構成することを特徴とする請求項 1 から 8 のいずれか 1 項に記載の半導体素子。

#### 【請求項10】

前記半導体基板はワイドバンドギャップ半導体によって形成されたことを特徴とする請求項1から9のいずれか1項に記載の半導体素子。

# 【請求項11】

前記ワイドバンドギャップ半導体は、炭化珪素、窒化ガリウム系材料又はダイヤモンドであることを特徴とする請求項10に記載の半導体素子。

# 【発明の詳細な説明】

#### 【技術分野】

## [0001]

この発明は、例えば大電流のスイッチングなどに用いられる半導体素子に関する。

#### 【背景技術】

# [0002]

近年、省電力化と小型化が進むエアコン及び冷蔵庫などの家電機器、鉄道のインバータ

ー並びに産業用ロボットのモーター制御等に、絶縁ゲート型バイポーラトランジスタ(IGBT)が幅広く用いられている。電力機器を高効率化するために、IGBTの定常損失とターンオン損失を低減することが求められている。

[00003]

特許文献1にはトレンチ構造をもつIGBTは、ゲートに接続したアクティブトレンチゲートの両側にエミッタ電極に接続したダミーゲートを配置し、このアクティブトレンチゲートとダミーゲート間のp型ベース層にn型ソースを形成することが開示されている。

[0004]

特許文献 2 には、隣接するアクティブトレンチゲートとアクティブトレンチゲート間の p型ベース層にn型ソースを形成するIGBTが開示されている。

10

【先行技術文献】

【特許文献】

[0005]

【特許文献1】特開2002-016252号公報

【特許文献 2 】特開 2 0 0 3 - 1 8 8 3 8 2 号公報

【発明の概要】

【発明が解決しようとする課題】

[0006]

コレクタが電源の高電位側(p側)に接続されたp側半導体素子のエミッタと、エミッタが電源の低電位側(n側)に接続されたn側半導体素子のコレクタを接続することがある。p側半導体素子とn側半導体素子の接続点に負荷が接続される。p側半導体素子とn側半導体素子には1つずつ還流ダイオードが接続される。p側半導体素子に逆並列に接続される還流ダイオードをp側ダイオードといい、n側半導体素子に逆並列に接続される還流ダイオードをn側ダイオードという。

20

30

40

[0007]

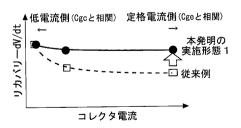

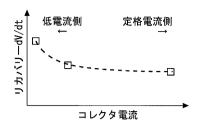

n側ダイオードに還流電流が流れている状態で、p側半導体素子をターンオンするとn側ダイオードにリカバリ電流が流れる。例えば、p側半導体素子として、特許文献 1、2に開示の半導体素子を採用すると、p側半導体素子のコレクタ電流に応じてn側ダイオードのリカバリd V / d t が変化する。具体的に言えば、p側 I G B T の低電流でのターンオン損失時におけるn側ダイオードのリカバリd V / d t は p側 I G B T の定格電流時でのリカバリd V / d t に比べ大きくなる。図 1 5 にはこのことが示されている。図 1 5 において、「低電流側」とは p側半導体素子のコレクタ電流が小さいことを意味し、「定格電流側」とは p側半導体素子のコレクタ電流が大きいことを意味する。 p側半導体素子のコレクタ電流が小さいときは n側ダイオードのリカバリd V / d t が大きいのに対し、p側半導体素子のコレクタ電流が大きいときは n側ダイオードのリカバリd V / d t が小さい。

[00008]

このように、ダイオードのリカバリ d V / d t が電流依存性をもつと以下の問題が生じる。すなわち、半導体素子のゲート抵抗は、大きいリカバリ d V / d t が所定の値になるように設定される。そのため、例えば、低電流側のリカバリ d V / d t が 2 0 k V /  $\mu$  s になるようゲート抵抗を決めた時、(ターンオン損失を評価する)定格電流側の d V / d t は 1 0 k V /  $\mu$  s 程度となる。その結果、半導体素子のスイッチング時間が長くなりターンオン時のターンオン損失(ターンオン損失)が増大する。つまり、ダイオードのリカバリ d V / d t が電流依存性をもつと、ターンオン損失が増大する。

[0009]

本発明は上述の問題を解決するためになされたものであり、還流ダイオードのリカバリ d V / d t が半導体素子のコレクタ電流に依存することを抑制できる半導体素子を提供することを目的とする。

【課題を解決するための手段】

[0010]

本願の発明にかかる半導体素子は、半導体基板と、該半導体基板の上に形成されたエミ ッタ電極と、該半導体基板の上に形成されたゲート電極と、該半導体基板の上面側に形成 された第1導電型のソース層と、該半導体基板の上面側に形成された第2導電型のベース 層と、該半導体基板の下に形成されたコレクタ電極と、該半導体基板の上面側に形成され た、該ゲート電極と接続された複数のアクティブトレンチゲートと、該半導体基板の上面 側に形成され、該ゲート電極に接続されていない複数のダミートレンチゲートと、を備え 、該アクティブトレンチゲートが3つ以上並ぶ第1構造と、該ダミートレンチゲートが3 つ以上並ぶ第2構造が、交互に設けられ、かつ該第1構造における該アクティブトレンチ ゲートの数よりも該第2構造における該ダミートレンチゲートの数が大きく、該ベース層 は、該第1構造と該第2構造との間で該エミッタ電極に接続されたことを特徴とする。

[0011]

本発明のその他の特徴は以下に明らかにする。

#### 【発明の効果】

## [0012]

この発明によれば、アクティブトレンチゲートが3つ以上並ぶ第1構造と、ダミートレ ンチゲートが3つ以上並ぶ第2構造を、交互に設けた半導体素子を提供することで、還流 ダイオードのリカバリdV/dtが半導体素子のコレクタ電流に依存することを抑制でき る。

#### 【図面の簡単な説明】

[0013]

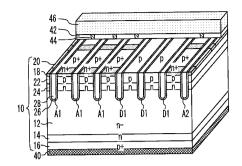

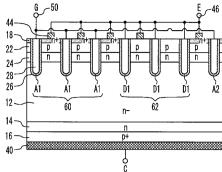

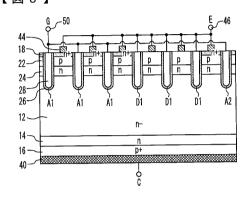

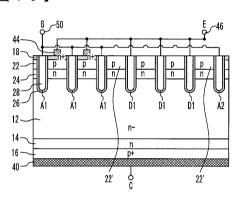

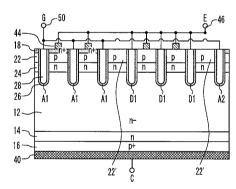

- 【図1】実施の形態1に係る半導体素子の一部断面斜視図である。

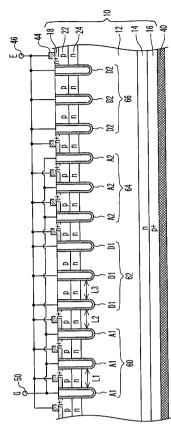

- 【図2】半導体素子の断面図である。

- 【図3】半導体素子を用いた回路構成例を示す回路図である。

- 【図4】半導体素子の動作時における空乏層の伸び方を示す図である。

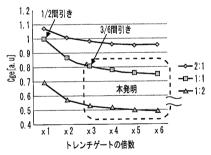

- 【図5】トレンチゲートの配列とCgeの関係を示す図である。

- 【図6】平準化されたリカバリdV/dtを示す図である。

- 【図7】低減されたターンオン損失を示す図である。

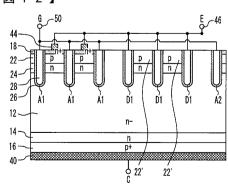

- 【図8】実施の形態2に係る半導体素子の一部断面図である。

- 【図9】変形例に係る半導体素子の一部断面図である。

- 【図10】実施の形態3に係る半導体素子の一部断面図である。

- 【図11】変形例に係る半導体素子の一部断面図である。

- 【図12】実施の形態4に係る半導体素子の一部断面図である。

- 【図13】実施の形態5に係る半導体素子を構成する半導体基板の平面図である。

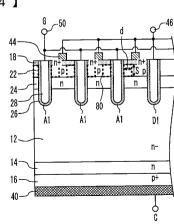

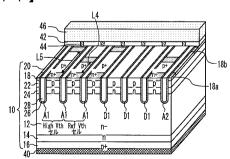

- 【図14】実施の形態6に係る半導体素子の一部断面斜視図である。

- 【図15】課題を説明する図である。

- 【発明を実施するための形態】

# [0014]

本発明の実施の形態に係る半導体素子について図面を参照して説明する。同じ又は対応 する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

# [0015]

# 実施の形態1.

図1は、本発明の実施の形態1に係る半導体素子の一部断面斜視図である。この半導体 素子はIGBTである。この半導体素子は半導体基板10を備えている。半導体基板10 には n - 型のドリフト層 1 2 が形成されている。ドリフト層 1 2 の下には n 型のバッファ 層14が形成されている。バッファ層14の下にはp+型のコレクタ層16が形成されて いる。

#### [0016]

半導体基板 1 0 の表面側には n + 型のソース層 1 8 と、 p + 型のコンタクト層 2 0 が形 成されている。ソース層18の下にはp型のベース層22が形成されている。ベース層2 2の下にはn型のキャリア蓄積層24が形成されている。そして、キャリア蓄積層24の 10

20

30

40

下には前述のドリフト層12がある。

## [0017]

半導体基板10の上面側には、複数のアクティブトレンチゲートA1、A2と、複数のダミートレンチゲートD1が形成されている。アクティブトレンチゲートとはゲート電極に電気的に接続されたトレンチゲートであり、ダミートレンチゲートとはエミッタ電極に電気的に接続されたトレンチゲートである。複数のアクティブトレンチゲートA1、A2と複数のダミートレンチゲートD1は、半導体基板10に溝を形成し、その溝の壁面に絶縁膜26を形成し、その後溝を導電体28で埋め込むことで形成される。複数のアクティブトレンチゲートA1、A2と複数のダミートレンチゲートD1は、半導体基板10の表面からソース層18、ベース層22及びキャリア蓄積層24を貫通し、ドリフト層12にまで達している。

[0018]

前述のソース層18は、アクティブトレンチゲートA1、A2の片側もしくは両側壁にそれぞれ接して形成されればよい。しかし、ダミートレンチゲートD1に挟まれた領域にソース層18を形成してもよい。

[0019]

半導体基板10の下にはコレクタ電極40が形成されている。半導体基板10の上面には層間絶縁膜42が設けられている。層間絶縁膜42には開口が設けられ、その開口には、コンタクト層20及びソース層18に接触するエミッタコンタクト44が設けられている。エミッタコンタクト44はベース層22の上に形成される。層間絶縁膜42の上にはエミッタコンタクト44に接触するエミッタ電極46が形成されている。

[0020]

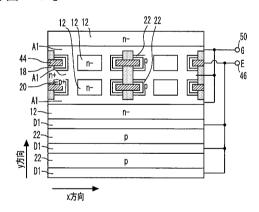

図2は、半導体素子の断面図である。図2を参照してトレンチゲートの配列を説明する。半導体基板10の上には、エミッタ電極46とゲート電極50が形成されている。3つのアクティブトレンチゲートA1と3つのアクティブトレンチゲートA2はゲート電極50と接続されている。3つのダミートレンチゲートD1と3つのダミートレンチゲートD2はゲート電極50に接続されず、エミッタ電極46に接続されている。

[0021]

ソース層 1 8 のうち、アクティブトレンチゲート A 1 、 A 2 に隣接する部分にはエミッタコンタクト 4 4 が接している。従って、ソース層 1 8 のうちアクティブトレンチゲート A 1 、 A 2 に隣接する部分はエミッタ電極 4 6 に接続されている。他方、ベース層 2 2 のうち、ダミートレンチゲート D 1 、 D 2 に挟まれた部分は、エミッタ電極 4 6 に接続されない。

[0022]

3つのアクティブトレンチゲートA1が並ぶことで第1構造60が形成されている。第1構造60の横には、3つのダミートレンチゲートD1が並ぶことで第2構造62が形成されている。第2構造62の横には、3つのアクティブトレンチゲートA2が並ぶことで第1構造64が形成されている。第1構造64の横には、3つのダミートレンチゲートD2が並ぶことで第2構造66が形成されている。このように、3つのアクティブトレンチゲートで構成される第1構造と、3つのダミートレンチゲートで構成される第1構造が交互に設けられている。

[0023]

図3は、半導体素子を用いた回路構成例を示す回路図である。 p 側半導体素子 7 0 と n 側半導体素子 7 4 の接続点 P 1 に負荷 7 8 が接続される。 p 側半導体素子 7 0 には還流ダイオードとして p 側ダイオード 7 2 が接続され、 n 側半導体素子 7 4 には還流ダイオードとして n 側ダイオード 7 6 が接続される。 p 側半導体素子 7 0 と n 側半導体素子 7 4 として、本発明の実施の形態 1 に係る半導体素子を採用する。

[0024]

図 2 の説明に戻る。第 1 構造 6 0 、 6 4 におけるアクティブトレンチゲート間の距離 L 1 は 1 . 5 μ m 以下とした。アクティブトレンチゲートとダミートレンチゲートの距離 L 10

20

30

40

20

30

40

50

2、及びダミートレンチゲートとダミートレンチゲートの距離 L 3 は特に限定しないが、 例えば 1 . 5 μ m 程度とする。

#### [0025]

本発明の実施の形態 1 に係る半導体素子の製造方法の一例について説明する。まず、 n 型の半導体基板を準備する。次いで、マスクとして酸化膜を形成し、その酸化膜上に写真製版法によってレジストパターンを形成する。レジストパターンをマスクとして酸化膜をエッチングする。次いで、レジストパターンを除去する。

## [0026]

#### [0027]

次に酸化膜からなるマスクを用いて、不純物としてヒ素(As)イオンを注入し、注入したヒ素をドライブにより拡散する。これにより、p型のベース層22の上に、n型のソース層18が形成される。例えばソース層18の不純物濃度は例えば5×1018~5×1019cm・3であり、拡散深さは例えば0.5μmである。

## [0028]

次にアクティブトレンチゲートとダミートレンチゲートを形成する。アクティブトレンチゲートはゲート電極に、ダミートレンチゲートはエミッタ電極に接続するようにパターニングされた酸化膜からなるマスクを用いて、ドライエッチングによりベース層 2 2 とキャリア蓄積層 2 4 を貫通してトレンチが形成される。例えば、トレンチの深さは 6 . 0 μm、幅は 1 . 0 μmである。

## [0029]

次に、酸化膜マスクを除去し、トレンチの側壁を覆う酸化膜(絶縁膜26)を形成する。続いて、絶縁膜26で覆われたトレンチにポリシリコンなどの導電体28を充填する。次いで、トレンチ内の導電体28を絶縁するための酸化膜等からなる層間絶縁膜42を形成する。層間絶縁膜42の膜厚はたとえば1.0 μ m である。

## [0030]

次いで、酸化膜からなるマスクを用いて、エミッタコンタクト44を形成する。次いでエミッタ電極46を形成する。エミッタ電極46の材料は、たとえばアルミニウム又はアルミニウムシリコンである。エミッタ電極46の膜厚はたとえば4.0µmである。また、エミッタ電極46と絶縁されたゲート電極50も形成する。

## [0031]

次いで、半導体基板10の下面にPイオン及びBイオンを注入し、アニールによりp型のコレクタ層16、n型のバッファ層14を形成する。アニールは工程を削減するため上記載の様に1回で行ってもよく、PイオンとBイオンをそれぞれ注入した後に2回に分けて行ってもよい。次いで、コレクタ電極40を形成する。コレクタ電極40の材料と膜厚は任意に設定することができる。

#### [0032]

発明者は、還流ダイオードのリカバリd V / d t が半導体素子のコレクタ電流に依存することを抑制するためには、半導体素子のゲート電極・コレクタ電極間容量(Cgc)をゲート電極・エミッタ電極間容量(Cge)で除した値(Cgc/Cge)を大きくすることが有効であることを見出した。より具体的には、半導体素子のCgcを大きくすることで低電流時のリカバリd V / d t の増加を抑制できる。また、半導体素子のCgeを小

20

30

40

50

さくすることで大電流時(定格電流時)のリカバリ d V / d t を増加させることができる。 C g c / C g e の値を大きくすることで、スイッチング時間を短くしターンオン損失を低減できる。本発明の実施の形態 1 に係る半導体素子は、この知見に基づき製造されたものである。

## [0033]

本発明の実施の形態 1 に係る半導体素子は、 C g c の値を維持しつつ C g e を低減するのに好適な構成となっている。そのことについて、半導体素子の動作時における空乏層の伸び方を示す図 4 を参照して説明する。ゲート電極 5 0 - エミッタ電極 4 6 間に電圧 V g e を印加すると、ベース層 2 2 において、アクティブトレンチゲート A 1 の側壁から空乏層 8 0 が広がる。例えば、空乏層 8 0 は破線で示された領域に形成される。半導体素子の C g e は酸化膜容量(絶縁膜 2 6 を誘電体層とする容量)と空乏層容量に依存する。そのため、空乏層 8 0 の距離 d が大きく、表面積 S が小さいほど、 C g e を低減することができる。

## [0034]

印加電圧Vgeが大きくなると、アクティブトレンチゲートの側壁から形成された空乏層と、隣のアクティブトレンチゲートから形成された空乏層が重なり、空乏層の距離dは大きくなる。本発明の実施の形態1では、第1構造におけるアクティブトレンチゲート間の距離を1.5μm以下としたので、低い印加電圧Vgeでも空乏層を重ねることができる。空乏層が重なると距離dが大きい1つの空乏層が形成されるので、Cgeを十分に低減することができる。

#### [0035]

空乏層の表面積 S を小さくすることは、キャリア蓄積層 2 4 の不純物濃度を調整することで実現した。つまり、キャリア蓄積層 2 4 の不純物濃度をドリフト層 1 2 の不純物濃度より大きくした。また、キャリア蓄積層 2 4 の不純物濃度をソース層 1 8 の不純物濃度より大きくした。キャリア蓄積層 2 4 の不純物濃度をドリフト層 1 2 の不純物濃度より大きくしたので、大規模な空乏層がキャリア蓄積層 2 4 に形成されることを防止できる。つまり空乏層の表面積 S の増加を抑制できる。また、キャリア蓄積層 2 4 の不純物濃度をソース層 1 8 の不純物濃度より小さくすることで、キャリア蓄積層 2 4 の不純物濃度が極端に大きくなり、ホールがキャリア蓄積層 2 4 の上方へ抜けにくくなることを防止できる。

# [0036]

隣接したアクティブトレンチゲート間の距離 L 1 を 1 . 5 μ m 以下とし、キャリア蓄積層 2 4 の不純物濃度をドリフト層 1 2 の不純物濃度より大きくしたので、空乏層容量を小さくすることができる。仮に上記のキャリア蓄積層の不純物濃度が実現されなければ、十分に C g e を低減できず、しかも C g c を増加させてしまう。

## [0037]

ところで、アクティブトレンチゲートとダミートレンチゲートが隣り合った部分では、アクティブトレンチゲートの側壁から空乏層が広がるが、ダミートレンチゲートの側壁からは空乏層が広がらない。そのため、2つの空乏層を重ねることによるCgeの低減効果を得ることができない。したがって、アクティブトレンチゲートとダミートレンチゲートの隣接箇所の密度を考慮して、アクティブトレンチゲートとダミートレンチゲートの配列を決める必要がある。

# [0038]

図 5 は、アクティブトレンチゲートとダミートレンチゲートの配列方法と、 C g e の関係を示すグラフである。 2 : 1 というのは、アクティブトレンチゲートの数とダミートレンチゲートの数の比(個数比)が 2 : 1 ということである。 1 : 1 はアクティブトレンチゲートの数とダミートレンチゲートの数の比が 1 : 1 であることを表し、 1 : 2 はアクティブトレンチゲートの数とダミートレンチゲートの数の比が 1 : 2 であることを表す。

#### [0039]

横軸のトレンチゲートの倍数というのは、前述の比における 1 がいくつのトレンチゲートで構成されるかを示す。具体的には、図 5 の 1 : 1 の場合における 6 つのプロットに着

20

30

40

50

目して説明する。 1:1 の場合において、トレンチゲートの倍数が $\times$  1 であれば、 1 つのアクティブトレンチゲートと 1 つのダミートレンチゲートが交互に設けられる。 1 つのアクティブトレンチゲートと 1 つのダミートレンチゲートの和が 2 であり、そのうち 1 つがアクティブであるから、 1/2 間引きと言う。 1:1 の場合において、トレンチゲートの倍数が $\times$  2 であれば、 2 つのアクティブトレンチゲートと 2 つのダミートレンチゲートが交互に設けられる。

#### [0040]

1:1の場合において、トレンチゲートの倍数が×3であれば、3つのアクティブトレンチゲートと3つのダミートレンチゲートが交互に設けられる。本発明の実施の形態1に係る半導体素子は、1:1でトレンチゲートの倍数が×3の場合に相当する。3つのアクティブトレンチゲートと3つのダミートレンチゲートの和が6であり、そのうち3つがアクティブであるから、3/6間引きと言う。

## [0041]

1:1の場合において、トレンチゲートの倍数が×4であれば、4つのアクティブトレンチゲートと4つのダミートレンチゲートが交互に設けられる。そして、トレンチゲートの倍数が×5であれば5つのアクティブトレンチゲートと5つのダミートレンチゲートが交互に設けられる。トレンチゲートの倍数が×6であれば6つのアクティブトレンチゲートと6つのダミートレンチゲートが交互に設けられる。

#### [0042]

例えば 2:1 の場合において、トレンチゲートの倍数が x 3 であれば、 6 つのアクティブトレンチゲートと 3 つのダミートレンチゲートが交互に設けられる。例えば 1:2 の場合において、トレンチゲートの倍数が x 3 であれば、 x 3 つのアクティブトレンチゲートと x 6 つのダミートレンチゲートが交互に設けられる。前述の「間引き」という言葉を用いる ことで、図 x 5 の x 8 プロットの各々を簡潔に言い表すことができる。例を挙げれば、個数比 x 2 : 1 の場合において、トレンチゲートの倍数が x 1 であれば「 x 1 / 3 間引き」といい、個数比 x 1 : 2 の場合において、トレンチゲートの倍数が x 1 であれば「 x 2 / 3 間引き」という。

### [0043]

ここまでの説明で明らかであるが、トレンチゲートの倍数を増加させることは、アクティブトレンチゲートとダミートレンチゲートの個数比を固定したままで、各本数を整数倍することを意味する。

# [0044]

本発明の実施の形態 1 では「 3 / 6 間引き」を採用したので、 1 / 2 間引きの半導体素子と比較すれば C g e を 2 0 %低減できる。しかも C g c の増加はない。そのため、 1 / 2 間引きと比較して C g c / C g e を 2 0 %増加させることができる。したがって、還流ダイオードのリカバリ d V / d t が半導体素子のコレクタ電流に依存することを抑制できる。

## [0045]

図5から、アクティブトレンチゲートの数とダミートレンチゲートの数の比(個数比)が1:2の場合にも低いCgeを得ることができることが分かる。しかしながら、個数比が2:1の場合、個数比が1:1の場合と比較してCgeが大きくなる。個数比が2:1の場合の基準構造である1/3間引はアクティブトレンチゲートが隣接する構造であるため、既にアクティブトレンチゲートが隣接することによるCge低減効果が得られているので、トレンチゲートの倍数を増加させてもCgeを大きく低下させることができない。

#### [0046]

本発明の実施の形態 1 では、 3 / 6 間引きを採用したが別の配列を採用してもよい。アクティブトレンチゲートが 3 つ以上並ぶ第 1 構造と、ダミートレンチゲートが 3 つ以上並ぶ第 2 構造が、交互に設けられた構成を採用することでアクティブトレンチゲートの隣接数を増やし、アクティブトレンチゲートとダミートレンチゲートの隣接密度を低下させることができるので、 C g e を低減することができる。その上で、第 1 構造におけるアクテ

ィブトレンチゲートの数よりも、第 2 構造におけるダミートレンチゲートの数を大きくすること(例えば 1 : 2 とすること)で、特に C g e を低下させることができる。なお、本発明の実施の形態 1 ではキャリア蓄積層 2 4 を形成したがこれに限定するものではなく、キャリア蓄積層 2 4 を形成しなくてもよい。

#### [0047]

図6は、本発明の実施の形態1に係る半導体素子のコレクタ電流と、還流ダイオードのリカバリdV/dtの関係を示す図である。実施の形態1の半導体素子では小さいCgeを実現しているので、Cgc/Cgeが大きくなり、還流ダイオードのリカバリdV/dtが半導体素子のコレクタ電流に依存することを抑制できている。図7は、ターンオン損失の低減効果を説明するグラフである。図7には、上記のとおりCgeを小さくすることで、ターンオン損失を低減できたことが示されている。

#### [0048]

本発明の実施の形態 1 に係る半導体素子によれば、定常損失(Vce(sat))を低減することができる。つまり、ベース層 2 2 のうち、ダミートレンチゲート D 1、 D 2 に挟まれた部分は、エミッタ電極 4 6 に接続されないので、フローティングベース層が形成される。フローティングベース層により I n j e c t i o n E n h a n c e m e n t 効果(IE効果)が促進される。フローティングベース層にはホールが蓄積し、伝導度変調が起こるため、ドリフト層 1 2 の比抵抗が低下しVce(sat)を低減できる。

#### [0049]

本発明の実施の形態 1 に係る半導体素子は、様々な変形が可能である。例えば半導体素子はIGBTを構成せず、トレンチMOSFET又はRC-IGBTを構成してもよい。半導体基板 1 0 はケイ素によって形成してもよいが、ケイ素に比べてバンドギャップが大きいワイドバンドギャップ半導体によって形成してもよい。ワイドバンドギャップ半導体としては、例えば、炭化珪素、窒化ガリウム系材料又はダイヤモンドがある。 n型の層は p型に置き換え、p型の層をn型に置き換えても良い。つまり、半導体基板の各層は第1 導電型か第 2 導電型で形成される。上述の各変形例については、以下の実施の形態に係る半導体素子については、実施の形態 1 との共通点が多いので実施の形態 1 との相違点を中心に説明する。

## [0050]

## 実施の形態2.

図8は、実施の形態2に係る半導体素子の一部断面図である。ベース層22のうち、ダミートレンチゲートD1に挟まれた部分は、エミッタ電極46に接続されている。つまり、エミッタコンタクト44をダミートレンチゲートD1の両側に設け、ダミートレンチゲートD1をエミッタコンタクト44で挟む。エミッタコンタクト44の下部にはコンタクト抵抗を低減させるためのp+型のコンタクト層20を形成してもよい。コンタクト層20のパターンは特定のパターンに限定されず、例えばエミッタコンタクト44の下部に選択的に形成してもよい。エミッタコンタクト44をダミートレンチゲートD1に挟まれた部分に設けることで、エミッタコンタクト44からのホールの排出を促進しターンオフ損失を低減することができる。

#### [0051]

特にダミートレンチゲートの本数が多くなると、フローティングベース層が形成されることによるIE効果によるVce(sat)の低減効果よりも、ターンオフ損失の増加が問題となる。そこで、図8に示すようにすべてのベース層22の上にエミッタコンタクト44を設けることで、ターンオフ損失を低減できる。

## [0052]

ここで、あるダミートレンチゲートD1の右側だけにエミッタコンタクト44を設け、そのダミートレンチゲートD1の左側にはエミッタコンタクト44を設けなくても良い。これによりホールの蓄積量を調整できる。あるいは、あるダミートレンチゲートD1の両側にはエミッタコンタクト44を設けるが、別のダミートレンチゲートD1については片側にだけエミッタコンタクト44を設けても良い。図9を参照しつつ説明すると、第2構

10

20

30

40

造62により、ダミートレンチゲートD1に挟まれたベース層22が2箇所以上あり、1箇所はエミッタ電極46に接続され、別の1箇所はエミッタ電極46に接続されない。こうすることで、ターンオフ損失とVce(sat)のトレードオフ特性を悪化させることなくターンオン損失を低減することができる。

## [0053]

実施の形態3.

図10は、実施の形態3に係る半導体素子の一部断面図である。ベース層22のうち、アクティブトレンチゲートに挟まれた部分だけに、エミッタ電極46(エミッタコンタクト44)が接続されている。アクティブトレンチゲートと、アクティブトレンチゲートとダミートレンチゲートの間にあるエミッタコンタクト44との間で発生するCgeを、エミッタコンタクト44を間引くことで低減する。

[0054]

アクティブトレンチゲートに隣接するフローティングベース層 2 2 ' はターンオン時に流入したホールにより電位が変動し変位電流を発生させるので、低電流時の d V / d t の増加につながる。したがって、上記のようにアクティブトレンチゲートが 3 つ以上並ぶ第 1 構造と、ダミートレンチゲートが 3 つ以上並ぶ第 2 構造を交互に設けることで当該フローティングベース層 2 2 ' の密度を低下させることが重要である。

[0055]

図11は、変形例に係る半導体素子の一部断面図である。ベース層22のうち、アクティブトレンチゲートに挟まれた部分と、ダミートレンチゲートに挟まれた部分だけにエミッタ電極46(エミッタコンタクト44)を接続する。アクティブトレンチゲートとダミートレンチゲートの間のベース層22にはエミッタコンタクト44を設けない。これにより、エミッタコンタクト44からのホールの排出を促進しつつ、Cgeを低減しターンオフ損失を低減できる。

[0056]

実施の形態4.

図12は、実施の形態4に係る半導体素子の一部断面図である。ベース層22は、アクティブトレンチゲートとダミートレンチゲートの間の領域を避けて形成されている。つまり、アクティブトレンチゲートA1とダミートレンチゲートD1の間にはベース層22が配置されない。これにより、アクティブトレンチゲートA1と、アクティブトレンチゲートA1とダミートレンチゲートD1の間のエミッタコンタクトの間で発生するCgeを削減することができる。

[0057]

上記のようにアクティブトレンチゲートが3つ以上並ぶ第1構造と、ダミートレンチゲートが3つ以上並ぶ第2構造を交互に設けることで、ベース層22が省略された部分(アクティブトレンチゲートとダミートレンチゲートの間の部分)の割合が減少していきベース層22の割合が増える。ベース層22は逆バイアス時に空乏層が伸びて耐圧を高める機能があるので、上述のようにベース層22の割合を増やすと耐圧を高めることができる。

[0058]

実施の形態5.

図13は、実施の形態5に係る半導体素子を構成する半導体基板の平面図である。アクティブトレンチゲートA1は横方向に3本伸びている。3本のアクティブトレンチゲートA1はそれらの短手方向に伸びるアクティブトレンチゲートによって接続され、アクティブトレンチゲートは平面視でメッシュ状になっている。ダミートレンチゲートD1は平面視でストライプ状に配置されている。なお、ダミートレンチゲートD1の形状はストライプ状に限定されずメッシュ状であってもよい。

[0059]

メッシュ状のアクティブトレンチゲートを形成することで、ゲート-エミッタ間に電圧を印加すると×正負方向だけでなく y 正負方向にも空乏層が広がり、広がった空乏層が互いに重なりあう。従って、空乏層の表面積 S は小さく、空乏層の距離 d は大きくなり、 C

10

20

30

40

g e を小さくすることができる。

## [0060]

第1構造を構成するアクティブトレンチゲートの数は3に限定されない。第1構造を構成する3つ以上のアクティブトレンチゲートを接続し平面視でメッシュ状の第1構造を形成することで、Cgeを小さくできる。

#### [0061]

実施の形態 6.

図14は、実施の形態6に係る半導体素子の一部断面斜視図である。ソース層18は、平行に伸びる複数のアクティブトレンチゲートA1,A2及び複数のダミートレンチゲートD1に対し交差する、第1ソース層18aと第2ソース層18bを有している。そして、第1ソース層18aと第2ソース層18bの間隔は一定ではない。つまり、ソース層の間隔が一定ではなく部分的に長くなるようにした。例えば、ソース層の間隔L4が1の場合、ソース層の間隔L5は10という比率である。

#### [0062]

このような構成にした場合、電子の注入効率がそれぞれのセルで変化する。ソース層の間隔が長いセルでは注入効率が小さくなり、閾値電圧Vthが高くなる。このため同一チップ内で、高Vthのセルと通常のVthのセルの二種類のセルが構成される。図14には、高Vthセル(High Vth セル)と通常のVthのセル(Ref Vth セル)が示されている。リカバリdV/dtはゲートエミッタ間電圧の時間変化dVge/dtに依存し、dVge/dtは閾値電圧Vthに依存する。ターンオン時においてdVge/dtが急増する場合はdV/dtも急増する。Vthの異なる二種類のセルを構成すると、それぞれのセルから出るdVge/dtの大きさは異なり、かつ位相がずれるため、チップとして見た場合、それぞれのセルから出たdVge/dtのピークが大きい箇所と小さい箇所が互い重なり合う。そのため、dVge/dtのピークは緩やかになる。その結果、リカバリdV/dtの電流依存性を小さくできる。更にdVge/dt波形のピークを小さくできるためEMIノイズを低減することも可能である。

#### [0063]

なお、上記の各実施の形態に係る半導体素子の特徴を適宜に組み合わせて、本発明の効果を高めても良い。

# 【符号の説明】

#### [0064]

10 半導体基板、 18 ソース層、 20 コンタクト層、 22 ベース層、 24 キャリア蓄積層、 46 エミッタ電極、 50 ゲート電極、 60,64 第1構造、 62,66 第2構造、 80 空乏層、 A1,A2 アクティブトレンチゲート、 D1,D2 ダミートレンチゲート

10

20

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図13】

【図12】

【図14】

# 【図15】

## フロントページの続き

(51) Int.CI. F I

H 0 1 L 29/78 6 5 2 C H 0 1 L 29/78 6 5 2 K H 0 1 L 29/78 6 5 2 B H 0 1 L 27/06 1 0 2 A H 0 1 L 29/78 6 5 2 T

(72)発明者 上馬場 龍

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 梅山 真理子

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 楢崎 敦司

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 多留谷 政良

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 杉山 芳弘

(56)参考文献 特開2015-072950(JP,A)

特開2008-205500(JP,A)

特開2015-103697(JP,A)

国際公開第2015/022989(WO,A1)

特開2004-228553(JP,A)

特開平10-321856(JP,A)

特開2006-005248(JP,A)

特開2007-324539(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 29/78

H01L 29/739

H01L 21/336