(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6421137号

(P6421137)

(45) 発行日 平成30年11月7日(2018.11.7)

(24) 登録日 平成30年10月19日(2018.10.19)

(51) Int.Cl.

H01G 4/30 (2006.01)

F 1

|      |      |      |

|------|------|------|

| H01G | 4/30 | 201H |

| H01G | 4/30 | 201F |

| H01G | 4/30 | 201C |

請求項の数 4 (全 17 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2016-61493 (P2016-61493)    |

| (22) 出願日  | 平成28年3月25日 (2016.3.25)        |

| (65) 公開番号 | 特開2017-175037 (P2017-175037A) |

| (43) 公開日  | 平成29年9月28日 (2017.9.28)        |

| 審査請求日     | 平成29年2月8日 (2017.2.8)          |

|           |                                           |

|-----------|-------------------------------------------|

| (73) 特許権者 | 000204284<br>太陽誘電株式会社<br>東京都中央区京橋二丁目7番19号 |

| (74) 代理人  | 100145517<br>弁理士 宮原 貴洋                    |

| (72) 発明者  | 加藤 洋一<br>東京都台東区上野6丁目16番20号 太陽誘電株式会社内      |

審査官 中野 和彦

最終頁に続く

(54) 【発明の名称】積層セラミックコンデンサ

## (57) 【特許請求の範囲】

## 【請求項 1】

直方体状のコンデンサ本体の高さ方向一面に矩形状の第1外部電極と矩形状の第2外部電極が設けられた積層セラミックコンデンサであって、

前記コンデンサ本体は、(1)誘電体層を介して交互に配された矩形状の複数の第1内部電極層と矩形状の複数の第2内部電極層とを内包する直方体状の容量素子と、(2)前記容量素子の長さ方向一面を覆う矩形状の第1導体層と、(3)前記容量素子の長さ方向他面を覆う矩形状の第2導体層と、(4)前記第1導体層の外面を覆う矩形状の第1被覆層と、(5)前記第2導体層の外面を覆う矩形状の第2被覆層と、を備えており、

前記第1導体層には、前記複数の第1内部電極層の長さ方向一端縁それぞれが接続され、前記第2導体層には、前記複数の第2内部電極層の長さ方向他端縁それぞれが接続され、前記第1外部電極には、前記第1導体層の高さ方向一端縁が接続され、前記第2外部電極には、前記第2導体層の高さ方向一端縁が接続されている、

積層セラミックコンデンサ。

## 【請求項 2】

前記第1導体層と前記第2導体層それぞれの厚さは、前記複数の第1内部電極層と前記複数の第2内部電極層それぞれの厚さの1~5倍の範囲内で設定されている、

請求項1に記載の積層セラミックコンデンサ。

## 【請求項 3】

前記第1被覆層と前記第2被覆層それぞれの厚さは、前記容量素子の前記誘電体層の厚

10

20

さの 1 ~ 10 倍の範囲内で設定されている、

請求項 1 又は 2 に記載の積層セラミックコンデンサ。

#### 【請求項 4】

前記第 1 導体層の前記第 1 外部電極に接続された一端縁を除く周縁は、前記第 1 被覆層の前記容量素子側に延びた部分によって覆われており、

前記第 2 導体層の前記第 2 外部電極に接続された一端縁を除く周縁は、前記第 2 被覆層の前記容量素子側に延びた部分によって覆われている、

請求項 1 ~ 3 の何れか 1 項に記載の積層セラミックコンデンサ。

#### 【発明の詳細な説明】

##### 【技術分野】

10

##### 【0001】

本発明は、略直方体状のコンデンサ本体の高さ方向一面に第 1 外部電極と第 2 外部電極が設けられた積層セラミックコンデンサに関する。

##### 【背景技術】

##### 【0002】

後記特許文献 1 の図 1 ~ 図 7 には、前掲に関連する積層セラミックコンデンサが開示されている。この積層セラミックコンデンサは、誘電体層を介して幅方向に交互に配された略矩形状の複数の第 1 内部電極層と略矩形状の複数の内部電極層とを内包した略直方体状のコンデンサ本体と、コンデンサ本体の高さ方向一面に設けられた略矩形状の第 1 外部電極と略矩形状の第 2 外部電極とを備えている。各第 1 内部電極層はコンデンサ本体の高さ方向一面に至る略矩形状の第 1 引出部を有していて、各第 1 引出部の端縁を第 1 外部電極に接続されている。各第 2 内部電極層はコンデンサ本体の高さ方向一面に至る略矩形状の第 2 引出部を有していて、各第 2 引出部の端縁を第 2 外部電極に接続されている。

20

##### 【0003】

前記積層セラミックコンデンサは、各第 1 内部電極層と各第 2 内部電極層が第 1 外部電極及び第 2 外部電極と略直角となる向きで配された構造であるため、各第 1 引出部の長さ方向寸法(幅)は各第 1 内部電極層の高さ方向寸法(幅)よりも狭くなり、且つ、各第 2 引出部の長さ方向寸法(幅)は各第 2 内部電極層の高さ方向寸法(幅)よりも狭くなる。依って、前記積層セラミックコンデンサにおいて小型化と大容量化の要求に応じようとすると、第 1 外部電極に対する各第 1 引出部の接続と第 2 外部電極に対する各第 2 引出部の接続が不安定になる懸念がある。

30

##### 【0004】

即ち、前記積層セラミックコンデンサにおいて小型化と大容量化の要求に応じるには、各第 1 内部電極層の高さ方向寸法(幅)及び長さ方向寸法と各第 2 内部電極層の高さ方向寸法(幅)及び長さ方向寸法の縮小が必要となるが、とりわけ長さ方向寸法の縮小に伴って各第 1 引出部の長さ方向寸法(幅)と各第 2 引出部の長さ方向寸法(幅)が極端に狭くなってしまうため、第 1 外部電極に対する各第 1 引出部の接続と第 2 外部電極に対する各第 2 引出部の接続が不安定になり易い。

##### 【先行技術文献】

##### 【特許文献】

40

##### 【0005】

##### 【特許文献 1】特開 2014 - 116571 号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0006】

本発明の課題は、略直方体状のコンデンサ本体の高さ方向一面に第 1 外部電極と第 2 外部電極が設けられた積層セラミックコンデンサにおいて小型化と大容量化の要求に応じる場合であっても、第 1 外部電極に対する各第 1 内部電極層の接続と第 2 外部電極に対する各第 2 内部電極層の接続のそれぞれに信頼性の高い接続を実現できる積層セラミックコンデンサを提供することにある。

50

**【課題を解決するための手段】****【0007】**

前記課題を解決するため、本発明に係る積層セラミックコンデンサは、略直方体状のコンデンサ本体の高さ方向一面に略矩形状の第1外部電極と略矩形状の第2外部電極が設けられた積層セラミックコンデンサであって、前記コンデンサ本体は、(1)誘電体層を介して交互に配された略矩形状の複数の第1内部電極層と略矩形状の複数の第2内部電極層とを内包する略直方体状の容量素子と、(2)前記容量素子の長さ方向一面を覆う第1導体層と、(3)前記容量素子の長さ方向他面を覆う第2導体層と、(4)前記第1導体層の外面を覆う第1被覆層と、(5)前記第2導体層の外面を覆う第2被覆層と、を備えており、前記第1導体層には、前記複数の第1内部電極層の長さ方向一端縁それぞれが前記複数の第1内部電極層それぞれの幅と同等の接続幅にて接続され、前記第2導体層には、前記複数の第2内部電極層の長さ方向他端縁それぞれが前記複数の第2内部電極層それぞれの幅と同等の接続幅にて接続され、前記第1外部電極には、前記第1導体層の高さ方向一端縁が前記第1導体層の幅と同等の接続幅にて接続され、前記第2外部電極には、前記第2導体層の高さ方向一端縁が前記第2導体層の幅と同等の接続幅にて接続されている。10

**【発明の効果】****【0008】**

本発明によれば、略直方体状のコンデンサ本体の高さ方向一面に第1外部電極と第2外部電極が設けられた積層セラミックコンデンサにおいて小型化と大容量化の要求に応じる場合であっても、第1外部電極に対する各第1内部電極層の接続と第2外部電極に対する各第2内部電極層の接続のそれに信頼性の高い接続を実現できる積層セラミックコンデンサを提供することができる。20

**【図面の簡単な説明】****【0009】**

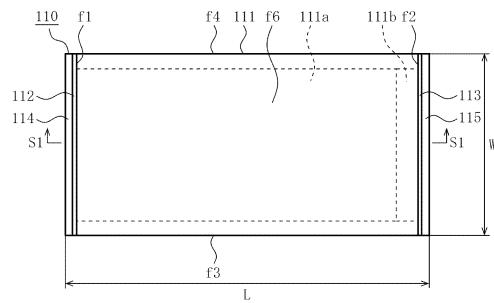

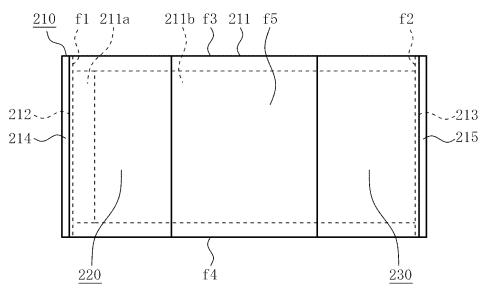

【図1】図1は本発明の第1実施形態に係る積層セラミックコンデンサを容量素子の第6面f6側から見た図である。

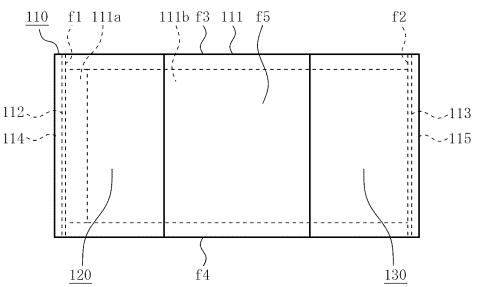

【図2】図2は図1に示した積層セラミックコンデンサを容量素子の第3面f3側から見た図である。

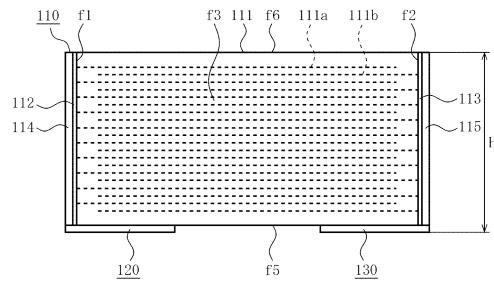

【図3】図3は図1に示した積層セラミックコンデンサを容量素子の第5面f5側から見た図である。30

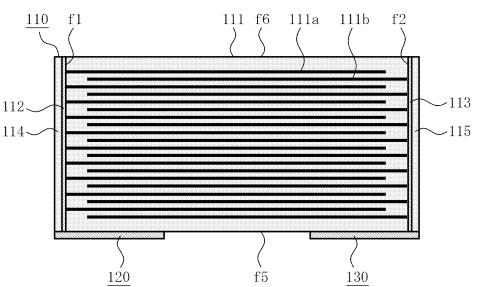

【図4】図4は図1のS1-S1線に沿う断面図である。

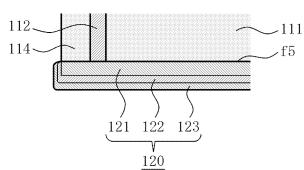

【図5】図5は図4の部分拡大図である。

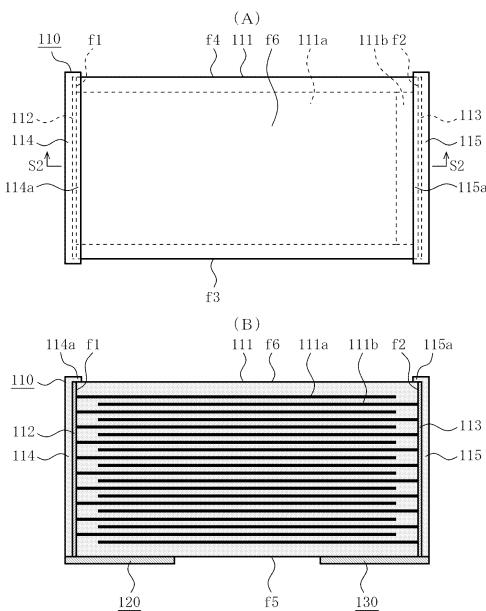

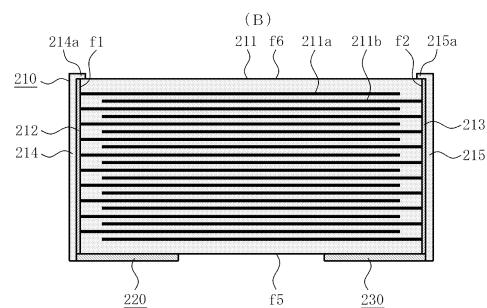

【図6】図6(A)は図1に示した積層セラミックコンデンサの第1変形例を示す図1対応図、図6(B)は図6(A)のS2-S2線に沿う断面図である。

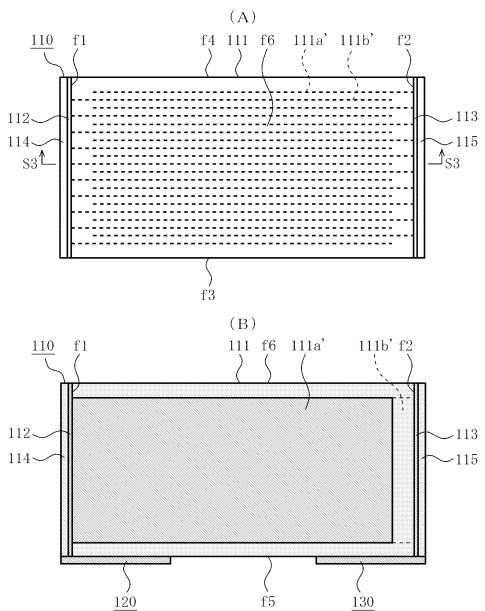

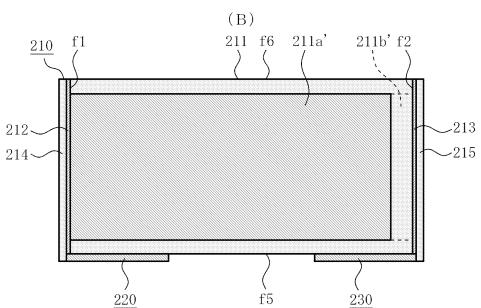

【図7】図7(A)は図1に示した積層セラミックコンデンサの第2変形例を示す図1対応図、図7(B)は図7(A)のS3-S3線に沿う断面図である。

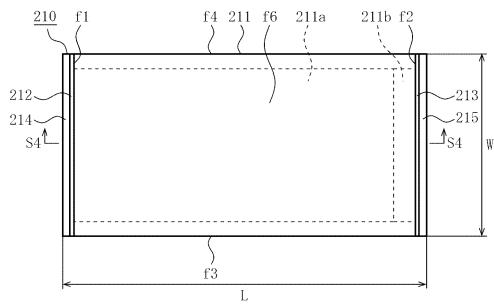

【図8】図8は本発明の第2実施形態に係る積層セラミックコンデンサを容量素子の第6面f6側から見た図である。

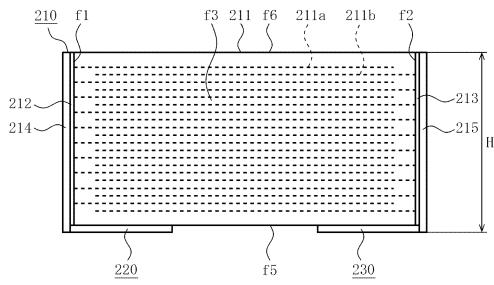

【図9】図9は図8に示した積層セラミックコンデンサを容量素子の第3面f3側から見た図である。40

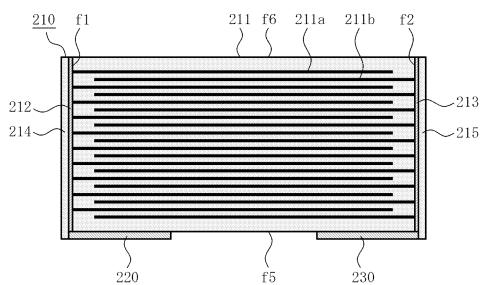

【図10】図10は図8に示した積層セラミックコンデンサを容量素子の第5面f5側から見た図である。

【図11】図11は図8のS4-S4線に沿う断面図である。

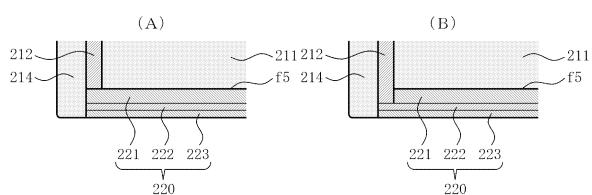

【図12】図12(A)は図11の部分拡大図、図12(B)は図12(A)と外部電極の下地膜の態様が異なる場合を示す図12(A)対応図である。

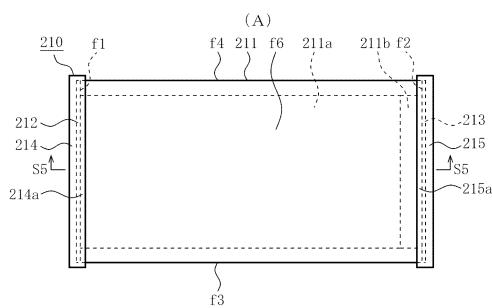

【図13】図13(A)は図8に示した積層セラミックコンデンサの第1変形例を示す図8対応図、図13(B)は図13(A)のS5-S5線に沿う断面図である。

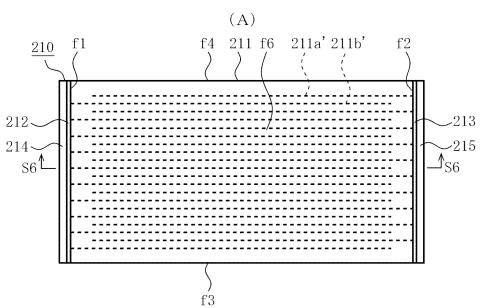

【図14】図14(A)は図8に示した積層セラミックコンデンサの第2変形例を示す図8対応図、図14(B)は図14(A)のS6-S6線に沿う断面図である。

**【発明を実施するための形態】**

10

20

30

40

50

## 【0010】

## 《第1実施形態》

先ず、図1～図5を用いて、本発明の第1実施形態に係る積層セラミックコンデンサの構造について説明する。この説明では、図1の左右方向を長さ方向と言い、図1の上下方向を幅方向と言い、図2の上下方向を高さ方向と言うと共に、各構成要素の長さ方向、幅方向及び高さ方向それぞれに沿う寸法を長さ、幅及び高さと言う。

## 【0011】

この積層セラミックコンデンサは、略直方体状のコンデンサ本体110と、コンデンサ本体110の高さ方向一面に設けられた略矩形状の第1外部電極120と略矩形状の第2外部電極130とを備えている、全体寸法が長さLと幅Wと高さHによって規定されている。ちなみに、図1～5に示した積層セラミックコンデンサの長さLと幅Wと高さHは、例えば1000μmと500μmと500μmや、600μmと300μmと300μmである。なお、図1～図5には、長さLと幅Wと高さHそれぞれが長さL>幅W=高さHである積層セラミックコンデンサを描いているが、これら長さLと幅Wと高さHの関係は長さL>幅W>高さHや、長さL>高さH>幅Wの他、幅W>長さL=高さHや、幅W>長さL>高さHや、幅W>高さH>長さLであってもよい。

## 【0012】

コンデンサ本体110は、容量素子111と、第1導体層112と、第2導体層113と、第1被覆層114と、第2被覆層115と、によって構成されている。

## 【0013】

容量素子111は、略直方体状を成していて、長さ方向で向き合う第1面f1及び第2面f2と、幅方向で向き合う第3面f3及び第4面f4と、高さ方向で向き合う第5面f5及び第6面f6とを有している。また、容量素子111は、誘電体層(符号省略)を介して高さ方向に交互に配された略矩形状の複数の第1内部電極層111aと略矩形状の複数の第2内部電極層111bを内包している。各第1内部電極層111aの幅、長さ及び厚さと各第2内部電極層111bの幅、長さ及び厚さは略同じであり、各誘電体層の厚さは略同じである。ちなみに、各第1内部電極層111aの厚さと各第2内部電極層111bの厚さは、例えば0.5～2μmの範囲内で設定されており、各誘電体層の厚さは、例えば0.5～2μmの範囲内で設定されている。なお、図1～図5には、第1内部電極層111aと第2内部電極層111bそれぞれを10層ずつ描いているが、これらは図示の都合によるものであって、第1内部電極層111aと第2内部電極層111bの数は11層以上であってもよい。

## 【0014】

容量素子111の各第1内部電極層111aと各第2内部電極層111bを除く部分には、チタン酸バリウム、チタン酸ストロンチウム、チタン酸カルシウム、チタン酸マグネシウム、ジルコン酸カルシウム、チタン酸ジルコン酸カルシウム、ジルコン酸バリウム、酸化チタン等を主成分とした誘電体セラミックス、好ましくは比誘電率が1000以上の高誘電率系誘電体セラミックスが使用できる。また、各第1内部電極層111aと各第2内部電極層111bには、ニッケル、銅、パラジウム、白金、銀、金、これらの合金等を主成分した良導体が使用できる。

## 【0015】

第1導体層112は、略矩形状を成していて、容量素子111の第1面f1を密着状態で覆っている。第1導体層112の幅及び高さは、第1面f1の幅及び高さと略同じである。第1導体層112の厚さは、コンデンサ本体110の長さに関与することから極力薄い方が望ましい。ちなみに、第1導体層112の厚さは、例えば第1内部電極層111aの厚さの1～5倍の範囲内で設定されており、好ましくは0.5～5μmの範囲内で設定されている。また、第1導体層112には、ニッケル、銅、パラジウム、白金、銀、金、これらの合金等を主成分した良導体が使用でき、好ましくは第1内部電極層111aの主成分と同じ主成分の良導体が使用できる。この第1導体層112には、各第1内部電極層111aの長さ方向一端縁が各第1内部電極層111aの幅と同等の接続幅にて接続され

10

20

30

40

50

ている。なお、第1導体層1112に対する各第1内部電極層111aの長さ方向一端縁の接続幅は理想的には各第1内部電極層111aの幅となるが、実際のものでは各第1内部電極層111aの長さ方向一端縁の幅に各第1内部電極層111aの幅の±5%程度の変動が確認できたため、ここでは敢えて「各第1内部電極層111aの幅と同じ接続幅」と表現せずに「各第1内部電極層111aの幅と同等の接続幅」と表現している。

#### 【0016】

第2導体層113は、略矩形状を成していて、容量素子111の第2面f2を密着状態で覆っている。第2導体層113の幅及び高さは、第2面f2の幅及び高さと略同じである。第2導体層113の厚さは、コンデンサ本体110の長さに関与することから極力薄い方が望ましい。ちなみに、第2導体層113の厚さは、例えば第2内部電極層111bの厚さの1~5倍の範囲内で設定されており、好ましくは0.5~5μmの範囲内で設定されている。また、第2導体層113には、ニッケル、銅、パラジウム、白金、銀、金、これらの合金等を主成分した良導体が使用でき、好ましくは第2内部電極層111bの主成分と同じ主成分の良導体が使用できる。この第2導体層113には、各第2内部電極層111bの長さ方向他端縁が各第2内部電極層111bの幅と同等の接続幅にて接続されている。なお、第2導体層113に対する各第2内部電極層111bの長さ方向他端縁の接続幅は理想的には各第2内部電極層111bの幅となるが、実際のものでは各第2内部電極層111bの長さ方向一端縁の幅に各第2内部電極層111bの幅の±5%程度の変動が確認できたため、ここでは敢えて「各第2内部電極層111bの幅と同じ接続幅」と表現せずに「各第2内部電極層111bの幅と同等の接続幅」と表現している。

10

#### 【0017】

第1被覆層114は、略矩形状を成していて、第1導体層112の外面を密着状態で覆っている。第1被覆層114の幅及び高さは、第1導体層112の外面の幅及び高さと略同じである。第1被覆層114の厚さは、コンデンサ本体110の長さに関与することから極力薄い方が望ましい。ちなみに、第1被覆層114の厚さは、例えば第1内部電極層111aと第2内部電極層111bとの間に介在する誘電体層の厚さの1~10倍の範囲内で設定されており、好ましくは1~10μmの範囲内で設定されている。また、第1被覆層114には、チタン酸バリウム、チタン酸ストロンチウム、チタン酸カルシウム、チタン酸マグネシウム、ジルコン酸カルシウム、チタン酸ジルコン酸カルシウム、ジルコン酸バリウム、酸化チタン等を主成分とした誘電体セラミックス、好ましくは比誘電率が1000以上の高誘電率系誘電体セラミックス、より好ましくは容量素子111の第1内部電極層111aと第2内部電極層111bを除く部分の主成分と同じ主成分の誘電体セラミックスが使用できる。

20

#### 【0018】

第2被覆層115は、略矩形状を成していて、第2導体層113の外面を密着状態で覆っている。第2被覆層115の幅及び高さは、第2導体層113の外面の幅及び高さと略同じである。第2被覆層115の厚さは、コンデンサ本体110の長さに関与することから極力薄い方が望ましい。ちなみに、第2被覆層115の厚さは、例えば第1内部電極層111aと第2内部電極層111bとの間に介在する誘電体層の厚さの1~10倍の範囲内で設定されており、好ましくは1~10μmの範囲内で設定されており、より好ましくは第1被覆層114の厚さと略同じである。また、第2被覆層115には、チタン酸バリウム、チタン酸ストロンチウム、チタン酸カルシウム、チタン酸マグネシウム、ジルコン酸カルシウム、チタン酸ジルコン酸カルシウム、ジルコン酸バリウム、酸化チタン等を主成分とした誘電体セラミックス、好ましくは比誘電率が1000以上の高誘電率系誘電体セラミックス、より好ましくは容量素子111の第1内部電極層111aと第2内部電極層111bを除く部分の主成分と同じ主成分の誘電体セラミックスが使用できる。

30

#### 【0019】

第1外部電極120は、略矩形状を成していて、コンデンサ本体110の高さ方向一面に相当する容量素子111の第5面f5の第1被覆層114側に密着状態で設けられている。第1外部電極120の幅は容量素子111の第5面f5の幅と略同じであり、長さは

40

50

例えば積層セラミックコンデンサの長さ L の  $1/8 \sim 1/3$  の範囲内で設定されており、厚さは例えば  $1 \sim 15 \mu\text{m}$  の範囲内で設定されている。また、第 1 外部電極 120 の長さ方向一端縁は、第 1 被覆層 114 の外面下まで達している。この第 1 外部電極 120 には、第 1 導体層 112 の高さ方向一端縁が第 1 導体層 112 の幅と同等の接続幅にて接続されている。なお、第 1 外部電極 120 に対する第 1 導体層 112 の高さ方向一端縁の接続幅は理想的には第 1 導体層 112 の幅となるが、実際のものでは第 1 導体層 112 の高さ方向一端縁の幅に第 1 導体層 112 の幅の  $\pm 5\%$  程度の変動が確認できたため、ここでは敢えて「第 1 導体層 112 の幅と同じ接続幅」と表現せずに「第 1 導体層 112 の幅と同等の接続幅」と表現している。

## 【0020】

10

第 2 外部電極 130 は、略矩形状を成していて、コンデンサ本体 110 の高さ方向一面に相当する容量素子 111 の第 5 面 f5 の第 2 被覆層 115 側に密着状態で設けられている。第 2 外部電極 130 の幅は容量素子 111 の第 5 面 f5 の幅と略同じであり、長さは例えば積層セラミックコンデンサの長さ L の  $1/8 \sim 1/3$  の範囲内で設定されており、厚さは例えば  $1 \sim 15 \mu\text{m}$  の範囲内で設定されている。また、第 2 外部電極 130 の長さ方向他端縁は、第 2 被覆層 115 の外面下まで達している。この第 2 外部電極 130 には、第 2 導体層 113 の高さ方向一端縁が第 2 導体層 113 の幅と同等の接続幅にて接続されている。なお、第 2 外部電極 130 に対する第 2 導体層 113 の高さ方向一端縁の接続幅は理想的には第 2 導体層 113 の幅となるが、実際のものでは第 2 導体層 113 の高さ方向一端縁の幅に第 2 導体層 113 の幅の  $\pm 5\%$  程度の変動が確認できたため、ここでは敢えて「第 2 導体層 113 の幅と同じ接続幅」と表現せずに「第 2 導体層 113 の幅と同等の接続幅」と表現している。

20

## 【0021】

ここで、図 5 を用いて、第 1 外部電極 120 と第 2 外部電極 130 の態様について補足する。なお、図 5 には第 1 外部電極 120 のみを描いているが、第 2 外部電極 130 も図 5 と同様の態様を有している。

## 【0022】

30

図 5 に示した第 1 外部電極 120 は、主として容量素子 111 の第 5 面 f5 に密着した下地膜 121 と、下地膜 121 の外面に密着した中間膜 122 と、中間膜 122 の外面に密着した表面膜 123 とを有する 3 層構造である。なお、第 1 外部電極 120 と第 2 外部電極 130 は必ずしも 3 層構造である必要はなく、中間膜 (122) を除外した 2 層構造や、中間膜 (122) を 2 層以上とした多層構造や、表面膜 (123) のみとした単層構造であってもよい。

## 【0023】

40

3 層構造の場合を例に挙げて説明すれば、下地膜 (121) は例えば焼き付け膜からなり、この焼き付け膜には好ましくはニッケル、銅、パラジウム、白金、銀、金、これらの合金等を主成分した良導体が使用できる。中間膜 (122) は例えばメッキ膜からなり、このメッキ膜には好ましくは白金、パラジウム、金、銅、ニッケル、これらの合金等を主成分とした良導体が使用できる。表面膜 (123) は例えばメッキ膜からなり、このメッキ膜には好ましくは銅、スズ、パラジウム、金、亜鉛、これらの合金等を主成分とした良導体が使用できる。

## 【0024】

次に、前述の積層セラミックコンデンサに適した製造方法の例を、図 1 ~ 図 5 に示した符号等を適宜用いて説明する。

## 【0025】

製造に際しては、誘電体セラミックス粉末、有機バインダ、有機溶剤及び各種添加剤を含有したセラミックスラリーと、良導体粉末、有機バインダ、有機溶剤及び各種添加剤を含有した電極ペーストを用意する。

## 【0026】

続いて、キャリアフィルムの表面にセラミックスラリーを塗工して乾燥することにより

50

、第1シートを作製する。また、この第1シートの表面に電極ペーストを印刷して乾燥することにより、内部電極層パターン群が形成された第2シートを作製する。

#### 【0027】

続いて、第1シートから取り出した単位シートを所定枚数に達するまで積み重ねて熱圧着する作業を繰り返すことにより、容量素子111の高さ方向一方のマージン部分に対応する部位を形成する。続いて、第2シートから取り出した単位シート（内部電極層パターン群を含む）を所定枚数に達するまで積み重ねて熱圧着する作業を繰り返すことにより、容量素子111の第1内部電極層111a及び第2内部電極層111bが存在する部分に対応する部位を形成する。続いて、第1シートから取り出した単位シートを所定枚数に達するまで積み重ねて熱圧着する作業を繰り返すことにより、容量素子111の高さ方向他方のマージン部分に対応する部位を形成する。最後に、積み重ねられた全体を本熱圧着することにより、未焼成シートを作製する。

#### 【0028】

続いて、未焼成シートを格子状に切断することにより、容量素子111に対応した未焼成素子を作製する。続いて、多数の未焼成素子の向きを揃えてから、各未焼成素子の長さ方向一面に第1導体層112に対応した未焼成導体層と第1被覆層114に対応した未焼成被覆層を作製すると共に、これらを反転させてから、各未焼成素子の長さ方向他面に第2導体層113に対応した未焼成導体層と第2被覆層115に対応した未焼成被覆層を作製する。これにより、コンデンサ本体110に対応した未焼成本体が作製される。

#### 【0029】

未焼成導体層と未焼成被覆層の作製方法としては、（w1）未焼成素子の長さ方向両面それぞれに導体層用ペーストを塗布、ディップ又は印刷して乾燥した後に、これに別途用意しておいた誘電体層用シートを押し付けて貼り付ける方法、（w2）別途用意しておいた誘電体層用シートに導体ペーストを塗布又は印刷して乾燥したもの未焼成素子の長さ方向両面それぞれに押し付けて貼り付ける方法、（w3）未焼成素子の長さ方向両面それぞれに導体層用ペーストを塗布、ディップ又は印刷して乾燥した後に、これに誘電体層用スラリーを塗布、ディップ又は印刷して乾燥する方法、が好ましく採用できる。

#### 【0030】

前記の導体層用ペーストには、前記電極ペーストと同じペーストの他、前記電極ペーストと良導体粉末の種類が異なるペーストや、良導体粉末と有機バインダと有機溶剤のみを含むペーストを使用できる。また、前記の誘電体層用シートには、前記セラミックスラリーと同じスラリーを塗工して乾燥したシートの他、前記セラミックスラリーと誘電体セラミック粉末の種類が異なるスラリーを塗工して乾燥したシートを使用できる。さらに、前記の誘電体層用スラリーには、前記セラミックスラリーと同じスラリーの他、前記セラミックスラリーと誘電体セラミック粉末の種類が異なるスラリーを使用できる。

#### 【0031】

続いて、未焼成本体をこれに含まれている誘電体セラミックス粉末と良導体粉末に応じた雰囲気下、並びに、温度プロファイルにて多数個一括で焼成（脱バインダ処理と焼成処理を含む）を行い、必要に応じて多数個一括でバレル研磨を行う。これにより、コンデンサ本体110が作製される。

#### 【0032】

続いて、多数のコンデンサ本体110の向きを揃えてから、各コンデンサ本体110の高さ方向一面に電極ペースト（前記電極ペーストと同じペースト、或いは、前記電極ペーストと良導体粉末の種類が異なる別のペースト）を塗布又は印刷して乾燥した後、焼き付け処理を行って下地膜（121）を形成する。続いて、下地膜（121）を覆う中間膜（122）と表面膜（123）をメッキ処理で形成して、第1外部電極120と第2外部電極130を作製する。

#### 【0033】

次に、前述の積層セラミックコンデンサによって得られる効果（効果e1～効果e3）について説明する。

10

20

30

40

50

## 【0034】

(e1) コンデンサ本体110が、(1) 誘電体層を介して交互に配された略矩形状の複数の第1内部電極層111aと略矩形状の複数の第2内部電極層111bとを内包する略直方体状の容量素子111と、(2) 容量素子111の長さ方向一面を覆う第1導体層112と、(3) 容量素子111の長さ方向他面を覆う第2導体層113と、(4) 第1導体層112の外面を覆う第1被覆層114と、(5) 第2導体層113の外面を覆う第2被覆層115と、によって構成されている。また、第1導体層112には複数の第1内部電極層111aの長さ方向一端縁それが複数の第1内部電極層111aそれぞれの幅と同等の接続幅にて接続され、第2導体層113には複数の第2内部電極層111bの長さ方向他端縁それが複数の第2内部電極層111bそれぞれの幅と同等の接続幅にて接続され、第1外部電極120には第1導体層112の高さ方向一端縁が第1導体層112の幅と同等の接続幅にて接続され、前記第2外部電極130には第2導体層113の高さ方向一端縁が第2導体層113の幅と同等の接続幅にて接続されている。

10

## 【0035】

即ち、コンデンサ本体110に、各第1内部電極層111aを各々の幅を活かして第1外部電極120に接続する役目を果たす第1導体層112と、各第2内部電極層111bを各々の幅を活かして第2外部電極130に接続する役目を果たす第2導体層113が設けられているため、各第1内部電極層111aの幅及び長さと各第2内部電極層111bの幅及び長さが縮小されても、第1外部電極120に対する各第1内部電極層111aの接続と第2外部電極130に対する各第2内部電極層111bの接続が不安定になることを極力回避することができる。依って、略直方体状のコンデンサ本体110の高さ方向一面に第1外部電極120と第2外部電極130が設けられた積層セラミックコンデンサにおいて小型化と大容量化の要求に応じる場合であっても、第1外部電極120に対する各第1内部電極層111aの接続と第2外部電極130に対する各第2内部電極層111bの接続のそれぞれに信頼性の高い接続を実現できる。

20

## 【0036】

(e2) コンデンサ本体110の第1導体層112と第2導体層113それぞれの厚さが、複数の第1内部電極層111aと複数の第2内部電極層111bそれぞれの厚さの1~5倍の範囲内で設定されているので、第1導体層112と第2導体層113それぞれの厚さによって積層セラミックコンデンサの長さLが増加することを極力回避することができる。

30

## 【0037】

(e3) コンデンサ本体110の第1被覆層114と第2被覆層115それぞれの厚さが、容量素子111の誘電体層の厚さの1~10倍の範囲内で設定されているので、第1被覆層114と第2被覆層115それぞれの厚さによって積層セラミックコンデンサの長さLが増加することを極力回避することができる。

## 【0038】

次に、前述の積層セラミックコンデンサの変形例(第1変形例m1~第4変形例m4)について説明する。

40

## 【0039】

(m1) 図6(A)及び図6(B)に示したように、第1導体層112の第1外部電極120に接続された一端縁を除く周縁を、第1被覆層114の容量素子111側に延びた部分114aによって覆うと共に、第2導体層113の第2外部電極130に接続された一端縁を除く周縁を、第2被覆層115の容量素子111側に延びた部分115aによって覆うようにしてもよい。このようにすれば、回路基板に実装するときに積層セラミックコンデンサが倒れても、第1導体層112と第2導体層113が回路基板の導体ラインや隣接する電子部品等に接触してショート等の問題を生じることを防げる、といった別の効果を得ることができる。

## 【0040】

(m2) 図7(A)及び図7(B)に示したように、容量素子111に、誘電体層(符

50

号省略)を介して幅方向に配された略矩形状の複数の第1内部電極層111a'、と略矩形状の複数の第2内部電極層111b'を内包させるようにしてもよい。このようにすると、各第1内部電極層111a'の向きと各第2内部電極層111b'の向きが第1外部電極120及び第2外部電極130と略直角になるが、前記同様の効果e1~効果e3を得ることができる。

#### 【0041】

(m3)先の製法例で述べた未焼成被覆層にMgO等の酸化促進剤を0.1~10at%程度含有させておけば、後の焼成工程で作製される第1導体層112の主として第1被覆層114との境界部分、並びに、第2導体層113の主として第2被覆層115との境界部分に金属酸化物を散在させて、この金属酸化物によって第1導体層112に対する第1被覆層114の密着性と第2導体層113に対する第2被覆層115の密着性を高めることができる。

10

#### 【0042】

(m4)先の製法例で述べた未焼成導体層に容量素子111の第1内部電極層111aと第2内部電極層111bを除く部分の主成分と同じ誘電体セラミック粉末を5~50wt%程度含有させておけば、容量素子111に対する第1導体層112の密着性と容量素子111に対する第2導体層113の密着性を高めることができる。

#### 【0043】

##### 《第2実施形態》

先ず、図8~図12を用いて、本発明の第2実施形態に係る積層セラミックコンデンサの構造について説明する。なお、第2実施形態に係る積層セラミックコンデンサの容量素子211(第1内部電極層211a、第2内部電極層211b及び誘電体層を含む)の構成は、第1実施形態に係る積層セラミックコンデンサの容量素子111(第1内部電極層111a、第2内部電極層111b及び誘電体層を含む)の構成と同じであるため、ここでは第2実施形態に係る積層セラミックコンデンサが第1実施形態に係る積層セラミックコンデンサと構造上で相違する点を主として説明する。

20

#### 【0044】

この積層セラミックコンデンサは、略直方体状のコンデンサ本体210と、コンデンサ本体210の高さ方向一面に設けられた略矩形状の第1外部電極220と略矩形状の第2外部電極230とを備えていて、全体寸法が長さLと幅Wと高さHによって規定されている。コンデンサ本体210は、略直方体状の容量素子211と、第1導体層212と、第2導体層213と、第2被覆層214と、第2被覆層215と、によって構成されている。

30

#### 【0045】

第1導体層212は、略矩形状を成していて、容量素子211の第1面f1を密着状態で覆っている。第1導体層212の幅及び高さは、第1面f1の幅及び高さと略同じである。第1導体層212の厚さは、コンデンサ本体210の長さに関与することから極力薄い方が望ましい。ちなみに、第1導体層212の厚さは、例えば第1内部電極層111aの厚さの1~5倍の範囲内で設定されており、好ましくは0.5~5μmの範囲内で設定されている。また、第1導体層212には、ニッケル、銅、パラジウム、白金、銀、金、これらの合金等を主成分した良導体が使用でき、好ましくは第1内部電極層211aの主成分と同じ主成分の良導体が使用できる。この第1導体層212には、各第1内部電極層211aの長さ方向一端縁が各第1内部電極層211aの幅と同等の接続幅にて接続されている。なお、第1導体層212に対する各第1内部電極層211aの長さ方向一端縁の接続幅は理想的には各第1内部電極層211aの幅となるが、実際のものでは各第1内部電極層211aの長さ方向一端縁の幅に各第1内部電極層211aの幅の±5%程度の変動が確認できたため、ここでは敢えて「各第1内部電極層211aの幅と同じ接続幅」と表現せずに「各第1内部電極層211aの幅と同等の接続幅」と表現している。

40

#### 【0046】

第2導体層213は、略矩形状を成していて、容量素子211の第2面f2を密着状態

10

20

30

40

50

で覆っている。第2導体層213の幅及び高さは、第2面f2の幅及び高さと略同じである。第2導体層213の厚さは、コンデンサ本体210の長さに関与することから極力薄い方が望ましい。ちなみに、第2導体層213の厚さは、例えば第2内部電極層211bの厚さの1~5倍の範囲内で設定されており、好ましくは0.5~5μmの範囲内で設定されている。また、第2導体層213には、ニッケル、銅、パラジウム、白金、銀、金、これらの合金等を主成分した良導体が使用でき、好ましくは第2内部電極層211bの主成分と同じ主成分の良導体が使用できる。この第2導体層213には、各第2内部電極層211bの長さ方向他端縁が各第2内部電極層211bの幅と同等の接続幅にて接続されている。なお、第2導体層213に対する各第2内部電極層211bの長さ方向他端縁の接続幅は理想的には各第2内部電極層211bの幅となるが、実際のものでは各第2内部電極層211bの長さ方向他端縁の幅に各第1内部電極層211aの幅の±5%程度の変動が確認できたため、ここでは敢えて「各第2内部電極層211bの幅と同じ接続幅」と表現せずに「各第2内部電極層211bの幅と同等の接続幅」と表現している。10

#### 【0047】

第1被覆層214は、略矩形状を成していて、第1導体層212の外面を密着状態で覆っている。第1被覆層214の幅は第1導体層212の外面の幅と略同じで、高さは第1導体層212の外面の高さよりも僅かに大きく、且つ、大きくなっている部分を第1外部電極220側に突出している。第1被覆層214の厚さは、コンデンサ本体210の長さに関与することから極力薄い方が望ましい。ちなみに、第1被覆層214の厚さは、例えば第1内部電極層111aと第2内部電極層111bとの間に介在する誘電体層の厚さの1~10倍の範囲内で設定されており、好ましくは1~10μmの範囲内で設定されている。また、第1被覆層214には、チタン酸バリウム、チタン酸ストロンチウム、チタン酸カルシウム、チタン酸マグネシウム、ジルコン酸カルシウム、チタン酸ジルコン酸カルシウム、ジルコン酸バリウム、酸化チタン等を主成分とした誘電体セラミックス、好ましくは比誘電率が1000以上の高誘電率系誘電体セラミックス、より好ましくは容量素子211の第1内部電極層211aと第2内部電極層211bを除く部分の主成分と同じ主成分の誘電体セラミックスが使用できる。20

#### 【0048】

第2被覆層215は、略矩形状を成していて、第2導体層213の外面を密着状態で覆っている。第2被覆層215の幅は第2導体層213の外面の幅と略同じで、高さは第2導体層213の外面の高さよりも僅かに大きく、且つ、大きくなっている部分を第2外部電極230側に突出している。第2被覆層215の厚さは、コンデンサ本体210の長さに関与することから極力薄い方が望ましい。ちなみに、第2被覆層215の厚さは、例えば第1内部電極層111aと第2内部電極層111bとの間に介在する誘電体層の厚さの1~10倍の範囲内で設定されており、好ましくは1~10μmの範囲内で設定されており、より好ましくは第1被覆層214の厚さと略同じである。また、第2被覆層215には、チタン酸バリウム、チタン酸ストロンチウム、チタン酸カルシウム、チタン酸マグネシウム、ジルコン酸カルシウム、チタン酸ジルコン酸カルシウム、ジルコン酸バリウム、酸化チタン等を主成分とした誘電体セラミックス、好ましくは比誘電率が1000以上の高誘電率系誘電体セラミックス、より好ましくは容量素子211の第1内部電極層211aと第2内部電極層211bを除く部分の主成分と同じ主成分の誘電体セラミックスが使用できる。3040

#### 【0049】

第1外部電極220は、略矩形状を成していて、コンデンサ本体210の高さ方向一面に相当する容量素子211の第5面f5の第1被覆層214側に密着状態で設けられている。第1外部電極230の幅は容量素子211の第5面f5の幅と略同じであり、長さは例えば積層セラミックコンデンサの長さLの1/8~1/3の範囲内で設定されており、厚さは例えば1~15μmの範囲内で設定されている。また、第1外部電極220の長さ方向一端縁は、第1被覆層214の内面下まで達していて、第1被覆層214の高さ方向一端部(第1外部電極220側に突出した部分)の内面に密着している。この第1外部電50

極 220 には、第 1 導体層 212 の高さ方向一端縁が第 1 導体層 212 の幅と同等の接続幅にて接続されている。なお、第 1 外部電極 220 に対する第 1 導体層 212 の高さ方向一端縁の接続幅は理想的には第 1 導体層 212 の幅となるが、実際のものでは第 1 導体層 212 の高さ方向一端縁の幅に第 1 導体層 212 の幅の ± 5 % 程度の変動が確認できたため、ここでは敢えて「第 1 導体層 212 の幅と同じ接続幅」と表現せずに「第 1 導体層 212 の幅と同等の接続幅」と表現している。

#### 【0050】

第 2 外部電極 230 は、略矩形状を成していて、コンデンサ本体 210 の高さ方向一面に相当する容量素子 211 の第 5 面 f5 の第 2 被覆層 215 側に密着状態で設けられている。第 2 外部電極 230 の幅は容量素子 211 の第 5 面 f5 の幅と略同じであり、長さは例えば積層セラミックコンデンサの長さ L の 1/8 ~ 1/3 の範囲内で設定されており、厚さは例えば 1 ~ 15 μm の範囲内で設定されている。また、第 2 外部電極 230 の長さ方向他端縁は、第 2 被覆層 215 の内面下まで達していて、第 2 被覆層 215 の高さ方向一端部（第 1 外部電極 230 側に突出した部分）の内面に密着している。この第 2 外部電極 230 には、第 2 導体層 213 の高さ方向一端縁が第 2 導体層 213 の幅と同等の接続幅にて接続されている。なお、第 2 外部電極 230 に対する第 2 導体層 213 の高さ方向一端縁の接続幅は理想的には第 2 導体層 213 の幅となるが、実際のものでは第 2 導体層 213 の高さ方向一端縁の幅に第 2 導体層 213 の幅の ± 5 % 程度の変動が確認できたため、ここでは敢えて「第 2 導体層 213 の幅と同じ接続幅」と表現せずに「第 2 導体層 213 の幅と同等の接続幅」と表現している。

10

#### 【0051】

ここで、図 12 (A) を用いて、第 1 外部電極 220 と第 2 外部電極 230 の態様について補足する。なお、図 12 (A) には第 1 外部電極 220 のみを描いているが、第 2 外部電極 230 も図 12 (A) と同様の態様を有している。

20

#### 【0052】

図 12 (A) に示した第 1 外部電極 220 は、主として容量素子 211 の第 5 面 f5 に密着した下地膜 221 と、下地膜 221 の外面に密着した中間膜 222 と、中間膜 222 の外面に密着した表面膜 223 とを有する 3 層構造である。なお、第 1 外部電極 220 と第 2 外部電極 230 は必ずしも 3 層構造である必要はなく、中間膜 (222) を除外した 2 層構造や、中間膜 (222) を 2 層以上とした多層構造や、表面膜 (223) のみとした単層構造であってもよい。

30

#### 【0053】

3 層構造の場合を例に挙げて説明すれば、下地膜 (221) は例えば焼き付け膜からなり、この焼き付け膜には好ましくはニッケル、銅、パラジウム、白金、銀、金、これらの合金等を主成分した良導体が使用できる。中間膜 (222) は例えばメッキ膜からなり、このメッキ膜には好ましくは白金、パラジウム、金、銅、ニッケル、これらの合金等を主成分とした良導体が使用できる。表面膜 (223) は例えばメッキ膜からなり、このメッキ膜には好ましくは銅、スズ、パラジウム、金、亜鉛、これらの合金等を主成分とした良導体が使用できる。

#### 【0054】

40

次に、前述の積層セラミックコンデンサに適した製造方法の例を、図 8 ~ 図 12 に示した符号等を適宜用いて説明する。

#### 【0055】

製造に際しては、誘電体セラミックス粉末、有機バインダ、有機溶剤及び各種添加剤を含有したセラミックスラリーと、良導体粉末、有機バインダ、有機溶剤及び各種添加剤を含有した電極ペーストを用意する。

#### 【0056】

続いて、キャリアフィルムの表面にセラミックスラリーを塗工して乾燥することにより、第 1 シートを作製すると共に、この第 1 シートの表面に電極ペーストを印刷して乾燥することにより、内部電極層パターン群が形成された第 2 シートを作製する。

50

## 【0057】

続いて、第1シートから取り出した単位シートを所定枚数に達するまで積み重ねて熱圧着する作業を繰り返すことにより、容量素子211の高さ方向一方のマージン部分に対応する部位を形成する。続いて、第2シートから取り出した単位シート（内部電極層パターン群を含む）を所定枚数に達するまで積み重ねて熱圧着する作業を繰り返すことにより、容量素子211の第1内部電極層211a及び第2内部電極層211bが存在する部分に対応する部位を形成する。続いて、第1シートから取り出した単位シートを所定枚数に達するまで積み重ねて熱圧着する作業を繰り返すことにより、容量素子211の高さ方向他方のマージン部分に対応する部位を形成する。最後に、積み重ねられた全体を本熱圧着することにより、未焼成シートを作製する。

10

## 【0058】

続いて、未焼成シートを格子状に切断することにより、容量素子211に対応した未焼成素子を作製する。続いて、多数の未焼成素子の向きを揃えてから、各未焼成素子の長さ方向一面に第1導体層212に対応した未焼成導体層を作製すると共に、これらを反転させてから、各未焼成素子の長さ方向他面に第2導体層213に対応した未焼成導体層を作製する。続いて、未焼成導体層を作製した後の各未焼成素子の高さ方向一面に第1外部電極220の下地膜に対応した未焼成下地膜と第2外部電極230の下地膜に対応した未焼成下地膜を作製する。続いて、未焼成下地膜を作製した後の各未焼成素子の向きを揃えてから、各未焼成素子の長さ方向一面に第1被覆層214に対応した未焼成被覆層を作製すると共に、これらを反転させてから、各未焼成素子の長さ方向他面に第2被覆層215に対応した未焼成被覆層を作製する。これにより、コンデンサ本体210に対応し、且つ、未焼成下地膜が形成された未焼成本体が作製される。

20

## 【0059】

未焼成導体層の作製方法としては、未焼成素子の長さ方向両面それぞれに導体層用ペーストを塗布、ディップ又は印刷して乾燥する方法が好ましく採用できる。また、未焼成下地膜の作製方法としては、未焼成素子の高さ方向一面に電極ペースト（前記電極ペーストと同じペースト、或いは、前記電極ペーストと良導体粉末の種類が異なる別のペースト）を塗布又は印刷して乾燥する方法が好ましく採用できる。さらに、未焼成被覆層の作製方法としては、別途用意しておいた誘電体層用シートを未焼成導体層及び未焼成下地膜に押し付けて貼り付ける方法や、誘電体層用スラリーを未焼成導体層及び未焼成下地膜に塗布、ディップ又は印刷して乾燥する方法が好ましく採用できる。

30

## 【0060】

なお、前記未焼成シート作製工程において、下地膜パターン群が形成された第3シートを用い、この第3シートが下地膜パターン群が外側を向くように配置された未焼成シートを作製すれば、前記切断工程によって未焼成下地膜を有する未焼成素子を得ることができるので、このようにすれば前記の未焼成下地膜の作製を省略することも可能である。この場合、第1外部電極220の下地膜221の態様は図12（B）に示したようになる（図示省略の第2外部電極230の下地膜の態様も同様である）。

## 【0061】

また、図11及び図12には、第1外部電極220の長さ方向一端縁が第1被覆層214の高さ方向一端部によって覆い隠されているものを示し、第2外部電極230の長さ方向他端縁が第2被覆層215の高さ方向一端部によって覆い隠されているものを示してあるが、第1外部電極220の長さ方向一端縁に第1被覆層214の高さ方向一端部が及んでおり、第2外部電極230の長さ方向他端縁に第1被覆層214の高さ方向一端部が及んでいれば、第1外部電極220の長さ方向一端縁が第1被覆層214の高さ方向一端部によって覆い隠されていなくてもよく、第2外部電極230の長さ方向他端縁が第2被覆層215の高さ方向一端部によって覆い隠されていなくてもよい。即ち、第1外部電極220の厚さ方向外側部分と第2外部電極230の厚さ方向外側部分、例えば図12に示した中間膜（222）及び表面膜（223）が露出するように、第1外部電極220の長さ方向一端縁が第1被覆層214の高さ方向一端部によって覆われていてもよいし、第2外

40

50

部電極 230 の長さ方向他端縁が第 2 被覆層 215 の高さ方向一端部によって覆われてもよい。

#### 【0062】

前記の導体層用ペーストには、前記電極ペーストと同じペーストの他、前記電極ペーストと良導体粉末の種類が異なるペーストや、良導体粉末と有機バインダと有機溶剤のみを含むペーストを使用できる。また、前記の誘電体層用シートには、前記セラミックスラリーと同じスラリーを塗工して乾燥したシートの他、前記セラミックスラリーと誘電体セラミック粉末の種類が異なるスラリーを塗工して乾燥したシートを使用できる。さらに、前記の誘電体層用スラリーには、前記セラミックスラリーと同じスラリーの他、前記セラミックスラリーと誘電体セラミック粉末の種類が異なるスラリーを使用できる。

10

#### 【0063】

続いて、未焼成下地膜を有する未焼成本体をこれに含まれている誘電体セラミックス粉末と良導体粉末に応じた雰囲気下、並びに、温度プロファイルにて多数個一括で焼成（脱バインダ処理と焼成処理を含む）を行い、必要に応じて多数個一括でバレル研磨を行う。これにより、下地膜付きのコンデンサ本体 210 が作製される。

#### 【0064】

続いて、各コンデンサ本体 210 の下地膜（221）を覆う中間膜（222）と表面膜（223）をメッキ処理で形成して、第 1 外部電極 220 と第 2 外部電極 230 を作製する。

20

#### 【0065】

次に、前述の積層セラミックコンデンサによって得られる効果（効果 e11 ~ 効果 e13）について説明する。

#### 【0066】

(e11) コンデンサ本体 210 が、(1) 誘電体層を介して交互に配された略矩形状の複数の第 1 内部電極層 211a と略矩形状の複数の第 2 内部電極層 211b とを内包する略直方体状の容量素子 211 と、(2) 容量素子 211 の長さ方向一面を覆う第 1 導体層 212 と、(3) 容量素子 211 の長さ方向他面を覆う第 2 導体層 213 と、(4) 第 1 導体層 212 の外面を覆う第 1 被覆層 214 と、(5) 第 2 導体層 213 の外面を覆う第 2 被覆層 215 と、によって構成されている。また、第 1 導体層 212 には複数の第 1 内部電極層 211a の長さ方向一端縁それが複数の第 1 内部電極層 211a それぞれの幅と同等の接続幅にて接続され、第 2 導体層 213 には複数の第 2 内部電極層 211b の長さ方向他端縁それが複数の第 2 内部電極層 211b それぞれの幅と同等の接続幅にて接続され、第 1 外部電極 220 には第 1 導体層 212 の高さ方向一端縁が第 1 導体層 212 の幅と同等の接続幅にて接続され、第 2 外部電極 230 には第 2 導体層 213 の高さ方向一端縁が第 2 導体層 213 の幅と同等の接続幅にて接続されている。

30

#### 【0067】

即ち、コンデンサ本体 210 に、各第 1 内部電極層 211a を各々の幅を活かして第 1 外部電極 220 に接続する役目を果たす第 1 導体層 212 と、各第 2 内部電極層 211b を各々の幅を活かして第 2 外部電極 230 に接続する役目を果たす第 2 導体層 213 が設けられているため、各第 1 内部電極層 211a の幅及び長さと各第 2 内部電極層 211b の幅及び長さが縮小されても、第 1 外部電極 220 に対する各第 1 内部電極層 211a の接続と第 2 外部電極 230 に対する各第 2 内部電極層 211b の接続が不安定になることを極力回避することができる。依って、略直方体状のコンデンサ本体 210 の高さ方向一面に第 1 外部電極 220 と第 2 外部電極 230 が設けられた積層セラミックコンデンサにおいて小型化と大容量化の要求に応じる場合であっても、第 1 外部電極 220 に対する各第 1 内部電極層 211a の接続と第 2 外部電極 230 に対する各第 2 内部電極層 211b の接続のそれぞれに信頼性の高い接続を実現できる。

40

#### 【0068】

(e12) コンデンサ本体 210 の第 1 導体層 212 と第 2 導体層 213 それぞれの厚さが、複数の第 1 内部電極層 211a と複数の第 2 内部電極層 211b それぞれの厚さの

50

1～5倍の範囲内で設定されているので、第1導体層212と第2導体層213それぞれの厚さによって積層セラミックコンデンサの長さLが増加することを極力回避することができる。

#### 【0069】

(e13) コンデンサ本体210の第1被覆層214と第2被覆層215それぞれの厚さが、容量素子111の誘電体層の厚さの1～10倍の範囲内で設定されているので、第1被覆層214と第2被覆層215それぞれの厚さによって積層セラミックコンデンサの長さLが増加することを極力回避することができる。

#### 【0070】

次に、前述の積層セラミックコンデンサの変形例(第1変形例m11～第4変形例m14)について説明する。 10

#### 【0071】

(m11) 図13(A)及び図13(B)に示したように、第1導体層212の第1外部電極220に接続された一端縁を除く周縁を、第1被覆層214の容量素子211側に伸びた部分214aによって覆うと共に、第2導体層213の第2外部電極230に接続された一端縁を除く周縁を、第2被覆層215の容量素子211側に伸びた部分215aによって覆うようにしてもよい。このようにすれば、回路基板に実装するときに積層セラミックコンデンサが倒れても、第1導体層212と第2導体層213が回路基板の導体ラインや隣接する電子部品等に接触してショート等の問題を生じることを防げる、といった別の効果を得ることができる。 20

#### 【0072】

(m12) 図14(A)及び図14(B)に示したように、容量素子211に、誘電体層(符号省略)を介して幅方向に配された略矩形状の複数の第1内部電極層211a' と略矩形状の複数の第2内部電極層211b' を内包させようにもよい。このようにすると、各第1内部電極層211a' の向きと各第2内部電極層211b' の向きが第1外部電極220及び第2外部電極230と略直角になるが、前記同様の効果e1～効果e3を得ることができる。

#### 【0073】

(m13) 先の製法例で述べた未焼成被覆層にMgO等の酸化促進剤を0.1～10wt%程度含有させておけば、後の焼成工程で作製される第1導体層212の主として第1被覆層214との境界部分、並びに、第2導体層213の主として第2被覆層215との境界部分に金属酸化物を散在させて、この金属酸化物によって第1導体層212に対する第1被覆層214の密着性と第2導体層213に対する第2被覆層215の密着性を高めることができる。 30

#### 【0074】

(m14) 先の製法例で述べた未焼成導体層に容量素子211の第1内部電極層211aと第2内部電極層211bを除く部分の主成分と同じ誘電体セラミック粉末を5～50wt%程度含有させておけば、容量素子211に対する第1導体層212の密着性と容量素子211に対する第2導体層213の密着性を高めることができる。

#### 【符号の説明】

#### 【0075】

110…コンデンサ本体、111…容量素子、111a, 111a'…第1内部電極層、111b, 111b'…第2内部電極層、112…第1導体層、113…第2導体層、114…第1被覆層、114a…第1被覆層の伸びた部分、115…第2被覆層、115a…第2被覆層の伸びた部分、120…第1外部電極、130…第2外部電極、210…コンデンサ本体、211…容量素子、211a, 211a'…第1内部電極層、211b, 211b'…第2内部電極層、212…第1導体層、213…第2導体層、214…第1被覆層、2146a…第1被覆層の伸びた部分、215…第2被覆層、215a…第2被覆層の伸びた部分、220…第1外部電極、230…第2外部電極。 40

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開2015-090977(JP,A)

特開2008-283170(JP,A)

特開2005-012167(JP,A)

特開平06-084687(JP,A)

特開2015-204451(JP,A)

特開2014-036149(JP,A)

特開2015-053503(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01G 4/30