## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

HO1L

23/532

(2006.01)

HO1L

21/768

(2006.01)

HO1L

21/8234

(2006.01)

HO1L

23/522

(2006.01)

HO1L

23/535

(2006.01)

(52) CPC특허분류

**H01L 23/53209** (2013.01) **H01L 21/76846** (2013.01)

(21) 출원번호 10-2023-0158224

(22) 출원일자 **2023년11월15일** 심사청구일자 **2023년11월15일**

(30) 우선권주장

63/453,083 2023년03월18일 미국(US) 18/220,886 2023년07월12일 미국(US)

전체 청구항 수 : 총 10 항

(11) 공개번호 10-2024-0141122

(43) 공개일자 2024년09월25일

(71) 출원인

**타이완 세미콘덕터 매뉴팩처링 컴퍼니 리미티드** 중화민국, 타이완, 신추, 신추 사이언스 파크, 리-신 로드 6, 넘버 8

(72) 발명자

창 치에

중화민국, 타이완, 신추, 신추 사이언스 파크, 리-신 로드 6, 넘버 8

린 옌-춘

중화민국, 타이완, 신추, 신추 사이언스 파크, 리-신 로드 6, 넘버 8

(뒷면에 계속)

(74) 대리인

김태홍, 김진회

(54) 발명의 명칭 상호연결 구조물 및 이를 형성하는 방법

## (57) 요 약

상호연결 구조물은, 층간 유전체 내의 콘택트 비아, 제1 유전체층 내의 제1 도전성 피처 - 제1 유전체층은 층간 유전체 위에 있음 -, 제1 유전체층 내의 제1 라이너를 포함하고, 제1 라이너는, 제1 도전성 피처의 측벽면과 접촉하는 제1 파트, 및 제1 도전성 피처의 바닥면과 접촉하는 제2 파트를 포함한다. 상호연결 구조물은, 제1 도전성 피처의 최상면과 접촉하는 제1 캡 층, 제2 유전체층 내의 제2 도전성 피처 - 제2 유전체층은 제1 유전체층 위에 있음 -, 제2 유전체층 내의 제2 라이너를 포함하고, 제1 도전성 피처와 제2 도전성 피처는 제1 도전성 물질을 포함하고, 콘택트 비아, 제1 라이너, 제1 캡 층, 및 제2 라이너는 제1 도전성 물질과는 화학적으로 상이한 제2 도전성 물질을 포함한다.

### 대표도

### (52) CPC특허분류

**H01L 21/76849** (2013.01)

H01L 21/76877 (2013.01)

**H01L 21/823475** (2013.01)

**H01L 23/5226** (2013.01)

**H01L 23/5283** (2013.01)

**H01L 23/5286** (2013.01)

**H01L 23/535** (2013.01)

### (72) 발명자

### 리우 젠-웨이

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 쩽 치-한

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

## 치엔 해리

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

#### 웽 쳉-후이

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 린 춘-치에

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 수 흥-웬

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 차이 밍-싱

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 창 치-웨이

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 명 세 서

### 청구범위

### 청구항 1

상호연결 구조물에 있어서,

층간 유전체 내의 콘택트 비아;

제1 유전체층 내의 제1 도전성 피처 - 상기 제1 유전체층은 상기 층간 유전체 위에 배치됨 -;

상기 제1 유전체층 내의 제1 라이너 - 상기 제1 라이너는,

상기 제1 도전성 피처의 측벽면과 접촉하는 제1 파트; 및

상기 제1 도전성 피처의 바닥면과 접촉하는 제2 파트

를 포함함 -;

상기 제1 도전성 피처의 최상면과 접촉하는 제1 캡 층;

제2 유전체층 내의 제2 도전성 피처 - 상기 제2 유전체층은 상기 제1 유전체층 위에 배치됨 -; 및

상기 제2 유전체층 내의 제2 라이너

를 포함하고,

상기 제1 도전성 피처와 상기 제2 도전성 피처는 제1 도전성 물질을 포함하고, 상기 콘택트 비아, 상기 제1 라이너, 상기 제1 캡 층, 및 상기 제2 라이너는 상기 제1 도전성 물질과는 화학적으로 상이한 제2 도전성 물질을 포함한 것인 상호연결 구조물.

### 청구항 2

제1항에 있어서,

상기 제2 도전성 피처와 접촉하는 제2 캡 층

을 더 포함하는 상호연결 구조물.

## 청구항 3

제2항에 있어서,

상기 제2 캡 층은 상기 제2 도전성 물질을 포함한 것인 상호연결 구조물.

### 청구항 4

제3항에 있어서,

상기 제2 도전성 물질은 코발트가 없는 것인 상호연결 구조물.

## 청구항 5

제2항에 있어서,

상기 제2 캡 층은 상기 제1 도전성 물질 및 상기 제2 도전성 물질과는 화학적으로 상이한 제3 도전성 물질을 포 함한 것인 상호연결 구조물.

## 청구항 6

제2항에 있어서,

상기 제2 캡 층은 추가로 상기 제2 라이너와 접촉하는 것인 상호연결 구조물.

### 청구항 7

제1항에 있어서,

상기 제1 유전체층 및 상기 제1 라이너와 접촉하는 제1 배리어층

을 더 포함하는 상호연결 구조물.

#### 청구항 8

제1항에 있어서,

상기 제1 라이너의 상기 제2 파트의 일부는 상기 충간 유전체 내로 연장된 것인 상호연결 구조물.

### 청구항 9

반도체 디바이스 구조물에 있어서,

제1 충간 유전체 내에 배치된 제1 소스/드레인 콘택트, 제2 소스/드레인 콘택트, 제3 소스/드레인 콘택트, 및 제4 소스/드레인 콘택트;

제2 층간 유전체 내의 제1 도전성 피처 - 상기 제1 도전성 피처는 상기 제2 층간 유전체 및 상기 제1 소스/드레인 콘택트와 직접 접촉함 -;

상기 제2 층간 유전체 내의 제2 도전성 피처 - 상기 제2 도전성 피처는 상기 제2 층간 유전체, 상기 제2 소스/드레인 콘택트, 상기 제3 소스/드레인 콘택트, 및 상기 제4 소스/드레인 콘택트와 직접 접촉함 -;

제1 유전체층 내의 제3 도전성 피처;

제2 유전체층 내의 제4 도전성 피처 - 상기 제2 유전체층은 상기 제1 유전체층 위에 배치됨 -;

상기 제3 도전성 피처의 측벽면, 상기 제3 도전성 피처의 바닥면, 및 상기 제1 도전성 피처의 최상면과 직접 접촉하는 제1 라이너; 및

상기 제4 도전성 피처의 측벽면 및 상기 제4 도전성 피처의 바닥면과 직접 접촉하는 제2 라이너

를 포함하며,

상기 제1 도전성 피처, 상기 제2 도전성 피처, 상기 제1 라이너, 및 상기 제2 라이너는 제1 도전성 물질을 포함하고, 상기 제3 도전성 피처와 상기 제4 도전성 피처는 상기 제1 도전성 물질과는 화학적으로 상이한 제2 도전성 물질을 포함한 것인 반도체 디바이스 구조물.

### 청구항 10

반도체 디바이스 구조물을 형성하기 위한 방법에 있어서,

층간 유전체 내에 제1 도전성 피처를 형성하는 단계 - 상기 제1 도전성 피처는 상기 층간 유전체와 직접 접촉하고, 상기 제1 도전성 피처는 제1 도전성 물질을 포함함 -;

상기 층간 유전체 및 상기 제1 도전성 피처 상에 제1 에칭 정지층을 형성하는 단계;

상기 제1 에칭 정지층 상에 제1 유전체층을 형성하는 단계;

상기 제1 도전성 피처의 일부를 노출시키기 위해 상기 제1 유전체층과 상기 제1 에칭 정지층을 관통하여 개구부를 형성하는 단계;

상기 제1 유전체층, 상기 제1 에칭 정지층, 및 상기 층간 유전체의 노출된 표면들 상에 제1 배리어층을 선택적으로 형성하는 단계;

상기 제1 도전성 피처의 노출된 표면과 상기 제1 배리어층 상에 제1 라이너층을 형성하는 단계 - 상기 제1 라이너층은 상기 제1 도전성 물질을 포함함 -;

제2 도전성 피처를 형성하기 위해 제2 도전성 물질로 상기 개구부를 채우는 단계 - 상기 제2 도전성 물질은 상기 제1 도전성 물질과는 화학적으로 상이함 -;

상기 제2 도전성 피처의 노출된 표면들 상에 제1 캡 층을 선택적으로 형성하는 단계 - 상기 제1 캡 층은 상기 제1 도전성 물질을 포함함 -;

상기 제1 유전체층 위에 제2 에칭 정지층을 형성하는 단계;

상기 제2 에칭 정지층 상에 제2 유전체층을 형성하는 단계;

상기 제2 유전체층 및 상기 제2 에칭 정지층을 관통하여 제3 도전성 피처를 형성하는 단계 - 상기 제3 도전성 피처는 상기 제2 도전성 물질을 포함함 -; 및

상기 제3 도전성 피처의 노출된 표면 상에 제2 캡 층을 선택적으로 형성하는 단계 - 상기 제2 캡 층은 상기 제1 도전성 물질을 포함함 -

를 포함하는 반도체 디바이스 구조물을 형성하기 위한 방법.

### 발명의 설명

## 기 술 분 야

[0001] 본 출원은 2023년 3월 18일에 출원된 미국 가특허 출원 63/453,083에 대한 우선권을 청구하며, 이 가특허 출원 내용의 전문은 참조로서 병합된다.

### 배경기술

[0002] 반도체 디바이스들은 예로서 개인 컴퓨터, 셀룰러폰, 디지털 카메라, 및 다른 전자 장비와 같은 다양한 전자 응용들에서 사용된다. 일반적으로, 전형적인 반도체 디바이스는 트랜지스터 및 커패시터와 같은 능동 디바이스를 갖는 기판을 포함한다. 이들 능동 디바이스들은 초기에 서로 격리되고, 상호연결 구조물들이 후속하여 능동 디바이스들 위에 형성되어 기능 회로들을 생성한다. 이러한 상호연결 구조물들은 기판 상의 능동 디바이스들에 전기적으로 커플링될 수 있는 콘택트 플러그를 포함할 수 있다. 그러나, 집적 회로의 치수가 진보된 노드 응용들에서 더 작은 미크론 미만 크기로 계속 스케일링됨에 따라, 원하는 접촉 신뢰성을 유지하면서 접촉 저항을 감소시키는 것이 점점 더 어려워지고 있다. 개선된 구조물들 및 이를 제조하기 위한 방법이 필요하다.

### 발명의 내용

### 과제의 해결 수단

- [0003] 상호연결 구조물의 실시예가 제공된다. 상호연결 구조물은, 충간 유전체 내의 콘택트 비아, 제1 유전체충 내의 제1 도전성 피처를 포함하며, 제1 유전체충은 충간 유전체 위에 배치된다. 상호연결 구조물은 또한, 제1 유전체충 내의 제1 라이너를 포함하고, 제1 라이너는, 제1 도전성 피처의 측벽면과 접촉하는 제1 파트, 및 제1 도전성 피처의 바닥면과 접촉하는 제2 파트를 포함한다. 상호연결 구조물은 또한, 제1 도전성 피처의 최상면과 접촉하는 제1 캡 충, 제2 유전체충 내의 제2 도전성 피처를 포함하고, 제2 유전체충은 제1 유전체충 위에 배치된다. 상호연결 구조물은 제2 유전체충 내의 제2 라이너를 더 포함하고, 제1 도전성 피처와 제2 도전성 피처는 제1 도전성 물질을 포함하고, 콘택트 비아, 제1 라이너, 제1 캡 충, 및 제2 라이너는 제1 도전성 물질과는 화학적으로 상이한 제2 도전성 물질을 포함한다.

- [0004] 다른 실시예는 반도체 디바이스 구조물이다. 구조물은, 제1 층간 유전체 내에 배치된 제1 소스/드레인 콘택트, 제2 소스/드레인 콘택트, 제3 소스/드레인 콘택트, 및 제4 소스/드레인 콘택트, 제2 층간 유전체 내의 제1 도전성 피처 제1 도전성 피처는 제2 층간 유전체 및 제1 소스/드레인 콘택트와 직접 접촉함 -, 제2 층간 유전체 내의 제2 도전성 피처 제2 도전성 피처는 제2 층간 유전체, 제2, 제3, 및 제4 소스/드레인 콘택트들과 직접 접촉함 -을 포함한다. 구조물은 또한, 제1 유전체층 내의 제3 도전성 피처, 제2 유전체층 내의 제4 도전성 피처 제2 유전체층은 제1 유전체층 위에 배치됨 -, 제3 도전성 피처의 측벽면, 제3 도전성 피처의 바닥면, 및 제1 도전성 피처의 최상면과 직접 접촉하는 제1 라이너를 포함한다. 구조물은, 제4 도전성 피처의 측벽면 및 제4 도전성 피처의 바닥면과 직접 접촉하는 제2 라이너를 더 포함하며, 제1 도전성 피처, 제2 도전성 피처, 제1 라이너, 및 제2 라이너는 제1 도전성 물질을 포함하고, 제3 도전성 피처와 제4 도전성 피처는 제1 도전성 물질을 포함한다.

- [0005] 반도체 디바이스 구조물을 형성하기 위한 방법의 추가적인 실시예가 제공된다. 방법은, 충간 유전체 내에 제1 도전성 피처를 형성하는 단계 - 제1 도전성 피처는 충간 유전체와 직접 접촉하고, 제1 도전성 피처는 제1 도전

성 물질을 포함함 -를 포함한다. 본 방법은 또한, 층간 유전체 및 제1 도전성 피처 상에 제1 에칭 정지층을 형성하는 단계, 제1 대칭 정지층 상에 제1 유전체층을 형성하는 단계, 제1 도전성 피처의 일부를 노출시키기 위해 제1 유전체층과 제1 에칭 정지층을 관통하여 개구부를 형성하는 단계, 제1 유전체층, 제1 에칭 정지층, 및 층간 유전체의 노출된 표면들 상에 제1 배리어층을 선택적으로 형성하는 단계를 포함한다. 본 방법은 또한, 제1 도전성 피처의 노출된 표면과 제1 배리어층 상에 제1 라이너층을 형성하는 단계 - 제1 라이너층은 제1 도전성 물질을 포함함 -를 포함한다. 본 방법은 또한, 제2 도전성 피처를 형성하기 위해 제2 도전성 물질로 개구부를 채우는 단계 - 제2 도전성 물질은 제1 도전성 물질과는 화학적으로 상이함 -, 제2 도전성 피처의 노출된 표면들 상에 제1 캡 층을 선택적으로 형성하는 단계 - 제1 캡 층은 제1 도전성 물질을 포함함 -를 포함한다. 본 방법은 또한, 제1 유전체층 위에 제2 에칭 정지층을 형성하는 단계, 제2 에칭 정지층 상에 제2 유전체층을 형성하는 단계, 제2 유전체층 및 제2 에칭 정지층을 관통하여 제3 도전성 피처를 형성하는 단계 - 제3 도전성 피처는 제2 도전성 물질을 포함함 -를 포함한다. 본 방법은, 제3 도전성 피처를 형성하는 단계 - 제2 캡 층은 세1 도전성 물질을 포함함 -를 포함한다. 본 방법은, 제3 도전성 피처의 노출된 표면 상에 제2 캡 층을 선택적으로 형성하는 단계 - 제2 캡 층은 제1 도전성 물질을 포함함 -를 더 포함한다.

## 도면의 간단한 설명

[0006] 본 개시의 양태들은 첨부 도면들과 함께 읽혀질 때 아래의 상세한 설명으로부터 최상으로 이해된다. 본 산업계에서의 표준적인 관행에 따라, 다양한 피처들은 실척도로 작도되지 않았음을 유념한다. 실제로, 다양한 피처들의 치수는 설명의 명료함을 위해 임의적으로 증가되거나 또는 감소될 수 있다.

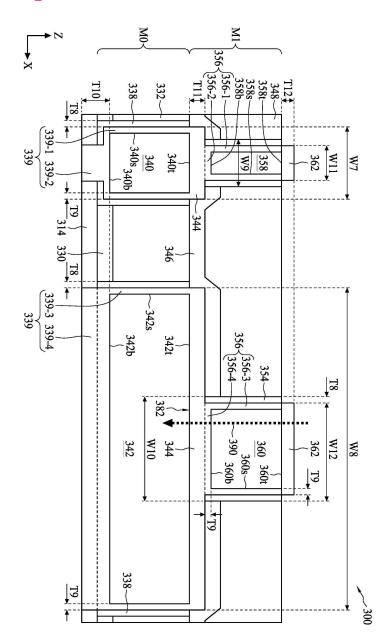

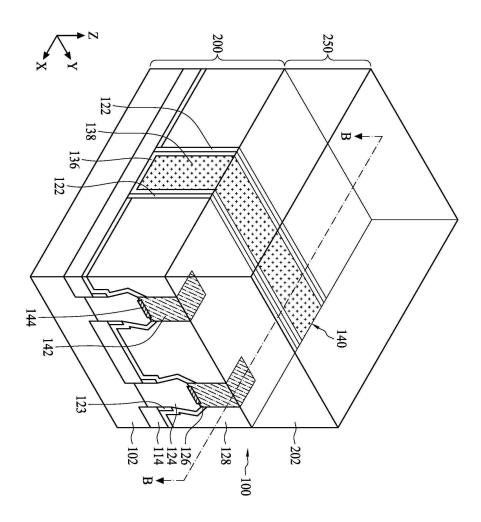

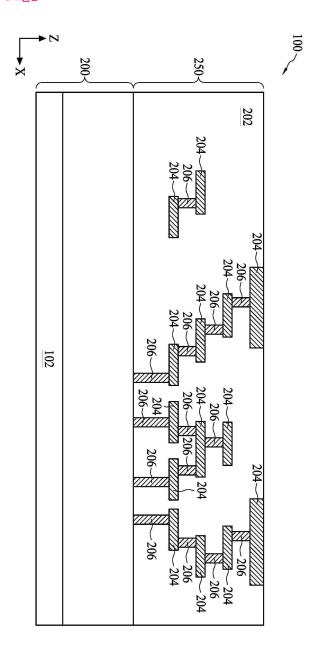

도 1a는 일부 실시예들에 따른, 반도체 디바이스 구조물을 제조하는 다양한 스테이지들 중 하나의 스테이지의 사시도이다.

도 1b는 일부 실시예들에 따른, 도 1a의 B-B 라인을 따라 취해진 반도체 디바이스 구조물을 제조하는 스테이지의 측단면도이다.

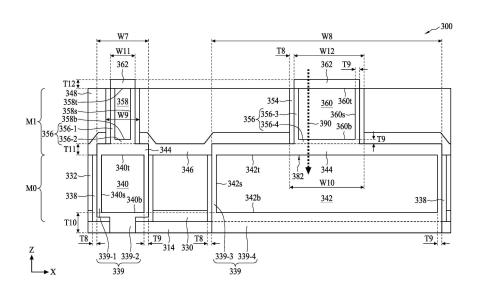

도 2는 일부 실시예들에 따른, 반도체 디바이스 구조물을 제조하는 스테이지의 측단면도이다.

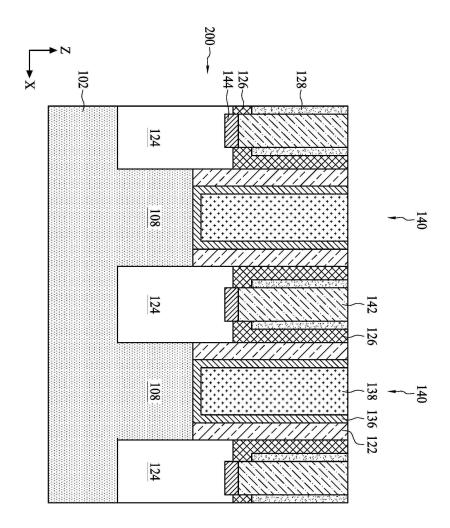

도 3a 내지 도 3p는 일부 실시예들에 따른, 상호연결 구조물을 제조하는 다양한 스테이지들의 측단면도들이다.

도 4는 일부 실시예들에 따른, 상호연결 구조물의 일부를 예시한다.

도 5는 일부 실시예들에 따른 금속간 유전체(intermetal dielectric; IMD) 충들을 보여주는 상호연결 구조물의 일부의 확대도를 예시한다.

### 발명을 실시하기 위한 구체적인 내용

[0007] 아래의 개시는 제공되는 본 발명내용의 여러 특징들을 구현하기 위한 많은 여러 실시예들 또는 예시들을 제공한다. 본 개시를 단순화하기 위해 컴포넌트 및 장치의 특정예들이 아래에서 설명된다. 물론, 이것들은 단지 예시들에 불과하며, 이것들로 한정시키고자 의도한 것은 아니다. 예를 들어, 이후의 상세설명에서 제2 피처 상에서의 또는 그 위에서의 제1 피처의 형성은 제1 및 제2 피처들이 직접적으로 접촉하여 형성되는 실시예들을 포함할 수 있으며, 또한 제1 및 제2 피처들이 직접적으로 접촉하지 않을 수 있도록 추가적인 피처들이 제1 및 제2 피처들 사이에서 형성될 수 있는 실시예들을 포함할 수 있다. 또한, 본 개시는 다양한 예시들에서 참조 숫자들 및/또는 문자들을 반복할 수 있다. 이러한 반복은 간략화 및 명료화를 목적으로 한 것이며, 그러한 반복 자체는 개시된 다양한 실시예들 및/또는 구성들 간의 관계에 영향을 주는 것은 아니다.

[0008] 뿐만 아니라, 도면들에서 예시된 하나의 엘리먼트 또는 피처에 대한 다른 엘리먼트(들) 또는 피처(들)의 관계를 설명하기 위해 "아래", "밑", "보다 낮은", "위", "위쪽에", "상에", "최상부에", 보다 위" 등과 같은 공간 상대적 용어들이 설명의 용이성을 위해 여기서 사용될 수 있다. 공간 상대적 용어들은 도면들에서 도시된 배향에 더하여 이용중에 있거나 또는 동작중에 있는 디바이스의 상이한 배향들을 망라하도록 의도된 것이다. 장치는 이와달리 배향될 수 있고(90° 회전되거나 또는 다른 배향으로 회전됨), 이에 따라 여기서 이용되는 공간 상대적기술어들이 이와 똑같이 해석될 수 있다.

[0009] 도 1a는 디바이스층(200) 및 상호연결 구조물(250)을 포함하는 반도체 디바이스 구조물(100)을 제조하는 스테이지를 예시한다. 도 1b는 일부 실시예들에 따른 디바이스층(200)의 단면도를 예시한다. 디바이스층(200)은 기판(102) 및 기판(102) 내에 또는 기판(102) 상에 형성된 하나 이상의 디바이스를 포함한다. 기판(102)은 반도체 기판일 수 있다. 일부 실시예들에서, 기판(102)은 적어도 기판(102)의 표면 상에서 단결정 반도체층을 포함한다. 기판(102)은 비제한적인 예시로서, 실리콘(Si), 게르마늄(Ge), 실리콘 게르마늄(SiGe), 갈륨 비화물

(GaAs), 인듐 안티몬화물(InSb), 갈륨 인화물(GaP), 갈륨 안티몬화물(GaSb), 인듐 알루미늄 비화물(InAlAs), 인듐 갈륨 비화물(InGaAs), 갈륨 안티몬 인화물(GaSbP), 갈륨 비화물 안티몬화물(GaAsSb), 및 인듐 인화물(InP)과 같은 결정질 반도체 물질을 포함할 수 있다. 예를 들어, 기판(102)은 Si로 제조된다. 일부 실시예들에서, 기판(102)은 두 개의 실리콘충들 사이에 배치된 절연충(도시되지 않음)을 포함하는 실리콘 온 절 연체(silicon-on-insulator; SOI) 기판이다. 일 양태에서, 절연충은 산화물과 같은 산소 함유 물질이다.

- [0010] 기판(102)은 불순물들(예를 들어, p형 또는 n형 불순물들)로 적절하게 도핑되었던 다양한 영역들을 포함할 수 있다. 도펀트는, 예를 들어, n형 핀 전계 효과 트랜지스터(fin field effect transistor; FinFET)의 경우 인이고, p형 FinFET의 경우 붕소이다.

- [0011] 위에서 설명된 바와 같이, 디바이스층(200)은 트랜지스터, 다이오드, 이미징 센서, 저항기, 커패시터, 인덕터, 메모리 셀, 또는 이들의 조합과 같은, 임의의 적절한 디바이스들을 포함할 수 있다. 일부 실시예들에서, 디바 이스층(200)은 평면 전계 효과 트랜지스터(planar field effect transistor; FET), FinFET, 나노구조 트랜지스 터, 또는 다른 적절한 트랜지스터와 같은 트랜지스터들을 포함한다. 나노구조 트랜지스터는 나노시트 트랜지스 터, 나노와이어 트랜지스터, 게이트 올 어라운드(gate-all-around; GAA) 트랜지스터, 멀티 브리지 채널(multibridge channel; MBC) 트랜지스터, 또는 채널을 둘러싸는 게이트 전극을 갖는 임의의 트랜지스터들을 포함할 수 있다. 기판(102) 상에 형성된 디바이스의 예시는 도 1a 및 도 1b에서 도시된 FinFET이다. 디바이스층(200)은 소스/드레인(source/drain; S/D) 영역(124) 및 게이트 스택(140)(도 1a에서는 하나만 도시됨)을 포함한다. 각 각의 게이트 스택(140)은 소스 영역으로서 역할을 하는 S/D 영역들(124)과 드레인 영역으로서 역할을 하는 S/D 영역들(124) 사이에 배치될 수 있다. 예를 들어, 각각의 게이트 스택(140)은 소스 영역으로서 역할을 하는 하 나 이상의 S/D 영역(124)과 드레인 영역으로서 역할을 하는 하나 이상의 S/D 영역(124) 사이에서 Y축을 따라 연 장될 수 있다. 소스/드레인 영역(들)은 상황에 따라 소스 또는 드레인을 개별적으로 또는 총칭하여 지칭할 수 있다는 것을 이해해야 한다. 도 1b에서 도시된 바와 같이, 두 개의 게이트 스택(140)이 기판(102) 상에 형성된 다. 일부 실시예들에서, 두 개보다 많은 게이트 스택(140)이 기판(102) 상에 형성된다. 도시되지 않았지만, 채널 영역들이 S/D 영역들(124) 사이에 형성되고 게이트 스택(140)에 의해 둘러싸인 적어도 세 개의 표면들을 갖는다.

- [0012] S/D 영역들(124)은 Si 또는 Ge, III-V족 화합물 반도체, II-VI족 화합물 반도체, 또는 다른 적절한 반도체 물질과 같은, 반도체 물질을 포함할 수 있다. 예시적인 S/D 영역(124)은, 비제한적인 예시로서, Ge, SiGe, GaAs, AlGaAs, GaAsP, SiP, InAs, AlAs, InP, GaN, InGaAs, InAlAs, GaSb, AlP, GaP 등을 포함할 수 있다. S/D 영역들(124)은 붕소와 같은 p형 도펀트들, 인 또는 비소와 같은 n형 도펀트들, 및/또는 이들의 조합을 포함한 다른 적절한 도펀트들을 포함할 수 있다. S/D 영역들(124)은 CVD, 원자층 성막(atomic layer deposition; ALD) 또는 분자 빔 에피택시(molecular beam epitaxy; MBE)를 사용하는 에피택셜 성장 방법에 의해 형성될 수 있다. 채널 영역들은 Si, Ge, GeSn, SiGe, GaAs, InSb, GaP, GaSb, InAlAs, InGaAs, GaSbP, GaAsSb, GaN, GaP, 또는 InP와 같은, 하나 이상의 반도체 물질을 포함할 수 있다. 채널 영역들은 기판(102)과 동일한 반도체 물질을 포함할 수 있다. 일부 실시예들에서, 디바이스층(200)은 FinFET을 포함할 수 있고, 채널 영역들은 게이트 스택(140) 아래에 배치된 복수의 핀들이다. 일부 실시예들에서, 디바이스층(200)은 나노구조 트랜지스터를 포함할수 있고, 채널 영역들은 게이트 스택(140)에 의해 둘러싸인다.

- [0013] 도 1a 및 도 1b에서 도시된 바와 같이, 각각의 게이트 스택(140)은 채널 영역 위에 배치된(또는 나노구조 트랜지스터들을 위한 채널 영역을 둘러싸는) 게이트 전극층(138)을 포함한다. 게이트 전극층(138)은 텅스텐, 코발트, 알루미늄, 루테늄, 구리, 이들의 다층 등과 같은 금속 함유 물질일 수 있으며, ALD, 플라즈마 강화 화학적기상 성막(plasma enhanced chemical vapor deposition; PECVD), MBD, 물리적 기상 성막(physical vapor deposition; PVD), 또는 임의의 적절한 성막 기술에 의해 성막될 수 있다. 게이트 스택(140)은 채널 영역 위에 배치된 게이트 유전체층(136)을 더 포함할 수 있다. 게이트 전극층(138)은 게이트 유전체층(136) 위에 배치될수 있다. 일부 실시예들에서, 채널 영역(108)과 게이트 유전체층(136) 사이에 계면층(도시되지 않음)이 배치될수 있고, 게이트 유전체층(136)과 게이트 전극층(138) 사이에 하나 이상의 일함수층(도시되지 않음)이 형성될수 있다. 계면 유전체층(136)과 게이트 전극층(138) 사이에 하나 이상의 일함수층(도시되지 않음)이 형성될수 있다. 계면 유전체층은, 산소 함유 물질 또는 질소 함유 물질, 또는 이들의 다층과 같은 유전체 물질을 포함할수 있고, CVD, PECVD, 또는 ALD와 같은 임의의 적절한 성막 방법에 의해 형성될 수 있다. 게이트 유전체층(136)은 CVD, PECVD, 또는 ALD와 같은 이들의 다층과 같은, 유전체 물질을 포함할수 있다. 게이트 유전체층(136)은 CVD, PECVD, 또는 ALD와 같은 임의의 적절한 방법에 의해 형성될수 있다. 게이트 유전체층(136)은 CVD, PECVD, 또는 ALD와 같은 임의의 적절한 방법에 의해 형성될수 있다. 일부 실시예들에서, 게이트 유전체층(136)은 건포멀층일수 있다. "컨포멀"이라는 용어는 다양한 영역들에 걸쳐 실질적으로 동일한 두께를 갖는 층에 대한 설명의

용이성을 위해 본원에서 사용될 수 있다. 하나 이상의 일함수층은 알루미늄 티타늄 탄화물, 알루미늄 티타늄 산화물, 알루미늄 티타늄 질화물 등을 포함할 수 있다.

- [0014] 케이트 스페이서(122)가 게이트 스택(140)의 측벽(예컨대, 게이트 유전체층(136)의 측벽)을 따라 형성된다. 게이트 스페이서(122)는 실리콘 산탄화물, 실리콘 질화물, 실리콘 산질화물, 실리콘 탄소 질화물 등, 이들의다층, 또는 이들의 조합을 포함할 수 있고, CVD, ALD, 또는 다른 적절한 성막 기술에 의해 성막될 수 있다. 일부 실시예들에서, 핀 측벽 스페이서(123)가 각각의 S/D 영역(124)의 양측 상에 배치될 수 있고, 핀 측벽 스페이서(123)는 게이트 스페이서(122)와 동일한 물질을 포함할 수 있다. 게이트 스택(140), 게이트 스페이서(122), 및 핀 측벽 스페이서(123)의 부분들은 격리 영역(114) 상에 배치될 수 있다. 격리 영역(114)은 기판(102) 상에 배치된다. 격리 영역(114)은 산소 함유 물질, 질소 함유 물질, 또는 이들의 조합과 같은 절연 물질을 포함할수 있다. 일부 실시예들에서, 격리 영역(114)은 쉘로우 트렌치 격리(shallow trench isolation; STI)이다. 절연 물질은 고밀도 플라즈마 화학적 기상 성막(high-density plasma chemical vapor deposition; HDP-CVD), 유동가능 화학적 기상 성막(flowable chemical vapor deposition; FCVD), 또는 다른 적절한 성막 공정에 의해 형성될 수 있다. 일 양태에서, 격리 영역(114)은 FCVD 공정에 의해 형성되는 실리콘 산화물을 포함한다.

- [0015] S/D 영역(124) 및 격리 영역(114) 상에 콘택트 에칭 정지층(contact etch stop layer; CESL)(126)이 형성되고, CESL(126) 상에 층간 유전체(interlayer dielectric; ILD) 층(128)이 형성된다. CESL(126)은 ILD 층(128) 내에 개구부들을 형성할 때 에칭 공정을 중단시키기 위한 메커니즘을 제공할 수 있다. CESL(126)은 S/D 영역(124) 및 격리 영역(114)의 표면들 상에 컨포멀하게 성막될 수 있다. CESL(126)은 실리콘 질화물, 실리콘 탄소 질화물, 실리콘 탄소 질화물, 실리콘 단소 잘화물, 실리콘 산질화물, 살리콘 산질화물, 살리콘 산질화물, 살리콘 산화물, 실리콘 탄소 산화물 등, 또는 이들의 조합과 같은, 산소 함유 물질 또는 질소 함유 물질을 포함할 수 있으며, CVD, PECVD, ALD, 또는 임의의 적절한 성막 기술에 의해 성막될 수 있다. ILD 층(128)은 TEOS(tetraethylorthosilicate), 무도핑 실리케이트 유리, 또는 BPSG(borophosphosilicate glass), FSG(fused silica glass), PSG(phosphosilicate glass), BSG(boron doped silicon glass), OSG(organosilicate glass), SiOC와 같은 도핑된 실리콘 산화물, 및/또는 임의의 적절한 로우 k 유전체 물질(예컨대, 실리콘 이산화물의 유전 상수보다 낮은 유전 상수를 갖는 물질)에 의해 형성된 산화물을 포함할 수 있고, 스핀 온, CVD, FCVD, PECVD, PVD, 또는 임의의 적절한 성막 기술에 의해 성막될 수 있다.

- [0016] S/D 콘택트(142)가 ILD 층(128) 내에 그리고 S/D 영역(124) 위에 배치될 수 있다. S/D 콘택트(142)는 전기 도 전성일 수 있고, Ru, Mo, Co, Ni, W, Ti, Ta, Cu, Al, TiN 및 TaN 중, 하나 이상을 갖는 물질을 포함할 수 있고, 도전성 콘택트가 전기화학 도금(electro-chemical plating; ECP) 또는 PVD와 같은 임의의 적절한 방법에 의해 형성될 수 있다. S/D 콘택트(142)와 S/D 영역(124) 사이에 실리사이드층(144)이 배치될 수 있다. 실리사이드층(144)은 금속 또는 금속 합금 실리사이드로 제조될 수 있고, 금속은 귀금속, 내화 금속, 희토류 금속, 이들의 합금, 또는 이들의 조합을 포함한다.

- [0017] 집적 회로에서, 반도체 디바이스들에 신호 라우팅 및 전력 공급을 제공하기 위해 상호연결 구조물들(또는 상호연결 구조물들)이 사용된다. 집적 회로 칩은 일반적으로 FEOL(front-end-of-line) 및 MEOL(middle-end-of-line) 공정들 동안 제조된 디바이스층, 및 BEOL(back-end-of-line) 층을 포함한다. 디바이스층은 기판 내에 및 /또는 기판 상에 형성될 수 있고, BEOL 층은 디바이스층의 전측 및/또는 후측 상에 형성된다. 디바이스층은 트랜지스터, 다이오드, 커패시터, 저항기 등과 같은, 다양한 반도체 디바이스들을 포함할 수 있고, 기판 내에 및/또는 기판 상에 형성될 수 있다. 일부 실시예들에서, 디바이스층은 또한, 디바이스층 내의 게이트 및 소스/드레인 피처들에 연결된 도전성 피처들을 갖는 하나 이상의 유전체층과 같은, MEOL 구조물들을 포함할 수 있다. 상호연결 구조물들은 일반적으로 디바이스층과 BEOL 층 둘 다 내에 형성된 도전성 라인들 및 비아들을 포함한다.

- [0018] 도 2는 일부 실시예들에 따른, 반도체 디바이스 구조물(100)을 제조하는 스테이지의 측단면도이다. 상호연결 구조물(250)이 디바이스층(200) 및 기판(102) 위에 배치된다. 상호연결 구조물(250)은 제1 복수의 도전성 피처들(204, 206)을 분리하고 격리시키기 위한 금속간 유전체(intermetal dielectric; IMD)층(202)을 포함한다. 일부 실시예들에서, 제1 복수의 도전성 피처들(204)은 도전성 라인들이고, 제2 복수의 도전성 피처들(206)은 도전성 비아들이다. 상호연결 구조물(250)은 다중 레벨들의 도전성 피처들(204)을 포함하고, 도전성 피처들(204)은 아래에 배치된 디바이스층(200)에 대한 전기적 경로들을 제공하기 위해 각각의 레벨에서 배열된다. 도전성 피처들(206)은 디바이스층(200)으로부터 도전성 피처들(204)로의 그리고 도전성 피처들(204) 간의 수직 전기적 라우팅을 제공한다. 예를 들어, 상호연결 구조물(250)의 최하부 도전성 피처들(206)은 S/D 영역들(124)(도 1a 및 도 1b) 및 게이트 전극층(138)(도 1a 및 도 1b) 위에 배치된 도전성 콘택트들에 전기적으로 연결될 수 있다. 도전성

피처들(204) 및 도전성 피처들(206)은 금속, 금속 합금, 금속 질화물, 또는 실리사이드와 같은, 하나 이상의 전기 도전성 물질로 제조될 수 있다. 예를 들어, 도전성 피처들(204) 및 도전성 피처들(206)은 구리, 알루미늄, 알루미늄 구리 합금, 티타늄, 티타늄 질화물, 탄탈륨, 탄탈륨 질화물, 티타늄 실리콘 질화물, 지르코늄, 금,은, 코발트, 니켈, 텅스텐, 텅스텐 질화물, 텅스텐 실리콘 질화물, 백금, 크롬, 몰리브덴, 하프늄, 다른 적절한 도전성 물질, 또는 이들의 조합으로부터 제조된다. 일부 실시예들에서, 상호연결 구조물(250)과 유사한 후측 상호연결 구조물(도시되지 않음)이 디바이스층(200)에 대한 전력 공급 및/또는 추가적인 신호 연결을 제공하기위해 디바이스층(200)의 후측 상에 형성될 수 있다.

- [0019] IMD 층(202)은 다양한 도전성 피처들(204, 206)에 대한 격리 기능들을 제공하기 위한 하나 이상의 유전체 물질을 포함한다. IMD 층(202)은 다중 레벨들의 도전성 피처들(204, 206)을 임베딩하는 다중 유전체층들을 포함할수 있다. IMD 층(202)은 SiO<sub>x</sub>, SiO<sub>x</sub>C<sub>y</sub>H<sub>z</sub>, 또는 SiO<sub>x</sub>C<sub>y</sub>와 같은 유전체 물질로 제조되며, 여기서 x, y, z은 정수 또는 비정수이다. 일부 실시예들에서, IMD 층(202)은 약 1 내지 약 5의 범위의 k 값을 갖는 유전체 물질을 포함한다.

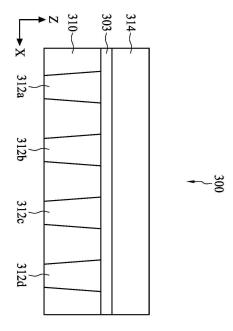

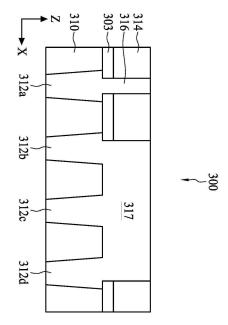

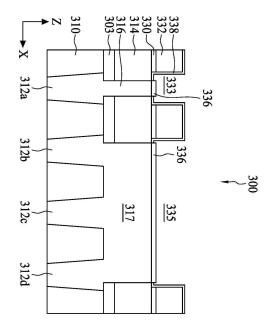

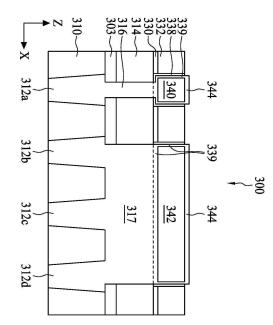

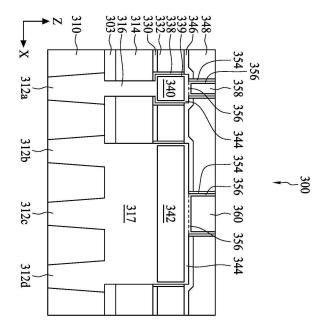

- [0020] 도 3a 내지 도 3p는 일부 실시예들에 따른, 상호연결 구조물(300)을 제조하는 다양한 스테이지들의 측단면도들이다. 상호연결 구조물(300)은 도 1a 및 도 1b뿐만 아니라 도 2에서 도시된 상호연결 구조물(250)의 하나 이상의 층을 형성하기 위해 사용될 수 있다. 도 3a에서 도시된 바와 같이, 상호연결 구조물(300)은 유전체층(310) (예컨대, 제로 레벨 층간 유전체(ILD0)) 및 유전체층(310) 위에 배치된 유전체층(314)(예컨대, 제1 층간 유전체(ILD1))을 포함한다. 유전체층(310)은 유전체층(310) 내에 배치된 하나 이상의 도전성 피처(312a~312d)(312라고 총칭함)을 포함한다. 에칭 정지층(303)은 선택적으로 유전체층(310)과 유전체층(314) 사이에 배치될 수 있다. 유전체층(310, 314)은 ILD 층 또는 IMD 층일 수 있다. 예를 들어, 유전체층(310, 314)은 ILD 층(128)(도 1a 및 도 1b) 또는 IMD 층(202)(도 2)일 수 있다. 유전체층(310, 314)은 ILD 층(128) 또는 IMD 층(202)과 동일한 물질을 포함할 수 있다. 하나의 예시적인 실시예에서, 유전체층(310)은 ILD 층이고, 유전체층(314)은 IMD 층이다.

- [0021] 에칭 정지층(303)은, 사용되는 경우, 유전체층(310) 및 하나 이상의 도전성 피처(312) 상에 형성된다. 에칭 정지층(303)은 단일층 또는 다층 구조물일 수 있다. 일부 실시예들에서, 에칭 정지층(303)은 SiN, SiCO, SiCN, SiCON, SiOx, SiC, SiON, 또는 다른 적절한 물질과 같은, 실리콘 함유 물질을 포함한다. 에칭 정지층(303)은 유전체층(310)과 비교하여 상이한 에칭 선택비를 갖도록 유전체층(310)과는 상이한 물질을 포함할 수 있다. 에칭 정지층(303)은 CVD, ALD, 스핀 온, 또는 임의의 컨포멀 성막 공정과 같은, 임의의 적절한 공정에 의해 형성될 수 있다. 에칭 정지층(303)은 약 1 옹스트롬 내지 약 100 옹스트롬의 범위의 두께를 가질 수 있다.

- [0022] 유전체층(310, 314)은 로우 k 유전체 물질일 수 있다. 예를 들어, 유전체층(310, 314)은 TEOS, 무도핑 실리케이트 유리, 또는 BPSG, 용융 FSG, PSG, BSG, OSG, SiOC, SiOCH, 및/또는 임의의 적절한 로우 k 유전체 물질과 같은, 도핑된 실리콘 산화물에 의해 형성된 산화물일 수 있다. 유전체층(310, 314)은 스핀 온 코팅, CVD, FCVD, PECVD, PVD, 또는 임의의 적절한 성막 기술에 의해 성막될 수 있다. 유전체층(310, 314)의 두께는 175 옹스트롬 내지 약 4500 옹스트롬 범위 내에 있을 수 있다.

- [0023] 도전성 피처들(312)은 Cu, Co, Ru, Mo, Cr, W, Mn, Rh, Ir, Ni, Pd, Pt, Ag, Au, Al, 이들의 합금들, 또는 다른 적절한 물질과 같은, 전기 도전성 물질을 포함한다. 일부 실시예들에서, 도전성 피처들(312)은 금속 함유 탄소이다. 이러한 경우들에서, 도전성 피처들(312) 내의 탄소의 원자 퍼센티지(at.%)는 약 1 at.% 이하일 수 있다. 예를 들어, 도전성 피처들(312)은 약 1 at.% 이하의 탄소를 갖는 Ru일 수 있다. 도전성 피처들(312)은 PVD, CVD, ALD, 또는 다른 적절한 공정에 의해 형성될 수 있다. 일 실시예에서, 도전성 피처들(312)은 CVD 공정에 의해 성막된다. 하나 이상의 도전성 피처(312)는 S/D 영역들(124)(도 1a 및 도 1b)을 게이트 전극층 (138)(도 1a 및 도 1b)에 전기적으로 연결하기 위해 사용될 수 있다. 일부 실시예들에서, 도전성 피처들(312)은 도 2에서 도시된 도전성 라인들 또는 도전성 비아들과 같은, ILD 층(128)에 배치된 도전성 콘택트(예컨대, S/D 콘택트), 또는 IMD 층(202)에 배치된 도전성 피처(204, 206)일 수 있다. 하나의 예시적인 실시예에서, 도전성 피처들(312)은 유전체층(310)과 직접 접촉한다(즉, 도전성 피처들(312)과 유전체층(310) 사이에 배리어가 배치되지 않음). 일부 실시예들에서, 도전성 피처(312)는 유전체층(310)과 도전성 피처(312)의 전기 도전성 물질 사이에 배치된 배리어층(도시되지 않음)을 포함할 수 있다. 배리어층은 금속 또는 금속 질화물과 같은, 전기 도전성 물질을 포함할 수 있다.

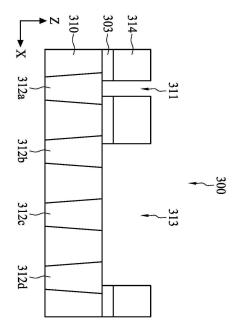

- [0024] 도 3b에서, 도전성 피처들(312)의 최상면을 노출시키기 위해 개구부들(311, 313)이 유전체층(314) 및 에칭 정지

충(303)을 통해 형성된다. 개구부들(311, 313)은 내부에 도전성 피처들(예컨대, 도전성 피처들(204 또는 206))을 형성하기 위해 전기 도전성 물질로 채워지도록 의도된다. 개구부들(311, 313)은 비아 개구부들 또는 라인 개구부들일 수 있고, 하나 이상의 예칭 공정의 결과로서 형성될 수 있다. 일부 실시예들에서, 둘 다의 개구부들(311, 313)은 라인 개구부들이다. 일부 실시예들에서, 둘 다의 개구부들(311, 313)은 라인 개구부들이다. 일부 실시예들에서, 개구부(311)는 비아 개구부이고, 개구부(313)는 라인 개구부이다. 개구부(311)는 제1 폭을 갖고, 개구부(313)는 제1 폭보다 큰 제2 폭을 갖는다. 제1 폭과 제2 폭은 약 1:4 내지 약 1:8의 비율일 수 있다. 일부 실시예들에서, 개구부(311)는 하나의 도전성 피처(예컨대, 도전성 피처(312a)) 바로 위에 있고 이것과 실질적으로 정렬되며, 개구부(313)는 복수의 도전성 피처들(312)(예컨대, 도전성 피처들(312b~312d))을 노출시키도록 형성된다.

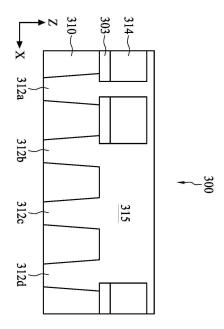

- [0025] 도 3c에서, 개구부들(311, 313)은 전기 도전성 물질(315)로 채워진다. 전기 도전성 물질(315)은 비제한적인 예시로서, Cu, Co, Al, Ru, Mo, W, Ni, Ti, Zr, Ta, Zn, 이들의 합금들, 또는 다른 적절한 물질을 포함할 수 있다. 하나의 예시적인 실시예에서, 개구부들(311, 313)은 Ru와 같은, 도전성 피처들(312)과 동일한 물질로 채워진다. 일부 실시예들에서, 도전성 물질(315)은 금속 함유 탄소이다. 이러한 경우들에서, 도전성 물질(315) 내의 탄소의 원자 퍼센티지(at.%)는 약 1 at.% 이하일 수 있다. 예를 들어, 도전성 물질(315)은 약 1 at.% 이하의 탄소를 갖는 Ru일 수 있다. 도전성 물질(315)은 ECP, 무전해 성막(electroless deposition; ELD), PVD, 또는 CVD와 같은, 임의의 적절한 공정을 사용하여 성막될 수 있다. 도전성 물질(315)은 도전성 물질의 높이가 유전체층(314) 상에 성막될 때까지 개구부들(311, 313)을 과충전할 수 있다. 도전성 물질(315)은 도전성 물질(315)과 유전체층(314)(또는 예칭 정지층(303)) 사이에 형성된 어떠한 배리어층 또는 라이너도 없이 개구부들(311, 313) 내에 성막된다.

- [0026] 도 3d에서, 유전체층(314)이 노출될 때까지 도전성 물질(315)에 대해 CMP 공정과 같은 평탄화 공정이 수행된다. 일부 실시예들에서, 유전체층(314)의 일부가 제거될 수 있다. 평탄화 공정 후에, 유전체층(314) 내에 도전성 피처들(316, 317)이 형성되고, 도전성 피처들(316, 317)과 유전체층(314)의 최상면들은 실질적으로 동일 평면 상에 있다. 도전성 피처들(316, 317)은 도전성 피처(206)(도 2)일 수 있다. 예를 들어, 도전성 피처들(316, 317)은 소스/드레인 콘택트들(예를 들어, 도전성 피처들(312))을 위한 도전성 비아들일 수 있다. 하나의 예시 적인 실시예에서, 도전성 피처들(316, 317)은 유전체층(314) 및 에칭 정지층(303)(사용되는 경우)과 직접 접촉한다.

- [0027] 도전성 피처들(316, 317)이 확산에 취약한 금속(예컨대, Cu)을 포함하는 경우들에서, 도전성 피처들(316, 317) 로부터 유전체층(314)으로의 금속 확산을 방지하기 위해 유전체층(314)과 도전성 피처들(316, 317) 사이에 배리 어층이 형성될 수 있다. 일부 실시예들에서, 배리어층과 도전성 피처들(316, 317) 사이에 라이너가 추가로 형성될 수 있다. 라이너는 도전성 피처들(316, 317) 및 배리어층 둘 다가 라이너에 부착되도록 접착층으로서 기능할 수 있다. 배리어층 및 라이너는 CVD, PECVD, 또는 ALD와 같은, 임의의 적절한 공정에 의해 형성될 수 있다. 일부 실시예들에서, 배리어층 및 라이너는 ALD에 의해 형성된 컨포멀층들이다. 사용되는 경우, 배리어층은 Ta, Ti, Mn, Zn, In, TaN, TiN, 또는 다른 적절한 물질을 포함할 수 있다. 라이너는 CO와 같은 금속을 포함할 수 있다. 대안적으로, 라이너는 도전성 피처들(316, 317)과 동일한 물질을 포함할 수 있다. 일부 실시예들에서, 도전성 피처들(316, 317)은 Ru 또는 Co와 같은 확산에 취약하지 않은 금속을 포함하고, 배리어층 및 라이너는 생략될 수 있다.

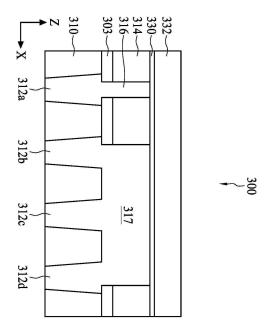

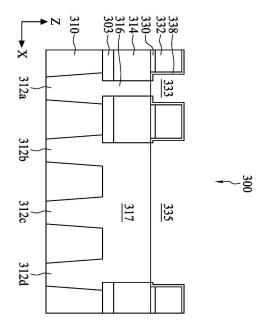

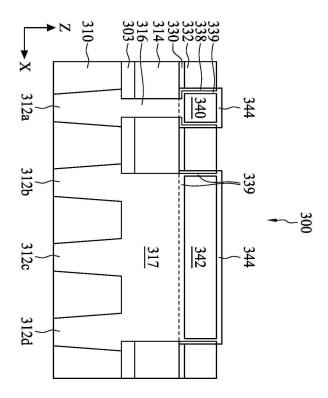

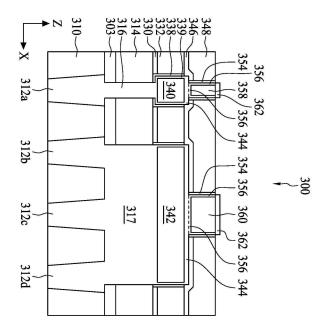

- [0028] 도 3e에서, BEOL(back-end-of-line) 상호연결 구조물을 위한 제1 에칭 정지층(330) 및 제1 유전체층(332)이 유전체층(314) 상에 형성된다. 제1 유전체층(332)은 유전체층(202)(도 2)일 수 있다. 제1 유전체층(332)은 유전체층(310, 314)과 동일한 물질을 포함할 수 있고, 유전체층(310, 314)과 동일한 공정에 의해 형성될 수 있다. 제1 에칭 정지층(330)은 제1 유전체층(332)과 비교하여 상이한 에칭 선택비를 갖기 위해 제1 유전체층(332)과는 상이한 물질을 포함할 수 있다. 일부 실시예들에서, 제1 에칭 정지층(330)은 산화물, 질화물, 금속 산화물, 금속 산화물, 금속 질화물, 또는 이들의 조합과 같은, 유전체 물질로 제조된다. 제1 에칭 정지층(330)을 위한 적절한 물질들은, 비제한적인 예시로서, 실리콘 질화물, 실리콘 탄화물, 산소 도핑된 실리콘 탄화물(oxygen-doped silicon carbide; ODC), 실리콘 탄소 절화물, 실리콘 산질화물, 탄소 질화물, 실리콘 산화물, 실리콘 산화물, 실리콘 산화물, 일리콘 탄소 산화물, 및 알루미늄 산화물 등을 포함할 수 있다. 제1 에칭 정지층(330)은 단일층 또는 다층 구조물일 수 있다. 일부 실시예들에서, 제1 에칭 정지층(330)은 탄화물 및 질화물을 포함한다. 일부 실시예들에서, 제1 에칭 정지층(330)은 본원에서 논의되는 둘이상의 유전체 물질층들을 포함할 수 있다. 제1 에칭 정지층(330)이 다층 구조물인 경우, 각각의 층은 상이한 비율, 조성, 및/또는 산화 레이트를 갖는 동일한 유전체 물질을 포함할 수 있다. 제1 에칭 정지층(330)은 CVD,

ALD, PVD, PEALD, 또는 PECVD와 같은, 임의의 적절한 공정에 의해 형성될 수 있다.

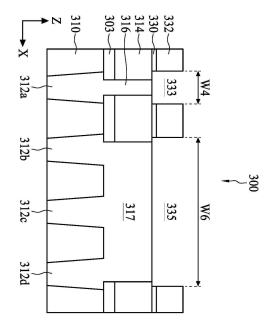

- [0029] 도 3f에서, 도전성 피처들(316, 317)의 일부를 각각 노출시키기 위해, 개구부들(333, 335)이 제1 유전체층(332) 및 제1 에칭 정지층(330) 내에 그리고 이를 관통하여 형성된다. 개구부(333)는 도전성 피처들(316) 중 적어도하나 위에 배치된다. 개구부들(333, 335)은 비아 또는 라인 개구부들일 수 있고, 도전성 물질로 채워져서 그 안에 도전성 피처들을 형성하도록 의도된다. 개구부들(333, 335)은 하나 이상의 에칭 공정과 같은 임의의 적절한 공정에 의해 형성될 수 있다. 에칭 공정들은 제1 유전체층(332) 및 제1 에칭 정지층(330)의 일부를 제거하여 개구부(333)가 대응하는 도전성 피처(316)의 최상면의 일부를 노출시키도록 한다. 마찬가지로, 에칭 공정들은 제1 유전체층(332) 및 제1 에칭 정지층(330)의 일부를 제거하여 개구부(335)가 대응하는 도전성 피처(317)의 최상면의 일부를 노출시키도록 한다. 일부 실시예들에서, 개구부(333)는 비아 개구부이고, 개구부(335)는 라인 개구부이다. 개구부들(333, 335)은 일반적으로 도전성 피처들(316, 317)의 직경보다 큰 직경을 각각 갖는다. 일부 실시예들에서, 개구부(333)는 치수(W4)를 가질 수 있고, 개구부(335)는 치수(W4)보다 큰 치수(W6)를 가질수 있다. 일부 실시예들에서, 치수(W4)와 치수(W6)는 약 1:3 내지 1:35의 범위 내의 비율(W4:W6)을 가질 수 있다.

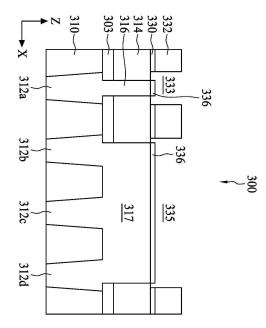

- [0030] 도 3g에서, 차단층(336)이 도전성 피처들(316, 317)의 노출된 최상면 상에 선택적으로 형성된다. 차단층(336)은 후속 제1 배리어층(338)이 도전성 피처들(316, 317)의 노출된 최상면 상에 형성되는 것을 방지하기 위해 사용된다. 일부 실시예들에서, 차단층(336)은 CVD, ALD, 습식 코팅, 침지 공정, 또는 다른 적절한 방법들의 사용을 통해 도전성 피처들(316, 317)의 최상면을 차단제에 노출시킴으로써 형성될 수 있다. 차단제는 도전성 피처들(316, 317)의 금속성 표면에 선택적으로 부착되도록 구성된 하나 이상의 억제제를 포함할 수 있다. 적절한 억제제는, 비제한적인 예시로서, 베조트리아졸(C<sub>6</sub>H<sub>5</sub>N<sub>3</sub>), 벤지이미다졸(C<sub>7</sub>H<sub>6</sub>N<sub>2</sub>), 톨릴트리아졸(C<sub>7</sub>H<sub>7</sub>N<sub>3</sub>), 옥살산(C<sub>2</sub>H<sub>2</sub>O<sub>4</sub>), 말론산(C<sub>3</sub>H<sub>4</sub>O<sub>4</sub>), 시트르산(C<sub>6</sub>H<sub>5</sub>O<sub>7</sub>), 젖산(C<sub>3</sub>H<sub>6</sub>O<sub>3</sub>), 에틸렌디아민테트라아세트산(C<sub>1</sub>OH<sub>16</sub>N<sub>2</sub>O<sub>8</sub>), 테트라아세트산(C<sub>1</sub>H<sub>1</sub>H<sub>24</sub>N<sub>2</sub>O<sub>10</sub>), 펜테트산(C<sub>1</sub>H<sub>2</sub>A<sub>3</sub>N<sub>3</sub>O<sub>10</sub>), 및 니트릴로트리아세트산(C<sub>6</sub>H<sub>9</sub>NO<sub>6</sub>) 등을 포함할 수 있다. 다른 실시예들에서, 차단제는 크롬산염, 질산염, 몰리브산염 및 인산염과 같은 무기 억제제들, 및 아연 및 폴리포스페이트 억제제들과 같은 캐소드형 억제제들을 포함할 수 있다.

- [0031] 일부 실시예들에서, 차단층(336)은 작은 분자 또는 폴리머를 포함하는 유기 물질일 수 있다. 차단층(336)은 머리기(head group) 및 꼬리기(tail group)를 갖는 하나 이상의 자체 조립 단층(self-assembled monolayer; SA M)을 포함할 수 있다. SAM의 머리기는 도전성 피처들(316, 317)의 물질에 따라 선택될 수 있다. 예를 들어, SAM의 머리기는 Ru가 도전성 피처들(316, 317)로서 사용될 때 알킨기로 종단된 화합물을, 또는 Cu 또는 Co가 도전성 피처들(316, 317)로서 사용될 때 아졸기 함유 화합물을 포함할 수 있다. 일부 실시예들에서, SAM의 머리기는 도전성 피처들(316, 317)의 금속성 표면들에만 부착될 수 있는 인(P), 황(S), 실리콘(Si), 또는 질소(N) 종단 화합물을 포함할 수 있다. SAM의 머리기는 제1 유전체층(332) 및 제1 에칭 정지층(330)의 유전체 표면 상에 형성되지 않을 수 있다. SAM의 꼬리기는 전구체(예컨대, 후속 제1 배리어층(338)을 형성하기 위한 전구체)의 흡착이 차단층(336) 상에 형성되는 것을 차단하는 고소수성(highly hydrophobic) 긴 알킬 사슬을 포함할 수 있다. 일부 실시예들에서, 꼬리기는 폴리이미드와 같은 폴리머를 포함한다. 차단층(336)은, 예컨대 CVD, ALD, 분자층 성막(molecular layer deposition; MLD), 습식 코팅, 침지 공정, 또는 다른 적절한 방법에 의해, 노출된 표면들에 차단제를 공급함으로써 형성될 수 있다.

- [0032] 일부 실시예들에서, 차단층(336)은 습식 코팅 공정에 의해 형성되고, 습식 코팅을 위한 용액은 알코올, 카르복 실산, 또는 이들의 조합과 같은 양성자성(protic) 유기 용매일 수 있다. 예시적인 양성자성 유기 용매들은, 비 제한적인 예시로서, 메탄올, 에탄올, 1-프로판올, 2-프로판올, 1-부탄올, 1-펜타놀, 1-헥산놀, 1-헵탄올, 2-에 톡시에탄올, 및 이들의 혼합물들을 포함할 수 있다. 습식 코팅을 위한 용액은 또한 극성 또는 비극성 양성자성 용매일 수 있다. 예시적인 극성 비양성자성(aprotic) 용매들은, 비제한적인 예시로서, N,N-디메틸포름아미드, N-메틸-2-피롤리디논, 아세토니트릴, 아세톤, 에틸 아세테이트, 벤질 에테르, 트리옥틸포스핀, 트리옥틸포스핀 산화물, 및 이들의 혼합물을 포함할 수 있다. 예시적인 비극성 양성자성 용매들은, 비제한적인 예시로서, 알칸, 올레핀, 방향족, 에스테르 또는 에테르 용매, 헥산, 옥탄, 벤젠, 톨루엔, 크실렌, 및 이들의 혼합물들을 포함할 수 있다.

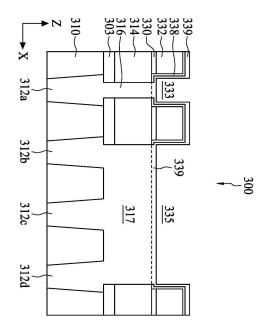

- [0033] 도 3h에서, 제1 배리어층(338)이 제1 유전체층(332), 제1 에칭 정지층(330), 및 유전체층(314) 상에 선택적으로 성막된다. 제1 배리어층(338)은 후속 도전성 피처들(340, 342)로부터 유전체층(314) 및 제1 유전체층(332)으로 의 금속 확산을 방지하는 역할을 한다. 제1 배리어층(338)은 금속 질화물, 금속 산화물, 2차원(2D) 물질, 또는 이들의 조합을 포함할 수 있다. 제1 배리어층(338)을 위한 적절한 금속들은, 비제한적인 예시로서, Ta, Ti, W,

Mn, Zn, In, 또는 Hf를 포함할 수 있다. 일부 실시예들에서, 제1 배리어층(338)은 TaN, TiN 또는 WN과 같은 금속 질화물, 또는 HFO와 같은 금속 산화물이다. 하나의 예시적인 실시예에서, 제1 배리어층(338)은 TaN이다. 본 개시에서 사용되는 용어 "2D 물질"은 층내 공유 본딩 및 층간 반 데르 발스 본딩을 갖는 원자적으로 얇은 결정질 고체인 단일층 물질 또는 단층형 물질을 지칭한다. 2D 물질의 예시들은, 그래핀, 육각형 붕소 질화물(h-BN), 또는 전이 금속 디칼코게나이드(MX<sub>2</sub>)를 포함할 수 있으며, 여기서 M은 전이 금속 원소이고 X는 칼코게나이드 원소이다. 일부 예시적인 MX<sub>2</sub> 물질은, 비제한적인 예시로서, Hf, Te<sub>2</sub>, WS<sub>2</sub>, MoS<sub>2</sub>, WSe<sub>2</sub>, MoSe<sub>2</sub>, 또는 이들의 임의의 조합을 포함할 수 있다.

- [0034] 차단층(336)이 도전성 피처들(316, 317)의 금속성 표면들 상에 형성되면, 제1 배리어층(338)은 제1 유전체층 (332), 제1 에칭 정지층(330), 및 유전체층(314)의 노출된 유전체 표면들 상에 선택적으로 형성되지만, 차단층 (336) 상에는 형성되지 않는다. 차단층(336)은 제1 배리어층(338)이 도전성 피처들(316, 317)의 금속성 표면 상에 형성되는 것을 차단할 수 있다. 구체적으로, 차단층(336)은 제1 배리어층(338)의 전구체(들)이 도전성 피처들(316, 317) 상에 형성되는 것을 차단하고, 따라서 제1 배리어층(338)의 전구체(들)은 제1 유전체층(332), 제1 에칭 정지층(330), 및 유전체층(314)의 표면들과 같은, 유전체 표면들 상에서 성장한다. 제1 배리어층 (338)의 선택적 성막은 또한 ALD 공정 및/또는 MLD 공정의 사용을 통해 달성되고/달성되거나 강화될 수 있고, 그에 따라, 제1 배리어층(338)은 자기-제한 표면 반응들을 통해 제1 유전체층(332), 제1 에칭 정지층(330), 및 유전체층(314)과의 본딩에서 특유적인 특성 또는 속성을 갖는다.

- [0035] 도 3i에서, 차단층(336)은 도전성 피처들(316, 317)의 최상면을 노출시키기 위해 제거된다. 차단층(336)은 열 저하 또는 플라즈마 충격, 또는 다른 적절한 공정을 사용하여 제거될 수 있다. 제거 공정은 제1 배리어층(338) 및 도전성 피처(316, 317)에 실질적으로 영향을 미치지 않는다.

- [0036] 도 3j에서, 제1 라이너(339)가 제1 배리어층(338) 상에 성막된다. 제1 라이너(339)는 제1 배리어층(338)에 대한 후속 도전성 피처들(340, 342)의 더 나은 접착을 가능하게 하기 위한 접착층으로서 역할을 한다. 도 5에서 더 상세히 논의될 바와 같이, 후속 도전성 피처들(340, 342)의 바닥면과 접촉하는 제1 라이너(339)의 일부는 도전성 피처들(340, 342)이 도전성 피처들(316, 317) 내로 확산되는 것을 방지하기 위해 더 두꺼운 두께를 가질수 있다. 제1 라이너(339)는 도전성 피처들(316, 317)과 동일한 물질을 포함할 수 있고, ALD와 같은, 컨포멀공정에 의해 형성될 수 있다. 제1 라이너(339)를 위한 적절한 물질은, 비제한적인 예시로서, Ru, Co, Mn, Zn, Zr, W, Mo, Os, Ir, Al, Fe, Ni, 이들의 합금들, 또는 이들의 조합들을 포함할 수 있다. 일부 실시예들에서, 제1 라이너(339)는 Ru 또는 Co이다. 일부 실시예들에서, 제1 라이너(339)는 Co 부재(Co-free) 층이다. 하나의 예시적인 실시예에서, 제1 라이너(339)는 순수 루테늄(Ru)이다. 본 개시에서 설명된 용어 "순수 Ru"는 약 99 at.% 이상의 농도를 갖는 루테늄을 지칭한다. 루테늄의 사용은, 도전성 피처들(340, 342)의 성막 공정 동안 Cu 리플로우를 제한하지 않고서 Cu와의 적절한 접착을 유지하는 것을 돕기 때문에, 후속 도전성 피처들(340, 342)을 위해 구리(Cu)가 사용될 때 유리할 수 있다. 제1 배리어층(338) 및 제1 라이너(339)는 각각 약 3 옹스트롬 내지 약 100 옹스트롬의 범위의 두께를 가질 수 있다.

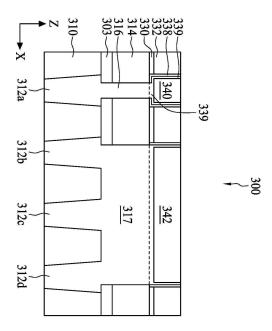

- [0037] 도 3k에서, 도전성 피처들(340, 342)이 개구부들(333, 335)(도 3j)에 각각 형성되고, CMP 공정과 같은 평탄화 공정이 수행된다. 도전성 피처들(340, 342)은 개구부들(333, 335)(도 3j) 내에 도전성 물질을 채움으로써 형성 될 수 있다. 일부 실시예들에서, 도전성 피처들(340, 342)은 둘 다 도전성 비아들이다. 일부 실시예들에서, 도전성 피처들(340, 342)은 둘 다 도전성 라인들이다. 일부 실시예들에서, 도전성 피처(340)는 도전성 비아이 고, 도전성 피처(342)는 도전성 라인이거나, 또는 그 반대이다. 도전성 피처들(340, 342)은 Cu, Ru, W, Ni, Al, Co, 이리듐(Ir), 오스뮴(OS), 금(Au), 팔라듐(Pd), 백금(Pt), 은(Ag), 탄탈륨(Ta), 티타늄(Ti), 또는 이들 의 합금들과 같은, 임의의 적절한 도전성 물질을 포함할 수 있다. 일부 실시예들에서, 도전성 피처들(340, 342)은 제1 라이너(339) 및 도전성 피처들(316, 317)과는 화학적으로 상이한 도전성 물질을 포함한다. 하나의 예시적인 실시예에서, 도전성 피처들(340, 342)은 Cu를 포함한다. 도전성 피처들(340, 342)은 PVD, CVD, ALD, 전기도금, ELD, 또는 다른 적절한 성막 공정, 또는 이들의 조합을 사용하여 성막될 수 있고, 그 다음에 평탄화 공정이 이어진다. 상호연결 구조물(300)은 제1 유전체층(332) 내에 형성된 도전성 피처들(340, 342)을 포함한 다. 도전성 피처(340)는 제1 치수를 가질 수 있고, 도전성 피처(342)는 제1 치수보다 큰 제2 치수를 가질 수 있다. 도전성 피처들(340, 342)은 각각 유전체층(314) 내의 도전성 피처들(316, 317)과 직접 접촉해 있는, 아 래의 제1 라이너(339)와 직접 접촉한다. 제1 라이너(339)는 도전성 피처들(316, 317)과 동일한 물질을 포함할 수 있기 때문에, 도전성 피처들(340, 342)은 도전성 피처들(316, 317)과 직접 접촉하는 것으로서 간주될 수 있 다. 도전성 피처들(316, 317)과 직접 접촉하는 도전성 피처들(340, 342)은 직접적 금속 대 금속 접촉으로 인해 가장 낮은 전기 저항을 가질 수 있다. 또한, 도전성 피처(340)와 도전성 피처(316) 사이 또는 도전성 피처

(342)와 도전성 피처(317) 사이에는 배리어층이 없기 때문에, 도전성 피처들(340, 342)의 접촉 저항이 감소될 수 있다.

- [0038] 도 31에서, 제1 캡 층(344)이 도전성 피처(340) 및 도전성 피처(342) 상에 선택적으로 형성된다. 제1 캡 층 (344)은 제1 라이너(339)의 최상면을 덮도록 더 연장될 수 있다. 제1 배리어층(338) 및 제1 라이너(339)가 동일한 금속들을 포함하는 일부 대안적인 실시예들에서, 도 31a에서 도시된 바와 같이, 제1 캡 층(344)이 또한 제1 배리어층(338) 및 제1 라이너(339) 상에 형성된다. 하나의 예시적인 실시예에서, 제1 캡 층(344)은 제1 라이너(339), 도전성 피처(340), 및 도전성 피처(342)의 최상면을 덮도록 성막된다. 제1 캡 층(344)은 CVD, ALD, 또는 PVD와 같은, 임의의 적절한 공정에 의해 형성될 수 있다. 일부 실시예들에서, 제1 유전체층(332)의 노출된 표면들은 먼저 소수성 작용기들을 함유하는 가스로 처리될 수 있고, 소수성 작용기들은 제1 유전체층(332)의 노출된 표면들 상에 형성된다. 소수성 작용기를 함유하는 가스는 도전성 피처(340), 도전성 피처(342), 제1 라이너(339), 및 제1 배리어층(338)의 금속성 표면들과 반응하지 않는다. 제1 유전체층(332)의 노출된 표면들 상에 형성된 소수성 작용기들은 제1 캡 층(344)이 제1 유전체층(332) 상에 형성되는 것을 차단한다. 어느 경우든, 제1 캡 층(344)은 도전성 피처(340), 도전성 피처(342), 제1 라이너(339), 및 선택적으로 제1 배리어층 (338)의 금속성 표면 상에 선택적으로 형성되고, 제1 유전체층(332)의 유전체 표면들 상에는 형성되지 않는다.

- [0039] 일부 실시예들에서, 제1 캡 층(344)은 제1 라이너(339)와 동일한 물질(예를 들어, Ru)을 포함한다. 일부 실시예들에서, 제1 캡 층(344)은 제1 라이너(339) 및 도전성 피처들(316, 317)과 동일한 물질(예를 들어, Ru)을 포함한다. 제1 캡 층(344)은 도전성 피처들(340, 342)과는 화학적으로 상이한 물질을 포함할 수 있다. 일부 대안적인 실시예들에서, 제1 캡 층(344)은 제1 라이너(339) 또는 도전성 피처들(316, 317)과는 화학적으로 상이한물질을 포함한다. 예를 들어, 제1 캡 층(344)은 제1 라이너(339) 또는 도전성 피처들(316, 317)의 물질보다 상대적으로 더 높은 탄소 용해도를 갖는 금속을 포함할 수 있다. 이러한 경우들에서, 제1 캡 층(344)은 Co, Ni, W, Mo, Ru를 포함하거나 또는 이것들로 제조될 수 있고, 도전성 피처들(340, 342)은 Cu를 포함하거나 또는 이것으로 제조될 수 있다.

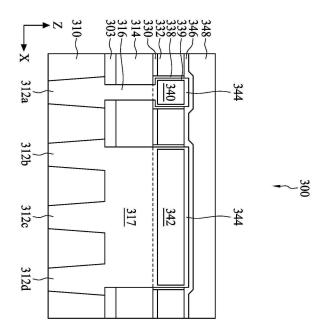

- [0040] 도 3m에서, 제1 유전체층(332), 제1 캡 층(344), 및 제1 배리어층(338)의 노출된 표면들(제1 캡 층(344)에 의해 이전에 덮이지 않은 경우) 상에 제2 에칭 정지층(346)이 형성된다. 이어서, 제2 에칭 정지층(346) 상에 제2 유전체층(348)이 형성된다. 제2 에칭 정지층(346) 및 제2 유전체층(348)은 각각 제1 에칭 정지층(330) 및 제1 유전체층(332)과 동일한 물질을 포함할 수 있고, 도 3e와 관련하여 위에서 논의된 바와 동일한 성막 기술을 사용하여 성막될 수 있다. 제2 에칭 정지층(346)은 제1 캡 층(344)의 노출된 표면들(예컨대, 최상면 및 측벽면)을 덮도록 성막된다. 따라서, 제2 에칭 정지층(346)은 제1 캡 층(344) 위에서 단차 높이를 형성하도록 제1 캡 층(344)과 제1 유전체층(332)의 프로파일을 따른다.

- [0041] 도 3n에서, 개구부들(350, 352)이 제1 캡 층(344)의 일부를 노출시키기 위해 제2 유전체층(348)과 제2 에칭 정지층(346) 내에 그리고 이를 관통하여 형성된다. 개구부(350)는 도전성 피처(340) 위에 배치되고, 개구부(352)는 도전성 피처(342) 위에 배치된다. 개구부들(350, 352)은 비아 또는 라인 개구부들일 수 있고, 도전성 물질로 채워져서 그 안에 도전성 피처들을 형성하도록 의도된다. 개구부들(350, 352)은 하나 이상의 에칭 공정과 같은 임의의 적절한 공정에 의해 형성될 수 있다. 에칭 공정들은 제2 유전체층(348) 및 제2 에칭 정지층(346)의 일부를 제거하여 개구부들(350, 352) 각각이 대응하는 제1 캡 층(344)의 최상면의 일부를 노출시키도록한다. 일부 실시예들에서, 개구부들(350, 352)은 둘 다 비아 개구부들이다. 개구부(350)와 개구부(352)는 각 각 도전성 피처들(340, 342)의 직경보다 작은 직경을 가질 수 있다.

- [0042] 개구부들(350, 352)이 형성된 후, 개구부들(350, 352) 내에 제2 배리어층(354) 및 제2 라이너(356)가 형성된다. 제2 배리어층(354) 및 제2 라이너(356)는 도 3g~도 3j와 관련하여 위에서 논의된 제1 배리어층(338) 및 제1 라이너(339)와 유사한 방식으로 형성될 수 있다. 제2 라이너(356)는 제1 캡 층(344)과 동일한 물질을 포함할 수 있다. 제2 배리어층(354)은 제1 배리어층(338)과 동일한 물질을 포함할 수 있고, 제2 라이너(356)는 제1 라이너(339)와 동일한 물질을 포함할 수 있다. 일부 실시예들에서, 제2 라이너(356)는 Co 부재 층이다. 일부 실시예들에서, 제2 배리어층(354)은 제1 배리어층(338)과는 화학적으로 상이한 물질을 포함할 수 있고, 제2 라이너(356)는 제1 라이너(339)와는 화학적으로 상이한 물질을 포함할 수 있다. 일 실시예에서, 제2 배리어층(354)은 TaN이고, 제2 라이너(356)는 Ru이다. 하나의 예시적인 실시예에서, 제2 라이너(356)는 Ru이고, 제1 캡 층(344)은 Ru이고, 제1 캡 층(344)은 Ru이고, 제1 캡 층(344)은 Ru이고, 제1 배리어층(338)은 TaN이고, 제1 라이너(339)는 Ru이다.

- [0043] 도 3o에서, 도전성 피처들(358, 360)이 개구부들(350, 352)(도 3n)에 각각 형성되고, CMP 공정과 같은 평탄화

공정이 수행된다. 도전성 피처들(358, 360)은 도 3k와 관련하여 위에서 논의된 것과 유사한 방식으로 개구부들 (350, 352) 내에 도전성 물질을 채움으로써 형성될 수 있다. 도전성 피처들(358, 360)은 도전성 피처들(340, 342)과 동일한 물질을 포함할 수 있고, 도전성 피처들(340, 342)과 동일한 성막 기술을 사용하여 성막될 수 있다. 하나의 예시적인 실시예에서, 도전성 피처들(358, 360)은 Cu를 포함한다.

- [0044] 상호연결 구조물(300)은 제2 유전체층(348) 내에 형성된 도전성 피처들(358, 360)을 포함한다. 도전성 피처 (358)는 제1 치수를 가질 수 있고, 도전성 피처(360)는 제1 치수보다 큰 제2 치수를 가질 수 있다. 도전성 피처들(358, 360)은 각각 제1 캡 층(344) 상에 배치된 제2 라이너(356)와 직접 접촉한다. 도전성 피처들(358, 360)과 도전성 피처들(340, 342) 사이의 제2 라이너(356) 및 제1 캡 층(344)은 둘 다 금속이기 때문에, 도전성 피처들(358, 360)의 접촉 저항이 감소된다.

- [0045] 도 3p에서, 도전성 피처들(358, 360) 상에 제2 캡 층(362)이 선택적으로 형성된다. 제2 배리어층(354) 및 제2 라이너(356)가 금속들을 포함하는 경우들에서, 제2 캡 층(362)은 또한 제2 배리어층(354) 및 제2 라이너(356)상에 형성된다. 일부 실시예들에서, 제2 캡 층(362)은 도전성 피처들(358, 360), 제2 라이너(356), 및 선택적으로 제2 배리어층(354)의 금속성 표면들 상에 선택적으로 형성되고, 제2 유전체층(348)의 유전체 표면들 상에는 형성되지 않는다. 하나의 예시적인 실시예에서, 제2 캡 층(362)은 제2 라이너(356)및 도전성 피처들(358, 360)의 최상면들을 덮도록 성막된다. 제2 캡 층(362)은 위에서 논의된 제1 캡 층(344)과 유사한 방식으로 성막될수 있다. 제2 캡 층(362)은 제2 라이너(356)및 도전성 피처들(358, 360)과는 화학적으로 상이한 물질을 포함할수 있다. 일부 실시예들에서, 제2 캡 층(362)은 제1 캡 층(344)과 동일한 물질을 포함한다. 일부 실시예들에서, 제2 캡 층(362)은 제1 캡 층(344)과는 화학적으로 상이한 물질을 포함한다. 일 실시예에서, 제2 캡 층(362)은 Ru이다. 다른 실시예에서, 제2 캡 층(362)은 Co이다. 어느 경우든, 제2 배리어층(354)은 TaN일수 있고, 제2 라이너(356)는 Ru일수 있다. 하나의 예시적인 실시예에서, 제2 캡 층은 Co 또는 Ru이고, 제2 라이너(356)는 Ru이고, 제1 캡 층(344)은 Ru이고, 제1 라이너(339)는 Ru이다. 하나의 예시적인 실시예에서, 제2 캡 층은 Co 또는 Ru이고, 제2 래리어층(354)은 TaN이고, 제2 라이너(356)는 Ru이고, 제1 캡 층(344)은 Ru이고, 제1 라이너(339)는 Ru이다.

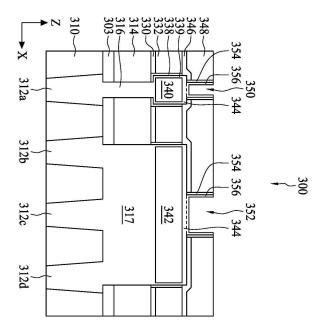

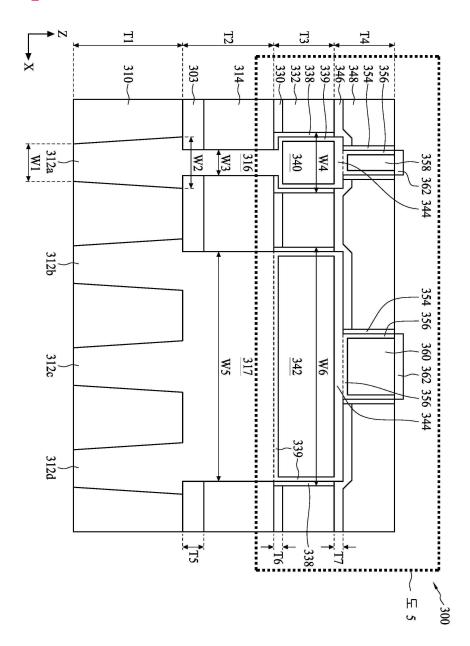

- [0046] 전통적인 상호연결 구조물들에서는, 루테늄이 도전성 피처들(312, 316, 317)을 위해 사용되고, 코발트가 제1 캡 충(344), 제1 라이너(339), 및 제2 라이너(356)를 위해 사용될 때, 고온(예컨대, 약 300℃ 이상)에서의 Ru/Co 상호혼합 및 MO/M1 계면에서의 Co 공핍으로 인해, 제1 캡 충(344) 및 도전성 피처들(340, 342) 근처의 Co/Cu 계 면들에서 물질 손실 및 이에 따른 보이드 형성이 발생할 것임이 관찰되었다. 모든 도전성 피처들(312, 316, 317), 제1 및 제2 라이너들(339, 356), 및 제1 캡 충(344)에 대한 순수 루테늄의 사용은 도전성 피처들(340, 342)과 인접한 충들 사이의 농도 구배 차이를 생성하지 않고 본질적 비호환성을 최소화시킨다. 결과적으로, 제 1 캡 충(344) 내의 물질(예컨대, Co)이 도전성 피처들(316, 317) 및/또는 제1 및 제2 라이너들(339, 356) 내로 확산되고 이들 내의 Ru와 혼합되는 것이 방지되어, 상호연결 구조물(300)의 접촉 신뢰성을 개선시킨다. 특히, 소스/드레인 콘택트 비아들(예컨대, 도전성 피처들(316, 317))과, 인접한 유전체충들(예컨대, 유전체충(314))은 물론 MO 콘택트들(예컨대, 도전성 피처들(340, 342) 사이에는 배리어충이 필요하지 않다. 또한, 도전성 피처들 (316, 317), 제1 및 제2 라이너들(339, 356), 및 제1 캡 충(344)은 모두 종래의 상호연결 구조물들에서 존재하는 이종 Ru/Co 계면(높은 접촉 저항)보다는 Ru를 사용하므로, 도전성 피처(340)와 도전성 피처(316)의 계면에서의 접촉 저항은, 예를 들어, 약 80 옴에서 약 40~60 옴으로, 또는 일부 경우들에서 32 옴에서 약 12 옴으로 효과적으로 감소될 수 있다.

- [0047] 두 개의 IMD 층들(예컨대, 제1 및 제2 유전체층들(332, 348)) 및 도전성 피처들(예컨대, 도전성 피처들(340, 342, 358, 360))만이 도시되고 논의되지만, 도 3e 내지 도 3p와 관련하여 위에서 논의된 공정들을 반복함으로써 더 많은 IMD 층들이 제조될 수 있다는 것이 고려된다.

- [0048] 도 4는 일부 실시예들에 따른, 상호연결 구조물(300)의 일부를 예시한다. 도전성 피처들(312, 316, 317, 340, 342, 358, 360)의 측벽들은 경사지거나 또는 수직일 수 있다. 일부 실시예들에서, 유전체층(310) 내의 도전성 피처들(312)(예컨대, 도전성 피처(312a))의 측벽들은 경사져 있고, 도전성 피처들(316, 317, 340, 342, 358, 360)은 실질적으로 수직일 수 있다. 이러한 경우들에서, 도전성 피처들(312)은 각각 치수가 Z 방향을 따라 점 진적으로 감소되는 측벽 프로파일을 가질 수 있다. 도전성 피처(312) 각각의 최상단에서의 치수(W2)는 도전성 피처(312)의 최하단에서의 치수(W1)보다 크다. 응용에 따라, 치수(W1)와 치수(W2)는 약 1:1.2 내지 약 1:3의 비율(W1:W2)로 있을 수 있다. 도전성 피처(312a) 위의 도전성 피처(316)는 치수(W3)를 가질 수 있고, 치수(W1)와 치수(W3)는 차수(W3)는 약 1:1 내지 약 1:2의 비율(W1:W3)로 있을 수 있다. 도전성 피처(316) 위의 도전성 피처(340)는 치수(W4)를 가질 수 있고, 치수(W1)와 치수(W4)는 약 1:1.25 내지 약 1:3의 비율(W1:W4)로 있을 수 있

다. 치수(W3)는 치수(W1) 및 치수(W4)보다 작다. 도전성 피처(317)는 치수(W5)를 가질 수 있고, 치수(W1)와 치수(W5)는 약 1:6 내지 약 1:20의 비율(W1:W5)로 있을 수 있다.

- [0049] 응용에 따라, 도전성 피처(312)는 높이(T1)를 가질 수 있고, 도전성 피처들(316, 317)은 높이(T2)를 가질 수 있다. 높이(T1)와 높이(T2)는 약 1:1 내지 약 1:0.8의 비율(T1:T2)로 있을 수 있다. 도전성 피처들(340, 342)과 제1 라이너(339)는 통합된 높이(T3)를 가질 수 있고, 도전성 피처들(358, 360), 제2 라이너(356), 및 제1 캡층(344)은 통합된 높이(T4)를 가질 수 있다. 높이(T3)와 높이(T4)는 약 1:1의 비율(T3:T4)로 있을 수 있다. 에칭 정지층(303)은 두께(T5)를 가질 수 있고, 높이(T2)와 두께(T5)는 약 1:0.6 내지 약 1:0.75의 비율(T2:T5)로 있을 수 있다. 제1 에칭 정지층(330)은 두께(T6)를 가질 수 있고, 높이(T3)와 두께(T6)는 약 1:0.6 내지약 1:0.75의 비율(T3:T6)로 있을 수 있다. 제2 에칭 정지층(346)은 두께(T7)를 가질 수 있고, 높이(T4)와 두께(T7)는 약 1:0.6 내지약 1:0.75의 비율(T4:T7)로 있을 수 있다.

- [0050] 도 5는 일부 실시예들에 따른 금속간 유전체(IMD) 충들(예컨대, M0, M1)을 보여주는 상호연결 구조물(300)의 일부의 확대도를 예시한다. 제1 배리어충(338)와 제2 배리어충(354)은 두께(T8)를 가질 수 있고, 제1 라이너 (339)와 제2 라이너(356)는 두께(T9)를 가질 수 있다. 두께(T8)와 두께(T9)는 약 1:1의 비율(T8:T9)에 있을수 있다. 일부 실시예들에서, 도전성 피처(340)의 측벽과 접촉하는 제1 라이너(339)의 일부는 두께(T9)를 갖고, 도전성 피처(340)의 바닥면과 접촉하는 제1 라이너(339)의 일부는 두께(T9)보다 큰 두께(T10)를 갖는다. 마찬가지로, 도전성 피처(342)의 측벽과 접촉하는 제1 라이너(339)의 일부는 두께(T9)를 갖고, 도전성 피처 (342)의 바닥면과 접촉하는 제1 라이너(339)의 일부는 두께(T9)보다 큰 두께(T9)를 갖고, 도전성 피처 (342)의 바닥면과 접촉하는 제1 라이너(339)의 일부는 두께(T9)보다 큰 두께(T10)를 갖는다. 두께(T9)와 두께 (T10)는 약 0.5 mm 내지 약 4 mm의 범위 내에 있을 수 있다. 일부 실시예들에서, 두께(T9)와 두께(T10)는 약 1:2 내지 약 1:8의 비율(T9:T10)로 있을 수 있다. 제1 캡 충(344)은 두께(T11)를 가질 수 있고, 제2 캡 충 (362)은 두께(T12)를 가질 수 있다. 두께(T11)와 두께(T12)는 약 1:1의 비율(T11:T12)로 있을 수 있다. 도전성 피처들(340, 342) 위에서의 제1 캡 충(344)의 존재는 그에 따라 제2 에칭 정지충(346)을 그 영역 내에서 들어올리는 돌출부를 형성한다.

- [0051] 응용에 따라, 도전성 피처(340) 위의 제1 캡 층(344)은 폭(W7)을 가질 수 있고, 도전성 피처(342) 위의 제1 캡 층(344)은 폭(W7)보다 큰 폭(W8)을 가질 수 있다. 폭(W7)과 폭(W8)은 약 1:3 내지 약 1:35의 범위 내의 비율 (W7:W8)을 가질 수 있다. 도전성 피처(358) 위의 제2 캡 층(362)은 폭(W11)을 가질 수 있고, 도전성 피처 (360) 위의 제2 캡 층(362)은 폭(W11)보다 큰 폭(W12)을 가질 수 있다. 제2 캡 층(362)이 제2 라이너(356)의 최상면을 덮도록 연장되는 경우들에서, 폭(W11)과 폭(W12)은 약 1:3 내지 약 1:30의 범위 내의 비율(W11:W12)을 가질 수 있다. 도전성 피처(358), 제2 배리어층(354), 및 제2 라이너(356)는 통합된 폭(W9)을 가질 수 있고, 도전성 피처(360), 제2 배리어층(354), 및 제2 라이너(356)는 통합된 폭(W9)보다 큰 통합된 폭(W10)을 가질 수 있다. 폭(W9)과 폭(W10)은 약 1:3 내지 약 1:36의 비율(W9:W10)을 가질 수 있다.

- [0052] 도 5에서의 상호연결 구조물(300)은 제1 유전체층(332)(예컨대, MO) 내의 도전성 피처들(예컨대, 도전성 비아들)(340, 342) 및 제2 유전체층(348)(예컨대, M1) 내의 도전성 피처들(예컨대, 도전성 비아들)(358, 360)을 도전성 피처(340)는 제1 캡 층(344)(예컨대, Ru)과 접촉하는 최상면(340t), 제1 도시한다. 라이너(339)(예컨대, Ru)의 제1 파트(339-1)와 접촉하는 측벽면(340s), 및 제1 라이너(339)의 제2 파트(339-2)와 접촉하는 바닥면(340b)을 포함한다. 제1 라이너(339)의 제2 파트(339-2)는 제1 라이너(339)의 제1 파트 (339-1)보다 두께가 약 두 배(또는 그 이상)이다. 도전성 피처(340)의 바닥면(340b)과 맞대어 있는 제1 라이너 (339)의 제2 파트(339-2)는 실질적으로 T자형 프로파일을 가질 수 있다. 일부 경우들에서, 제2 파트(339-2)의 일부는 유전체층(314) 내로 하방으로 연장된다. 마찬가지로, 도전성 피처(342)는 제3 캡 층(344)(예컨대, Ru) 과 접촉하는 최상면(342t), 제1 라이너(339)(예컨대, Ru)의 제3 파트(339-3)와 접촉하는 측벽면(342s), 및 제1 라이너(339)의 제4 파트(339-3)와 접촉하는 바닥면(342b)을 포함한다. 제1 라이너(339)의 제4 파트(339-4)는 제1 라이너(339)의 제3 파트(339-3)보다 두께가 약 두 배(또는 그 이상)이다. 도전성 피처(342)의 바닥면 (342b)과 맞대어 있는 제1 라이너(339)의 제4 파트(339-4)는 실질적으로 직사각형 프로파일을 가질 수 있다. 일부 실시예들에서, 도전성 피처들(340, 342)은 제1 라이너(339) 및 제1 캡 층(344)과 동일한 도전성 물질(예를 들어, Ru)에 의해 완전히 둘러싸이거나 에워싸인다.

- [0053] 도전성 피처들(358)은 제2 캡 층(362)(예컨대, Co 또는 Ru)과 접촉하는 최상면(358t), 제2 라이너(356)(예컨대, Ru)의 제1 파트(356-1)와 접촉하는 측벽면(358s), 및 제2 라이너(356)(예컨대, Ru)의 제2 파트(356-2)와 접촉하는 바닥면(358b)을 포함한다. 마찬가지로, 도전성 피처(360)는 제2 캡 층(362)(예컨대, Co 또는 Ru)과 접촉하는 최상면(360t), 제2 라이너(356)(예컨대, Ru)의 제3 파트(356-3)와 접촉하는 측벽면(360s), 및 제2 라이너(356)(예컨대, Ru)의 제4 파트(356-4)와 접촉하는 바닥면(360b)을 포함한다. 제2 라이너(356)의 제4 파트

(356-4)는 제2 라이너(356)의 제3 파트(356-3)와 두께가 거의 동일하다. 제1 배리어층(338)은 도전성 피처(340) 주위에 배치되고 제1 라이너(339)의 제1 파트(339-1)와 접촉한다. 제1 배리어층(338)은 도전성 피처(342) 주위에 배치되고 제1 라이너(339)의 제3 파트(339-3)와 접촉한다. 마찬가지로, 제2 배리어층(354)은 도전성 피처(358) 주위에 배치되고 제2 라이너(356)의 제1 파트(356-1)와 접촉한다. 제2 배리어층(354)은 도전성 피처(360) 주위에 배치되고 제2 라이너(356)의 제3 파트(356-3)와 접촉한다.

- [0054] 도전성 피처(360)가 구리(Cu)를 포함하는 일부 실시예들에서, 제2 라이너(356)는 루테늄(Ru)을 포함하고, 제1 캡 층(344)은 Ru를 포함하고, 도전성 피처(342)는 Cu를 포함하며, Cu의 원자 퍼센티지(at.%)는 제1 Cu/Ru 계면 (380)과 제2 Cu/Ru 계면(382)에서 이들 층들 내에서 Z 방향(390)을 따라 점진적으로 변화할 수 있다. 예를 들어, Cu의 at.%는 제1 Cu/Ru 계면(380)(예컨대, Cu의 at.%는 약 100 at.%임)에서 제2 Cu/Ru 계면(382)(예컨대, Cu의 at.%는 약 0 at.%임)으로 점진적으로 감소될 수 있는 반면에, Ru의 at.%는 제1 Cu/Ru 계면(380)(예컨대, Ru의 at.%는 약 100 at.%임)이서 제2 Cu/Ru 계면(382)(예컨대, Ru의 at.%는 약 0 at.%임)으로 점진적으로 증가할 수 있다. 일부 실시예들에서, 제1 Cu/Ru 계면(380)과 제2 Cu/Ru 계면(382)은 각각 약 2 mm 내지 약 7 mm의 길이를 가질 수 있다.

- [0055] 본 개시의 실시예들은 루테늄계 소스/드레인 콘택트 비아들(예컨대, 도전성 피처들(316, 317)과 통합되도록 코발트 없이 루테늄계 MO 라이너(예컨대, 제1 라이너(339)) 및 루테늄계 M1 선택적 캡핑(예컨대, 제2 캡 층(362))을 사용함으로써 저저항 상호연결 구조물들을 제공한다. M1/M0/비아 콘택트 상호혼합 문제가 없기 때문에, 소스/드레인 콘택트 비아들과, 인접한 유전체충들(예컨대, 유전체충(314))은 물론 MO 콘택트들(예컨대, 도전성 피처들(340, 342)) 사이의 배리어 두께가 감소되거나 또는 심지어 제거될 수 있다. M1 선택적 캡핑(예컨대, 제2 캡 층(362)), 소스/드레인 콘택트 캡(예컨대, 제1 캡 층(344)), MO 루테늄 라이너(예컨대, 제1 라이너(339)), 루테늄 소스/드레인 콘택트 비아(예컨대, 도전성 피처(316))를 위한 순수 루테늄의 사용은 고온에서의 Ru/Co 상호혼합으로 인한 Ru 및 Co 신뢰성 문제를 방지하면서 총 상호연결 저항을 80 ohm에서 40~60 ohm으로 효과적으로 감소시킬 수 있다.

- [0056] 다양한 실시예들에서, 개선된 상호연결 구조물은 다음에 의해 제조될 수 있다: (1) 각각의 소스/드레인 피처들 위에 제1 층간 유전체(ILD0)를 관통하여 소스/드레인 콘택트들을 형성하는 동작 - 소스/드레인 콘택트는 루테늄 (Ru)과 같은 도전성 물질을 포함할 수 있음 -; (2) 소스/드레인 콘택트들 위에 에칭 정지층과 제2 층간 유전체 (ILD1)를 후속적으로 형성하는 동작; (3) ILD1 및 에칭 정지층을 관통하여 제1 및 제2 콘택트 비아 개구부들을 형성하는 동작 - 제1 콘택트 비아 개구부는 하나의 소스/드레인 콘택트의 최상면을 노출시키고, 제2 콘택트 비 아 개구부는 복수의 소스/드레인 콘택트들의 최상면을 노출시키도록 형성됨 -; (4) 제1 및 제2 콘택트 비아들을 형성하기 위해 루테늄(Ru)과 같은 도전성 물질로 제1 및 제2 콘택트 비아 개구부들을 채우는 동작; (5) ILD1의 최상면이 노출될 때까지 CMP를 수행하는 동작; (6) 제1 캡 층 및 로우 k 유전체를 순차적으로 형성하는 동작; (7) 로우 k 유전체 및 제1 캡 층을 관통하여 제1 및 제2 금속 콘택트 개구부들을 형성하는 동작 - 제1 금속 콘 택트 개구부는 제1 콘택트 비아의 최상면을 노출시키고, 제2 금속 콘택트 개구부는 제2 콘택트 비아의 전체 최 상면을 노출시키도록 형성됨 -; (8) 제1 및 제2 콘택트 개구부들의 노출된 측벽면들 상에 배리어층을 선택적으 로 형성하는 동작 - 배리어층은 TaN을 포함할 수 있음 -; (9) 제1 및 제2 콘택트 비아들의 최상면들과 배리어층 상에 라이너층을 형성하는 동작 - 라이너층은 루테늄(Ru)과 같은 도전성 물질을 포함할 수 있음 -; (10) 제1 및 제2 금속 콘택트들을 각각 형성하기 위해 구리(Cu)와 같은 도전성 물질로 제1 및 제2 금속 콘택트 개구부들을 채우는 동작; (11) 로우 k 유전체의 최상면이 노출될 때까지 CMP를 수행하는 동작; (12) 라이너층 뿐만 아니라 제1 및 제2 금속 콘택트들 상에 제2 캡 층을 선택적으로 형성하는 동작; 및 (13) 제1 및 제2 금속 콘택트들 바 로 위에 제3 및 제4 금속 콘택트들을 형성하기 위해 동작들 (7)~(12)을 반복하는 동작.

- [0057] 본 개시의 양태들을 본 발명분야의 당업자가 보다 잘 이해할 수 있도록 앞에서는 여러 개의 실시예들의 특징들을 약술해왔다. 본 발명분야의 당업자는 여기서 소개한 실시예들의 동일한 목적들을 수행하거나 및/또는 동일한 장점들을 달성하기 위한 다른 공정들 및 구조물들을 설계하거나 또는 수정하기 위한 기초로서 본 개시를 자신들이 손쉽게 이용할 수 있다는 것을 알아야 한다. 본 발명분야의 당업자는 또한 이와 같은 등가적 구성들은 본 발명개시의 사상과 범위를 이탈하지 않는다는 것과, 본 발명개시의 사상과 범위를 이탈하지 않고서 당업자가다양한 변경들, 대체들, 및 개조들을 본 발명에서 행할 수 있다는 것을 자각해야 한다.

- [0058] 실시예들

- [0059] 실시예 1. 상호연결 구조물에 있어서,

- [0060] 충간 유전체 내의 콘택트 비아;

- [0061] 제1 유전체층 내의 제1 도전성 피처 상기 제1 유전체층은 상기 층간 유전체 위에 배치됨 -;

- [0062] 상기 제1 유전체층 내의 제1 라이너 상기 제1 라이너는,

- [0063] 상기 제1 도전성 피처의 측벽면과 접촉하는 제1 파트; 및

- [0064] 상기 제1 도전성 피처의 바닥면과 접촉하는 제2 파트

- [0065] 를 포함함 -;

- [0066] 상기 제1 도전성 피처의 최상면과 접촉하는 제1 캡 층;

- [0067] 제2 유전체층 내의 제2 도전성 피처 상기 제2 유전체층은 상기 제1 유전체층 위에 배치됨 -; 및

- [0068] 상기 제2 유전체층 내의 제2 라이너

- [0069] 를 포함하고,

- [0070] 상기 제1 도전성 피처와 상기 제2 도전성 피처는 제1 도전성 물질을 포함하고, 상기 콘택트 비아, 상기 제1 라이너, 상기 제1 캡 층, 및 상기 제2 라이너는 상기 제1 도전성 물질과는 화학적으로 상이한 제2 도전성 물질을 포함한 것인 상호연결 구조물.

- [0071] 실시예 2. 실시예 1에 있어서,

- [0072] 상기 제2 도전성 피처와 접촉하는 제2 캡 층

- [0073] 을 더 포함하는 상호연결 구조물.

- [0074] 실시예 3. 실시예 2에 있어서,

- [0075] 상기 제2 캡 층은 상기 제2 도전성 물질을 포함한 것인 상호연결 구조물.

- [0076] 실시예 4. 실시예 3에 있어서,

- [0077] 상기 제2 도전성 물질은 루테늄인 것인 상호연결 구조물.

- [0078] 실시예 5. 실시예 3에 있어서,

- [0079] 상기 제2 도전성 물질은 코발트가 없는 것인 상호연결 구조물.

- [0080] 실시예 6. 실시예 2에 있어서,

- [0081] 상기 제2 캡 층은 상기 제1 도전성 물질 및 상기 제2 도전성 물질과는 화학적으로 상이한 제3 도전성 물질을 포함한 것인 상호연결 구조물.

- [0082] 실시예 7. 실시예 6에 있어서,

- [0083] 상기 제3 도전성 물질은 코발트인 것인 상호연결 구조물.

- [0084] 실시예 8. 실시예 2에 있어서,

- [0085] 상기 제2 캡 층은 추가로 상기 제2 라이너와 접촉하는 것인 상호연결 구조물.

- [0086] 실시예 9. 실시예 1에 있어서,

- [0087] 상기 제1 유전체층 및 상기 제1 라이너와 접촉하는 제1 배리어층

- [0088] 을 더 포함하는 상호연결 구조물.

- [0089] 실시예 10. 실시예 9에 있어서,

- [0090] 상기 제2 유전체층 및 상기 제2 라이너와 접촉하는 제2 배리어층

- [0091] 을 더 포함하는 상호연결 구조물.

- [0092] 실시예 11. 실시예 10에 있어서,

- [0093] 상기 제1 배리어층과 상기 제2 배리어층은 제4 도전성 물질을 포함한 것인 상호연결 구조물.

- [0094] 실시예 12. 실시예 1에 있어서,

- [0095] 상기 제1 라이너의 상기 제2 파트의 일부는 상기 층간 유전체 내로 연장된 것인 상호연결 구조물.

- [0096] 실시예 13. 반도체 디바이스 구조물에 있어서,

- [0097] 제1 충간 유전체 내에 배치된 제1 소스/드레인 콘택트, 제2 소스/드레인 콘택트, 제3 소스/드레인 콘택트, 및 제4 소스/드레인 콘택트;

- [0098] 제2 층간 유전체 내의 제1 도전성 피처 상기 제1 도전성 피처는 상기 제2 층간 유전체 및 상기 제1 소스/드레인 콘택트와 직접 접촉함 -;

- [0099] 상기 제2 충간 유전체 내의 제2 도전성 피처 상기 제2 도전성 피처는 상기 제2 충간 유전체, 상기 제2 소스/드레인 콘택트, 상기 제3 소스/드레인 콘택트, 및 상기 제4 소스/드레인 콘택트와 직접 접촉함 -;

- [0100] 제1 유전체층 내의 제3 도전성 피처;

- [0101] 제2 유전체층 내의 제4 도전성 피처 상기 제2 유전체층은 상기 제1 유전체층 위에 배치됨 -;

- [0102] 상기 제3 도전성 피처의 측벽면, 상기 제3 도전성 피처의 바닥면, 및 상기 제1 도전성 피처의 최상면과 직접 접촉하는 제1 라이너; 및

- [0103] 상기 제4 도전성 피처의 측벽면 및 상기 제4 도전성 피처의 바닥면과 직접 접촉하는 제2 라이너

- [0104] 를 포함하며.

- [0105] 상기 제1 도전성 피처, 상기 제2 도전성 피처, 상기 제1 라이너, 및 상기 제2 라이너는 제1 도전성 물질을 포함하고, 상기 제3 도전성 피처와 상기 제4 도전성 피처는 상기 제1 도전성 물질과는 화학적으로 상이한 제2 도전성 물질을 포함한 것인 반도체 디바이스 구조물.

- [0106] 실시예 14. 실시예 13에 있어서,

- [0107] 상기 제1 유전체층과 상기 제1 라이너 사이에 배치되고, 상기 제1 유전체층 및 상기 제1 라이너와 접촉하는 제1 배리어층; 및

- [0108] 상기 제2 유전체층과 상기 제2 라이너 사이에 배치되고, 상기 제2 유전체층 및 상기 제2 라이너와 접촉하는 제2 배리어츳

- [0109] 을 더 포함하는 반도체 디바이스 구조물.

- [0110] 실시예 15. 실시예 13에 있어서,

- [0111] 상기 제3 도전성 피처의 최상면과 상기 제2 라이너 사이에 배치되고, 상기 제3 도전성 피처의 최상면 및 상기 제2 라이너와 접촉하는 제1 캡 층

- [0112] 을 더 포함하는 반도체 디바이스 구조물.

- [0113] 실시예 16. 실시예 15에 있어서,

- [0114] 상기 제4 도전성 피처와 상기 제2 라이너의 최상면들과 접촉하는 제2 캡 층

- [0115] 을 더 포함하는 반도체 디바이스 구조물.

- [0116] 실시예 17. 실시예 16에 있어서, 상기 제2 캡 층은 상기 제1 도전성 물질을 포함한 것인 반도체 디바이스 구조물.

- [0117] 실시예 18. 실시예 15에 있어서,

- [0118] 상기 제1 유전체층 내의 제5 도전성 피처; 및

- [0119] 상기 제1 유전체층 내에 배치되고, 상기 제2 도전성 피처, 상기 제5 도전성 피처의 측벽면, 및 상기 제5 도전성 피처의 바닥면과 접촉하는 제3 라이너

- [0120] 를 더 포함하는 반도체 디바이스 구조물.

- [0121] 실시예 19. 반도체 디바이스 구조물을 형성하기 위한 방법에 있어서,

- [0122] 충간 유전체 내에 제1 도전성 피처를 형성하는 단계 상기 제1 도전성 피처는 상기 충간 유전체와 직접 접촉하고, 상기 제1 도전성 피처는 제1 도전성 물질을 포함함 -;

- [0123] 상기 층간 유전체 및 상기 제1 도전성 피처 상에 제1 에칭 정지층을 형성하는 단계;

- [0124] 상기 제1 에칭 정지층 상에 제1 유전체층을 형성하는 단계;

- [0125] 상기 제1 도전성 피처의 일부를 노출시키기 위해 상기 제1 유전체층과 상기 제1 에칭 정지층을 관통하여 개구부를 형성하는 단계;

- [0126] 상기 제1 유전체층, 상기 제1 에칭 정지층, 및 상기 층간 유전체의 노출된 표면들 상에 제1 배리어층을 선택적으로 형성하는 단계;

- [0127] 상기 제1 도전성 피처의 노출된 표면과 상기 제1 배리어층 상에 제1 라이너층을 형성하는 단계 상기 제1 라이너층은 상기 제1 도전성 물질을 포함함 -;

- [0128] 제2 도전성 피처를 형성하기 위해 제2 도전성 물질로 상기 개구부를 채우는 단계 상기 제2 도전성 물질은 상기 제1 도전성 물질과는 화학적으로 상이함 -;

- [0129] 상기 제2 도전성 피처의 노출된 표면들 상에 제1 캡 층을 선택적으로 형성하는 단계 상기 제1 캡 층은 상기 제1 도전성 물질을 포함함 -;

- [0130] 상기 제1 유전체층 위에 제2 에칭 정지층을 형성하는 단계;

- [0131] 상기 제2 에칭 정지층 상에 제2 유전체층을 형성하는 단계;

- [0132] 상기 제2 유전체층 및 상기 제2 에칭 정지층을 관통하여 제3 도전성 피처를 형성하는 단계 상기 제3 도전성 피처는 상기 제2 도전성 물질을 포함함 -; 및

- [0133] 상기 제3 도전성 피처의 노출된 표면 상에 제2 캡 층을 선택적으로 형성하는 단계 상기 제2 캡 층은 상기 제1 도전성 물질을 포함함 -

- [0134] 를 포함하는 반도체 디바이스 구조물을 형성하기 위한 방법.

- [0135] 실시예 20. 실시예 18에 있어서,

- [0136] 상기 제2 유전체층 내에 제2 라이너층을 제공하는 단계 상기 제2 라이너층은 상기 제3 도전성 피처의 측벽면 및 바닥면과 접촉함 -; 및

- [0137] 상기 제2 유전체층 내에 제2 배리어층을 제공하는 단계 상기 제2 유전체층은, 상기 제2 배리어층과 상기 제2 라이너층 사이에 배치되고, 상기 제2 배리어층 및 상기 제2 라이너층과 접촉함 -

- [0138] 을 더 포함하는 반도체 디바이스 구조물을 형성하기 위한 방법.

## 도면

# 도면1a

## *도면1b*

# 도면2

# 도면3a

## 도면3b

# 도면3c

## 도면3d

## *도면3e*

## 도면3f

# 도면3g

## 도면3h

## *도면3i*

## 도면3j

## *도면3k*

## 도면31

# 도면31a

## 도면3m

## 도면3n

## 도면30

# 도면3p

## 도면4

## 도면5