## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**H01L 31/0232** (2014.01) **H01L 31/10** (2006.01)

(21) 출원번호

10-2014-0009157

(22) 출원일자

2014년01월24일

심사청구일자 없음

(43) 공개일자(71) 출원인

(11) 공개번호

#### 한국전자통신연구원

대전광역시 유성구 가정로 218 (가정동)

10-2015-0088627

2015년08월03일

(72) 발명자

#### 강세경

대전광역시 유성구 엑스포로 448,210동 1301호 (전민동, 엑스포아파트)

#### 이상수

대전광역시 중구 계룡로 923,103동 503호 (문화 동, 하우스토리1차)

(74) 대리인

특허법인 신지

전체 청구항 수 : 총 7 항

(54) 발명의 명칭 **수광 소자**

#### (57) 요 약

본 발명은 수광 소자로, 광신호가 전기신호로 변환되는 제 1 금속층들과, 광도파로의 양단 및 상기 광 도파로를 통해 전달되는 광신호를 흡수하는 성장부의 소정 영역에 도핑된 영역들과 상기 도핑된 영역들 및 상기 제 1 금속층 사이에 형성되는 제 1 비아들과, 광 신호를 전기신호로 변환되는 제 2 금속층들과, 상기 제 1 금속층들 및 상기 제 2 금속층 사이에 형성되는 제 2 비아들로 형성된다.

#### 대 표 도 - 도3

### 명세서

#### 청구범위

#### 청구항 1

광 신호를 전기신호로 변환되는 제 1 금속층들과,

광도파로의 양단 및 상기 광 도파로를 통해 전달되는 광신호를 흡수하는 성장부의 소정 영역에 도핑된 영역들과 상기 도핑된 영역들 및 상기 제 1 금속층 사이에 형성되는 제 1 비아들과,

광 신호를 전기신호로 변환되는 제 2 금속층들과,

상기 제 1 금속층들 및 상기 제 2 금속층 사이에 형성되는 제 2 비아들로 형성됨을 특징으로 하는 수광 소자.

#### 청구항 2

제 1항에 있어서, 상기 광도파로와 성장부는

에바네센트 결합(evanescent coupling) 또는 버트 커플링됨을 특징으로 하는 수광 소자.

### 청구항 3

제 1항에 있어서, 상기 광도파로는

실리콘으로 생성됨을 특징으로 하는 수광 소자.

## 청구항 4

제 1항에 있어서, 상기 성장부는

게르마늄으로 생성됨을 특징으로 하는 수광 소자.

## 청구항 5

제 1항에 있어서,

상기 제 1 비아 및 제 2 비아가 일직선을 이루도록 동일한 위치에 형성됨을 특징으로 하는 수광 소자.

### 청구항 6

제 1항에 있어서,

상기 제 1 비아와 제 2 비아가 서로 어긋나게 위치됨을 특징으로 하는 수광 소자.

### 청구항 7

제 6항에 있어서,

상기 제 1 비아들 간의 이격 거리는 제 2 비아 크기이고, 제 2 비아들 간의 이격 거리는 제 1 비아의 크기임을 특징으로 하는 수광 소자.

### 발명의 설명

#### 기술분야

[0001]

[0008]

[0009]

본 발명은 광소자에 관한 것으로, 특히 광신호를 전기 신호로 변환하는 수광 소자에 관한 것이다.

#### 배경기술

- [0002] 최근 광통신 시스템의 저가화, 고속화 및 대용량화에 따라 CMOS 포토닉스 기반의 전자 회로부와 광회로부를 하나의 칩으로 구현하는 기술이 점점 부각되고 있다. 이러한 기술은 10년 전부터 연구되어 왔으며, 현재는 이러한 제조 공정을 상용으로 파운드리(foundry)를 제공하는 업체가 등장하였다.

- [0003] 그런데, CMOS 전자 소자에 비해 광소자의 크기가 상당히 크며, 전자 소자와 광소자 제작 마스크의 레이어 차이가 상당하여, 현재는 이러한 기술이 높은 제작 단가 및 낮은 기술 레벨의 상태에 있지만 향후 광통신 시스템 소형화 및 저가화를 위한 핵심 기술이 될 수 있다.

- [0004] 실리콘 포토닉스 기반의 광소자로는 광도파로, 광분배기 및 결합기, 광다중화기 및 역다중화기, 수광 소자, 변조기, 기타 수동 소자 등이 제작 가능하다. 상용 파운드리 업체는 전술한 소자들 중에서 기술의 완성도 등을 고려하여 광도파로, 수광소자, 변조기, 광분배기 및 결합기 등을 라이브러리로 제공하고 있다.

- [0005] 이러한 소자들 중에서 광수신부의 핵심 소자인 수광 소자는 실리콘 상에 게르마늄을 성장시켜 구현된다. 이는 게르마늄의 광신호 흡수 파장 영역이 광통신에서 사용하는 광신호 파장 대역인 1.3um 및 1.5um를 포함하고 있기 때문이다. 실리콘의 광신호 파장 흡수 영역은 단파장 영역인 400nm~700nm로 장파장 영역인 일반 광통신에 적용이 불가능하다.

- [0006] 이러한 수광 소자는 크게 두 가지 구조로 구현될 수 있다.

- [0007] 첫 번째로, 실리콘 광도파로 위에 게르마늄(Germanium) 층을 성장시킨 에바네센트 결합(evanescent coupling) 구조이다. 이러한 구조에서 실리콘 광도파로를 통해 진행하는 광신호는 광도파로 내에서 완벽하게 모드가 갇힌 상태로 진행하지 않으므로, 게르마늄층으로 굴절율 차에 의해 모드 결합(evanescent coupling)이 일어난다. 이러한 과정을 통해 광신호는 게르마늄 진성층(intrinsic layer)에 입사되고, 실리콘 광도파로 및 게르마늄층에 형성된 수광 소자의 전극(anode, cathode)에 인가된 전기적 바이어스에 따라 상기 입사된 광신호에 해당하는 전류 신호가 생성된다.

- 두 번째로, 광신호가 진행하는 광도파로 종단의 실리콘 상에 게르마늄을 성장시킨 버트 결합(butt coupling) 구조이다. 이러한 구조에서는 실리콘 광도파로를 통해 진행하는 광신호는 바로 게르마늄충으로 입사 및 결합된다. 이후 기본 동작은 에바네센트 결합(evanescent coupling) 구조의 수광 소자 동작과 동일하다.

- 그런데, 이러한 수광 소자에서 실리콘 상에 게르마늄을 성장시키는 데 있어, 두 물질의 격자 상수 차이가 4% 이상이므로, 게르마늄과 실리콘과의 경계면에서 전위(dislocation)가 발생하게 된다. 이러한 전위는 누설 전류 (leakage current)를 발생시켜 수광 소자의 성능 파라미터인 암전류(dark current) 특성을 저하시키는 원인이된다. 이러한 암전류를 발생시키는 다른 원인으로는 금속(metal)과 반도체(수광 소자에서 실리콘 또는 게르마늄 영역에 p-type 또는 n-type 도핑 영역) 사이의 전기적 연결(ohmic contact)에서 금속과 반도체 경계면에서 발생되는 누설 전류(leakage current)로 이는 접촉 면적에 비례하여 증가하게 된다.

### 발명의 내용

#### 해결하려는 과제

[0010] 본 발명은 금속과 반도체 사이의 접촉 면적을 감소시키고 비아 저항 증가를 최소화하여 암전류(dark current) 및 반응도(responsivity)를 개선할 수 있는 수광 소자를 제공한다.

#### 과제의 해결 수단

[0011]

본 발명은 수광 소자로, 광신호가 전기신호로 변환되는 제 1 금속층들과, 광도파로의 양단 및 상기 광 도파로를 통해 전달되는 광신호를 흡수하는 성장부의 소정 영역에 도핑된 영역들과 상기 도핑된 영역들 및 상기 제 1 금속층 사이에 형성되는 제 1 비아들과, 광 신호를 전기신호로 변환되는 제 2 금속층들과, 상기 제 1 금속층들 및 상기 제 2 금속층 사이에 형성되는 제 2 비아들로 형성된다.

#### 발명의 효과

[0012]

본 발명에 따라, 금속과 반도체 사이의 접촉 면적을 감소시키고 비아 저항 증가를 최소화하여 암전류(dark current) 및 반응도(responsivity)를 개선할 수 있다.

#### 도면의 간단한 설명

[0013]

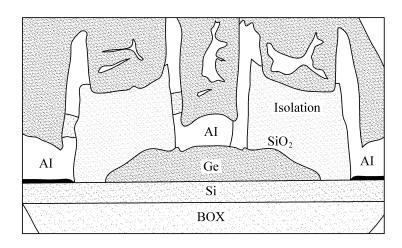

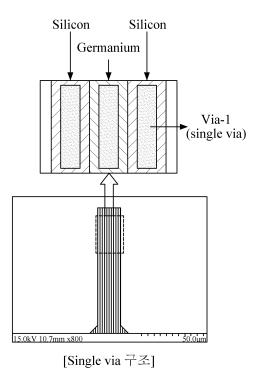

- 도 1은 에바네센트 결합(evanescent coupling)된 수광 소자 구조의 일 예를 도시한 도면이다.

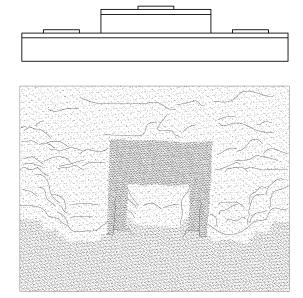

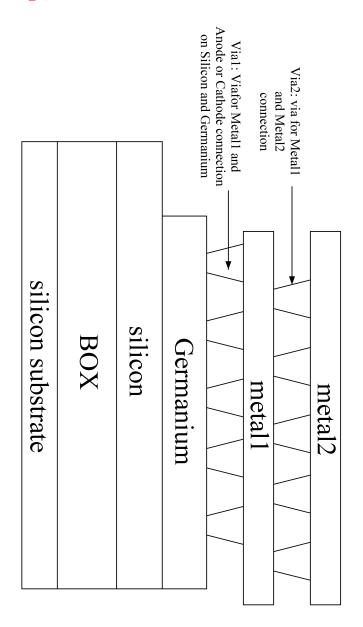

- 도 2는 버트 결합(butt coupling)된 수광 소자 구조의 일 예를 도시한 도면이다.

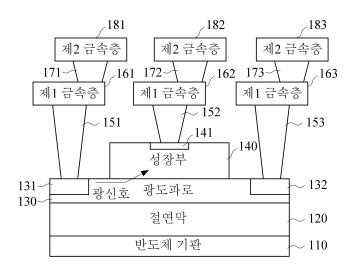

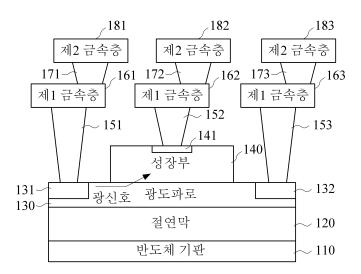

- 도 3은 본 발명의 일 실시 예에 따른 수광 소자의 구조도이다.

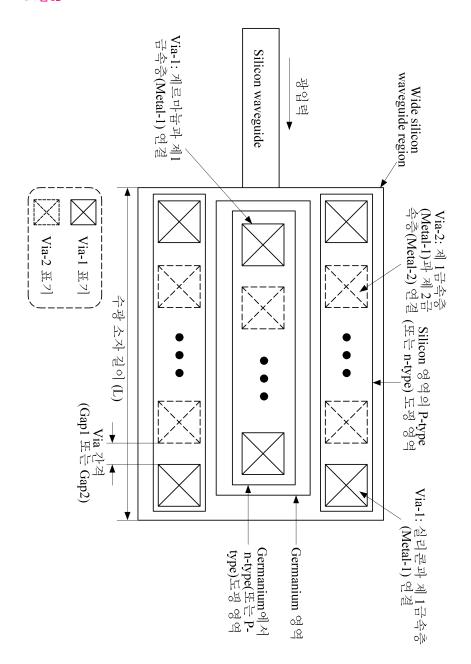

- 도 4a는 본 발명의 일 실시 예에 따른 수광 소자의 단면도이다.

- 도 4b는 본 발명의 일 실시 예에 따른 수광 소자의 평면도이다.

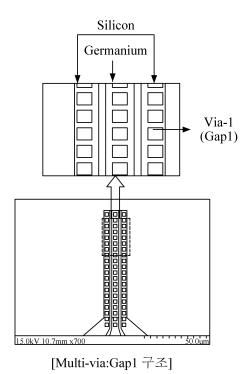

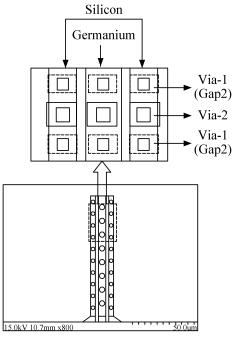

- 도 5a 내지 도 5c는 3가지 비아 구조를 가지는 수광 소자의 도면이다.

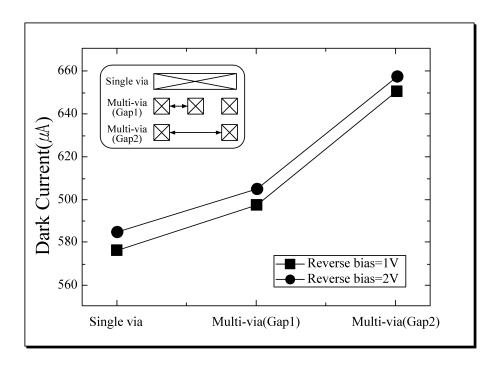

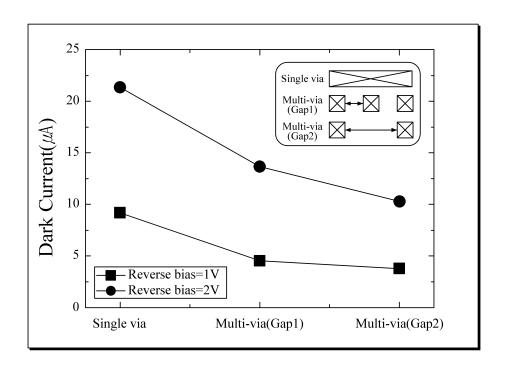

도 6a는 수광 소자에 대해 세 가지 구조로 각각 제작된 수광 소자의 암전류 특성을 측정한 결과를 도시한 그래 프이다.

도 6b는 수광 소자에 대해 세 가지 구조를 가지는 각각의 수광 소자의 입력 광에 대한 반응도를 측정한 결과를 도시한 그래프이다.

#### 발명을 실시하기 위한 구체적인 내용

[0014]

- 이하, 첨부된 도면을 참조하여 기술되는 바람직한 실시 예를 통하여 본 발명을 당업자가 용이하게 이해하고 재 현할 수 있도록 상세히 기술하기로 한다.

- [0015] 본 발명을 설명함에 있어 관련된 공지 기능 또는 구성에 대한 구체적인 설명이 본 발명 실시 예들의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우에는 그 상세한 설명을 생략할 것이다.

- [0016] 명세서 전반에 걸쳐 사용되는 용어들은 본 발명 실시 예에서의 기능을 고려하여 정의된 용어들로서, 사용자 또는 운용자의 의도, 관례 등에 따라 충분히 변형될 수 있는 사항이므로, 이 용어들의 정의는 본 발명의 명세서 전반에 걸친 내용을 토대로 내려져야 할 것이다.

- [0017]

- 도 1은 에바네센트 결합(evanescent coupling)된 수광 소자 구조의 일 예를 도시한 도면이다.

- [0018]

- 도 1을 참조하면, 싱가폴의 IME(Institute of Microelectronics)에서 개발한 수광 소자의 구조가 도시되어 있는데, 금속(Al, Aluminium)을 실리콘(Si) 및 게르마늄(Ge) 영역의 각각 서로 다른 타입으로 도핑된 영역에 연결할 때, 수광 소자 길이에 해당하는 단일 비아(single via)로 형성된다. 이 경우, 비아(via) 저항값은 감소하지만 두 물질의 접촉 면적 증가로 누설 전류가 증가하는 단점이 있다.

- [0019]

- 도 2는 버트 결합(butt coupling)된 수광 소자 구조의 일 예를 도시한 도면이다.

- [0020]

- 도 2를 참조하면, 유럽 HELIOS 프로젝트 일환으로 프랑스의 IEF(Institute Europeen de Francais)와 CEA-LETI에서 개발한 수광소자가 도시되어 있는데, 금속과 실리콘 및 게르마늄 영역의 각각 서로 다른 타입으로 도 핑된 영역에 연결할 때 수광 소자 길이에 해당하는 단일 비아(single via)로 형성하였다. 이 구조 또한 비아(via) 저항값은 감소하지만, 두 물질의 접촉 면적의 증가로 누설 전류가 증가하는 단점이 있다.

- [0021]

- 본 발명에서는 두 물질의 접촉 면적을 최대한 감소시키기 위해, 두 개 이상의 층으로 비아들이 적층되는 구조를

가지는 수광 소자를 제안한다. 설명의 편의를 위해 본 발명에서는 에바네센트 결합(evanescent coupling)된 수 광 소자에서의 비아 구조에 대해 기술하나, 버트 결합(butt coupling)된 수광 소자에서도 본 발명에 따른 비아 구조가 적용 가능함은 물론이다.

- [0022] 도 3은 본 발명의 일 실시 예에 따른 수광 소자의 구조도이다.

- [0023] 도 3을 참조하면, 본 발명의 일 실시 예에 따른 수광 소자는 반도체 기판(110)과, 반도체 기판(110)의 상부에 형성된 절연막(BOX : Buried Oxide Layer)(120)과, 절연막(120)의 상부에 형성되어 광신호를 통과시키는 광도과로(130)와, 광도과로(130)의 상부에 광도과로(130)와 상이한 물질로 성장되어 광신호를 흡수하는 성장부(140)와, 광도과로(130)의 양단 및 성장부(140)의 소정 영역에 도핑되는 도핑 영역부들(131, 132, 141)와, 도핑 영역부들(131, 132, 141)과 제 1 금속층(161, 162, 163) 사이에 형성된 제 1 비아들(151, 152, 153)과, 제 1 금속층(161, 162, 163)과 제 2 금속층(181, 182, 183) 사이에 형성된 제 2 비아들(171, 172, 173)로 형성된다.

- [0024] 반도체 기판(110) 및 광도파로(130)는 실리콘으로 생성될 수도 있고, 성장부(140)는 게르마늄(Germanium)으로 생성될 수 있다. 반도체 기판(110), 절연막(120) 및 광도파로(130)는 잘 알려진 내용이므로 여기서는 그 상세한 설명을 생략하기로 한다.

- [0025] 수광 소자에서 광신호는 광도파로(130)를 통해 진행한 후, 넓은 폭을 가진 실리콘 광도파로(130)에서 성장부 (140)로 광결합되며, 두 층간 광신호가 지그재그 진행하면서 성장부(140)에 대부분 광결합된다.

- [0026] 도핑 영역부(131, 132, 141)는 수광 소자의 전극 형성을 위하여 p-type(일반적으로 boron 도핑) 또는 n-type(일반적으로 phosphorus 도핑)으로 도핑된 영역이다. 여기서, 도핑 농도는 도핑 영역부(131, 132, 141)와 제 1비아(Via-1)(151, 152, 153) 사이의 전기적 결합(ohmic contact) 조건에 부합하도록 도핑되어야 한다. 그 렇지 않을 경우, 도핑 영역부(131, 132, 141)와 제 1비아(Via-1)(151, 152, 153) 사이의 경계면에서의 접촉 저항(contact resistance)이 상당히 커지게 된다.

- [0027] 성장부(140) 또한 수광 소자의 광도파로(130)의 전극과 반대 극성을 가지는 전극을 형성하기 위하여 n-type(일 반적으로 phosphorus 도핑) 또는 p-type(일반적으로 boron 도핑)으로 도핑하게 된다. 여기서, 도핑 농도는 광도 파로(130)의 전극 형성과 같은 이유로 전기적 결합(ohmic contact) 조건에 부합되도록 한다.

- [0028] 본 발명에서는 제 1 비아들(Via1)(161, 162, 163)과 제 2비아들(Via-2)(171, 172, 173)는 공정에 따라 수직 적 층 또는 서로 어긋나도록 적충되도록 배열될 수 있다.

- [0029] 도 4a 및 도 4b는 서로 어긋나게 적충될 경우의 수광 소자의 단면도 및 평면도를 도시한다.

- [0030] 여기서, 반도체 기판 및 광도파로는 실리콘으로 생성되고, 성장부는 게르마늄(Germanium)으로 생성된 것으로 도 시되어 있으나, 본 발명은 이에 한정되지 않느다.

- [0031] 도 4a 및 도 4b를 참조하면, 다수의 제 1 비아가 제 2 비아 크기에 해당되는 거리만큼 이격되어 배치된다. 즉, 동일한 공정 조건에서 제 1 비아의 비아 저항값을 감소시키기 위해 제 1 비아와 제 1 비아 이격 거리를 공정상 최소 이격 거리로 하여 보다 많은 제 1 비아를 형성하고, 수광 소자의 칩 패드 부분에서 제 2 비아를 이용하여 제 2 금속층과 연결하는 경우도 가능하다.

- [0032] 도 5a 내지 도 5c는 3가지 비아 구조를 가지는 수광 소자의 도면이다.

- [0033] 도 5a를 참조하면, 제 1비아를 단일 비아(single via) 형태로 수광 소자에 적충한 구조를 가지며 제 2비아는 수 광 소자의 칩 패드 부분에 형성된 구조이다.

- [0034] 도 5b를 참조하면, 제 1비아만을 수광 소자에 적흥하고 제 2 비아는 수광 소자 칩 패드 부분에 형성된 구조이다.

- [0035] 도 5c를 참조하면, 제 1비아 및 제 2비아를 수광 소자에 적충한 구조이며 제 1비아와 제 2비아는 서로 어긋나게 배치하여 적충한 구조를 가진다.

- [0036] 도 6a는 수광 소자에 대해 세 가지 구조로 각각 제작된 수광 소자의 암전류 특성을 측정한 결과를 도시한 그래 프이고, 도 6b는 수광 소자에 대해 세 가지 구조를 가지는 각각의 수광 소자의 입력 광에 대한 반응도를 측정한 결과를 도시한 그래프이다. 여기서, 측정 조건은 수광 소자의 양 전극(Anode와 Cathode)에 역바이어스가 1V와 2V가 되도록 인가한다.

[0037]

도 6a를 참조하면, 제 1비아를 단일 비아(single via) 형태로 했을 경우에 비해 제 1 비아를 다수의 비아 (multi-via) 구조를 채택한 수광 소자의 암전류가 감소하는 것을 알 수 있다. 다수의 비아 구조 중에서도 제 1 비아와 제 2비아를 서로 어긋나게 배치 적층한 경우(multi-via: Gap2)가 가장 낮은 암전류 값을 보인다.

[0038]

이는 제 1금속층(metal-1)과 반도체(실리콘과 게르마늄의 전극 형성을 위해 도핑한 영역) 사이의 접촉 면적에따라 누설 전류량 차이 때문인 것으로 판단된다.

[0039]

도 6b를 참조하면, 암전류에 대한 세가지 구조에 비해 반응도에서의 조금의 개선된 값을 보인다. 이러한 현상은 수광 소자에서 광신호를 전류 신호로 변환되어 순간 변환된 전류가 다수의 비아를 통해 국부적으로 전류 밀도가 높아지는 현상을 막아주기 때문이다. 특히, 제 1비아와 제 2비아가 서로 어긋나게 배치하여 적층한 구조의 경우 제 1금속층에 비해 낮은 저항값을 가지는 제 2금속층을 다수의 제 2비아를 이용하여 수광 소자에 적층하여 제 1 금속층에서 포집한 전류 신호를 손실 없이 출력하기 때문에 보다 개선된 반응도를 보인다.

### 도면

#### 도면1

### 도면2

## 도면3

## 도면4a

## *도면4b*

## 도면5a

## *도면5b*

## 도면5c

[Multi-via:Gap2 구조]

## 도면6a

# *도면6b*