(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3854190号 (P3854190)

(45) 発行日 平成18年12月6日 (2006.12.6)

(24) 登録日 平成18年9月15日 (2006.9.15)

(51) Int.C1.

FI

HO2P 6/16 (2006.01) HO2M 7/537 (2006.01) HO2P 6/00 331H HO2M 7/537 C

請求項の数 5 (全 18 頁)

(21) 出願番号 (22) 出願日 特願2002-126962 (P2002-126962) 平成14年4月26日 (2002.4.26)

(65) 公開番号 (43) 公開日

審査請求日

特開2003-324928 (P2003-324928A) 平成15年11月14日 (2003.11.14) 平成16年8月4日 (2004.8.4) (73)特許権者 000001247

株式会社ジェイテクト

大阪府大阪市中央区南船場3丁目5番8号

|(74)代理人 100068755

弁理士 恩田 博宣

(74)代理人 100105957

弁理士 恩田 誠

|(72)発明者 鈴木 浩

愛知県刈谷市朝日町1丁目1番地 豊田工

機株式会社内

審査官 杉浦 貴之

最終頁に続く

#### (54) 【発明の名称】モータ制御装置

## (57)【特許請求の範囲】

#### 【請求項1】

電源の印加点と接地点の間にブラシレスDCモータのU,V,W各相毎に対応して設けられた各回路において、直列に配置され排他的に選択されるスイッチ手段である電源側に配置された上段FET及び接地側に配置された下段FETと、

当該上段FET及び下段FETの間に設けられ、各相の上段FET及び下段FETの開閉の組み合わせによりU,V,W各相のモータ巻線に駆動電流を供給する接続点と、

前記回路の電流を検出するため電流検出手段と、

前記スイッチ手段を制御して前記ブラシレスDCモータを駆動するスイッチ制御手段と を備えたモータ制御装置において、

所定のタイミングで前記電流検出手段により電流を検出する異常電流検出手段と、

前記異常電流検出手段により検出した電流値に基づきモータ駆動回路の異常を判定するモータ駆動回路異常判定手段と、

前記異常電流検出手段により検出した電流値に基づきデッドタイム設定値を修正する修 正手段とを備え、

前記異常電流検出手段は、U,V,W相のいずれかのゲート信号が少なくともオンからオフする立ち下がりエッジ、若しくは、オフからオンする立ち上がりエッジのいずれかを検出して、当該タイミングを基準にして前記電流検出手段により各相毎のデッドタイムの貫通電流を検出することを特徴とするモータ制御装置。

## 【請求項2】

前記修正手段は、予め設定されたターンオフデッドタイムおよびターンオンデッドタイムにより設定されるデッドタイム設定値を、前記異常電流検出手段に基づいて所定の貫通電流を検出しない場合は所定時間短縮し、前記所定の貫通電流を検出した場合は所定時間延長することを特徴とする請求項1に記載のモータ制御装置。

#### 【請求項3】

前記修正手段は、所定のデッドタイム設定値で貫通電流を検出した場合は、当該貫通電流を検出したデッドタイム設定値より短縮しないことを特徴とする請求項2に記載のモータ制御装置。

#### 【請求項4】

<u>前記修正手段は、各相毎に独立してデッドタイム設定値を設定することを特徴とする請</u> 求項2又は請求項3に記載のモータ制御装置。

#### 【請求項5】

<u>前記修正手段は、前記デッドタイム設定値をターンオフデッドタイムおよびターンオン</u> デッドタイム毎に独立して設定すること

を特徴とする請求項2乃至請求項4のいずれか1項に記載のモータ制御装置。

#### 【発明の詳細な説明】

#### [00001]

## 【発明の属する技術分野】

本発明は、電動パワーステアリング装置のアシスト用モータ等に利用する 3 相ブラシレス D C モータのモータ制御装置に係り、詳しくは、デッドタイムを極力小さくするようにアクティブにデッドタイム値を設定し、モータの電源利用率、制御性の向上と異音低減を図ることができるモータ制御装置に関するものである。

### [0002]

#### 【従来の技術】

例えば電動パワーステアリング装置のアシスト用モータには比較的俊敏で高トルクを発生でき、制御がしやすいU,V,W相をもった3相プラシレスDCモータ(以下モータと略記する)が利用されている。このモータの制御装置では、モータ駆動装置にパワーMOSFET(Metal Oxide Semiconductor Field Effect Transistor)などにより構成されるスイッチ手段を備えたトランジスタインバータを備える。このモータ駆動装置では、モータのU,V,Wの各相毎に上段のFETと下段のFETを、CPUを備えたモータ制御されている。しかし、何らかの理由でこの上段FETと下段FETは、同時にオンされた状態になると、その相の上段FETと同相の下段FETは、同時にオンされた状態になると、その相の上段FETと同相の下段FETがモータを通過しないで、電源から法になると、その相の上段FETと同相の下段FETが充っタを通過しないで、電源が流れてしまう。この場合、下ETを破壊してしまうことがある。そこで、一方のFETをオンするときには、遅延回路により遅延させデッドタイムを設けて他方のFETがオフされてから所定時間経過後にオンすることで貫通電流を防止し、FETを保護するようにしていた。

## [0003]

# 【発明が解決しようとする課題】

しかしながら、パワーMOSFET等では、生産時のバラツキが生じるため、反応時間や信号の立ち上がり等に差を生じる場合がある。さらに、温度変化、経年変化により特性に変化を生じる場合がある。このような場合をすべて考慮し所定のデッドタイムを余裕を見て大きめに設定したとき、電源利用率の低下を招き効率が下がるばかりでなく、モータ駆動の信号の非線形的要素となり、トルクリップル(トルクの脈動)を生じて操作性が悪くなったり、異音が生じてしまうという問題があった。

## [0004]

なお、デッドタイムに起因する非線形性を修正するため、デッドタイム補償の処理を行う ことも考えられるが、処理が複雑になるにもかかわらず、静的な処理であるため経年変化 や温度変化に対しては適切な対処ができないという問題があった。

20

30

40

30

40

50

#### [0005]

上記課題を解決するため、本発明のモータ制御装置では、各スイッチ手段が生産のバラツキなどの静的な誤差の他、温度変化や経年変化などの動的な変化により差を生じても、デッドタイム時の貫通電流の発生を早期に発見するモータ制御装置を提供することを目的とする。併せて、デッドタイムを極力小さくするようにアクティブにデッドタイム値を設定し、スイッチ手段の特性のバラツキに起因する非線形性を小さくし、モータの効率と制御性の向上と異音低減を図ることができるモータ制御装置を提供することを目的とする。

## [0006]

#### 【課題を解決するための手段】

請求項1に係るモータ制御装置では、電源の印加点と接地点の間にブラシレスDCモータのU,V,W各相毎に対応して設けられた各回路において、直列に配置され排他的に選択されるスイッチ手段である電源側に配置された上段FET及び接地側に配置された下段FETと、当該上段FET及び下段FETの間に設けられ、各相の上段FET及び下段FETの開閉の組み合わせによりU,V,W各相のモータ巻線に駆動電流を供給する接続点と、前記回路の電流を検出するため電流検出手段と、前記スイッチ手段を制御して前記プラシレスDCモータを駆動するスイッチ制御手段とを備えたモータ制御装置において、所定のタイミングで前記電流検出手段により電流を検出する異常電流検出手段と、前記異常電流検出手段と、前記異常電流検出手段により検出した電流値に基づきデッドタイム設定値を修正する修正手段とが前記異常電流検出手段は、U,V,W相のいずれかのゲート信号が少なくともオンからオフする立ち下がりエッジ、若しくは、オフからオンする立ち上がりエッジのいずれかを検出して、当該タイミングを基準にして前記電流検出手段により各相毎のデッドタイムの貫通電流を検出することを要旨とする。

#### [0007]

この構成に係るモータ制御装置では、モータ駆動回路異常判定手段により異常電流検出手段により検出した電流値に基づきモータ駆動回路の異常を直ちに判定できると<u>とともに</u>、モータ駆動回路異常判定手段により異常と判定されたときに修正手段により異常電流検出手段により検出した電流値に基づきデッドタイム設定値を修正することができ、さらに、U,V,W相のいずれかのゲート信号がオンからオフする立ち下がりエッジ、若しくは、オフからオンする立ち上がりエッジのいずれかを検出して、各相毎の貫通電流をデッドタイムに合わせたタイミングで検出するため、精緻な制御をおこなうことができるという作用がある。

#### [0015]

請求項<u>2</u>に係るモータ制御装置では、請求項<u>1</u>に記載のモータ制御装置<u>の構成に加え</u>、 <u>前記修正手段は、</u>予め設定されたターンオフデッドタイムおよびターンオンデッドタイム により設定されるデッドタイム設定値を、前記異常電流検出手段に基づいて所定の貫通電 流を検出しない場合は所定時間短縮し、前記所定の貫通電流を検出した場合は所定時間延 長することを要旨とした。

## [0016]

この構成に係るモータ制御装置では、請求項<u>1</u>に記載のモータ制御装置の作用に加え、 貫通電流が流れていない場合はデッドタイムを短縮して、電源利用率を高め、且つトルク リップルや異音を低減させることができ、貫通電流が流れてしまった場合は、ターンオフ デッドタイムおよびターンオンデッドタイムを再設定してデッドタイムを延長することで 、FETを安全に保護することができる。

### [0017]

請求項<u>3</u>に係るモータ制御装置では、請求項<u>2</u>に記載のモータ制御装置の構成に加え、前記修正手段は、所定のデッドタイム設定値で貫通電流を検出した場合は、当該貫通電流を検出したデッドタイム設定値より短縮しないことを要旨とする。

#### [0018]

この構成に係るモータ制御装置では、請求項2に記載のモータ制御装置の作用に加え、

修正手段は、所定のデッドタイム設定値で貫通電流を検出した場合は、貫通電流を検出したデッドタイム設定値より短縮しないため、FETを安全に保護するという作用がある。

### [0019]

請求項<u>4</u>に係るモータ制御装置では、請求項<u>2</u>又は請求項<u>3</u>に記載のモータ制御装置の構成に加え、前記修正手段は、各相毎に独立してデッドタイム設定値を設定することを要旨とする。

#### [0020]

この構成に係るモータ制御装置では、請求項<u>2</u>又は請求項<u>3</u>に記載のモータ制御装置の作用に加え、各相毎に独立してデッドタイムを設定するため、個別のFETのバラツキに対応した最適な設定とすることができるという作用がある。

### [0021]

請求項<u>5</u>に係るモータ制御装置では、請求項<u>2</u>乃至請求項<u>4</u>のいずれか1項に記載のモータ制御装置記載のモータ制御装置の構成に加え、前記修正手段は、前記デッドタイム設定値をターンオフデッドタイムおよびターン<u>オン</u>デッドタイム毎に独立して設定することを要旨とする。

### [0022]

この構成に係るモータ制御装置では、請求項<u>2</u>乃至請求項<u>4</u>のいずれか1項に記載のモータ制御装置の作用に加え、ターンオフデッドタイムおよびターン<u>オン</u>デッドタイム毎に独立してデッドタイムを設定するため、個別のFETのバラツキに対応した最適な設定とすることができるという作用がある。

### [0023]

## 【発明の実施の形態】

## (第1の実施形態)

以下、本発明のモータ駆動回路異常判定手段を備えたモータ制御装置を電動パワーステアリング装置におけるモータ制御装置 2 0 として具体化した第 1 の実施形態を図 1 ~ 図 6 を参照して説明する。

## [0024]

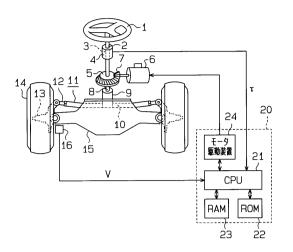

図 1 は、電動パワーステアリング装置の概略を示す。ステアリングホイール 1 に連結したステアリングシャフト 2 には、トーションバー 3 が設けられている。このトーションバー 3 には、トルクセンサ 4 が装着されている。そして、ステアリングシャフト 2 が回転してトーションバー 3 に力が加わると、加わった力に応じてトーションバー 3 が捩れ、その捩れ、即ちステアリングホイール 1 にかかる操舵トルク をトルクセンサ 4 が検出している

## [0025]

ステアリングシャフト 2 には減速機 5 が固着されている。この減速機 5 には電動機としてのブラシレス D C モータ (以下、モータ 6 という)の回転軸に取着したギア 7 が噛合されている。このモータ 6 は、コアに永久磁石を用いた三相同期式永久磁石モータとして構成されている。

## [0026]

又、モータ6には、同モータ6の回転角を検出するためのエンコーダにより構成された回転角センサ30が組み付けられている(図3参照)。回転角センサ30は、モータ6の回転子の回転に応じて / 2ずつ位相の異なる2相パルス列信号と基準回転位置を表す零相パルス列信号を出力する。

## [0027]

減速機 5 にはピニオンシャフト 8 が固着されている。ピニオンシャフト 8 の先端には、ピニオン 9 が固着されるとともに、このピニオン 9 はラック 1 0 と噛合している。ラック 1 0 の両端には、タイロッド 1 2 が固設されており、そのタイロッド 1 2 の先端部にはナックル 1 3 が回動可能に連結されている。このナックル 1 3 には、タイヤとしての前輪 1 4 が固着されている。又、ナックル 1 3 の一端は、クロスメンバ 1 5 に回動可能に連結されている。

10

20

30

50

#### [0028]

従って、モータ6が回転すると、その回転数は減速機5によって減少されてピニオンシャフト8に伝達され、ピニオン及びラック機構11を介してラック10に伝達される。そして、ラック10は、タイロッド12を介してナックル13に設けられた前輪14の向きを変更して車両の進行方向を変えることができる。

#### [0029]

前輪14には、車速センサ16が設けられている。この車速センサ16は、その時の車速を前輪14の回転数に相対する周期のパルス信号としてモータ制御装置20のCPU21にインタフェイスを介して出力する。また、トルクセンサ4は、ステアリングホイール1の操舵トルク に応じた電圧をCPU21にインタフェイスを介して出力している。モータ制御装置20は、車速センサ16、トルクセンサ4からの信号に基づいてモータ6に駆動信号を送って制御する。

#### [0030]

次に、モータ制御装置20の電気的構成を示す。モータ制御装置20は、CPU21、ROM22及びRAM23、U,V,W各相に駆動電流を供給するための電源、インバータ、スイッチ手段からなるモータ駆動装置24を備えている。このモータ制御装置20が本発明のモータ制御装置の一例に相当する。また、このCPU21が本発明のスイッチ制御 手段に相当する。ROM22には、CPU21による演算処理を行わせるための制御ログラムや、演算に必要なデータ等が格納されている。また図示しない基本アシストマップは、操舵トルク (回動トルク)に対応し、かつ車速に応じた基本アシスト電流を求めるためのものであり、操舵トルク に対する基本アシスト電流が記憶されている。RAM23は、CPU21が演算処理を行わせるように構成された記憶手段により、電源を落としてもデッドタイムDT、デッドタイム最小値DTminが保持できるように構成されている。

#### [0031]

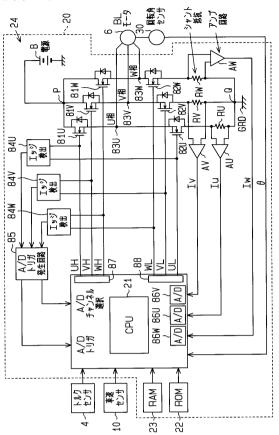

図 2 は、図 1 に示すモータ制御装置 2 0 を詳細に示す図である。以下、モータ制御装置 2 0 についてさらに詳細に説明する。モータ制御装置 2 0 は、演算を行う C P U 2 1 と、モータ 6 に電流を供給するモータ駆動装置 2 4 を主要部とする。

## [0032]

モータ駆動装置 2 4 は、図 2 において、モータ制御装置 2 0 の C P U 2 1 、 R O M 2 2 、 R A M 2 3 を除く部分により構成される。モータ駆動装置 2 4 には図 2 に示すように、スイッチ手段であるパワーMOS F E T (Metal Oxide Semiconductor Field Effect Transistor) により構成されるトランジスタインバータを備える。これらの F E T には、寄生ダイオードが生成されている。そして、このダイオードは、巻線に並列に接続された逆起電力を吸収するフライホイールダイオードとして機能する。まず U 相に対応する F E T 8 1 U , F E T 8 2 U の直列回路と、 V 相に対応する F E T 8 1 V , 8 2 V の直列回路と、 W 相に対応する F E T 8 1 W , F E T 8 2 W の直列回路とが並列に接続されている。

## [0033]

各直列回路のFET81U、FET81V、FET81Wのドレイン側の印加点Pにおいて、車両に搭載されたDC12Vのバッテリからなる電源Bの電圧が印加されている。また、各直列回路のFET82U、FET82V、FET82Wのソース側は、接続点Qで合流された接地点である接地GRDに接続されている。

## [0034]

本実施形態において、U,V,W各相の電源側のFET81U、FET81V、FET8 1Wを「上段FET」という。また、接地GRD側のFET82U、FET82V、FE T82Wを「下段FET」という。

## [0035]

40

20

30

40

50

また、 F E T 8 1 U , F E T 8 2 U間の接続点 8 3 Uがモータ 6 の U 相巻線に接続され、 F E T 8 1 V , F E T 8 2 V間の接続点 8 3 Vがモータ 6 の V 相巻線に接続され、そして F E T 8 1 W , F E T 8 2 W間の接続点 8 3 Wがモータ 6 の W 相巻線に接続されている。 【 0 0 3 6 】

また、下段FETのFET82U、FET82V、FET82Wと接地GRDへの接続点Qとの間には、シャント抵抗RU、RV、RWがそれぞれ挿入されている。シャント抵抗RU、RV、RWの電源側はオペアンプAU、AV、AWの 非反転入力端子に、シャント抵抗RU、RV、RWの電源側はオペアンプAU、AV、AWの 非反転入力端子に、シャント抵抗RU、RV、RWの接地側はオペアンプAU、AV、AWの反転入力端子にそれぞれ接続されている。シャント抵抗RU、RV、RWは、モータ 駆動に影響を与えない極めて小さな抵抗値の抵抗である。そのため、シャント抵抗RU、RV、RWに電流が流れるとその両端に僅かに電位差が生じる。その電位差をオペアンプAU、AV、AWによってそれぞれ増幅し、これをA/Dコンバータ86U、86V、86Wによりディジタル化してシャント抵抗RU、RV、RWを通っている電流をCPU21でそれぞれ演算する。

#### [0037]

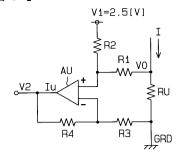

ここで、図5は、アンプ回路を詳細に示す図である。なお、アンプ回路は各相が共通の構成であるため、ここではU相を例に説明する。このアンプ回路は、差動入力型のオペアンプAUを用いて差動増幅回路として構成されている。各相に流れる電流は双方向に流れるため、アンプ回路は、抵抗R2を介して基準電圧V1として+2.5[V]が供給されている。U相の回路のシャント抵抗RUの電源側のV0から抵抗R1を介してオペアンプAUの非反転入力端子+に接続される。また、シャント抵抗RUの接地GRD側から抵抗R3を介してオペアンプの反転入力端子・に接続される。また反転入力端子・と出力端子には、負帰還抵抗R4を接続している。ここでは、R1=R3、R2=R4としている。従って、増幅率Gは、R4/R3により決定される。これらはいわゆるシャントアンメータとして構成され、これらが本発明の電流検出手段に相当する。

## [0038]

なお、電流検出手段を構成する各相のシャント抵抗RU,RV,RWが配設される場所は、下段FETと接地GRDの間に限定されるものではなく、上段FETと電源Bなど適宜設計変更できる。さらに電流検出手段は、シャントアンメータにより構成されるものに限定されず、電流が直接又は間接に検出可能であれば他の構成によるものでもよい。

## [0039]

CPU21は、上段ドライブ回路87を介して、上段FETであるFET81U、FET81V、FET81Wのゲートに接続される。そして、PWM制御部62(図3参照)であるCPU21から所定のタイミングでそれぞれPWM制御信号UU,VU,WU(各相のPWM制御信号にはPWM波信号及びモータ6の回転方向を表す信号を含む)が入力される。

### [0040]

同様に、CPU21は、下段ドライブ回路88を介して、下段FETであるFET82U、FET82V、FET82Wのゲートに接続される。そして、CPU21からそれぞれ PWM制御信号UU,VU,WU(各相のPWM制御信号にはPWM波信号及びモータ6の回転方向を表す信号を含む)が入力される。

## [0041]

トランジスタインバータとして構成されたモータ駆動装置 2 4 は、 P W M 制御信号 U U , V U , W U に対応した 3 相の励磁電流を発生して、 3 相の励磁電流路を介してモータ 6 に それぞれ供給する。

#### [0042]

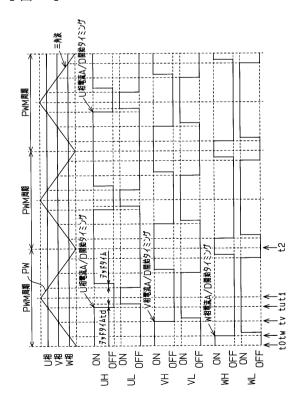

ここで図4は、CPU21からU、V、W各相の上段FET及び下段FETのスイッチングのための制御信号であるゲート信号のタイミングを示したタイミングチャートである。 CPU21は、図4の上部に示すようなPWM周期となる三角波PWを発生させ、U相、 V相、W相に対応するスレッショルドレベルに応じて、それぞれのスイッチングのタイミングを決定する。具体的には、三角波PWがそれぞれのスレッショルドレベルに達すると、上段のFETから下段のFETに切り替えられる。また、スレッショルドレベルを下回れば再び下段のFETから上段のFETに切り替えられる。

#### [0043]

なお、同相の上段FETと下段が同時にオンされた状態になると、モータ6を通過しないで、電源Bから、その相の上段FET、下段FET、接地GRDに直接抜ける回路が形成されていわゆる貫通電流が流れてしまう。この場合、抵抗の大きなモータ6の巻線を通過していないため回路の抵抗値が低く、大電流が流れ、上段FET、下段FETを破壊してしまうことがある。そこで、下段FET82Wのオンのタイミングについては、遅延回路により遅延させデッドタイムtdを設けて貫通電流を防止するようにしている。

#### [0044]

さらに、CPU21がゲート信号を送出していない場合においても、FETが故障して絶縁不良になっている場合には、貫通電流が生じることがある。この場合は、デッドタイムの設定の不良の場合と異なり、初期故障の場合は微弱な電流が流れる場合もある。この場合も他のFET等のさらなる故障を招いたり、著しい制御不良が生じるため速やかに発見して修理する必要が生じる。

### [0045]

ここで、図4に示すタイミングチャートは、上段ドライブ回路87又は下段ドライブ回路888における制御オン/オフ信号(ゲート信号)についてのものであり、ドライブ回路88、各FETの作動については、ゲート信号からスイッチング遅延による遅れを生じている。ここで、ターンオフデッドタイムtd。ffとは、一方のFETがゲート信号によりオフされ、このFETを流れる電流がオフされるまでの時間であり、デッドタイムの開始となる時間である。また、ターンオンデッドタイムtd。nとは、一方のFETがゲート信号によりオンされ、このFETを流れる電流がオンされるまでの時間であり、デッドタイムの終了となる時間である。いずれもゲート信号を契機に開始される。したがって、デッドタイムtdは、理論的には、ターンオフデッドタイムtd。ffとターンオンデッドタイムtd。nの合計時間となる。しかしながら、実際のデッドタイムtdには、種々の変動が生じうるため、これらのタイムラグに加えてマージン分がを含められて、ゲート信号のタイミングが決定される。そのため、図4に示すデッドタイムtdについては、制御オン/オフ信号に非ラップ期間を設けるだけでなく、所定の余裕を持った時間とする必要がある。

## [0046]

このデッドタイム t d の所定時間は、スイッチング遅延の状態などにより異なり、また変化する。具体的には、FET自体の特性、製品のバラツキ、温度変化、経年変化、ノイズの影響などにより異なる。そこで、従来は安全を見て、全ての相のFETに貫通電流が流れないように十分なターンオフデッドタイム t d off とターンオンデッドタイム t d i 必要不可欠な時間であるが、必要以上に大きなマージンを取ると、電源利用率の低下を招く他、トルクリップルや異音の原因となるため、可能な限度で短縮することが好ましい。

## [0047]

以下、図4に従って各FETへの制御信号の送出タイミングを説明する。図4の上部に示すように、初期状態であるタイミングt0では、三角波PWは、U、V、Wのスレッショルドレベルのいずれにも達していないため、全ての上段FETがオンされ、下段FETがオフとなっている。このタイミングでは、図2において、電源Bから接地GRDへ閉じた回路は形成されない。この初期のタイミングでは、モータ巻線のインダクタンスによる逆起電力は生じない。なお、同じ三角波の谷の部分でもタイミングt2のときはモータ6が回転しているため、電源Bからモータ6に電力が供給されていないときでも、スイッチオフによりモータ6の巻線に発生する逆起電力により電流が流れる。

## [0048]

50

40

10

20

このとき、例えば図示しないモータのU相の巻線から発生した電流は、図示しないモータ6内でV相とW相とに分岐する。そして、V相の接続点83Vを通った電流は上段のFET81Vから印加点Pに、W相の接続点83Wを通った電流は上段のFET81Vから印加点Pにそれぞれ流れる。そして印加点Pで合流してU相の上段のFET81Uから接続点83Uを経てモータ6のU相の巻線に環流する。

#### [0049]

t2のタイミングの場合には、上段FET81U、81V、81Wのみで電流が還流し、シャント抵抗RU、RV、RWのいずれにも電流は流れておらず、したがって、いずれのシャント抵抗RU、RV、RWの両端部にも電位差は生じてない。

#### [0050]

次に、t1から三角波PWがW相に対応するレベルになると、制御信号WHが停止してW相の上段FET81Wがオフとなる。次に、デッドタイムtdが経過すると制御信号WLが入力されてW相の下段FET82Wがオンされる。ここで、デッドタイムtdをさらに詳細に説明する。予め設定されたタイミングにより制御信号WHが停止されるとW相の上段FET81Wに起因するターンオフデッドタイムtd。ffが経過後、回路に流れる電流が停止する。ここで、所定のマージンを挟み、W相の下段FET82Wに起因するターンオンデッドタイムtd。nから予め逆算されて設定されたタイミングでFET82Wに制御信号WLが入力される。このように、デッドタイムtdは、制御信号WLの送出タイミングで決定されるターンオフデッドタイムtd。ffと、制御信号WLの送出タイミングで決定されるターンオフデッドタイムtd。nから設定される。これら制御信号WH、WLの送出タイミングは、CPU21が三角波PWを基準にROM22、RAM23に記憶されたデータにより決定される。

### [0051]

W相の上段FET81Wに換えて、W相の下段FET82Wがオンされると、電源Bから印加された電圧により、オンされているU相の上段FET81UとV相の上段FET81 Vに電流が流れるが、オフされているW相の上段FET81Wは回路が開いているため電流が流れない。接続点83U、83Vからそれぞれモータ6に流れ込んだ電流は、モータ6内で合流し、接続点83Wに出力されオンされた下段FET82Wからシャント抵抗RWを経て接地GRDに流れる。このため、オペアンプAWでは、シャント抵抗RWの両端の電位が入力され、その差を増幅してA/Dコンバータ86Wに出力する。A/Dコンバータ86Wでディジタル化された数値がCPU21に入力され、電流値が演算される。

## [0052]

なお、 A / D コンバータ 8 6 Wでは、デッドタイム t d を監視するため、三角波 P W が W 相のレベルに達したタイミング t w で、制御信号 W L のオフを検出しながら、エッジ検出 回路 8 4 W により制御信号 W H の立下りのエッジを検出する。このようにして制御信号 W H の立下りのエッジを検出すると、 A / D トリガ発生回路 8 5 で A / D トリガ信号及び A / D チャンネル選択信号を発生させて、インタフェイスを介して C P U 2 1 に出力し、 A / D コンバータ 8 6 W により直ちにそのチャンネル(相)のサンプリングを開始する。

## [0053]

同様に、三角波 P W が V 相のレベルに達するタイミング t v では、 V 相の上段 F E T 8 1 V がオフされる。デッドタイム t d の経過後 U 相の上段 F E T 8 1 U のみがオンされており、下段では V 相、 W 相の F E T 8 2 V , 8 2 W がオンされた状態になる。そうすると、シャント抵抗 R V 、 R W に電流が流れるため、 V 相、 W 相の電流を検出できる。

## [0054]

また、三角波PWがU相のレベルに達するタイミングtuではU相の上段FET81Uがオフされる。デッドタイムtdの経過後、上段FETはすべてオフとなっており、U相、V相、W相の下段のすべてのFET82U、82V,82Wがオンされた状態になる。そうすると、タイミングtwから三角波PWの山のタイミングt1を含む区間では、例えば、図示しないU相の巻線から流れる電流は、モータ6内のV相、W相の巻線に分岐し接続点83V、83Wからそれぞれ下段FET82V、82Wを通り、シャント抵抗RV、R

10

20

30

Wを通る。そしてGRD側の接続点QでV相、W相の電流が合流してU相のシャント抵抗RU、下段FET82Uを経て接続点83UからU相の巻線に還流する。したがって、この場合は、シャント抵抗RU、RV、RWによりU相、V相、W相の電流を検出できる。また、この場合であるとシャント抵抗RUに流れる電流は、シャント抵抗RV、RWに流れる電流の和に等しい。

#### [0055]

つまり、三角波 P W の山のタイミング t 1 では、全てのシャント抵抗 R U 、 R V 、 R W に電流が流れ、一方、三角波 P W の谷のタイミング t 2 では、全てのシャント抵抗 R U 、 R V 、 R W に電流が流れない。

#### [0056]

さらに所定時間が経過して、三角波PWがU相に対応するレベルを下回ると、U相の下段FET82Uがオフとなる。そして、所定のデッドタイムtd経過後、U相の上段FET81Uがオンになる。次に、三角波PWがV相に対応するレベルを下回ると、V相の下段FET82Vがオフとなり、所定のデッドタイムtd経過後、V相の上段FET81Vがオンになる。そして、三角波PWがW相に対応するレベルを下回ると、W相の下段FET82Wがオフとなり、所定のデッドタイムtd経過後、WV相の上段FET81Wがオンになる。このようにして三角波PWのPWM周期に応じて各FETへの制御信号の送出タイミングが制御される。

#### [0057]

図2に示す、エッジ検出回路84Uは制御信号ULがオフの時の制御信号UHの立下りのエッジを検出する。同様に、エッジ検出回路84Vは、制御信号VLがオフの時の制御信号VHの立下りのエッジを検出し、エッジ検出回路84Wは、制御信号WLがオフの時の制御信号WHの立下りのエッジを検出する。このようにしてそれぞれのエッジを検出すると、A/Dトリガ発生回路85でA/Dトリガ信号及びA/Dチャンネル選択信号を発生させて、インタフェイスを介してCPU21に入力する。

#### [0058]

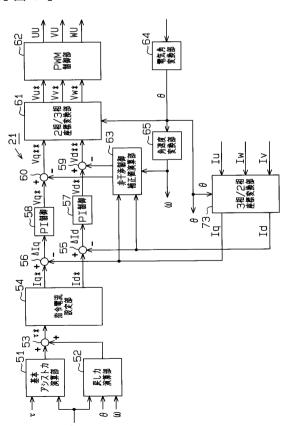

図3は、CPU21内部において、プログラムで実行される機能を示す制御ブロック図である。以下、図3に沿って、電動パワーステアリング装置の機能を説明する。なお、この制御ブロック図で図示されている各部は、独立したハードウエアを示すものではなく、CPU21で実行される機能を概念的に示すものである。

### [0059]

モータ制御装置 2 0 の C P U 2 1 は、指令トルク \*を計算するための基本アシスト力演算部 5 1、戻し力演算部 5 2 及び加算部 5 3を備える。基本アシスト力演算部 5 1 は、トルクセンサ 4 からの操舵トルク 及び車速センサ 1 6 によって検出された車速 V を入力し、操舵トルク の増加にしたがって増加するとともに車速 V の増加にしたがって減少するアシストトルクを計算する。

## [0060]

戻し力演算部52は、車速Vと共にモータ6の回転子の電気角 (回転角に相当)及び角速度 を入力し、これらの入力値に基づいてステアリングシャフト2の基本位置への復帰力及びステアリングシャフト2の回転に対する抵抗力に対応した戻しトルクを計算する。 加算部53は、アシストトルクと戻しトルクを加算することにより指令トルク \*を計算し、指令電流設定部54に出力する。

## [0061]

指令電流設定部 5 4 は、指令トルク \* に基づいて、 2 相指令電流 I d\* , I q \*を計算する。指令電流 I d\* , I q\* は、モータ 6 の回転子上の永久磁石が作り出す回転磁束と同期した回転座標系において、永久磁石と同一方向の d 軸及びこれに直交した q 軸にそれぞれ対応する。これらの指令電流 I d\* , I q\* はそれぞれ d 軸及び g 軸指令電流という。

#### [0062]

d 軸指令電流 I d\*, q 軸指令電流 I q\*は減算器 5 5 , 5 6 に供給される。減算器 5 5 , 5 6 は、 d 軸指令電流 I d\*, q 軸指令電流 I q\*と、 d 軸及び q 軸検出電流 I d , I q とのそ

10

20

30

40

れぞれの差分値 Id, Iqを演算し、その結果をPI制御部(比例積分制御部)57, 58に供給する。

### [0063]

PI制御部57,58は、差分値 Id, Iqに基づきd軸及びq軸検出電流Id,Iqがd軸指令電流Id\*,q軸指令電流Iq\*に追従するようにd軸及びq軸指令電圧Vd\*,Vq\*をそれぞれ計算する。

#### [0064]

d 軸及び q 軸指令電圧 V d\*, V q\*は、非干渉制御補正値演算部63及び減算器59,60により、 d 軸及び q 軸補正指令電圧 V d\*\*, V q\*\*に補正されて2相/3相座標変換部61に供給される。

### [0065]

非干渉制御補正値演算部63は、d軸及びa軸検出電流 Id,Iq及びモータ6の回転子の角速度 に基づいて、d軸及びa軸指令電圧 Vd\*, Va\*のための非干渉制御補正値 ・La・Ia,- ・( a+ La・Id)を計算する。なお、インダクタンスLa、及び磁束 a は、予め決められた定数である。

#### [0066]

減算器 5 9 , 6 0 は、 d 軸及び q 軸指令電圧 V d\* , V q\*から前記非干渉制御補正値をそれぞれ減算することにより、 d 軸及び q 軸補正指令電圧 V d\*\* , V q\*\*を算出して、 2 相 / 3 相座標変換部 6 1 に出力する。 2 相 / 3 相座標変換部 6 1 は、 d 軸及び q 軸補正指令電圧 V d\*\* , V q\*\*を 3 相指令電圧 V u\* , V v\* , V w\*に変換して、同変換した 3 相指令電圧 V u\* , V v\* , V w\*を P W M 制御部 6 2 に出力する。

### [0067]

PWM制御部62は、この3相指令電圧 V u\*, V v\*, V w\*に対応した P W M 制御信号 U U, V U, W U (P W M 波信号及びモータ6の回転方向を表す信号を含む)に変換し、インバータ回路であるモータ駆動装置24に出力する。

#### [0068]

図2に示すように3相の下段FETと接地GRDの間に配設されたシャント抵抗RU,RV,RWの両端から検出した電位差を、オペアンプAU,AV,AWにより増幅する。そして、A/Dコンバータ86U,86V,86WによりA/D変換して、CPU21で電流値を演算してその値を図3に示す3相/2相座標変換部73に電流Iu,Iv,Iwを出力する。

## [0069]

3 相 / 2 相座標変換部 7 3 は、これらの 3 相検出励磁電流 I u , I v , I wを 2 相の d 軸及 び q 軸検出電流 I d , I qに変換し、減算器 5 5 , 5 6 、非干渉制御補正値演算部 6 3 に入力する。

## [0070]

又、回転角センサ30からの2相パルス列信号及び零相パルス列信号は、所定のサンプリング周期で電気角変換部64に連続的に供給されている。電気角変換部64は、前記各パルス列信号に基づいてモータ6における回転子の固定子に対する電気角 を演算し、演算された電気角 を角速度変換部65に入力する。角速度変換部65は、電気角 を微分して回転子の固定子に対する角速度 を演算する。角速度 は、正により回転子の正方向の回転を表し、負により回転子の負方向の回転を表している。

## [0071]

ここで、第1の実施形態のモータ駆動回路異常判定手段を説明する。なお、このモータ駆動回路異常判定の手順を実行する CPU21が本発明のモータ駆動回路異常判定手段に相当する。

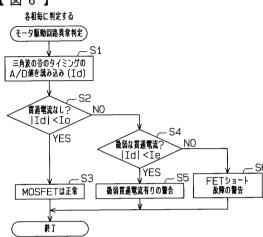

### [0072]

ここで、図6は、モータ駆動回路異常判定の手順を示すフローチャートである。ここでは 説明の便宜上、U相について説明し、他の相の手順は同様であるため省略する。まず、上 述した三角波PW(図4参照)の谷のタイミングt0、t2などでシャント抵抗RUの両 10

20

30

40

端の電位差をオペアンプAUで増幅してA/Dコンバータ86U(図2参照)によりA/D変換してCPU21で演算する。その結果である電流値Idを読み込み、RAM23の所定領域に記憶する(S1)。ここで、読み込んだ電流値Idの絶対値を、異常電流が流れているか否かを判断するため予めROM22に記憶されている所定の閾値であるIoと比較する(S2)。

### [0073]

ここでは、三角波 P W (図 4 参照)の谷のタイミング t 0、 t 2 などでシャント抵抗 R U に流れる電流値 I d を読み込んでいるため、下段 F E T のすべてがオフの状態で、シャント抵抗 R U には、電源 B からの電流が流れていないはずである。但し、下段 F E T が貫通電流などにより損傷を受けて絶縁不良を生じ、タイミング不良により生じる貫通電流に比較して微弱な貫通電流が流れる場合がある。さらに、ダイオードなどに電流が還流することがある。そこで、異常な電流か、正常な電流かを判断する閾値として、予め設定された電流値 I o と比較して判断する。なお、電流値 I d は、回路を両方向に流れるため、この絶対値 | I d | を電流値 I o と比較して、貫通電流か否かを判断する。なお、この所定のタイミングで異常電流を検出する C P U 2 1 が、本発明の異常電流検出手段に相当する。

#### [0074]

ここでもし、  $\mid$  I d  $\mid$  < I o であれば、U相の回路には異常電流が流れていないものと判断し(S 2 ; Y E S)、F E T 8 1 U、F E T 8 2 UのMOSFETは正常として処理をし(S 3)、処理を終了する(終了)。

### [0075]

次に、検出された電流値 I d が、 |I d |<I o ではない場合(S 2; N O)、モータ駆動回路に異常が認められる。そこで、この異常が、微弱な貫通電流によるものか、大電流が流れるものかを判断するため、電流値 I d の絶対値を、予め設定され、R O M 2 2 に記憶されていた電流値 I e と比較をする(S 4)。ここで、もし、 |I d |<I e の場合には(S 4; Y E S)、貫通電流が微弱であると判断され、図示しない報知手段である表示手段に微弱貫通電流有りの警告を表示して(S 5)、処理を終了する(終了)。

## [0076]

一方、  $\mid$  I d  $\mid$  < I e ではない場合には(S 4; NO)、貫通電流が微弱ではないと判断され、F E T のショート故障が疑われるため、報知手段である図示しない表示手段にF E T ショート故障の警告を表示して(S 6)、処理を終了する。

### [0077]

第1の実施形態のモータ制御装置20によれば、上記のような構成及び作用を備えるため、以下のような特徴を得ることができる。

・ モータ駆動回路異常判定手段である CPU21により、異常電流が流れた場合に表示 装置に警告が表示されるため、直ちに使用の中止、故障の修理等の対処が可能になるとい う効果がある。

## [0078]

- ・ 特に、検出されにくい微弱な貫通電流も直ちに検出できるため、他のFETが破壊する前に対処することができるという効果がある。

- ・ さらに、異常が発見された場合に、パワーステアリング装置におけるステアリングの 40 アシストを中止することもできるという効果がある。

#### [0079]

なお、本実施形態は以下のように構成してもよい。

以上のように異常が検出された場合に、表示手段による表示に替えて、若しくは加えてパワーステアリング装置におけるステアリングのアシストを中止するように構成にして もよい。

#### [0800]

或いは、EEPRPMなどからなる記録手段に時間と電流値などを記録しておき、後日のメンテナンスにより読み出して分析するようにしてもよい。

上記実施形態では、電流検出手段を構成するシャント抵抗RU,RV,RWは、下段

20

30

20

30

40

50

FETの下流側に流れる電流を検出するように配置される。また、CPU21は、U,V,W相のすべての上段FETのゲート信号がオフしており、かつすべての下段のFETのゲート信号がオンしているタイミングを検出して、そのタイミングで前記電流検出手段で各相毎の貫通電流を検出している。しかしながら本発明の所定のタイミングはこのようなタイミングに限定されるものではない。例えば、U,V,W相のいずれかのゲート信号がオンからオフする立ち下がリエッジをエッジ検出回路84U,84V,84Wで検出して、当該タイミングを基準にしてCPU21により各相毎の貫通電流を独立して検出するようにしてもよい。このように構成することで、各相のデッドタイムを個別に直接監視でき、より正確な判定が可能になるという効果がある。

#### [0081]

電流の検出はシャント抵抗RU,RV,RW以外の、例えば、ホール素子などを用いて検出するものなどその方法は限定されるものではない。また、その位置も各相の電流が直接又は間接に検出できれば限定されるものではない。また、2つのセンサから3相それぞれの電流を求めるような構成のものでもよい。

#### [0082]

さらに、各相毎に電流検出手段を配置しなくても、全体で 1 つで構成することもできる。このような構成でも異常電流は発見できるからである。

## (第2の実施形態)

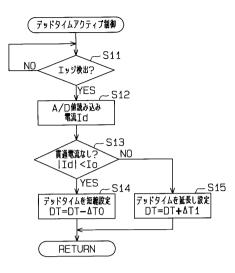

次に、本発明の第2の実施形態を説明する。第2の実施形態では、第1の実施形態のモータ制御装置20の構成に加え、所定タイミングは各相のデッドタイムを直接監視するタイミングである。また、異常電流検出手段により検出する異常電流は、貫通電流であり、この貫通電流の電流値に基づきデッドタイム設定値をアクティブに修正する修正手段をさらに備えたことを特徴とするものである。詳しくは、修正手段であるCPU21は、予め設定されたデッドタイムDTを、異常電流検出手段により検出された電流値Idが、所定の貫通電流を示す電流値Ioより大きな値を検出しない場合は T0時間短縮し、貫通電流を検出した場合は T1の時間延長することを特徴とするものである。なお、ハード構成及び基本的な作用は共通するため、この修正手段における手順のみを説明し、他の説明は省略する。

## [0083]

ここで、図7は、第2の実施形態の修正手段であるCPU21によるデッドタイムアクティブ制御の手順を示すフローチャートである。以下、このフローチャートに従って、デッドタイムアクティブ制御の手順を説明する。なお、この手順は、各相毎に行われるため、U相について説明をし、他の相については説明を省略する。まず、CPU21では、エッジ検出回路84Uによって、上段ドライブ回路87からの制御信号UHの立下リエッジの検出するのを待つ(S11)。ここで、図4に示すtuのタイミングで制御信号UHの立下リエッジの検出をしたときは(S11;YES)、デッドタイムtdの開始であるので、そのときのU相の回路を流れる電流値IdのA/D値を読み込む(S12)。この読み込みは、シャント抵抗RU、オペアンプAU、A/Dコンバータ86Uにより行い、RAM23の所定領域に記憶する。

#### [0084]

次に、ROM22から予め設定された基準電圧である電流値Ioを呼び出し、RAM23に記憶された電流値Idの絶対値と比較する(S13)。ここで、|Id| < Ioである場合は(S13; YES)、貫通電流が流れていないため、DT=DT- T0としてデッドタイムDTを所定時間 T0だけ短縮して設定し(S14)、次のエッジ検出を待つ(S11)。このDTの設定変更により、このDTに基づいて決定される図4のデッドタイムtdが短縮される。なお、デッドタイムtdの短縮は、制御信号のオフのタイミングを遅らせる方法と、制御信号のオンのタイミングを早める方法があり、本実施形態では、それぞれを独立して制御することが可能となっている。

#### [0085]

一方、 | Id | < Ioでない場合は(S13;NO)、貫通電流が流れているため、DT

30

40

50

= D T + T 1 としてデッドタイム D T を所定時間 T 1 だけ延長して設定し(S 1 5 ) 次のエッジ検出を待つ(S 1 1 )。なお、デッドタイム t d の延長は、制御信号のオフのタイミングを早める方法と、制御信号のオンのタイミングを遅らせる方法があり、本実施形態では、それぞれを独立して制御することが可能となっている。この設定により、図 4 のデッドタイム t d が延長される。なお、この T 1 は、制御を損なわない程度に T 0 より十分大きい数値であると、貫通電流の回数が減少するため好ましい。

### [0086]

以上の手順を繰り返すことで、デッドタイムDTは最短化されるという効果がある。なお、この手順は以下のようにしてもよい。

例えば、この処理全体をメインルーチンの途中でカウンターを挿入して所定回数カウントする毎に行うようにして、所定時間ごとに行われるようにしてもよい。このようにすることで、デッドタイム設定値が短時間で変動し、貫通電流が頻繁に流れることを抑制することができる。

## [0087]

特に、S13で貫通電流を検出したNOの場合には、S14のデッドタイム短縮の手順を所定時間実行しないようなフラグをたてて、貫通電流を検出して十分な時間が経過してからS14の手順を行わせるように構成することも好ましい。このようにすることでも貫通電流が流れる回数を抑制することができる。

#### [0088]

### (第3の実施形態)

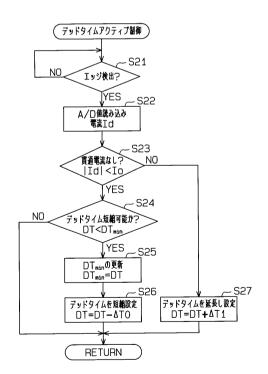

第3の実施形態では、第2の実施形態と比較して、修正手段であるCPU21は、所定のデッドタイム設定値で貫通電流を検出した場合は、その貫通電流を検出したデッドタイム設定値より短縮しないことを特徴とする。第2の実施形態では、貫通電流が繰り返し流れるため、耐圧性のよいFETであれば耐えうるが、耐圧性が低い場合はFETの破壊を生じる。そのため、一旦貫通電流が流れた場合には、そのデッドタイムDTより短いデッドタイムには設定しないように処理をしてFETの保護を高めるものである。なお、ハード構成及び基本的な作用は第1、第2の実施形態と共通するため、この修正手段の手順のみを説明し、他の説明は省略する。

## [0089]

ここで、図8は、第3の実施形態の修正手段であるCPU21によるデッドタイムアクティブ制御の手順を示すフローチャートである。以下、このフローチャートに従って、デッドタイムアクティブ制御の手順を説明する。なお、この手順は、各相毎に行われるため、U相について説明をし、他の相については説明を省略する。まず、CPU21では、エッジ検出回路84Uによって、上段ドライブ回路87からの制御信号UHの立下リエッジの検出するのを待つ(S21)。ここで、図4に示すtuのタイミングで制御信号UHの立下リエッジの検出をしたときは(S21;YES)、デッドタイムtdの開始であるので、そのときのU相の回路を流れる電流値IdのA/D値を読み込む(S22)。この読み込みは、シャント抵抗RU、オペアンプAU、A/Dコンバータ86Uにより行い、RAM23の所定領域に記憶する。

#### [0090]

次に、ROM22から予め設定された基準電圧である電流値Ioを呼び出し、RAM23に記憶された電流値Idの絶対値と比較する(S23)。

ここで、 | Id | < Ioである場合は(S23;YES)、貫通電流が流れていないため、予め設定されているデッドタイム最小値DTminと現在設定されているデッドタイムDTとを比較して、デッドタイムDTが短縮可能か否か判断する(S24)。ここで、仮に、デッドタイム最小値DTminの初期値がDTmin=200nsであり、現在のデッドタイムDT=100nsであるとする。そうすれば、DT<DTminであるので(S24;YES)、DTminを更新する(S25)。

## [0091]

ここでは、DTmin=DTと代入するため、DTminが現在のデッドタイムDT=1

20

30

40

50

0.0 n s となり、D T m i n = 1.0 0 n s に更新される。この場合、さらに貫通電流が流れるデッドタイム D T t d 、現在の値より小さいため、所定時間、例えば、1.0 n s デッドタイムを短くするため、D T = D T - T.0 として、D T = 9.0 n s と短縮設定する(S 2.6)。そして、同様にS 2.1 からの処理を繰り返す(R E T U R N)。

#### [0092]

この場合、貫通電流がなければ(S 2 3 ; Y E S )、S 2 4 では、D T = 9 0 n s であり、D T m i n = 1 0 0 となるので、デッドタイム D T は短縮可能であるので(S 2 4 ; Y E S )、D T m i n = 9 0 n s に更新される(S 2 5 )。そして、D T = 8 0 n s に短縮設定される。

#### [0093]

ここで、実際のデッドタイムの最短の値を55nsとすると、S21~S26で同様の手順が繰り返されてDTが短縮されると、DT=50nsに設定された時に貫通電流が流れることになる。この状態では、DT=50ns、DTmin=60nsとなっている。ここで貫通電流が流れたため(S23;NO)、デッドタイムDTは、DT=DT+ T1と延長される(S27)。ここで所定時間を、例えば T1=10nsとすると、DT=60nsとなる。なお、再び貫通電流を流さないためには、 T0 T1である必要がある。ここで、DT=60nsに設定されると、他の条件が変化しなければ、貫通電流は流れない(S23;YES)。ここで、DT=60nsであり、DTmin=60nsであるので、DT<DTminとなる。前述のように T0 T1であるので、一旦貫通電流が流れた場合は(S23;NO)、必ずS24はNOとなる。したがって、一旦貫通電流が流れた場合は、デッドタイムDTは再びS26の手順で短縮されることはない。

### [0094]

ここで、経年変化や温度変化等の条件が変化して、仮に実際に必要なデッドタイムが65nsに変化した場合を考える。現在の設定値であるDT=60nsの状態では、貫通電流が再び流れ(S23;NO)、デッドタイムはDT=70nsに延長設定される(S27)。この場合は、DTmin=60nsの設定は変更されることはないため、S24では、DT<DTminを満たしえず(S24;NO)、デッドタイムDTは、減少することがない。

## [0095]

以上説明したように、第3の実施形態では、この制御を開始して一回貫通電流が流れると、条件が変化しない限り、貫通電流は二度と流れることがない。またそのときのDTは一定の値を示す。また、条件が変化して再び貫通電流が流れた場合でも、その後は直ちに貫通電流の流れないデッドタイムに再設定され、条件が変わらない限り再び貫通電流が流れることはない。

# [0096]

第3の実施形態では、デッドタイムの最小化をしつつ、貫通電流の流れるリスクを最小化し、FETを最も効果的に保護することができるという効果がある。そのため、比較的耐圧性の低いFETであっても破壊することが少ない。

## [0097]

なお、上記第1~第3の実施形態では、以下のように変更してもよい。

例えば、上記実施形態においてデッドタイム設定値は、各相毎に設定、制御しても、 あるいは3相をまとめて設定、制御してもよい。

## [0098]

なお、実施形態は上段 F E T と下段 F E T を備えたモータ制御装置 2 0 を例に説明したが、モータ制御装置の回路構成はこれに限定されるものではない。また、モータ自体も実施形態に限定されず同様の課題を有するものにも適用できる。

#### [0099]

スイッチ手段として使用するFETは、パワーMOSFETに限定されるものではなく、本発明の適用可能なFETであれば使用できる。

その他、特許請求の範囲を逸脱しない範囲で、当業者により適宜変更し若しくは改良

20

30

して実施できることは言うまでもない。

## [0100]

なお、上記実施形態から以下の発明が抽出できる。

・報知手段を備えたことを特徴とする請求項1乃至請求項<u>5</u>に記載のモータ制御装置。報知手段には、例えばLED、ブザー等が使用できる。この、構成によるモータ制御装置では、異常を早期に発見、認識することができるという効果がある。

## [0101]

## 【発明の効果】

以上、詳述したように、本発明のモータ制御装置では温度変化や経年変化などの動的な変化により差を生じても、デッドタイム時の貫通電流の発生を早期に発見することができるという効果がある。また、デッドタイムを極力小さくするようにアクティブにデッドタイム値を設定し、モータの効率と制御性の向上と異音低減を図ることができるという効果がある。

## 【図面の簡単な説明】

- 【図1】 電動パワーステアリング装置の概略を示す図。

- 【図2】 図1に示すモータ制御装置20を詳細に示す図。

- 【図3】 CPU21内部において、プログラムで実行される機能を示す制御ブロック図

- 【図5】 アンプ回路を詳細に示す図。

- 【図6】 CPU21によるモータ駆動回路異常判定の手順を示すフローチャート。

- 【図7】 第2の実施形態の修正手段である、CPU21によるデッドタイムアクティブ 制御の手順を示すフローチャート。

- 【図8】 第3の実施形態の修正手段である、CPU21によるデッドタイムアクティブ 制御の手順を示すフローチャート。

## 【符号の説明】

B...電源、GRD...接地、P...印加点、Q,83U,83V,83W...接続点、AU,AV,AW...オペアンプ、RU,RV,RW...シャント抵抗、t1,t2,tu,tv,tw...タイミング、td...デッドタイム、DT...デッドタイム、DTmin...最小デッドタイム設定値、Id,Ie,Io...電流値、Iu,Iv,Iw...電流、6...モータ、20...モータ制御装置、CPU...21、24...モータ駆動回路としてのモータ駆動装置、81U,81V,81W...スイッチ手段としての上段のFET、82U,82V,82W...スイッチ手段としての下段のFET

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

# フロントページの続き

## (56)参考文献 特開昭63-099778(JP,A)

特開平04-058782(JP,A)

特開平03-212168(JP,A)

特開平10-337046(JP,A)

特開2003-284352(JP,A)

特開2001-112283(JP,A)

特開2002-204581(JP,A)

# (58)調査した分野(Int.CI., DB名)

H02P 6/16

H02M 7/537