(19) **日本国特許庁(JP)**

(51) Int.C1.

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3831951号 (P3831951)

(45) 発行日 平成18年10月11日(2006.10.11)

(24) 登録日 平成18年7月28日 (2006.7.28)

HO4N 5/14 (2006.01)

HO4N 5/14

$\mathbf{F} \cdot \mathbf{L}$

Z

請求項の数 42 (全 35 頁)

(21) 出願番号 特願平11-500468

(86) (22) 出願日 平成10年5月25日 (1998. 5. 25)

(86) 国際出願番号 PCT/JP1998/002286

(87) 国際公開番号 W01998/054891 (87) 国際公開日 平成10年12月3日 (1998.12.3)

審查譜求日 平成10年12月3日 (1996, 12.5 審查譜求日 平成15年3月5日 (2003, 3.5)

(31) 優先権主張番号 特願平9-154480

(32) 優先日 平成9年5月27日 (1997.5.27)

(33) 優先権主張国 日本国(JP) (31) 優先権主張番号 特願平10-15111

(32) 優先日 平成10年1月9日(1998.1.9)

(33) 優先権主張国 日本国(JP)

(73) 特許権者

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

||(74)代理人

弁理士 五十嵐 孝雄

(74) 代理人

弁理士 下出 隆史

|(74)代理人

弁理士 市川 浩

(72)発明者 竹内 啓佐敏

長野県諏訪市大和3丁目3番5号 セイコ

ーエプソン株式会社内

審査官 佐藤 直樹

最終頁に続く

#### (54) 【発明の名称】画像処理装置およびそのための集積化回路

# (57)【特許請求の範囲】

#### 【請求項1】

画像処理装置であって、

入力される第1のアナログ画像信号の第1の同期信号に同期した第1の周波数をそれぞれ有し、順次位相の異なるNw個の第1のサンプリングクロック信号を生成する第1のサンプリングクロック生成部と、

前記第1のアナログ画像信号のNw個の画素に対するNw個のデジタル画像信号を生成するアナログデジタル変換部と、

# を備え、

前記アナログデジタル変換部は、

前記第1のアナログ画像信号が共通に入力され、前記順次位相の異なるNw個の第1のサンプリングクロック信号のそれぞれに応じて前記第1のアナログ画像信号を順次アナログデジタル変換することによって、Nw個の画素に対する順次位相の異なる前記Nw個のデジタル画像信号を生成するNw個のアナログデジタル変換器と、

# を備え、

前記第1のサンプリングクロック生成部は、

前記第1の同期信号に応じて、前記第1の周波数を有する第1の原サンプリングクロック 信号を生成するための第1の原サンプリングクロック生成回路と、

前記第1の原サンプリングクロック信号に応じて、前記順次位相の異なるNw個の第1のサンプリングクロック信号を生成する第1のサンプリングクロック生成回路と、

を備え、

前記第1のサンプリングクロック生成回路は、前記第1の同期信号と前記順次位相の異なるNw個の第1のサンプリングクロック信号のそれぞれとが一定の位相関係を有するように、前記第1の同期信号のパルスに応じて前記順次位相の異なるNw個の第1のサンプリングクロック信号を初期化することを特徴とする画像処理装置。

#### 【請求項2】

請求項1記載の画像処理装置であって、

前記第1のサンプリングクロック生成回路は、

前記第1の原サンプリングクロック信号に応じて、前記第1の周波数のNw倍の第2の周波数を有し、前記第1のアナログ画像信号をサンプリングするために適した第1のドットクロック信号を生成する第1のPLL回路と、

前記第1のドットクロック信号に応じて、前記第1の周波数を有し、前記第1のドットクロック信号の1周期ずつ位相が異なる前記Nw個の第1のサンプリングクロック信号を抽出する第1のサンプリングクロック抽出回路と、

を備える、画像処理装置。

# 【請求項3】

請求項1記載の画像処理装置であって、

前記第1のサンプリングクロック生成回路は、

前記第1の原サンプリングクロック信号を順次遅延させることにより順次位相の異なる前記Nw個の第1のサンプリングクロック信号を生成する第1の遅延クロック生成回路を備える、画像処理装置。

### 【請求項4】

請求項1ないし3のいずれかに記載の画像処理装置であって、さらに、

デジタル画像信号を記憶するための画像メモリと、

前記アナログデジタル変換部から出力された前記Nw個のデジタル画像信号を前記画像メモリの連続した記憶領域に書き込む書込制御手段と、

を備える、画像処理装置。

#### 【請求項5】

請求項1ないし4のいずれかに記載の画像処理装置であって、

前記第1のサンプリングクロック生成部は、さらに、

前記順次位相の異なるN w 個の第 1 のサンプリングクロック信号のそれぞれと一定の位相関係を有し、順次位相の異なるN w 個の第 2 のサンプリングクロック信号を生成するための第 2 のサンプリングクロック生成回路を備え、

前記アナログデジタル変換部は、さらに、

前記Nw個のアナログデジタル変換器から出力された前記順次位相の異なる前記Nw個のデジタル画像信号を、前記順次位相の異なるNw個の第2のサンプリングクロック信号に従って保持して出力するNw個の保持回路を備える、画像処理装置。

# 【請求項6】

請求項4記載の画像処理装置であって、

前記第1のサンプリングクロック生成部は、さらに、

前記順次位相の異なるN w 個の第 1 のサンプリングクロック信号のそれぞれと一定の位相関係を有し、順次位相の異なるN w 個の第 2 のサンプリングクロック信号を生成するための第 2 のサンプリングクロック生成回路を備え、

前記アナログデジタル変換部は、さらに、

前記Nw個のアナログデジタル変換器から出力された前記順次位相の異なる前記Nw個のデジタル画像信号を、前記順次位相の異なるNw個の第2のサンプリングクロック信号に従って保持して出力するNw個の保持回路を備え、

前記書込制御手段は、前記アナログデジタル変換部から前記Nw個のデジタル画像信号を供給されるとともに、前記第1のサンプリングクロック生成部から前記順次位相の異なるNw個の第2のサンプリングクロック信号のうち少なくとも1個を供給される、画像処理

10

20

30

40

20

30

50

装置。

# 【請求項7】

請求項4または6記載の画像処理装置であって、

前記書込制御手段は、

前記アナログデジタル変換部から供給された前記順次位相の異なるNw個のデジタル画像信号を同位相として出力するための複数段のデジタル画像信号位相調整回路群を備え、

前記複数段のデジタル画像信号位相調整回路群は、各段に含まれる回路数が最終段に向けて次第に減少する階層構造を有しており、

最終段以外の各段に含まれる複数のデジタル画像信号位相調整回路のそれぞれは、入力された複数のデジタル画像信号を当該段の他のデジタル画像信号位相調整回路とは異なる一定の位相で保持して次段のデジタル画像信号位相調整回路に供給し、

前記最終段のデジタル画像信号位相調整回路は、前段から供給された前記Nw個のデジタル画像信号を同じ位相で保持する、画像処理装置。

# 【請求項8】

請求項5または6記載の画像処理装置であって、さらに、

前記順次位相の異なるNw個の第1のサンプリングクロック信号の少なくとも一部を、前記Nw個のアナログデジタル変換器のうちの任意のアナログデジタル変換器にそれぞれ供給するための第1の切換回路と、

前記順次位相の異なるNw個の第2のサンプリングクロック信号の少なくとも一部を、前記Nw個の保持回路のうちで前記第1の切換回路によって前記第1のサンプリングクロック信号が供給されたアナログデジタル変換器に対応した保持回路にそれぞれ供給するための第2の切換回路と、

を備える、画像処理装置。

#### 【請求項9】

請求項1ないし8のいずれかに記載の画像処理装置であって、

前記第1のサンプリングクロック生成部と、前記アナログデジタル変換部とが1チップ内に集積化されている、画像処理装置。

#### 【請求項10】

画像処理装置であって、

出力される第2のアナログ画像信号の第2の同期信号に同期した第3の周波数をそれぞれ有し、順次位相の異なるNr個の第3のサンプリングクロック信号を生成する第2のサンプリングクロック生成部と、

Nr個の画素のデジタル画像信号が並列に入力され、前記順次位相の異なるNr個の第3のサンプリングクロック信号にそれぞれ応じて、前記Nr個の画素のデジタル画像信号をそれぞれデジタルアナログ変換することによって、互いに位相が異なるNr個の部分アナログ画像信号を生成するNr個のデジタルアナログ変換器と、

前記Nr個のデジタルアナログ変換器から出力された前記Nr個の部分アナログ画像信号を、順次切り換えることによって、前記第2のアナログ画像信号を生成するビデオスイッチと、

を備え、 40

前記第2のサンプリングクロック生成部は、

前記第2の同期信号に応じて、前記第3の周波数を有する第2の原サンプリングクロック 信号を生成するための第2の原サンプリングクロック生成回路と、

前記第2の原サンプリングクロック信号に応じて、前記順次位相の異なるNr個の第3のサンプリングクロック信号を生成する第3のサンプリングクロック生成回路と、

# を備え、

前記第3のサンプリングクロック生成回路は、前記第2の同期信号と前記順次位相の異なるNr個の第3のサンプリングクロック信号のそれぞれとが一定の位相関係を有するように、前記第2の同期信号のパルスに応じて前記順次位相の異なるNr個の第3のサンプリングクロック信号を初期化することを特徴とする画像処理装置。

#### 【請求項11】

請求項10記載の画像処理装置であって、

前記第3のサンプリングクロック生成回路は、

前記第2の原サンプリングクロック信号に応じて、前記第3の周波数のNr倍の第4の周波数を有し、前記第2のアナログ画像信号をサンプリングするために適した第2のドットクロック信号を生成する第2のPLL回路と、

前記第2のドットクロック信号に応じて、前記第3の周波数を有し、前記第2のドットクロック信号の1周期ずつ位相が異なる前記Nr個の第3のサンプリングクロック信号を抽出する第2のサンプリングクロック抽出回路と、

を備える、画像処理装置。

# 【請求項12】

請求項10記載の画像処理装置であって、

前記第3のサンプリングクロック生成回路は、

前記第2の原サンプリングクロック信号を順次遅延させることにより順次位相の異なる前記Nr個の第3のサンプリングクロック信号を生成する第2の遅延クロック生成回路を備える、画像処理装置。

#### 【請求項13】

請求項10ないし12のいずれかに記載の画像処理装置であって、さらに、

デジタル画像信号を記憶するための画像メモリと、

前記画像メモリからNr個の画素のデジタル画像信号を読み出す読出制御手段と、

を備える、画像処理装置。

#### 【請求項14】

請求項13記載の画像処理装置であって、

前記読出制御手段は、前記第2のサンプリングクロック生成部から前記順次位相の異なるNr個の第3のサンプリングクロック信号のうち少なくとも1個を供給される、画像処理装置。

# 【請求項15】

請求項10ないし14のいずれかに記載の画像処理装置であって、さらに、

前記順次位相の異なるNr個の第3のサンプリングクロック信号の少なくとも一部を、前記Nr個のデジタルアナログ変換器のうちの任意のデジタルアナログ変換器にそれぞれ供給するための第3の切換回路を備える、画像処理装置。

# 【請求項16】

請求項10ないし14のいずれかに記載の画像処理装置であって、

前記第2のサンプリングクロック生成部と、前記Nr個のデジタルアナログ変換器とが1チップ内に集積化されている、画像処理装置。

# 【請求項17】

画像処理装置であって、

入力された第1のアナログ画像信号が共通に入力されるMw(Mwは2以上の整数)個のアナログデジタル変換器を備えるアナログデジタル変換部と、

前記第1のアナログ画像信号の第1の同期信号に同期した第1の周波数をそれぞれ有し、順次位相の異なるNw(Nwは1以上Mw以下の整数であり、使用されるアナログデジタル変換器の個数を示す)個の第1のサンプリングクロック信号を生成する第1のサンプリングクロック生成部と、

前記アナログデジタル変換器の使用個数Nwに応じて、使用されない(Mw・Nw)個のアナログデジタル変換器の動作を停止させるとともに、前記第1のサンプリングクロック生成部の動作を前記使用個数Nwの値に従って制御し、前記順次位相の異なるNw個の第1のサンプリングクロック信号にそれぞれ応じて前記第1のアナログ画像信号を前記Nw個のアナログデジタル変換器で順次アナログデジタル変換させることによって、前記Nw個の画素のデジタル画像信号を生成させる書込制御信号調整手段と、

を備えることを特徴とする画像処理装置。

10

20

30

40

#### 【請求項18】

請求項17記載の画像処理装置であって、

前記第1のサンプリングクロック生成部は、

前記第1の同期信号に応じて、前記第1の周波数を有する第1の原サンプリングクロック 信号を生成するための第1の原サンプリングクロック生成回路と、

前記第1の原サンプリングクロック信号に応じて、前記順次位相の異なるNw個の第1のサンプリングクロック信号を生成する第1のサンプリングクロック生成回路と、

を備える、画像処理装置。

# 【請求項19】

請求項18記載の画像処理装置であって、

前記第1のサンプリングクロック生成回路は、前記第1の同期信号と前記順次位相の異なるNw個の第1のサンプリングクロック信号のそれぞれとが一定の位相関係を有するように、前記第1の同期信号のパルスに応じて前記順次位相の異なるNw個の第1のサンプリングクロック信号を初期化する、画像処理装置。

## 【請求項20】

請求項18または19記載の画像処理装置であって、

前記第1のサンプリングクロック生成回路は、

前記第1の原サンプリングクロック信号に応じて、前記第1の周波数のNw倍の第2の周波数を有し、前記第1のアナログ画像信号をサンプリングするために適した第1のドットクロック信号を生成する第1のPLL回路と、

前記第1のドットクロック信号に応じて、前記第1の周波数を有し、前記第1のドットクロック信号の1周期ずつ位相が異なる前記Nw個の第1のサンプリングクロック信号を抽出する第1のサンプリングクロック抽出回路と、

を備える、画像処理装置。

# 【請求項21】

請求項18または19記載の画像処理装置であって、

前記第1のサンプリングクロック生成回路は、

前記第1の原サンプリングクロック信号を順次遅延させることにより順次位相の異なる前記Nw個の第1のサンプリングクロック信号を生成する第1の遅延クロック生成回路を備える、画像処理装置。

### 【請求項22】

請求項17ないし21のいずれかに記載の画像処理装置であって、さらに、

デジタル画像信号を記憶するための画像メモリと、

前記アナログデジタル変換部から出力された前記Nw個のデジタル画像信号を前記画像メモリの連続した記憶領域に書き込む書込制御手段と、

を備える、画像処理装置。

#### 【請求項23】

請求項17ないし21のいずれかに記載の画像処理装置であって、

前記第1のサンプリングクロック生成部は、さらに、

前記順次位相の異なるNw個の第1のサンプリングクロック信号のそれぞれと一定の位相 40 関係を有し、順次位相の異なるNw個の第2のサンプリングクロック信号を生成するため の第2のサンプリングクロック生成回路を備え、

前記アナログデジタル変換部は、さらに、

前記Nw個のアナログデジタル変換器から出力された前記順次位相の異なる前記Nw個のデジタル画像信号を、前記順次位相の異なるNw個の第2のサンプリングクロック信号に従って保持して出力するNw個の保持回路を備える、画像処理装置。

# 【請求項24】

請求項22記載の画像処理装置であって、

前記第1のサンプリングクロック生成部は、さらに、

前記順次位相の異なるNw個の第1のサンプリングクロック信号のそれぞれと一定の位相

20

10

~~

30

関係を有し、順次位相の異なるNw個の第2のサンプリングクロック信号を生成するための第2のサンプリングクロック生成回路を備え、

(6)

前記アナログデジタル変換部は、さらに、

前記Nw個のアナログデジタル変換器から出力された前記順次位相の異なる前記Nw個のデジタル画像信号を、前記順次位相の異なるNw個の第2のサンプリングクロック信号に従って保持して出力するNw個の保持回路を備え、

前記書込制御手段は、前記アナログデジタル変換部から前記Nw個のデジタル画像信号を供給されるとともに、前記第1のサンプリングクロック生成部から前記順次位相の異なるNw個の第2のサンプリングクロック信号のうち少なくとも1個を供給される、画像処理装置。

【請求項25】

請求項22または24記載の画像処理装置であって、

前記書込制御手段は、

前記アナログデジタル変換部から供給された前記順次位相の異なるNw個のデジタル画像信号を同位相として出力するための複数段のデジタル画像信号位相調整回路群を備え、

前記複数段のデジタル画像信号位相調整回路群は、各段に含まれる回路数が最終段に向けて次第に減少する階層構造を有しており、

最終段以外の各段に含まれる複数のデジタル画像信号位相調整回路のそれぞれは、入力された複数のデジタル画像信号を当該段の他のデジタル画像信号位相調整回路とは異なる一定の位相で保持して次段のデジタル画像信号位相調整回路に供給し、

前記最終段のデジタル画像信号位相調整回路は、前段から供給された前記Nw個のデジタル画像信号を同じ位相で保持する、画像処理装置。

【請求項26】

請求項23または24記載の画像処理装置であって、さらに、

前記順次位相の異なるNw個の第1のサンプリングクロック信号の少なくとも一部を、前記Nw個のアナログデジタル変換器のうちの任意のアナログデジタル変換器にそれぞれ供給するための第1の切換回路と、

前記順次位相の異なるNw個の第2のサンプリングクロック信号の少なくとも一部を、前記Nw個の保持回路のうちで前記第1の切換回路によって前記第1のサンプリングクロック信号が供給されたアナログデジタル変換器に対応した保持回路にそれぞれ供給するための第2の切換回路と、

を備える、画像処理装置。

【請求項27】

請求項17ないし26のいずれかに記載の画像処理装置であって、

前記第1のサンプリングクロック生成部と、前記アナログデジタル変換部とが1チップ内に集積化されている、画像処理装置。

【請求項28】

画像処理装置であって、

Mr(Mrは2以上の整数)個のデジタルアナログ変換器と、

出力される第2のアナログ画像信号の第2の同期信号に同期した第3の周波数をそれぞれ有し、順次位相の異なるNr(Nrは1以上Mr以下の整数であり、使用されるデジタルアナログ変換器の個数を示す)個の第3のサンプリングクロック信号を生成する第2のサンプリングクロック生成部と、

前記デジタルアナログ変換器の使用個数Nrに応じて、使用されない(Mr-Nr)個のデジタルアナログ変換器の動作を停止させるとともに、前記第2のサンプリングクロック生成部の動作を前記使用個数Nrの値に従って制御し、前記順次位相の異なるNr個の第3のサンプリングクロック信号にそれぞれ応じて前記Nr個の画素のデジタル画像信号を前記Nr個のデジタルアナログ変換器で順次デジタルアナログ変換させることによって、互いに位相が異なるNr個の部分アナログ画像信号を生成させる読出制御信号調整手段と

10

20

30

50

前記Nr個のデジタルアナログ変換器から出力された前記Nr個の部分アナログ画像信号を、順次切り換えることによって、前記第2のアナログ画像信号を生成するビデオスイッチと、

を備えることを特徴とする画像処理装置。

### 【請求項29】

請求項28記載の画像処理装置であって、

前記第2のサンプリングクロック生成部は、

前記第2の同期信号に応じて、前記第3の周波数を有する第2の原サンプリングクロック 信号を生成するための第2の原サンプリングクロック生成回路と、

前記第2の原サンプリングクロック信号に応じて、前記順次位相の異なるNr個の第3のサンプリングクロック信号を生成する第3のサンプリングクロック生成回路と、

を備える、画像処理装置。

# 【請求項30】

請求項29記載の画像処理装置であって、

前記第3のサンプリングクロック生成回路は、前記第2の同期信号と前記順次位相の異なるNr個の第3のサンプリングクロック信号のそれぞれとが一定の位相関係を有するように、前記第2の同期信号のパルスに応じて前記順次位相の異なるNr個の第3のサンプリングクロック信号を初期化する、画像処理装置。

#### 【請求項31】

請求項29または30記載の画像処理装置であって、

前記第3のサンプリングクロック生成回路は、

前記第2の原サンプリングクロック信号に応じて、前記第3の周波数のNr倍の第4の周波数を有し、前記第2のアナログ画像信号をサンプリングするために適した第2のドットクロック信号を生成する第2のPLL回路と、

前記第2のドットクロック信号に応じて、前記第3の周波数を有し、前記第2のドットクロック信号の1周期ずつ位相が異なる前記Nr個の第3のサンプリングクロック信号を抽出する第2のサンプリングクロック抽出回路と、

を備える、画像処理装置。

# 【請求項32】

請求項29または30記載の画像処理装置であって、

前記第3のサンプリングクロック生成回路は、

前記第2の原サンプリングクロック信号を順次遅延させることにより順次位相の異なる前記Nr個の第3のサンプリングクロック信号を生成する第2の遅延クロック生成回路を備える、画像処理装置。

# 【請求項33】

請求項28ないし32のいずれかに記載の画像処理装置であって、さらに、

デジタル画像信号を記憶するための画像メモリと、

前記画像メモリからNr個の画素のデジタル画像信号を読み出す読出制御手段と、

を備える、画像処理装置。

#### 【請求項34】

請求項33記載の画像処理装置であって、

前記読出制御手段は、前記第2のサンプリングクロック生成部から前記順次位相の異なるNr個の第3のサンプリングクロック信号のうち少なくとも1個を供給される、画像処理装置。

#### 【請求項35】

請求項28ないし34のいずれかに記載の画像処理装置であって、さらに、

前記順次位相の異なるNr個の第3のサンプリングクロック信号の少なくとも一部を、前記Nr個のデジタルアナログ変換器のうちの任意のデジタルアナログ変換器にそれぞれ供給するための第3の切換回路を備える、画像処理装置。

# 【請求項36】

20

30

請求項28ないし35のいずれかに記載の画像処理装置であって、

前記第2のサンプリングクロック生成部と、前記Mr個のデジタルアナログ変換器とが1チップ内に集積化されている、画像処理装置。

#### 【請求項37】

請求項1ないし9、18ないし27のいずれかに記載の画像処理装置であって、さらに、前記第1の原サンプリングクロック信号から、前記第1の原サンプリングクロック信号と同周期であり、Nw個の前記デジタル画像信号を処理するのに適した位相を有する外部サンプリングクロック信号を生成する位相調整回路を備える、画像処理装置。

#### 【請求項38】

請求項1ないし9、37のいずれかに記載の画像処理装置であって、

カラー画像を表すための複数の色信号のそれぞれに関して前記Nw個のアナログデジタル変換器をそれぞれ備えており、各色信号のための前記Nw個のアナログデジタル変換器がそれぞれ別個の集積回路に集積化されている、画像処理装置。

# 【請求項39】

請求項10ないし16のいずれかに記載の画像処理装置であって、

カラー画像を表すための複数の色信号のそれぞれに関して前記Nr個のデジタルアナログ 変換器をそれぞれ備えており、各色信号のための前記Nr個のデジタルアナログ変換器が それぞれ別個の集積回路に集積化されている、画像処理装置。

#### 【請求項40】

請求項17ないし27、37のいずれかに記載の画像処理装置であって、

カラー画像を表すための複数の色信号のそれぞれに関して前記 M w 個のアナログデジタル変換器をそれぞれ備えており、各色信号のための前記 M w 個のアナログデジタル変換器がそれぞれ別個の集積回路に集積化されている、画像処理装置。

#### 【請求項41】

請求項28ないし36のいずれかに記載の画像処理装置であって、

カラー画像を表すための複数の色信号のそれぞれに関して前記Mr個のデジタルアナログ 変換器をそれぞれ備えており、各色信号のための前記Mr個のデジタルアナログ変換器が それぞれ別個の集積回路に集積化されている、画像処理装置。

# 【請求項42】

請求項1,10,17,28のいずれかに記載の画像処理装置と、

前記画像処理装置により処理された画像を表示する表示手段と、

を備える、画像表示装置。

#### 【発明の詳細な説明】

# 技術分野

この発明は、A-D変換やD-A変換の機能を有する画像処理装置に関し、特に、高周波数の画像信号を処理するための技術に関するものである。

#### 背景技術

近年の映像技術の進歩に伴って、画像処理装置において取り扱う画像信号の周波数が次第に高くなる傾向にある。画像信号の周波数が高くなると、これに伴ってアナログデジタル変換(以下、「A-D変換」と称する)器やデジタルアナログ変換(以下、「D-A変換」と称する)器の動作周波数も高くなる。

しかし、 A - D 変換器や D - A 変換器の動作周波数をあまり高めることはできないので、高周波数の画像信号を A - D 変換や D - A 変換するのが困難であるという問題があった。この発明は、従来技術における上述の課題を解決するためになされたものであり、周波数の高い画像信号に対して、 A - D 変換や D - A 変換を容易に行うことのできる技術を提供することを目的とする。

#### 発明の開示

上述の課題の少なくとも一部を解決するため、本発明の第1の画像処理装置は、

入力される第1のアナログ画像信号の第1の同期信号に同期した第1の周波数をそれぞれ有し、順次位相の異なるNw個の第1のサンプリングクロック信号を生成する第1のサン

10

20

30

40

プリングクロック生成部と、

前記第1のアナログ画像信号のNw個の画素に対するNw個のデジタル画像信号を生成するA-D変換部と、

を備え、

前記A - D変換部は、

前記第1のアナログ画像信号が共通に入力され、前記順次位相の異なるN w 個の第1のサンプリングクロック信号のそれぞれに応じて前記第1のアナログ画像信号を順次A - D 変換することによって、N w 個の画素に対する順次位相の異なる前記N w 個のデジタル画像信号を生成するN w 個のA - D 変換器と、

を備えることを特徴とする。

この画像処理装置では、Nw個のA-D変換器のそれぞれが、比較的低い第1の周波数でA-D変換を行えばよいので、入力されるアナログ画像信号の周波数が高い場合にも、容易にアナログ画像信号をデジタル画像信号に変換することが可能となる。

上記画像処理装置において、

前記第1のサンプリングクロック生成部は、

前記第1の同期信号に応じて、前記第1の周波数を有する第1の原サンプリングクロック 信号を生成するための第1の原サンプリングクロック生成回路と、

前記第1の原サンプリングクロック信号に応じて、前記順次位相の異なるNw個の第1のサンプリングクロック信号を生成する第1のサンプリングクロック生成回路と、

を備えることが好ましい。

上記のようにアナログ画像信号の同期信号に同期した原サンプリングクロックを生成すれば、同期信号に同期した順次位相の異なるNw個の第1のサンプリングクロックを容易に生成できる。

上記画像処理装置において、

前記第1のサンプリングクロック生成回路は、前記第1の同期信号と前記順次位相の異なるNw個の第1のサンプリングクロック信号のそれぞれとが一定の位相関係を有するように、前記第1の同期信号のパルスに応じて前記順次位相の異なるNw個の第1のサンプリングクロック信号を初期化することが好ましい。

こうすれば、Nw個の第1のサンプリングクロック信号のそれぞれが、常にアナログ画像信号の同期信号と同じ位相関係を有するので、アナログ画像信号の同期信号間に含まれる時系列に並んだ画素のそれぞれを、常に同じ一定の位相でA-D変換することが可能となる。

上記画像処理装置において、

前記第1のサンプリングクロック生成回路は、

前記第1の原サンプリングクロック信号に応じて、前記第1の周波数のNw倍の第2の周波数を有し、前記第1のアナログ画像信号をサンプリングするために適した第1のドットクロック信号を生成する第1のPLL回路と、

前記第1のドットクロック信号に応じて、前記第1の周波数を有し、前記第1のドットクロック信号の1周期ずつ位相が異なる前記Nw個の第1のサンプリングクロック信号を生成する第1のサンプリングクロック抽出回路と、

を備えるようにしてもよい。

上記のように第1の周波数のNw倍の第2の周波数を有するドットクロック信号を生成すれば、Nw個のA-D変換器のそれぞれにおけるA-D変換に適したNw個の第1のサンプリングクロック信号を容易に生成することができる。

また、上記画像処理装置において、

前記第1のサンプリングクロック生成回路は、

前記第1の原サンプリングクロック信号を順次遅延させることにより順次位相の異なる前記Nw個の第1のサンプリングクロック信号を生成する第1の遅延クロック生成回路を備えるようにしてもよい。

こうすれば、上記の比較的高い第2の周波数を有するドットクロックを生成しなくてもN

10

20

30

40

w個の第1のサンプリングクロック信号を生成できる。この場合には、例えば、各回路を プリント基板上に実装した際に、各回路間の配線に周波数の高い信号を伝送させなくて済 むという利点がある。

さらに、上記画像処理装置において、

デジタル画像信号を記憶するための画像メモリと、

前記 A - D 変換部から出力された前記 N w 個のデジタル画像信号を前記画像メモリの連続した記憶領域に書き込む書込制御手段と、

を備えることが好ましい。

書込制御手段は、Nw個の画素に対するNw個のデジタル画像信号を、画像メモリの連続した記憶領域に書き込むので、画像メモリ内には、元の画素配列の通りに画像信号が格納される。

上記画像処理装置において、

前記第1のサンプリングクロック生成部は、さらに、

前記順次位相の異なるN w 個の第 1 のサンプリングクロック信号のそれぞれと一定の位相関係を有し、順次位相の異なるN w 個の第 2 のサンプリングクロック信号を生成するための第 2 のサンプリングクロック生成回路を備え、

前記A-D変換部は、さらに、

前記Nw個のA-D変換器から出力された前記順次位相の異なる前記Nw個のデジタル画像信号を、前記順次位相の異なるNw個の第2のサンプリングクロック信号に従って保持して出力するNw個の保持回路を備えることが好ましい。

こうすれば、A - D変換部は、A - D変換器から第1のサンプリングクロック信号に従って出力される順次位相の異なるN w 個のデジタル画像信号を、第1のサンプリングクロック信号と一定の位相関係を有する第2のサンプリングクロック信号に従い出力できる。また、上記画像処理装置において、

前記書込制御手段は、前記A-D変換部から前記Nw個のデジタル画像信号を供給されるとともに、前記第1のサンプリングクロック生成部から前記順次位相の異なるNw個の第2のサンプリングクロック信号のうち少なくとも1個を供給されることが好ましい。

こうすれば、書込制御手段において、 A - D 変換部から出力されるデジタル画像信号と同期した信号を用いることができる。したがって、書込制御手段がデジタル画像信号をそのデータの変化点でサンプリングしてしまうという恐れが無くなり、デジタル画像信号のサンプリングを確実に行うことができる。

また、上記画像処理装置において、

前記書込制御手段は、

前記A-D変換部から供給された前記順次位相の異なるNw個のデジタル画像信号を同位相として出力するための複数段のデジタル画像信号位相調整回路群を備え、

前記複数段のデジタル画像信号位相調整回路群は、各段に含まれる回路数が最終段に向けて次第に減少する階層構造を有しており、

最終段以外の各段に含まれる複数のデジタル画像信号位相調整回路のそれぞれは、入力された複数のデジタル画像信号を当該段の他のデジタル画像信号位相調整回路とは異なる一定の位相で保持して次段のデジタル画像信号位相調整回路に供給し、

前記最終段のデジタル画像信号位相調整回路は、前段から供給された前記Nw個のデジタル画像信号を同じ位相で保持するようにしてもよい。

こうすれば、各段のデジタル画像信号位相調整回路において、比較的余裕のあるタイミングでサンプリングすることができるので、順位位相の異なるNw個のデジタル画像信号を容易に同位相のデジタル画像信号とすることができる。

さらに、上記画像処理装置において、

前記順次位相の異なるNw個の第1のサンプリングクロック信号の少なくとも一部を、前記Nw個のA-D変換器のうちの任意のA-D変換器にそれぞれ供給するための第1の切換回路と、

前記順次位相の異なるNw個の第2のサンプリングクロック信号の少なくとも一部を、前

20

10

30

記Nw個の保持回路のうちで前記第1の切換回路によって前記第1のサンプリングクロック信号が供給されたA-D変換器に対応した保持回路にそれぞれ供給するための第2の切換回路と、

を備えるようにしてもよい。

こうすれば、任意の A - D 変換器および保持回路に第 1 および第 2 のサンプリングクロック信号を供給できるので、 N w 個の A - D 変換器および N w 個の保持回路のそれぞれを任意の順番で動作させることができる。

上記画像処理装置において、

前記第1のサンプリングクロック生成部と、前記A-D変換部とが1チップ内に集積化されていることが好ましい。

このように集積化すれば、比較的高い周波数の信号を用いた場合にも誤動作を低減することが可能となる。

本発明の第2の画像処理装置は、

出力される第2のアナログ画像信号の第2の同期信号に同期した第3の周波数をそれぞれ有し、順次位相の異なるNr個の第3のサンプリングクロック信号を生成する第2のサンプリングクロック生成部と、

Nr個の画素のデジタル画像信号が並列に入力され、前記順次位相の異なるNr個の第3のサンプリングクロック信号にそれぞれ応じて、前記Nr個の画素のデジタル画像信号をそれぞれD-A変換することによって、互いに位相が異なるNr個の部分アナログ画像信号を生成するNr個のD-A変換器と、

前記Nr個のD-A変換器から出力された前記Nr個の部分アナログ画像信号を、順次切り換えることによって、前記第2のアナログ画像信号を生成するビデオスイッチと、 を備えることを特徴とする。

この画像処理装置では、Nr個のD-A変換器のそれぞれが、比較的低い第3の周波数でD-A変換を行えばよいので、周波数の高いアナログ画像信号を出力する場合にも、容易にデジタル画像信号をアナログ画像信号に変換することが可能となる。

本発明の第3の画像処理装置は、

入力された第1のアナログ画像信号が共通に入力されるMw(Mwは2以上の整数)個のA-D変換器を備えるA-D変換部と、

前記第1のアナログ画像信号の第1の同期信号に同期した第1の周波数をそれぞれ有し、順次位相の異なるNw(Nwは1以上Mw以下の整数であり、使用されるA-D変換器の個数を示す)個の第1のサンプリングクロック信号を生成する第1のサンプリングクロック生成部と、

前記A - D変換器の使用個数Nwに応じて、使用されない(Nw - Nw)個のA - D変換器の動作を停止させるとともに、前記第1のサンプリングクロック生成部の動作を前記使用個数Nwの値に従って制御し、前記順次位相の異なるNw個の第1のサンプリングクロック信号にそれぞれ応じて前記第1のアナログ画像信号を前記Nw個のA - D変換器で順次A - D変換させることによって、前記Nw個の画素のデジタル画像信号を生成させる書込制御信号調整手段と、

を備えることを特徴とする。

この第3の画像処理装置では、上記の第1の画像処理装置の作用・効果に加えて、例えば、第1のアナログ画像信号の周波数に応じてA-D変換器の使用個数Nwを調整することによって、消費電力を低減することができるという効果がある。

本発明の第4の画像処理装置は、

Mr(Mrは2以上の整数)個のD-A変換器と、

出力される第2のアナログ画像信号の第2の同期信号に同期した第3の周波数をそれぞれ有し、順次位相の異なるNr(Nrは1以上Mr以下の整数であり、使用されるD-A変換器の個数を示す)個の第3のサンプリングクロック信号を生成する第2のサンプリングクロック生成部と、

前記D-A変換器の使用個数Nrに応じて、使用されない(Mr-Nr)個のD-A変換

10

20

30

40

器の動作を停止させるとともに、前記第2のサンプリングクロック生成部の動作を前記使用個数Nrの値に従って制御し、前記順次位相の異なるNr個の第3のサンプリングクロック信号にそれぞれ応じて前記Nr個の画素のデジタル画像信号を前記Nr個のD-A変換器で順次D-A変換させることによって、互いに位相が異なるNr個の部分アナログ画像信号を生成させる読出制御信号調整手段と、

前記Nr個のD-A変換器から出力された前記Nr個の部分アナログ画像信号を、順次切り換えることによって、前記第2のアナログ画像信号を生成するビデオスイッチと、

を備えることを特徴とする。

この第4の画像処理装置では、上記の第2の画像処理装置の作用・効果に加えて、例えば、第2のアナログ画像信号の周波数に応じて D - A 変換器の使用個数 N r を調整することによって、消費電力を低減することができるという効果がある。

上記第1および第3の画像処理装置は、さらに、

前記原サンプリングクロック信号から、前記原サンプリングクロック信号と同周期であり、Nw個の前記デジタル画像信号を処理するのに適した位相を有する外部サンプリングクロック信号を生成する位相調整回路を備えるようにしてもよい。

上記の画像処理装置では、位相調整回路でNw個のデジタル画像信号を処理するのに適した位相を有する外部サンプリングクロック信号を生成することができるので、後段の回路においてA-D変換後のデータの遅延が問題となる場合でも、後段の回路に適切なサンプリングクロックを供給することができる。

本発明の第1の画像処理装置は、

カラー画像を表すための複数の色信号のそれぞれに関して前記 N w 個の A - D 変換器をそれぞれ備えており、各色信号のための前記 N w 個の A - D 変換器がそれぞれ別個の集積回路に集積化されていてもよい。

上記の画像処理装置では、色信号毎にNw個のA-D変換器が集積化されているので、A-D変換器固有のバラツキを調整するリファレンス電圧を、1チップのA-D変換器毎にそれぞれ設けることができ、各色に関する画素間の輝度のバラツキを容易に抑えることができる。

本発明の第2の画像処理装置は、

カラー画像を表すための複数の色信号のそれぞれに関して前記 N r 個の D - A 変換器をそれぞれ備えており、各色信号のための前記 N r 個の D - A 変換器がそれぞれ別個の集積回路に集積化されていてもよい。

上記の画像処理装置では、色信号毎にNr個のD・A変換器が集積化されているので、D・A変換器固有のバラツキを調整するリファレンス電圧を、1チップのD・A変換器毎にそれぞれ設けることができ、各色に関する画素間の輝度のバラツキを容易に抑えることができる。

本発明の第3の画像処理装置は、

カラー画像を表すための複数の色信号のそれぞれに関して前記 M w 個の A - D 変換器をそれぞれ備えており、各色信号のための前記 M w 個の A - D 変換器がそれぞれ別個の集積回路に集積化されていてもよい。

上記の画像処理装置では、色信号毎にMw個のA-D変換器が集積化されているので、A-D変換器固有のバラツキを調整するリファレンス電圧を、1チップのA-D変換器毎にそれぞれ設けることができ、各色に関する画素間の輝度のバラツキを容易に抑えることができる。

本発明の第4の画像処理装置は、

カラー画像を表すための複数の色信号のそれぞれに関して前記 M r 個の D - A 変換器をそれぞれ備えており、各色信号のための前記 M r 個の D - A 変換器がそれぞれ別個の集積回路に集積化されていてもよい。

上記の画像処理装置では、色信号毎にMr個のD-A変換器が集積化されているので、D-A変換器固有のバラツキを調整するリファレンス電圧を、1チップのD-A変換器毎にそれぞれ設けることができ、各色に関する画素間の輝度のバラツキを容易に抑えることが

20

40

50

できる。

本発明の画像表示装置は、

第1ないし第4のいずれかの画像処理装置と、

前記画像処理装置により処理された画像を表示する表示手段と、

を備えることが好ましい。

こうすれば、第1ないし第4の画像処理装置によって処理された画像を、液晶パネルなど の表示手段に表示させることができる。

なお、本発明の態様としては、以下のような種々のものがある。

第1の態様は、コンピュータに上記の発明の各工程または各手段の少なくとも一部の機能 を実行させるコンピュータプログラムを記録した記録媒体である。記録媒体としては、フ レキシブルディスクやCD-ROM、光磁気ディスク、パンチカード、バーコードなどの 符号が印刷された印刷物、コンピュータの内部記憶装置(RAMやROMなどのメモリ) および外部記憶装置等の、コンピュータが読取り可能な種々の媒体を利用できる。

第2の態様は、コンピュータに上記の発明の各工程または各手段の少なくとも一部の機能 を実行させるコンピュータプログラムを通信経路を介して供給するプログラム供給装置で ある。

# 【図面の簡単な説明】

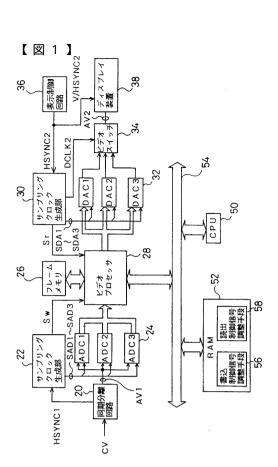

図1は、この発明の実施例としての画像処理装置の全体構成を示すブロック図である。

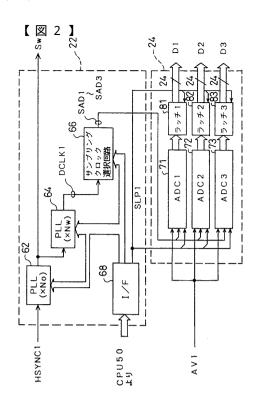

図2は、書込サンプリングクロック生成部22とA-D変換部24の内部構成を示すブロ ック図である。

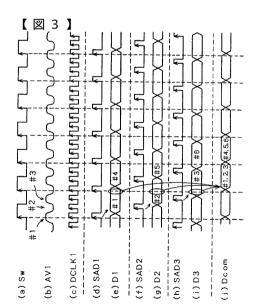

図3は、画像信号の書込動作に関連する主要な信号を示すタイミングチャートである。

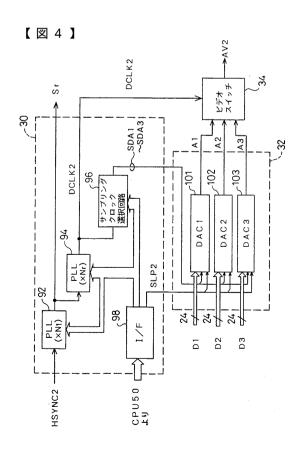

図4は、読出サンプリングクロック生成部30とD-A変換部32の内部構成を、ビデオ スイッチ34と共に示すブロック図である。

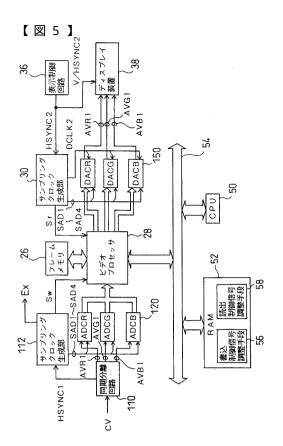

図5は、この発明の第2実施例としての画像処理装置の全体構成を示すブロック図である

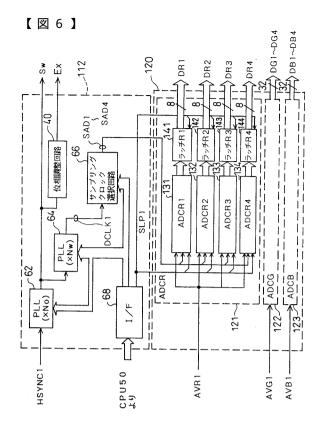

図6は、書込サンプリングクロック生成部112とA-D変換部120の内部構成を示す ブロック図である。

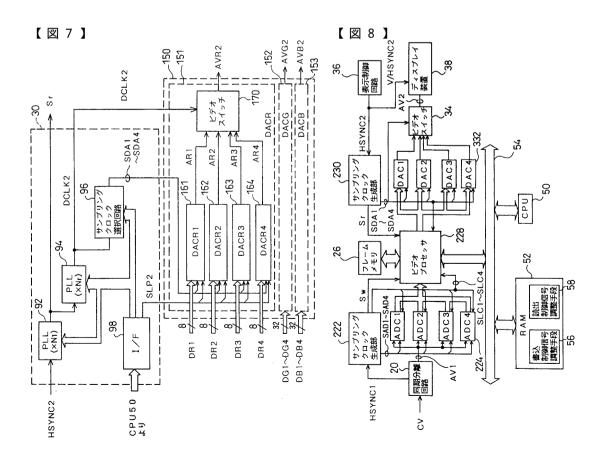

図7は、読出サンプリングクロック生成部30とD-A変換部150の内部構成を示すブ ロック図である。

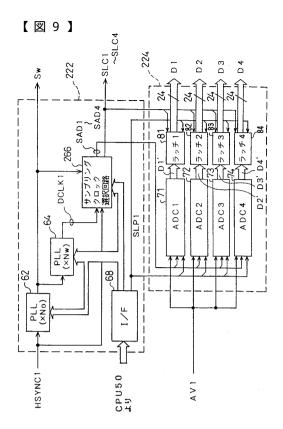

図8は、この発明の第3実施例としての画像処理装置の全体構成を示すブロック図である

図9は、第3実施例における書込サンプリングクロック生成部222とA-D変換部22 4の内部構成を示すブロック図である。

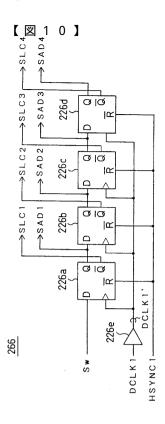

図10は、サンプリングクロック選択回路266の一例を示す回路図である。

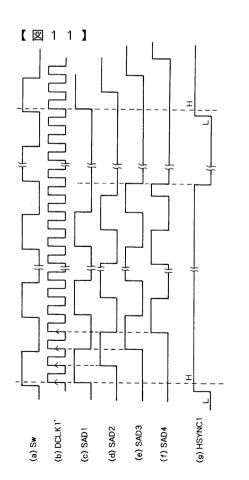

図11は、サンプリングクロック選択回路266の動作を示すタイミングチャートである

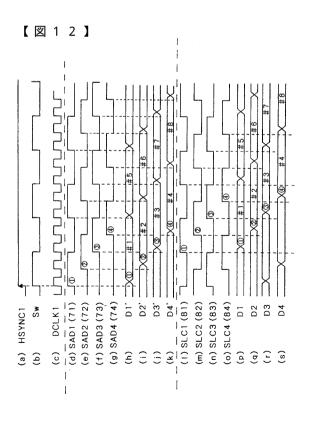

図12は、デジタル画像信号D1~D4の出力を示すタイミングチャートである。

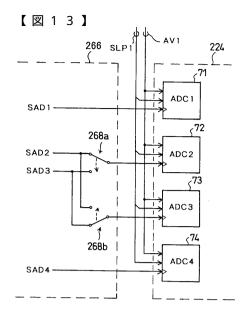

図13は、サンプリングクロック信号SAD1~SAD4のそれぞれを供給するA-D変 換器を変更するためのサンプリングクロック切換回路の一例を示す説明図である。

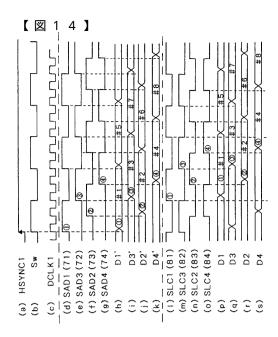

図14は、サンプリングクロック信号SAD1~SAD4のそれぞれを供給するA-D変 換器を変更した場合のデジタル画像信号D1~D4の出力を示すタイミングチャートであ

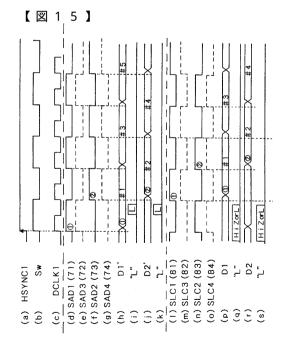

図15は、4個のA-D変換器71~74のうち2個のA-D変換器を休止させた場合の タイミングチャートである。

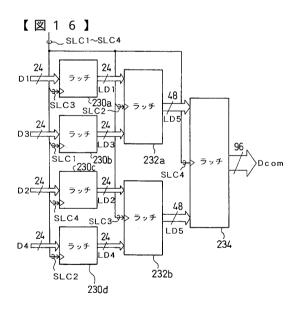

図16は、ビデオプロセッサ228内部のインタフェース部分に備えられたデジタル画像 信号位相調整回路を示すブロック図である。

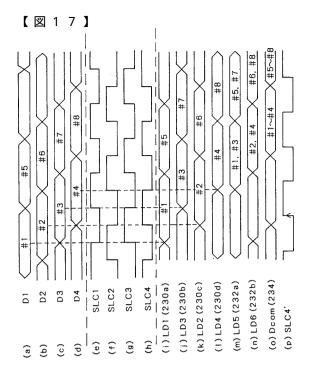

図17は、図16のデジタル画像信号位相調整回路を用いた場合のデジタル画像信号D1 ~ D 4 のタイミングチャートである。

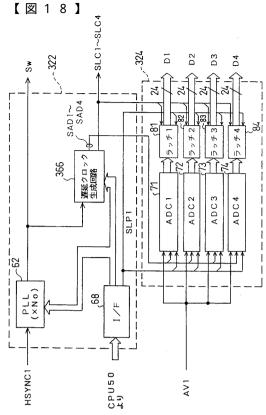

図18は、第4実施例における書込サンプリングクロック生成部322とA-D変換部3 24の内部構成を示すブロック図である。

20

30

40

30

40

50

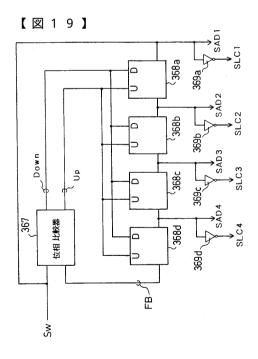

図19は、遅延クロック生成回路366の内部構成を示すブロック図である。

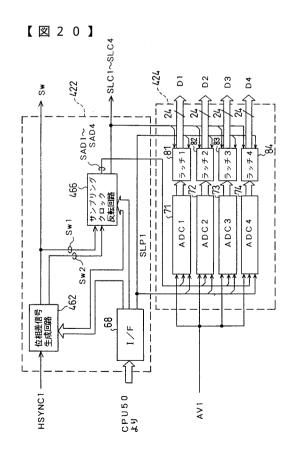

図 2 0 は、第 5 実施例における書込サンプリングクロック生成部 4 2 2 と A - D 変換部 4 2 4 の内部構成を示すブロック図である。

発明を実施するための最良の形態

# A . 第 1 実施例:

次に、本発明の実施の形態を実施例に基づき説明する。図1は、この発明の第1実施例としての画像処理装置の全体構成を示すブロック図である。この画像処理装置は、同期分離回路20と、書込サンプリングクロック生成部22と、3個のA-D変換器を備えたA-D変換部24と、フレームメモリ26と、ビデオプロセッサ28と、読出サンプリングクロック生成部30と、3個のD-A変換器を備えたD-A変換部32と、ビデオスイッチ34と、表示制御回路36と、ディスプレイ装置38と、CPU50と、RAM52とを備えるコンピュータである。ビデオプロセッサ28と、CPU50と、RAM52は、バス54によって互いに接続されている。また、2つのサンプリングクロック生成部22,30と、表示制御回路36もバス54に接続されているが、図1ではその接続を省略している。

同期分離回路20は、入力されたコンポジット画像信号CVから同期信号を分離し、その同期信号とコンポーネント画像信号(同期信号を含まないアナログ画像信号)とを出力する。コンポーネント画像信号は、RGBの3色の画像を表す3つの色信号で構成されている。同期分離回路20で分離された水平同期信号HSYNC1は、書込サンプリングクロック生成部22に供給される。

同期分離回路 2 0 から出力されたコンポーネント画像信号は、A - D変換部 2 4 内の 3 個の A - D変換器によってデジタル画像信号に変換される。後述するように、3 個の A - D変換器は、順次 1 つずつ切り換えながら使用され、アナログ画像信号 A V 1 の 1 / 3 の周波数で A - D変換を行う。この詳しい動作については後述する。

ビデオプロセッサ28は、フレームメモリ26への画像の書込み制御や読出し制御を行うためのマイクロプロセッサである。A-D変換部24で得られたデジタル画像信号は、一旦フレームメモリ26に書き込まれ、必要に応じてフレームメモリ26から読み出される。フレームメモリ26から読み出されたデジタル画像信号は、D-A変換部32で3つの部分アナログ画像信号に変換される。この変換動作については後述する。これらの3つの部分アナログ画像信号は、ビデオスイッチ34で順次切り換えられて、1つのアナログ画像信号AV2と、表示制御回路36から供給される同期信号(垂直同期信号VSYNC2および水平同期信号HSYNC2)に従って画像を表示する。ディスプレイ装置38としては、液晶パネルやCRT、プラズマディスプレイパネルなどを用いた種々の表示装置を用いることができる。

なお、A-D変換動作と、フレームメモリ26への画像信号の書込み動作とは、同期分離回路20から出力された同期信号に同期して行われる。書込サンプリングクロック生成部22は、水平同期信号HSYNC1に基づいて、A-D変換に使用されるサンプリングクロック信号SAD1~SAD3を生成してA-D変換部24に供給するするとともに、書込み動作に使用される書込サンプリングクロック信号SWを生成してビデオプロセッサ28に供給する。

フレームメモリ 2 6 からの画像信号の読み出し動作と、読み出された画像信号のD-A変換動作とは、表示制御回路 3 6 から出力された同期信号に同期して行われる。読出サンプリングクロック生成部 3 0 は、水平同期信号 H S Y N C 2 に基づいて、D-A変換に使用されるサンプリングクロック信号 S D A 1~ S D A 3を生成してD-A変換部 3 2 に供給するするとともに、読出し動作に使用される読出サンプリングクロック信号 S r を生成してビデオプロセッサ 2 8 に供給する。

RAM52には、書込制御信号調整手段56として機能するコンピュータプログラムと、 読出制御信号調整手段58として機能するコンピュータプログラムが格納されている。書 込制御信号調整手段56は、書込時に使用される各種のサンプリングクロック信号Sw,

30

40

50

SAD1~SAD3の周波数を調整するためのパラメータ(後述する)を書込サンプリングクロック生成部22に設定する。また、読出制御信号調整手段58は、読出時に使用される各種のサンプリングクロック信号Sr、SDA1~SDA3の周波数を調整するためのパラメータ(後述する)を読出サンプリングクロック生成部30に設定する。これらの各手段の機能については後述する。

なお、これらの各手段の機能を実現するコンピュータプログラムは、フロッピディスクや CD-ROM等の、コンピュータ読み取り可能な記録媒体に記録された形態で提供される。コンピュータ(画像処理装置)は、その記録媒体からコンピュータプログラムを読み取って内部記憶装置または外部記憶装置に転送する。あるいは、通信経路を介してプログラム供給装置からコンピュータにコンピュータプログラムを供給するようにしてもよい。コンピュータの機能を実現する時には、内部記憶装置に格納されたコンピュータプログラムがコンピュータのCPU50(マイクロプロセッサ)によって実行される。また、記録媒体に記録されたコンピュータプログラムをコンピュータが直接実行するようにしてもよい

この明細書において、コンピュータとは、ハードウェア装置とオペレーションシステムとを含む概念であり、オペレーションシステムの制御の下で動作するハードウェア装置を意味している。また、オペレーションシステムが不要でアプリケーションプログラム単独でハードウェア装置を動作させるような場合には、そのハードウェア装置自体がコンピュータに相当する。ハードウェア装置は、CPU等のマイクロプロセッサと、記録媒体に記録されたコンピュータプログラムを読み取るための手段とを少なくとも備えている。コンピュータプログラムは、このようなコンピュータに、上述の各手段の機能を実現させるプログラムコードを含んでいる。なお、上述の機能の一部は、アプリケーションプログラムでなく、オペレーションシステムによって実現されていても良い。

なお、この発明における「記録媒体」としては、フレキシブルディスクやCD-ROM、 光磁気ディスク、ICカード、ROMカートリッジ、パンチカード、バーコードなどの符 号が印刷された印刷物、コンピュータの内部記憶装置(RAMやROMなどのメモリ)お よび外部記憶装置等の、コンピュータが読取り可能な種々の媒体を利用できる。

図 2 は、書込サンプリングクロック生成部 2 2 と A - D 変換部 2 4 の内部構成を示すブロック図である。書込サンプリングクロック生成部 2 2 は、 2 つの P L L 回路 6 2 , 6 4 と、サンプリングクロック選択回路 6 6 と、 C P U インターフェイス回路 6 8 とを備えている。 A - D 変換部 2 4 は、 3 つの A - D 変換器 7 1 ~ 7 3 と、 3 つのラッチ 8 1 ~ 8 3 とを含んでいる。 3 つの A - D 変換器 7 1 ~ 7 3 は、それぞれ別個に 1 チップに集積化されている。

図3は、画像信号の書込動作に関連する主要な信号のタイミングチャートである。以下では、図2の回路の動作を図3のタイミングチャートに即して説明する。

書込サンプリングクロック生成部22の第1のPLL回路62は、同期分離回路20(図1)から与えられた水平同期信号HSYNC1をN0倍に逓倍することによって、ポットクロック信号Swをヒ成する。第2のPLL回路64は、この書込サングクロック信号SwをNw倍に逓倍することによって、ドットクロック信号Swと、A-D変換部24に入力されるアナログ画像信号AV1の信号レベルは、各画素をサンプリングクロック信号DCLK1の波形1つのピークを有する。符号#1~#3は、アナログ画像信号AV1の信号レベルは、各画素をプリリングするのに適した周波数と位相とを有する。ドットクロック信号DCLK1の全画素をサンソグするのに適した周波数と位相とを有する。ドットクロック信号DCLK1のエッジでアナログ画像信号AV1をA-D変換すれば、全ての画像#1,#2,#3,にをうまくデジタル画像信号に変換することができる。但し、このドットクロック信号DCLK1の変換を行なおうとすると、極めて高速なA-D変換器を使用しなければならない。これに対して、この実施例では、以下に説明するように、ドットクロック信号DCLK1の数分

30

40

50

1 の周波数で A - D 変換を行うだけで、アナログ画像信号 A V 1 の全ての画素に関する A - D 変換を実現することができる。

図3(a)に示す書込サンプリングクロック信号Swは、入力されるアナログ画像信号AV1の水平同期信号HSYNC1に同期し、かつ、ドットクロック信号DCLK1の周波数の1/Nw(Nwは、第2のPLL回路64の逓倍数)の周波数を有する。通常は、第2のPLL回路64の逓倍数Nwは、A-D変換器71~73の全個数に等しく設定される。すなわち、図2の場合には逓倍数Nwの値が3に設定される。A-D変換部24におけるA-D変換動作と、フレームメモリ26へのデジタル画像信号の書込動作とは、この書込サンプリングクロック信号Swと同じ周波数で実行される。

サンプリングクロック選択回路66は、ドットクロック信号DCLK1から、3つのA-D変換器71~73に供給するための3つのサンプリングクロック信号SAD1~SAD3を生成する。図3(d),(f),(h)には、3つのサンプリングクロック信号SAD1~SAD1~SAD3の波形が示されている。3つのサンプリングクロック信号SAD1~SAD3は、書込サンプリングクロック信号Swと同じ周波数を有し、ドットクロック信号DCLK1の1周期ずつ順次位相が異なる信号である。サンプリングクロック選択回路66は、ドットクロック信号DCLK1から3パルスに1パルスの割合でパルスを順次選択して出力することによって、3つのサンプリングクロック信号SAD1~SAD3を生成している。

図2に示すように、3つのA・D変換器71~73には、アナログ画像信号AV1が共通に入力されているとともに、3つのサンプリングクロック信号SAD1~SAD3がそれぞれ供給されている。第1のA・D変換器71は、第1のサンプリングクロック信号SAD1の立ち上がリエッジでアナログ画像信号AV1をA・D変換する。変換されたデジタル画像信号D1は、第1のラッチ81で保持される。図3(e)には、第1のサンプリングクロック信号SAD1の立ち上がリエッジでサンプリングされた第1の画素#1のデジタル画像信号が、第1のラッチ81で保持されて出力されている状態が示されている。同様に、図3(g)には、第2のサンプリングクロック信号SAD2の立ち上がリエッジでサンプリングされた第2の画素#2のデジタル画像信号が、第2のラッチ82で保持されて出力されている状態が示されている。また、図3(ⅰ)には、第3のサンプリングクロック信号SAD3の立ち上がリエッジでサンプリングされた第3の画素#3のデジタル画像信号が、第3のラッチ83で保持されて出力されている状態が示されている。

なお、各画素のデジタル画像信号は、例えばRGBの3色を表す3つの色信号を有する。 RGBの各色信号がそれぞれ8ビットで表現されている場合には、デジタル画像信号D1~D3はそれぞれ24ビットになる。なお、3つのA-D変換器71~73は、3つの色信号を変換するために、独立した3色分の変換器をそれぞれ有している。

こうして得られた3画素分のデジタル画像信号 D 1 ~ D 3 は、7 2 ビットの1組のデジタル画像信号 D com(図 3 ( j ))としてフレームメモリ2 6 内の連続した記憶領域に書き込まれる。この書込動作は、書込サンプリングクロック信号 S w(図 3 ( a ))に同期して行われる。3画素分の1組のデジタル画像信号 D comは7 2 ビットであり、9バイトに相当するので、ビデオプロセッサ2 8 は、1回の書込動作の度に、フレームメモリ2 6 に与える書込アドレス(画素アドレス)を9つずつ増加させる。また、1ラインのデジタル画像信号の書込みが終了すると、ラインアドレスを1つ増加させ、画素アドレスを初期化する。この結果、各ライン上の全ての画素のデジタル画像信号が、フレームメモリ2 6 内では、RGBの3色の色成分を含む1画素分の24ビットの画像信号が、元の画像における画素配列の通りに配列されて格納される。このように、フレームメモリ2 6 内には、同一ライン上の全の画素のデジタル画像信号が、連続したアドレスに格納されているので、フレームメモリ2 6 からデジタル画像信号を読み出す際には、任意の位置のデジタル画像信号を容易に読み出すことができる。

このように、図2に示す書込サンプリングクロック生成部22では、PLL回路64がアナログ画像信号AV1の全画素をサンプリングするのに適したドットクロック信号DCL

K1を生成し、一方、他のPLL回路62が、ドットクロック信号DCLK1の1/3の周波数を有する書込サンプリングクロック信号Swを生成している。また、サンプリングクロック選択回路66は、ドットクロック信号DCLK1の1/3の周波数を有し、かつ、ドットクロック信号DCLK1の1周期ずつ順次位相がずれている3つのサンプリングクロック信号SAD1~SAD3を生成している。この説明からも理解できるように、図2のPLL回路62が本発明における第1の原サンプリングクロック生成回路に相当する。PLL回路64とサンプリングクロック選択回路66とは第1のPLL回路に相当し、サンプリングクロック選択回路66が第1のサンプリングクロック抽出回路に相当する

10

図 2 の各 A - D 変換器 7 1 ~ 7 3 は、サンプリングクロック信号  $SAD1 \sim SAD3$  の周波数で A - D 変換を行えばよいので、ドットクロック信号 DCLK1 に同期して A - D 変換を行う場合に比べて、 1 / 3 の比較的低い速度で変換を行えば済むという利点がある。また、 A - D 変換で得られた 3 画素分のデジタル画像信号  $D1 \sim D3$  は、 1 組のデジタル画像信号 Dcome してフレームメモリ 2 6 内の連続した記憶領域に書き込まれるので、この書込動作もドットクロック信号 DCLK1 の 1 / 3 の周波数で実行すればよい。換言すれば、この実施例では、 A - D 変換動作とフレームメモリ 2 6 への書込動作をドットクロック信号 DCLK1 の周波数の 1 / 3 の周波数で行えばよいので、比較的低速なハードウェア回路を用いて、高周波数のアナログ画像信号を取り扱うことができるという利点がある。

20

また、図2の回路では、高周波数のドットクロック信号 DCLK1で動作するのは、サンプリングクロック選択回路66だけである。すなわち、この実施例の回路では、高い周波数で動作する回路要素が最小限で済むので、回路構成が比較的簡単で、かつ、消費電力も少ないという利点がある。

30

でアリインターフェイス回路68内の図示しないレジスタには、PLL回路62,64の 逓倍数N0,Nw等のパラメータが書込制御信号調整手段56によって設定されている。 第2のPLL回路64における逓倍数Nwは、通常の場合には、実装されているA-D変換器71~73の個数に等しく設定される。しかし、ドットクロック信号DCLK1の周波数が十分に低く、1個あるいは2個のA-D変換器で十分変換を行えるような場合にも3個のA-D変換器71~73の動作クロック周波数が約10のMHzを超える範囲では、周波数の増加に伴ってA-D変換器の10のMHz以下の範囲では、周波数が増加してもA-D変換器の消費電力はあまり変わらない。従って、A-D変換器の動作クロック周波数が約10のMHz以下にできるような場合には、1個あるいは2個のA-D変換器のみで変換を行う方が好ましい。

40

そこで、この実施例では、3つのA・D変換器 7 1~73を使用する場合のサンプリングクロック信号 SAD1~SAD3の周波数が所定値(例えば60MHz)以下になる場合には、CPUインターフェイス回路68が、3つのA・D変換器 7 1~73のいくつかを休止させるためのスリープ信号 SLP1を出力する。例えば、2つのA・D変換器 7 1,72のみを使用する場合には、第3のA・D変換器 7 3にスリープ信号 SLP1を供給して、その動作を停止させる。この時、第2のPLL回路64の逓倍数 Nwは、A・D変換器の使用個数(=2)に等しく設定され、第1のPLL回路62の逓倍数 N0は、元の値のNw0/Nw(=3/2)の値に設定される(ここで、Nw0はA・D変換器の全個数)。この結果、第1のPLL回路62は、元のNw0/Nw(=3/2)倍の周波数を有する書込サンプリングクロック信号 Swを生成し、第2のPLL回路64は、元と同じ周波数のドットクロック信号 DCLK1を生成する。

このように、書込制御信号調整手段56は、CPUインターフェイス回路68を介して、A-D変換器71~73に供給されるサンプリングクロック信号SAD1~SAD3の周波数が所定の範囲内(例えば約50MHz~約100MHz)に収まるように、A-D変

30

50

換器 7 1 ~ 7 3 の使用個数 N w ( N w は 1 ~ 3 ) を調整する機能を有する。こうすれば、処理の対象となるアナログ画像信号 A V 1 の周波数に応じて、画像処理装置の消費電力を低減する動作モードを選択できるという利点がある。なお、 A - D 変換器の動作を停止させるためには種々の方法が可能であり、例えば、 A - D 変換器への電力供給を停止してもよく、また、 A - D 変換器に供給するサンプリングクロック信号の供給を停止してもよい

なお、入力されたアナログ画像信号AV1の水平同期信号HSYNC1および垂直同期信号VSYNC1は、画像の解像度によって固有の特性(周波数や位相関係、信号の極性等)を有している。従って、あらかじめ、主要な画像の解像度と、その同期信号の特性との関係をメモリ等にテーブルとして記憶しておき、同期分離回路20(図1)で分離された同期信号の特性を図示しない同期信号分析回路や同期信号分析プログラムで解析すれば、メモリに記憶されたテーブルから同期信号の特性に対応するドットクロック信号DCLK1の周波数(アナログ画像信号AV1の全画素をサンプリングするための周波数)を求めることができる。そして、アナログ画像信号をサンプリングするための周波数と、A-D変換器に供給する前述のサンプリングクロック信号の所定範囲の周波数との関係から、適切なA-D変換器の使用個数Nwを決定することができる。これにより、比較的低い周波数から非常に高い周波数までの第1のアナログ画像信号に自動的に対応することができる

フレームメモリ26に格納されたデジタル画像信号は、ビデオプロセッサ28によって読み出された後、D-A変換部32によってアナログ画像信号に変換される。図4は、読出サンプリングクロック生成部30とD-A変換部32の内部構成を、ビデオスイッチ34と共に示すブロック図である。読出サンプリングクロック生成部30は、2つのPLL回路92,94と、サンプリングクロック選択回路96と、CPUインターフェイス回路98とを備えている。この読出サンプリングクロック生成部30は、図2に示す書込サンプリングクロック生成部22と同一の構成を有している。D-A変換部32は、3つのD-A変換器101~103を備えている。

読出サンプリングクロック生成部30の第1のPLL回路92は、表示制御回路36(図1)から与えられた水平同期信号HSYNC2をN1倍に逓倍することによって、読出サンプリングクロック信号Srを生成する。第2のPLL回路94は、この読出サンプリングクロック信号SrをNr倍に逓倍することによって、ドットクロック信号DCLK2を生成する。また、サンプリングクロック選択回路96は、このドットクロック信号DCLK2から、3つのD・A変換器101~103に供給するための3つのサンプリングクロック信号SDA1~SDA3を生成する。

読出サンプリングクロック生成部30内で生成される3種類の信号Sr,DCLK2,SDA1~SDA3の周波数および位相の関係は、書込サンプリングクロック生成部22(図2)で生成される3種類の信号Sw,DCLK1,SAD1~SAD3の周波数および位相の関係と同じである。すなわち、ドットクロック信号DCLK2は、ディスプレイ装置38に与えられるアナログ画像信号AV2の全画素をサンプリングするのに適した周波数と位相とを有する。ドットクロック信号DCLK2の周波数は、ディスプレイ装置38のタイプによって決定されている。読出サンプリングクロック信号Srの周波数は、ドットクロック信号DCLK2の周波数の1/Nrである。この値Nr(PLL回路94の逓倍数)は、通常は実装されているD・A変換器101~103の全個数に等しく設定される。また、3つのサンプリングクロック信号SDA1~SDA3は、ドットクロック信号DCLK2の1/Nrの周波数を有すると共に、ドットクロック信号DCLK2の1間期での順次位相がずれている。

3 つのD-A 変換器 1 0 1 ~ 1 0 3 は、3 つのサンプリングクロック信号 S D A 1 ~ S D A 3 の立ち上がリエッジでデジタル画像信号 D 1 ~ D 3 をそれぞれ D - A 変換する。この D - A 変換の動作は、図 3 に示す A - D 変換の動作と逆であり、極めて類似しているので、その詳細な説明は省略する。この D - A 変換によって、例えば、連続した 3 画素分のデジタル画像信号 D 1 ~ D 3 が、位相が互いに異なる 3 つのアナログ画像信号 A 1 ~ A 3 に

30

40

50

それぞれ変換される。これらの3つのアナログ画像信号 A 1 ~ A 3 は、ビデオスイッチ3 4 に入力される。ビデオスイッチ3 4 は、ドットクロック信号 D C L K 2 に同期して3つのアナログ画像信号 A 1 ~ A 3 を順次選択して出力するように切換動作を行う。この結果、元の順番の通りの画素配列で画像を表すアナログ画像信号 A V 2 がビデオスイッチ3 4 から出力される。なお、各 D - A 変換器101~103から出力されるアナログ画像信号 A V 2 の一部を構成しているので、「部分アナログ画像信号」とも呼ぶ。また、部分アナログ画像信号 A 1 ~ A 3 は、それぞれR G B の 3 色を表す3つの色信号を有しているので、ビデオスイッチ3 4 も 3 色分の3つスイッチを有している。

このように、実施例の画像処理装置では、フレームメモリ26からの読出動作と、D-Α 変換動作とをドットクロック信号DCLK2の周波数の1/Nrの周波数で行えばよいので、比較的低速なハードウェア回路を用いて、高周波数のアナログ画像信号AV2を出力することができるという利点がある。また、高周波数のドットクロック信号DCLK2で動作するのは、サンプリングクロック選択回路96と、ビデオスイッチ34だけなので、高い周波数で動作する回路要素が最小限で済み、回路構成が比較的簡単で、かつ、消費電力も少ないという利点がある。

なお、読出制御信号調整手段 5 8 (図 1 ) は、読出サンプリングクロック生成部 3 0 の C P U インターフェイス回路 9 8 に、 D - A 変換器の使用個数 N r (これは P L L 回路 9 4 の逓倍数とも等しい)を設定することが可能である。 C P U インターフェイス回路 9 8 は、 D - A 変換器の使用個数 N r に応じて、 P L L 回路 9 2 , 9 4 の逓倍数 N 1 , N r を設定し、また、必要に応じて D - A 変換器 1 0 1 ~ 1 0 3 のいくつかの動作を停止させるためのスリープ信号 S L P 2 を生成する。この結果、 D - A 変換の電力消費量を低減することができる。

なお、前述したように、フレームメモリ 2 6 内には、同一ライン上の全ての画素のデジタル画像信号が連続したアドレスに格納されている。このため、フレームメモリ 2 6 からデジタル画像信号を読み出す際には、任意の位置のデジタル画像信号を読み出すことができる。従って、A - D 変換器の使用個数 N w と、D - A 変換器の使用個数 N r は、互いに独立に設定することが可能である。また、実装する A - D 変換器の個数も、互いに独立に決定することができる。

B . 第 2 実施例:

図5は、この発明の第2実施例としての画像処理装置の全体構成を示すブロック図である。この画像処理装置は、同期分離回路110と、書込サンプリングクロック生成部112と、A-D変換部120と、フレームメモリ26と、ビデオプロセッサ28と、読出サンプリングクロック生成部30と、D-A変換部150と、表示制御回路36と、ディスプレイ装置38と、CPU50と、RAM52とを備えるコンピュータである。ビデオプロセッサ28と、CPU50と、RAM52は、バス54によって互いに接続されている。また、2つのサンプリングクロック生成部112,30と、表示制御回路36もバス54に接続されているが、図5ではその接続を省略している。同期分離回路110と、書込サンプリングクロック生成部112と、A-D変換部120と、D-A変換部150以外の構成は。第1実施例における画像処理装置とほぼ同じ構成なので、それらの詳細な説明は省略する。

同期分離回路 1 1 0 は、入力されたコンポジット画像信号 C V から同期信号ととコンポーネント画像信号(同期信号を含まないアナログ画像信号)とを分離する。同期分離回路 1 1 0 は、さらに、コンポーネント画像信号を 3 つの色信号に分離する。したがって、同期分離回路 1 1 0 からは、同期信号と 3 つの色信号が出力される。

同期分離回路 1 1 0 によって分離された 3 つの色信号は、 A - D 変換部 1 2 0 内の 3 つの A - D 色信号変換部 1 2 1 ~ 1 2 3 によって色信号毎にデジタル画像信号要素に変換される。ここで、「デジタル画像信号要素」とは、デジタル画像信号の色毎の信号であり、 R G B の 3 つのデジタル画像信号要素の組でデジタル画像信号を構成する。

図6は、書込サンプリングクロック生成部112とA-D変換部120の内部構成を示す

30

40

50

ブロック図である。書込サンプリングクロック生成部112については、第1実施例と同様の構成であるが、さらに位相調整回路40(後述する)を含んでいる。A-D変換部120は、3つのA-D色信号変換部121~123を含んでいる。A-D色信号変換部121は、4つのA-D変換器131~134と、4つのラッチ141~144とを含んでおり、他のA-D色信号変換部122,123についても同様である。

書込サンプリングクロック生成部112では、PLL回路64により、書込サンプリングクロック信号Swを4倍に逓倍したドットクロック信号DCLK1が生成される。また、サンプリングクロック選択回路66により、4つのサンプリングクロック信号SAD1~SAD4が生成される。4つのサンプリングクロック信号SAD1~SAD4は、書込サンプリングクロック信号Swと同じ周波数を有し、ドットクロック信号DCLK1の1周期ずつ順次位相が異なる信号である。

A - D色信号変換部 1 2 1 では、R G B の 3 つの色信号のうち、1 つの色信号 A V R 1 が A - D 変換される。 A - D 色信号変換部 1 2 1 内の 4 つの A - D 変換器 1 3 1 ~ 1 3 4 に は、色信号 A V R 1 が共通に入力されているとともに、4 つのサンプリングクロック信号 S A D 1 ~ S A D 4 がそれぞれ供給されている。第 1 の A - D 変換器 1 3 1 は、第 1 のサンプリングクロック信号 S A D 1 に基づいて、1 つの画素についての色信号 A V R 1 を A - D 変換する。他の A - D 変換器 1 3 2 ~ 1 3 4 についても、それぞれサンプリングクロック信号 S A D 2 ~ S A D 4 に基づいて同様に A - D 変換する。このように、時系列に並んだ 4 つの画素の色信号 A V R 1 が書込サンプリングクロック信号 S w と同じ周期で順次変換される。 A - D 変換器 1 3 1 で変換されたデジタル画像信号要素 D R 1 は第 1 のラッチ 1 4 1 で保持される。他の A - D 変換器 1 3 2 ~ 1 3 4 で変換されたデジタル画像信号 要素 D R 2 ~ D R 4 についても、それぞれラッチ 1 4 2 ~ 1 4 4 で保持される。

A - D色信号変換部121と同じように、他のA - D色信号変換部122,123においても、上述した処理が実行される。すなわち、A - D色信号変換部122に入力された色信号AVG1は、A - D変換されて、変換されたデジタル画像信号要素DG1~DG4はラッチで保持される。また、A - D色信号変換部123に入力された色信号AVB1は、A - D変換されて、変換されたデジタル画像信号要素DB1~DB4はラッチで保持される。なお、1画素分のデジタル画像信号D1は、DR1,DG1,DB1の組で形成され、同様にデジタル画像信号D2~D4が形成される。

こうして得られた4画素分のデジタル画像信号D1~D4は、96ビットの1組のデジタル画像信号として、第1実施例と同じようにフレームメモリ26(図5)内の連続した記憶領域に書き込まれる。

CPUインターフェイス回路 6 8 内の図示しないレジスタには、第1実施例と同様に、PLL回路 6 2 ,6 4 の逓倍数 N 0 ,N w 等のパラメータが書込制御信号調整手段 5 6 によって設定されている。PLL回路 6 4 における逓倍数 N w は、通常の場合には、1 つの A - D 色信号変換部内の A - D 変換器の全個数(4個)に等しく設定される。しかし、ドットクロック信号 D C L K 1 の周波数が低く、1 個ないし 3 個の A - D 変換器で十分変換を行えるような場合には、A - D 変換部 1 2 0 の消費電力を小さくするために 1 個ないし 3 個の A - D 変換器のみで変換を行う方が好ましい。本実施例においても、第1実施例と同様の手法で任意の個数の A - D 変換器の動作を停止することができ、これに適した書込サンプリングクロック信号 S w を生成することができる。

本実施例の画像処理装置は、RGBの3つの色信号毎にA-D色信号変換部121~123 は それぞれ別個に1チップに集積化されている。1色分のA-D変換部を1チップに集積化した場合には、各色に関する画素間の輝度のバラツキを抑えることが容易となる。すなわち、A-D変換器固有のバラツキを調整するリファレンス電圧は、通常、1チップのA-D変換器毎にそれぞれ設けられる。第1実施例では、1チップの各A-D変換器(例えば図2のA-D変換器71)が3色分の変換器を含んでおり、3つのA-D変換器71~73から3色分のデジタル画像信号が出力される。これらの3つのA-D変換器71~73におけるリファレンス電圧が異なる場合には、各色信号の画素間の輝度にバラツキが生じる可能性がある。しかし、

30

40

50

第2実施例においては、色信号毎にA-D色信号変換部121~123が1チップ化されているので、各色信号に対するリファレンス電圧は一定である。したがって、各色信号の画素間の輝度のバラツキを抑えることができる。

位相調整回路40は、書込サンプリングクロック信号Swからの位相を調整することによって、書込サンプリングクロック信号Swと同周期の外部サンプリングクロック信号Exを生成する。外部サンプリングクロック信号Exは、書込サンプリングクロック信号Swと同周期の信号であるため、デジタル画像信号D1~D4とも同周期である。したがって、デジタル画像信号D1~D4の処理を行う後段の回路に適した位相を有するサンプリングクロックとして用いることができる。すなわち、後段の回路でデジタル画像信号D1~D4の遅延が問題となる場合でも、外部サンプリングクロック信号Exを供給すれば、適切なサンプリングを行うことが可能となる。

なお、位相調整回路40は、第1実施例の画像処理装置に設けてもよい。第1実施例において位相調整回路40を設けた場合にも、上述と同様の効果がある。

フレームメモリ 2 6 (図 5 ) に格納されたデジタル画像信号は、ビデオプロセッサ 2 8 によって読み出された後、 D - A 変換部 1 5 0 によってアナログ画像信号に変換される。図 7 は、読出サンプリングクロック生成部 3 0 と D - A 変換部 1 5 0 の内部構成を示すプロック図である。読出サンプリングクロック生成部 3 0 については、第 1 実施例と同様の構成である。 D - A 変換部 1 5 0 は、 3 つの D - A 色信号変換部 1 5 1 ~ 1 5 3 を含んでいる。 D - A 色信号変換部 1 5 1 は、 4 つの D - A 変換器 1 6 1 ~ 1 6 4 と、 1 つのビデオスイッチ 1 7 0 とを含んでいる。他の D - A 色信号変換部 1 5 2 , 1 5 3 についても同様である。

読出サンプリングクロック生成部30では、PLL回路94により、読出サンプリングクロック信号Srを4倍に逓倍したドットクロック信号DCLK2が生成される。また、サンプリングクロック選択回路96により、4つのサンプリングクロック信号SDA1~SDA4が生成される。4つのサンプリングクロック信号SDA1~SDA4は、読出サンプリングクロック信号Srと同じ周波数を有し、ドットクロック信号DCLK2の1周期ずつ順次位相が異なる信号である。

D-A色信号変換部151内の4つのD-A変換器161~164の動作は、A-D変換器131~134(図6)の動作と逆である。このD-A変換によって、デジタル画像信号要素 DR1~DR4は、それぞれ色信号AR1~AR4に変換される。色信号AR1~AR4はビデオスイッチ170に入力され、ドットクロック信号 DCLK2に同期して順次選択して出力するように切換動作を行う。このように出力された色信号 AVR2は、元の順番の通りの画素配列である。

D-A色信号変換部151と同じように、他のD-A色信号変換部152,153においても、上述した処理が実行される。すなわち、D-A色信号変換部152に入力されたデジタル画像信号要素DG1~DG4は、D-A変換されて、色信号AVG2が出力される。また、D-A色信号変換部153に入力されたデジタル画像信号要素DB1~DB4は、D-A変換されて、色信号AVB2が出力される。

CPUインターフェイス回路 6 8 内の図示しないレジスタには、第1実施例と同様に、PLL回路 9 2 , 9 4 の逓倍数 N 1 , N r 等のパラメータが読出制御信号調整手段 5 8 によって設定されている。PLL回路 9 4 における逓倍数 N r は、通常の場合には、1つの D - A 色信号変換部内の D - A 変換器の全個数 (4 個)に等しく設定される。しかし、ドットクロック信号 D C L K 2 の周波数が低く、1 個ないし 3 個の D - A 変換器で十分変換を行えるような場合には、D - A 変換部 1 5 0 の消費電力を小さくするために 1 個ないし 3 個の D - A 変換器のみで変換を行う方が好ましい。本実施例においても、第1実施例と同様の手法で任意の個数の D - A 変換器の動作を停止することができ、これに適した読出サンプリングクロック信号 S r を生成することができる。

本実施例の画像処理装置は、RGBの3つの色信号毎にD-A色信号変換部151~15 3を備えているため、集積化した場合には、画素間の輝度のバラツキを抑えることが容易 となる。すなわち、第1実施例においては、D-A変換器固有のバラツキを調整するリフ ァレンス電圧は、通常、1画素毎のD-A変換器101~103(図4)にそれぞれ設けるため、画素間の輝度にバラツキが生じる可能性がある。しかし、第2実施例においては、色信号毎のD-A色信号変換部151~153のそれぞれにリファレンス電圧を設けることが容易にできるため、画素間の輝度のバラツキを抑えることができる。

なお、本実施例においても、フレームメモリ26内には、同一ライン上の全ての画素のデジタル画像信号が連続したアドレスに格納されている。このため、フレームメモリ26からデジタル画像信号を読み出す際には、任意の位置のデジタル画像信号を読み出すことができる。従って、A-D変換器の使用個数Nwと、D-A変換器の使用個数Nrは、互いに独立に設定することが可能である。また、実装するA-D変換器の個数と、実装するD-A変換器の個数も、互いに独立に決定することができる。

C.第3実施例:

図8は、この発明の第3実施例としての画像処理装置の全体構成を示すブロック図である。この画像処理装置の構成は、図1に示す画像処理装置の構成とほぼ同じであるが、本実施例においては、A-D変換部224は4個のA-D変換器を備え、D-A変換部332は4個のD-A変換器を備えている。本実施例においては、書込サンプリングクロック生成部222とA-D変換部224とビデオプロセッサ228以外については、図1に示す画像処理装置とほぼ同じ動作をするので詳細な説明は省略する。

図9は、第3実施例における書込サンプリングクロック生成部222とA-D変換部224の内部構成を示すブロック図である。書込サンプリングクロック生成部222の内部構成は、第1実施例の内部構成(図2)とほぼ同じである。A-D変換部224は、上述のように4つのA-D変換器71~74と、4つのラッチ81~84とを含んでいる。なお、本実施例のPLL回路62が本発明における第1の原サンプリングクロック生成回路に相当する。PLL回路64とサンプリングクロック選択回路266とは第1のサンプリングクロック生成回路に相当する。また、PLL回路64が本発明における第1のPLL回路に相当し、サンプリングクロック選択回路266が第1のサンプリングクロック抽出回路に相当する。

本実施例のサンプリングクロック選択回路 2 6 6 は、 A - D変換器 7 1 ~ 7 4 に供給するためのサンプリングクロック信号 S A D 1 ~ S A D 4 を出力するとともに、ラッチ 8 1 ~ 8 4 に供給するためのラッチクロック信号 S L C 1 ~ S L C 4 を出力する。また、サンプリングクロック選択回路 2 6 6 には、ドットクロック信号 D C L K 1 に加えて、書込サンプリングクロック信号 S W と水平同期信号 H S Y N C 1 とが入力されている。

図10は、サンプリングクロック選択回路266の一例を示す回路図である。サンプリングクロック選択回路266は4つのDフリップフロップ226a~226dから構成されたシフトレジスタと、遅延回路226eとを備えている。書込サンプリングクロック信号Swは第1のDフリップフロップ226aのデータ入力端子に入力されている。ドットクロック信号DCLK1は遅延回路226eに入力されている。遅延回路226eから出力されたドットクロック信号DCLK1、は4つのDフリップフロップ226a~226dのクロック端子に共通に入力されている。また、水平同期信号HSYNC1は、4つのDフリップフロップ226a~226dのDセット端子に共通に入力されている。

図11は、サンプリングクロック選択回路266の動作を示すタイミングチャートである。以下、図11のタイミングチャートに則してサンプリングクロック選択回路266の動作を説明する。第1のDフリップフロップ226a(図10)は、データ入力端子から入力された書込サンプリングクロック信号Swを、ドットクロック信号DCLK1'の立ち上がりエッジでサンプリングし、サンプリングクロック信号SRD1を出力する。図11(a)~(c)には、書込サンプリングクロック信号Sw、ドットクロック信号DCLK1'、サンプリングクロック信号SAD1の波形が示されている。第2のDフリップフロップ226bは、Dフリップフロップ226aから出力されたサンプリングクロック信号SAD1(図11(c))をドットクロック信号DCLK1'でサンプリングクロック信号SAD3およびサンプリングクロック信号SA

10

20

30

40

30

40

50

D 4 を出力する。図 1 1 ( d ) ~ ( f ) には、サンプリングクロック信号 S A D 2 ~ S A D 4 の波形が示されている。このようにしてサンプリングクロック選択回路 2 6 6 は、順次位相が 9 0 度ずつ異なる 4 つのサンプリングクロック信号 S A D 1 ~ S A D 4 ( 図 1 1 ( C ) ~ ( f ) ) を出力する。

Dフリップフロップ 2 2 6 a ~ 2 2 6 d は、そのリセット端子にLレベルが入力されると、それぞれの出力信号 S A D 1 ~ S A D 4 をLレベルに変化させる。一方、リセット端子にHレベルが入力されると、リセット状態が解除され、再び上述の動作を開始してサンプリングクロック信号 S A D 1 ~ S A D 4 を出力する。したがって、Dフリップフロップのリセット信号として図 1 1 (g)に示すような水平同期信号 H S Y N C 1 を用いれば、水平同期信号 H S Y N C 1 と 4 つのサンプリングクロック信号 S A D 1 ~ S A D 4 との位相関係を常に同じ位相関係に保つことが可能となる。

このサンプリングクロック信号SAD1~SAD4をA-D変換器71~74(図9)に供給すれば、各水平ラインの先頭の画素の画素信号を常に第1のA-D変換器71でA-D変換することができる。一方、上述したような水平同期信号HSYNC1によるリセット動作を行わない場合には、1水平ライン上に存在する第1番目の画素の画像信号を変換するA-D変換器は固定されておらず、いずれのA-D変換器が用いられるかが各水平ライン毎に変動する可能性がある。これに対し、本実施例においては、第1番目の画素信号は、常に第1番目のA-D変換器71で変換できる。なお、リセット信号としては、図11(g)に示す水平同期信号HSYNC1に限られず、例えば、水平同期信号HSYNC1のパルスと常に一定の位相関係で発生するようなパルスを有する他の信号を用いてもよい。

Dフリップフロップ226a~226dから出力されるサンプリングクロック信号SAD1~SAD4は、図10に示すように反転出力端子から出力すればラッチクロック信号SLC1~SLC4としても利用できる。本実施例においては、サンプリングクロック信号SAD1~SAD4のそれぞれと180度異なる位相関係を有するラッチクロック信号SLC1~SLC4が出力されている。すなわち、本実施例においては、PLL回路64とサンプリングクロック選択回路266とが本発明の第2のサンプリングクロック生成回路に相当する。なお、本実施例においては、第1のサンプリングクロック生成回路が第2のサンプリングクロック生成回路も兼ねているが、もちろん第2のサンプリングクロック生成回路を独立に設けてもよい。

図12は、本実施例におけるデジタル画像信号D1~D4の出力を示すタイミングチャー トである。図12(a)~(c)は、上記の水平同期信号HSYNC1と、書込サンプリ ングクロック信号Swと、ドットクロック信号DCLK1の波形を示している。また、図 12(d)~(g)には、サンプリングクロック信号SAD1~SAD4の波形が示され ている。A-D変換器71~74(図9)に入力されたアナログ画像信号AV1は、順次 位相の異なる4つのサンプリングクロック信号SAD1~SAD4(図12(d)~(g ))のそれぞれの立ち上がりエッジで A - D 変換される。図中、信号名と共に記されてい る括弧書き、例えば、図12(d)の「SAD1」と共に記されている「(71)」は、 A - D 変換器「 7 1 」に入力されるクロック信号がサンプリングクロック信号「 S A D 1 」であることを示している。A-D変換器71~74でA-D変換されたアナログ画像信 号 A V 1 は、それぞれデジタル画像信号 D 1 '~ D 4 'として出力される。図 1 2 ( h ) ~ (k)は、デジタル画像信号 D 1 ′ ~ D 4 ′を示している。この信号 D 1 ′ ~ D 4 ′ は ラッチ81~84(図9)に入力され、ラッチクロック信号SLC1~SLC4に従い保 持される。ラッチ81~84で保持された4つのデジタル画像信号D1~D4は、順次9 0 度ずつ位相の異なるデータとなって出力される。図 1 2 ( 1 ) ~ ( o ) は、ラッチクロ ック信号SLC1~SLC4の波形を示しており、図12(p)~(s)は、ラッチクロ ック信号SLC1~SLC4に従い出力されたデジタル画像信号D1~D4を示している

図 1 2 は、サンプリングクロック信号 S A D 1 ~ S A D 4 のそれぞれを A - D 変換器 7 1 ~ 7 4 に供給 し、 A - D 変換器を 7 1、 7 2、 7 3、 7 4 の順に動作させて A - D 変換を

30

40

50

行った場合について示しているが、4つのサンプリングクロック信号 SAD1~SAD4のそれぞれを供給するA-D変換器を変えることにより、A-D変換器の動作順序を変えてもよい。

図13は、サンプリングクロック信号SAD1~SAD4のそれぞれを供給するA-D変 換器を変更するためのサンプリングクロック切換回路268の一例を示す説明図である。 この切換回路は、本実施例においてはサンプリングクロック選択回路266内部に設けら れており、2つのスイッチ268a,bを備えている。2つのスイッチ268a,bを同 時に切り替えることにより、サンプリングクロック信号SAD2、SAD3のそれぞれを A - D 変換器 7 2 、 7 3 のどちらにも供給することができる。なお、この場合には、 4 つ のラッチクロック信号SLC1~SLC4のそれぞれを供給するラッチを変更するラッチ クロック切換回路も必要であるが、サンプリングクロック切換回路268と同様であるた め図示は省略する。本実施例のサンプリングクロック切換回路268が本発明の第1の切 換回路に相当し、ラッチクロック切換回路が本発明の第2の切換回路に相当する。なお、 A - D変換器 7 1 ~ 7 4 に供給されているスリープ信号 S L P 1 については後述する。 図14は、サンプリングクロック信号SAD1~SAD4のそれぞれを供給するA-D変 換器を変更した場合のデジタル画像信号D1~D4の出力を示すタイミングチャートであ る。図14(a)~(c)は、水平同期信号HSYNC1と、書込サンプリングクロック 信号Swと、ドットクロック信号DCLK1の波形を示している。図14(d)~(g) に示す波形は、サンプリングクロック信号SAD1~SAD4のそれぞれが、A-D変換 器71、73、72、74に変更して供給されている場合を示している。また、図14( 1)~(o)に示すように、ラッチクロック信号SLC1~SLC4についてもサンプリ ングクロック信号SAD1~SAD4と同様に供給先のラッチが変更されている。このよ うにサンプリングクロック信号の供給先のA-D変換器を変更する際には、上記の2つの 切換回路は、対応するA-D変換器とラッチ(例えば、A-D変換器71とラッチ81) に供給するサンプリングクロック信号とラッチクロック信号との関係が一定の位相関係と なるように設定される。このように変更した場合には、順次位相の異なるデジタル画像信 号D1~D4が図14(p)~(s)に示すように出力される。こうすれば、デジタル画 像信号D1~D4を受け取る側の仕様に応じて出力することが可能となる。

図 1 3 に示すスリープ信号 S L P 1 は、 4 個の A - D 変換器 7 1 ~ 7 4 のうちのいくつかを休止させるために用いられる。例えば、 4 個の A - D 変換器 7 1 ~ 7 4 のうち 2 個の A - D 変換器を休止させる場合には、 2 個の A - D 変換器にスリープ信号 S L P 1 が供給される。

図 1 5 は、 4 個の A - D 変換器 7 1 ~ 7 4 のうち 2 個の A - D 変換器を休止させた場合の タイミングチャートである。このタイミングチャートは、図13のスイッチ268a,b によりサンプリングクロック信号SAD2がA-D変換器73に供給されている場合を示 している。書込サンプリングクロック信号Swおよびドットクロック信号DCLK1は、 第 1 実施例において説明したように 2 つの P L L 回路 6 2 , 6 4 (図 9 )の N 0 , N w の 値を変更することによって調整されている。図15(a)~(c)は、水平同期信号HS YNC1と、書込サンプリングクロック信号Swと、ドットクロック信号DCLK1の波 形を示している。図10に示すサンプリングクロック選択回路266において、サンプリ ングクロック信号Swとドットクロック信号DCLK1とから互いに180度位相の異な る2つのサンプリングクロック信号SAD1,SAD2が生成され、A-D変換器71, 7 3 に供給される。図 1 5 ( d ) , ( f )は、サンプリングクロック信号 S A D 1 , S A D2の波形を示している。このとき、サンプリングクロック選択回路266においては、 サンプリングクロック信号SAD1、SAD2のそれぞれと同位相になる不要な信号SA D3、SAD4(図15(e),(g))が生成され、A-D変換器72,74に供給さ れる。しかし、A-D変換器72,74にはスリープ信号SLP1が供給されているため 変換処理は行われない(図15(i), (k))。なお、不要な信号SAD3,SAD4 については、サンプリングクロック選択回路266(図9)内で処理してもよく、この場 合にはスリープ信号SLP1をサンプリングクロック選択回路266に供給すればよい。

30

40

50

図15(d),(f)に示す2つのサンプリングクロック信号SAD1,SAD2の位相関係は、4個のA-D変換器を動作させた場合の図12(d),(f)のサンプリングクロック信号SAD1,SAD3の位相関係と同じであり、180度位相が異なっている。このようにスイッチ268a,bを切り替えれば、A-D変換器の使用個数が変わった場合にも、サンプリングクロック信号SAD1に対し180度位相の異なるサンプリングクロック信号を常にA-D変換器73に供給することが可能である。

サンプリングクロック信号 S A D 1 , S A D 2 と同様に、ラッチクロック信号 S L C 1 , S L C 2 (図 1 5 (1), (m))をラッチ 8 1 , 8 3 に供給すれば、デジタル画像信号 D 1 , D 2 (図 1 5 (p), (r))を図 1 2 (p), (r)と同じ位相関係で出力できる。この場合にも、デジタル画像信号 D 1 ~ D 4 を受け取る側の仕様に応じて出力することが可能となる。

A - D変換器 2 2 4 (図9) から出力されるデジタル画像信号 D 1 ~ D 4 は、前述のように順次位相の異なる信号となっている。この 4 つのデジタル画像信号 D 1 ~ D 4 は、図 8 に示すビデオプロセッサ 2 2 8 に取り込まれる。

図16は、ビデオプロセッサ228内部のインタフェース部分に備えられたデジタル画像信号位相調整回路群を示すブロック図である。複数段のデジタル画像信号位相調整回路で構成されたデジタル画像信号位相調整回路群は、各段に含まれる回路数が最終段に向けて次第に減少する階層構造を有している。最終段以外の各段に含まれる複数のデジタル画像信号位相調整回路のそれぞれは、入力された複数のデジタル画像信号を当該段の他のデジタル画像信号位相調整回路とは異なる一定の位相で保持して次段のデジタル画像信号位相調整回路は、前段から供給されたNw個のデジタル画像信号を同じ位相で保持する機能を有している。

各段のデジタル画像信号位相調整回路はラッチで構成されている。各ラッチには、図9のサンプリングクロック選択回路266で生成されたラッチクロック信号SLC1~SLC4のいずれかが入力されている。

第1段目の4つのラッチ230a~230dは、A-D変換部224から出力された順次位相の異なるデジタル画像信号D1~D4をビデオプロセッサ228内部に取り込むためのラッチである。第2段目の2つのラッチ232a,232bは、第1段目の4つのラッチから出力された順次位相の異なる4つのデジタル画像信号D1~D4を1つおきに2つずつまとめて、それぞれ出力するためのラッチである。第3段目のラッチ234は、第2段目の2つのラッチ232a,232bでそれぞれまとめられた位相の異なる2組のデジタル画像信号をさらに1つにまとめて、同位相のデジタル画像信号Dcomとして出力するための回路である。

図 1 7 は、図 1 6 のデジタル画像信号位相調整回路群を用いた場合のデジタル画像信号 D 1 ~ D 4 のタイミングチャートである。図 1 7 (a) ~ (d) は、図 1 2 ,図 1 4 に示す A - D 変換部 2 2 4 から出力された順次位相の異なる 4 つのデジタル画像信号 D 1 ~ D 4 を示している。図 1 7 (e) ~ (h) は、ビデオプロセッサ 2 2 8 に入力されるラッチクロック信号 S L C 1 ~ S L C 4 の波形を示している。

図16の第1段目のラッチ230a~230dには、それぞれデジタル画像信号D1、D3、D2、D4が入力されている。ラッチ230aは、デジタル画像信号D1を、ラッチクロック信号SLC3でサンプリングして、デジタル画像信号D1と180度位相が異なるデジタル画像信号LD1を出力する。同様にして、ラッチ230b~230dからはそれぞれラッチクロック信号SLC1、SLC4、SLC2に従いデジタル画像信号LD3、LD2、LD4が出力される。図17(i)~(1)は、ラッチ230a~dから出力されるデジタル画像信号LD1、LD3、LD2、LD4を示している。

第2段目のラッチ232 aには、順次位相の異なる4つのデジタル画像信号 L D 1 ~ L D 4のうち1つおきのデジタル画像信号 L D 1 と L D 3 とが入力されている。ラッチ232 a は、デジタル画像信号 L D 1、L D 3 をラッチクロック信号 S L C 2 の立ち上がリエッジでサンプリングして、デジタル画像信号 L D 1、L D 3 のデータを含むデジタル画像信号 L D 5 を出力する。同様に、ラッチ232 b はデジタル画像信号 L D 2、L D 4 をラッ

30

40

50

チクロック信号SLC3でサンプリングして、デジタル画像信号LD2、LD4のデータを含むデジタル画像信号LD6を出力する。図17(m),(n)は、ラッチ232a, bから出力されるデジタル画像信号LD5、LD6を示している。

第3段目のラッチ234には、位相の異なる2つのデジタル画像信号LD5,LD6が入力されている。ラッチ234は、デジタル画像信号LD5、LD6をラッチクロック信号SLC4でサンプリングして、デジタル画像信号LD1~LD4のデータを含むデジタル画像信号Dcom(図17(o))を出力する。このように、複数段のラッチを用いることによりデジタル画像信号D1~D4を同位相のデジタル画像信号Dcomとして出力することができる。

このように、複数段のラッチを用いて、順次位相の異なるいくつかおきの信号をまとめな がら同位相の信号としてゆけば、安定したサンプリングを実現することが可能となる。す なわち、この場合には、各ラッチにおいて、まとめる対象となる各デジタル画像信号のデ ータ変化点とまとめるためのサンプリング点(ラッチクロック信号の立ち上がリエッジ) との間隔を比較的大きく確保することができるため、各デジタル画像信号のデータ変化点 でサンプリングしてしまう可能性を低減できる。例えば、図17に示すように4つの順次 位相の異なるデジタル画像信号D1~D4(図17(a)~(d))が入力されている場 合には、ラッチクロック信号SLC4から90度位相を遅らせた信号SLC4^(図17 (p))により一度にすべての信号 D1 ~ D4 をサンプリングして、同位相として出力す ることも可能である。しかし、この場合にはサンプリング点(ラッチクロック信号SLC 4 'の立ち上がリエッジ)とデジタル画像信号 D 1 および D 4 のデータ変化点との間隔が それぞれ1周期の1/8と小さくなってしまう。これに対し、図16に示すような複数段 のラッチを用いて順次位相の異なる信号を1つおきにサンプリングする場合には、例えば 、デジタル画像信号LD1、LD3(図17(i),(j))をラッチクロック信号SL C2でサンプリングする場合には、サンプリング点(ラッチクロック信号SLC2の立ち 上がリエッジ)と2つの信号LD1、LD3の変化点との間隔を各信号の1周期の1/4 と比較的大きくすることができる。

また、本実施例においては、上述のようにラッチクロック信号SLC1~SLC4をA-D変換部224に供給するとともにビデオプロセッサ228にも供給しているので、A-D変換部224から出力されるデジタル画像信号D1~D4に適したタイミングでサンプリングすることが可能となっている。このようにすれば、動作温度によって各クロック信号の遅延等にバラツキが生じる場合にも、バラツキによる誤動作を回避することができる

なお、このデジタル画像信号位相調整回路は、本実施例においてはビデオプロセッサ228内部に設けられているが、A-D変換部224内部に設けてもよい。この場合には、デジタル画像信号D1~D4を同位相のデジタル画像信号DcomとしてA-D変換部224から出力することができるので、ビデオプロセッサ228にラッチクロック信号SLC1~SLC4のすべてを供給しなくて済むという利点がある。この場合にも、ビデオプロセッサ228内でデジタル画像信号Dcomをサンプリングするためにラッチクロック信号SLC1~SLC4の少なくとも1個を供給することが好ましい。

このようにビデオプロセッサ 2 2 8 内部に取り込まれたデジタル画像信号 D comは、第 1 実施例で説明したようにフレームメモリ 2 6 に格納される。

上記第1~第3実施例においては、水平同期信号HSYNC1から生成されるドットクロック信号DCLK1を利用してアナログ画像信号AV1の各画素をサンプリングするのに適したクロック信号を生成している。しかし、ドットクロック信号DCLK1は比較的周波数が高く、プリント基板上に形成された配線を伝送させる場合には、無視できない波形の乱れや遅延等が生じる場合がある。したがって、ドットクロック信号DCLK1は、集積化された1チップ内部で生成および利用して、チップの外部に出力しないことが好ましい。

第3実施例においては、サンプリングクロック生成部222とA-D変換部224とが1チップに集積化されている場合を想定しているので上記の問題を回避できる。なお、サン

30

40

50

プリングクロック生成部 2 2 2 と A - D 変換部 2 2 4 との全てを 1 チップ化しない場合でも、ドットクロック信号 D C L K 1 をチップの外部に出力しなくて済むように、少なくとも P L L 回路 6 4 とサンプリングクロック選択回路 2 6 6 とは 1 チップ内に集積化されていることが好ましい。

フレームメモリ 2 6 に格納されたデジタル画像信号は、ビデオプロセッサ 2 2 8 によって読み出され、D - A 変換されたのちアナログ画像信号 A V 2 として出力される。この動作は、A - D 変換の動作と逆であり、類似しているので、その詳細な説明は省略する。

本実施例において説明した書込サンプリングクロック生成部 2 2 2 の内部構成は、読出サンプリングクロック生成部 2 3 0 にも同様に適用可能である。

また、図8に示すように、D-A変換に使用されるサンプリングクロック信号SDA1~SDA4は、読出サンプリングクロック生成部230において生成され、D-A変換部332に入力されるとともにビデオプロセッサ228にも入力されている。したがって、ラッチクロック信号SLC1~SLC4がビデオプロセッサ228に入力されている場合と同様に、ビデオプロセッサから出力されるNr個のデジタル画像信号に適したタイミングでD-A変換することが可能となる。

D - A 変換部 3 3 2 で D - A 変換された部分アナログ画像信号は、ビデオスイッチ 3 4 で順次切り換えられて、1 つのアナログ画像信号 A V 2 に合成される。本実施例においては、図 8 に示すようにビデオスイッチ 3 4 にはドットクロック信号 D C L K 2 に代えて、サンプリングクロック信号 S D A 1 ~ S D A 4 が供給されている。この場合には、ビデオスイッチ 3 4 は、各クロック信号毎に位相が順次ずれていることを利用して切換動作を行えばよい。

D - A 変換する場合にも、 A - D 変換する場合と同様に、サンプリングクロック生成部 2 3 0 と D - A 変換部 3 3 2 とが 1 チップに集積化されていることが好ましい。また、ビデオスイッチ 3 4 をドットクロック信号 D C L K 2 で動作させる場合には、ビデオスイッチ 3 4 も一緒に集積化することが好ましい。なお、図 8 では、比較的周波数の高いドットクロック信号 D C L K 2 を読出サンプリングクロック生成部 2 3 0 の外部に出力しなくて済むため、集積化しなくてもビデオスイッチ 3 4 において安定した切換動作を実現することができる。

# D.第4実施例:

図18は、第4実施例における書込サンプリングクロック生成部322とA-D変換部324の内部構成を示すブロック図である。なお、画像処理装置の全体構成は第3実施例の図8に示す構成とほぼ同じである。本実施例においては、図9に示すPLL回路64およびサンプリングクロック選択回路266に代えて遅延クロック生成回路366が用いられている。したがって、本実施例のPLL回路62が本発明における第1の原サンプリングクロック生成回路に相当し、遅延クロック生成回路366が第1のサンプリングクロック生成回路に相当する。図19は、遅延クロック生成回路366の内部構成を示すブロック図である。遅延クロック生成回路は、位相比較器367と、4つの遅延回路368a~368dを備えている。遅延回路368a~368dのそれぞれは、内部に図示しないUp/Downカウンタと遅延調整回路とを備えている。遅延調整回路としては、例えば、複数個の遅延調整用バッファを直列に配置したものを用いることができる。

遅延回路368a~368dの内部に備えられたUp/Downカウンタは、位相比較器367から出力されたUp/Down信号に応じてカウンタの出力値を変化させる。カウンタの出力値は、遅延調整回路による遅延量の調整に用いられる。例えば、Up信号によりカウンタ出力値が大きくなった場合には、遅延調整用バッファの使用個数を増加させて遅延量を大きくし、Down信号によりカウンタ出力値が小さくなった場合には、遅延調整用バッファの使用個数を減少させて遅延量を小さくする。このようにして、4つの遅延

30

40

50

回路368a~368dにおける遅延量が調整される。

なお、図19においては、書込サンプリングクロック信号 S w をそのままサンプリングクロック信号 S A D 1 として利用しているが、4つの遅延回路 3 6 8 a ~ 3 6 8 d から出力される信号をサンプリングクロック信号 S A D 1 ~ S A D 4 として用いてもよい。

また、本実施例においては、Up/Downカウンタは遅延回路368a~368dのそれぞれに設けられているが、位相比較器367の内部に設けてもよい。この場合には、Up/Downカウンタが1つで済むという利点がある。

このように生成されたサンプリングクロック信号SAD1~SAD4およびラッチクロック信号SLC1~SLC4を用いても、第3実施例と同様の処理を行うことができる。本実施例においては、第1~第3実施例と異なり、周波数の高いドットクロック信号DCLK1を生成しなくてもよいため、回路の消費電力を比較的小さくすることができる。また、周波数の高いドットクロック信号DCLK1をプリント基板上の配線を介して伝送する場合の問題(例えば、波形の乱れや遅延)を回避できるため、各回路を実装するためのプリント基板設計が容易となる。

なお、本実施例においては、書込サンプリングクロック生成部322の内部構成について 説明したが、上記の構成は読出サンプリングクロック生成部230においても同様に適用 できる。

# E . 第 5 実施例:

図20は、第5実施例における書込サンプリングクロック生成部422とA-D変換部424の内部構成を示すブロック図である。なお、画像処理装置の全体構成は図8に示す構成とほぼ同じである。本実施例においては、図9に示すPLL回路62に代えて、90度位相の異なる2つの書込サンプリングクロック信号Sw1,Sw2を生成する位相差信号生成回路462が用いられている。また、PLL回路64とサンプリングクロック選択回路266の代わりにサンプリングクロック反転回路466が用いられている。したがって、本実施例においては、位相差信号生成回路466がありる第1の原サンプリングクロック生成回路に相当し、サンプリングクロック反転回路466が第1のサンプリングクロック生成回路に相当する。

位相差信号生成回路 4 6 2 は、内部に P L L 回路を備えており、水平同期信号 H S Y N C 1 から書込サンプリングクロック信号 S w 1 を出力するとともに、書込サンプリングクロック信号 S w 2 を出力することができる。この位相差信号生成回路 4 6 2 としては、例えば、 I C S 社の I C S 1 5 2 2 を用いることができる。

サンプリングクロック反転回路466は、入力された書込サンプリングクロック信号Sw1,Sw2からサンプリングクロック信号SAD1~SAD4を生成する。サンプリングクロック反転回路466に入力される信号は90度位相のずれた信号であるため、反転回路466内部で2つの信号Sw1,Sw2を反転させた信号を生成すれば、90度ずつ位相の異なる4つのサンプリングクロック信号SAD1~SAD4を容易に生成することができる。なお、4つのサンプリングクロック信号SAD1~SAD4は、本実施例においてもラッチクロック信号SLC1~SLC4として用いることができる。

この回路構成を用いる場合には、周波数の高いドットクロック信号は、1チップ化された

30

40

位相差信号生成回路462の内部で生成および利用されており、チップの外部に出力されない。したがって、本実施例の位相差信号生成回路462を用いた場合にも、第4実施例と同様にプリント基板設計を容易に行うことが可能となる。

本実施例においては、書込サンプリングクロック生成部 4 2 4 の内部構成について説明したが、上記の構成は読出サンプリングクロック生成部 2 3 0 においても同様に適用できる

なお、この発明は上記の実施例や実施形態に限られるものではなく、その要旨を逸脱しない範囲において種々の態様において実施することが可能であり、例えば次のような変形も可能である。

第1ないし第3実施例における書込サンプリングクロック生成部22、112、222(図2,図6,図9)では、水平同期信号HSYNC1を第1のPLL回路62でN0倍に 逓倍することによって、書込サンプリングクロック信号Swを生成しているが、この代わりに、ドットクロック信号DCLK1を1/Nw(NwはA-D変換器の使用個数)に分周することによって書込サンプリングクロック信号Swを生成してもよい。この場合には、水平同期信号HSYNC1を1つのPLL回路で逓倍することによって、ドットクロック信号DCLK1を生成することができる。換言すれば、書込サンプリングクロック信号Swを生成するための回路としては、PLL回路や分周器などの種々の回路構成を採用することができる。

上述の変形は、第 1 ないし第 3 実施例における読出サンプリングクロック生成部 3 0 (図4,図7)における読出サンプリングクロック信号 S r とドットクロック信号 D C L K 2 の生成に係わる回路に関しても適用可能である。

上記第1ないし第3実施例において、PLL回路64(図2,図6,図9)は、アナログ画像信号AV1の全画素をサンプリングするのに適したドットクロック信号DCLK1を生成するが、ドットクロック信号DCLK1は全画素のサンプリングに適した周波数以外の周波数を有していてもよい。例えば、画素を1/2に間引くのに適したドットクロック信号DCLK1を生成してもよい。すなわち、ドットクロック信号DCLK1は、アナログ画像信号AV1の画素を、サンプリングするための周波数を有するクロック信号であればよい。これは、読出サンプリングクロック生成部30(図4,図7)におけるドットクロック信号DCLK2についても同様である。

また、上記第1ないし第5実施例の画像処理装置においては、アナログ画像信号の入力からフレームメモリ26(図1,図5,図8)へのデジタル画像信号の書き込みまで(A-D側)と、フレームメモリ26に書き込まれたデジタル画像信号の読み出しからアナログ画像信号までの出力まで(D-A側)との双方に本発明の構成を用いているが、どちらか一方についてのみ本発明の構成を用いてもよい。例えば、A-D側の画像信号の周波数が高く、D-A側の画像信号の周波数が低い場合には、A-D側にのみ本発明の構成を用いて、D-A側については本発明の構成を用いなくてもよい。

上記実施例において、ハードウェアによって実現されていた構成の一部をソフトウェアに置き換えるようにしてもよく、逆に、ソフトウェアによって実現されていた構成の一部を ハードウェアに置き換えるようにしてもよい。

#### 産業上の利用可能性

この発明は、A - D変換やD - A変換の機能を有する種々の画像処理装置に適用可能であり、例えば、液晶プロジェクタなどの投射型表示装置に適用できる。また、液晶パネルを用いた画像表示装置に限らず、CRTやプラズマディスプレイパネル等の表示手段を用いた画像表示装置や、それらを含む種々の電子機器に適用できる。

# フロントページの続き

(56)参考文献 特開昭60-160222(JP,A)

特開平07-231417(JP,A)

特開平09-023448(JP,A)

特開平02-067883(JP,A)

(58)調査した分野(Int.CI., DB名)

H04N 5/14