### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4841204号 (P4841204)

(45) 発行日 平成23年12月21日(2011, 12, 21)

(24) 登録日 平成23年10月14日(2011.10.14)

(56) 参考文献 特開平5-198742 (JP. A)

| (51) Int.Cl. |                                     | F I          |                     |                  |          |        |  |

|--------------|-------------------------------------|--------------|---------------------|------------------|----------|--------|--|

| HO1L 27/04   | (2006.01)                           | HO1L         | 27/04               | A                |          |        |  |

| HO1L 21/822  | (2006.01)                           | HO1L         | 27/06               | 1 O 2 A          |          |        |  |

| HO1L 27/06   | (2006.01)                           | HO1L         | 27/08               | 321A             |          |        |  |

| HO1L 21/823  | 4 (2006.01)                         | HO1L         | 21/82               | M                |          |        |  |

| HO1L 21/823  | 8 (2006.01)                         | HO1L         | 27/04               | D                |          |        |  |

|              |                                     |              |                     | 請求項の数 6          | (全 14 頁) | 最終頁に続く |  |

| (21) 出願番号    | 特願2005-252002 (F                    | 2005-252002) | (73) 特許権            | 者 302062931      |          |        |  |

| (22) 出願日     | 平成17年8月31日 (2005.8.31)              |              |                     | ルネサスエレクトロニクス株式会社 |          |        |  |

| (65) 公開番号    | 5) 公開番号 特開2007-67207 (P2007-67207A) |              | 神奈川県川崎市中原区下沼部1753番地 |                  |          |        |  |

| (43) 公開日     | 平成19年3月15日(2                        | 2007. 3. 15) | (74) 代理人            | . 100102864      |          |        |  |

| 審査請求日        | 平成20年6月13日(2                        | 2008. 6. 13) |                     | 弁理士 工藤           | 実        |        |  |

|              |                                     |              | (72) 発明者            | 青木 泰             |          |        |  |

|              |                                     |              | 神奈川県川崎市中原区下沼部1753番地 |                  |          |        |  |

|              |                                     |              |                     | NECエレク           | フトロニクス構  | k式会社内  |  |

|              |                                     |              | 審査官                 | 田代 吉成            |          |        |  |

最終頁に続く

## (54) 【発明の名称】半導体装置

#### (57)【特許請求の範囲】

## 【請求項1】

複数のСМОS基本セルが並べられた、СМОS基本セル列と、

前記CMOS基本セル列に並設され、前記CMOS基本セル列に接続された第1の電源配線と、

前記CMOS基本セル列に並設され、前記CMOS基本セル列に接続された第1の接地配線と、

前記第1の電源配線の直下に設けられた第1のデカップリング容量と、前記第1の接地 配線の直下に設けられた第2のデカップリング容量とを備え、

前記第1のデカップリング容量は、ゲート電極が前記第1の接地配線に接続され、ソース・ドレイン拡散層が前記第1の電源配線に接続されたPチャネル型MOSトランジスタによって形成され、

前記第2のデカップリング容量は、ゲート電極が前記第1の電源配線に接続され、ソース・ドレイン拡散層が前記第1の接地配線に接続されたNチャネル型MOSトランジスタによって形成された、

前記第1のデカップリング容量を構成する、前記Pチャネル型MOSトランジスタのソース・ドレイン拡散層の一方は、前記第1の電源配線に接続され、他方は開放され、

前記第2のデカップリング容量を構成する、前記Nチャネル型MOSトランジスタのソ ース・ドレイン拡散層の一方は、前記第1の接地配線に接続され、他方は開放されている 半導体装置。

20

### 【請求項2】

請求項1に記載の半導体装置において、

前記CMOS基本セル列の端のCMOS基本セルを構成するPチャネル型MOSトラン ジスタに隣接して設けられた第3のデカップリング容量と、

前記CMOS基本セル列の端のCMOS基本セルを構成するNチャネル型MOSトラン ジスタに隣接して設けられた第4のデカップリング容量とを更に具備し、

前記第3のデカップリング容量は、ゲート電極が前記第1の接地配線に接続され、ソー ス・ドレイン拡散層が前記第1の電源配線に接続されるPチャネル型MOSトランジスタ によって形成され、

前記第4のデカップリング容量は、ゲート電極が前記第1の電源配線に接続され、ソー ス・ドレイン拡散層が前記第1の接地配線に接続されるNチャネル型MOSトランジスタ によって形成される

半導体装置。

## 【請求項3】

請求項1又は2に記載の半導体装置において、

前記第1の電源配線の直下に設けられ、N型基板を前記第1の電源配線に接続して前記 N型基板の電位を固定するN型拡散層と、

前記第1の接地配線の直下に設けられ、P型基板を前記第1の接地配線に接続して前記 P型基板の電位を固定する P型拡散層とを更に備える

半導体装置。

#### 【請求項4】

請求項1又は2に記載の半導体装置において、

前記第1の電源配線に並設され、N型基板の電位を固定する第2の電源配線と、

前記第1の接地配線に並設され、P型基板の電位を固定する第2の接地配線とを更に備 える

半導体装置。

#### 【請求項5】

請求項4に記載の半導体装置において、

前記第1の電源配線は、前記CMOS基本セル列に隣接して設けられ、前記第2の電源 配線は、前記第1の電源配線に隣接して設けられており、

前記第1の接地配線は、前記CMOS基本セル列に隣接して設けられ、前記第2の接地 配線は、前記第1の接地配線に隣接して設けられている

半導体装置。

## 【請求項6】

請求項4に記載の半導体装置において、

前記第2の電源配線は、前記CMOS基本セル列に隣接して設けられ、前記第1の電源 配線は、前記第2の電源配線に隣接して設けられており、

前記第2の接地配線は、前記CMOS基本セル列に隣接して設けられ、前記第1の接地 配線は、前記第2の接地配線に隣接して設けられている

半導体装置。

【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は、半導体装置に関し、特に、CMOS(Complementary Oxide Semiconductor)基本セルを備える半導体装置に関する

## 【背景技術】

### [0002]

CMOS基本セルを複数用いたLSI(Large Scale Integrati on)、特に電源ノイズに敏感なアナログ回路とデジタル回路を混載したLSI等におい

10

20

30

40

て、電源ノイズによる誤動作や動作速度の低下を抑制することすることが求められている。このため、基本セル数個毎にデカップリング容量を配置して耐電源ノイズ特性を向上させてきた。

### [0003]

特開平02-241061号公報に電源電位と接地電位間にノイズ吸収用のバイパスコンデンサ(デカップリング容量)を備えたCMOSゲートアレイが開示されている(特許文献1参照)。特許文献1には、Pチャネル型MOSトランジスタ及びNチャネル型MOSトランジスタからなる基本セルを複数配列してなるCMOSゲートアレイにおいて、未使用の基本セルのPチャネル型MOSトランジスタ及びNチャネル型MOSトランジスタのうち、Pチャネル型MOSトランジスタのソース及びドレインを電源電位配線に接続するとともにゲートを接地電位配線に接続し、Nチャネル型MOSトランジスタのソース及びドレインを接地電位配線に接続するとともに、ゲートを電源電位配線に接続してデカップリング容量を構成するCMOSゲートアレイが記載されている。

#### [0004]

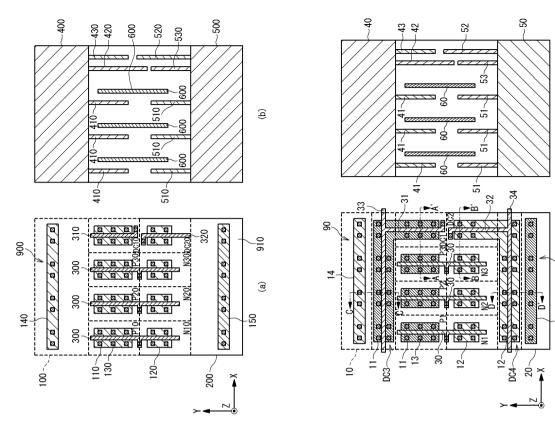

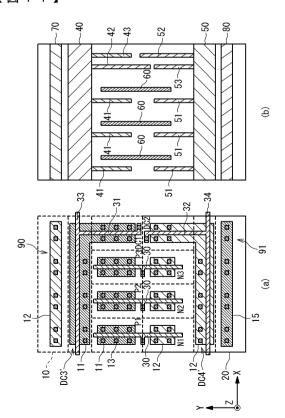

図1は、特許文献1に記載のデカップリング容量を備える基本セルのレイアウトの一例である。図1(a)は、下層から、素子の基板となるウェル層、拡散層、ポリシリコン層、コンタクト層の順で構成される素子部のレイアウト図である。図1(b)は、図1(a)に示される素子部の Z 軸方向上部に配されるメタル配線層で構成される配線部のレイアウト図である。

## [0005]

図1(a)を参照して、従来例によるデカップリング容量を備える基本セルの素子部の構成は、複数のCMOS基本セルとしてインバータセルを備えた回路領域と、未使用のCMOSインバータセルを利用したデカップリング容量セルと、基本セル内におけるトランジスタの基板電位を安定化するTap領域900、910とを具備する。図1(b)を参照して、配線部の構成は、X軸方向に延設され、電源VDDに接続される電源配線400と、X軸方向に延設され、グランドGNDに接続される接地配線500とを具備する。回路領域内及びデカップリング容量内の各トランジスタは、コンタクトホール13を介して電源電位VDDの電源配線400に接続される。又、回路領域内及びデカップリング容量内の各トランジスタは、コンタクトホール13を介して接地電位GNDの接地配線500に接続される。

#### [0006]

てMOSインバータセルは、共通のゲート電極300を有し、接続配線600を介して相互に接続されたPチャネル型MOSトランジスタ群P10、P20、P30とNチャネル型MOSトランジスタ群N10、N20、N30とから構成される。又、Pチャネル型MOSトランジスタ群P10、P20、P30は、N型ウェル100上に設けられたP型拡散層110とゲート電極300とから形成される。Nチャネル型MOSトランジスタ群N10、N20、N30は、P型ウェル200上に設けられたN型拡散層120とゲート電極300とから形成される。ここで、Pチャネル型MOSトランジスタ群P10、P20、P30の各ソースはコンタクトホール130及び配線410を介して電源配線400に接続され、Nチャネル型MOSトランジスタ群N10、N20、N30の各ソースはコンタクトホール130及び配線510を介して接地配線500に接続される。

## [0007]

Tap領域900は電源VDDに接続される電源配線400のZ軸方向直下の領域に設けられる。Tap領域900はPチャネル型MOSトランジスタ群P10、P20、P30の基板となるN型ウェル100を電源VDDに接続するためのN型拡散層140及びコンタクトホール130を備える。Tap領域900によって電源VDDとN型ウェル100は接続され、N型ウェル100の電位を安定化することができる。又、Tap領域910はグランドGNDに接続される接地配線500のZ軸方向直下の領域に設けられる。Tap領域910は、Nチャネル型MOSトランジスタ群N10、N20、N30の基板となるP型ウェル200をグランドGNDに接続するためのP型拡散層150及びコンタク

10

20

30

40

トホール 1 3 0 を備える。 T a p 領域 9 1 0 によってグランド G N D と P 型ウェル 2 0 0 は接続され、 P 型ウェル 2 0 0 の電位を安定化することができる。

#### [0008]

従来技術によるデカップリング容量セルは、基本セルにおいて回路領域として利用されないCMOSインバータセルによって構成される。デカップリング容量セルは、配線520を介して接地配線500に接続されたゲート電極310を有するPチャネル型MOSトランジスタDC10と、配線420を介して電源配線400に接続されたゲート電極320を有するNチャネル型MOSトランジスタDC20とを備える。ここで、Pチャネル型MOSトランジスタDC20とを備える。ここで、Pチャネル型MOSトランジスタDC20のソース・ドレイン拡散層は、コンタクトホール130及び配線420、430を介して電源配線400に接続され、Nチャネル型MOSトランジスタDC20のゲート容量、及びNチャネル型MOSトランジスタDC10のゲート容量、及びNチャネル型MOSトランジスタDC20のゲート容量によってデカップリング容量を構成し、回路領域に接続される電源VDD及びグランドGNDの電源ノイズを抑制することができる。

[0009]

【特許文献1】特開平02-241061号公報

【発明の開示】

【発明が解決しようとする課題】

[0010]

従来技術によるLSIでは、上述のデカップリング容量セルを有した基本セルが、基本セル数個に1個の割合で配置される。従来技術による基本セルは回路領域として使用しないトランジスタのゲート容量をデカップリング容量として利用している。又、電源ノイズの抑制量を増大させるためには、ゲート面積を増大させる必要がある。このため、従来技術によるLSIでは、電源ノイズを所望の値まで抑制する場合、LSI内に配置するデカップリング容量セルの割合(数)を多くしなければならず、チップ面積が増大してしまうという問題があった。

【課題を解決するための手段】

[0011]

以下に、 [発明を実施するための最良の形態]で使用される番号・符号を括弧付きで用いて、 [課題を解決するための手段]を説明する。この番号・符号は、 [特許請求の範囲]の記載と [発明を実施するための最良の形態]の記載との対応関係を明らかにするために付加されたものであるが、 [特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

[0012]

以上のような課題を解決するため、本発明による半導体装置は、複数のCMOS基本セルが並べられた、CMOS基本セル列と、CMOS基本セル列に並設され、CMOS基本セル列に接続された第1の電源配線(40)と、CMOS基本セル列に並設され、CMOS基本セル列に接続された第1の接地配線(50)と、第1の電源配線の直下に設けられた第1のデカップリング容量(DC3、DC3')と、前記第1の接地配線の直下に設けられた第2のデカップリング容量(DC4、DC4')とを備え、第1のデカップリング容量(DC3、DC3')とで備え、第1のデカップリング容量(DC3、DC3')は、ゲート電極が前記第1の接地配線に接続され、ソース・ドレイン拡散層が前記第1の接地配線に接続されたNチャネル型MOSトランジスタによって形成されている。

【発明の効果】

[0013]

本発明による半導体装置によれば、電流容量を確保するために一定の幅が必要な、電源配線と接地配線の直下のスペースを利用して、デカップリング容量を設けることにより、

10

20

40

30

小さいチップ面積を維持しながら電源ノイズを抑制することができる。

#### [0014]

又、電源ノイズによる誤動作及び動作速度の低下を抑制することができる。

【発明を実施するための最良の形態】

#### [0015]

以下、添付図面を参照して、本発明による半導体装置の実施の形態が説明される。本実施の形態では、CMOS基本セルとしてCMOSインバータを複数備えたLSIにおいて、デカップリング容量が設けられたセルについて説明される。以下では、同一及び相当部分には同一符号を付して説明される。

#### [0016]

(第1の実施の形態)

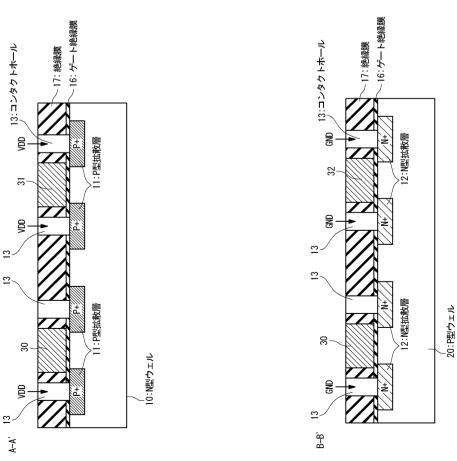

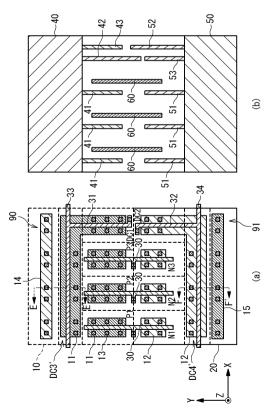

図2から図7を参照して、本発明による半導体装置の第1の実施の形態が説明される。

図2は、本発明による半導体装置の第1の実施の形態におけるレイアウト図である。

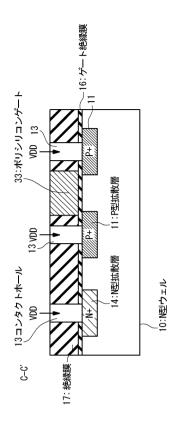

図3は、回路領域においてCMOSインバータを形成するPチャネル型MOSトランジスタと、デカップリング容量セルを形成するPチャネル型MOSトランジスタDC1の断面構造図である。

図4は、回路領域においてCMOSインバータを形成するNチャネル型MOSトランジスタと、デカップリング容量セルを形成するNチャネル型MOSトランジスタDC2の断面構造図である。

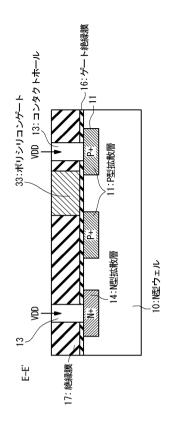

図5は、デカップリング容量を形成するPチャネル型MOSトランジスタDC3と、Tap領域90の断面構造図である。

図6は、デカップリング容量を形成するNチャネル型MOSトランジスタDC4と、Tap領域91の断面構造図である。

#### [0017]

図 2 (a)は、下層から、素子の基板となるウェル層、拡散層、ポリシリコン層、コンタクト層の順で構成される素子部のレイアウト図である。図 2 (b)は、図 2 (a)に示される素子部の Z 軸方向上部に配されるメタル配線層で構成される配線部のレイアウト図である。

### [0018]

図2(a)を参照して、本発明による半導体装置の素子部の構成は、複数のCMOSインバータセルを備えるCMOS基本セル列からなる回路領域と、デカップリング容量と、基本セル列内におけるトランジスタの基板の電位を安定化するためのTap領域90、91とを具備する。図2(b)を参照して、配線部の構成は、X軸方向に延設され、電源VDDに接続される電源配線40と、X軸方向に延設され、グランドGNDに接続される接地配線50とを具備する。電源配線40は基本セル列のPチャネル型MOSトランジスタ側に並設され、接地配線50は基本セル列のNチャネル型トランジスタ側に並設されている。回路領域内及びデカップリング容量内の各トランジスタは、コンタクトホール13を介して電源電位VDDの電源配線に接続される。又、回路領域内及びデカップリング容量内の各トランジスタは、コンタクトホール13を介して接地電位GNDの接地配線に接続される。

## [0019]

CMOS基本セル列であるCMOSインバータセル列は、共通のゲート電極30を有し、接続配線60を介して相互に接続されたPチャネル型MOSトランジスタ群P1、P2、P3とNチャネル型MOSトランジスタ群N1、N2、N3とから構成される。図3は、図2(a)におけるA-A'線の断面構造図である。図2及び図3を参照して、Pチャネル型MOSトランジスタ群P3は、N型ウェル10上に設けられたP型拡散層11とゲート電極30とから形成される。ここで、Pチャネル型MOSトランジスタP3のP型拡散層11はコンタクトホール13及び配線41を介して電源配線40に接続され、電源電位VDDが入力される。図4は、図2(a)におけるB-B'線の断面構造図である。図2及び図4を参照して、Nチャネル型MOSトランジスタN3は、P型ウェル20上に設

10

20

30

40

20

30

40

50

けられたN型拡散層12とゲート電極30とから形成される。Nチャネル型MOSトランジスタN3のソースはコンタクトホール13及び配線51を介して接地配線50に接続され、接地電位GNDが入力される。又、コンタクトホール13及び接続配線60を介してPチャネル型トランジスタP3とNチャネル型MOSトランジスタN3とが接続される。CMOS基本セル列で構成された回路領域は、このような構成のCMOSインバータセルを複数備える。尚、本実施の形態では、3つのCMOSインバータセルを回路領域としたが、回路領域に含まれるCMOSインバータセルの数はこれに限定されない。

### [0020]

本発明による半導体装置に含まれるデカップリング容量は、基本セルのうちCMOSインバータセルとして使用しされないMOSトランジスタのゲート容量を利用したデカップリング容量セルと、電源配線40又は接地配線50のZ軸下方の領域に配置されたMOSトランジスタのゲート容量を利用したデカップリング容量領域とを備える。第1の実施の形態におけるデカップリング容量セルは回路領域に隣接して設けられ、デカップリング容量領域は、Tap領域90、91と回路領域との間に配されて、回路領域に隣接して設けられる。

#### [0021]

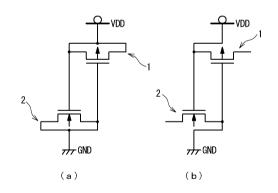

CMOSインバータセルとして使用されないMOSトランジスタを利用したデカップリ ング容量セルは、回路領域のPチャネル型MOSトランジスタP3に隣接するPチャネル 型MOSトランジスタDC1と、回路領域のNチャネル型MOSトランジスタN3に隣接 するNチャネル型MOSトランジスタDC2とを備える。図2及び図3を参照して、Pチ ャネル型MOSトランジスタDC1は、N型ウェル10上に設けられたP型拡散層11と ゲート電極31とから形成される。ゲート電極31は、コンタクトホール13及び配線5 2 を介して接地配線 5 0 に接続される。又、P型拡散層 1 1 はコンタクトホール 1 3 、配 線42及び配線43を介して電源配線40に接続される。このように、Pチャネル型MO SトランジスタDC1のソース・ドレイン拡散層に電源電圧VDDが印加され、ゲートに 接地電圧GNDが印加される。図2及び図3を参照して、Nチャネル型MOSトランジス タ D C 2 は、 P 型 ウェル 2 O 上に設けられた N 型拡散層 1 2 とゲート電極 3 2 とから形成 される。ゲート電極32は、コンタクトホール13及び配線42を介して電源配線40に 接続される。又、N型拡散層12はコンタクトホール13、配線52及び配線53を介し て接地配線50に接続される。このように、Nチャネル型MOSトランジスタDC2のソ -ス・ドレイン拡散層に接地電圧GNDが印加され、ゲートに電源電圧VDDが印加され る。このような構成により、図7(a)に示されるような、ソース・ドレイン拡散層が電 源VDDに接続され、ゲートがグランドGNDに接続されたPチャネル型MOSトランジ スタ1と、ソース・ドレイン拡散層がグランドGNDに接続され、ゲートが電源VDDに 接続されたNチャネル型トランジスタ2とを備えるMOSキャパシタが、デカップリング 容量セルに形成される。

## [0022]

以上のように、デカップリング容量セルにおけるPチャネル型MOSトランジスタDC1のゲート容量とNチャネル型MOSトランジスタDC2のゲート容量とによって、回路領域に接続される電源VDD及びグランドGNDの電源ノイズを抑制することができる。尚、Pチャネル型MOSトランジスタDC1及びNチャネル型MOSトランジスタDC2において、ソース・ドレイン拡散層の一方のみに、コンタクトホール13が設けられる形態であっても構わない。この場合、デカップリング容量セルに形成されるMOSキャパシタは、図7(b)に示されるように各MOSトランジスタのソース・ドレイン拡散層の一方が開放された回路構成となる。

## [0023]

デカップリング容量領域は、電源配線40のZ軸方向直下の領域に設けられたPチャネル型MOSトランジスタDC3と、接地配線50のZ軸方向直下の領域に設けられたNチャネル型MOSトランジスタDC4とを備える。図5は、図2(a)におけるC-C<sup>°</sup>線の断面構造図である。図2及び図5を参照して、Pチャネル型MOSトランジスタDC3

は、ゲート電極31及び配線52を介して接地配線50に接続されるゲート電極33と、 N型ウェル10上に設けられたP型拡散層11とから形成される。ゲート電極33は、電 源配線40の直下に、電源配線の延在する方向と同じ方向に延在して形成されている。P 型拡散層11はコンタクトホール13を介して電源配線40に接続されている。このよう に、Pチャネル型MOSトランジスタDC3のソース・ドレイン拡散層に電源電圧VDD が印加され、ゲートに接地電圧GNDが印加される。図6は、図2(a)におけるD-D ′線の断面構造図である。図2及び図6を参照して、Nチャネル型MOSトランジスタD C 4 は、ゲート電極 3 2 及び配線 4 2 を介して電源配線 4 0 に接続されるゲート電極 3 4 と、 P 型ウェル 2 0 上に設けられた N 型拡散層 1 2 とから形成される。ゲート電極 3 4 は 、電源配線50の直下に、電源配線の延在する方向と同じ方向に延在して形成されている 。N型拡散層12は、コンタクトホールを介して接地配線50に接続されている。このよ うに、Nチャネル型MOSトランジスタDC4のソース・ドレイン拡散層に接地電圧GN Dが印加され、ゲートに電源電圧 V D D が印加される。このような構成により、図 7 ( a )に示されるような、ソース・ドレイン拡散層が電源VDDに接続され、ゲートがグラン ドGNDに接続されたPチャネル型MOSトランジスタ1と、ソース・ドレイン拡散層が グランドGNDに接続され、ゲートが電源VDDに接続されたNチャネル型トランジスタ 2とを備えるMOSキャパシタが電源配線40又は接地配線50下の領域に形成される。

[0024]

以上のように、電源配線40又は接地配線50のZ軸方向下方の領域に設置されるデカップリング容量領域において、回路領域に接続される電源VDD及びグランドGNDの電源ノイズを抑制することができる。

[0025]

又、Tap領域90は電源VDDに接続される電源配線40のZ軸方向直下の領域に設けられる。図2及び図5を参照して、Tap領域90は、Pチャネル型MOSトランジスタ群P1、P2、P3、DC3の基板となるN型ウェル10を電源VDDに接続するN型拡散層14及びコンタクトホール13を備える。このようなTap領域90によって電源VDDとN型ウェル100は接続され、N型ウェル10の電位を安定化することができる。Tap領域91はグランドGNDに接続される接地配線50のZ軸方向直下の領域に設けられる。図2及び図6を参照して、Tap領域91は、Nチャネル型MOSトランジスタ群N1、N2、N3、DC4の基板となるP型ウェル20をグランドGNDに接続するためのP型拡散層15及びコンタクトホール13を備える。Tap領域91によってグランドGNDとP型ウェル20は接続され、P型ウェル20の電位を安定化することができる。

[0026]

以上のように、電源配線40及び接地配線50の2方向直下の空いている領域にMOSトランジスタを形成して、より大きなゲート面積を確保することができる。このため、基本セル中の使用しないMOSトランジスタのゲート容量をデカップリング容量として利用するとともに、電源配線40及び接地配線50の下の領域にゲート容量を形成することで、チップ面積の増加を抑制しつつ、デカップリング容量を増大させることができる。従って、小チップ面積で電源ノイズを抑制することが可能となる。

[0027]

(第2の実施の形態)

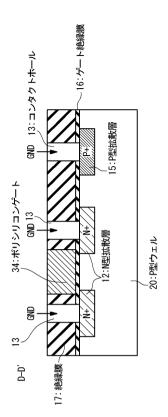

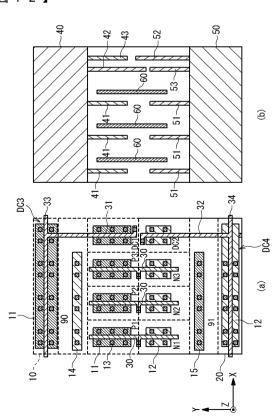

図8から図10を参照して、本発明による半導体装置の第2の実施の形態が説明される

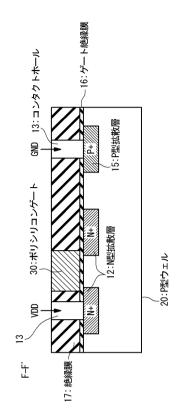

図 8 は、本発明による半導体装置の第 2 の実施の形態におけるレイアウト図である。 図 9 は、デカップリング容量を形成する P チャネル型 M O S トランジスタ D C 3 'と、 T a p 領域 9 0 の断面構造図である。

図10は、デカップリング容量を形成するNチャネル型MOSトランジスタDC4 ' と 、Tap領域91の断面構造図である。

[0028]

10

20

30

20

30

40

50

第2の実施の形態における半導体装置は、第1の実施の形態におけるPチャネル型MOSトランジスタDC3及びNチャネル型MOSトランジスタDC4に換えてPチャネル型MOSトランジスタDC4<sup>'</sup>を備える構成である。

## [0029]

第2の実施の形態におけるデカップリング容量領域は、電源配線40のZ軸方向直下の 領域に設けられたPチャネル型MOSトランジスタDC3′と、接地配線50のZ軸方向 直下の領域に設けられたNチャネル型MOSトランジスタDC4′とを備える。図9は、 図8(a)におけるE-E′線の断面構造図である。図8及び図9を参照して、Pチャネ ル型 M O S トランジスタ D C 3 ' は、ゲート電極 3 1 及び配線 5 2 を介して接地配線 5 0 に接続されるゲート電極33と、N型ウェル10上に設けられたP型拡散層11とから形 成される。Pチャネル型MOSトランジスタDC3′は、ソース又はドレインを形成する P型拡散層 1 1 の一方のみ(回路領域側)に設けられたコンタクトホール 1 3 を介して電 源配線40に接続されている。このため、Pチャネル型MOSトランジスタDC3′のソ ース又はドレインの一方に電源電圧 V D D が印加され、ゲートに接地電圧 G N D が印加さ れる。図10は、図8(a)におけるF-F′線の断面構造図である。図8及び図10を 参照して、Nチャネル型MOSトランジスタDC4′は、ゲート電極32及び配線42を 介して電源配線40に接続されるゲート電極34と、P型ウェル20上に設けられたN型 拡散層12とから形成される。Nチャネル型MOSトランジスタDC4'は、ソース又は ドレインを形成するN型拡散層12の一方のみ(回路領域側)に設けられたコンタクトホ ール13を介して接地配線50に接続されている。このため、Nチャネル型MOSトラン ジスタDC4'のソース又はドレインの一方に接地電圧GNDが印加され、ゲートに電源 電圧VDDが印加される。このような構成により、図7(b)に示されるような、ソース 又はドレインの一方が電源VDDに接続され、ゲートがグランドGNDに接続されたPチ ャネル型MOSトランジスタ1と、ソース又はドレインの一方がグランドGNDに接続さ れ、ゲートが電源VDDに接続されたNチャネル型トランジスタ2とを備えるMOSキャ パシタが電源配線40又は接地配線50下の領域に形成される。

## [0030]

第2の実施の形態によれば、電源配線40又は接地配線50直下の領域において、Tap領域90、91と回路領域との間の面積が小さく、コンタクトホール13を配置するスペースを多く確保できない場合に有効である。

## [0031]

(第3の実施の形態)

図11を参照して、本発明による半導体装置の第3の実施の形態が説明される。

図11は、本発明による半導体装置の第3の実施の形態におけるレイアウト図である。

第3の実施の形態におけるTap領域90及びTap領域91は、回路領域と接続する電源VDD又はグランドGNDとは別系統の電源又はグランドに接続される電源配線70又は接地配線80に接続される構成である。

### [0032]

図11(a)は、下層から、素子の基板となるウェル層、拡散層、ポリシリコン層、コンタクト層の順で構成される素子部のレイアウト図である。図11(b)は、図11(a)に示される素子部のZ軸方向上部に配されるメタル配線層で構成される配線部のレイアウト図である。ここで第3の実施の形態における素子部は、第1の実施の形態と同じ構成であるので説明は省略される。

#### [0033]

図11(b)を参照して、配線層において電源配線40及び接地配線50は、X軸方向に延設される。電源配線70は、回路領域に電源電位VDDを与える電源配線40に対し並行に設けられる。又、接地配線80は、回路領域に接地電位GNDを与える接地配線50に対し並行に設けられる。図11(a)を参照して、Tap領域90は、電源配線70のZ軸方向直下に設けられ、N型拡散層12及びコンタクトホール13を介して電源配線

20

30

50

70に接続され、回路領域におけるPチャネル型MOSトランジスタP1、P2、P3のN型ウェル10の電位を安定化する。同様に、Tap領域91は、接地配線80のZ軸方向直下に設けられ、P型拡散層15及びコンタクトホール13を介して接地配線80に接続され、回路領域におけるNチャネル型MOSトランジスタN1、N2、N3のP型ウェル20の電位を安定化する。

#### [0034]

本発明によるTap領域90、91は、基板ノイズに敏感なアナログ回路とデジタル回路が混載したLSI等において基板ノイズを遮断するガードリングの役割を担っている。第3の実施の形態における半導体装置のTap領域90、91は、回路領域に接続される電源VDD又はグランドGNDと異なる系統の電源配線70又は接地配線80に接続されるため、第1及び第2の実施の形態よりも効果的に基板ノイズを遮断することができる。尚、本実施の形態における素子部は第1の実施の形態と同様の構成として説明されたが、第2の実施の形態と同様の構成、すなわち一端が開放されたMOSキャパシタを利用したデカップリング容量領域及びデカップリング容量セルが設けられた構成でも構わない。

#### [0035]

以上のように、本発明による半導体装置によれば、電源配線及び接地配線下の空いている領域を有効に利用してゲート面積を大きくできるため、CMOS LSIのデジタル回路においてチップ面積を増大させることなく、電源ノイズの抑制量を増加することができる。このため、電源ノイズによる誤動作、動作速度の低下を抑制することができ、特に電源ノイズに敏感なアナログ・デジタル混載LSI等では耐電源ノイズ特性を向上させることができる。

## [0036]

以上、本発明の実施の形態を詳述してきたが、具体的な構成は上記実施の形態に限られるものではなく、本発明の要旨を逸脱しない範囲の変更があっても本発明に含まれる。実施の形態において、CMOS基本セルとしてCMOSインバータを用いて説明したが、NANDゲート、NORゲート、ANDゲート、ORゲート、フリップフロップ等任意のCMOSセルであってもよいし、これらの組み合わせて配置したCMOS基本セルとでもよい。又、第1及び2の実施の形態におけるTap領域90、91は、デカップリング容量は、の外側に設けられた構成であるが、図12に示されるように、回路領域に隣接し、ップリング容量領域との間にTap領域90及びTap領域91を配置すカップリング容量領域との間にTap領域90及びTap領域91を配置すカップリング容量領域との間にTap領域90及びTap領域91を配置するのアチャネル型トランジスタ群P1、P2、P3に隣接するN型ウェル10にN型拡散層14及びコンタクトホール13が設けられ、電源配線40に接続されてN型ウェル10の電位を安定化する。又、Tap領域91は、回路領域のNチャネル型トランジスタ群N1、N2、N3に隣接するP型ウェル20にP型拡散層15及びコンタクトホール13が設けられ、接地配線50に接続されてP型ウェル20の電位を安定化する。尚、図12(a)を参照して、配線部は第1及び第2の実施の形態と同じ構成である。

【図面の簡単な説明】

## [0037]

【図1】図1は、従来技術によるデカップリング容量を備えた半導体装置のレイアウト図 40 である。

【図2】図2は、本発明によるデカップリング容量を備えた半導体装置の第1の実施の形態におけるレイアウト図である。

【図3】図3は、本発明に係る回路領域においてCMOSインバータを形成するPチャネル型MOSトランジスタと、デカップリング容量セルを形成するPチャネル型MOSトランジスタの断面構造図である。

【図4】図4は、本発明に係る回路領域においてCMOSインバータを形成するNチャネル型MOSトランジスタと、デカップリング容量セルを形成するNチャネル型MOSトランジスタの断面構造図である。

【図5】図5は、本発明に係るデカップリング容量を形成するPチャネル型MOSトラン

ジスタと、Tap領域の断面構造図である。

【図6】図6は、本発明に係るデカップリング容量を形成するNチャネル型MOSトラン ジスタと、Tap領域の断面構造図である。

【図7】図7は、本発明に係るデカップリング容量を形成するMOSキャパシタの回路図 である。

【図8】図8は、本発明に係るデカップリング容量を備えた半導体装置の第2の実施の形 態におけるレイアウト図である。

【図9】図9は、第2の実施の形態におけるデカップリング容量を形成するPチャネル型 MOSトランジスタと、Tap領域の断面構造図である。

【図10】図10は、第2の実施の形態におけるデカップリング容量を形成するNチャネ ル型MOSトランジスタと、Tap領域の断面構造図である。

【図11】図11は、本発明によるデカップリング容量を備えた半導体装置の第3の実施 の形態におけるレイアウト図である。

【図12】図12は、本発明によるデカップリング容量を備える半導体装置の変形例のレ イアウト図である。

#### 【符号の説明】

#### [0038]

10、100:N型ウェル

20、200: P型ウェル

20 3 0 、 3 1 、 3 2 、 3 3 、 3 4 、 3 0 0 、 3 1 0 、 3 2 0 : ゲート電極 ( ポリシリコンゲ **- | | |**

40、41、70、400、410:電源配線

50、51、80、500、510:接地配線

41、42、43、51、52、53、60、410、420、430、510、520 、530、600:配線

90、91、900、910: Tap領域

1 1 、 1 5 、 1 1 0 、 1 5 0 : P型拡散層

12、14、120、140:N型拡散層

13、130: コンタクトホール

16:ゲート絶縁膜

17: 絶縁膜

V D D:電源(電源電位)

**GND: グランド(接地電位)**

1、P1、P2、P3、DC1、DC3、P10、P20、P30、DC10、DC30

: P チャネル型 M O S トランジスタ

2、N1、N2、N3、DC2、DC4、N10、N20、N30、DC20、DC40

: N チャネル型 M O S トランジスタ

10

(a)

【図1】 【図2】

【図3】 【図4】

【図5】 【図6】

【図7】 【図8】

【図9】 【図10】

【図11】

【図12】

## フロントページの続き

(51) Int.CI. F I

**H 0 1 L 27/092 (2006.01)** H 0 1 L 27/04 C

H 0 1 L 27/118 (2006.01) H 0 1 L 21/82 (2006.01)

(58)調査した分野(Int.CI., DB名)

H01L 21/822

H01L 21/82

H01L 21/8234

H01L 21/8238

H01L 27/04

H01L 27/06

H01L 27/092

H01L 27/118